Похожие презентации:

Периферійні вузли AVR - мікроконтролерів

1.

Національний аерокосмічний університет ім. М.Є. ЖуковськогоЦифрові пристрої

Digital devices

&

Microprocessors

Мікропроцесори

Тема 10:

Периферійні вузли AVR-мікроконтролерів.

Модуль ПЗПД (ППЗПЕС).

к.т.н., доцент каф.501

Мазуренко О.В.

2.

1Регістри керування ПЗПД (ППЗПЕС)

Регістр адреси ППЗПЕС (EEAR – EEPROM Address Register)

Біти:

15

14

13

12

11

10

9

$1F ($3F) EEARH:

$1E ($3E) EEARL: EEAR7 EEAR6 EEAR5 EEAR4 EEAR3 EEAR2 EEAR1

Біти

7

6

5

4

3

2

1

R

R

R

R

R

R

R

Режим доступу:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

Початковий стан:

x

x

x

x

x

x

x

Bits 15…9 – Res: Reserved Bits – Зарезервовані біти

Bits 8…0 – EEAR8..0: EEPROM Address – Біти адреси ППЗПЕС

Регістр даних ППЗПЕС (EEDR – EEPROM Data Register)

Біти:

7

6

5

4

3

2

$1D ($3D)

EEDR: EEDR7 EEDR6 EEDR5 EEDR4 EEDR3 EEDR2

Режим доступу:

R/W

R/W

R/W

R/W

R/W

R/W

Початковий стан:

0

0

0

0

0

0

1

EEDR1

R/W

0

8

EEAR8

EEAR0

0

R/W

R/W

x

x

0

EEDR0

R/W

0

Bits 7…0 – EEDR7..0: EEPROM Data bits – Біти даних ППЗПЕС

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

3.

2Регістр керування ПЗПД. Обмін даними з ПЗПД

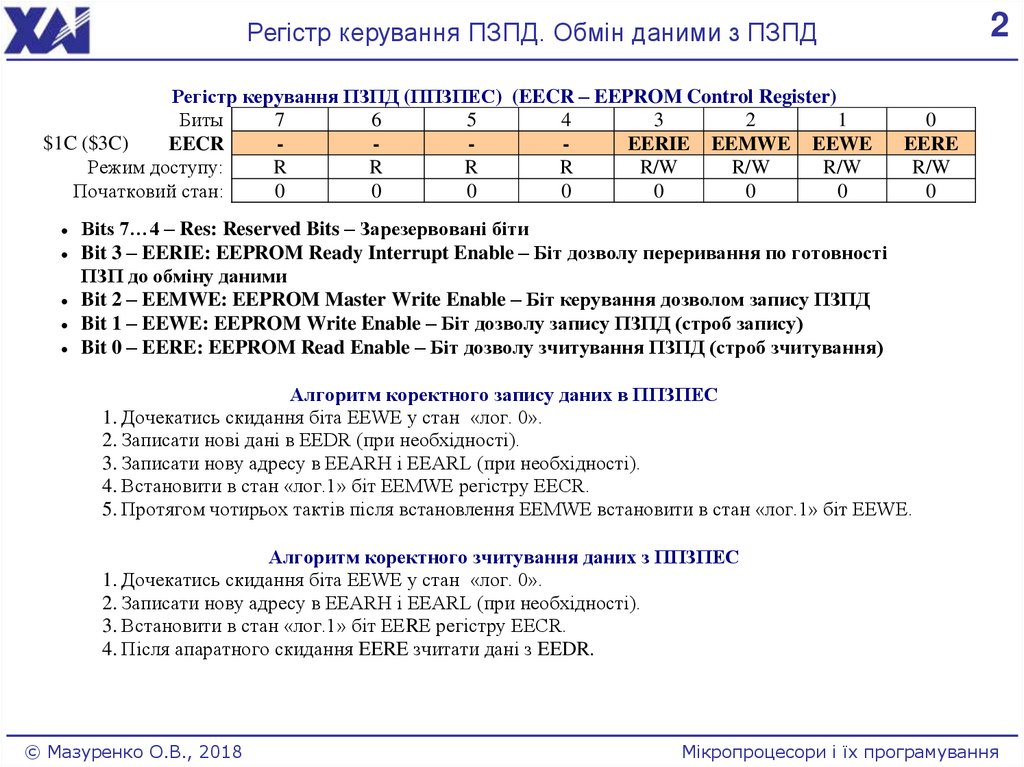

Регістр керування ПЗПД (ППЗПЕС) (EECR – EEPROM Control Register)

Биты

7

6

5

4

3

2

1

$1C ($3C)

EECR

EERIE EEMWE EEWE

Режим доступу:

R

R

R

R

R/W

R/W

R/W

Початковий стан:

0

0

0

0

0

0

0

0

EERE

R/W

0

Bits 7…4 – Res: Reserved Bits – Зарезервовані біти

Bit 3 – EERIE: EEPROM Ready Interrupt Enable – Біт дозволу переривання по готовності

ПЗП до обміну даними

Bit 2 – EEMWE: EEPROM Master Write Enable – Біт керування дозволом запису ПЗПД

Bit 1 – EEWE: EEPROM Write Enable – Біт дозволу запису ПЗПД (строб запису)

Bit 0 – EERE: EEPROM Read Enable – Біт дозволу зчитування ПЗПД (строб зчитування)

Алгоритм коректного запису даних в ППЗПЕС

1. Дочекатись скидання біта EEWE у стан «лог. 0».

2. Записати нові дані в EEDR (при необхідності).

3. Записати нову адресу в EEARH і EEARL (при необхідності).

4. Встановити в стан «лог.1» біт EEMWE регістру EECR.

5. Протягом чотирьох тактів після встановлення EEMWE встановити в стан «лог.1» біт EEWE.

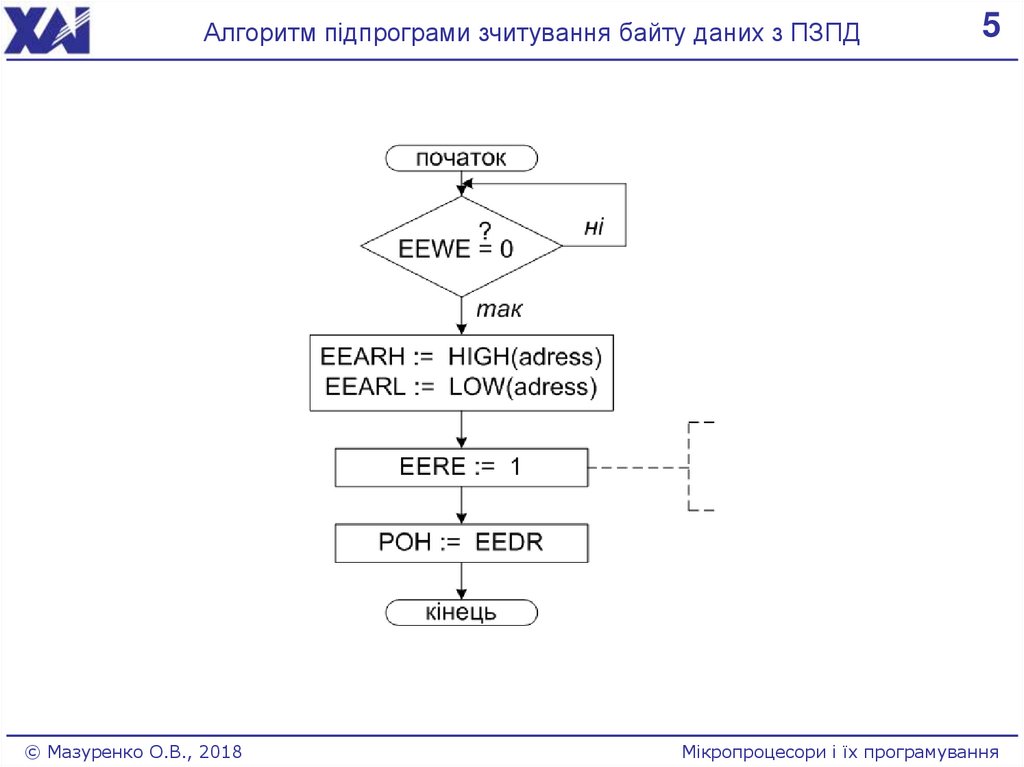

Алгоритм коректного зчитування даних з ППЗПЕС

1. Дочекатись скидання біта EEWE у стан «лог. 0».

2. Записати нову адресу в EEARH і EEARL (при необхідності).

3. Встановити в стан «лог.1» біт EERE регістру EECR.

4. Після апаратного скидання EERE зчитати дані з EEDR.

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

4.

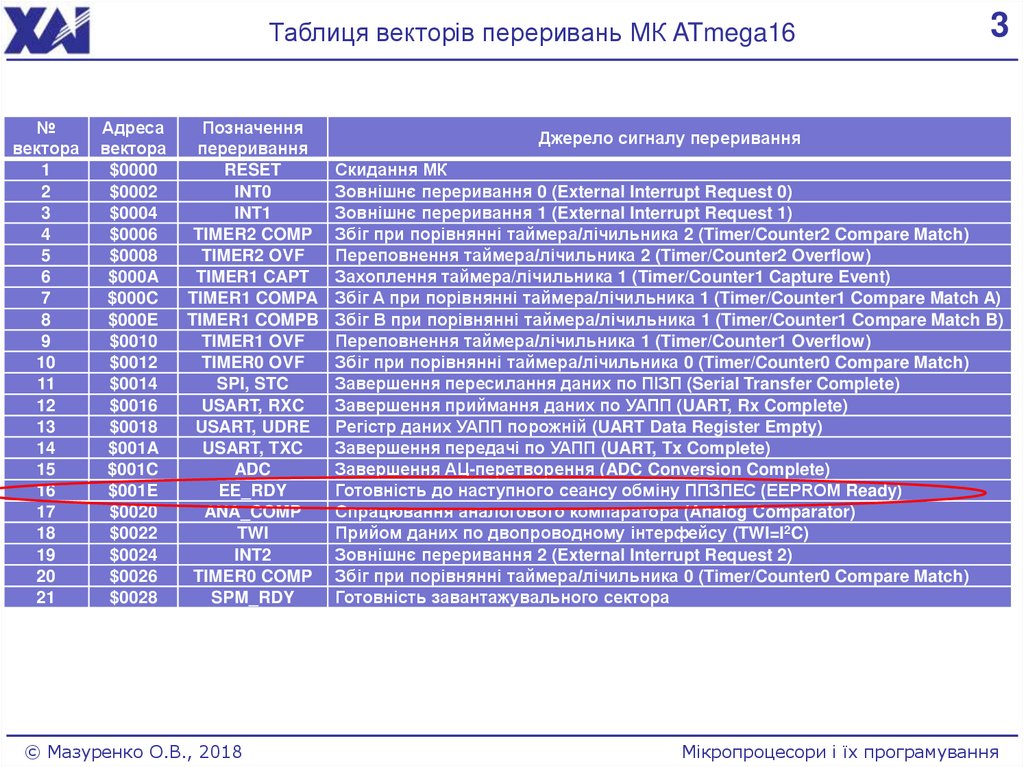

Таблиця векторів переривань МК ATmega16№

вектора

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

Адреса

вектора

$0000

$0002

$0004

$0006

$0008

$000A

$000C

$000E

$0010

$0012

$0014

$0016

$0018

$001A

$001C

$001E

$0020

$0022

$0024

$0026

$0028

Позначення

переривання

RESET

INT0

INT1

TIMER2 COMP

TIMER2 OVF

TIMER1 CAPT

TIMER1 COMPA

TIMER1 COMPB

TIMER1 OVF

TIMER0 OVF

SPI, STC

USART, RXC

USART, UDRE

USART, TXC

ADC

EE_RDY

ANA_COMP

TWI

INT2

TIMER0 COMP

SPM_RDY

© Мазуренко О.В., 2018

3

Джерело сигналу переривання

Скидання МК

Зовнішнє переривання 0 (External Interrupt Request 0)

Зовнішнє переривання 1 (External Interrupt Request 1)

Збіг при порівнянні таймера/лічильника 2 (Timer/Counter2 Compare Match)

Переповнення таймера/лічильника 2 (Timer/Counter2 Overflow)

Захоплення таймера/лічильника 1 (Timer/Counter1 Capture Event)

Збіг A при порівнянні таймера/лічильника 1 (Timer/Counter1 Compare Match A)

Збіг В при порівнянні таймера/лічильника 1 (Timer/Counter1 Compare Match B)

Переповнення таймера/лічильника 1 (Timer/Counter1 Overflow)

Збіг при порівнянні таймера/лічильника 0 (Timer/Counter0 Compare Match)

Завершення пересилання даних по ПІЗП (Serial Transfer Complete)

Завершення приймання даних по УАПП (UART, Rx Complete)

Регістр даних УАПП порожній (UART Data Register Empty)

Завершення передачі по УАПП (UART, Tx Complete)

Завершення АЦ-перетворення (ADC Conversion Complete)

Готовність до наступного сеансу обміну ППЗПЕС (EEPROM Ready)

Спрацювання аналогового компаратора (Analog Comparator)

Прийом даних по двопроводному інтерфейсу (TWI=I2C)

Зовнішнє переривання 2 (External Interrupt Request 2)

Збіг при порівнянні таймера/лічильника 0 (Timer/Counter0 Compare Match)

Готовність завантажувального сектора

Мікропроцесори і їх програмування

5.

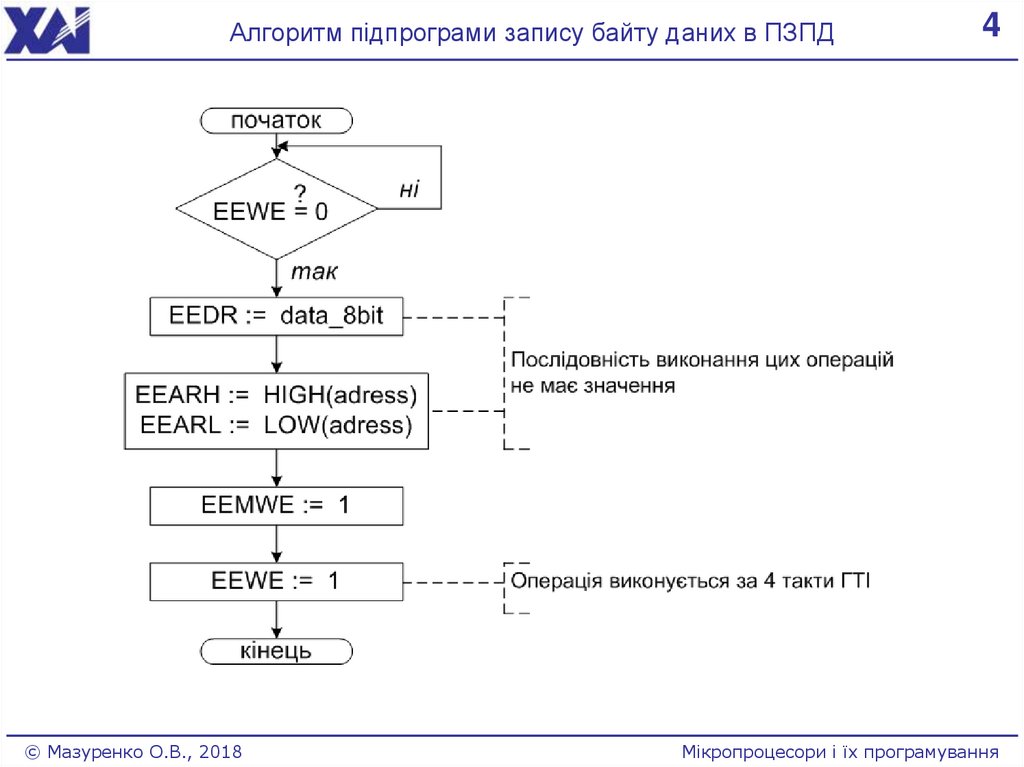

Алгоритм підпрограми запису байту даних в ПЗПД© Мазуренко О.В., 2018

4

Мікропроцесори і їх програмування

6.

Алгоритм підпрограми зчитування байту даних з ПЗПД© Мазуренко О.В., 2018

5

Мікропроцесори і їх програмування

7.

Рекомендації по захисту ПЗПД від некоректного запису даних6

- Утримання сигналу скидання в активному (низькому) стані підчас

зниження напруги живлення за допомогою зовнішньої або

внутрішньої схеми захисту від зниження напруги живлення (BrownOut Detector (BOD).

- Утримання ядра МК в енергозбережному режимі Power Down

підчас зниження напруги живлення.

- Збереження констант в ПЗП програм, якщо немає необхідності

змінювати їх в програмі.

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

Электроника

Электроника