Похожие презентации:

Интерфейс SPI (лекция 8)

1.

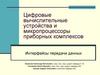

Интерфейс SPI1

2.

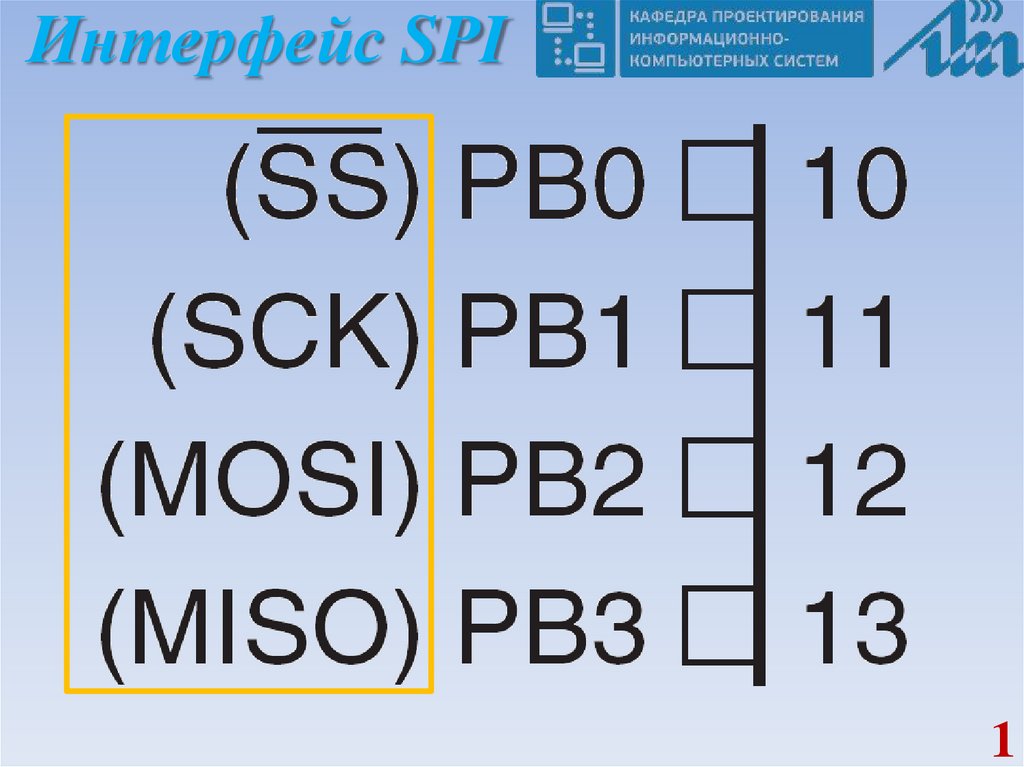

Интерфейс SPIСоединение

SPI-устройств

SPI – Serial Peripheral

Interface

MOSI – Master Output

Slave Input

MISO – Master Input

Slave Output

SCK – Serial ClocK 2

3.

Интерфейс SPIПространственная адресация

SPI-устройств с посредством

дешифратора

3

4.

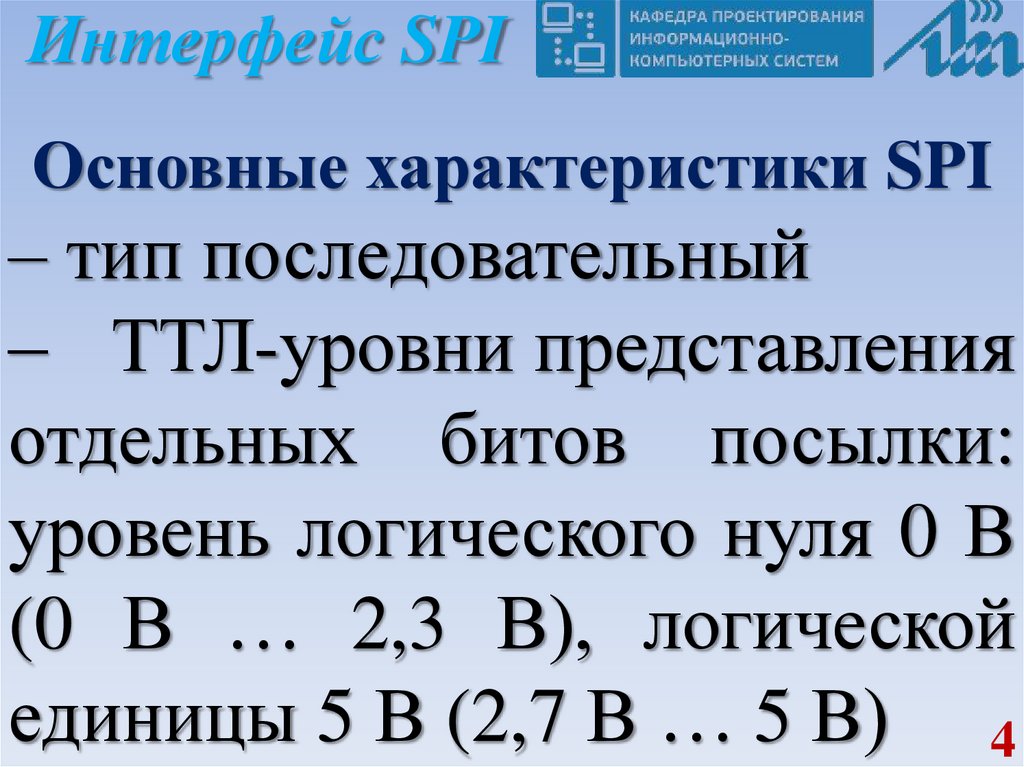

Интерфейс SPIОсновные характеристики SPI

– тип последовательный

– ТТЛ-уровни представления

отдельных битов посылки:

уровень логического нуля 0 В

(0 В … 2,3 В), логической

единицы 5 В (2,7 В … 5 В) 4

5.

Интерфейс SPIОсновные характеристики SPI

– интерфейс синхронный;

– протокол гибкий;

– интерфейс

двунаправленный

(полнодуплексный);

– расстояние связи до 10 м

5

6.

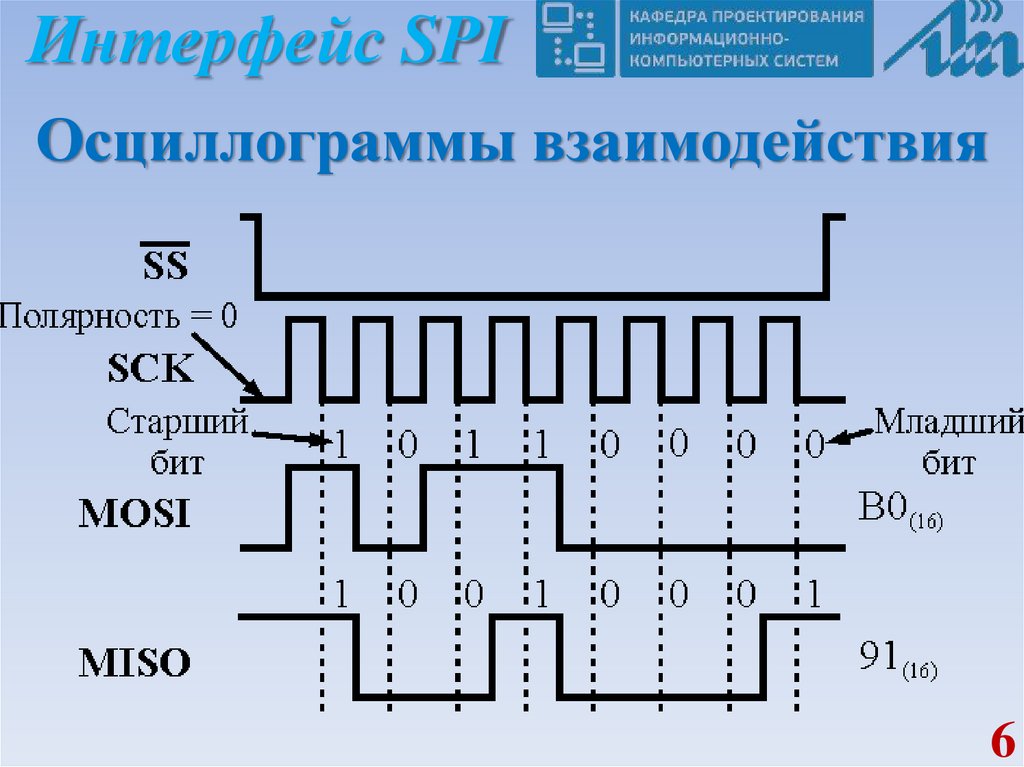

Интерфейс SPIОсциллограммы взаимодействия

6

7.

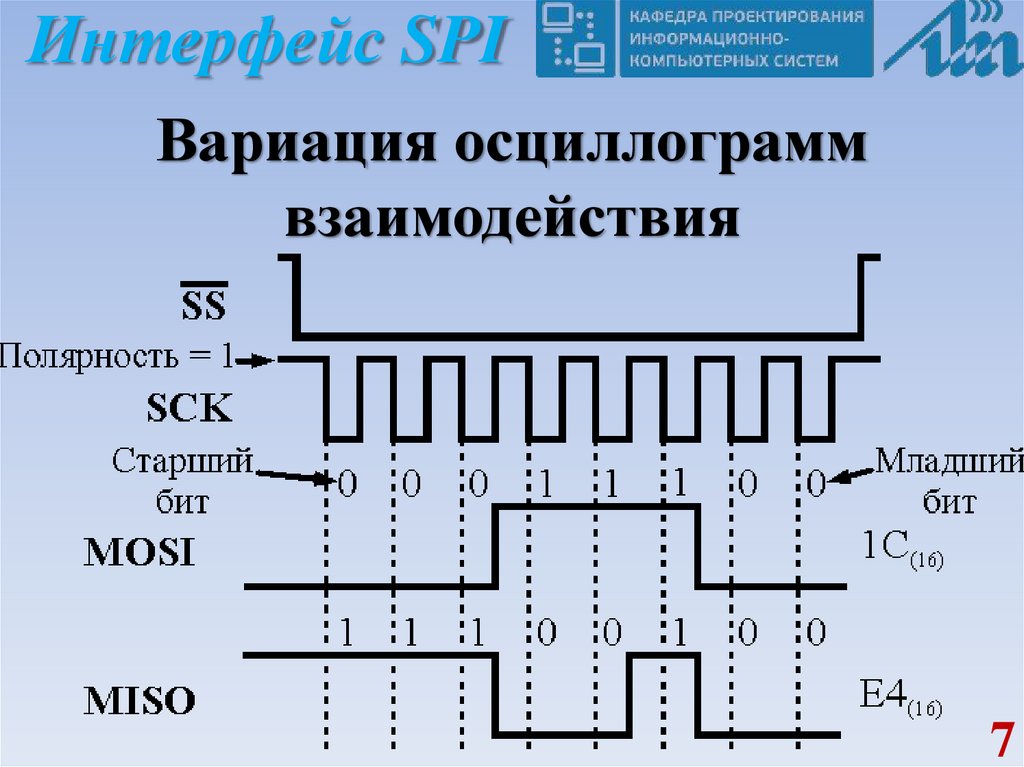

Интерфейс SPIВариация осциллограмм

взаимодействия

7

8.

Интерфейс SPIОсновное событие в SPI

завершение передачи/

приёма данного →

единственный бит

состояния – бит SPIF

8

9.

Интерфейс SPIВнешнее соединение ведущего и ведомого

Тактирование осуществляется ведущим!!!

9

10.

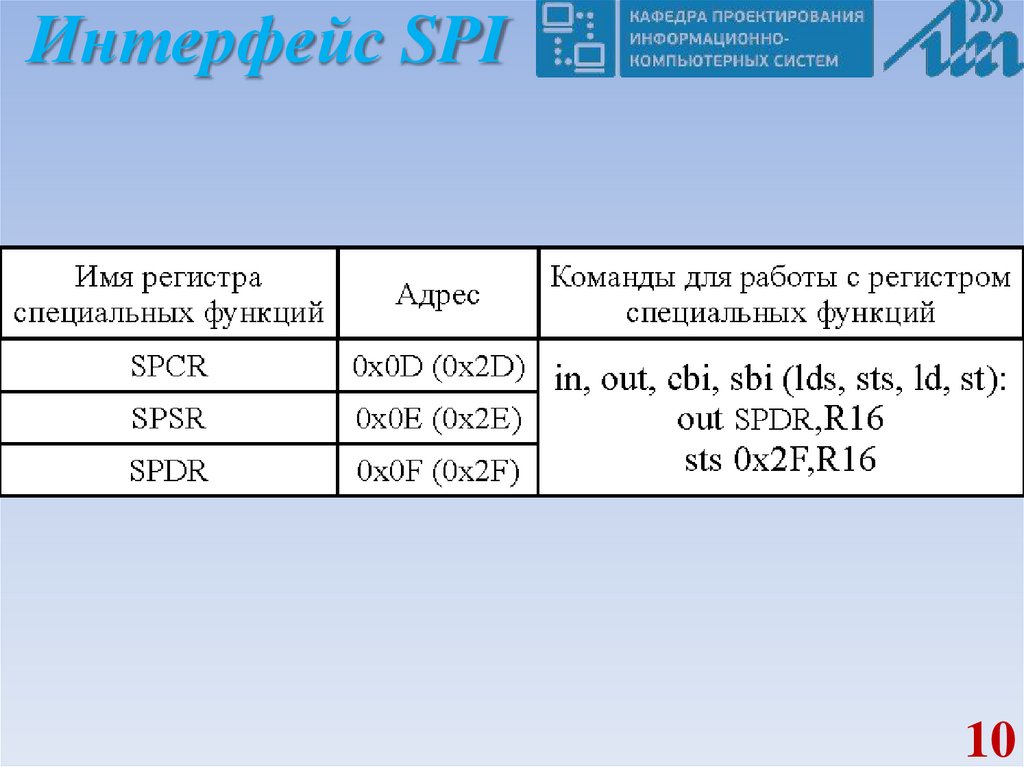

Интерфейс SPI10

11.

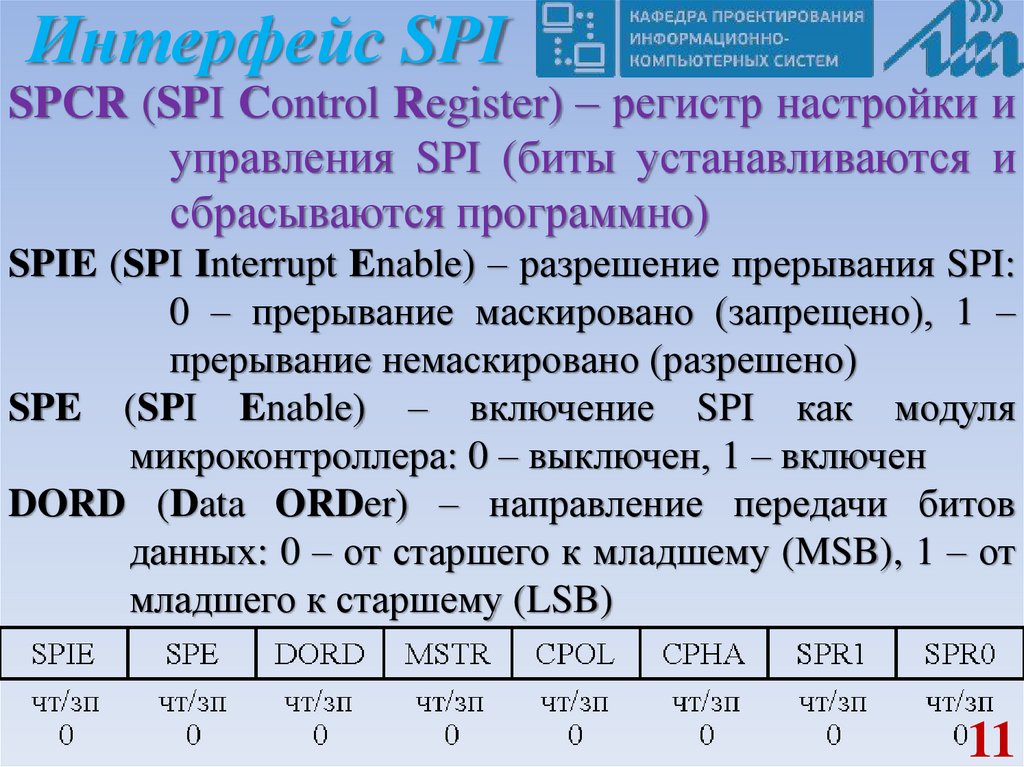

Интерфейс SPISPCR (SPI Control Register) – регистр настройки и

управления SPI (биты устанавливаются и

сбрасываются программно)

SPIE (SPI Interrupt Enable) – разрешение прерывания SPI:

0 – прерывание маскировано (запрещено), 1 –

прерывание немаскировано (разрешено)

SPE (SPI Enable) – включение SPI как модуля

микроконтроллера: 0 – выключен, 1 – включен

DORD (Data ORDer) – направление передачи битов

данных: 0 – от старшего к младшему (MSB), 1 – от

младшего к старшему (LSB)

11

12.

Интерфейс SPIMSTR (MaSTeR) – включение режима «ведущего»:

0 – режим «ведущего» выключен, 1 – режим

«ведущего» включен

CPOL (Clock POLarity) – уровень (полярность) линии

SCK синхронизации в состоянии ожидания, т.е. во время

паузы между приёмопередачей: 0 – низкий, 1 – высокий

12

13.

Интерфейс SPISPCR (SPI Control Register) – регистр настройки и

управления SPI (биты устанавливаются и

сбрасываются программно)

CPHA (Clock PHAse) – фаза синхронизации, т.е. фаза

установки или выборки бита данных

13

14.

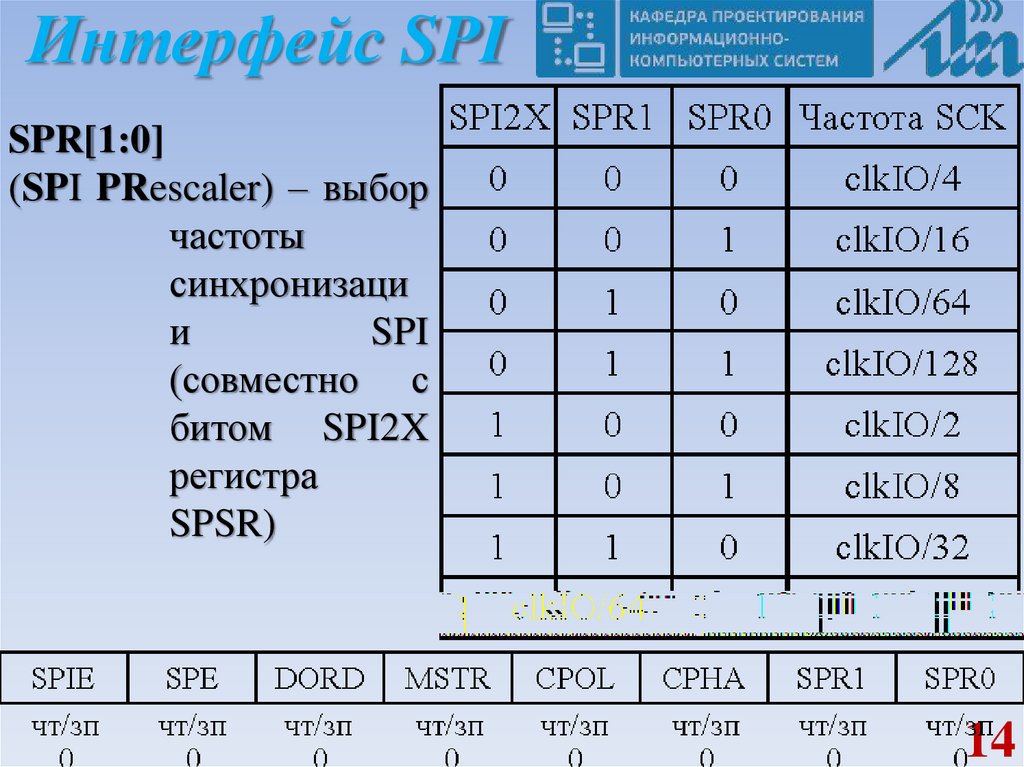

Интерфейс SPISPR[1:0]

(SPI PRescaler) – выбор

частоты

синхронизаци

и

SPI

(совместно с

битом SPI2X

регистра

SPSR)

14

15.

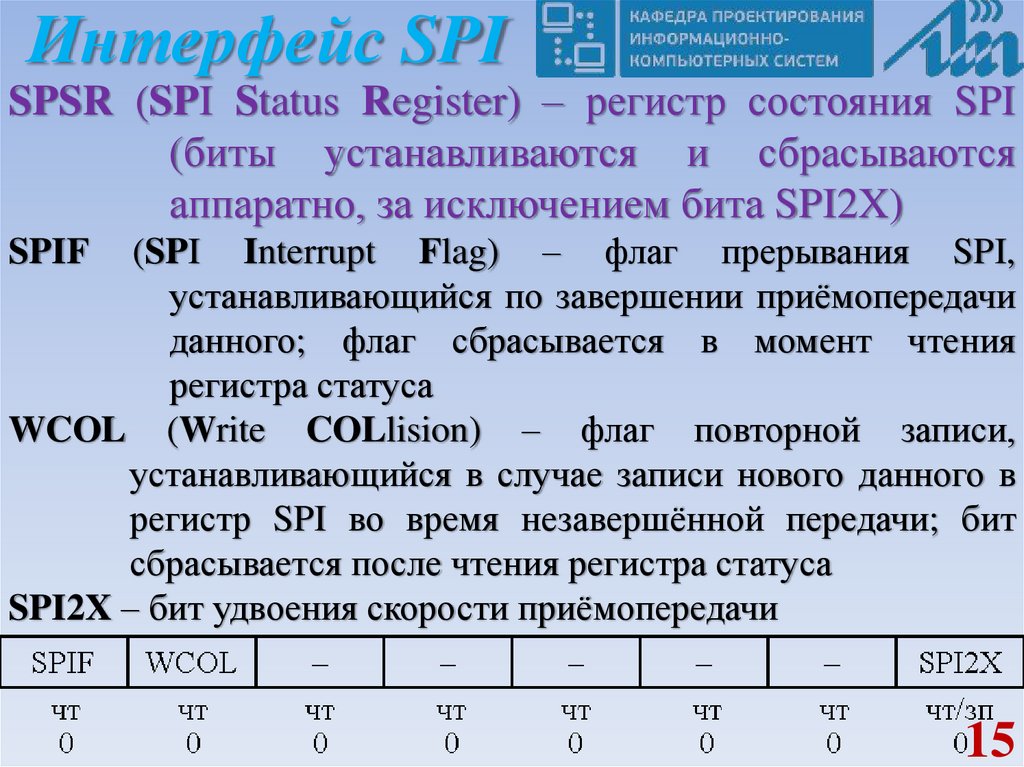

Интерфейс SPISPSR (SPI Status Register) – регистр состояния SPI

(биты устанавливаются и сбрасываются

аппаратно, за исключением бита SPI2X)

(SPI Interrupt Flag) – флаг прерывания SPI,

устанавливающийся по завершении приёмопередачи

данного; флаг сбрасывается в момент чтения

регистра статуса

WCOL (Write COLlision) – флаг повторной записи,

устанавливающийся в случае записи нового данного в

регистр SPI во время незавершённой передачи; бит

сбрасывается после чтения регистра статуса

SPI2X – бит удвоения скорости приёмопередачи

SPIF

15

16.

Интерфейс SPISPDR (SPI Data Register) – регистр данных SPI (биты

устанавливаются и сбрасываются программно)

Режимы

передачи

данных

16

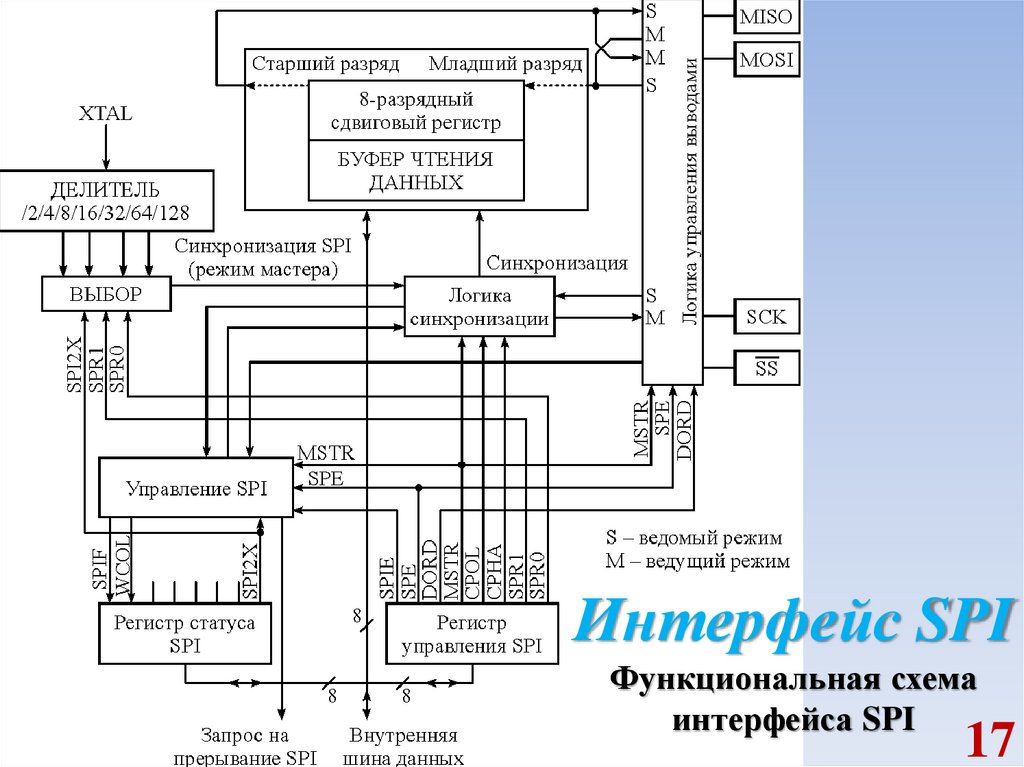

17.

Интерфейс SPIФункциональная схема

интерфейса SPI

17

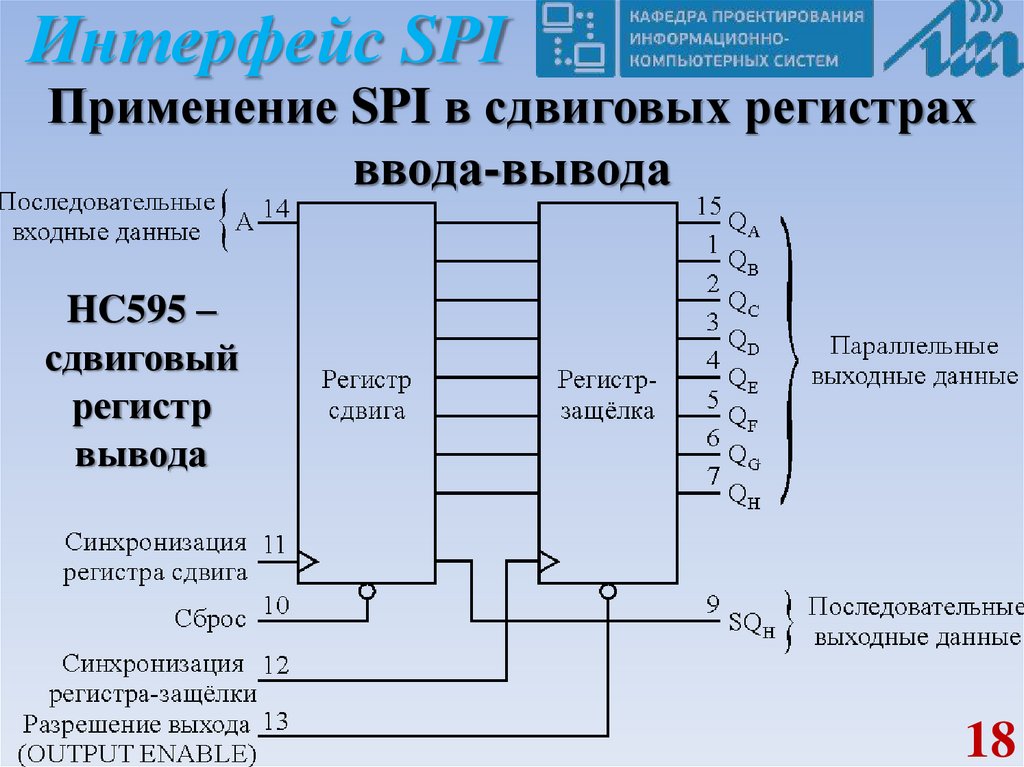

18.

Интерфейс SPIПрименение SPI в сдвиговых регистрах

ввода-вывода

HC595 –

сдвиговый

регистр

вывода

18

19.

Интерфейс SPIДемонстрационное

видео моделирования

работы выходного

регистра сдвига

HC595

19

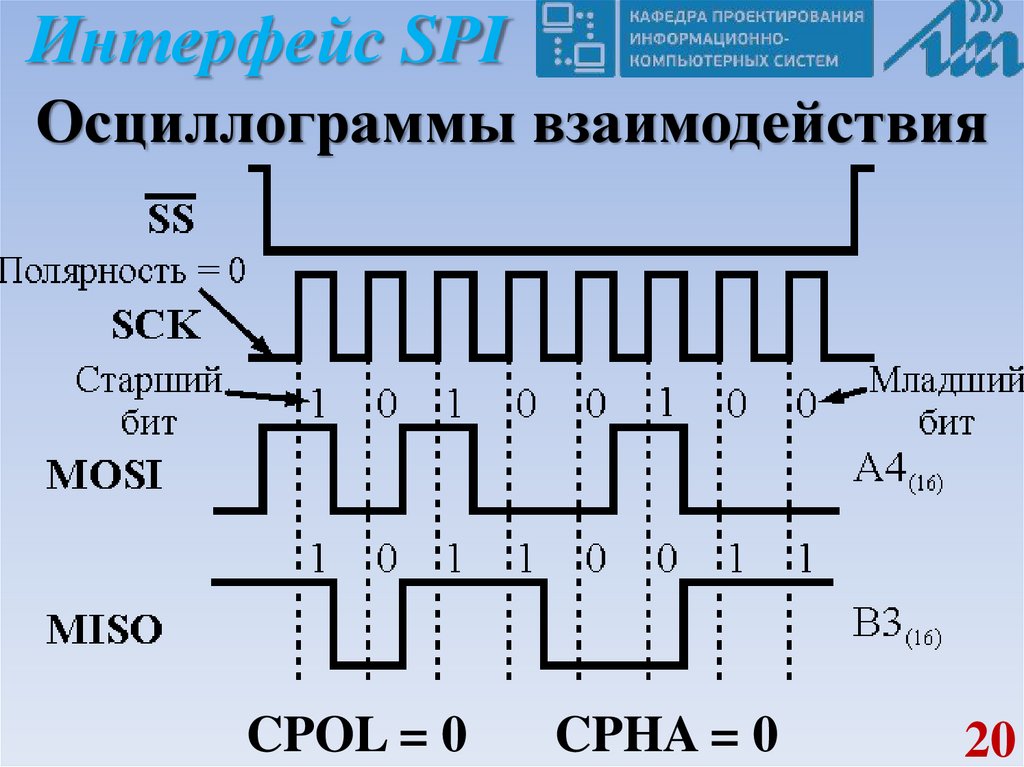

20.

Интерфейс SPIОсциллограммы взаимодействия

CPOL = 0

CPHA = 0

20

21.

Интерфейс SPIДемонстрационное

видео применения

сдвигового регистра в

дисплее

21

22.

Интерфейс SPI22

23.

Интерфейс SPI23

24.

Интерфейс SPI24

25.

Интерфейс SPI25

26.

Интерфейс SPI26

27.

Интерфейс SPI27

28.

Интерфейс SPI28

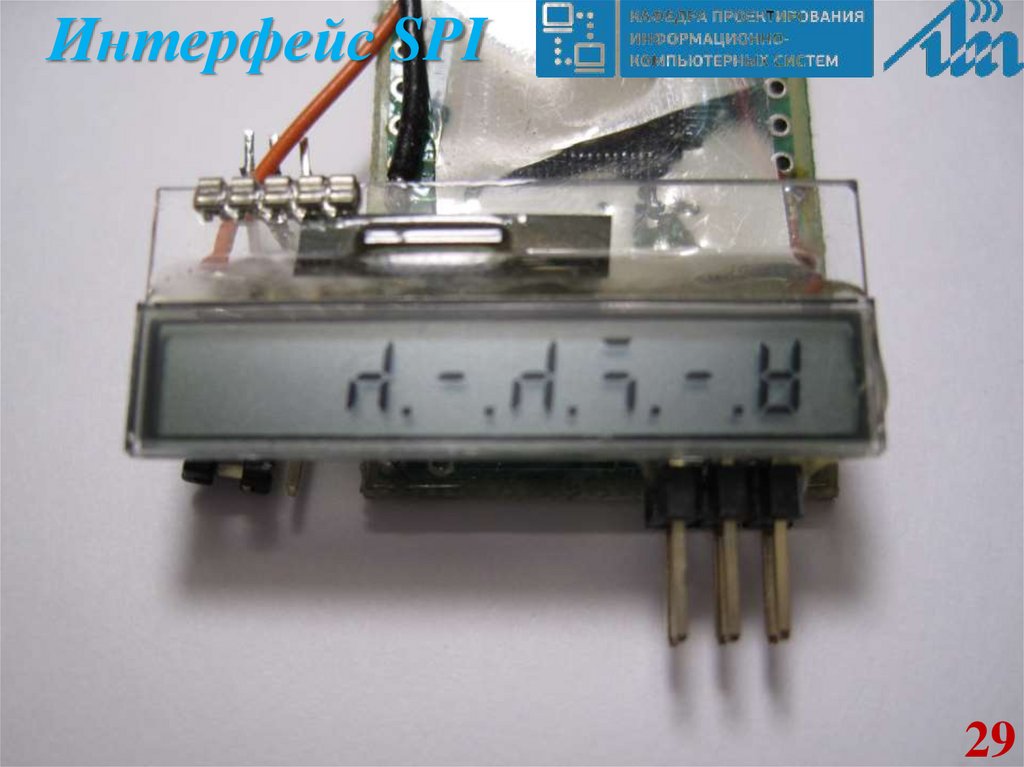

29.

Интерфейс SPI29

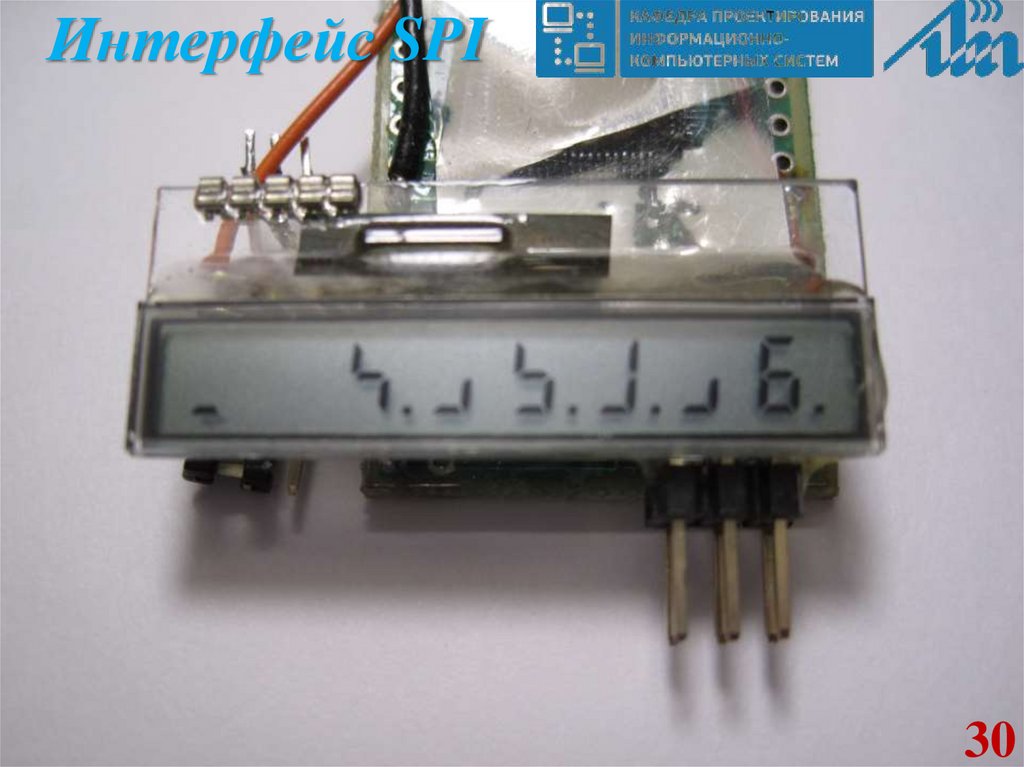

30.

Интерфейс SPI30

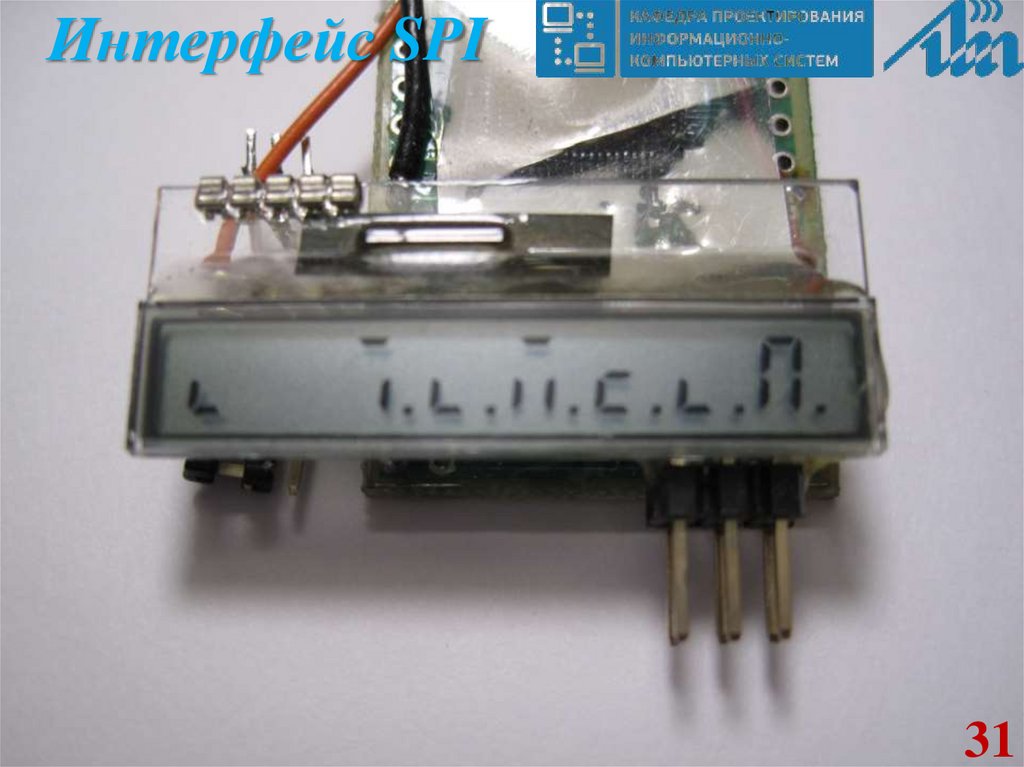

31.

Интерфейс SPI31

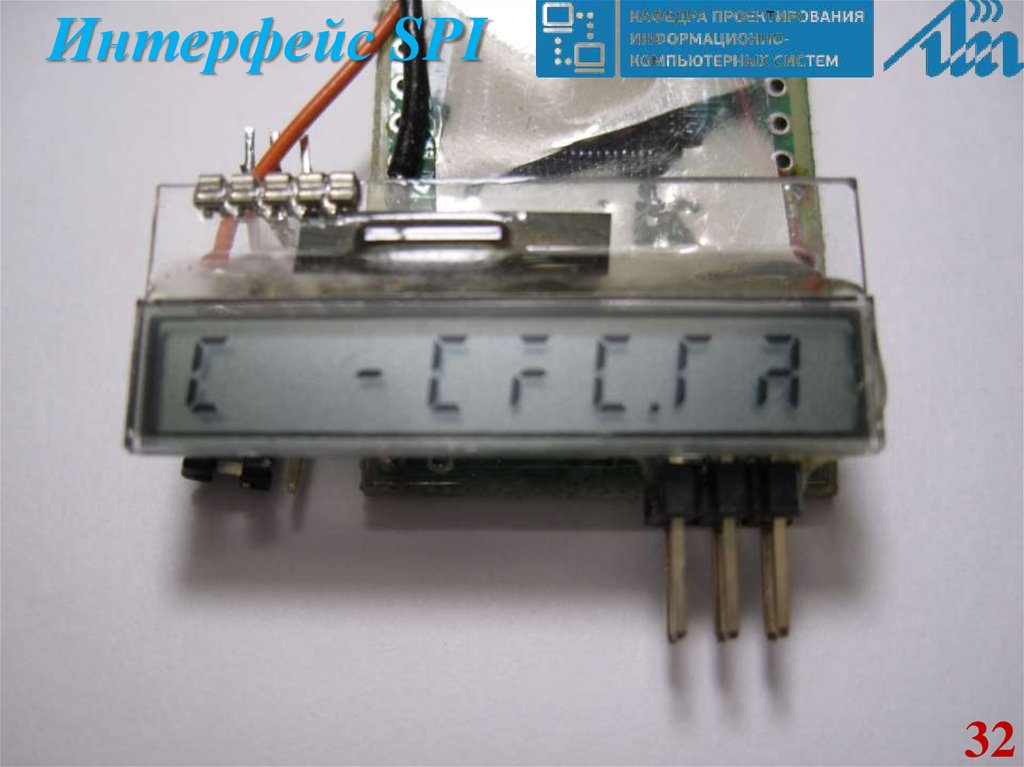

32.

Интерфейс SPI32

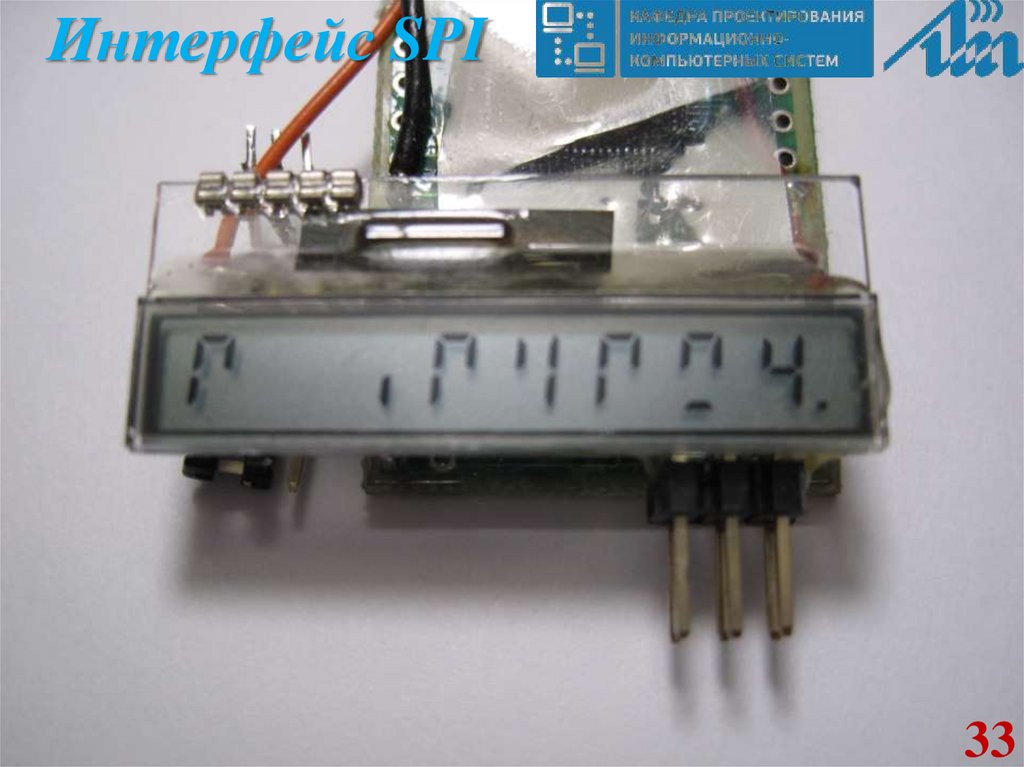

33.

Интерфейс SPI33

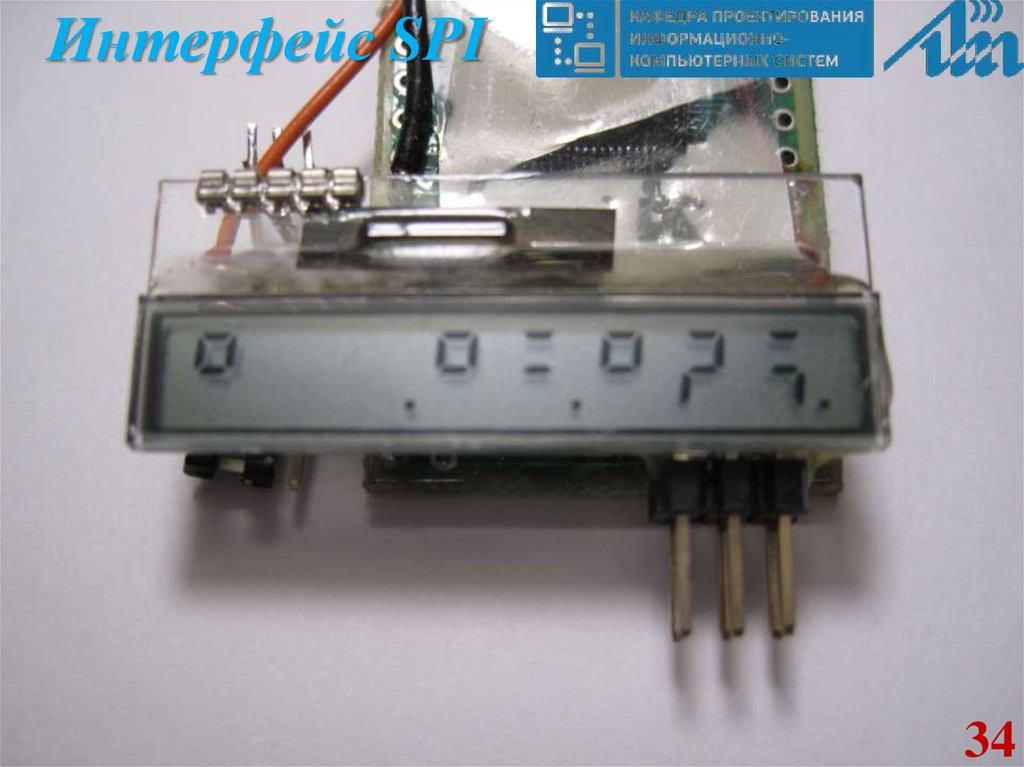

34.

Интерфейс SPI34

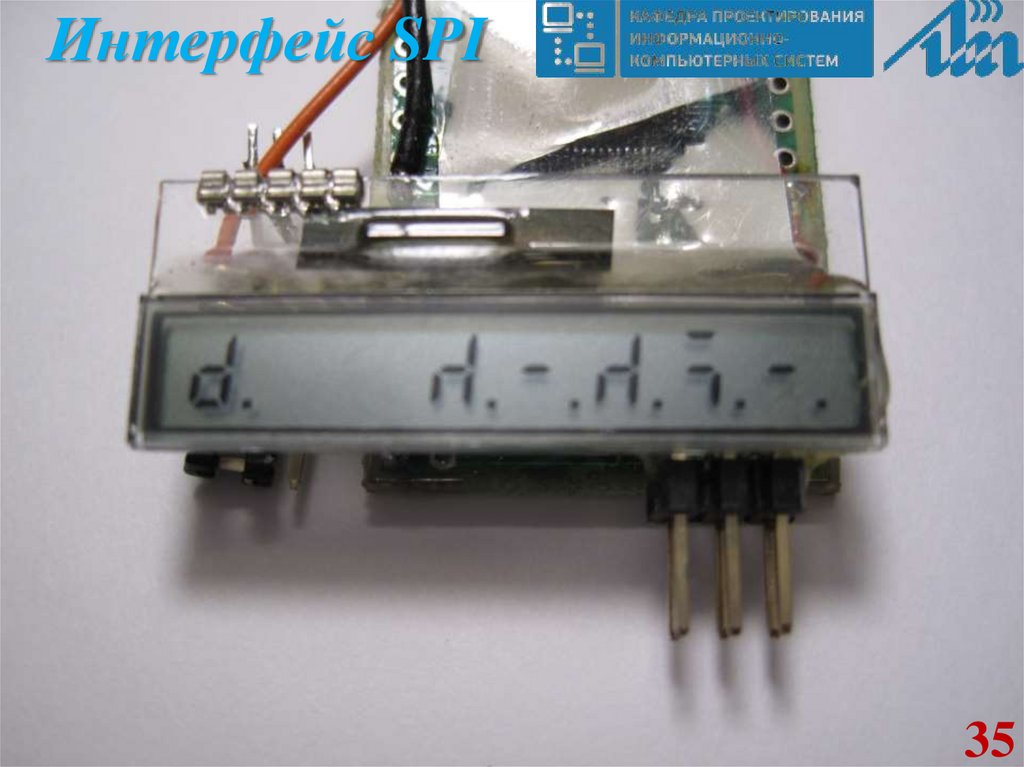

35.

Интерфейс SPI35

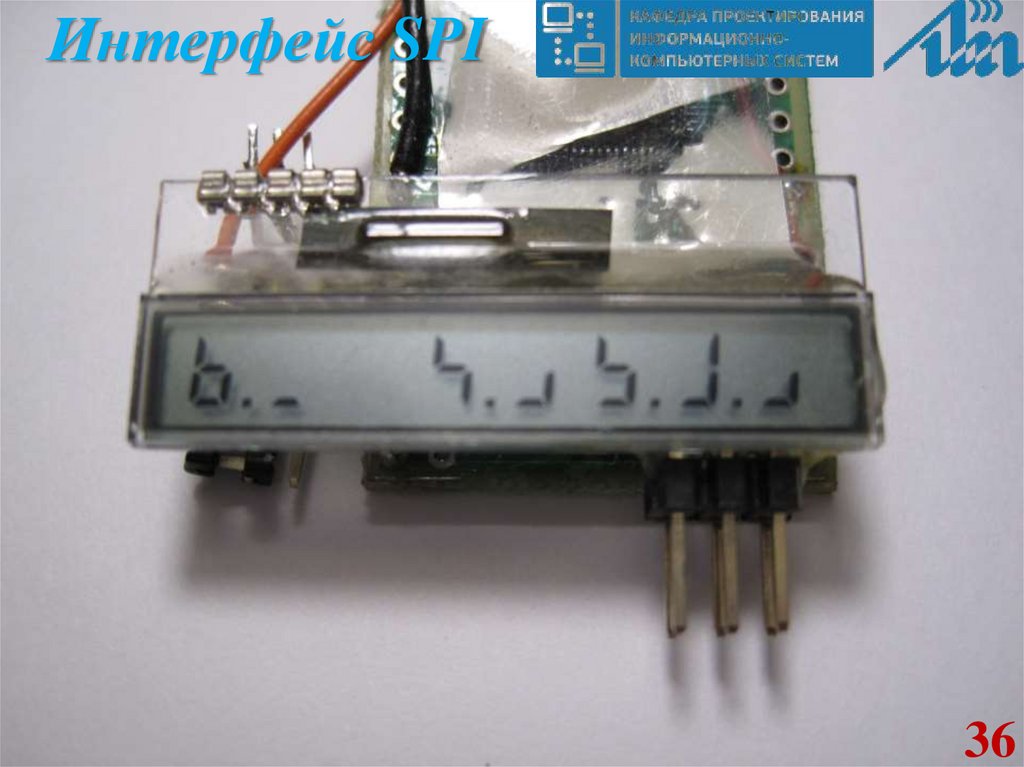

36.

Интерфейс SPI36

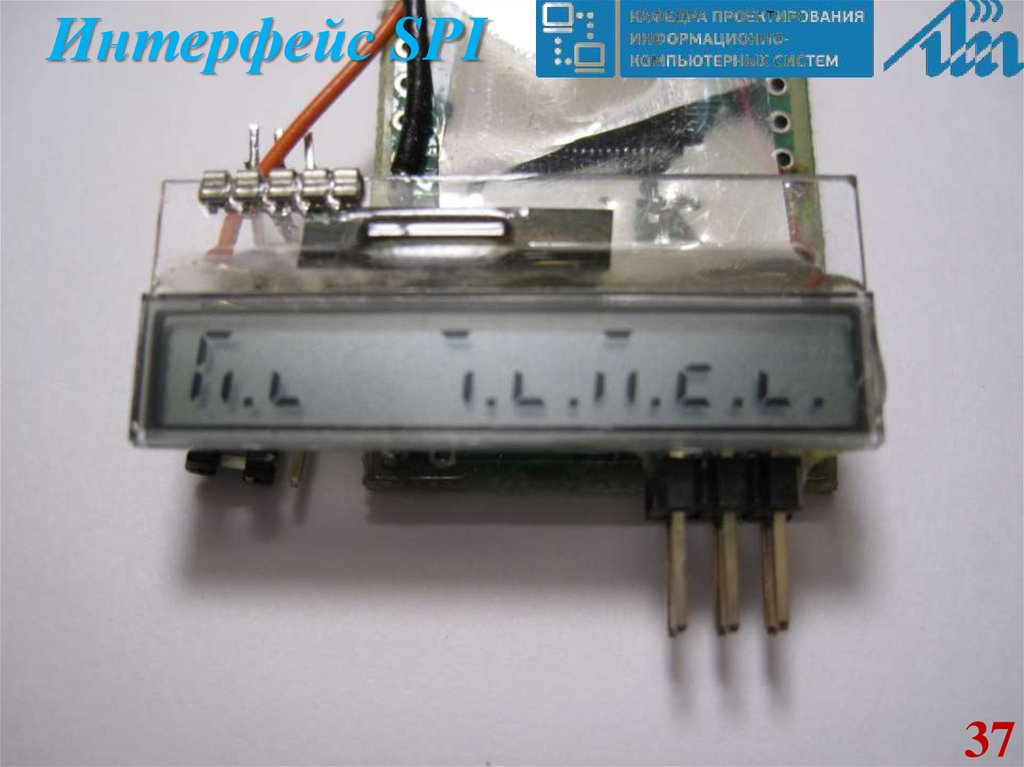

37.

Интерфейс SPI37

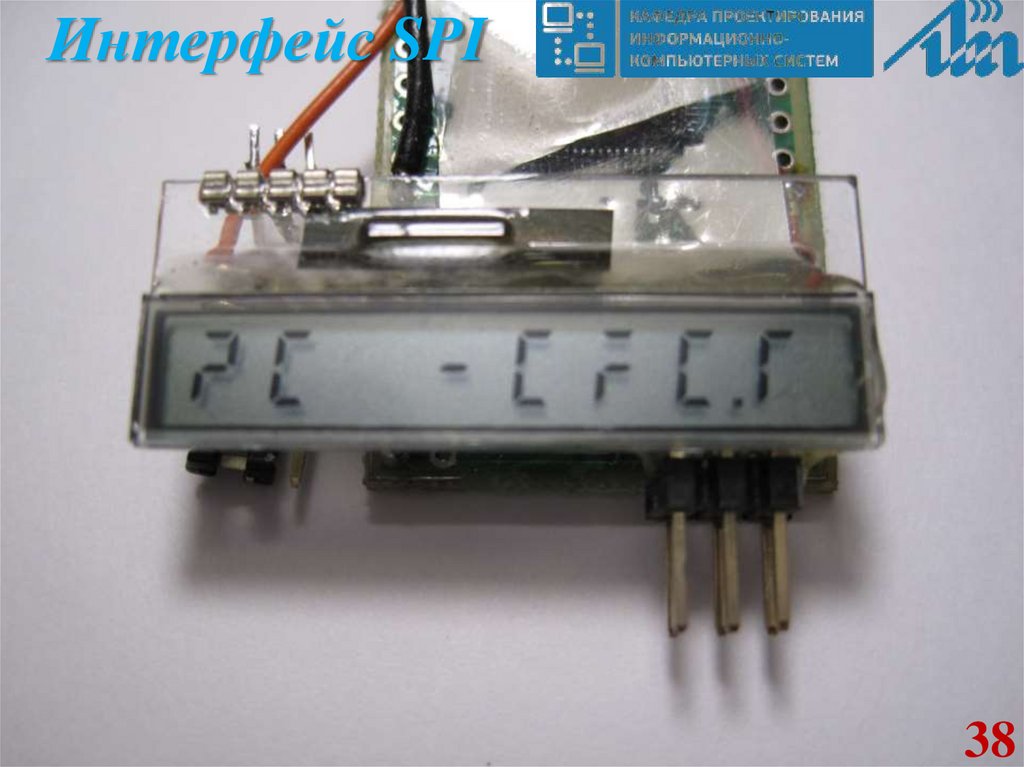

38.

Интерфейс SPI38

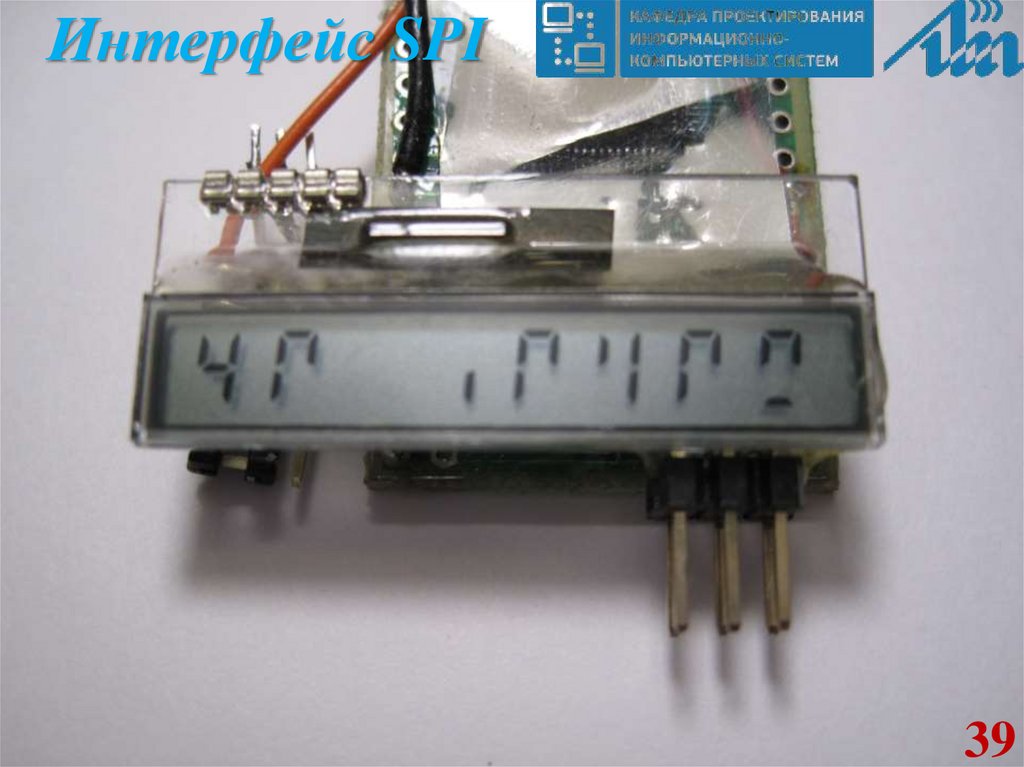

39.

Интерфейс SPI39

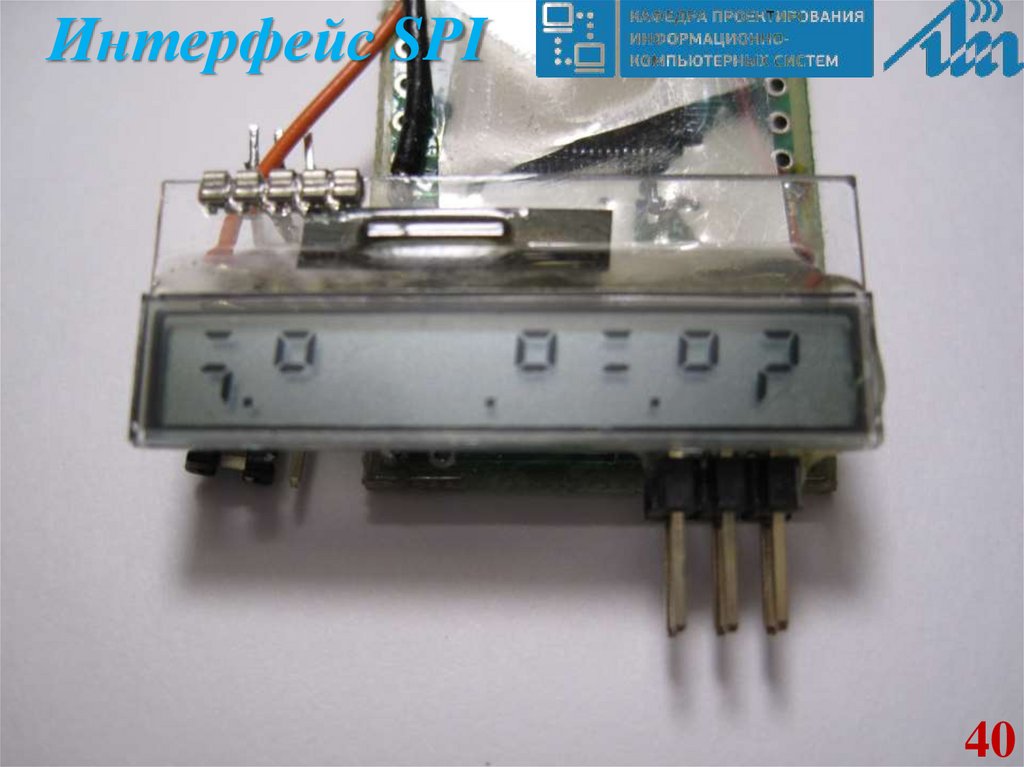

40.

Интерфейс SPI40

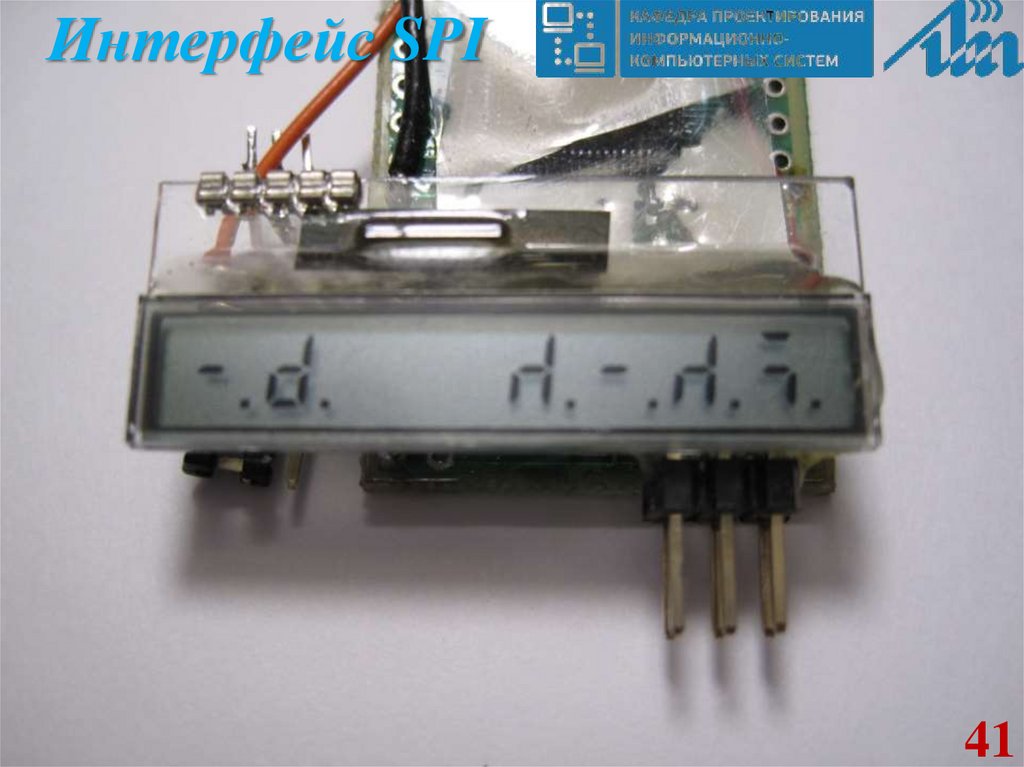

41.

Интерфейс SPI41

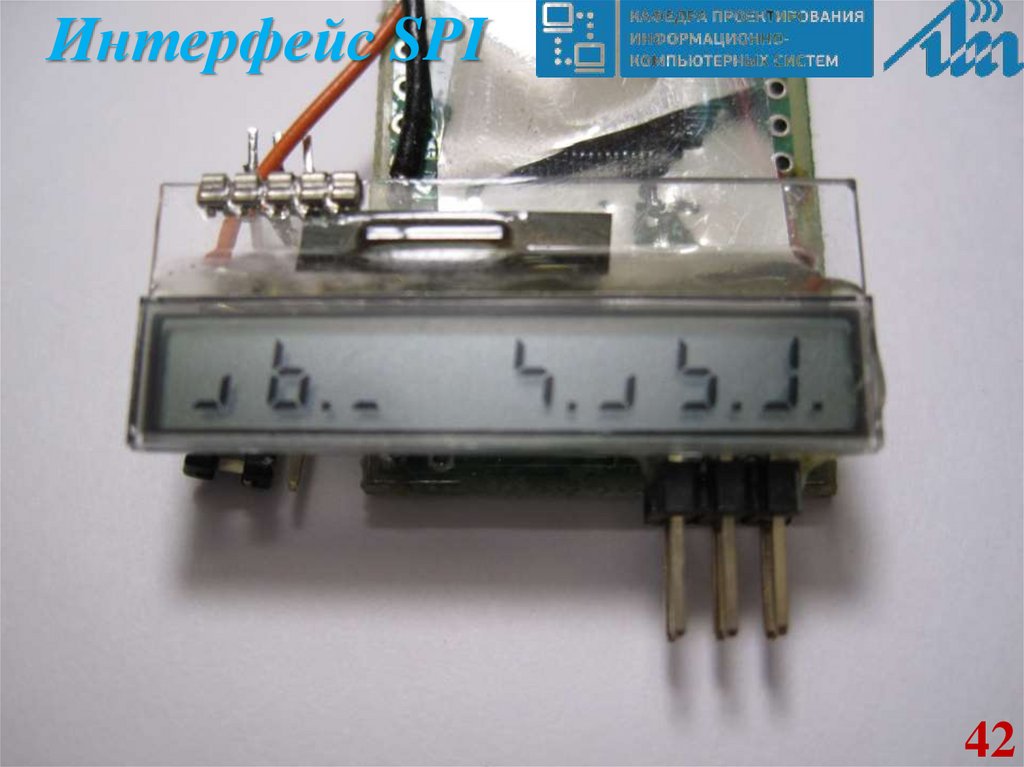

42.

Интерфейс SPI42

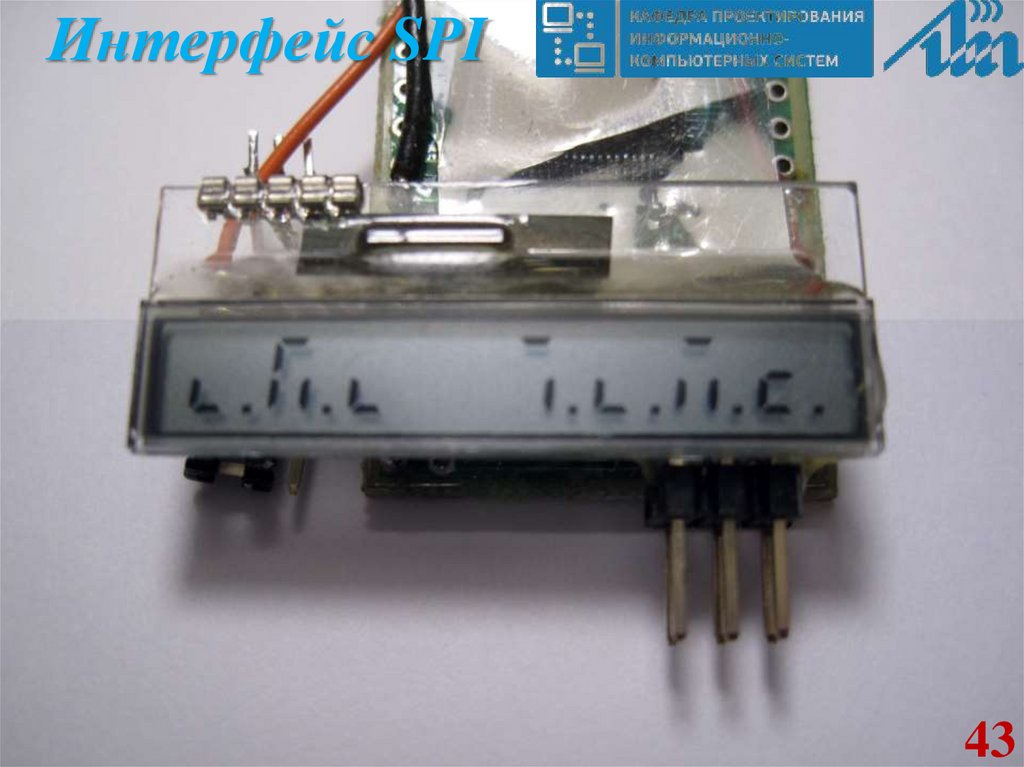

43.

Интерфейс SPI43

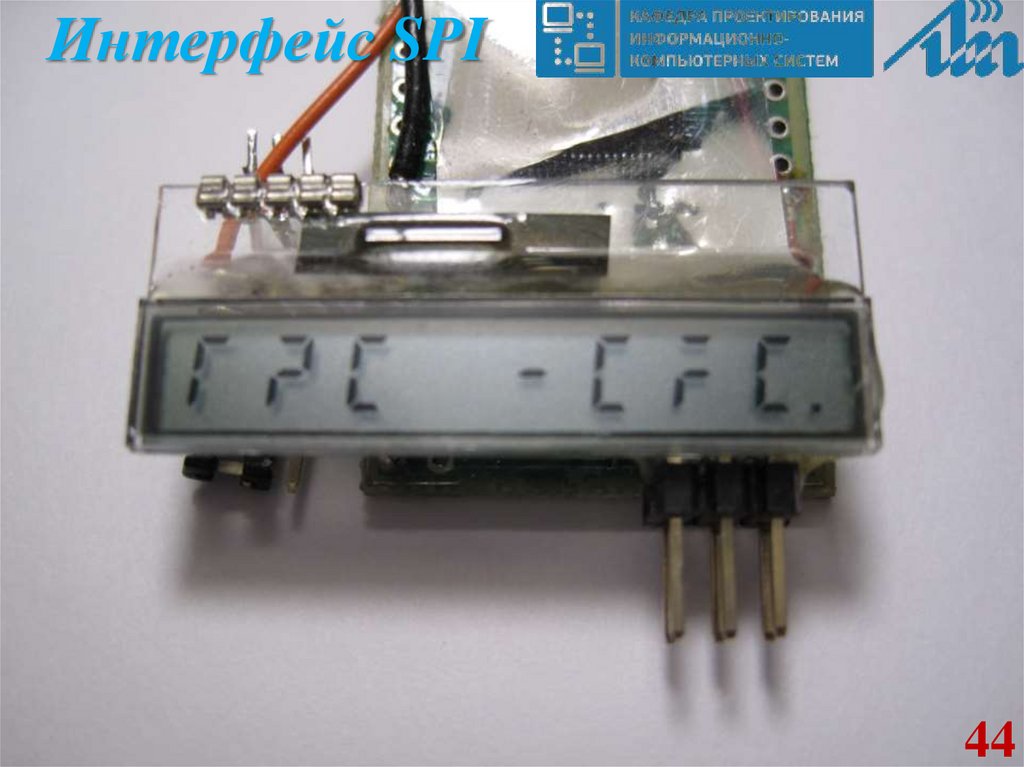

44.

Интерфейс SPI44

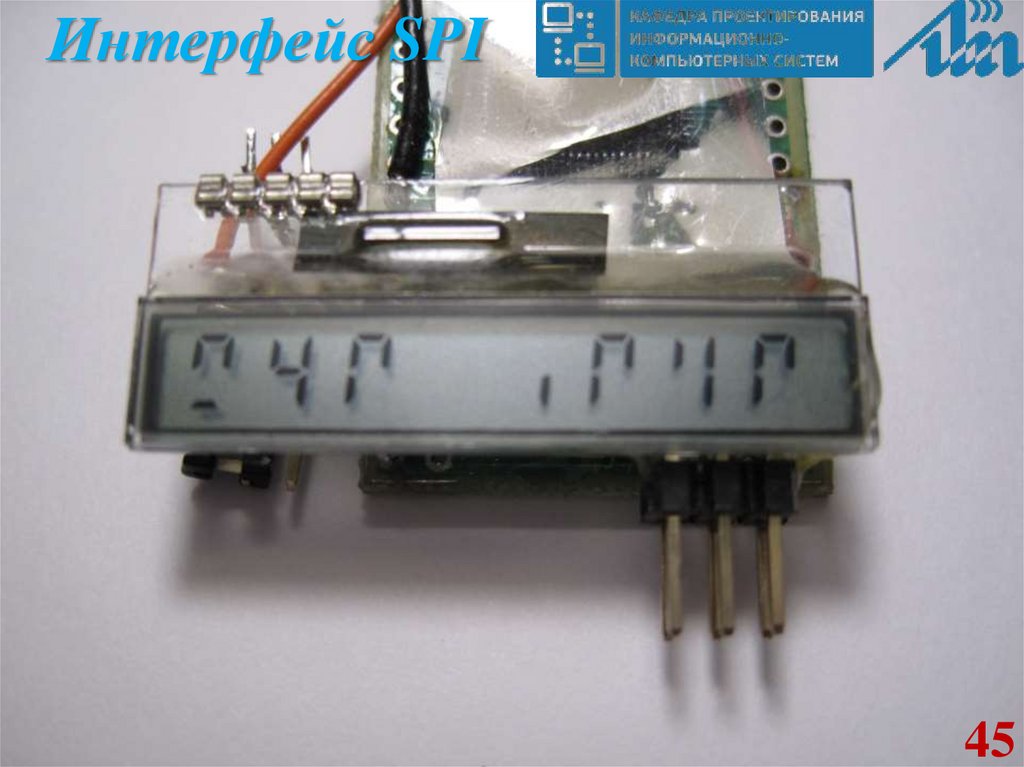

45.

Интерфейс SPI45

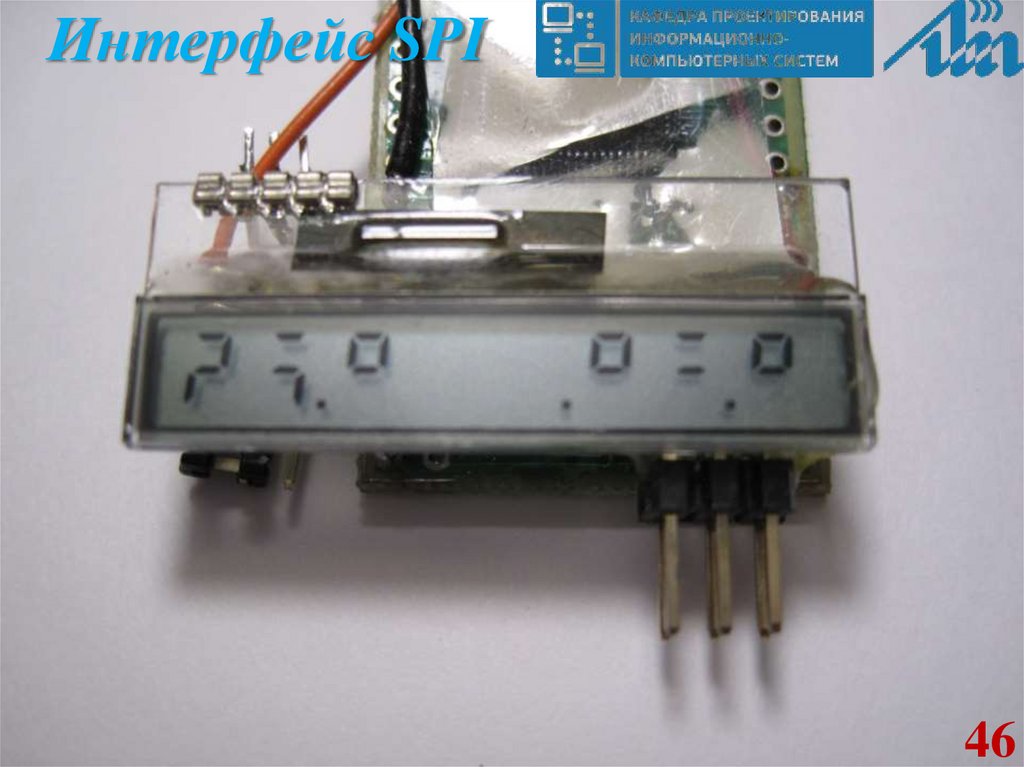

46.

Интерфейс SPI46

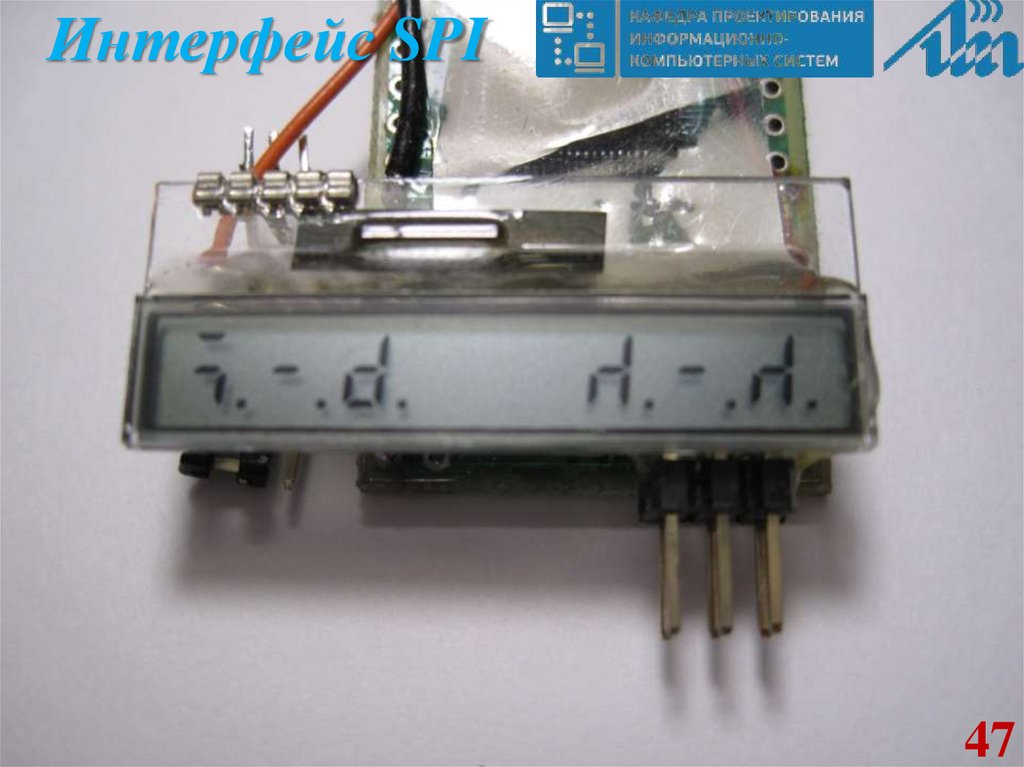

47.

Интерфейс SPI47

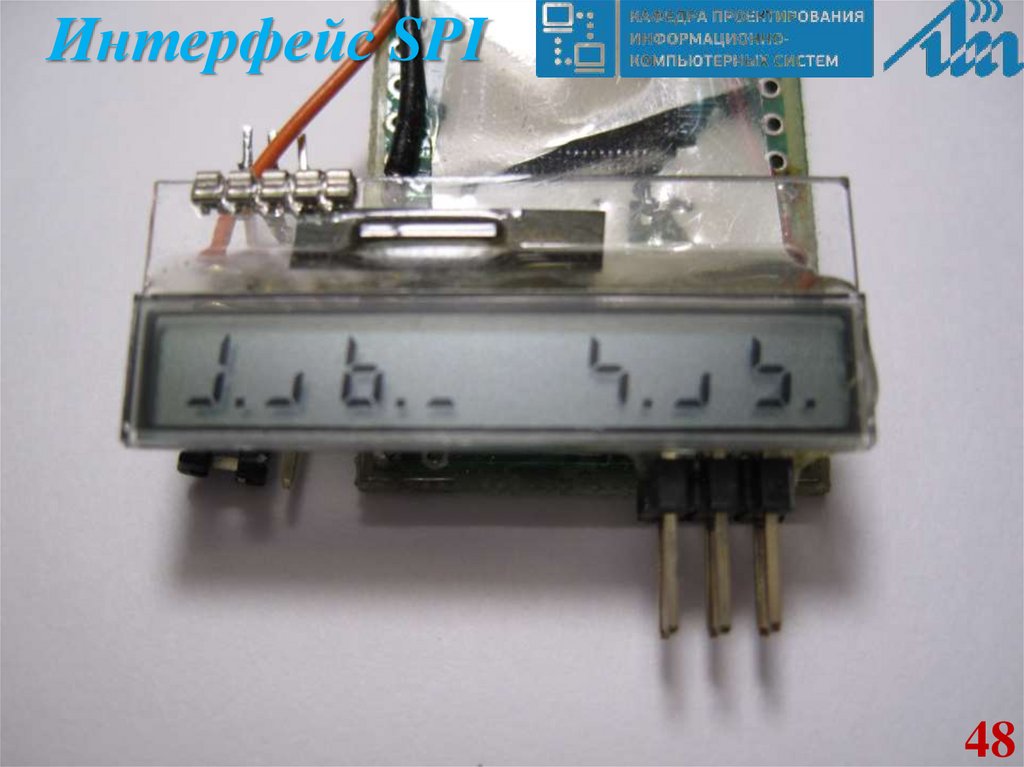

48.

Интерфейс SPI48

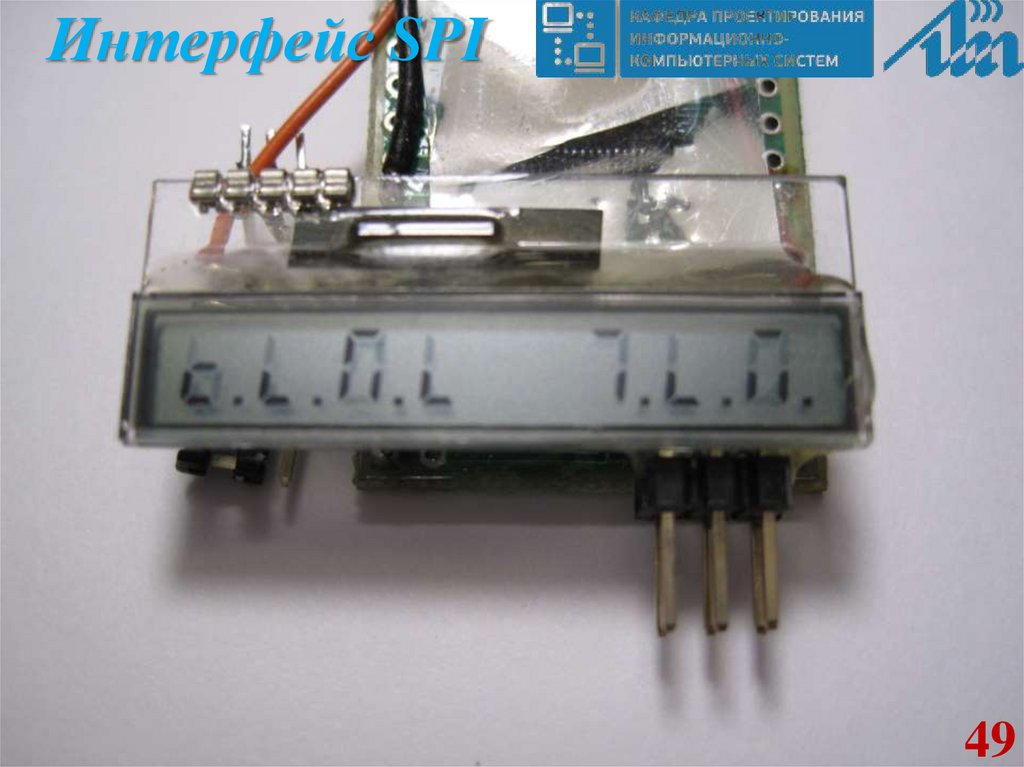

49.

Интерфейс SPI49

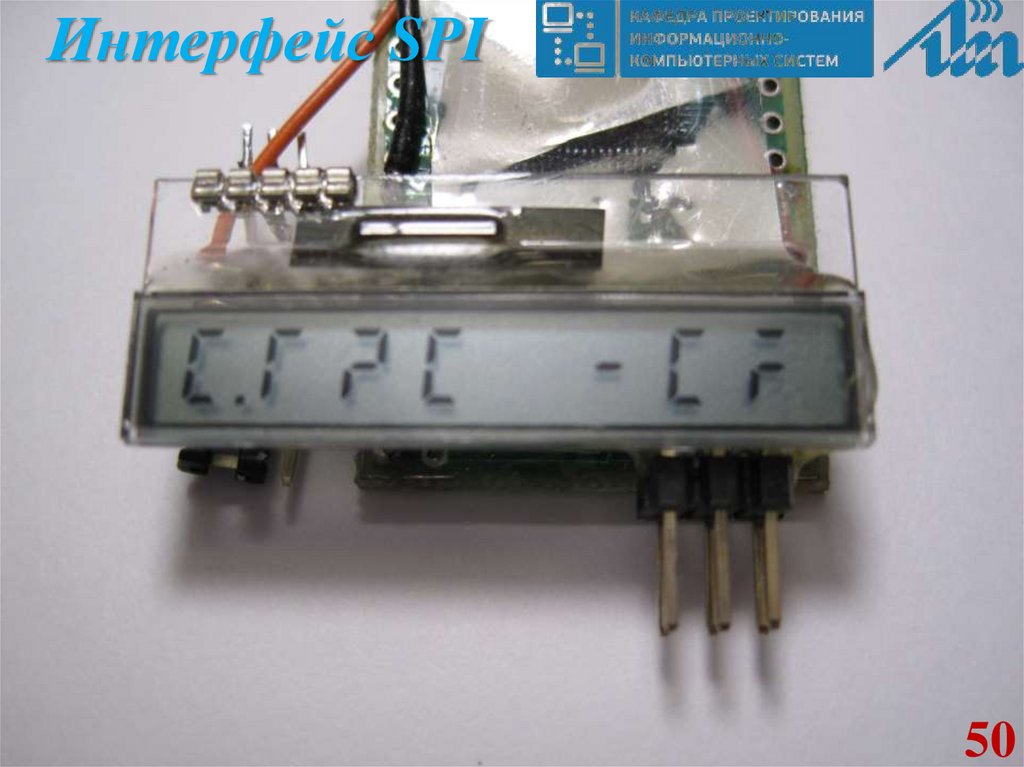

50.

Интерфейс SPI50

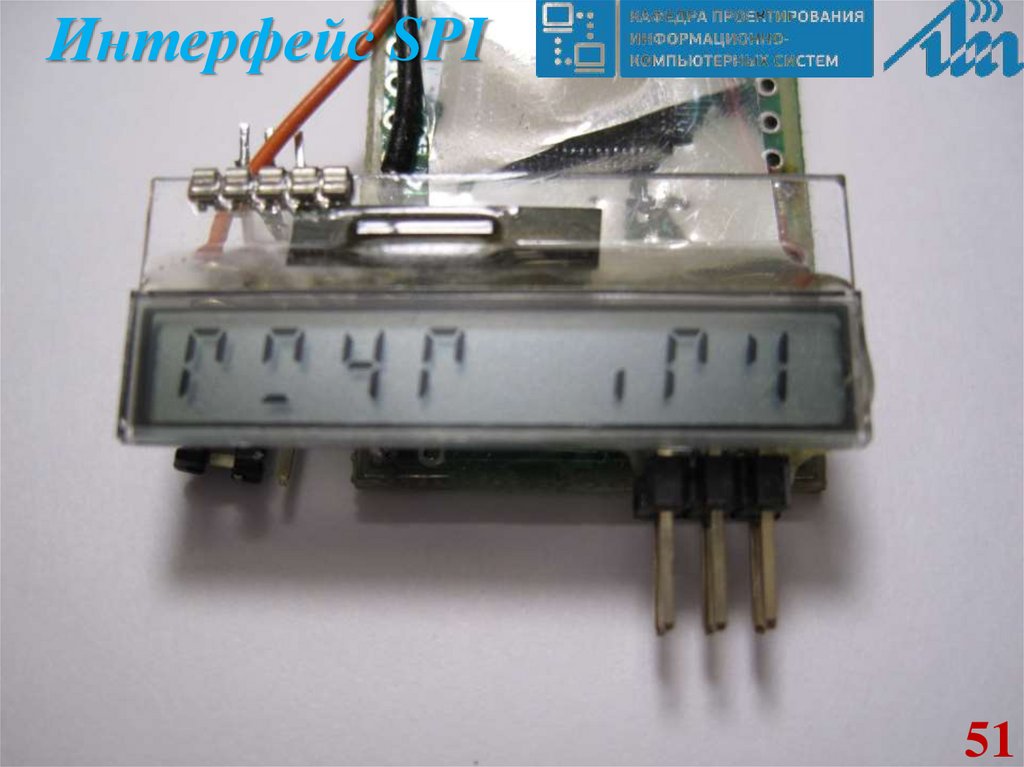

51.

Интерфейс SPI51

52.

Интерфейс SPI52

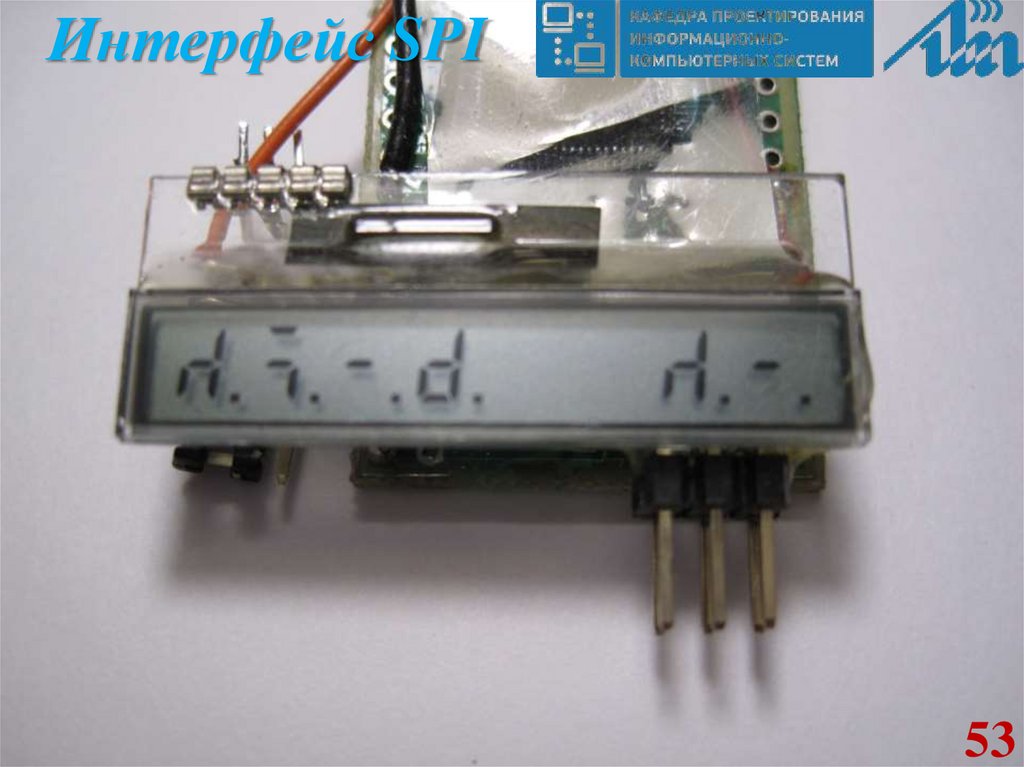

53.

Интерфейс SPI53

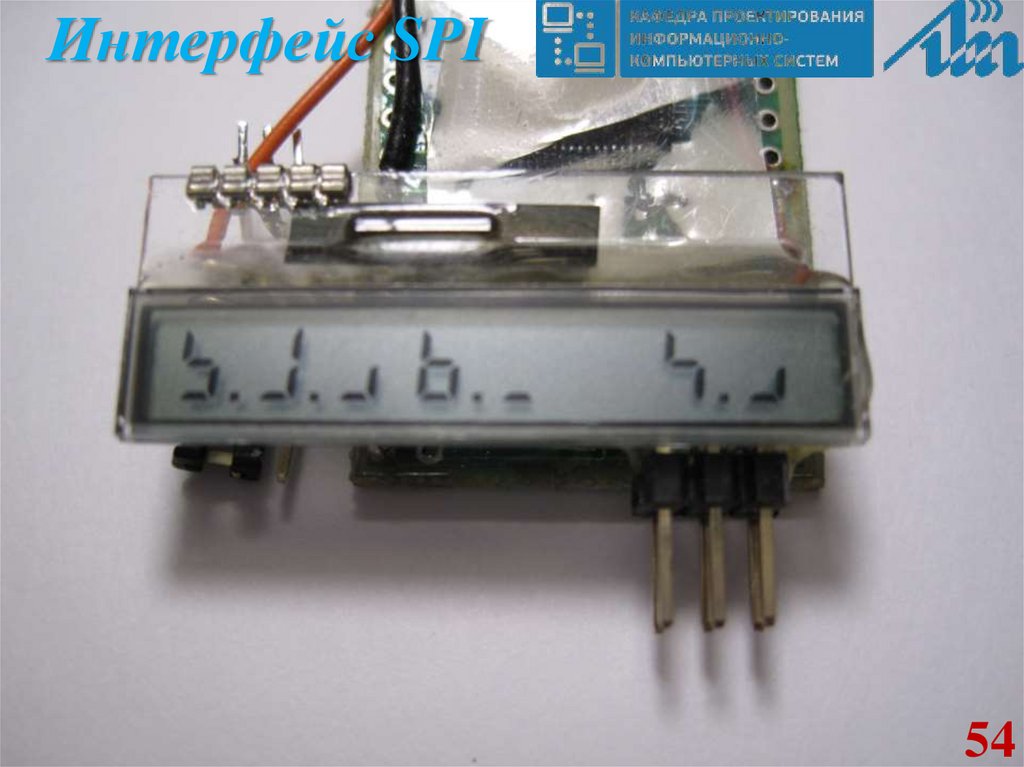

54.

Интерфейс SPI54

55.

Интерфейс SPI55

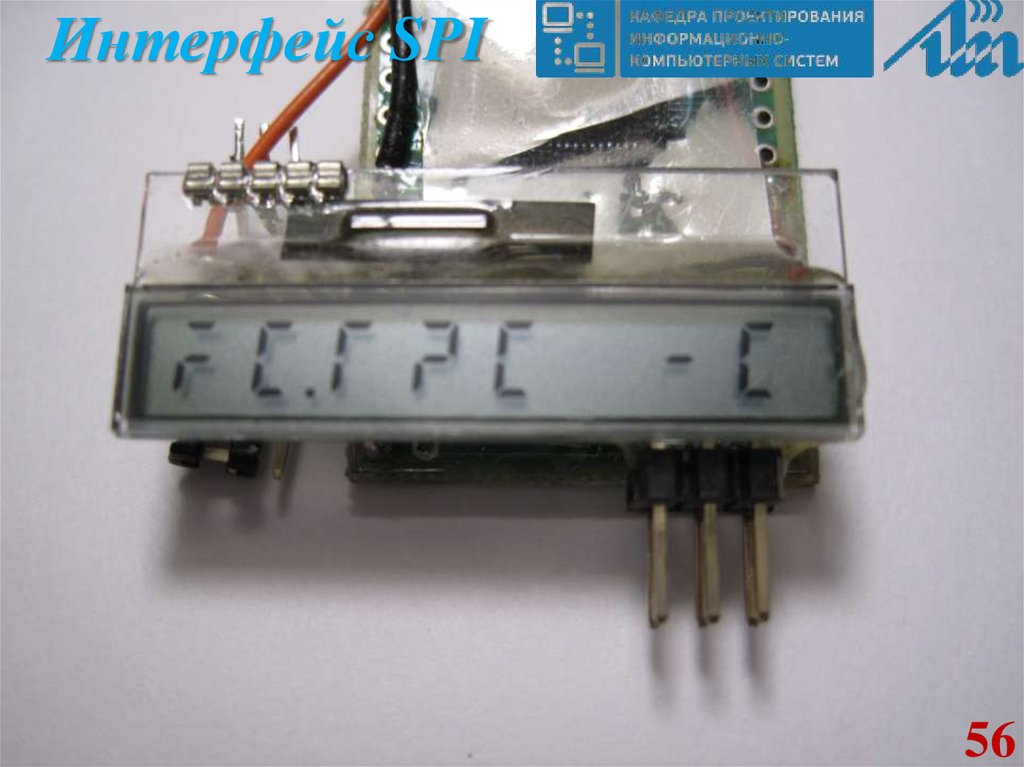

56.

Интерфейс SPI56

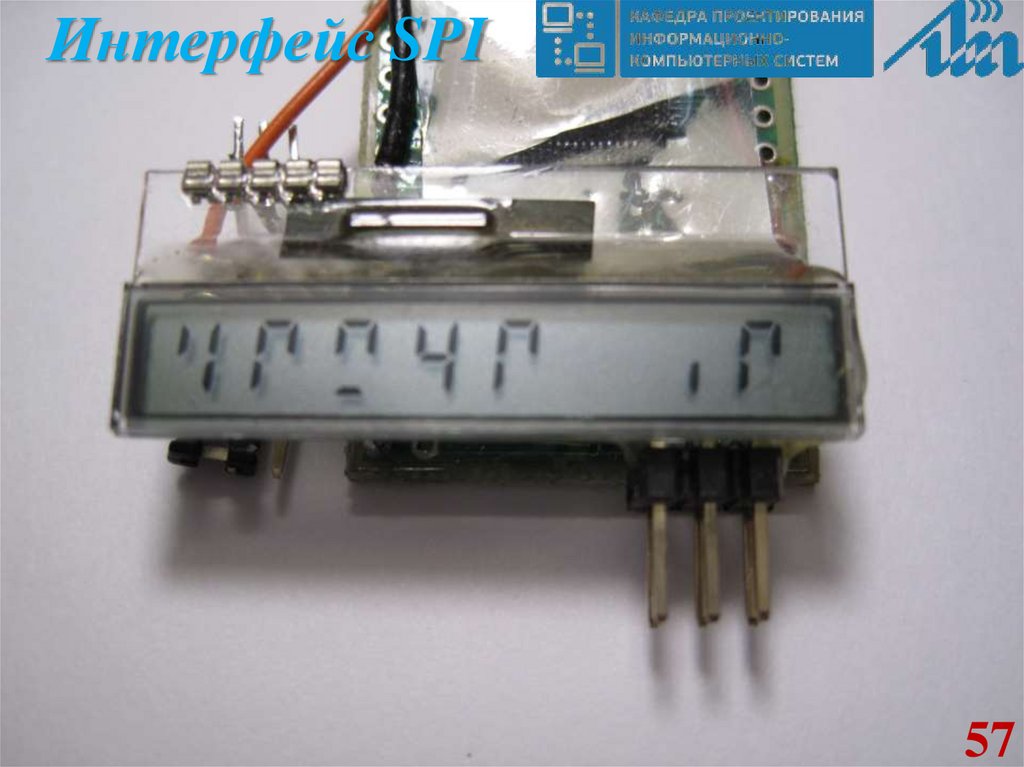

57.

Интерфейс SPI57

58.

Интерфейс SPI58

59.

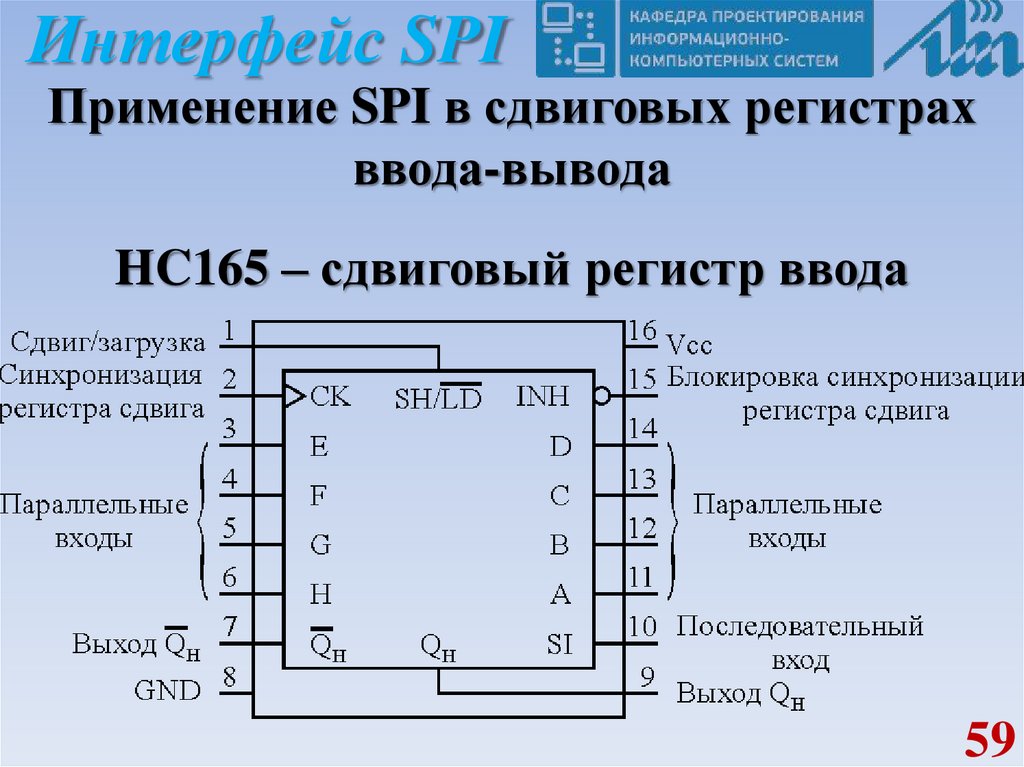

Интерфейс SPIПрименение SPI в сдвиговых регистрах

ввода-вывода

HC165 – сдвиговый регистр ввода

59

60.

Интерфейс SPIПрименение SPI в сдвиговых регистрах

ввода-вывода

Таблица

функций

сдвигового

регистра

ввода

HC165

60

61.

Интерфейс SPIДемонстрационное

видео моделирования

работы входного

регистра сдвига

HC165

CPOL = 0

CPHA = 0

61

Электроника

Электроника