Похожие презентации:

Dasturlanuvchi mantiqiy qurilmalar. Ma’ruza №7

1.

MA’RUZA № 7. DASTURLANUVCHI MANTIQIY QURILMALARReja:

1. Dasturlanuvchi mantiqiy integral sxema (DMIS);

2. DMIS larning qo‘llanilish sohasi va turlari;

3. Dasturlanuvchi mantiqiy matritsa (DMM).

Dasturlanuvchi mantiqiy integral sxema. Dasturlanuvchi mantiqiy

integral sxema(FPGA, ingl. Programmable logic device, PLD) - konfiguratsiya

qilinadigan raqamli elektron sxemalarni yaratish uchun ishlatiladigan elektron

komponent. An'anaviy raqamli mikrosxemalardan farqli o'laroq, DMIS ishining

mantig'i ishlab chiqarish vaqtida aniqlanmaydi, balki dasturlash (dizayn) orqali

o'rnatiladi. Dasturlash uchun dasturchi va IDE (disk raskadrovka muhiti)

ishlatiladi, bu sizga raqamli qurilmaning kerakli tuzilishini elektron sxema yoki

maxsus apparat tavsifi tillarida dastur shaklida o'rnatish imkonini beradi: Verilog,

VHDL, AHDL va boshqalar. Muqobil DMIS -lar:

- dasturlash uchun zavod ishlab chiqarish jarayonini talab qiladigan asosiy

matritsa kristallari (BMC);

- ASIC- kichik o'lchamli va bitta bo'lakli ishlab chiqarish uchun ancha

qimmat bo'lgan maxsus ixtisoslashtirilgan yirik integral mikrosxemalar (KIS);

- algoritmlarning dasturiy ta'minoti tufayli DMIS -ga qaraganda sekinroq

ishlaydigan maxsus kompyuterlar, protsessorlar (masalan, raqamli signal

protsessori) yoki mikrokontrollerlar;

-ilgari ma'lum bo'lgan muammolarni hal qilish uchun tuzilgan,

dasturlashtirilmaydigan raqamli qurilmalar va tizimlar, bu printsiplar asosida

qurilgan. "qattiq mantiq".

Ba'zi ishlab chiqaruvchilar DMIS -lari uchun dasturiy protsessorlarni taklif

qilishadi, ularni ma'lum bir vazifa uchun o'zgartirish mumkin va keyin DMIS larga o'rnatish mumkin. Shunday qilib:

- bosilgan elektron kartada bo'sh joyning ko'payishi ta'minlanadi (taxta

hajmini kamaytirish imkoniyati);

- DMIS dizaynining o'zi soddalashtirilgan;

- DMIS ishlashi oshadi.

DMISni oyihalash bosqichlari:

1. Uskunani tavsiflovchi maxsus tillarda sxemani yoki dasturni o'rnatish:

Verilog, VHDL, AHDL va boshqalar.

2. Sintezator dasturlari yordamida mantiqiy sintez (apparat tavsifi tilida

yozilgan mavhum modeldan elektr ulanishlar ro'yxatini (matn shaklida) qilish).

3. DMIS mikrosxemasi va boshqa elektron komponentlar (rezistorlar,

kondensatorlar, generatorlar, ARO‘ lar, ulagichlar va boshqalar va hokazo)

joylashadigan qurilmaning pechatli platasini avtomatlashtirilgan loyihalash tizimi

(Altium Designer, P-CAD va h.) yordamida loyihalash.

4. DMIS konfiguratsiya faylini yaratish.

2.

5. Faylni DMIS mikrosxemasiga yoki alohida konfiguratsion xotiramikrosxemasiga yuklash. Konfiguratsiyani yuklash natijasida DMIS mikrosxemasi

belgilangan funktsiyaga ega bo'ladi.

DMIS qo‘llanilish sohasi. DMIS lar har xil murakkablik va imkoniyatlarga

ega raqamli qurilmalarni yaratish uchun keng qo'llaniladi, masalan:

- ko'p sonli kirish-chiqish portlari bo'lgan qurilmalar (1000 dan ortiq

chiqadigan DMIS lar mavjud ("pinlar"));

- signallarni raqamli qayta ishlashni amalga oshiruvchi qurilmalar (SRQI);

- raqamli video audio uskunalar;

- ma'lumotlarni uzatishni yuqori tezlikda bajaradigan qurilmalar;

- kriptografik operatsiyalarni bajaruvchi qurilmalar, axborot xavfsizligi

tizimlari;

- maxsus maqsadli integral mikrosxemalarni (ASIC) loyihalash va

prototiplash uchun mo'ljallangan qurilmalar;

- har xil mantiq va quvvat kuchlanishli tizimlar o'rtasida ko'prik

(kommutator) vazifasini bajaruvchi qurilmalar;

- neyrochiplarni amalga oshirish;

- kvant hisoblash simulyatsiyasini bajaruvchi qurilmalar;

- radar ma'lumotlarini qayta ishlash qurilmalari.

DMIS turlari:

- Dastlabki DMIS. 1970 yilda «TI»kompaniyasi «IBM» firmasining

assotsiativ ROM(ROAM) ga asoslangan niqoblangan (ya’ni, niqob yordamida

Dasturlanuvchi, ingl. mask-programmable) integral mikrosxemalarni (keyinchalik

IC) ishlab chiqdi. Ushbu mikrosxemalar TMS2000 deb nomlangan va integral

mikrosxemani (IC) ishlab chiqarish jarayonida metall qatlamlarni bir -biriga

yopishtirib dasturlashtirilgan. TMS2000 xotira sifatida 8 ta JK-triggerli 17 ta kirish

va 18 ta chiqishga ega edi. Ushbu qurilmalar uchun «TI» kompaniyasi PLA

atamasini kiritdi – ingl. programmable logic array - Dasturlanuvchi mantiq

matritsasi.

- PAL (ingl. programmable logic array) - bu mantiqning Dasturlanuvchi

massivi (matritsasi). Ilgari, PLA va PLM farq qilmagan va PLM (Dasturlanuvchi

mantiqiy matritsa) sifatida belgilangan. PLA va PLM o'rtasidagi farq - bu ichki

tuzilmani (matritsalarni) dasturlashning mavjudligi.

- GAL (ingl. generic array logic) - bu Dasturlanuvchi VA matritsali va sobit

YOKI matritsali FPGA.

- CPLD (ingl. complex programmable logic device) - murakkab

Dasturlanuvchi mantiqiy qurilmalar nisbatan katta Dasturlanuvchi mantiq

bloklarini - tashqi chiqish va ichki shinalarga ulangan makroyacheykalarni o'z

ichiga oladi (7.1 -rasm). CPLD funktsiyasi doimiy xotirada kodlangan, shuning

uchun ularni qayta ishga tushirishning hojati yo'q. U katta kristallar yaqinidagi

kirish -chiqish sonini kengaytirish yoki signalni oldindan qayta ishlash uchun

ishlatilishi mumkin (masalan, COM port boshqaruvchisi, USB, VGA).

3.

7.1-rasm. «Altera» kompaniyasining CPLD turidagi DMISi, «MAX 7128»modeli.

FPGA (ingl. field-programmable gate array)-larda signallarni qayta

ishlashda (DSP, ingl. digital signal processing) keng qo'llaniladigan ko'paytirish

bloklari, shuningdek, mantiq elementlari (odatda qidiruv jadvallari-haqiqat

jadvallari) va ularning kommutator birliklari mavjud. FPGA odatda signallarni

qayta ishlash uchun ishlatiladi, mantiq elementlari ko'proq va CPLDlarga

qaraganda moslashuvchan arxitekturaga ega. FPGA dasturi tarqatilgan xotirada

saqlanadi, uni statik operativ xotiraning uchuvchan hujayralari asosida ham

bajarish mumkin (bunday mikrosxemalar, masalan, "Xilinx" va "Altera" firmalari

tomonidan ishlab chiqariladi) - bu holda, mikrosxemaning quvvat manbai

yo'qolganda yoki uchuvchan bo'lmagan flesh xotira xujayralari yoki antifuzik o'tish

moslamalariga asoslangan dastur saqlanmaydi (bunday mikrosxemalar Actel va

Lattice Semiconductor tomonidan ishlab chiqariladi) - bu holda, dastur saqlanadi.

elektr ta'minoti ishlamayapti. Agar dastur o'zgaruvchan xotirada saqlansa, u holda

har safar mikrosxemani yoqilganda, uni yuklash vositasi yordamida qayta sozlash

kerak, uni FPGA -ga o'rnatish mumkin.Sekinroq raqamli signal protsessorlari

FPGA -larga alternativa. FPGA -lar, shuningdek, superkompyuterlarda umumiy

maqsadli protsessor tezlatgichlari sifatida ishlatiladi (masalan, Cray's Cray XD1

kompyuteri, Silicon Graphics -ning RASC loyihasi (SGI)).

PLD ning asosiy afzalligi - rivojlanishning past vaqti va egiluvchanligi.

VLSI PLD -dagi zamonaviy dizayn vositalari va texnologiyalaridan foydalangan

malakali muhandis bir kunda funktsional ravishda qurilmani tasvirlab berishi va

disk raskadrovka qilishi mumkin, buning uchun o'nlab an'anaviy mikrosxemalar

"tarqalishi" kerak bo'ladi. Biroq, PLD ning haqiqiy dasturlashi atigi bir necha

daqiqa davom etadi. Shu tarzda olingan ixtisoslashtirilgan VLSI tezlik, quvvat sarfi

va ishonchlilik bo'yicha eng qat'iy talablarga javob beradi.

Dasturlanuvchi mantiqiy matritsa. PLA printsipi PROMga o'xshaydi,

faqat PLA o'zgaruvchilarning to'liq dekodlanishini ta'minlamaydi va barcha

minimal qiymatlarni yaratmaydi. Dekoderning o'rnini VA elementlari majmuasi

egallaydi, ularni kirish o'zgaruvchilari mahsulotlarining istalgan muddatini yaratish

uchun dasturlash mumkin. Mahsulot shartlari YOKI elementlari bilan bog'lanib,

kerakli bull funktsiyalari uchun mahsulot yig'indisini oladi.

Uch kirish va ikkita chiqishga ega bo'lgan ichki PLA mantig'i 7.2-rasmda

ko'rsatilgan. Bu tartib tijorat maqsadlarida foydalanish uchun juda kichik, lekin bu

erda PLA mantiqiy konfiguratsiyasini ko'rsatish uchun taqdim etilgan. Sxemada

murakkab sxemalar uchun mantiqiy grafik belgilar majmuasi ishlatiladi. Har bir

4.

kirish bufer-inverter kombinatsiyasidan o'tadi, bu diagrammada ham haqiqiy, hamyordamchi chiqishga ega bo'lgan grafik belgisi bilan ko'rsatilgan.Vertikal va

gorizontal chiziqlar orasidagi kesishmalarda ko'rsatilgandek, har bir kirish va uni

to'ldiruvchi har bir VA mantiqiy elementining kirishiga ulanadi. VA

elementlarining chiqishlari har bir YOKI -elementning kirishiga ulanadi. YOKI

elementi chiqishi XOR elementiga yo'naltiriladi, bu erda boshqa kirishni mantiq 1

yoki mantiq 0 ga teng signalni qabul qilish uchun dasturlash mumkin. XOR usuli 1

ga ulanganda chiqish teskari bo'ladi (chunki x {1 = x). XOR usuli 0 ga ulanganda

chiqish o'zgarmaydi (chunki x {0 = x). 7.2-rasmda alohida mantiqiy funktsiyalar

PLAda bajarilgan:

F1 =AB’ +AC +A’BC’

F2 = (AC +BC)’

7.2-rasm. PLA uchta kirish va ikkita chiqish bilan ishlashning to’rt sharti.

Har bir VA shlyuzida hosil qilingan mahsulot shartlari diagrammada

element chiqishida keltirilgan, mahsulot shartlari kesishish nuqtalari bog'langan va

*bilan belgilangan kirishlar bo'yicha aniqlanadi. YOKI elementi chiqishi tanlangan

mahsulot shartlarining mantiqiy yig'indisini beradi. Chiqish amalga oshiriladigan

mantiqqa qarab, to'ldirilishi yoki asl shaklida qoldirilishi mumkin.

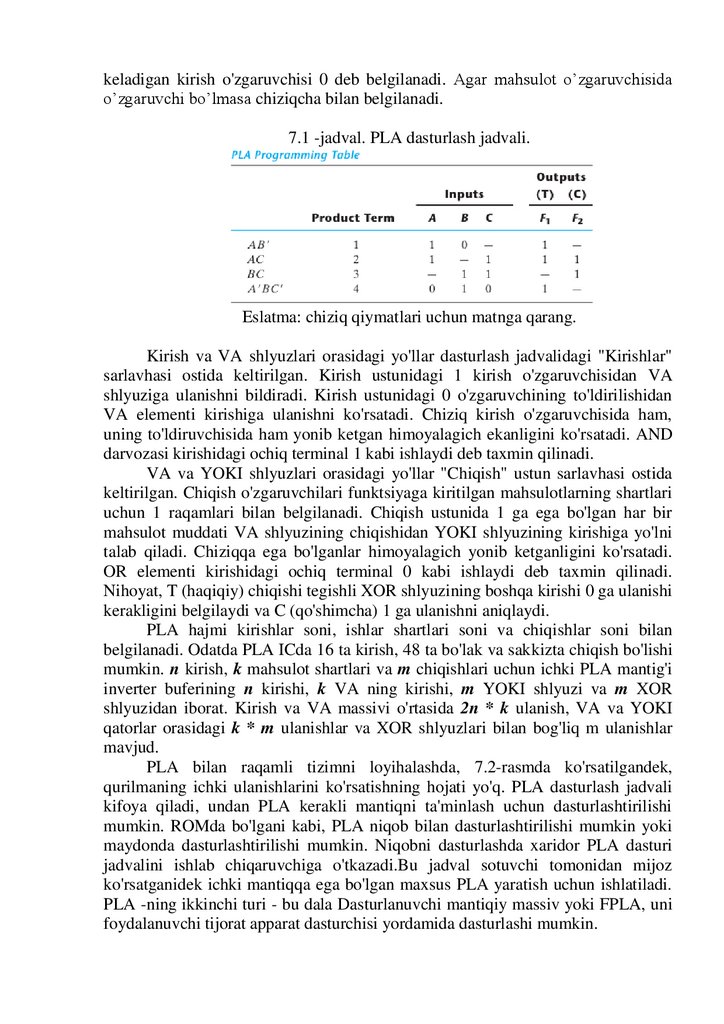

PLA himoyalagichlar xaritasini jadval shaklida ko'rsatish mumkin. Masalan,

PLA ni aniqlaydigan dasturlash jadvali 7.1 -jadvalda keltirilgan. PLA dasturlash

jadvali uchta bo'limga bo'lingan. Birinchi bo'limda asarlar shartlari raqamli shaklda

keltirilgan. Ikkinchi bo'limda kirish va VA shlyuzlari orasidagi kerakli yo'llar

ko'rsatilgan.Uchinchi bo'lim VA va YOKI elementlari orasidagi yo'llarni

belgilaydi. Har bir chiqish o'zgaruvchisi uchun biz XOR shlyuzini dasturlash

uchun T (to'g'ri) yoki C (qo'shimcha uchun) bo'lishi mumkin. Chapda sanab

o'tilgan asarlar shartlari jadvalga kirmaydi; ular faqat ma'lumot uchun kiritilgan.

Har bir mahsulot muddati uchun kirish 1, 0 yoki - (chiziqcha) bilan belgilanadi.

Agar mahsulot terminidagi o'zgarmaydigan to'g'ri ko'rinishda bo'lsa, mos keladigan

kirish o'zgaruvchisi 1 deb belgilanadi. Agar u kengaytirilgan ko'rinsa, mos

5.

keladigan kirish o'zgaruvchisi 0 deb belgilanadi. Agar mahsulot o’zgaruvchisidao’zgaruvchi bo’lmasa chiziqcha bilan belgilanadi.

7.1 -jadval. PLA dasturlash jadvali.

Eslatma: chiziq qiymatlari uchun matnga qarang.

Kirish va VA shlyuzlari orasidagi yo'llar dasturlash jadvalidagi "Kirishlar"

sarlavhasi ostida keltirilgan. Kirish ustunidagi 1 kirish o'zgaruvchisidan VA

shlyuziga ulanishni bildiradi. Kirish ustunidagi 0 o'zgaruvchining to'ldirilishidan

VA elementi kirishiga ulanishni ko'rsatadi. Chiziq kirish o'zgaruvchisida ham,

uning to'ldiruvchisida ham yonib ketgan himoyalagich ekanligini ko'rsatadi. AND

darvozasi kirishidagi ochiq terminal 1 kabi ishlaydi deb taxmin qilinadi.

VA va YOKI shlyuzlari orasidagi yo'llar "Chiqish" ustun sarlavhasi ostida

keltirilgan. Chiqish o'zgaruvchilari funktsiyaga kiritilgan mahsulotlarning shartlari

uchun 1 raqamlari bilan belgilanadi. Chiqish ustunida 1 ga ega bo'lgan har bir

mahsulot muddati VA shlyuzining chiqishidan YOKI shlyuzining kirishiga yo'lni

talab qiladi. Chiziqqa ega bo'lganlar himoyalagich yonib ketganligini ko'rsatadi.

OR elementi kirishidagi ochiq terminal 0 kabi ishlaydi deb taxmin qilinadi.

Nihoyat, T (haqiqiy) chiqishi tegishli XOR shlyuzining boshqa kirishi 0 ga ulanishi

kerakligini belgilaydi va C (qo'shimcha) 1 ga ulanishni aniqlaydi.

PLA hajmi kirishlar soni, ishlar shartlari soni va chiqishlar soni bilan

belgilanadi. Odatda PLA ICda 16 ta kirish, 48 ta bo'lak va sakkizta chiqish bo'lishi

mumkin. n kirish, k mahsulot shartlari va m chiqishlari uchun ichki PLA mantig'i

inverter buferining n kirishi, k VA ning kirishi, m YOKI shlyuzi va m XOR

shlyuzidan iborat. Kirish va VA massivi o'rtasida 2n * k ulanish, VA va YOKI

qatorlar orasidagi k * m ulanishlar va XOR shlyuzlari bilan bog'liq m ulanishlar

mavjud.

PLA bilan raqamli tizimni loyihalashda, 7.2-rasmda ko'rsatilgandek,

qurilmaning ichki ulanishlarini ko'rsatishning hojati yo'q. PLA dasturlash jadvali

kifoya qiladi, undan PLA kerakli mantiqni ta'minlash uchun dasturlashtirilishi

mumkin. ROMda bo'lgani kabi, PLA niqob bilan dasturlashtirilishi mumkin yoki

maydonda dasturlashtirilishi mumkin. Niqobni dasturlashda xaridor PLA dasturi

jadvalini ishlab chiqaruvchiga o'tkazadi.Bu jadval sotuvchi tomonidan mijoz

ko'rsatganidek ichki mantiqqa ega bo'lgan maxsus PLA yaratish uchun ishlatiladi.

PLA -ning ikkinchi turi - bu dala Dasturlanuvchi mantiqiy massiv yoki FPLA, uni

foydalanuvchi tijorat apparat dasturchisi yordamida dasturlashi mumkin.

6.

PLA bilan kombinatsion sxemani amalga oshirayotganda, mahsulotningindividual shartlari sonini kamaytirish uchun sinchkovlik bilan tekshirish kerak,

chunki PLAda VA shlyuzlari soni cheklangan. Buni har bir mantiqiy funktsiyani

minimal atamalar soniga soddalashtirish orqali amalga oshirish mumkin. Bir

davrdagi harflar soni muhim emas, chunki hamma kirish o'zgaruvchilari baribir

mavjud. Har bir funktsiyaning haqiqiy ma'nosi ham, qo'shilishi ham

soddalashtirilishi kerak, bunda qaysi biri kamroq ish shartlari bilan ifodalanishi

mumkin va qaysi boshqa funktsiyalar uchun umumiy bo'lgan ish shartlarini beradi.

Misol. PLA yordamida quyidagi ikkita mantiqiy funktsiyani bajaring:

F1(A,B,C) = ∑ (0, 1, 2, 4)

F2(A,B,C) = ∑ (0, 5, 6, 7)

Ikkala funktsiya ham 7.3-rasmda ko'rsatilgan xaritalarda soddalashtirilgan.

Haqiqiy ma'no ham, funktsiyalarga qo'shilish ham mahsulot yig'indisi sifatida

soddalashtirilgan. Asarlarning minimal sonini beradigan kombinatsiya

F1 = (AB +AC +BC)’ иF2 =AB +AC +A’B’C’

Bu kombinatsiya bo'laklarning to'rt xil atamasini beradi: AB, AC, BC va

A'B'C'. Kombinatsiya uchun PLA dasturlash jadvali 7.3-rasmda ko'rsatilgan.

E'tibor bering, F1 chiqishi haqiqiy chiqishdir, garchi uning ustida jadvalda C

belgisi qo'yilgan bo'lsa ham. Buning sababi, F1 VA-YOKI sxemasi yordamida

hosil qilingan va YOKI elementi chiqishida mavjud. XOR shlyuzi haqiqiy F1

chiqishini olish uchun funktsiyani to'ldiradi.

7.3-rasm. Misol uchun yechim.

Misolda ishlatiladigan kombinatsiya sxemasi PLA bilan amalga oshirish

uchun juda oddiy. Bu faqat tasviriy maqsadlar uchun taqdim etilgan. Oddiy PLA

ko'p sonly kirishlar va mahsulot shartlariga ega. Mantiqiy funktsiyalarni juda ko'p

o'zgaruvchilar bilan soddalashtirish kompyuterni soddalashtirish protseduralari

yordamida amalga oshirilishi kerak. Kompyuterli dizayn (SAPR) dasturi har bir

funktsiyani soddalashtiradi va uni minimal shartlarga qo'shadi. Keyin dastur

barcha vazifalarni to'g'ri yoki kengaytirilgan shaklda qamrab oladigan asarlar

shartlarining minimal sonini tanlaydi. Keyin PLA dasturlash jadvali tuziladi va

kerakli sug'urta xaritasi olinadi. Sug'urta xaritasi FPLA dasturchisiga qo'llaniladi, u

apparat protsedurasidan o'tib, integral mikrosxemadagi ichki sigortalarni o'chiradi.

Программирование

Программирование Электроника

Электроника