Похожие презентации:

Схемотехника вычислительных систем. Лекция 4. Регистры

1. СХЕМОТЕХНИКА ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ

Ким Валерий Львовичд.т.н., профессор ТПУ

СХЕМОТЕХНИКА ВЫЧИСЛИТЕЛЬНЫХ

СИСТЕМ

Лекция 4

РЕГИСТРЫ

2. Регистры

1. Регистрыпоследовательностные устройства для приема,хранения и выдачи цифровых данных

2. Классификация:

Параллельные,

последовательные,

комбинированные (универсальные). Строятся на основе D-,

JK-триггеров. Q 7

Q6

Q0

out

D 7 D 6 … .D 1 D 0

Р7

Р6

Q7

Q6… .

Р7

Р6

Р5

Р4

Р3

Р2

Р1

Р0

SI

СИ

… … .Q 0

Р5

Р4

Р3

Р2

Р1

Р0

СИ

D 7 D 6 … .D 1 D 0

2

3. Классификация

По способу приёма и выдачи информации• Параллельные – приём и выдача данных

производится по всем разрядам (PIPO).

• Последовательные

(сдвигающие)

–

данные

записываются в последовательном коде разряд за

разрядом; тактирующие сигналы перемещают

слово в разрядной сетке; выдача информации

также последовательным кодом. (SISO)

• Параллельно-последовательные (универсальные)

– имеют входы и выходы для приёма и выдачи

данных,

как

последовательным,

так

и

параллельным кодом. (SIPO, PISO)

3

4. Микрооперации

• Установка регистра в нулевое состояние (сброс),либо в единичное (предустановка).

• Запись входных данных в последовательном коде.

• Запись входных данных в параллельном коде.

• Хранение данных.

• Сдвиг хранимого кодового слова вправо или влево.

• Выдача хранимых данных в последовательном

коде.

• Выдача хранимых данных в параллельном коде.

4

5. Обычный регистр (PIPO)

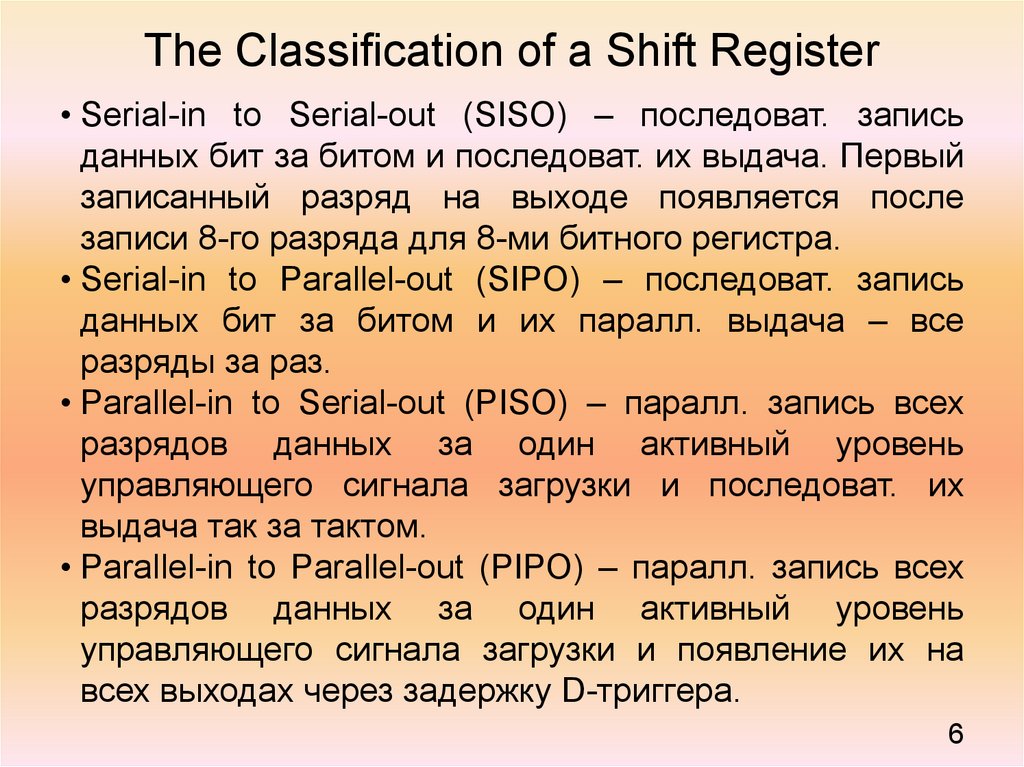

56. The Classification of a Shift Register

• Serial-in to Serial-out (SISO) – последоват. записьданных бит за битом и последоват. их выдача. Первый

записанный разряд на выходе появляется после

записи 8-го разряда для 8-ми битного регистра.

• Serial-in to Parallel-out (SIPO) – последоват. запись

данных бит за битом и их паралл. выдача – все

разряды за раз.

• Parallel-in to Serial-out (PISO) – паралл. запись всех

разрядов данных за один активный уровень

управляющего сигнала загрузки и последоват. их

выдача так за тактом.

• Parallel-in to Parallel-out (PIPO) – паралл. запись всех

разрядов данных за один активный уровень

управляющего сигнала загрузки и появление их на

всех выходах через задержку D-триггера.

6

7. The Universal Register

78. Классификация

По количеству каналов передачи данных• Однофазные.

• Парафазные. В парафазном регистре каждый бит

данных передаётся по двум каналам – в прямом и

инверсном коде.

8

9. The Shift Register

SIPODSL

• Какого типа?

• В какую сторону осуществляется сдвиг?

9

10. The Shift Register

1011. Последовательные сдвигающие регистры (DSL)

Последовательные сдвигающие регистрыData Shift Left

(DSL)

SISO

11

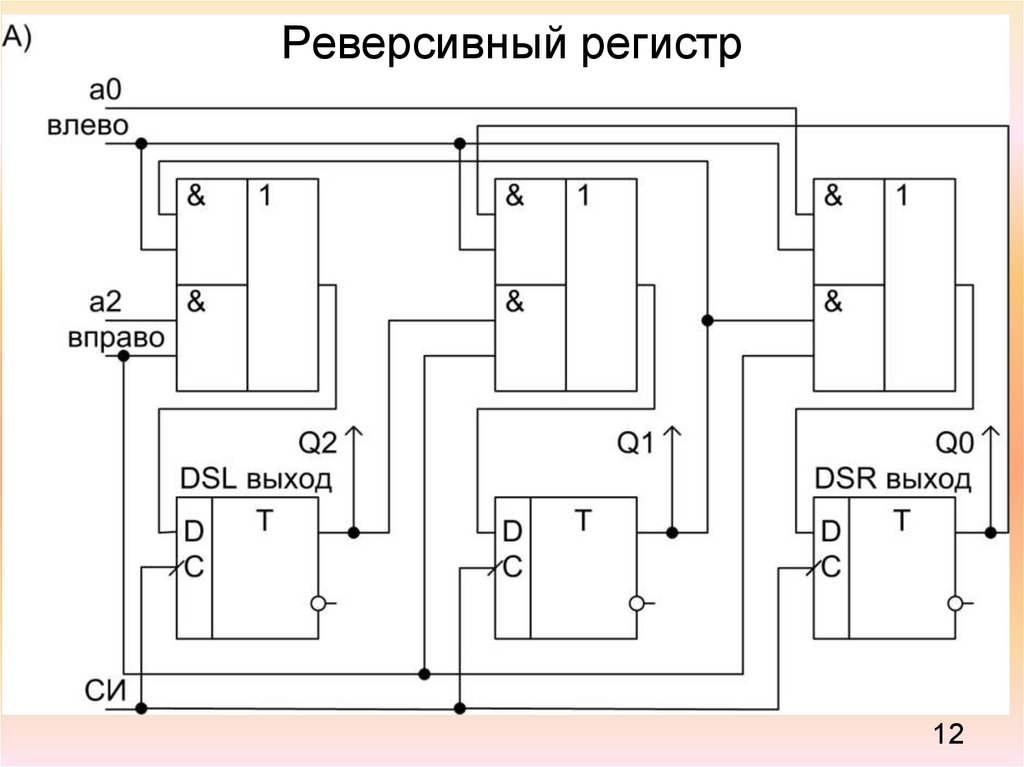

12. Реверсивный регистр

1213. Реверсивный регистр

1314. Asynchronous Load (CLR Missing)

1415. Synchronous Load

LoadSRI

• SRI – Serial Data Shift Right Input.

• Load – сигнал разрешения синхронной загрузки

данных параллельным кодом.

15

16. Регистровый файл

• ИС регистровых запоминающих устройств (ЗУ)входят в состав большинства серий, в том числе и

микропроцессорные комплекты БИС в качестве

регистров

общего

назначения

(РОН)

и

многорежимных буферных регистров (МБР).

• ЗУ произвольного доступа, позволяет обращаться

к любому регистру для записи или чтения данных.

Они реализуются на параллельных регистрах.

• Регистровое ЗУ с последовательным доступом для

обращения к нужной информации требует перебор

адреса в сторону увеличения или уменьшения

адресов.

16

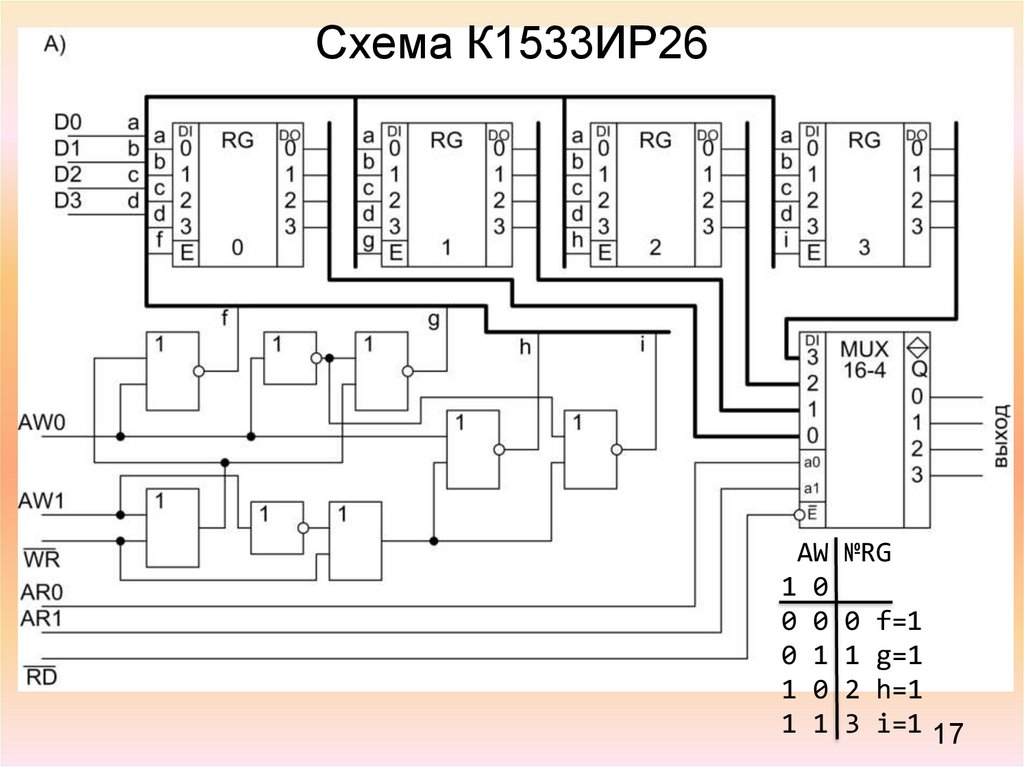

17. Схема К1533ИР26

AW №RG1 0

0 0 0 f=1

0 1 1 g=1

1 0 2 h=1

1 1 3 i=1 17

18. УГО К1533ИР26

1819. УГО регистров

Параллельный 4-х разрядныйс тремя состояниями

Последовательные 8-ми разрядные

сдвиг вправо

сдвиг влево

DD1

DD2

D RG QZ

1

2

3

4

1

2

3

4

8

SI RG

С

DD3

8

Q0

SI RG Q7

С

С

OE

19

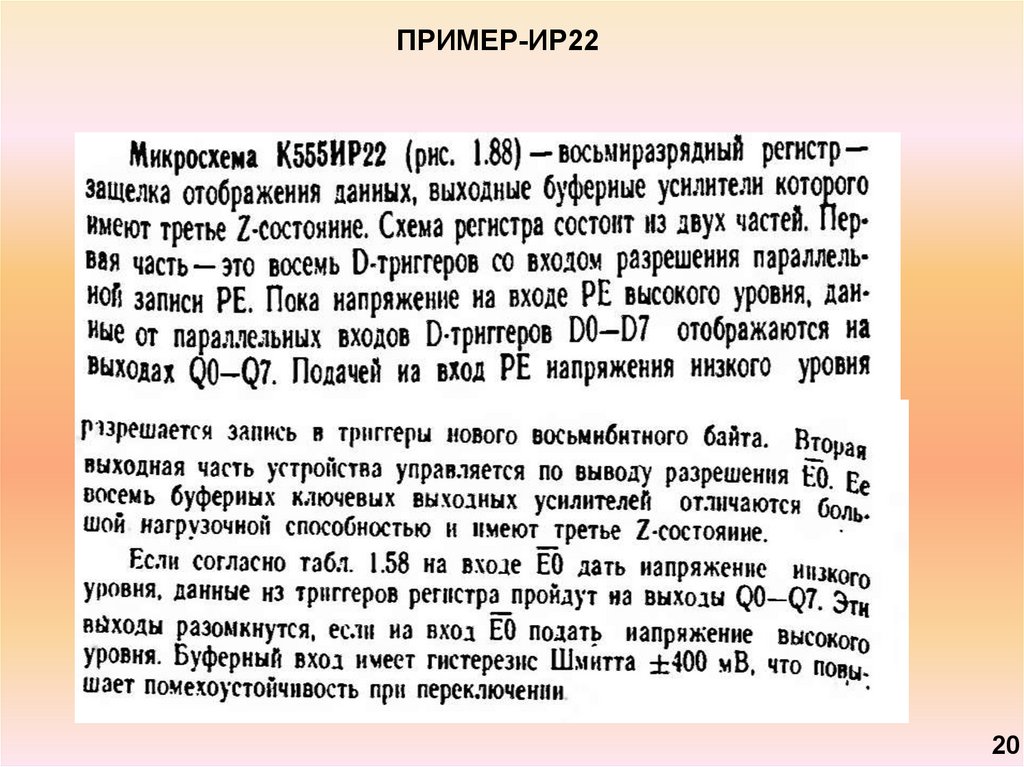

20. ПРИМЕР-ИР22

2021. ИР22

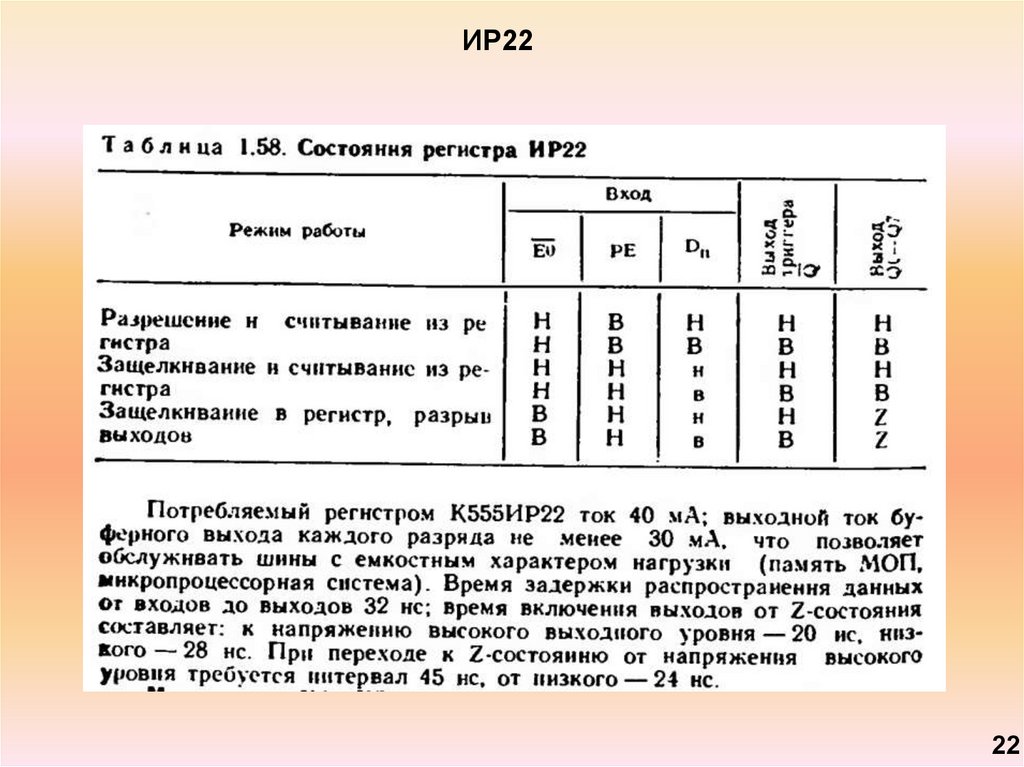

2122. ИР22

2223. ПРИМЕР-ИР9

2324. ИР9

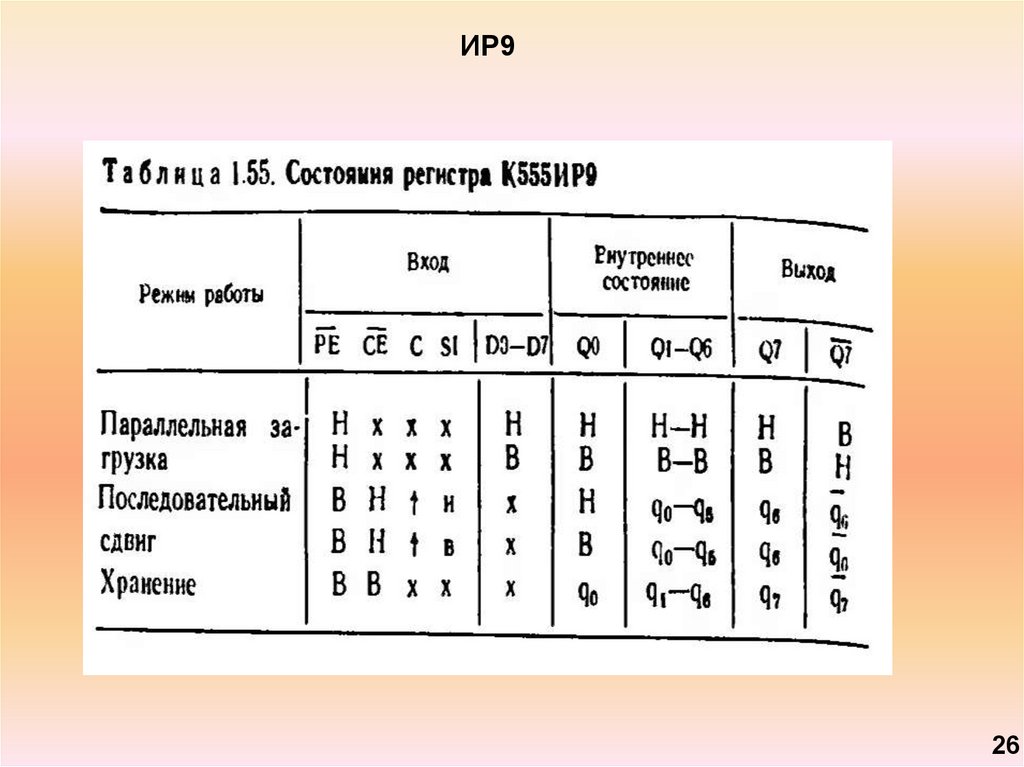

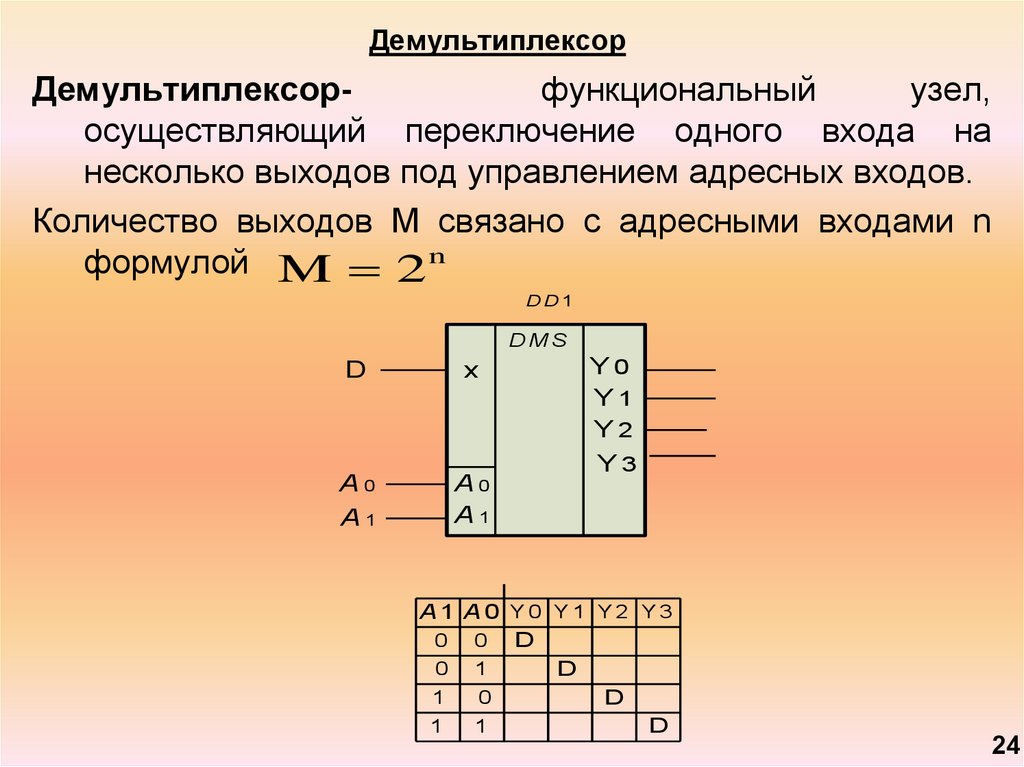

2425. ИР9

2526. ИР9

2627. ПРИМЕР-ИР25

2728. ПРИМЕР – ИР25

2829. Комбинационные устройства

1. КУ – устройства, осуществляющие преобразованиецифровой информации без запоминания.

Выходные переменные КУ однозначно определяются

входными переменными и не зависят от состояния в

предшествующий момент времени.

Типичные

представители

КУ

–

шифраторы

и

дешифраторы, мультиплексоры и демультиплексоры,

компараторы кодов, сумматоры и АЛУ.

Такие устройства состоят их логических элементов И-НЕ,

ИЛИ-НЕ и др. Проектируются на основе теории

логических схем.

19

30. Шифраторы и дешифраторы

1. Шифраторы- функциональный узел, преобразующийвходной M-разрядный код в n-разрядный выходной код

с меньшим числом разрядов.

Если

M 2 n , то шифратор полный, если

M

2 n , то шифратор неполный.

20

31. Шифраторы и дешифраторы

+ E питDD1

R1

R2

CD

x0

x1

x2

x3

D0

D1

D2

D3

Y0

VD1

VD2

Y1

Дешифраторы- функциональный узел, преобразующий

входной n-разрядный код в M-разрядный выходной код

с большим числом разрядов.

Если

n , то дешифратор полный,

M 2

если

M

2n

, то дешифратор неполный.

21

32. Дешифратор 3*8 с инверсными выходами

DD1DC

D0

0

1

2

3

4

5

6

7

1

D1

2

D2

4

В ходы

В ы ходы

D2

D1

D0

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

22

33. Мультиплексоры и демультиплексоры

Мультиплексор- функциональный узел, осущеcтвляющийпереключение нескольких входных данных на один

выход под управлением адресных входов.

Количество входов М связано с адресными входами n

n

формулой

M 2

DD1

MS

x0

x1

x2

x3

А0

А1

Y

А0

А1

А1

0

0

1

1

А0

0

1

0

1

Y

x0

x1

x2

x3

23

34. Демультиплексор

Демультиплексорфункциональныйузел,

осущеcтвляющий переключение одного входа на

несколько выходов под управлением адресных входов.

Количество выходов М связано с адресными входами n

формулой M 2 n

DD1

DMS

D

x

А0

А1

А0

А1

Y0

Y1

Y2

Y3

А1 А0 Y0 Y1 Y2 Y3

0 0

D

0 1

D

1

0

D

1

1

D

24

35. Интегральные микросхемы КУ

К Р 1533К П 7C

D

0

1

2

3

4

5

6

7

A

B

C

SED

1

2

3

DD1

1

MS

D0

D1

D2

F

D3

5

4

3

15

D4

F

6

D5

D6

D7

A

B

10

11

12

13

2

14

E1

D1

0

1

2

3

E2

D2

0

1

2

3

a0

a1

MS

7

F1

F2

9

UП – 16, общ– 8

25

36.

Спасибо за внимание![email protected]

Электроника

Электроника