Похожие презентации:

Микроконтроллеры ATMEL

1. Микроконтроллеры ATMEL

Слядзевская К.П., к.т.н., доценткаф.ЭПА

2. Выводы микроконтроллера ATTiny 2313

(RESET / dW ) PA21

20

VCC

(RXD) PD0

2

19

PB7 (UCSK/ SCK/ PCINT 7)

(TXD) PD1

3

18

PB6 (DO/ PCINT 6)

(XTAL2) PA1

4

17

PB5 (DI / SDA/ PCINT 5)

(XTAL1) PA0

5

16

PB4 (OC1B/ PCINT 4)

(CKOUT/ XCK / INT 0) PD2

6

15

PB3 (OC1A/ PCINT 3)

(INT 1) PD3

7

14

PB2 (OC0A/ PCINT 2)

(T0) PD4

8

13

PB1 (AIN 1/ PCINT 1)

(OC0B/T1) PD5

9

12

PB0 (AIN 0/ PCINT 0)

10

11

PD6 (ICP)

GND

3. Выводы микроконтроллера ATMega128x

4. Структурная схема ATTiny 2313

5. Структурная схема ATMega128x

6. Упрощенная архитектура ATTiny 2313

7. Карта памяти микроконтроллера ATTiny 2313

8. Регистр управления EEPROM ATTiny 2313

9.

10.

11. Карта памяти ATMega128x

$0000$000

$0000

32 Регистра

общего назначения

FLASH

$001F

$0020

$FFFF

64 регистра

ввода/вывода

EEPROM

$005F

$0060

160 дополнительных

регистров ввода/вывода

$FFF

Внутреннее

статическое

ОЗУ

Внешнее

статическое

ОЗУ

$10FF

$1100

$FFFF

12. Регистр управления EEPROM ATMega128

13.

14. Регистровый файл

70

Адрес

R0

0х00

R1

0x01

R2

0x02

Рабочие

регистры

…..

R26

0x1A

Х-регистр младший байт

R27

0x1B

Х-регистр старший байт

R28

0x1C

Y-регистр младший байт

R29

0x1D

Y-регистр старший байт

R30

0x1E

Z-регистр младший байт

R31

0x1F

Z-регистр старший байт

15. МЕТОДЫ АДРЕСАЦИИ

• Методы адресации памяти данных• Различают следующие восемь способов адресации памяти

данных:

• - прямая адресация одного регистра РОН;

• - прямая адресация двух регистров РОН;

• - прямая адресация регистра ввода/вывода;

• - прямая адресация ОЗУ;

• - простая косвенная адресация;

• - относительная косвенная адресация;

• - косвенная адресация с преддекрементом;

• - косвенная адресация постинкрементном.

Из перечисленных способов адресации обращения к памяти

данных микроконтроллер без ОЗУ поддерживают только 1,2,3 и

5 варианты способ адресации.

16. Прямая регистровая адресация с одним регистром

17. Прямая адресация 2-х РОН

18. Прямая адресация регистров ввода/вывода

19. Косвенная адресация

20. Непосредственная прямая регистровая адресация

КОПК

Адрес

К

При этом способе адресации поле адреса составляет 4

бита, и поэтому обращаться можно только к 16-ти

старшим РОН (R16…R31).

• LDI R17, $14

• ANDI R20, $20

21. Относительная адресация памяти программ

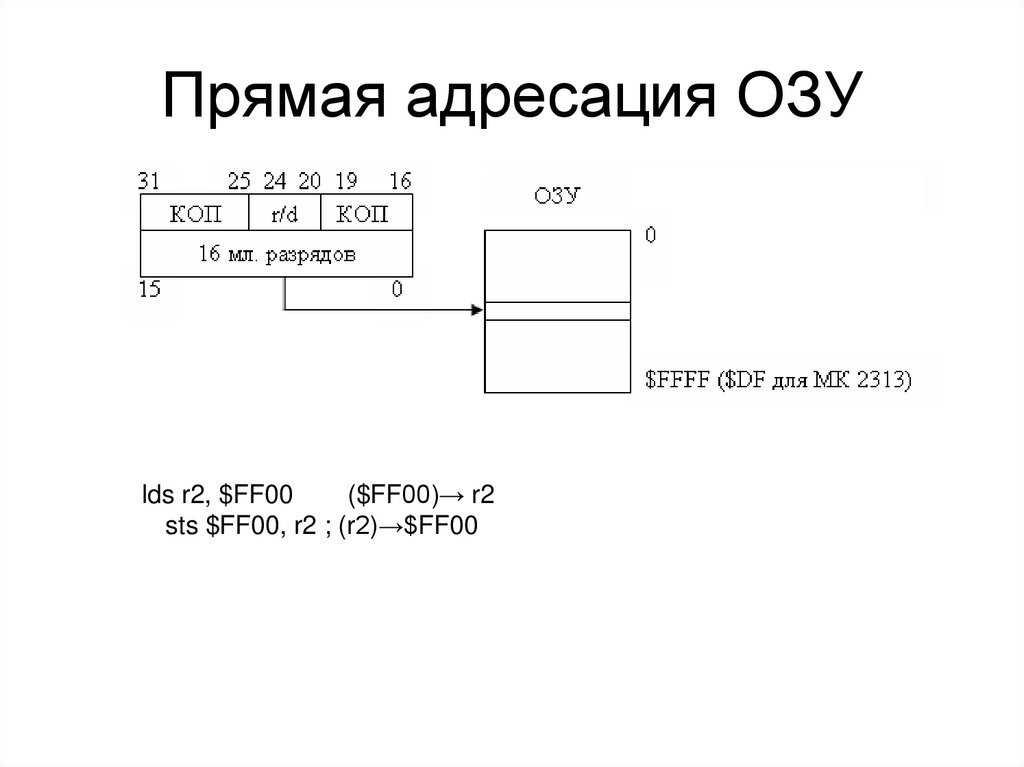

22. Прямая адресация ОЗУ

lds r2, $FF00($FF00)→ r2

sts $FF00, r2 ; (r2)→$FF00

23. Относительная косвенная адресация

Пример:[(z+3)]→r4,Тогда необходимо

clr r31 – очистить старший байт инд. регистра Z

ldi r30, $65; загрузить младший байт адреса

ldd r4, z+3; r4=[$0065]

24. Косвенная адресация с преддекрементом

сlr r27; очистка младшего байт Хldi r26, $65; загрузить мл. байт адр

ld r3,-x; r3=[$0064]

25. Косвенная адресация с постинкрементом

Пример:Загрузить ячейку $65 в регистр r3 через y

LDR3 ,y+

clr r29; очистка ст. б. y

ldi r28, $65;

ld r3, y+; [$65] →r3

in r2, r28; в r28 - $66

26. Косвенная адресация памяти программ( команд IJMP и ICALL)

27. Относительная адресация памяти программ (RCALL, RJMP)

28. Конфигурирование выводов порта

DDхnРОRТхn

РUD (in МСUСR2)

Ввод/выво

д

Нагрузка

Комментарий

0

0

x

Ввод

Выкл.

Третье

состояние (2 —

состояние)

0

1

0

Ввод

Вкл.

Рхn создает

выходящий ток,

если внешняя

цепь замкнута

на общий

провод

0

1

1

Ввод

Выкл.

Третье

состояние (z —

состояние)

1

0

x

Вывод

Выкл.

Вывод низкого

уровня

(Приемник

тока)

1

1

x

Вывод

Выкл.

Вывод высокого

уровня

(Источник тока)

29. Пример на языке Ассемблер

; Включение нагр. резисторов и установка выходных уровней; Определение направления передачи сигналов для разрядов

ldi

r16, (1<<PB7)|(1<<PB6)| (1<<PB1)| (1<<PB0)

ldi

r17, (1<<DDB3)| (1<<DDB2)| (1<<DDB1)| (1<<DDB0)

out

PORTB, r16

out

DDRB, r 17

; Добавлен nop для синхронизации

nop

Чтение разрядов порта

in

r16, PINB

30. Векторы сброса и обработки прерываний ATTiny2313

Номервектора

Адрес

перехода

Источник

Описание прерывания

1

0x0000

RESET

Внешний сброс, сброс при включении питания, сброс по

срабатыванию охранного таймера

2

0x0001

INT0

Внешний запрос на прерывание по входу INT0

3

0x0002

INT1

Внешний запрос на прерывание по входу INT1

4

0x0003

ТIМЕR1 СAPT

Прерывание по захвату таймера/счетчика 1

5

0x0004

TIMER1 СОМРА

Прерывание по совпадению таймера/счетчика 1. Канал А

6

0x0005

ТIМЕR1 ОVF

Прерывание по переполнению таймера/счетчика 1

7

0x0006

ТIМЕR0 OVF

Прерывание по переполнению таймера/счетчика 0

8

0x0007

USART0, RX

USART0, прием завершен

9

0x0008

USART0, UDRE

USART0 буфер данных пуст

10

0x0009

USART0, TX

USART0, передача завершена

11

0x000A

ANALOG COMP

Прерывание от аналогового компаратора

12

0x000B

PCINT

Прерывание по изменению на любом из выводов

13

0x000C

TIMER1 COMPB

Прерывание по совпадению таймера/счетчика 1. Канал В

14

0x000D

TIMER0 COMPA

Прерывание по совпадению таймера/счетчика 0. Канал В

15

0x000E

TIMER0 COMPB

Прерывание по совпадению таймера/счетчика 0. Канал А

16

0x000F

USI START

Прерывание по USI. Готовность к старту

17

0x0010

USI OVERFLOW

Прерывание по USI. Переполнение

18

0x0011

EE READY

Готовность ЕЕPROM

19

0x0012

WDT OVERFLOW

Переполнение охранного таймера

31. Регистр управления микроконтроллером — MCUCR

Номер битаЧтение (R)/Запись(W)

Начальное значение

7

6

5

4

3

2

1

0

PUD

SM1

SE

SM0

ISC11

ISC10

ISC01

ISC00

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

MCUCR

32. Режимы вызова прерывания INT0

ISC01ISC00

Описание

0

0

Низкий уровень на входе INT0 генерирует запрос на

прерывание

0

1

Любое изменение логического уровня на входе INT0

генерирует запрос на прерывание

1

0

Задний фронт входного сигнала INT0 вызывает

запрос на прерывание

1

1

Передний фронт входного cигнала INT0 вызывает

запрос на прерывание

33. Главный регистр маски прерываний — GIMSK

Номер битаЧтение(R)/Запись(W)

Начальное значение

7

6

5

4

3

2

1

0

INT1

INT0

PCIE

-

-

-

-

-

R/W

R/W

R/W

R

R

R

R

R

0

0

0

0

0

0

0

0

GIMSK

34. Регистр флагов внешних прерываний — EIFR

Номер битаЧтение(R)/Запись(W)

Начальное значение

7

6

5

4

3

2

1

0

INTF1

INTF0

PCIF

-

-

-

-

-

R/W

R/W

R/W

R

R

R

R

R

0

0

0

0

0

0

0

0

EIFR

35. Таблица векторов прерываний для микроконтроллера ATMega128

ИсточникINT0

INT1

INT2

INT3

INT4

INT5

INT6

INT7

TIMER2 COMP

TIMER2 OVF

TIMER1 CAPT

TIMER1 COMPA

TIMER1 COMPB

TIMER1 OVF

TIMER0 COMP

TIMER0 OVF

SPI, STC

Описание

Внешнее прерывание 0

Внешнее прерывание 1

Внешнее прерывание 2

Внешнее прерывание 3

Внешнее прерывание 4

Внешнее прерывание 5

Внешнее прерывание 6

Внешнее прерывание 7

Совпадение таймера/счетчика Т2

Переполнение таймера/счетчика Т2

Захват таймера/счетчика Т1

Совпадение «А» таймера/счетчика Т1

Совпадение «В» таймера/счетчика Т1

Переполнение таймера/счетчика Т1

Совпадение таймера/счетчика Т0

Переполнение таймера/счетчика Т0

Передача по SPI завершена

№

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Адрес

$0002

$0004

$0006

$0008

$000A

$000C

$000E

$0010

$0012

$0014

$0016

$0018

$001A

$001C

$001E

$0020

$0022

36. Таблица векторов прерываний для микроконтроллера ATMega128 продолжение

USART0, RXUSART0, UDRE

USART0, TX

ADC

EE_RDY

ANA_COMP

TIMER1 COMPC

TIMER3 CAPT

TIMER3 COMPA

TIMER3 COMPB

TIMER3 COMPC

TIMER3 OVF

USART1, RX

USART1, UDRE

USART1, TX

TWI

SPM_RDY

USART0, прием завершен

Регистр данных USART0 пуст

USART0, передача завершена

Преобразование АЦП завершено

EEPROM, готово

Аналоговый компаратор

Совпадение «C» таймера/счетчика Т1

Захват таймера/счетчика Т3

Совпадение «А» таймера/счетчика Т3

Совпадение «В» таймера/счетчика Т3

Совпадение «C» таймера/счетчика Т3

Переполнение таймера/счетчика Т3

USART1, прием завершен

Регистр данных USART1 пуст

USART1, передача завершена

Прерывание от модуля TWI

Готовность SPM

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

$0024

$0026

$0028

$002A

$002C

$002E

$0030

$0032

$0034

$0036

$0038

$003A

$003C

$003E

$0040

$0042

$0044

37. Формат регистра EIMSK

Бит7

6

5

4

3

2

1

0

INT7 INT6 INT5 INT4 INT3 INT2 INT1 INT0

Чтение/запись

Начальное

значение

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

38. Формат регистра EICRA

Бит7

6

5

4

3

2

1

0

ISC31 ISC30 ISC21 ISC20 ISC11 ISC10 ISC01 ISC00

Чтение/запись

Начальное

значение

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

39. Формат регистра EICRB

Бит7

6

5

4

3

2

1

0

ISC71 ISC70 ISC61 ISC60 ISC51 ISC50 ISC41 ISC40

Чтение/запись

Начальное

значение

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

40. Формат регистра EIFR

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

INTF7

INTF6 INTF5 INTF4 INTF3 INTF2 INTF1 INTF0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

41. Блок схема 8-разрядного таймера/счетчика T0

42. Устройство синхронизации

43. Временные диаграммы для режима СТС

44.

45.

46.

47.

48.

49. Формат регистра MCUCR

50.

51.

52.

53.

54.

55. Формирование ШИМ – сигнала в режиме Fast PWM

56. Формирование ШИМ – сигнала в режиме Phase Correct PWM

57. Регистр маски прерываний таймера/счетчика — TIMSK

Номер бита7

6

5

4

3

2

1

0

TOIE1

OCIE1A

OCIE1B

-

TICIE1

OCIE0B

TOIE0

OCIE0A

Чтение

(R)/Запись(W)

W

W

R

R

R

R

R

R

Начальное

значение

0

0

0

0

0

0

0

0

TIMSK

58. Формат регистра TIFR

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

TOV1

OCF1A

OCF1B

-

ICF1

OCF0B

TOV0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

0

OCF0A

R/W

0

59. Формат регистра TCCR0A

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

COM0A1

COM0A0

COM0B1

COM0B0

-

-

WGM01

WGM00

R/W

R/W

R/W

R/W

R

R

R/W

R/W

0

0

0

0

0

0

0

0

60. Формат регистра TCCR0B

Бит7

6

5

4

3

2

1

0

FOC0A

FOC0B

-

-

WGM02

CS02

CS01

CS00

Чтение/запись

W

W

R

R

R/W

R/W

R/W

R/W

Начальное

значение

0

0

0

0

0

0

0

0

61. Выбор режимов работы таймера 0

№реж

има

WGM2

WGM1

WGM0

Название режима

Верхний предел

(TOP)

OCRx

изменяется

Флаг TOV

устанавливает

ся от

0

0

0

0

Normal

0xFF

Непосредс

твенно

МАХ

1

0

0

1

PWM Phase

Correct

0xFF

При

достижени

и TOP

BOTTOM

2

0

1

0

СТС

OCRA

Непосредс

твенно

МАХ

3

0

1

1

Fast PWM

0xFF

При

достижени

и ТОР

МАХ

4

1

0

0

Зарезервировано

-

-

-

5

1

0

1

PWM Phase Correct

OCRA

При

достижени

и ТОР

BOTTOM

6

1

1

0

Зарезервировано

-

-

-

7

1

1

1

Fast PWM

OCRA

При

достижени

и ТОР

ТОР

62. Выбор источника тактового сигнала

CSx2CSx1

CSx0

Описание

0

0

0

Нет источника сигнала (таймер/счетчик остановлен)

0

0

1

clkI/O/l (нет предварительного деления)

0

1

0

clkI/O/8 (деление на 8)

0

1

1

clkI/O/64 (деление на 64)

1

0

0

clkI/O/256 (деление на 256)

1

0

1

clkI/O/1024 (деление на 1024)

1

1

0

Внешний источник сигнала, вход Тx. Синхронизация по заднему фронту

1

1

1

Внешний источник сигнала, вход Тx. Синхронизация по переднему

фронту

63. Блок-схема 16-разрядного таймера/счетчика T1

64. Режимы работы таймера T1

ModeWGM

13

WGM

12

(СТС1)

WGM

11

(PW

M11)

WGM

10

(PWM

10)

Режим работы

таймера/ счетчика

TOP

Регистр OCR1

x загружается

из

Флаг TOV1

устанавливается

пo

0

0

0

0

0

Normal

0xFFFF

Непосредстве

нно

MAX

1

0

0

0

1

PWM, Phase

Correct, 8-бит

0x00FF

TOP

BOTTOM

2

0

0

1

0

PWM, Phase

Correct, 9-бит

0x01FF

TOP

BOTTOM

3

0

0

1

1

PWM, Phase

Correct, 10-бит

0x03FF

TOP

BOTTOM

4

0

1

0

0

CTC

OCR1A

Непосредстве

нно

MAX

5

0

1

0

1

Fast PWM, 8-бит

0x00FF

TOP

TOP

6

0

1

1

0

Fast PWM, 9- бит

0x0IFF

TOP

top

7

0

1

1

1

Fast PWM, 10- бит

0x03FF

TOP

TOP

65. Режимы работы таймера T1

ModeWGM

13

WGM

12

(СТС1)

WGM

11

(PW

M11)

WGM

10

(PWM

10)

Режим работы

таймера/ счетчика

TOP

Регистр OCR1

x загружается

из

Флаг TOV1

устанавливается

пo

8

1

0

0

0

PWM, Phase and

Frequency Correct

ICR1

BOTTOM

BOTTOM

9

1

0

0

1

PWM, Phase and

Frequency Correct

OCR1A

BOTTOM

BOTTOM

10

1

0

1

0

PWM, Phase Correct

ICR1

TOP

BOTTOM

11

1

0

1

1

PWM, Phase Correct

OCR1A

TOP

BOTTOM

12

1

1

0

0

CTC

ICR1

Непосредстве

нно

MAX

13

1

1

0

1

(Зарезервировано)

-

-

-

14

1

1

1

0

Fast PWM

ICR1

TOP

top

15

1

1

1

1

Fast PWM

OCR1A

TOP

TOP

66. Регистр В управления таймером/счетчиком — TCCR1В

Номер битаЧтение

(R)/Запись(W)

Начальное

значение

7

6

5

4

3

2

1

0

ICNC1

ICES1

-

WGM13

WGM12

CS12

CS11

CS20

R/W

R/W

R

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

TCCR1B

67. Регистр А управления таймером/счетчиком — TCCR1A

Номер битаЧтение

(R)/Запись(W)

Начальное

значение

7

6

5

4

3

2

1

0

COM1A1

COM1A0

COM1B1

COM1B0

-

-

WGM11

WGM10

R/W

R/W

R/W

R/W

R

R

R

R/W

0

0

0

0

0

0

0

0

TCCR1A

68. Формат регистра TIMSK ATMega128x

Бит7

6

5

4

3

2

1

0

OCIE2 TOIE2 TICIE1 OCIE1A OCIE1B TOIE1 OCIE0 TOIE0

Чтение/запись

Начальное

значение

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

69. Формат регистра ЕTIMSK

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

-

-

R

R

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

TICIE3 OCIE3A OCIE3B TOIE3 OCIE3С OCIE1С

70. Формат регистра TIFR

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

OCF2 TOV2 ICF1

OCF1A

OCF1B

TOV1

OCF0

TOV0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

71. Формат регистра ETIFR

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

-

-

ICF3

OCF3A

OCF3B

TOV3

OCF3С

R

R

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

OCF1C

72. Формат регистра TCCR0

БитЧтение/запись

Начальное

значение

7

6

5

4

3

FOC0

WGM00

COM01

COM00

WGM01

R/W

R/W

0

0

W

R/W

0

0

2

1

0

CS02

CS01

CS00

R/W

R/W

R/W

R/W

0

0

0

0

73. Формат регистра TCCR2

БитЧтение/запись

Начальное

значение

7

6

5

4

3

FOC2

WGM20

COM21

COM20

WGM21

R/W

R/W

0

0

W

R/W

0

0

2

1

0

CS22

CS21

CS20

R/W

R/W

R/W

R/W

0

0

0

0

74. Выбор режима работы таймера Т0 и T2

WGMn1 WGMn0 Режим работы таймера/счетчика Tn0

0

Normal

0

1

Phase correct PWM

1

0

CTC (сброс при совпадении)

1

1

Fast PWM

75. Выбор источника тактового сигнала таймера Т0

CS020

0

0

0

1

1

1

1

CS01

0

0

1

1

0

0

1

1

CS00

0

1

0

1

0

1

0

1

Источник тактового сигнала

AS0= «1»

AS0= «0»

Таймер/счетчик остановлен

Clk TOSC1

Clk I/O

Clk TOSC1/8

Clk I/O/8

Clk ТOSC1/32

Clk I/O/32

Clk TOSC1/64

Clk I/O/64

Clk TOSC1/128

Clk I/O/128

Clk TOSC1/256

Clk I/O/256

Clk TOSC1/1024

Clk I/O/1024

76. Формат регистра TCCR1А

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

COM1A1

COM1A0

COM1B1

COM1В0

COM1С1

COM1С0

WGM11

WGM10

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

77. Формат регистра TCCR1В

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

ICNC1

ICES1

-

WGM13

WGM12

CS12

CS11

CS10

R/W

0

R/W

0

R

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

78. Формат регистра TCCR1С

БитЧтение/запись

Начальное

значение

7

6

5

4

3

2

1

0

FOC1A

FOC1B

FOC1C

-

-

-

-

-

W

0

W

0

W

0

R

0

R

0

R

0

R

0

R

0

79. Структурная схема модуля АЦП

80. Формат регистра ADCSRA

БитЧтение/запись

Начальное

значение

7

6

ADEN

R/W

0

5

3

2

1

0

ADSC ADFR ADIF

ADIE

ADPS2

ADPS1

ADPS0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

4

R/W

0

81. Выбор коэффициента предделителя АЦП

ADPS20

0

0

0

1

1

0

1

ADPS1

0

0

1

1

0

0

1

1

ADPS0

0

1

0

1

0

1

0

1

Коэффициент деления

2

2

4

8

16

32

64

128

82. Формат регистра ADMUX

БитЧтение/запись

Начальное

значение

7

6

5

REFS1

REFS0

R/W

0

R/W

0

4

3

2

1

0

ADLAR MUX4

MUX3

MUX2

MUX1

MUX0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

83. Выбор источника опорного напряжения

REFS10

0

1

1

REFS0 Источник опорного напряжения(ИОН)

0

Внешний ИОН, подключенный к выводу AREF,

внутренний ИОН отключен.

1

Напряжение питания AVcc

0

Зарезервировано

1

Внутренний ИОН напряжением 2,56В, подключенный

к выводу AREF.

84. Выбор входного канала

MUX4:MUX000000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

10000

10001

10010

10011

10100

Несимметричный

вход

Дифференциальный вход

положительный

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC6

ADC7

Не применяется

отрицательный

Предварительное

усиление

Не применяется

ADC0

ADC1

ADC0

ADC1

ADC2

ADC3

ADC2

ADC3

ADC0

ADC1

ADC2

ADC3

ADC4

ADC0

ADC0

ADC0

ADC0

ADC2

ADC2

ADC2

ADC2

ADC1

ADC1

ADC1

ADC1

ADC1

10x

10x

200X

200X

10x

10x

200x

200x

1x

1x

1x

1x

1x

85. Выбор входного канала продолжение

1010110110

10111

11000

11001

11010

11011

11100

11101

11110

Не применяется

1.22В

ADC5

ADC6

ADC7

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

ADC1

ADC1

ADC1

ADC2

ADC2

ADC2

ADC2

ADC2

ADC2

Не применяется

1x

1x

1x

1x

1x

1x

1x

1x

1x

86. Временная диаграмма первого преобразования

87. Временные диаграммы работы АЦП в режиме одиночного преобразования (а) и в режиме непрерывного преобразования (б)

88. Структурная схема модуля SPI в ATMega128

89. Переназначение режима работы выводов модуля SPI

ВыводMOSI

MISO

SCK

SS

Режим «Master»

Определяется пользователем

Вход

Определяется пользователем

Определяется пользователем

Режим «Slave»

Вход

Определяется пользователем

Вход

Вход

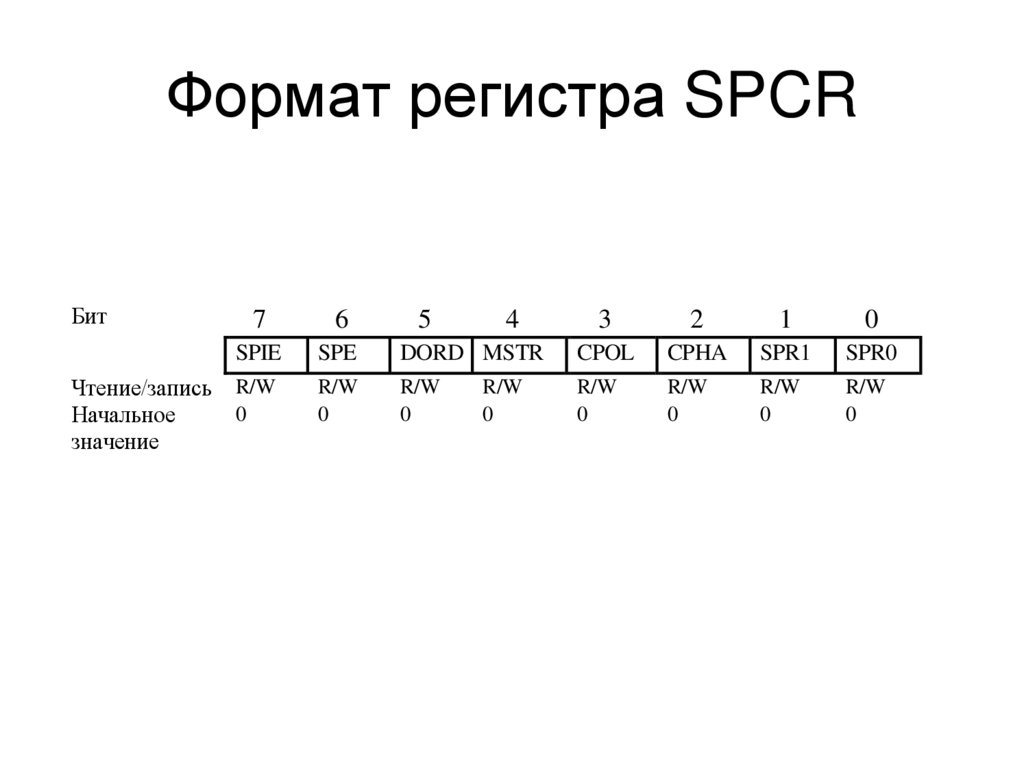

90. Формат регистра SPCR

БитЧтение/запись

Начальное

значение

7

6

SPIE

SPE

R/W

0

R/W

0

5

4

3

2

1

0

DORD MSTR

CPOL

CPHA

SPR1

SPR0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

91. Формат регистра SPSR

БитЧтение/запись

Начальное

значение

7

6

SPIF

WCOL

R

0

R

0

5

R

0

R

0

4

3

2

1

-

-

-

-

R

0

R

0

R

0

0

SPI2X

R/W

0

92. Задание режима передачи данных

РазрядОписание

CPOL

Полярность тактового сигнала

«0» — генерируются импульсы положительной полярности,

при отсутствии импульсов на выводе присутствует низкий

уровень;

«1» — генерируются импульсы отрицательной полярности,

при отсутствии импульсов на выводе присутствует высокий

уровень

СРНА

Фаза тактового сигнала

«0» — обработка данных производится по переднему фронту

импульсов сигнала SCK (для CPOL = «0» — по нарастающему

фронту, а для CPOL = «1» — по спадающему фронту);

«1» — обработка данных производится по заднему фронту

импульсов сигнала SCK (для CPOL = «0» — по спадающему

фронту, а для CPOL = «1» — по нарастающему фронту)

93.

94.

95. Задание частоты тактового сигнала SCK

SPI2X0

0

0

0

1

1

1

1

SPR1

0

0

1

1

0

0

1

1

SPR0

0

1

0

1

0

1

0

1

Частота сигнала SCK

fСLK/4

fCLK/16

fCLK/64

fCLK/128

fСLK/2

fCLK/8

fСLK/32

fCLK/64

Электроника

Электроника