Похожие презентации:

Логические элементы

1. Логические элементы

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ2.

Сигналы,действующие в устройствах, и, соответственно сами устройства можно

разделить на две большие группы: аналоговые и цифровые.

Аналоговый сигнал – сигнал непрерывный, может быть периодическим,

существует в любой момент времени и может принимать любой уровень из заданного

диапазона. Аналоговые сигналы можно подвергать различным преобразованиям без

потери информации содержащейся в них.

Квантованный

сигнал – аналоговый сигнал, который может принимать

только определенные (квантованные) значения, соответствующие уровням

квантования. Расстояние между двумя соседними уровнями - шаг квантования.

Дискретизированный сигнал – сигнал импульсный, значения которого

заданы только в определенные моменты времени, называемые моментами дискретизации. Расстояние между соседними моментами дискретизации – шаг дискретизации dT. При постоянном шаге (dT=соnst) применима теорема Котельникова:

1/dT=df> 2fB, где fB - верхняя граничная частота спектра сигнала.

Цифровой сигнал - сигнал, квантованный по уровню и дискретизированный во времени. Квантованные значения цифрового сигнала могут быть кодированы цифровым кодом, при этом каждый выделенный в процессе дискретиза-ции

отсчет заменяется соответствующим кодовым словом, которое выражает величину

этого отсчета (количество уровней квантования, попавших в этот отсчет) символы

которого имеют два значения - 0 и 1.

3. Логический элемент

ЛОГИЧЕСКИЙ ЭЛЕМЕНТЛогический элемент – это такая схема, у которой

несколько входов и один выход. Каждому состоянию сигналов

на входах, соответствует определенный сигнал на выходе.

Схема выполняет какую-либо логическую операцию

(операции) над входными данными, заданными в виде

уровней напряжения, и возвращает результат операции в

виде выходного уровня напряжения.

Для того, чтобы понять как логический элемент работает,

нужно нарисовать таблицу, в которой будут перечислены

состояния на выходе при любой комбинации входных

сигналов. Такая таблица называется таблицей истинности

или переключательной таблицей.

Логические элементы предназначены для реализации

логических функций и являются одним из наиболее

распространенных типов цифровых устройств, имеющих

как самостоятельное применение, так и входящих в состав

более сложных схем, выполненных на их основе, например,

триггеров, регистров,

счетчиков,

распределителей,

сумматоров, дешифраторов.

4. Логические элементы

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫЛогические элементы (или, как их еще называют, вентили, "gates") — это наиболее

простые цифровые микросхемы. Именно в этой простоте и состоит их отличие от других

микросхем. Как правило, в одном корпусе микросхемы может располагаться от одного

до шести одинаковых логических элементов. Иногда в одном корпусе могут

располагаться и разные логические элементы.

Обычно каждый логический элемент имеет несколько входов (от одного до двенадцати)

и один выход. При этом связь между выходным сигналом и входными сигналами

(таблица истинности) предельно проста. Каждой комбинации входных сигналов

элемента соответствует уровень нуля или единицы на его выходе. Никакой внутренней

памяти у логических элементов нет, поэтому они относятся к группе так называемых

комбинационных микросхем. Но в отличие от более сложных комбинационных

микросхем, логические элементы имеют входы, которые не могут быть разделены на

группы, различающиеся по выполняемым ими функциям.

Главные достоинства логических элементов, по сравнению с другими цифровыми

микросхемами, — это их высокое быстродействие (малые времена задержек), а также

малая потребляемая мощность (малый ток потребления). Поэтому в тех случаях, когда

требуемую функцию можно реализовать исключительно на логических элементах,

всегда имеет смысл проанализировать этот вариант. Недостаток же их состоит в том,

что на их основе довольно трудно реализовать сколько-нибудь сложные функции.

Поэтому чаще всего логические элементы используются только в качестве дополнения

к более сложным, к более "умным" микросхемам. И любой разработчик обычно

стремится использовать их как можно меньше и как можно реже.

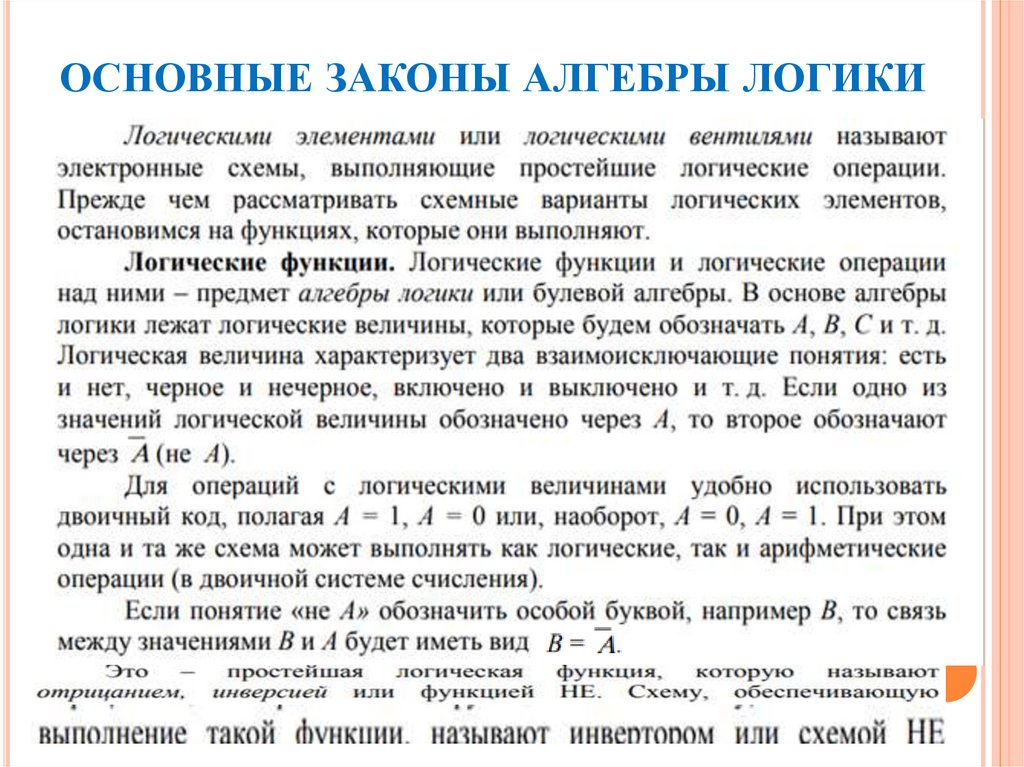

5. основные законы алгебры логики

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ6.

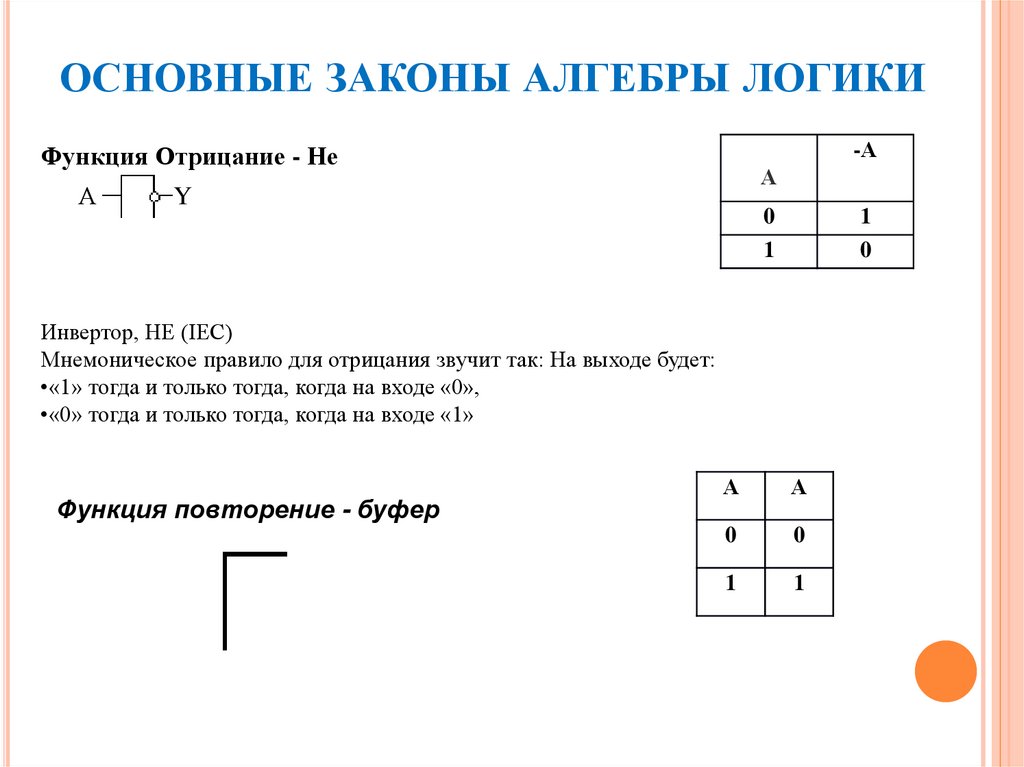

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ-А

Функция Отрицание - Не

А

А

Y

0

1

1

0

Инвертор, НЕ (IEC)

Мнемоническое правило для отрицания звучит так: На выходе будет:

•«1» тогда и только тогда, когда на входе «0»,

•«0» тогда и только тогда, когда на входе «1»

Функция повторение - буфер

А

А

0

0

1

1

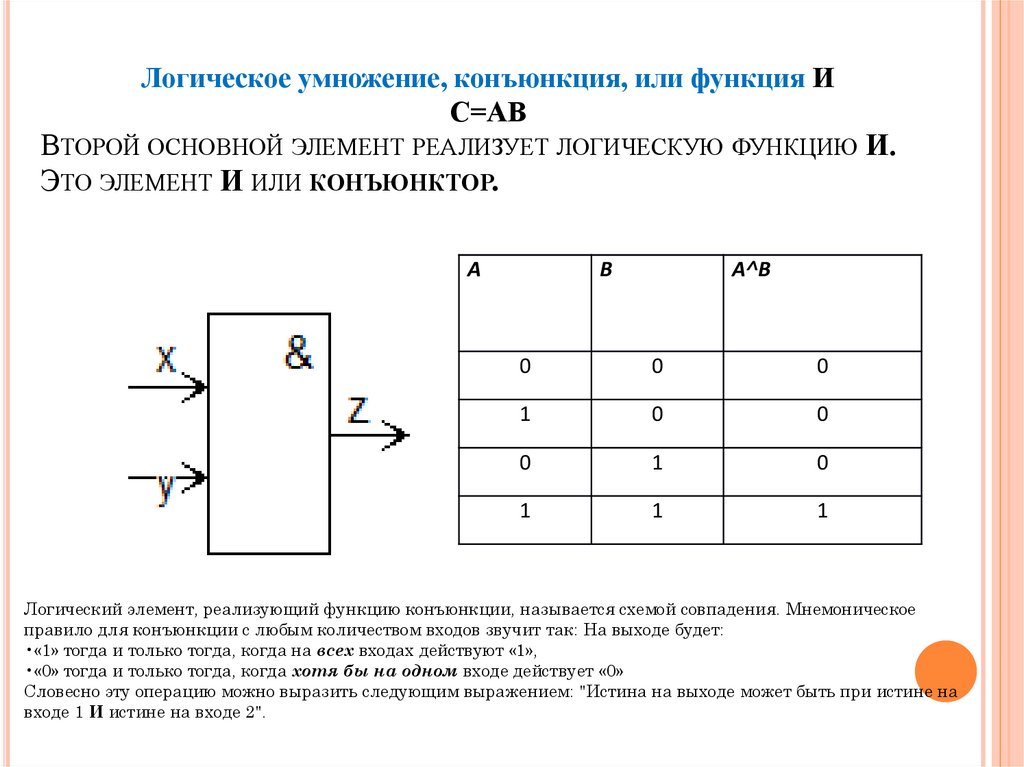

7. Второй основной элемент реализует логическую функцию И. Это элемент И или конъюнктор.

Логическое умножение, конъюнкция, или функция ИС=АВ

ВТОРОЙ ОСНОВНОЙ ЭЛЕМЕНТ РЕАЛИЗУЕТ ЛОГИЧЕСКУЮ ФУНКЦИЮ И.

ЭТО ЭЛЕМЕНТ И ИЛИ КОНЪЮНКТОР.

А

В

А˄В

0

0

0

1

0

0

0

1

0

1

1

1

Логический элемент, реализующий функцию конъюнкции, называется схемой совпадения. Мнемоническое

правило для конъюнкции с любым количеством входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на всех входах действуют «1»,

•«0» тогда и только тогда, когда хотя бы на одном входе действует «0»

Словесно эту операцию можно выразить следующим выражением: "Истина на выходе может быть при истине на

входе 1 И истине на входе 2".

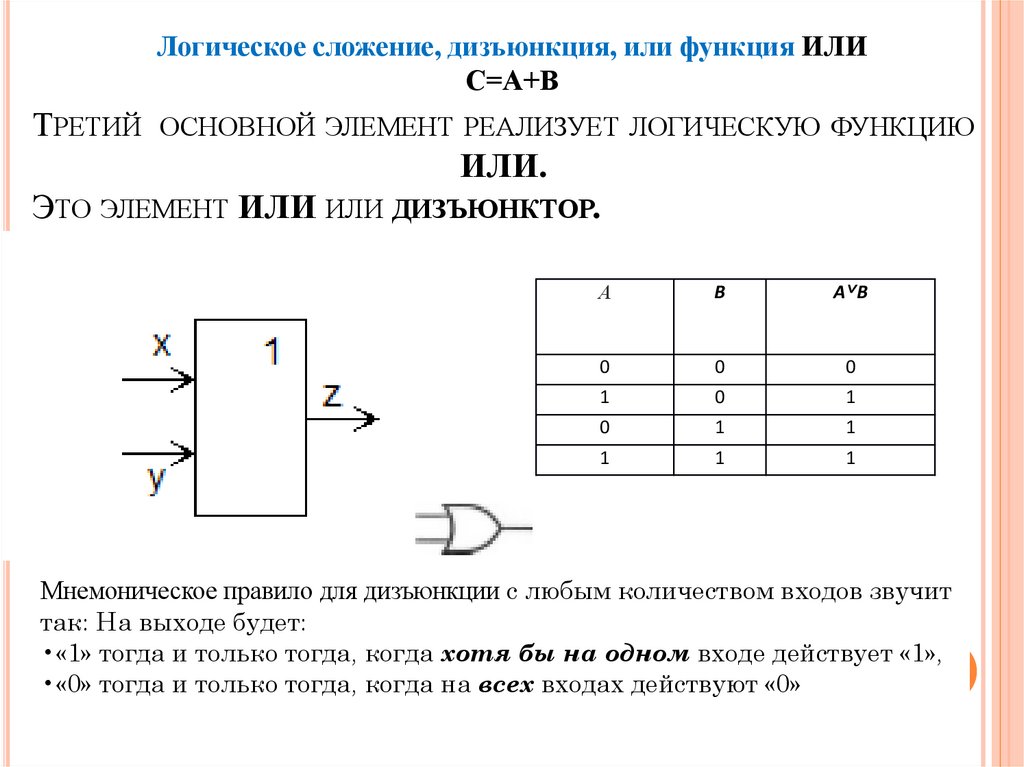

8. Третий основной элемент реализует логическую функцию ИЛИ. Это элемент ИЛИ или дизъюнктор.

Логическое сложение, дизъюнкция, или функция ИЛИС=А+В

ТРЕТИЙ

ОСНОВНОЙ ЭЛЕМЕНТ РЕАЛИЗУЕТ ЛОГИЧЕСКУЮ ФУНКЦИЮ

ИЛИ.

ЭТО ЭЛЕМЕНТ ИЛИ ИЛИ ДИЗЪЮНКТОР.

А

В

А˅В

0

0

0

1

0

1

0

1

1

1

1

1

Мнемоническое правило для дизъюнкции с любым количеством входов звучит

так: На выходе будет:

•«1» тогда и только тогда, когда хотя бы на одном входе действует «1»,

•«0» тогда и только тогда, когда на всех входах действуют «0»

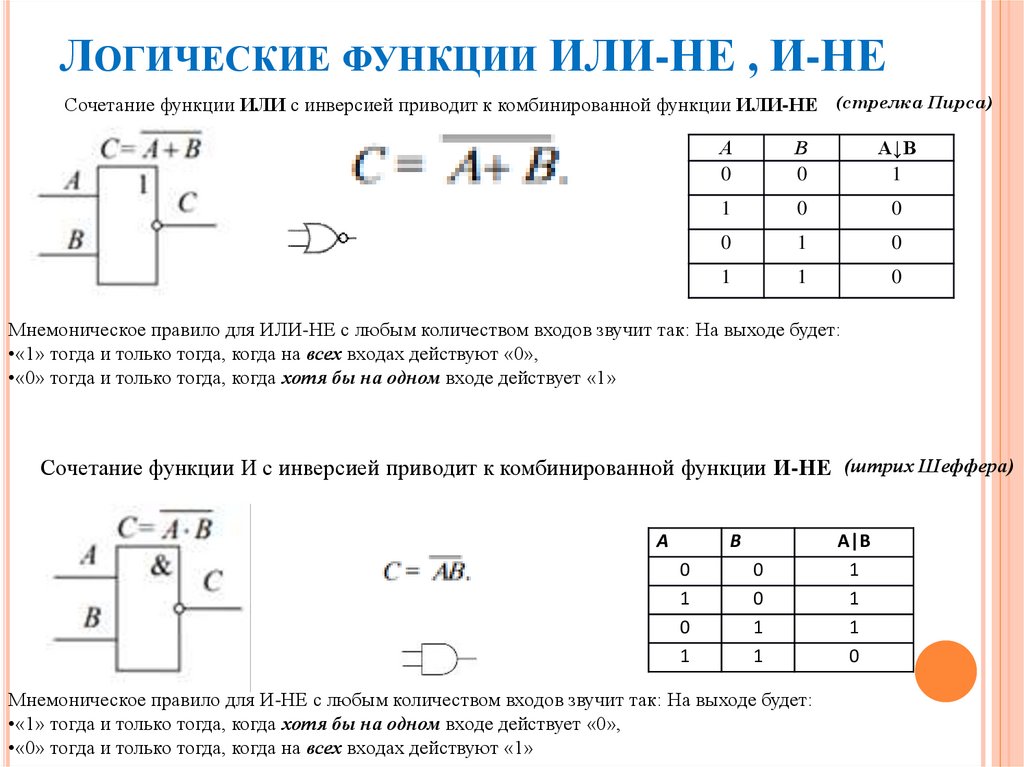

9. Логические функции ИЛИ-НЕ , И-НЕ

ЛОГИЧЕСКИЕ ФУНКЦИИ ИЛИ-НЕ , И-НЕСочетание функции ИЛИ с инверсией приводит к комбинированной функции ИЛИ-НЕ (стрелка Пирса)

А

0

В

0

А↓В

1

1

0

0

0

1

0

1

1

0

Мнемоническое правило для ИЛИ-HE с любым количеством входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на всех входах действуют «0»,

•«0» тогда и только тогда, когда хотя бы на одном входе действует «1»

Сочетание функции И с инверсией приводит к комбинированной функции И-НЕ (штрих Шеффера)

А

В

0

1

0

1

0

0

1

1

Мнемоническое правило для И-НЕ с любым количеством входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда хотя бы на одном входе действует «0»,

•«0» тогда и только тогда, когда на всех входах действуют «1»

А|В

1

1

1

0

10. Логические функции ИЛИ-НЕ , И-НЕ

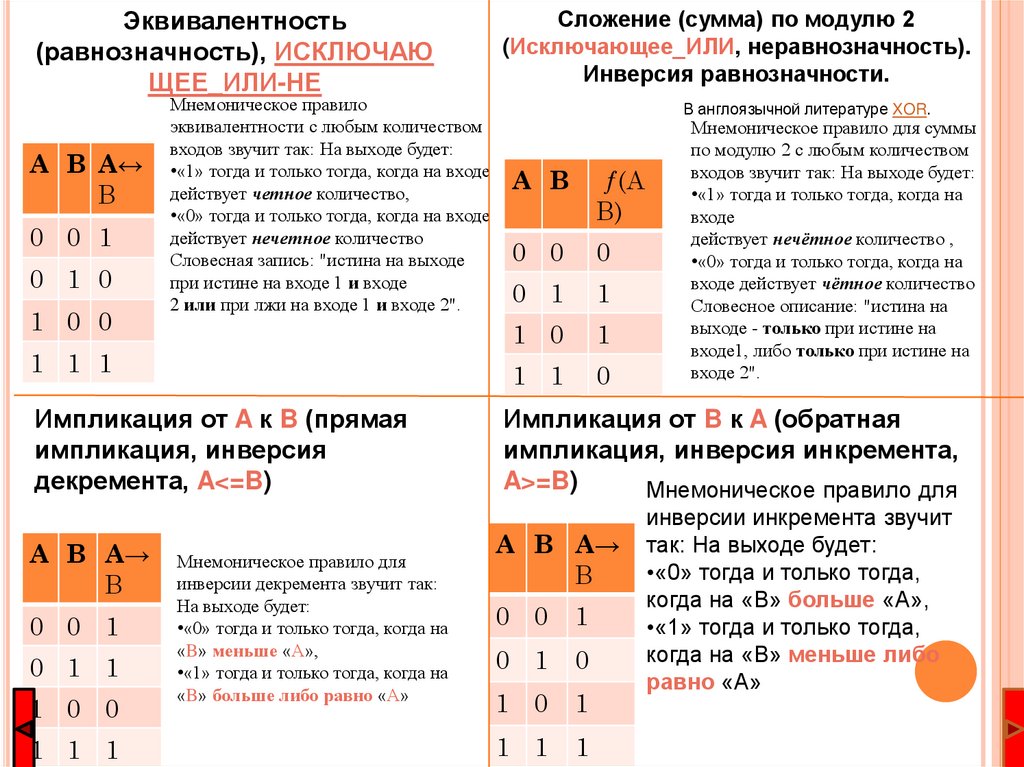

ЛОГИЧЕСКИЕ ФУНКЦИИ ИЛИ-НЕ , И-НЕЭквивалентность (равнозначность), ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

А

В

А↔В

0

0

1

1

0

0

0

1

0

1

1

1

Мнемоническое правило эквивалентности с любым количеством входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на входе действует четное количество,

•«0» тогда и только тогда, когда на входе действует нечетное количество

Словесная запись: "истина на выходе при истине на входе 1 и входе 2 или при лжи на входе

1 и входе 2".

Сложение (сумма) по модулю 2 (Исключающее ИЛИ, неравнозначность)

А

(инверсия равнозначности)

В

f(АВ)

0

0

0

1

0

1

0

1

1

1

1

0

Мнемоническое правило для суммы по модулю 2 с любым количеством входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на входе действует нечётное количество,

•«0» тогда и только тогда, когда на входе действует чётное количество

Словесное описание: «истина на выходе - только при истине на входе 1, либо только при истине на входе 2»

11.

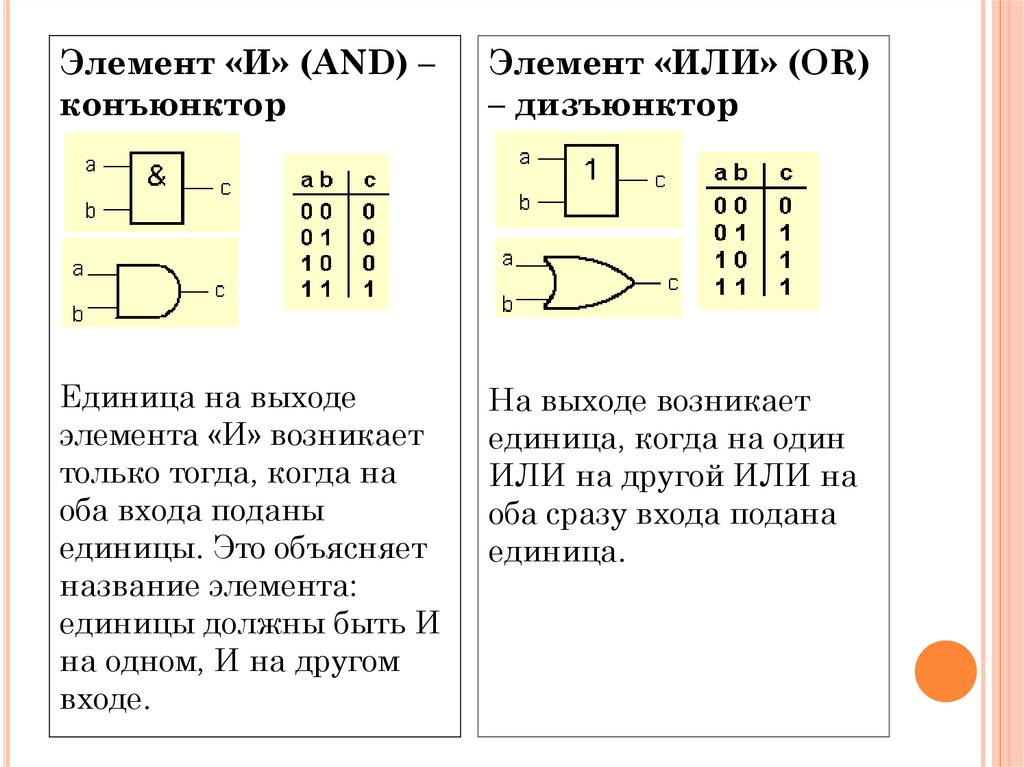

Элемент «И» (AND) –конъюнктор

Элемент «ИЛИ» (OR)

– дизъюнктор

Единица на выходе

элемента «И» возникает

только тогда, когда на

оба входа поданы

единицы. Это объясняет

название элемента:

единицы должны быть И

на одном, И на другом

входе.

На выходе возникает

единица, когда на один

ИЛИ на другой ИЛИ на

оба сразу входа подана

единица.

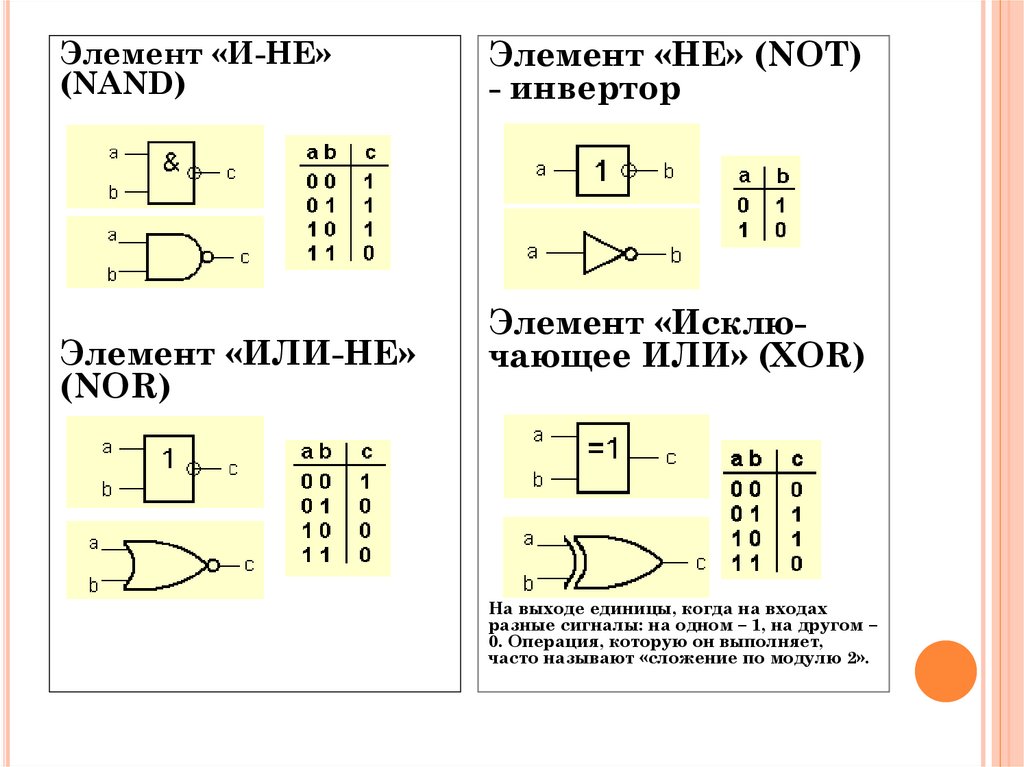

12.

Элемент «И-НЕ»(NAND)

Элемент «ИЛИ-НЕ»

(NOR)

Элемент «НЕ» (NOT)

- инвертор

Элемент «Исключающее ИЛИ» (XOR)

На выходе единицы, когда на входах

разные сигналы: на одном – 1, на другом –

0. Операция, которую он выполняет,

часто называют «сложение по модулю 2».

13.

Эквивалентность(равнозначность), ИСКЛЮЧАЮ

ЩЕЕ_ИЛИ-НЕ

A B A↔

B

0 0 1

0 1 0

1 0 0

Мнемоническое правило

эквивалентности с любым количеством

входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на входе

действует четное количество,

•«0» тогда и только тогда, когда на входе

действует нечетное количество

Словесная запись: "истина на выходе

при истине на входе 1 и входе

2 или при лжи на входе 1 и входе 2".

1 1 1

Импликация от A к B (прямая

импликация, инверсия

декремента, A<=B)

A B A→

B

0 0 1

0 1 1

1 0 0

1 1 1

Мнемоническое правило для

инверсии декремента звучит так:

На выходе будет:

•«0» тогда и только тогда, когда на

«B» меньше «А»,

•«1» тогда и только тогда, когда на

«B» больше либо равно «А»

Сложение (сумма) по модулю 2

(Исключающее_ИЛИ, неравнозначность).

Инверсия равнозначности.

В англоязычной литературе XOR.

A B

ƒ(A

B)

0 0

0

0 1

1

1 0

1

1 1

0

Мнемоническое правило для суммы

по модулю 2 с любым количеством

входов звучит так: На выходе будет:

•«1» тогда и только тогда, когда на

входе

действует нечётное количество ,

•«0» тогда и только тогда, когда на

входе действует чётное количество

Словесное описание: "истина на

выходе - только при истине на

входе1, либо только при истине на

входе 2".

Импликация от B к A (обратная

импликация, инверсия инкремента,

A>=B)

Мнемоническое правило для

A B A→

B

0 0

1

0 1

0

1 0

1

1 1

1

инверсии инкремента звучит

так: На выходе будет:

•«0» тогда и только тогда,

когда на «B» больше «А»,

•«1» тогда и только тогда,

когда на «B» меньше либо

равно «А»

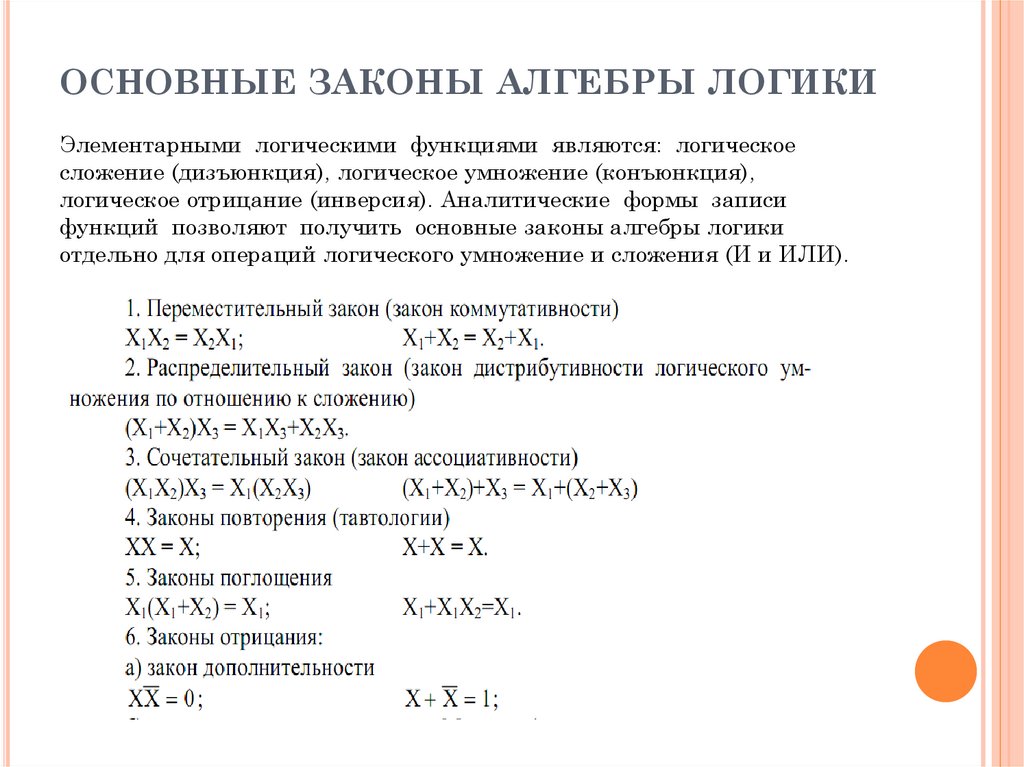

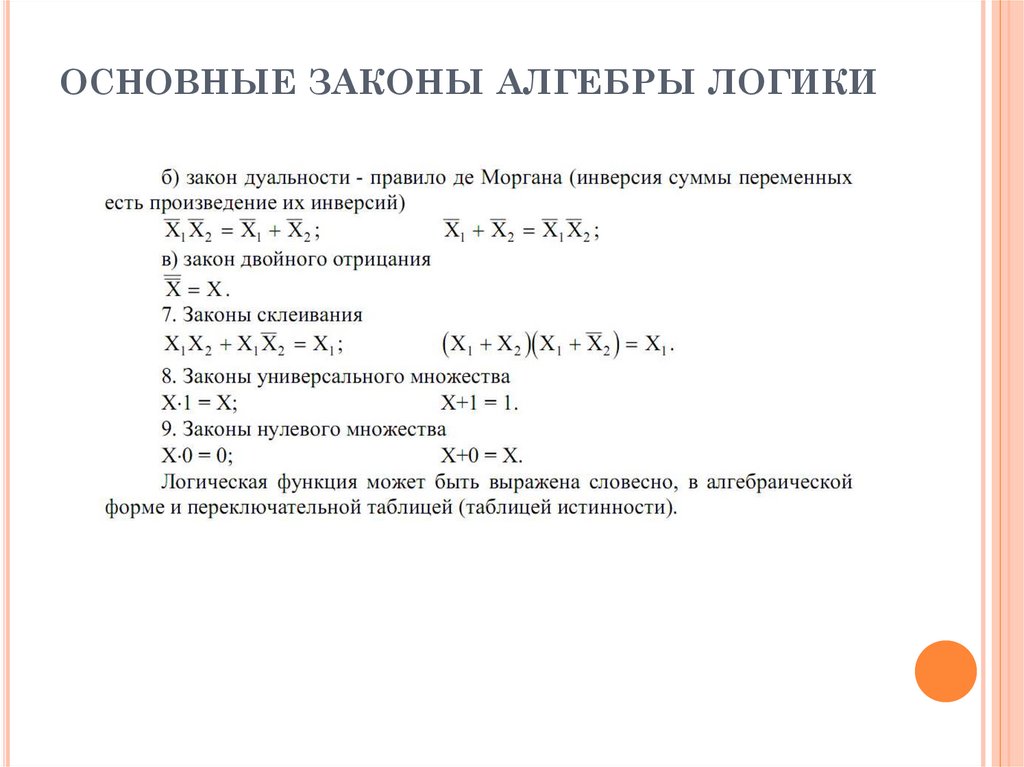

14. основные законы алгебры логики

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИЭлементарными логическими функциями являются: логическое

сложение (дизъюнкция), логическое умножение (конъюнкция),

логическое отрицание (инверсия). Аналитические формы записи

функций позволяют получить основные законы алгебры логики

отдельно для операций логического умножение и сложения (И и ИЛИ).

15. основные законы алгебры логики

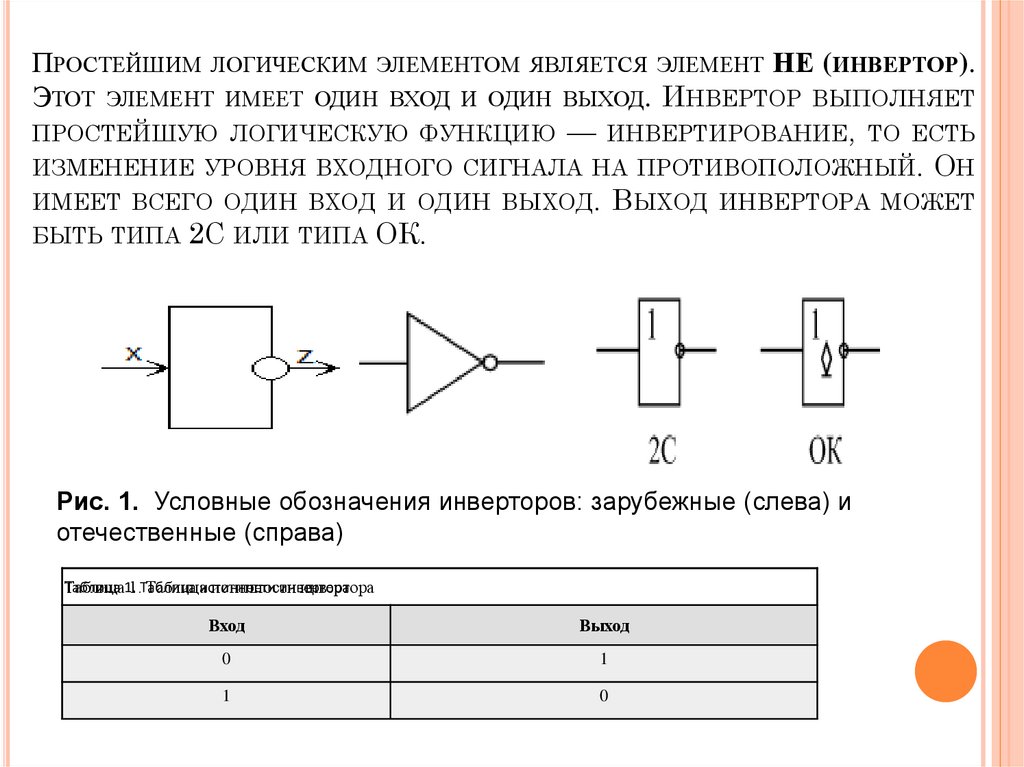

ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ16. Простейшим логическим элементом является элемент НЕ (инвертор). Этот элемент имеет один вход и один выход. Инвертор выполняет

ПРОСТЕЙШИМ ЛОГИЧЕСКИМ ЭЛЕМЕНТОМ ЯВЛЯЕТСЯ ЭЛЕМЕНТ НЕ (ИНВЕРТОР).ЭТОТ ЭЛЕМЕНТ ИМЕЕТ ОДИН ВХОД И ОДИН ВЫХОД. ИНВЕРТОР ВЫПОЛНЯЕТ

ПРОСТЕЙШУЮ ЛОГИЧЕСКУЮ ФУНКЦИЮ — ИНВЕРТИРОВАНИЕ, ТО ЕСТЬ

ИЗМЕНЕНИЕ УРОВНЯ ВХОДНОГО СИГНАЛА НА ПРОТИВОПОЛОЖНЫЙ. ОН

ИМЕЕТ ВСЕГО ОДИН ВХОД И ОДИН ВЫХОД. ВЫХОД ИНВЕРТОРА МОЖЕТ

БЫТЬ ТИПА 2С ИЛИ ТИПА ОК.

Рис. 1. Условные обозначения инверторов: зарубежные (слева) и

отечественные (справа)

Таблица 1.1.Таблица

инвертора

Таблица

Таблицаистинности

истинности

инвертора

Вход

Выход

Выход

0

1

1

0

17. Инверторы

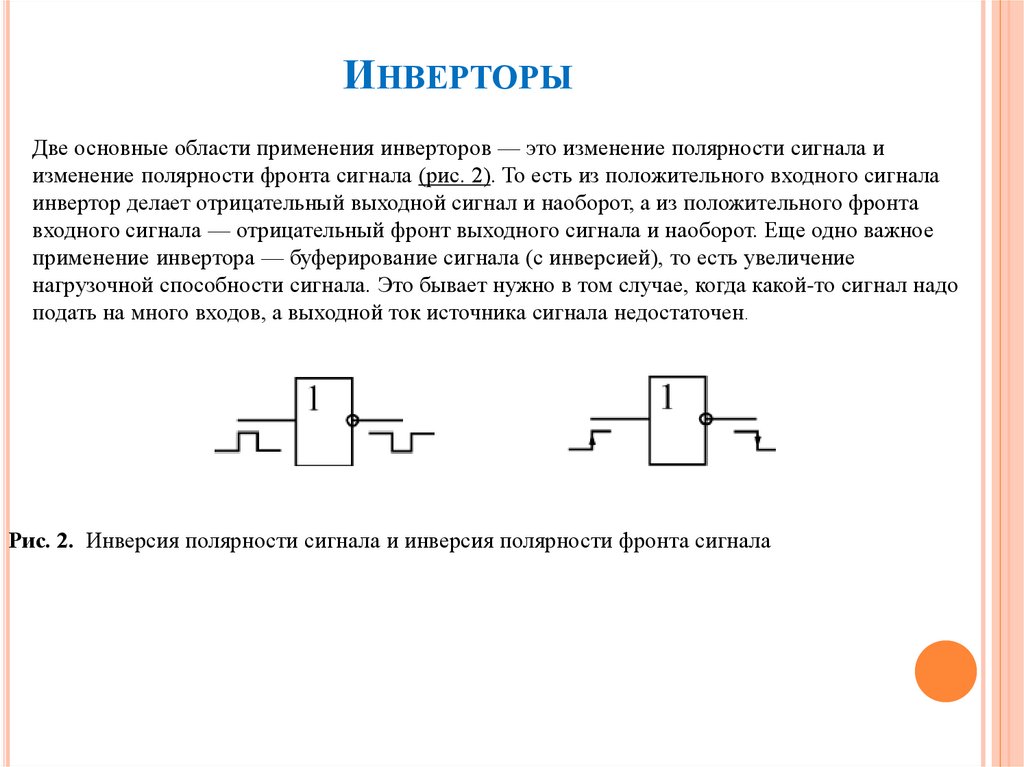

ИНВЕРТОРЫДве основные области применения инверторов — это изменение полярности сигнала и

изменение полярности фронта сигнала (рис. 2). То есть из положительного входного сигнала

инвертор делает отрицательный выходной сигнал и наоборот, а из положительного фронта

входного сигнала — отрицательный фронт выходного сигнала и наоборот. Еще одно важное

применение инвертора — буферирование сигнала (с инверсией), то есть увеличение

нагрузочной способности сигнала. Это бывает нужно в том случае, когда какой-то сигнал надо

подать на много входов, а выходной ток источника сигнала недостаточен.

Рис. 2. Инверсия полярности сигнала и инверсия полярности фронта сигнала

18.

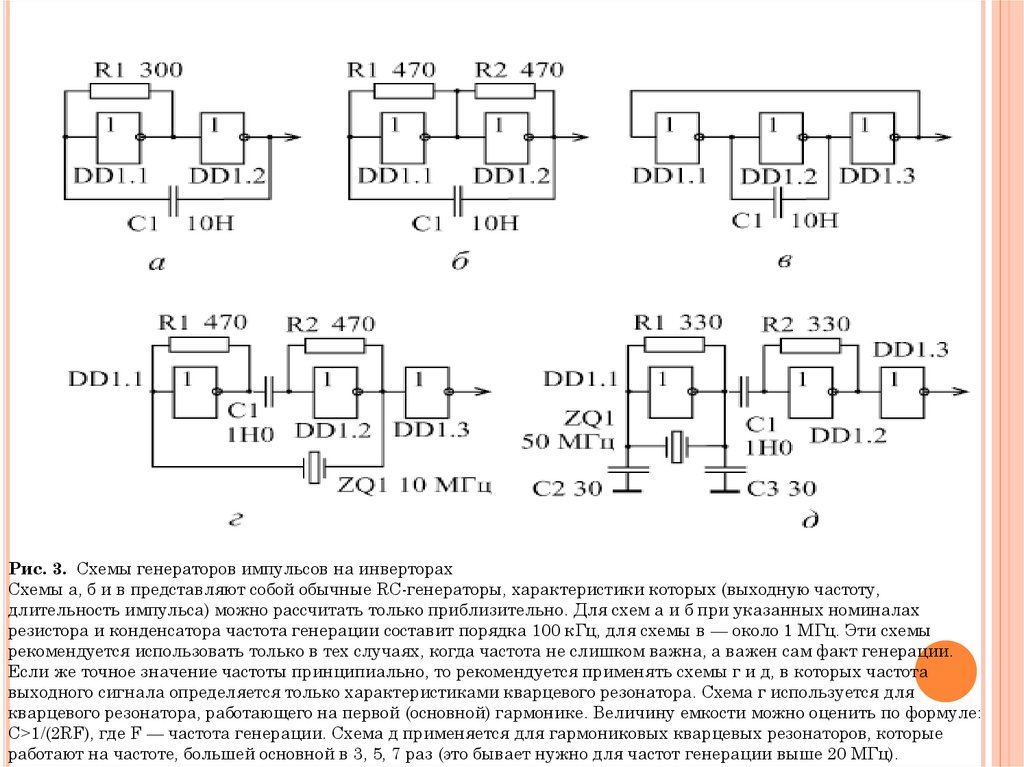

Рис. 3. Схемы генераторов импульсов на инверторахСхемы а, б и в представляют собой обычные RC-генераторы, характеристики которых (выходную частоту,

длительность импульса) можно рассчитать только приблизительно. Для схем а и б при указанных номиналах

резистора и конденсатора частота генерации составит порядка 100 кГц, для схемы в — около 1 МГц. Эти схемы

рекомендуется использовать только в тех случаях, когда частота не слишком важна, а важен сам факт генерации.

Если же точное значение частоты принципиально, то рекомендуется применять схемы г и д, в которых частота

выходного сигнала определяется только характеристиками кварцевого резонатора. Схема г используется для

кварцевого резонатора, работающего на первой (основной) гармонике. Величину емкости можно оценить по формуле:

C>1/(2RF), где F — частота генерации. Схема д применяется для гармониковых кварцевых резонаторов, которые

работают на частоте, большей основной в 3, 5, 7 раз (это бывает нужно для частот генерации выше 20 МГц).

19. Инверторы

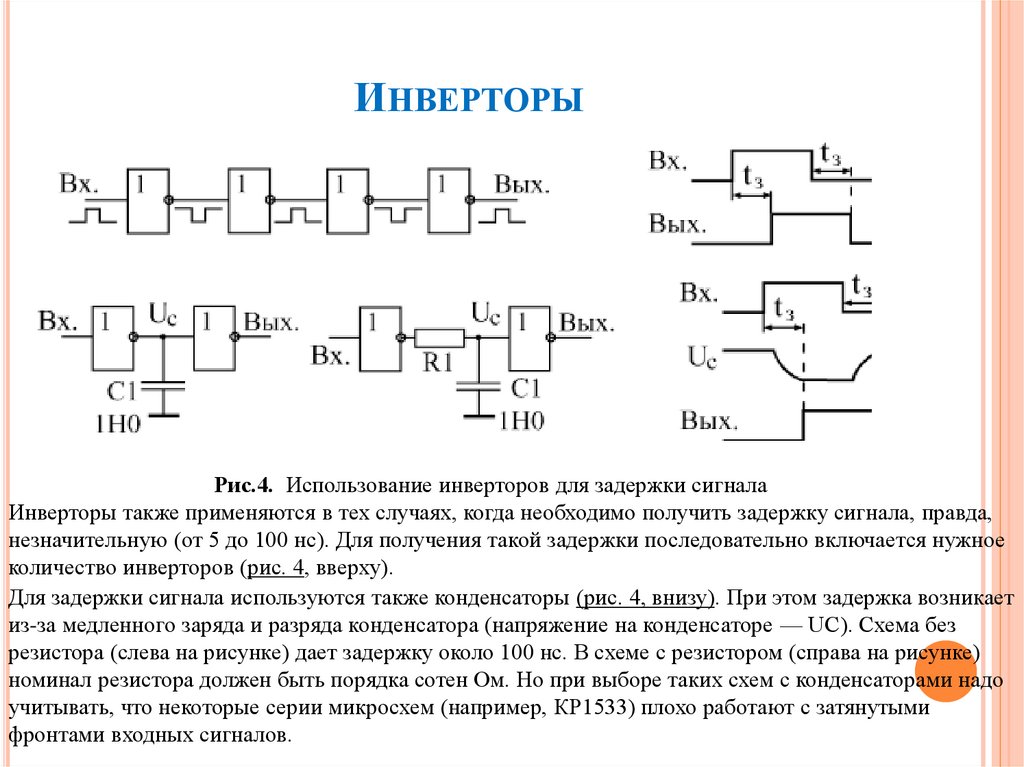

ИНВЕРТОРЫРис.4. Использование инверторов для задержки сигнала

Инверторы также применяются в тех случаях, когда необходимо получить задержку сигнала, правда,

незначительную (от 5 до 100 нс). Для получения такой задержки последовательно включается нужное

количество инверторов (рис. 4, вверху).

Для задержки сигнала используются также конденсаторы (рис. 4, внизу). При этом задержка возникает

из-за медленного заряда и разряда конденсатора (напряжение на конденсаторе — UC). Схема без

резистора (слева на рисунке) дает задержку около 100 нс. В схеме с резистором (справа на рисунке)

номинал резистора должен быть порядка сотен Ом. Но при выборе таких схем с конденсаторами надо

учитывать, что некоторые серии микросхем (например, КР1533) плохо работают с затянутыми

фронтами входных сигналов.

20. Инверторы

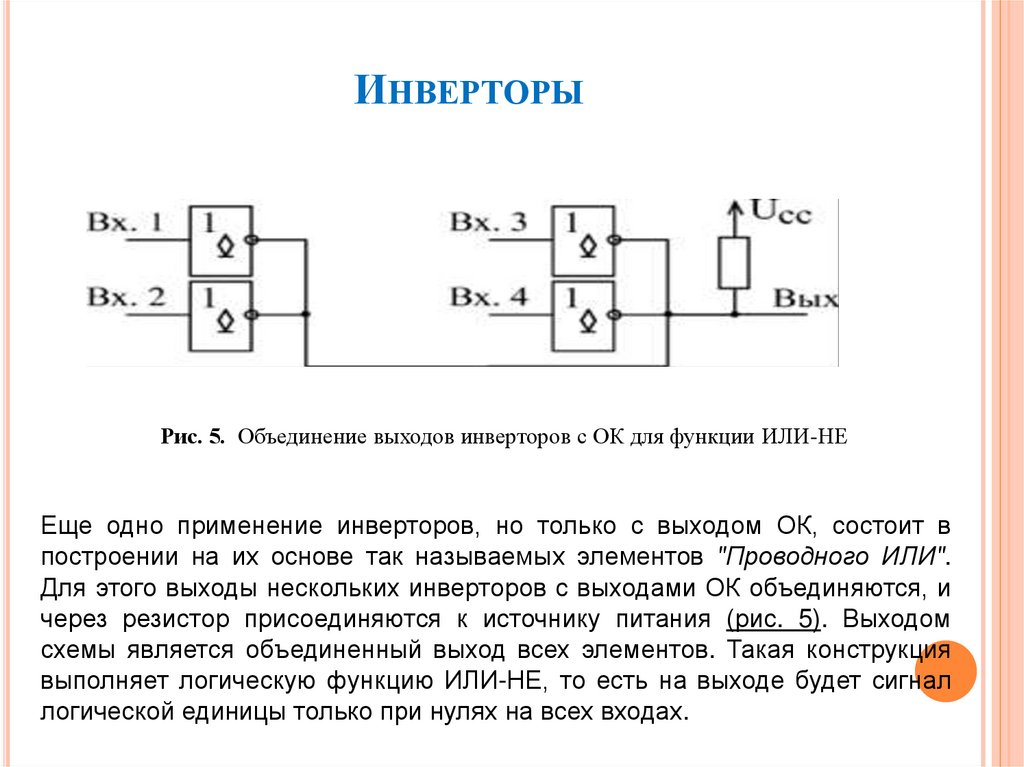

ИНВЕРТОРЫРис. 5. Объединение выходов инверторов с ОК для функции ИЛИ-НЕ

Еще одно применение инверторов, но только с выходом ОК, состоит в

построении на их основе так называемых элементов "Проводного ИЛИ".

Для этого выходы нескольких инверторов с выходами ОК объединяются, и

через резистор присоединяются к источнику питания (рис. 5). Выходом

схемы является объединенный выход всех элементов. Такая конструкция

выполняет логическую функцию ИЛИ-НЕ, то есть на выходе будет сигнал

логической единицы только при нулях на всех входах.

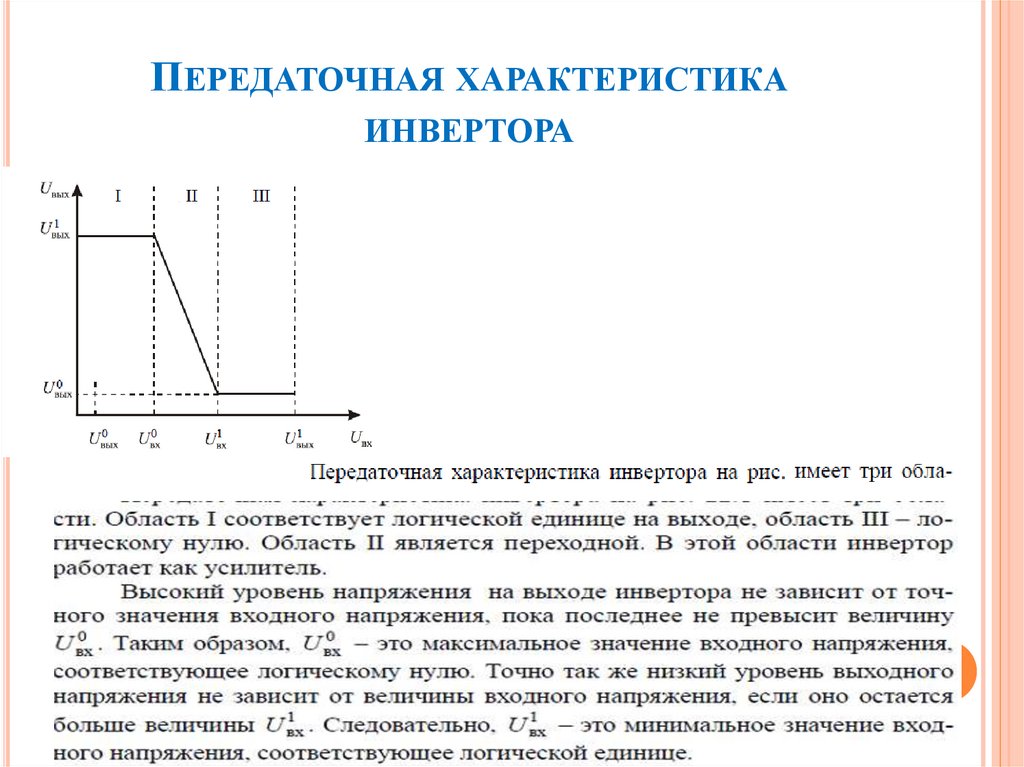

21. Передаточная характеристика инвертора

ПЕРЕДАТОЧНАЯ ХАРАКТЕРИСТИКАИНВЕРТОРА

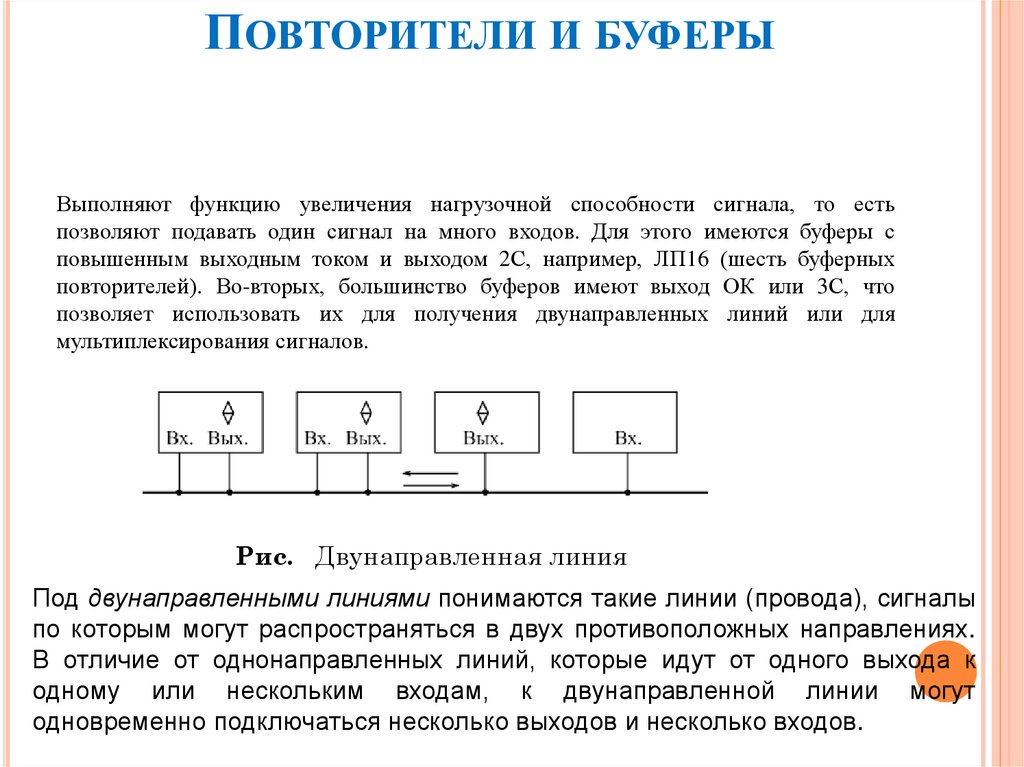

22. Повторители и буферы

ПОВТОРИТЕЛИ И БУФЕРЫВыполняют функцию увеличения нагрузочной способности сигнала, то есть

позволяют подавать один сигнал на много входов. Для этого имеются буферы с

повышенным выходным током и выходом 2С, например, ЛП16 (шесть буферных

повторителей). Во-вторых, большинство буферов имеют выход ОК или 3С, что

позволяет использовать их для получения двунаправленных линий или для

мультиплексирования сигналов.

Рис. Двунаправленная линия

Под двунаправленными линиями понимаются такие линии (провода), сигналы

по которым могут распространяться в двух противоположных направлениях.

В отличие от однонаправленных линий, которые идут от одного выхода к

одному или нескольким входам, к двунаправленной линии могут

одновременно подключаться несколько выходов и несколько входов.

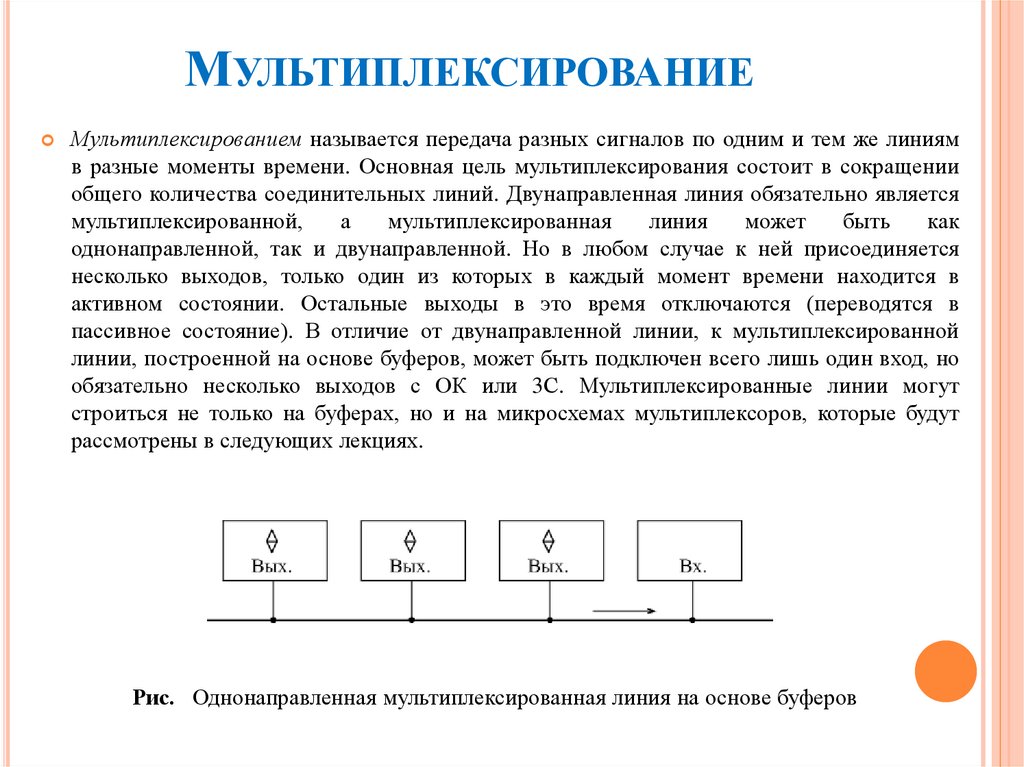

23. Мультиплексирование

МУЛЬТИПЛЕКСИРОВАНИЕМультиплексированием называется передача разных сигналов по одним и тем же линиям

в разные моменты времени. Основная цель мультиплексирования состоит в сокращении

общего количества соединительных линий. Двунаправленная линия обязательно является

мультиплексированной,

а

мультиплексированная

линия

может

быть

как

однонаправленной, так и двунаправленной. Но в любом случае к ней присоединяется

несколько выходов, только один из которых в каждый момент времени находится в

активном состоянии. Остальные выходы в это время отключаются (переводятся в

пассивное состояние). В отличие от двунаправленной линии, к мультиплексированной

линии, построенной на основе буферов, может быть подключен всего лишь один вход, но

обязательно несколько выходов с ОК или 3С. Мультиплексированные линии могут

строиться не только на буферах, но и на микросхемах мультиплексоров, которые будут

рассмотрены в следующих лекциях.

Рис. Однонаправленная мультиплексированная линия на основе буферов

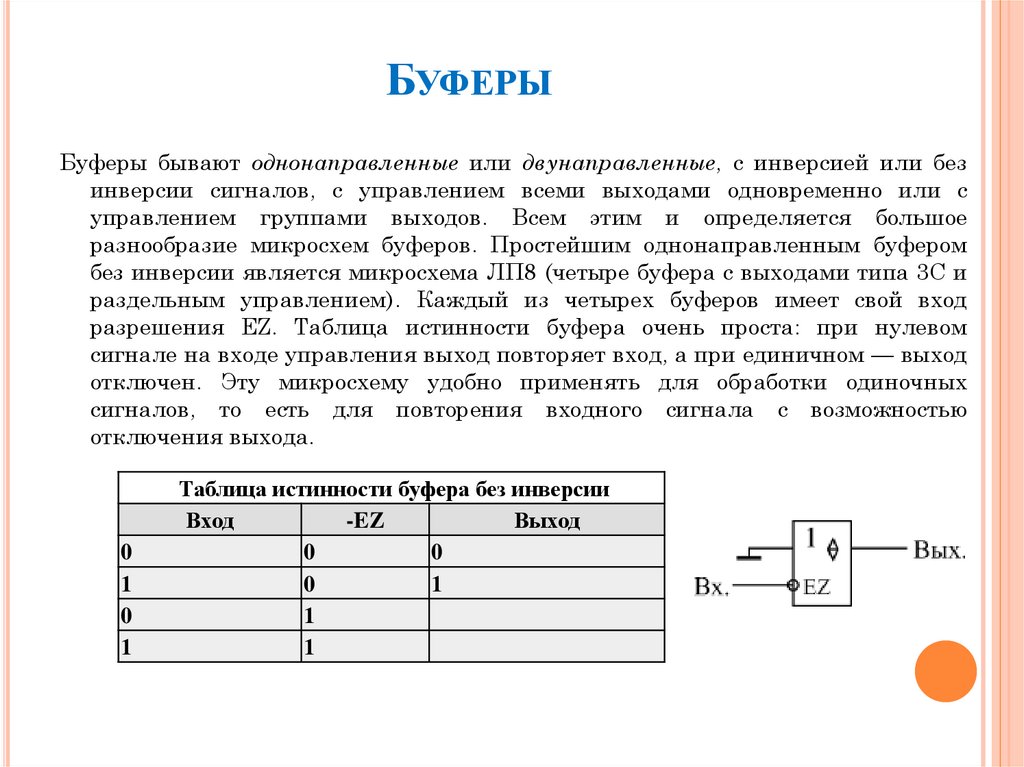

24. Буферы

БУФЕРЫБуферы бывают однонаправленные или двунаправленные, с инверсией или без

инверсии сигналов, с управлением всеми выходами одновременно или с

управлением группами выходов. Всем этим и определяется большое

разнообразие микросхем буферов. Простейшим однонаправленным буфером

без инверсии является микросхема ЛП8 (четыре буфера с выходами типа 3С и

раздельным управлением). Каждый из четырех буферов имеет свой вход

разрешения EZ. Таблица истинности буфера очень проста: при нулевом

сигнале на входе управления выход повторяет вход, а при единичном — выход

отключен. Эту микросхему удобно применять для обработки одиночных

сигналов, то есть для повторения входного сигнала с возможностью

отключения выхода.

0

1

0

1

Таблица истинности буфера без инверсии

Вход

-EZ

Выход

0

0

0

1

1

1

25.

26. Физические реализации

ФИЗИЧЕСКИЕ РЕАЛИЗАЦИИРеализация логических элементов возможна при помощи

устройств, использующих самые разнообразные физические

принципы:

механические,

гидравлические,

пневматические,

электромагнитные,

электромеханические,

электронные.

Физические реализации одной и той же логической функции, а

также обозначения для истины и лжи, в разных системах

электронных и неэлектронных элементов отличаются друг от

друга.

27. Физические реализации

ФИЗИЧЕСКИЕ РЕАЛИЗАЦИИэлектромагнитные

механические

пневматические

электронные

электромеханические

гидравлические

28. Комбинационные логические устройства

КОМБИНАЦИОННЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВАКомбинационными называются такие логические устройства, выходные

сигналы которых однозначно определяются входными сигналами:

Сумматор

Полусумматор

Шифратор

Дешифратор

Мультиплексор

Демультиплексор

Цифровой компаратор

Мажоритарный элемент

Постоянное запоминающее устройство (ПЗУ) как универсальная

комбинационная логическая схема

Все они выполняют двоичные, троичные или n-ичные логические функции

29. Классификация электронных транзисторных физических реализаций логических элементов

КЛАССИФИКАЦИЯ ЭЛЕКТРОННЫХ ТРАНЗИСТОРНЫХФИЗИЧЕСКИХ РЕАЛИЗАЦИЙ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Логические элементы подразделяются и по

типу использованных в них электронных

элементов. Наибольшее применение в

настоящее время находят следующие

логические элементы:

РТЛ (резисторно-транзисторная логика)

ДТЛ (диодно-транзисторная логика)

ТТЛ (транзисторно-транзисторная логика)

ЭСЛ (эмитерно-связанная логика)

И2Л (интегрально-инжекционная логика)

30. ДТЛ

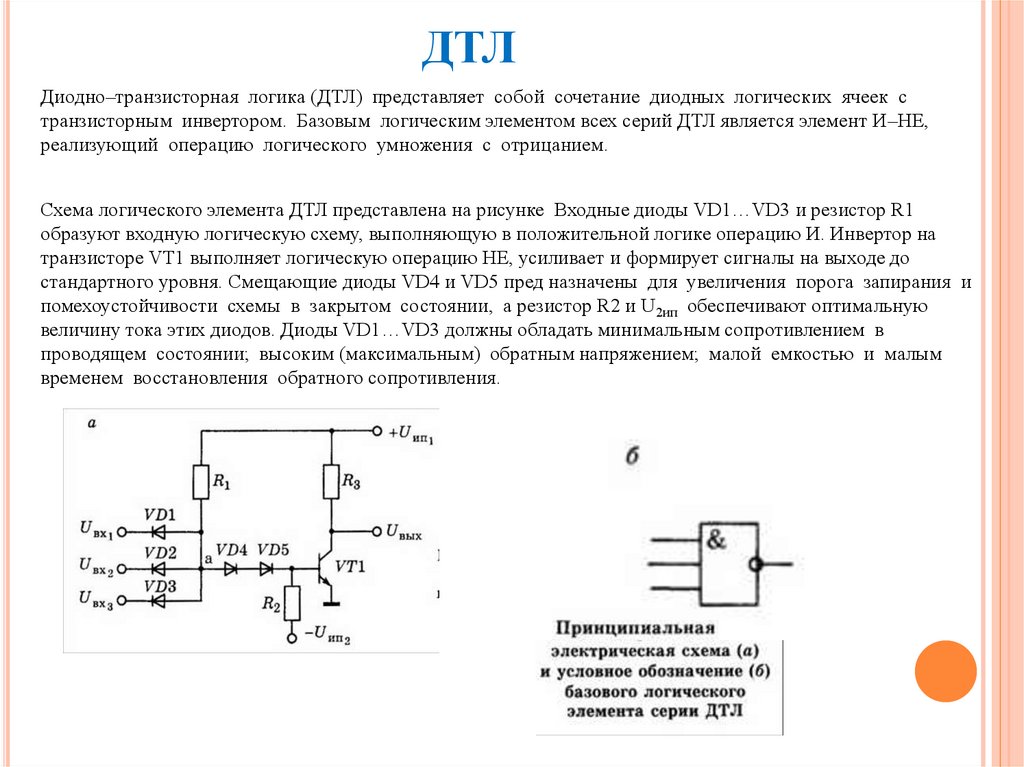

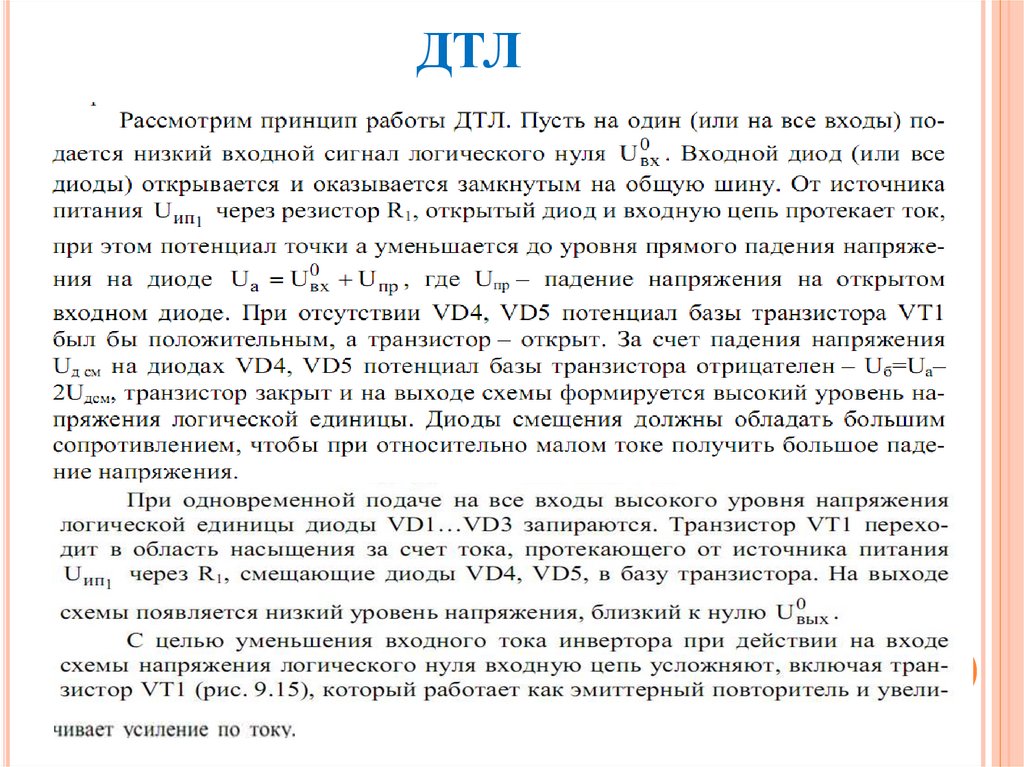

Диодно–транзисторная логика (ДТЛ) представляет собой сочетание диодных логических ячеек странзисторным инвертором. Базовым логическим элементом всех серий ДТЛ является элемент И–НЕ,

реализующий операцию логического умножения с отрицанием.

Схема логического элемента ДТЛ представлена на рисунке Входные диоды VD1…VD3 и резистор R1

образуют входную логическую схему, выполняющую в положительной логике операцию И. Инвертор на

транзисторе VТ1 выполняет логическую операцию НЕ, усиливает и формирует сигналы на выходе до

стандартного уровня. Смещающие диоды VD4 и VD5 пред назначены для увеличения порога запирания и

помехоустойчивости схемы в закрытом состоянии, а резистор R2 и U2ип обеспечивают оптимальную

величину тока этих диодов. Диоды VD1…VD3 должны обладать минимальным сопротивлением в

проводящем состоянии; высоким (максимальным) обратным напряжением; малой емкостью и малым

временем восстановления обратного сопротивления.

31. ДТЛ

32. ДТЛ. Принципиальная схема с усовершенствованной входной цепью

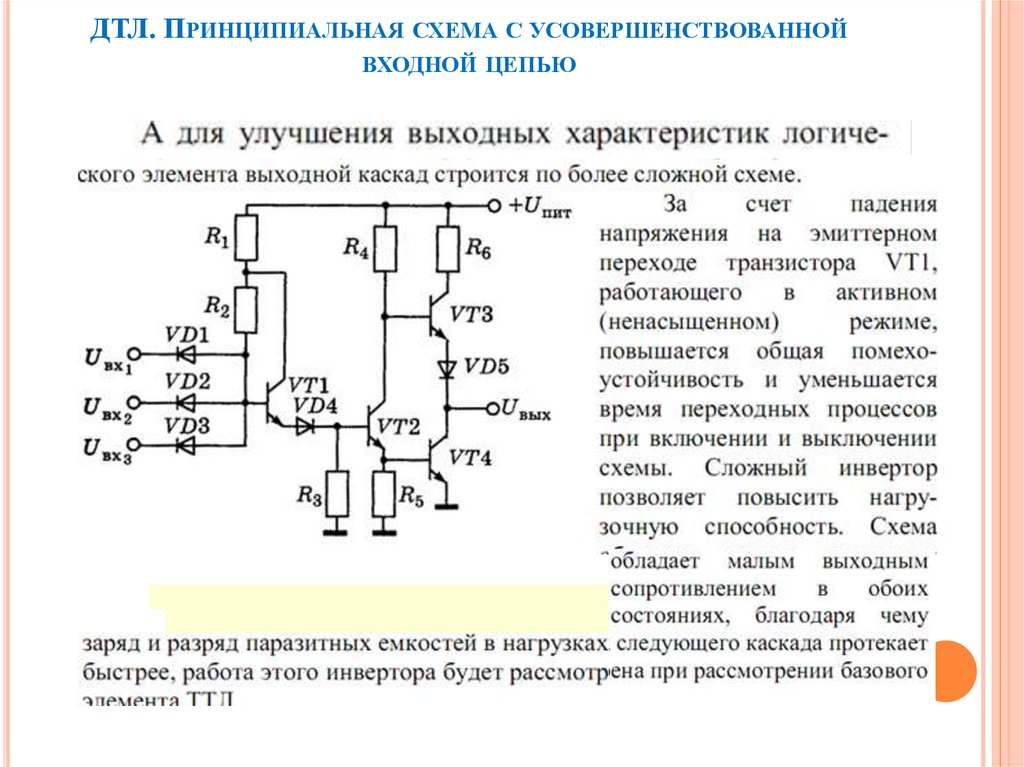

ДТЛ. ПРИНЦИПИАЛЬНАЯ СХЕМА С УСОВЕРШЕНСТВОВАННОЙВХОДНОЙ ЦЕПЬЮ

33. ТТЛ

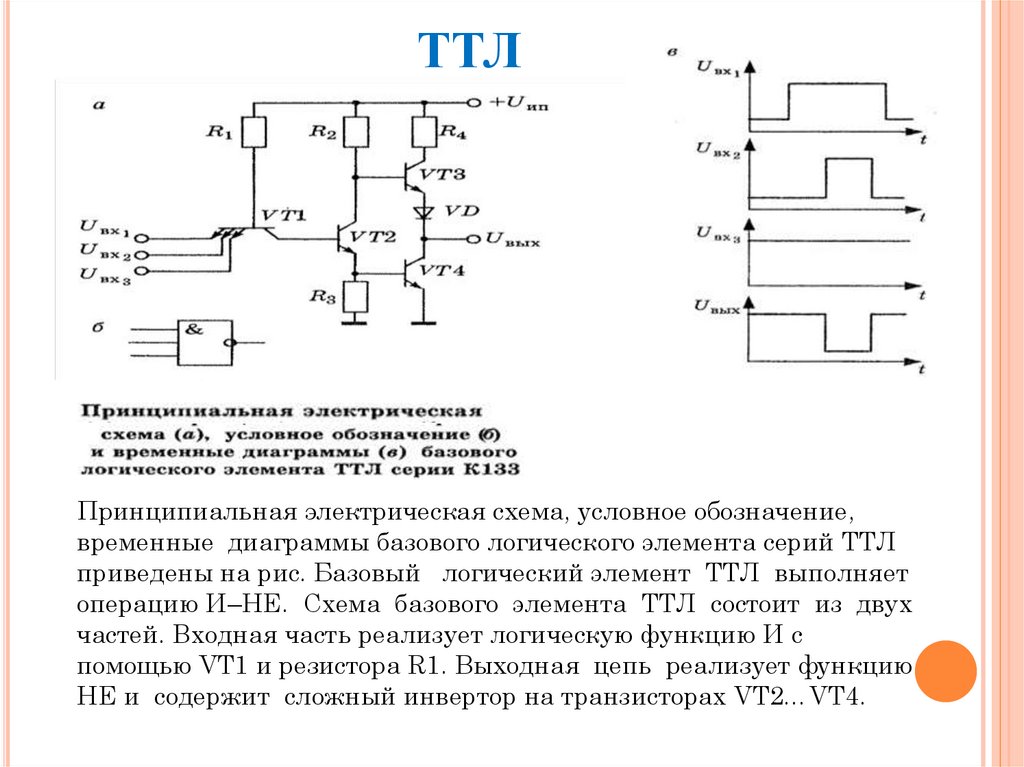

Принципиальная электрическая схема, условное обозначение,временные диаграммы базового логического элемента серий ТТЛ

приведены на рис. Базовый логический элемент ТТЛ выполняет

операцию И–НЕ. Схема базового элемента ТТЛ состоит из двух

частей. Входная часть реализует логическую функцию И с

помощью VТ1 и резистора R1. Выходная цепь реализует функцию

НЕ и содержит сложный инвертор на транзисторах VТ2…VТ4.

34. ТТЛ

Базовые элементы различных серий ТТЛ различаются толькоинверторами, которые должны улучшать переходные характеристики,

повышать помехоустойчивость и нагрузочную способность,

потреблять небольшую мощность.

Для уменьшения входных токов транзистор VТ1 должен обладать

малым коэффициентом передачи тока базы в инверсном режиме h i э 21

≈0,005…0,05 .

Логические элементы со сложным инвертором потребляют большую

мощность, занимают большую площадь кристалла, поэтому на их

основе изготавливаются цифровые микросхемы малой и средней

степени интеграции.

Быстродействие логических элементов различных серий ТТЛ можно

повысить двумя путями:

– уменьшая сопротивление резисторов и паразитные емкости;

– обеспечивая работу транзисторов в активном, т.е. ненасыщенном

режиме, при котором отсутствует накопление и рассасывание носителей

в базах транзисторов. Оба эти способа повышения быстродействия

нашли практическое применение.

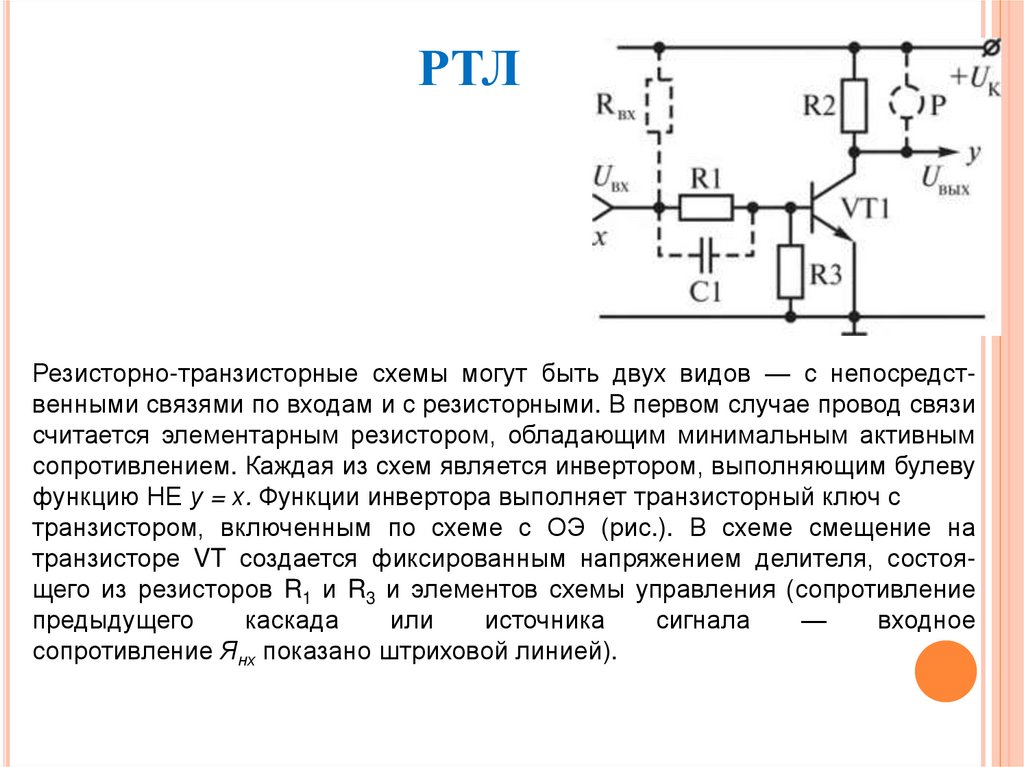

35. РТЛ

Резисторно-транзисторные схемы могут быть двух видов — с непосредственными связями по входам и с резисторными. В первом случае провод связисчитается элементарным резистором, обладающим минимальным активным

сопротивлением. Каждая из схем является инвертором, выполняющим булеву

функцию НЕ у = х. Функции инвертора выполняет транзисторный ключ с

транзистором, включенным по схеме с ОЭ (рис.). В схеме смещение на

транзисторе VT создается фиксированным напряжением делителя, состоящего из резисторов R1 и R3 и элементов схемы управления (сопротивление

предыдущего

каскада

или

источника

сигнала

—

входное

сопротивление Янх показано штриховой линией).

36.

При подаче на вход схемы сигнала низкого уровня (для положительной логики это отрицательныйпотенциал — лог.О) транзисторный ключ закрыт, так как отсутствует необходимое напряжение

прямого смещения эмиттерного перехода, равное (7Эз < 0,6 В. При этом на выходе схемы действует

положительный потенциал (лог.1). При подаче на вход сигнала лог.1 (сигнал высокого уровня

(положительный потенциал)) на резисторах делителя создается падение напряжения, которое

действует на эмиттерный переход как прямое смещение (f/R3) и как обратное смещение на

коллекторный переход (?/r3 Rbx). Транзистор открывается и на выходе транзисторного ключа

появляется отрицательный потенциал (лог.О), т.е. выполняется логическая операция НЕ. Это

происходит, когда напряжение на входе х (UBX)достигает порогового напряжения (t/^op). Транзистор

открывается

при иЭз > 0,6 В. Поэтому для создания этого условия необходимо подобрать резисторы делителя

R1 и R3 так, чтобы выполнялось равенство

37.

Таким образом, транзисторный ключ является схемотехническим решением логического элемента НЕ.Недостатком схемы является уменьшение входного сигнала (?/вх) за счет падения напряжения на

резисторе R1, что потребует увеличения амплитуды входного сигнала. Если не увеличивать амплитуду

входного сигнала, т.е. не компенсировать потери на R1, то снизится быстродействие схемы из-за

уменьшения амплитуды сигнала, действующего на транзистор. Для повышения амплитуды этого

сигнала резистор связи R1 шунтируют ускоряющим (форсирующим) конденсатором С1.

Инверторы в схемотехническом решении РТЛ могут выполняться с открытым коллектором, т.е. без

конструктивного нагрузочного резистора в коллекторной цепи (R2), когда коллектор не подключен в

схеме и является свободным выходом (например, в схеме на рис. 14.9 не включать резистор R2).

Открытый коллектор позволяет включать в качестве конструктивной нагрузки между коллектором и

источником питания ?/к лампочку накаливания, реле и другие нагрузки (например, в схеме на рис. реле Р

показано штрихами). В таком схемном решении можно использовать более высоковольтный

источник UK для коллекторной цепи (при высоковольтном транзисторе), получая схемы с более высоким

выходным током (/ВЬ1Х) и объединять выходы отдельных схем, работающих на общую нагрузку.

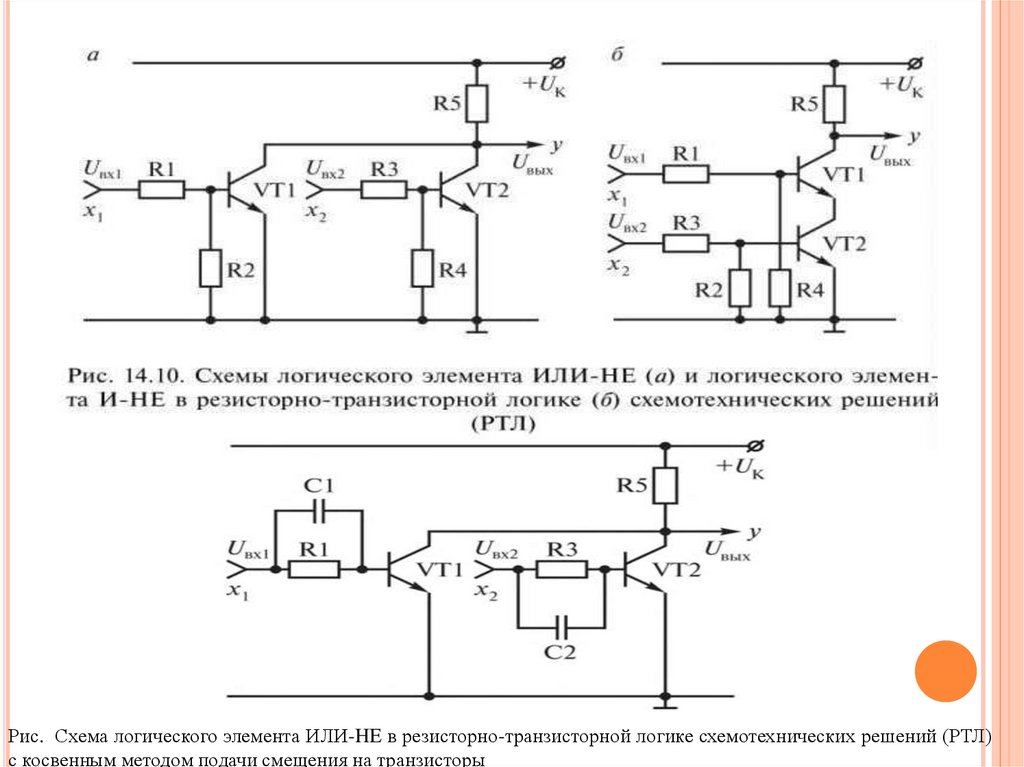

Для реализации схемотехнических решений базисных функций И-НЕ и ИЛ И-НЕ применяют

соответственно последовательное и параллельное соединение транзисторных ключей (инверторов)

между собой, работающих на общую нагрузку (рис.).

На рис., а, показана схема параллельно соединенных инверторов. В этой схеме на выходе формируется

высокий уровень (лог. 1), если одновременно на все входы подается сигнал низкого уровня (лог.О),

закрывающий транзисторы. В результате на выходе формируется функция у = х]лх2 — И-НЕ на сигналах

низкого уровня. На сигналах высокого уровня выполняется логическая функция у = Xj vx2 — ИЛИ-HE.

Действительно, если на один из входов (например, х,) подать сигнал высокого уровня, то откроется

транзистор VT1 и за счет протекающего выходного тока через R5 на выходе получим низкий уровень

сигнала (лог.О). Данное схемотехническое решение в ДРЛ применяется в логическом элементе ИЛИ-НЕ.

38.

Рис. Схема логического элемента ИЛИ-HE в резисторно-транзисторной логике схемотехнических решений (РТЛ)с косвенным методом подачи смещения на транзисторы

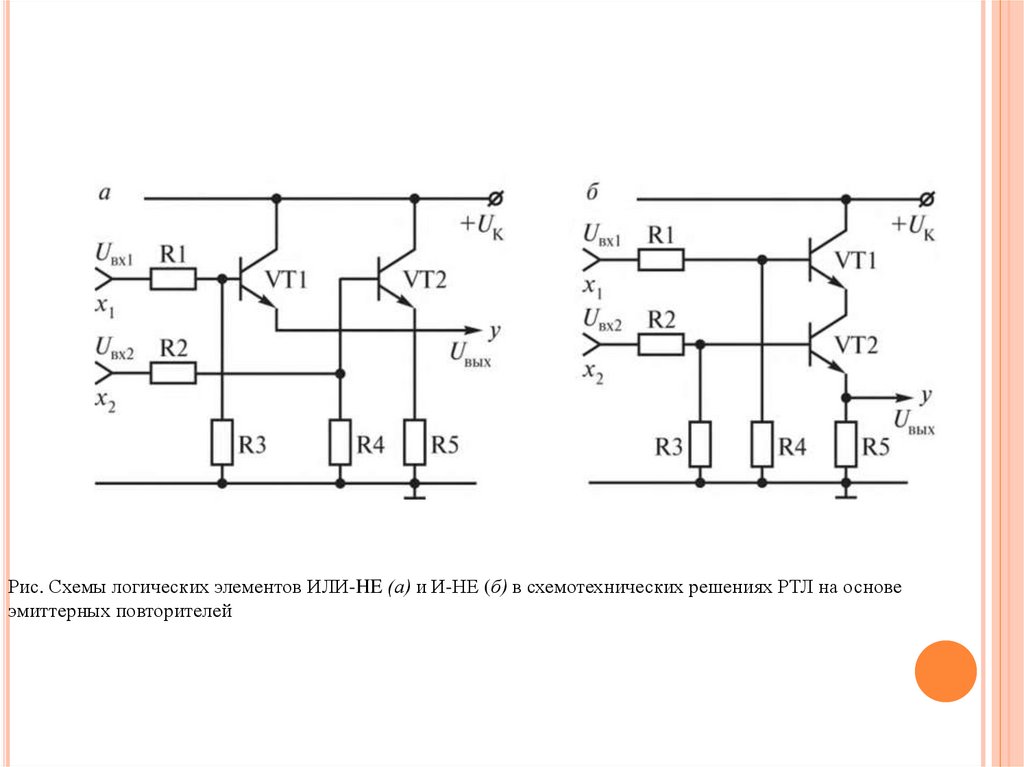

39.

Рис. Схемы логических элементов ИЛИ-HE (а) и И-НЕ (б) в схемотехнических решениях РТЛ на основеэмиттерных повторителей

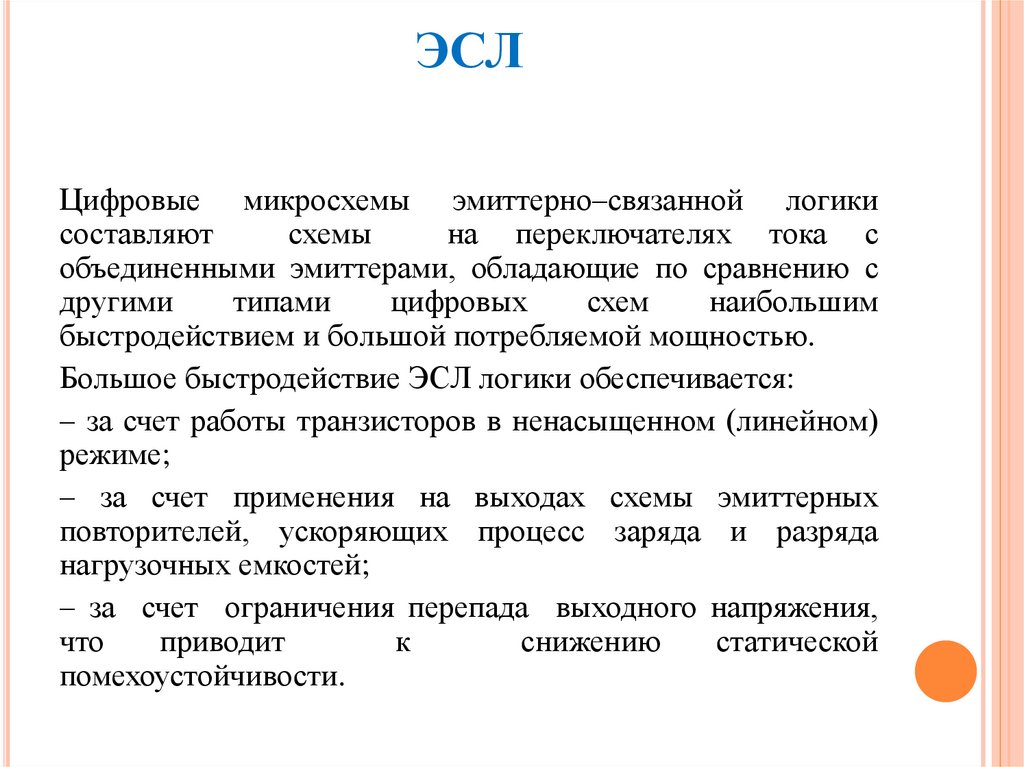

40. ЭСЛ

Цифровые микросхемы эмиттерно–связанной логикисоставляют

схемы

на переключателях тока с

объединенными эмиттерами, обладающие по сравнению с

другими

типами

цифровых

схем

наибольшим

быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ логики обеспечивается:

– за счет работы транзисторов в ненасыщенном (линейном)

режиме;

– за счет применения на выходах схемы эмиттерных

повторителей, ускоряющих процесс заряда и разряда

нагрузочных емкостей;

– за счет ограничения перепада выходного напряжения,

что

приводит

к

снижению

статической

помехоустойчивости.

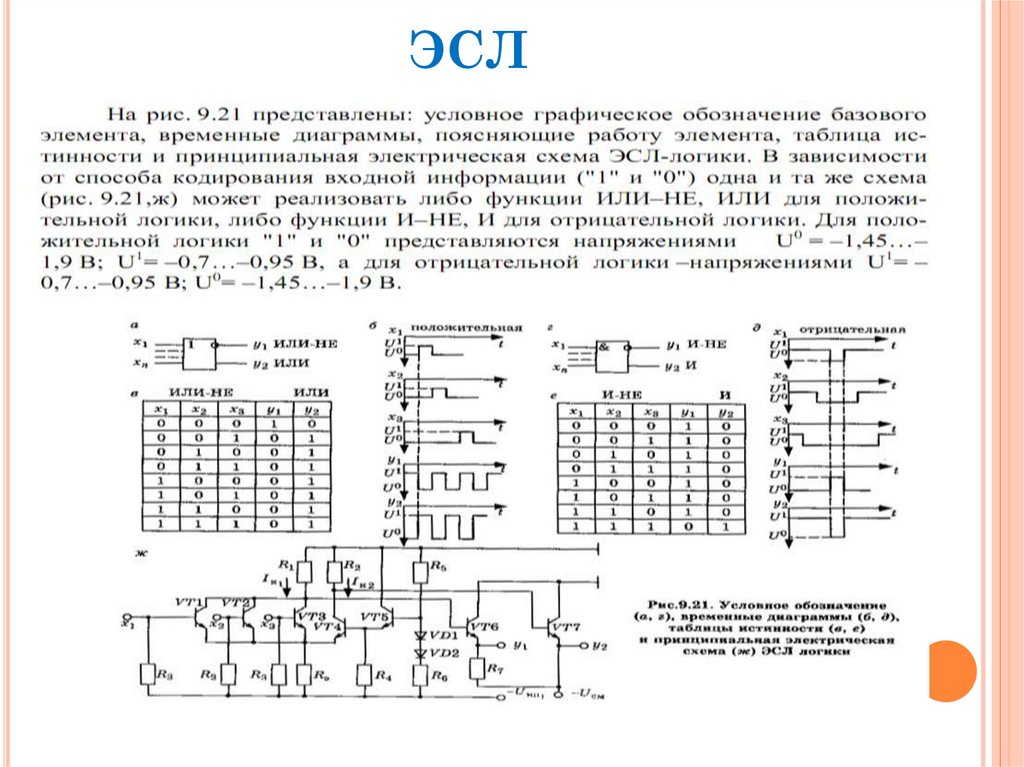

41. ЭСЛ

42. ЭСЛ

Логический элемент состоит из трех частей: токового переключателя(ТП), эмиттерных повторителей (ЭП), источника опорного напряжения

(ИОН).

Рассмотрим принцип работы базового логического элемента для

положительной логики. Если на все логические входы подается

напряжение низкого уровня, соответствующее логическому нулю, то

транзисторы VТ1–VТ3 закрываются, а транзистор VТ 4 открывается, так

как напряжение на его базе становится выше, чем на базах входных

транзисторов. Через открытый транзистор протекает ток Iк2, значение

которого задается резистором Rэ, и создает падение напряжения на

резисторе R2. Потенциал коллектора транзистора VТ4 при этом

понижается и подается на вход эмиттерного повторителя, собранного на

транзисторе VТ7. На выходе эмиттерного повторителя получается

низкий уровень напряжения, соответствующий логическому нулю.

В это же время через резистор R1 левой ветви токового ключа протекает

небольшой обратный ток Iк1. Потенциал коллектора транзистора VТ3

повышается и поступает на базу эмиттерного повторителя транзистора

VТ6. На выходе транзистора VT6 имеем большой потенциал,

логическую единицу, при этом выполняется логическая операция ИЛИ–

НЕ.

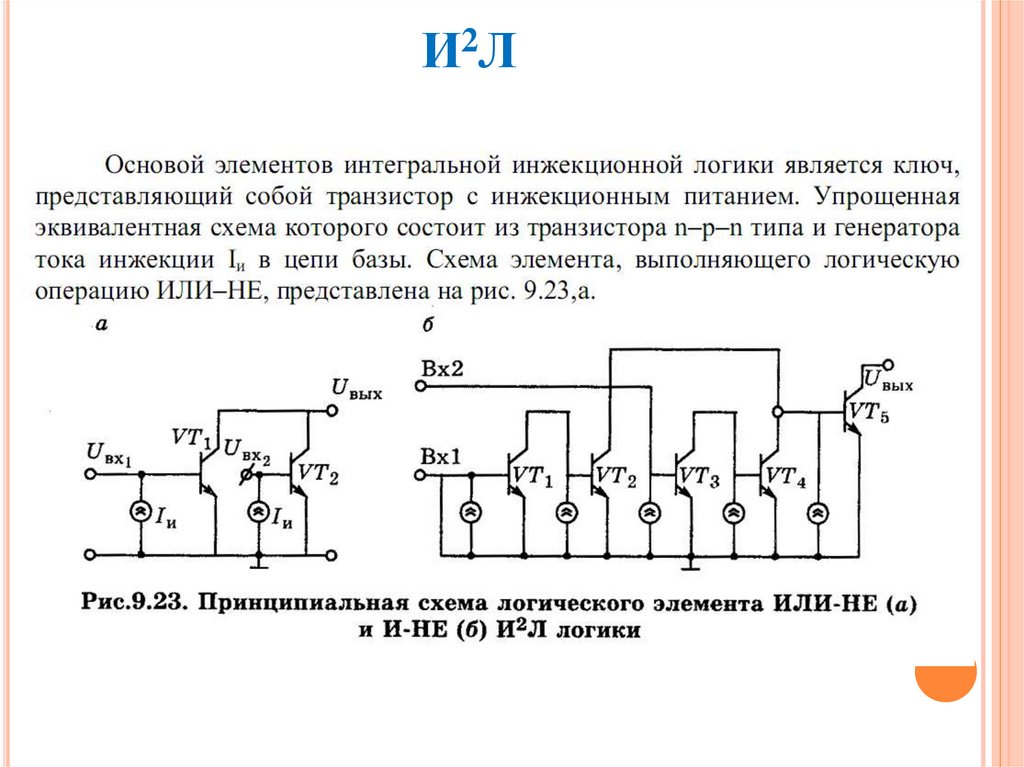

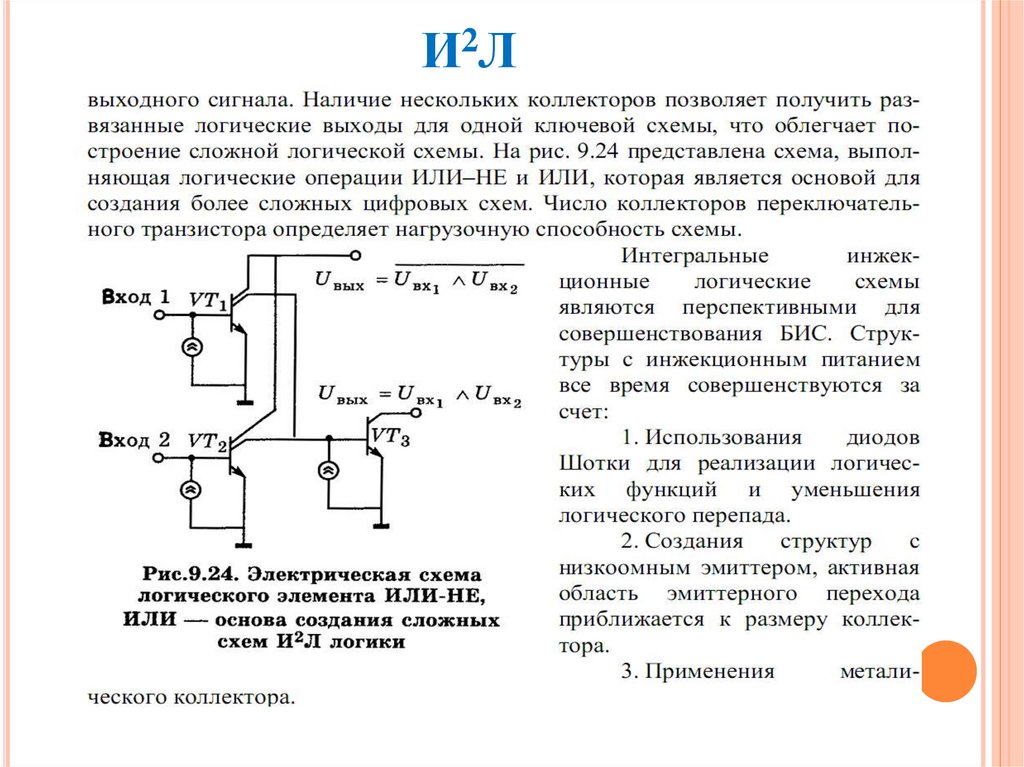

43. И2Л

44. И2Л

45. И2Л

46. И2Л

47. КМОП

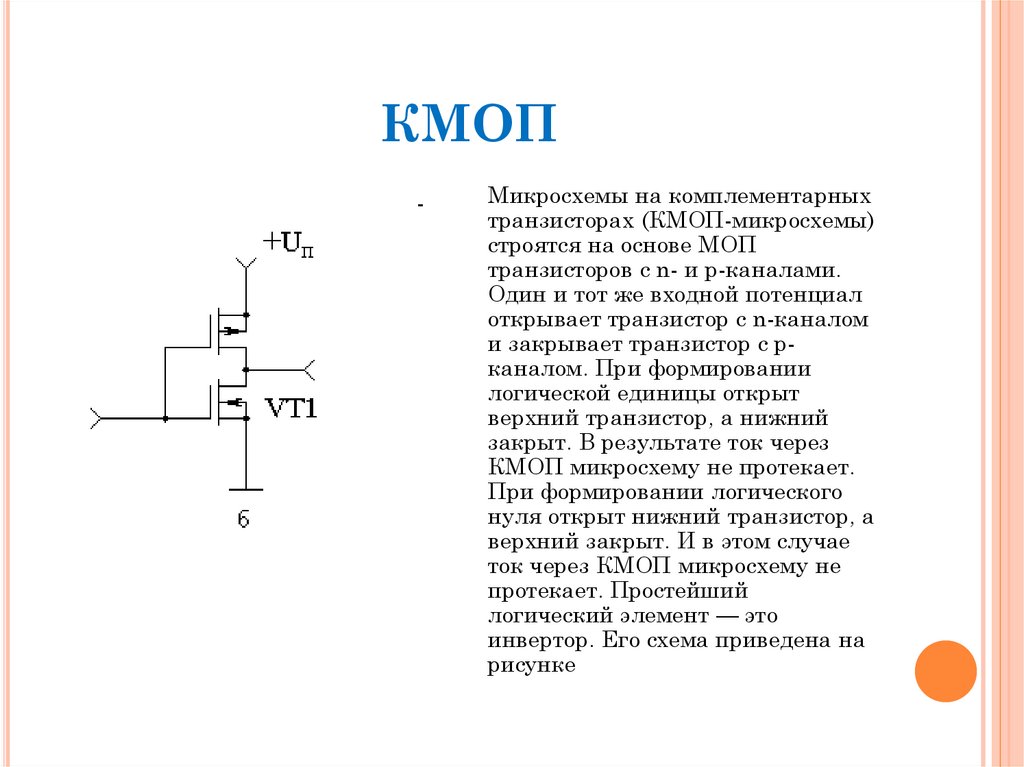

Микросхемы на комплементарныхтранзисторах (КМОП-микросхемы)

строятся на основе МОП

транзисторов с n- и p-каналами.

Один и тот же входной потенциал

открывает транзистор с n-каналом

и закрывает транзистор с pканалом. При формировании

логической единицы открыт

верхний транзистор, а нижний

закрыт. В результате ток через

КМОП микросхему не протекает.

При формировании логического

нуля открыт нижний транзистор, а

верхний закрыт. И в этом случае

ток через КМОП микросхему не

протекает. Простейший

логический элемент — это

инвертор. Его схема приведена на

рисунке

48. КМОП

Особенностью микросхем накомплементарных МОП

транзисторах является то, что

в этих микросхемах в

статическом режиме ток

практически не потребляется.

Потребление тока происходит

только в момент переключения

КМОП микросхемы из

единичного состояния в

нулевое и наоборот. Этот ток

вызван двумя причинами —

одновременным переходом

верхнего и нижнего МОП

транзисторов в активный

режим работы и перезарядом

паразитной ёмкости нагрузки.

49. КМОП

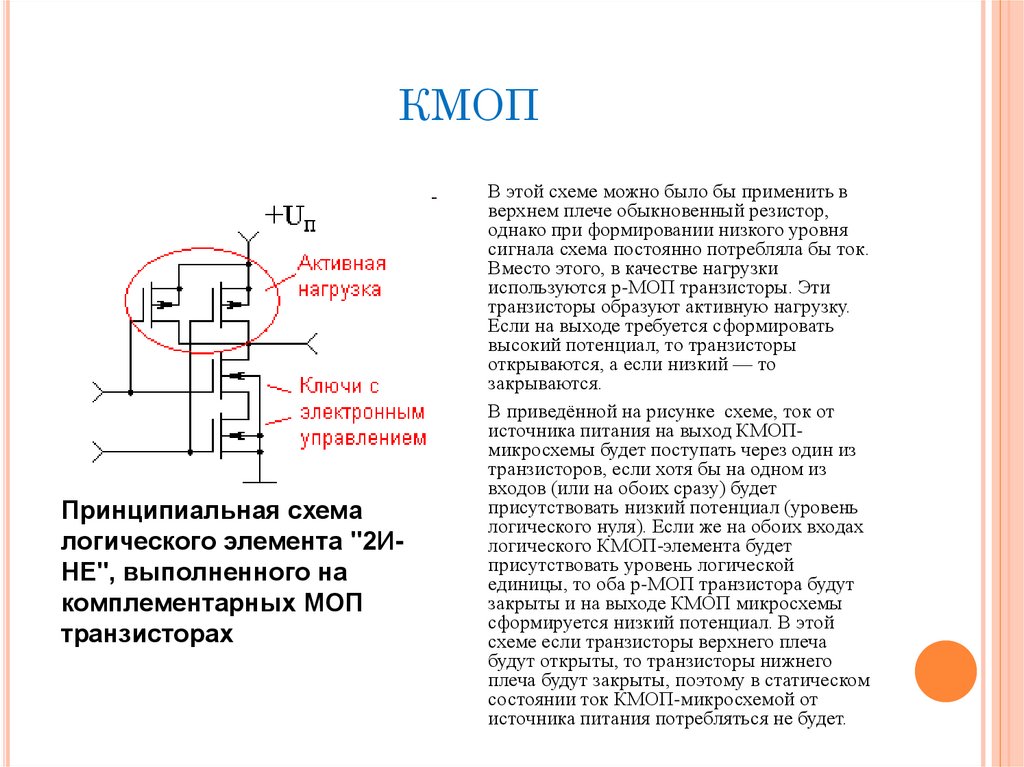

Принципиальная схемалогического элемента "2ИНЕ", выполненного на

комплементарных МОП

транзисторах

В этой схеме можно было бы применить в

верхнем плече обыкновенный резистор,

однако при формировании низкого уровня

сигнала схема постоянно потребляла бы ток.

Вместо этого, в качестве нагрузки

используются p-МОП транзисторы. Эти

транзисторы образуют активную нагрузку.

Если на выходе требуется сформировать

высокий потенциал, то транзисторы

открываются, а если низкий — то

закрываются.

В приведённой на рисунке схеме, ток от

источника питания на выход КМОПмикросхемы будет поступать через один из

транзисторов, если хотя бы на одном из

входов (или на обоих сразу) будет

присутствовать низкий потенциал (уровень

логического нуля). Если же на обоих входах

логического КМОП-элемента будет

присутствовать уровень логической

единицы, то оба p-МОП транзистора будут

закрыты и на выходе КМОП микросхемы

сформируется низкий потенциал. В этой

схеме если транзисторы верхнего плеча

будут открыты, то транзисторы нижнего

плеча будут закрыты, поэтому в статическом

состоянии ток КМОП-микросхемой от

источника питания потребляться не будет.

50. КМОП

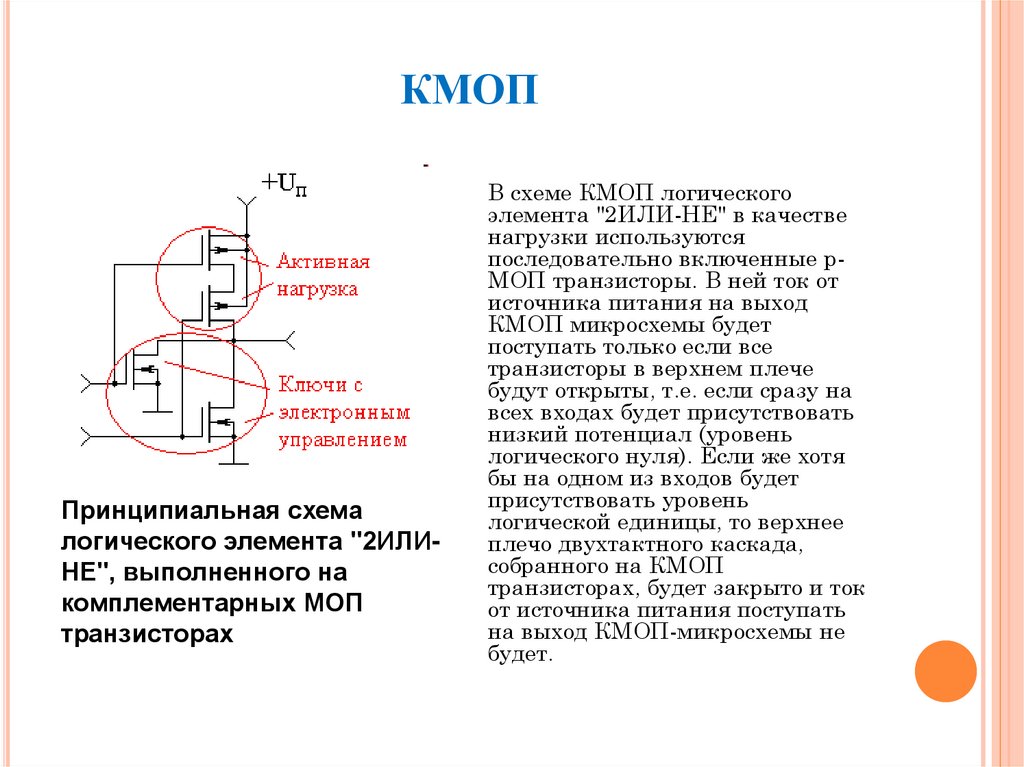

Принципиальная схемалогического элемента "2ИЛИНЕ", выполненного на

комплементарных МОП

транзисторах

В схеме КМОП логического

элемента "2ИЛИ-НЕ" в качестве

нагрузки используются

последовательно включенные pМОП транзисторы. В ней ток от

источника питания на выход

КМОП микросхемы будет

поступать только если все

транзисторы в верхнем плече

будут открыты, т.е. если сразу на

всех входах будет присутствовать

низкий потенциал (уровень

логического нуля). Если же хотя

бы на одном из входов будет

присутствовать уровень

логической единицы, то верхнее

плечо двухтактного каскада,

собранного на КМОП

транзисторах, будет закрыто и ток

от источника питания поступать

на выход КМОП-микросхемы не

будет.

Электроника

Электроника