Похожие презентации:

Аппаратная реализация диспетчера задач в многопроцессорной вычислительной системе

1. Аппаратная реализация диспетчера задач в многопроцессорной вычислительной системе

Дипломный проектВыполнил: студент группы 05ВВ1

Меркурьев А. И.

Руководитель: профессор кафедры ВТ

Пензенского Государственного Университета

д.т.н. Вашкевич Н. П.

Пенза

2010

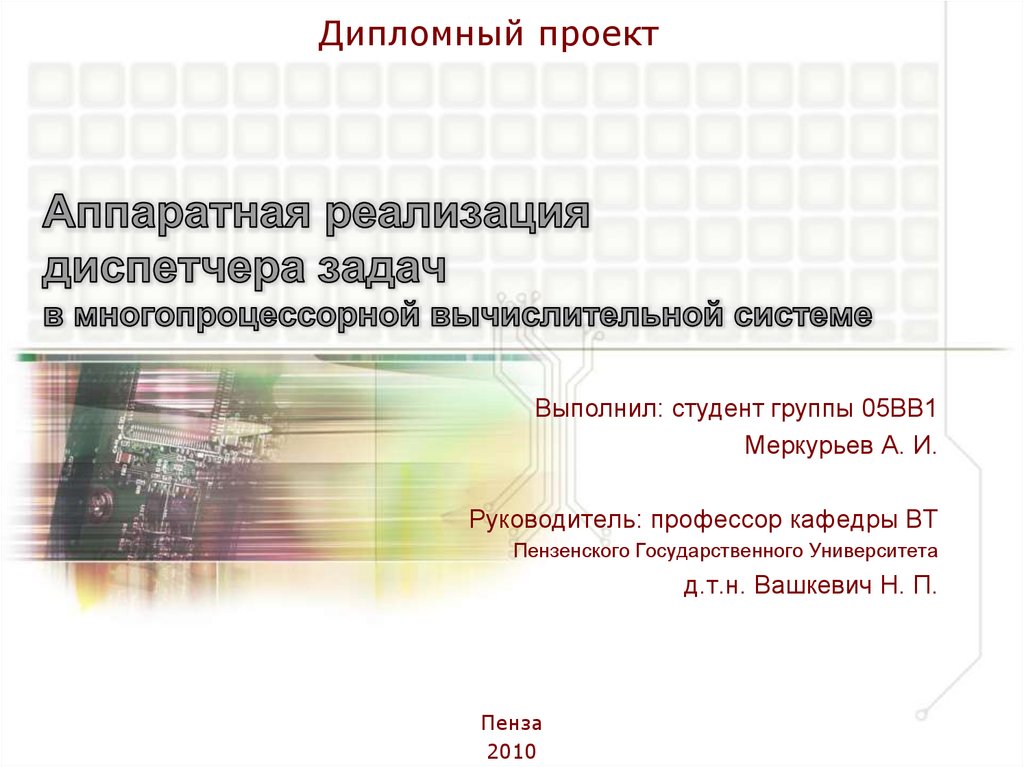

2. Программная реализация алгоритмов

Аппаратнаяреализация алгоритмов

3. Целью дипломного проекта является

разработка устройства, являющегося частьюмногопроцессорной системы, обеспечивающего

повышение производительности операционной

системы, и выполняющего совместно с ней

следующие функции:

• планирование процессов

• диспетчеризация задач

• восстановление контекста задачи

4. Модели недетерминированных автоматов

VHDL(язык описания аппаратуры интегральных схем)

Синтезируемая модель

вычислительного устройства

5. Алгоритмы диспетчеризации задач

Алгоритм с глобальной единой очередью задачАлгоритм с распределенными очередями задач

6. Диспетчер с глобальной очередью задач

свободензанят

З

свободен

занят

7. Диспетчер с распределенными очередями задач

свободензанят

свободен

занят

З

свободен

занят

8.

Конфликт за доступ каппаратному диспетчеру

Учет распределения задач

по очередям процессоров

Более сложная

реализация

Мониторинг контроля

работоспособности

процессоров

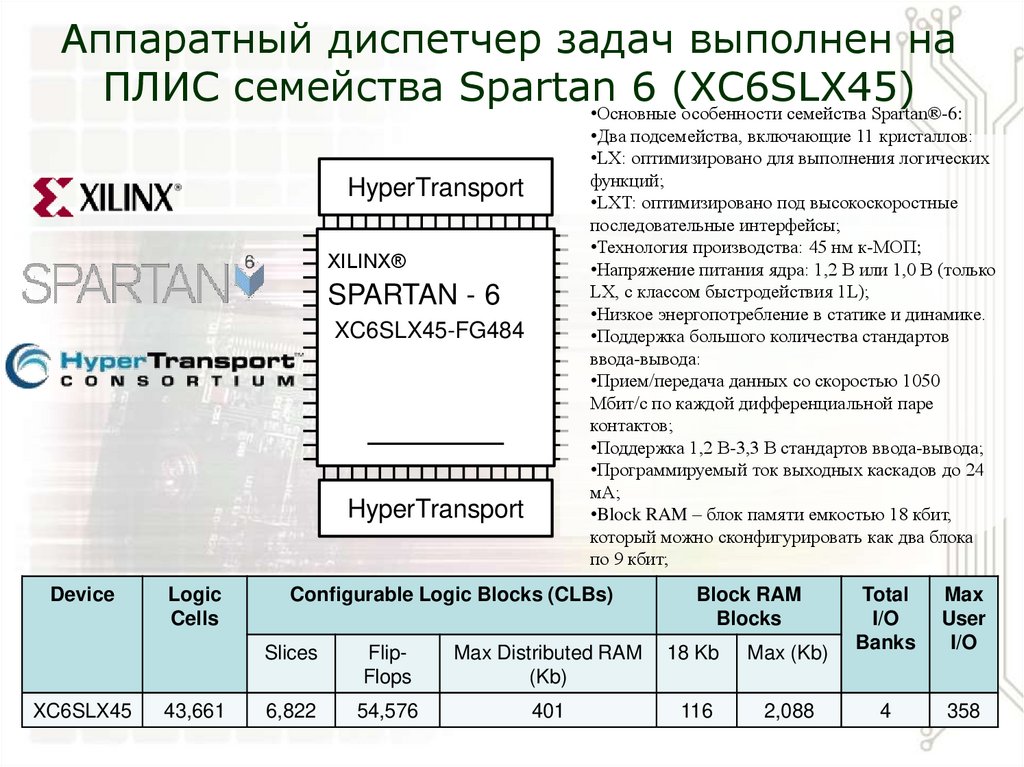

9. Аппаратный диспетчер задач выполнен на ПЛИС семейства Spartan 6 (XC6SLX45)

•Основные особенности семейства Spartan®-6:•Два подсемейства, включающие 11 кристаллов:

•LX: оптимизировано для выполнения логических

функций;

•LXT: оптимизировано под высокоскоростные

последовательные интерфейсы;

•Технология производства: 45 нм к-МОП;

•Напряжение питания ядра: 1,2 В или 1,0 В (только

LX, с классом быстродействия 1L);

•Низкое энергопотребление в статике и динамике.

•Поддержка большого количества стандартов

ввода-вывода:

•Прием/передача данных со скоростью 1050

Мбит/с по каждой дифференциальной паре

контактов;

•Поддержка 1,2 В-3,3 В стандартов ввода-вывода;

•Программируемый ток выходных каскадов до 24

мА;

•Block RAM – блок памяти емкостью 18 кбит,

который можно сконфигурировать как два блока

по 9 кбит;

HyperTransport

XILINX®

SPARTAN - 6

XC6SLX45-FG484

HyperTransport

Device

XC6SLX45

Logic

Cells

43,661

Configurable Logic Blocks (CLBs)

Block RAM

Blocks

Slices

FlipFlops

Max Distributed RAM

(Kb)

18 Kb

Max (Kb)

6,822

54,576

401

116

2,088

Total

I/O

Banks

Max

User

I/O

4

358

10. Аппаратный диспетчер в многопроцессорной SUMA-системе

DDR400 PC3200128-bits Registered

200 MHz 16-bits ECC

AMD Dual-core Opteron

Processor

Hardware Scheduler

Аппаратный диспетчер

SPARTAN-6

AMD Dual-core Opteron

Processor

HyperTransport x16

(6,4GB/s)

HyperTransport x8

(800MB/s)

PCI-X

32bits

533MHz

64bits

100MHz

AGP 3.0

8151

AMD-8132

HyperTransport

Graphics Tunnel

8111

AMD-8111

HyperTransport

I/O Hub

AC’97,USB,LPC,PCI,IDE,SMBus,LAN

Chipset components AMD 8000

8132

AMD-8132

HyperTransport

PCI-X Tunnel

11. Структура аппаратного диспетчера задач

12. Этапы проектирования устройства

ФормальноеРазработка

Функциональное

описание

проекта

алгоритма

и временное

для ПЛИС

работы

Создание

Разработка

базовой

электрической

модели устройства

схемы

моделирование

наустройства

языке

проекта

VHDLдля ПЛИС

Создание базовой модели устройства

Формальное описание алгоритма работы устройства

Разработка проекта для ПЛИС на языке VHDL

Функциональное и временное моделирование проекта для

ПЛИС

Разработка электрической схемы

Изготовление макетного образца

Тестирование и отладка работы устройства

13.

Сочетание универсальных и специализированныхпроцессоров – одно из перспективных направлений

повышения производительности многопроцессорных

систем

Сервер HP семейства Integrity NonStop

Серверы IBM Power Systems

Блейд-сервер HP ProLiant BL465c

Электроника

Электроника