Похожие презентации:

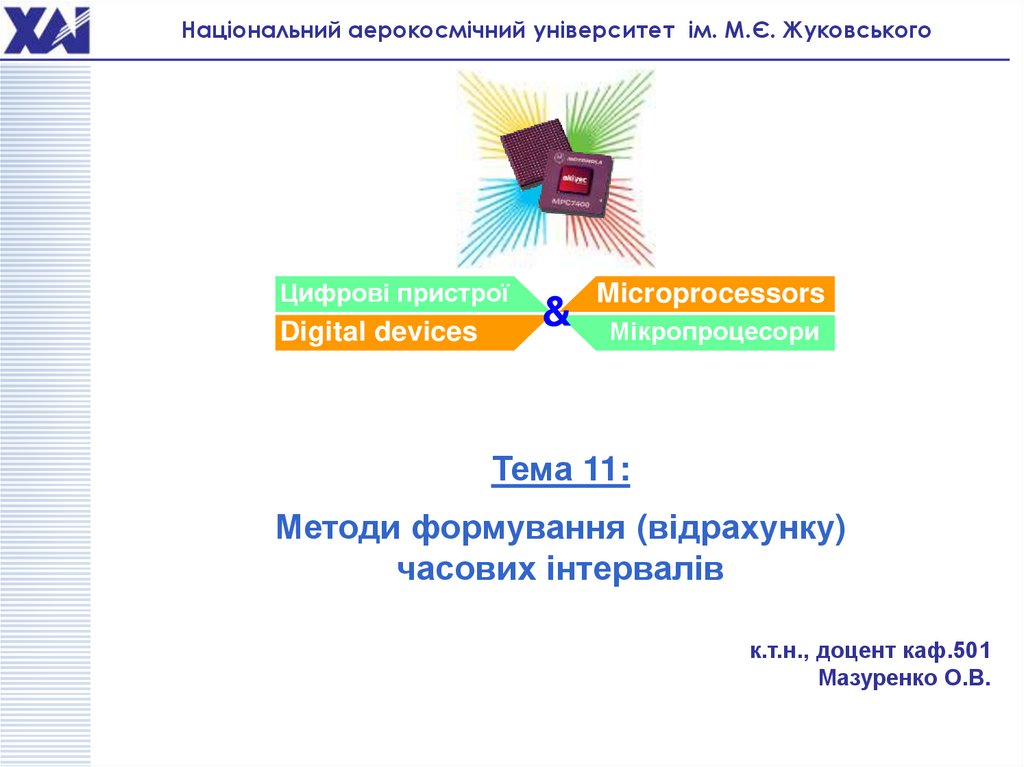

Методи формування (відрахунку) часових інтервалів. Тема 11

1.

Національний аерокосмічний університет ім. М.Є. ЖуковськогоЦифрові пристрої

Digital devices

&

Microprocessors

Мікропроцесори

Тема 11:

Методи формування (відрахунку)

часових інтервалів

к.т.н., доцент каф.501

Мазуренко О.В.

2.

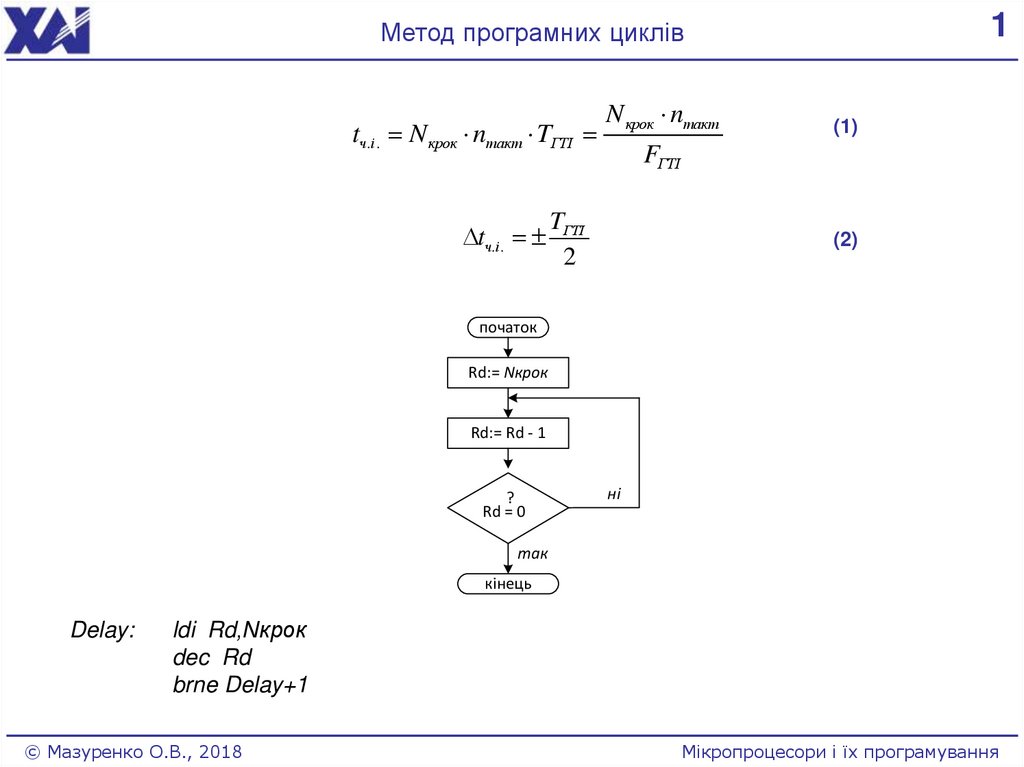

1Метод програмних циклів

tч.і . N крок nтакт TГТІ

tч.і.

N крок nтакт

(1)

FГТІ

TГТІ

2

(2)

початок

Rd:= Nкрок

Rd:= Rd - 1

?

Rd = 0

ні

так

кінець

Delay:

ldi Rd,Nкрок

dec Rd

brne Delay+1

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

3.

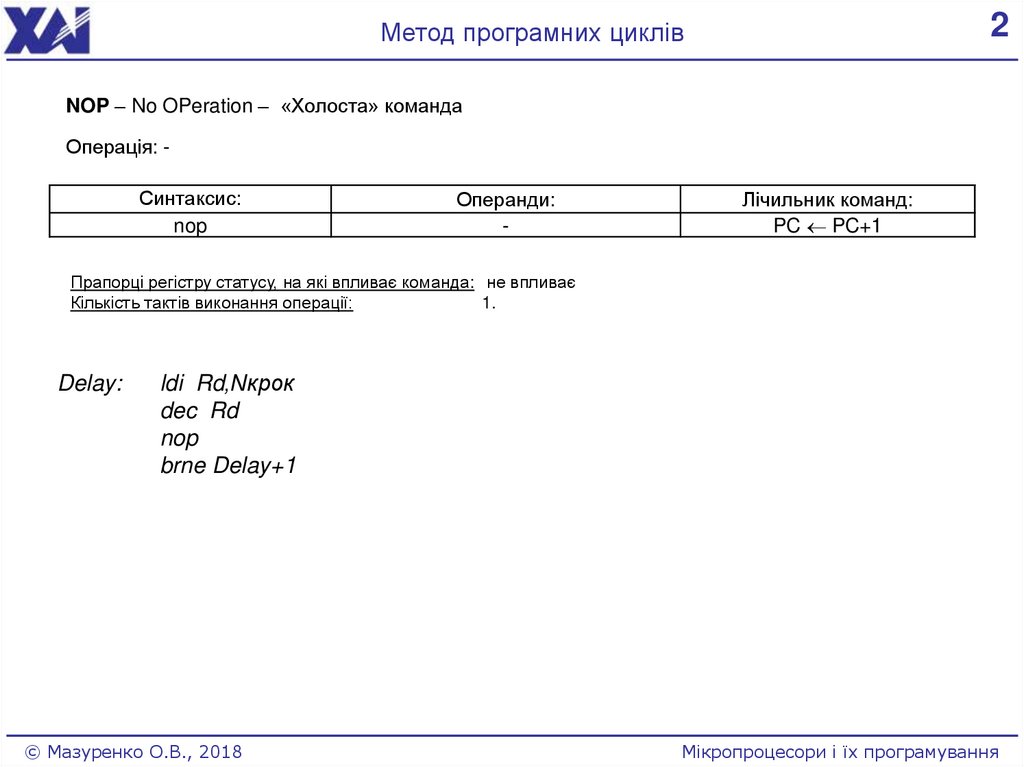

2Метод програмних циклів

NOP – No OPeration – «Холоста» команда

Операція: Синтаксис:

nop

Операнди:

-

Лічильник команд:

PC PC+1

Прапорці регістру статусу, на які впливає команда: не впливає

Кількість тактів виконання операції:

1.

Delay:

ldi Rd,Nкрок

dec Rd

nop

brne Delay+1

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

4.

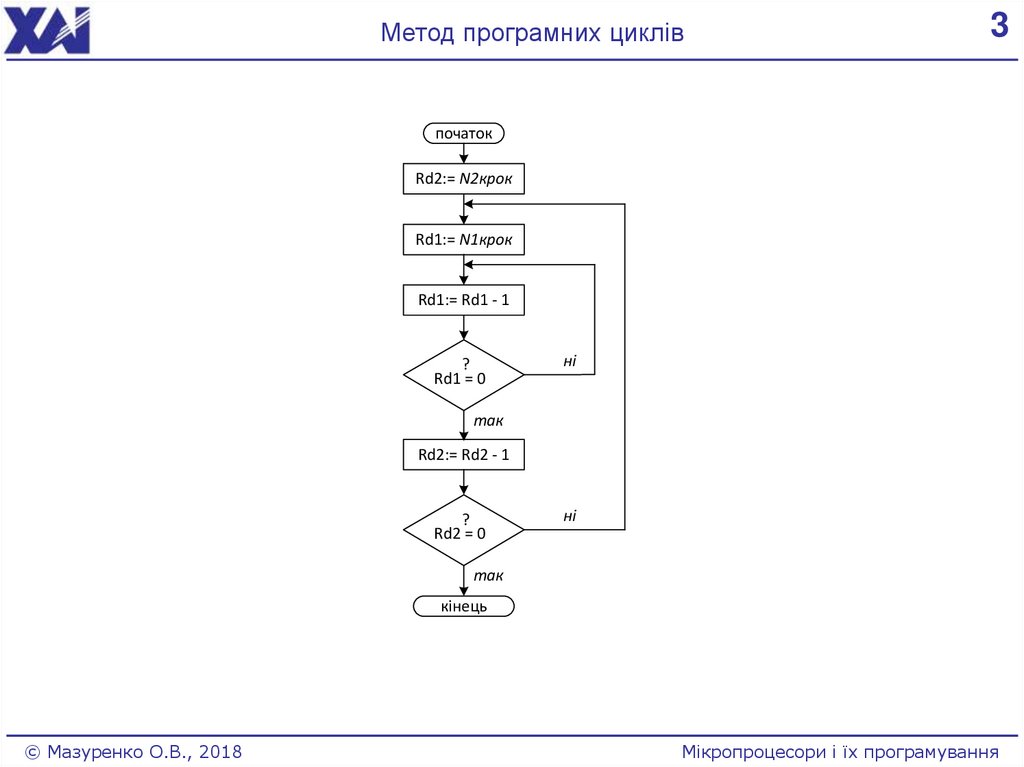

Метод програмних циклів3

початок

Rd2:= N2крок

Rd1:= N1крок

Rd1:= Rd1 - 1

?

Rd1 = 0

ні

так

Rd2:= Rd2 - 1

?

Rd2 = 0

ні

так

кінець

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

5.

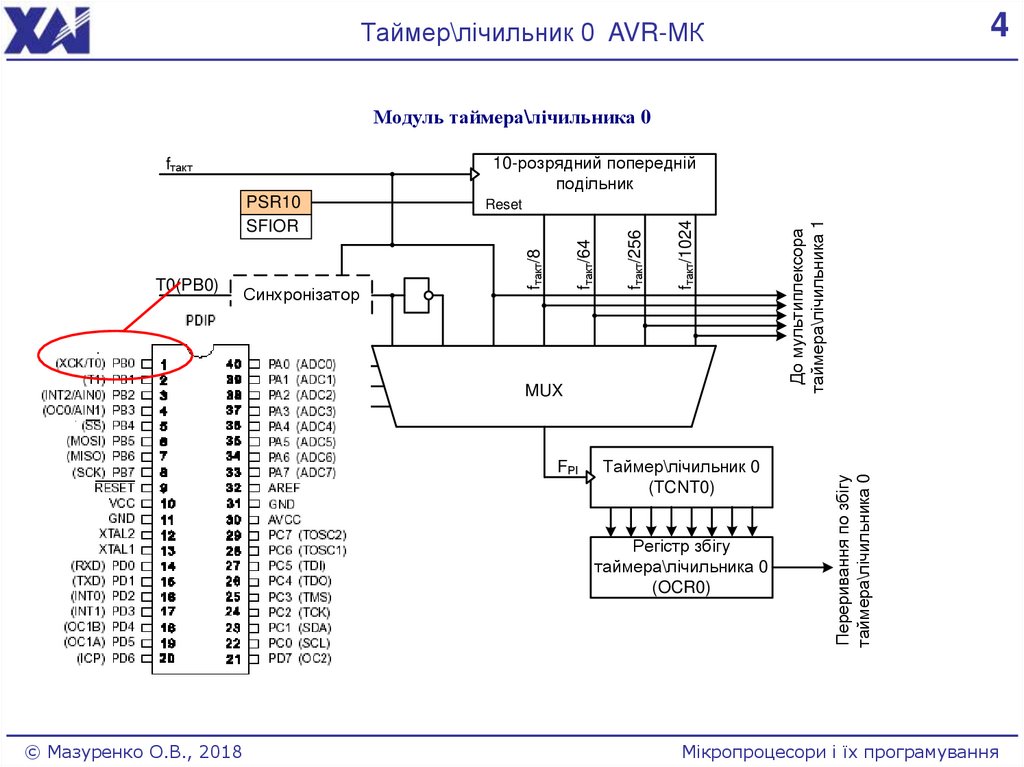

4Таймер\лічильник 0 AVR-МК

Модуль таймера\лічильника 0

10-розрядний попередній

подільник

FРІ

Таймер\лічильник 0

(TCNT0)

Регістр збігу

таймера\лічильника 0

(OCR0)

© Мазуренко О.В., 2018

Переривання по збігу

таймера\лічильника 0

MUX

До мультиплексора

таймера\лічильника 1

CS00

CS01

CS02

TCCR0

fтакт/1024

Синхронізатор

fтакт/256

T0(PB0)

Reset

fтакт/64

PSR10

SFIOR

fтакт/8

fтакт

Мікропроцесори і їх програмування

6.

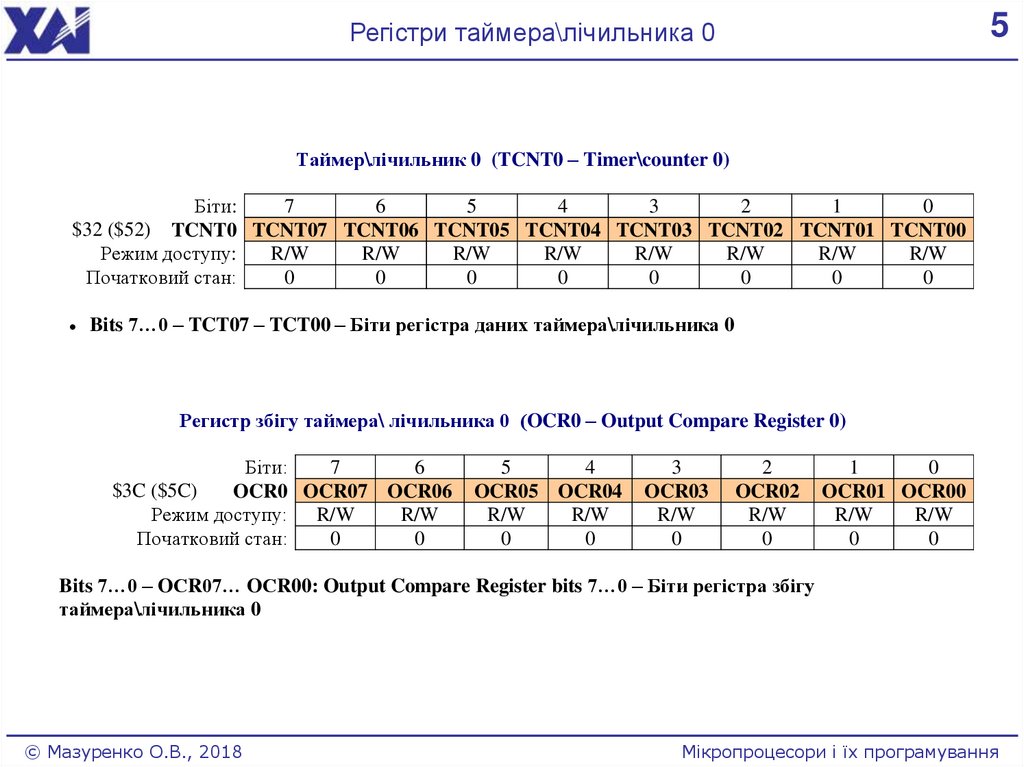

5Регістри таймера\лічильника 0

Таймер\лічильник 0 (TCNT0 – Timer\counter 0)

Біти:

7

6

5

4

3

2

1

0

$32 ($52) TCNT0 TCNT07 TCNT06 TCNT05 TCNT04 TCNT03 TCNT02 TCNT01 TCNT00

Режим доступу:

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Початковий стан:

0

0

0

0

0

0

0

0

Bits 7…0 – TCT07 – TCT00 – Біти регістра даних таймера\лічильника 0

Регистр збігу таймера\ лічильника 0 (OCR0 – Output Compare Register 0)

Біти:

7

6

$3C ($5C)

OCR0 OCR07 OCR06

Режим доступу: R/W

R/W

Початковий стан:

0

0

5

4

OCR05 OCR04

R/W

R/W

0

0

3

OCR03

R/W

0

2

OCR02

R/W

0

1

0

OCR01 OCR00

R/W

R/W

0

0

Bits 7…0 – OСR07… OСR00: Output Compare Register bits 7…0 – Біти регістра збігу

таймера\лічильника 0

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

7.

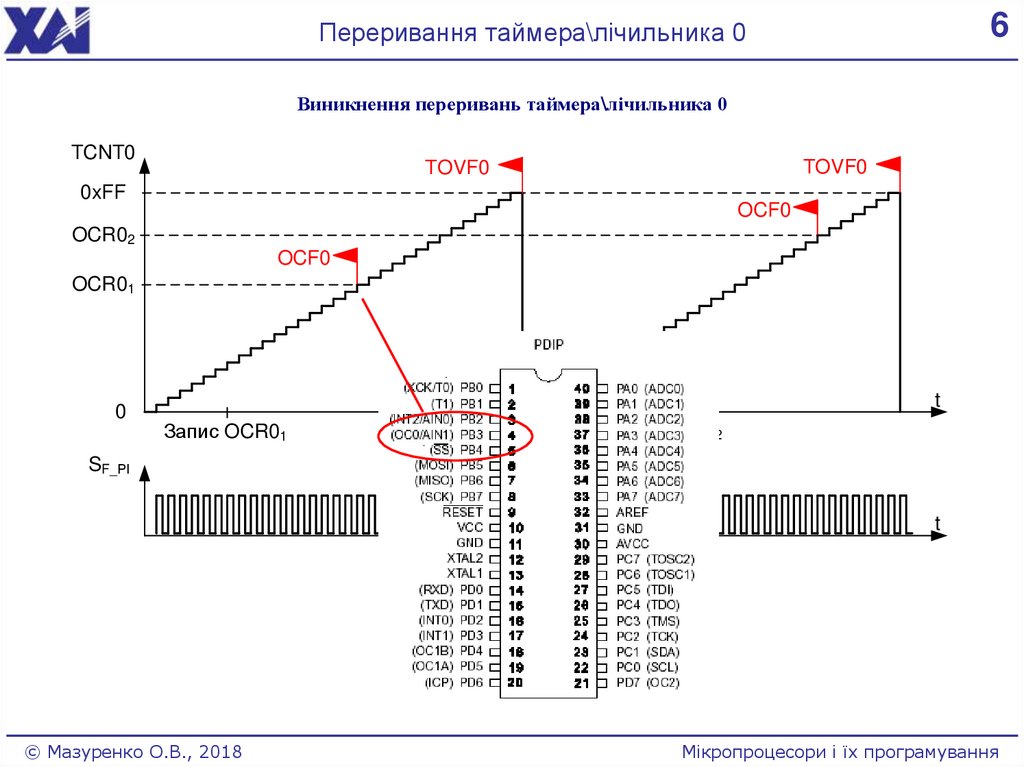

6Переривання таймера\лічильника 0

Виникнення переривань таймера\лічильника 0

TCNT0

TOVF0

TOVF0

0xFF

OCF0

OCR02

OCF0

OCR01

0

t

Запис OCR01

Запис OCR02

SF_РІ

t

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

8.

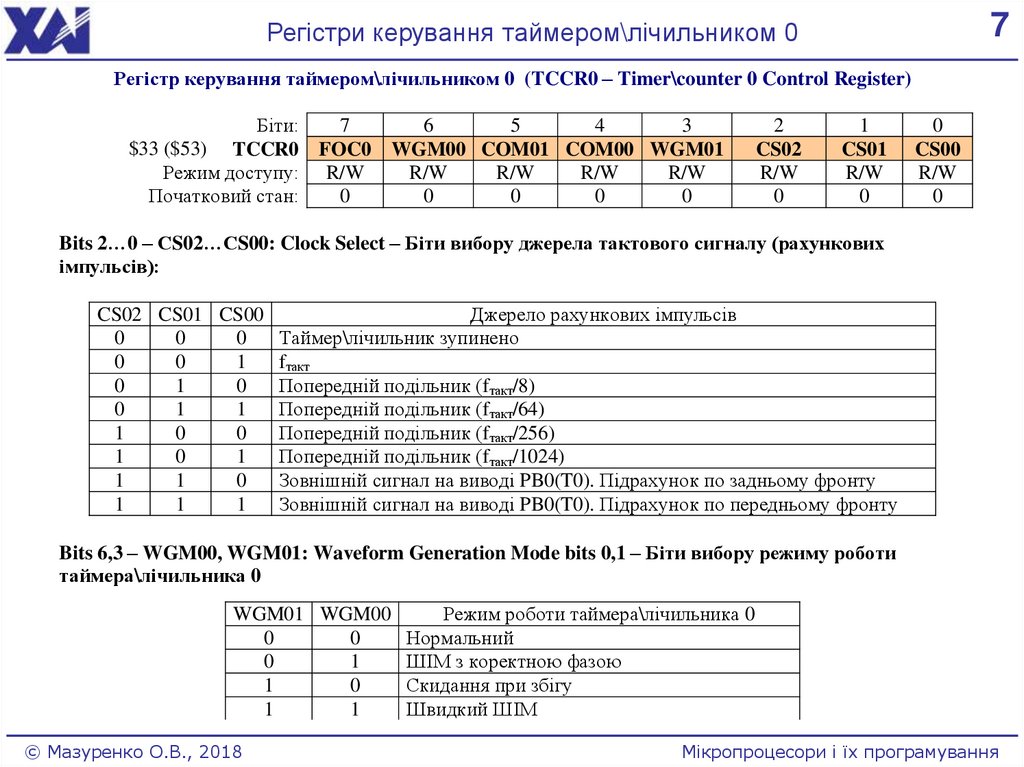

7Регістри керування таймером\лічильником 0

Регістр керування таймером\лічильником 0 (TCCR0 – Timer\counter 0 Control Register)

Біти:

7

6

5

4

3

$33 ($53) TCCR0 FOC0 WGM00 COM01 COM00 WGM01

Режим доступу: R/W

R/W

R/W

R/W

R/W

Початковий стан:

0

0

0

0

0

2

CS02

R/W

0

1

CS01

R/W

0

0

CS00

R/W

0

Bits 2…0 – СS02…СS00: Clock Select – Біти вибору джерела тактового сигналу (рахункових

імпульсів):

CS02 CS01 CS00

Джерело рахункових імпульсів

0

0

0

Таймер\лічильник зупинено

0

0

1

fтакт

0

1

0

Попередній подільник (fтакт/8)

0

1

1

Попередній подільник (fтакт/64)

1

0

0

Попередній подільник (fтакт/256)

1

0

1

Попередній подільник (fтакт/1024)

1

1

0

Зовнішній сигнал на виводі PB0(T0). Підрахунок по задньому фронту

1

1

1

Зовнішній сигнал на виводі PB0(T0). Підрахунок по передньому фронту

Bits 6,3 – WGM00, WGM01: Waveform Generation Mode bits 0,1 – Біти вибору режиму роботи

таймера\лічильника 0

WGM01 WGM00

Режим роботи таймера\лічильника 0

0

0

Нормальний

0

1

ШІМ з коректною фазою

1

0

Скидання при збігу

1

1

Швидкий ШІМ

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

9.

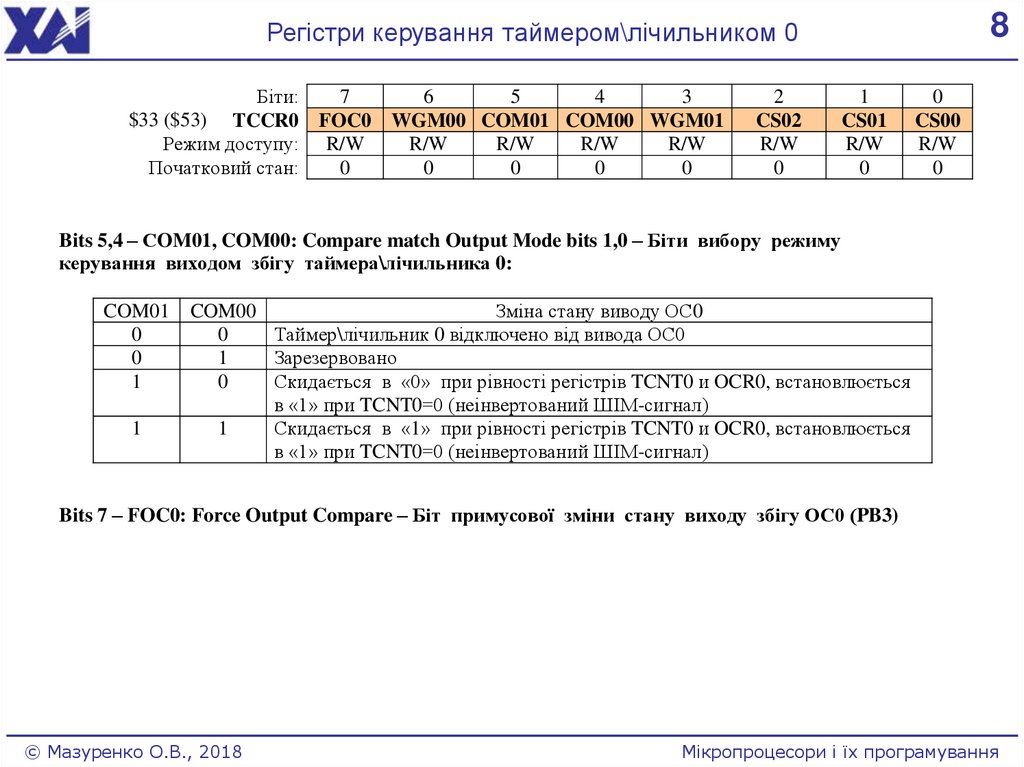

8Регістри керування таймером\лічильником 0

Біти:

7

6

5

4

3

$33 ($53) TCCR0 FOC0 WGM00 COM01 COM00 WGM01

Режим доступу: R/W

R/W

R/W

R/W

R/W

Початковий стан:

0

0

0

0

0

2

CS02

R/W

0

1

CS01

R/W

0

0

CS00

R/W

0

Bits 5,4 – СOM01, COM00: Compare match Output Mode bits 1,0 – Біти вибору режиму

керування виходом збігу таймера\лічильника 0:

COM01

0

0

1

1

COM00

Зміна стану виводу ОС0

0

Таймер\лічильник 0 відключено від вивода OC0

1

Зарезервовано

0

Скидається в «0» при рівності регістрів TCNT0 и OCR0, встановлюється

в «1» при TCNT0=0 (неінвертований ШІМ-сигнал)

1

Скидається в «1» при рівності регістрів TCNT0 и OCR0, встановлюється

в «1» при TCNT0=0 (неінвертований ШІМ-сигнал)

Bits 7 – FOC0: Force Output Compare – Біт примусової зміни стану виходу збігу ОС0 (PB3)

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

Программирование

Программирование