Похожие презентации:

Процессоры, память и периферийные устройства ВС, их простейшие модели и разновидности. Лекция 6

1.

Лекция 6: Процессоры, память ипериферийные устройства ВС, их

простейшие модели и разновидности. Конвейерный способ выполнения команд в современных ЭВМ.

Архитектура памяти и систем

хранения информации.

2.

Архитектура вычислительных средствПри описании аппаратных средств вычислительной техники обычно

выделяют собственно вычислительное устройство – процессор;

различные типы и системы организации памяти (кэши, оперативная,

энергонезависимая), контроллеры системных шин и периферийных

устройств, сами эти устройства. Организация связей между ними

может быть различной, соответственно выделяют несколько типов

архитектур вычислительных систем, две из них наиболее известны:

принстонская и гарвардская.

Принстонская архитектура, часто называемая архитектурой фон

Неймана, характеризуется использованием общей оперативной

памяти для хранения программ, данных, а также для организации

стека. Для обращения к этой памяти используется общая системная

шина, по которой в процессор поступают и команды, и данные.

Гарвардская архитектура была разработана Говардом Эйкеном с

целью

увеличить

скорость

вычислительных

операций

и

оптимизировать работу памяти. Она характеризуется физическим

разделением памяти команд (программ) и памяти данных. В ее

оригинальном варианте использовался также отдельный стек для

хранения

содержимого

программного

счетчика,

который

обеспечивал возможности выполнения вложенных подпрограмм.

Каждая память соединяется с процессором отдельной шиной, что

позволяет одновременно с чтением-записью данных при выполнении

текущей команды производить выборку и декодирование следующей

команды.

3.

Гарвардская архитектура4.

Архитектура вычислительных средствАрхитектура

современных

персональных

компьютеров

основана на магистрально-модульном принципе.

Шина – это кабель, состоящий из множества проводников.

Количество проводников, входящих в состав шины, определяет

максимальную разрядность шины.

Системная шина, в свою очередь, представляет собой

совокупность

шины данных, служащей для переноса информации;

шины

адреса,

которая

определяет,

куда

переносить

информацию;

шины управления, которая определяет правила для передачи

информации;

шины питания, подводящей электропитание ко всем узлам

вычислительной машины.

Шины данных и адреса могут объединяться в режиме

мультиплексирования.

Системная шина характеризуется тактовой частотой и

разрядностью. Количество одновременно передаваемых по

шине бит называется разрядностью шины.

Тактовая частота характеризует число элементарных операций

по передаче данных в 1 секунду. Разрядность шины

измеряется в битах, тактовая частота – в мегагерцах.

5.

Архитектура вычислительных средствУстройство управления

(УУ) выполняет функции

управления

вычислительным процессом на основе кодов команд и признаков

результатов предыдущих операций. Современные УУ, как правило,

строятся по принципу микропрограммирования, когда в результате

дешифрации команды и значений ряда регистров запускаются

последовательности

управляющих

сигналов

(микрокоманды)

различным блокам процессора.

УУ формирует адрес команды, которая должна быть выполнена в

данном цикле, и выдает управляющий сигнал на чтение

содержимого соответствующей ячейки запоминающего устройства

(ЗУ). Считанная команда передается в УУ. По информации,

содержащейся в адресных полях команды, УУ формирует адреса

операндов и управляющие сигналы для их чтения из ЗУ и передачи в

арифметико-логическое устройство (АЛУ). После считывания

операндов

устройство

управления

по

коду

операции,

содержащемуся в команде, выдает в АЛУ сигналы на выполнение

операции. Полученный результат записывается в ЗУ по адресу

приемника результата под управлением сигналов записи. Признаки

результата (знак, наличие переполнения, признак нуля и так далее)

поступают в устройство управления, где записываются в специальный

регистр признаков. Эта информация может использоваться при

выполнении следующих команд программы, например команд

условного перехода.

6.

Архитектура вычислительных средствСтруктура гипотетического процессора

7.

Архитектура вычислительных средствРегистр адреса (РА) предназначен для хранения адреса ячейки

основной

памяти

вплоть

до

завершения

операции

(считывание или запись) с этой ячейкой.

Указатель стека (УкС) — это регистр, где хранится адрес

вершины стека. В реальных вычислительных машинах стек

реализуется в виде участка основной памяти обычно

расположенного

в

области

наибольших

адресов.

Заполнение стека происходит в сторону уменьшения

адресов, при этом вершина стека — это ячейка, куда была

произведена последняя по времени запись. Для хранения

адреса такой ячейки и предназначен УкС. При выполнении

операции занесения в стек содержимое УкС сначала

уменьшается на единицу, после чего используется в качестве

адреса, по которому производится запись. Соответствующая

ячейка становится новой вершиной стека. Считывание из

стека происходит из ячейки, на которую указывает текущий

адрес в УкС, после чего содержимое указателя стека

увеличивается на единицу. Таким образом, вершина стека

опускается, а считанное слово считается удаленным из стека.

Хотя физически считанное слово и осталось в ячейке памяти,

при следующей записи в стек оно будет заменено новой

информацией.

8.

Архитектура вычислительных средствСчетчик команд (СК) — неотъемлемый элемент процессора

любой

ЭВМ,

построенной

в

соответствии

с

фоннеймановским принципом программного управления.

Согласно этому принципу соседние команды программы

располагаются в ячейках памяти со следующими по порядку

адресами и выполняются преимущественно в той же

очередности, в какой они размещены в памяти ЭВМ. Перед

началом вычислений в СК заносится адрес ячейки основной

памяти, где хранится команда, которая должна быть

выполнена первой. В процессе выполнения каждой команды

путем увеличения содержимого СК на длину выполняемой

команды в счетчике формируется адрес следующей

подлежащей выполнению команды. По завершении текущей

команды адрес следующей команды программы всегда

берется из счетчика команд. Для изменения естественного

порядка вычислений (перехода в иную точку программы)

достаточно занести в СК адрес точки перехода.

Регистр команды. Чтобы приступить к выполнению команды, ее

необходимо извлечь из памяти и разместить в регистре

команды (РК). Этот этап носит название выборки команды. В

РК команда хранится в течение всего времени ее выполнения.

9.

Архитектура вычислительных средствРегистры общего назначения (РОН), служат для временного

хранения операндов и результатов вычислений. Это самый

быстрый, но и минимальный по емкости тип памяти, который

иногда

объединяют

понятием

сверхоперативное

запоминающее устройство — СОЗУ. Как правило, количество

регистров невелико, хотя в архитектурах с сокращенным

набором команд их число может доходить до нескольких

десятков.

Индексные регистры (ИР) служат для формирования адресов

операндов при реализации циклических участков программ.

Регистр признака результата (РПР) предназначен для фиксации

и

хранения

признака,

характеризующего

результат

последней выполненной арифметической или логической

операции. Такие признаки могут информировать о равенстве

результата нулю, о знаке результата, о возникновении

переноса из старшего разряда, переполнении разрядной

сетки и т. д. Содержимое РПР обычно используется

устройством управления для реализации условных переходов

по результатам операций АЛУ. Под каждый из возможных

признаков отводится один разряд РПР.

10.

Архитектура вычислительных средствАккумулятор (Акк) — это регистр, на который возлагаются

самые

разнообразные

функции.

Так,

в

него

предварительно

загружается

один

из

операндов,

участвующих

в

арифметической

или

логической

операции. В Акк может храниться результат предыдущей

команды и в него же заносится результат очередной

операции. Через Акк зачастую производятся операции

ввода и вывода. Строго говоря, аккумулятор в равной

мере можно отнести как к АЛУ, так и к УУ, а в ЭВМ с

регистровой архитектурфой его можно рассматривать

как один из регистров общего назначения.

Буфер данных призван компенсировать разницу в

быстродействии запоминающих устройств и устройств,

выступающих в роли источников и потребителей хранимой

информации. В буфер данных при чтении заносится

содержимое ячейки ОП, а при записи — помещается

информация, подлежащая сохранению в ячейке ОП.

Буфер адреса. Наличие буфера адреса также позволяет

компенсировать различия в быстродействии оперативной

памяти и других устройств ЭВМ.

11.

Архитектура вычислительных средствСовременные процессоры имеют различные по сложности

наборы команд (RISC и CISC), используют технологии

конвейерной обработки команд, многопоточность и

многоядерность. На кристалле процессора либо рядом, в

конструктиве чипа, размещается кэш-память второго и

третьего уровня.

Если процессоры для серверов, как правило освобождены от

графических задач и работают с сокращёнными системами

команд, то линейки процессоров для ПК имеют графический

процессор

вместе

с

основным

в

одном

чипе.

Соответственно,

архитектура

современных

чипсетов

представлена только микросхемой «южного моста», т.е.

реализует интерфейсы лишь относительно медленных

устройств. Шинами оперативной памяти и видео управляет

центральный процессор.

В мобильных устройствах интеграция идёт ещё дальше,

применяются SoC – системы на чипе (System-on-Chip). На

одном кристалле размещают:

Вычислительные ядра (2-10, с различной группировкой);

Графический ускоритель;

Модем;

Контроллеры Wi-Fi и Bluetooth;

Контроллеры заряда. (технологии быстрой зарядки);

Процессор обработки изображений.

12.

Архитектура вычислительных средствАрхитектура современного АРМ процессора

13.

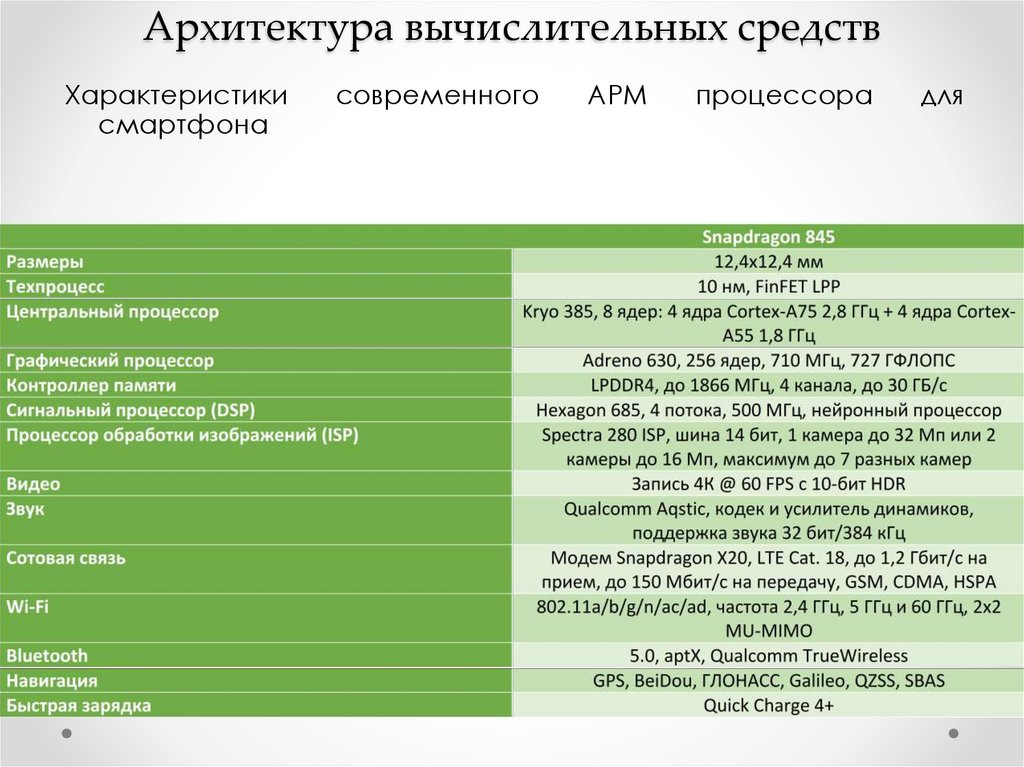

Архитектура вычислительных средствХарактеристики

смартфона

современного

АРМ

процессора

для

14.

Архитектура параллельных вычисленийОбычно рассматриваются два возможных вида параллелизма:

независимость потоков заданий (команд), существующих в

системе,

и

независимость

(несвязанность)

данных,

обрабатываемых в каждом потоке. С этой тчки зрения

существует четыре основных архитектуры вычислительных

систем:

• одиночный поток команд — одиночный поток данных (ОКОД),

в английском варианте — SingleInstructionSingleData (SISD) —

одиночный поток инструкций — одиночный поток данных;

• одиночный поток команд — множественный поток данных

(ОКМД), или SingleInstructionMultipleData (SIMD) — одиночный

поток инструкций — множественный поток данных;

• множественный поток команд — одиночный поток данных

(МКОД),

или

MultipleInstructionSingleData

(MISD)

—

множественный поток инструкций — одиночный поток данных;

• множественный поток команд — множественный поток

данных (МКМД), или MultipleInstructionMultipleData (MIMD) —

множественный поток инструкций — множественный поток

данных (MIMD).

15.

Архитектура параллельных вычисленийАрхитектура ОКОД охватывает все однопроцессорные и

одномашинные варианты систем, т.е. с одним вычислителем.

Параллелизм вычислений обеспечивается путем совмещения

выполнения операций отдельными блоками АЛУ, а также

параллельной работы устройств ввода-вывода информации

и процессора. Применимо для повышения надёжности

систем за счёт принятия решения по консенсусу или

большинству.

Архитектура ОКМД предполагает создание структур векторной

или матричной обработки. Системы этого типа обычно

строятся как однородные, т.е. процессорные элементы,

входящие в систему, идентичны, и все они управляются одной

и той же последовательностью команд. Однако каждый

процессор обрабатывает свой поток данных. Под эту схему

хорошо подходят задачи обработки матриц или векторов

(массивов), задачи решения систем линейных и нелинейных,

алгебраических и дифференциальных уравнений, задачи

теории поля и др. В структурах данной архитектуры

желательно обеспечивать соединения между процессорами,

соответствующие

реализуемым

математическим

зависимостям. Как правило, эти связи напоминают матрицу, в

которой каждый процессорный элемент связан с соседними.

16.

Архитектура параллельных вычисленийАрхитектура МКОД предполагает построение межпроцессорного

конвейера, в котором результаты обработки передаются от

одного процессора к другому по цепочке. В современных ЭВМ

по этому принципу реализована схема совмещения операций,

в которой параллельно работают различные функциональные

блоки в общем цикле обработки команды.

Конвейер должны образовывать группы процессоров. Очень трудно

выявить регулярный характер в универсальных вычислениях.

Кроме того, на практике нельзя обеспечить и «большую длину»

такого конвейера, при которой достигается наивысший эффект.

Схема нашла применение в скалярных процессорах суперЭВМ, в которых они применяются как специальные процессоры

для поддержки векторной обработки. Пример — сигнальные

процессоры.

Архитектура МКМД предполагает, что все процессоры системы

работают по своим программам с собственным потоком

команд. В простейшем случае они могут быть автономны и

независимы. Такая схема использования ВС часто применяется

на многих крупных вычислительных центрах для увеличения

пропускной способности центра. Больший интерес представляет

возможность согласованной работы ЭВМ (процессоров), когда

каждый элемент делает часть общей задачи. Теоретическая база

такого вида работ практически отсутствует. Такие системы могут

быть многомашинными и многопроцессорными.

17.

Конвейерные вычисленияВыполнение типичной команды ЭВМ можно разделить на этапы:

выборка команды - IF (по адресу, заданному счетчиком

команд, из памяти извлекается команда);

декодирование команды / выборка операндов из регистров - ID;

выполнение операции / вычисление эффективного адреса

памяти - EX;

обращение к памяти - MEM;

запоминание результата - WB.

Можно

представить

схему

простейшего

процессора,

выполняющего указанные выше этапы выполнения команд без

совмещения. Чтобы конвейеризовать эту схему, можно

разбить выполнение команд на этапы, отведя для выполнения

каждого один такт синхронизации, и начинать в каждом такте

выполнение новой команды. Для хранения промежуточных

результатов каждого этапа необходимо использовать

регистровые станции. Хотя общее время выполнения одной

команды в таком конвейере будет составлять пять тактов, в

каждом такте аппаратура будет выполнять в совмещенном

режиме пять различных команд.

Для представления работы конвейера используются временные

диаграммы, на которых обычно изображаются выполняемые

команды, номера тактов и этапы выполнения команд.

18.

Конвейерные вычисленияКонвейеризация увеличивает пропускную способность

процессора, но не сокращает время выполнения

отдельной команды. Она даже несколько увеличивает это

время

из-за

накладных

расходов,

связанных

с

управлением регистровыми станциями.

Кроме ограничений, связанных с задержкой конвейера,

имеются также ограничения, возникающие в результате

несбалансированности задержки на каждой его ступени

и из-за накладных расходов на конвейеризацию. Такт

синхронизации не может быть меньше, чем время,

необходимое для работы наиболее медленной ступени

конвейера.

Накладные

расходы

на

организацию

конвейера возникают из-за задержки сигналов в

конвейерных регистрах (защелках) и из-за перекосов

сигналов синхронизации. Конвейерные регистры к

длительности такта добавляют время установки и задержку

распространения сигналов. В предельном случае

длительность такта можно уменьшить до суммы накладных

расходов и перекоса сигналов синхронизации, однако

при этом в такте не останется времени для выполнения

полезной работы по преобразованию информации.

19.

Конвейерные вычисленияВ качестве примера рассмотрим неконвейерную машину с

пятью этапами выполнения операций, которые имеют

длительность 50, 50, 60, 50 и 50 нс соответственно. Пусть

накладные расходы на организацию конвейерной

обработки составляют 5 нс. Тогда среднее время

выполнения команды в неконвейерной машине будет

равно 260 нс. Если же используется конвейерная

организация, длительность такта будет равна длительности

самого медленного этапа обработки плюс накладные

расходы, т.е. 65 нс. Это время соответствует среднему

времени выполнения команды в конвейере.

Конвейеризация эффективна только тогда, когда загрузка

конвейера близка к полной, а скорость подачи новых

команд и операндов соответствует максимальной

производительности

конвейера.

Если

произойдет

задержка, то параллельно будет выполняться меньше

операций и суммарная производительность снизится.

Такие задержки могут возникать в результате возникновения

конфликтных ситуаций. В следующих разделах будут

рассмотрены различные типы конфликтов, возникающие

при выполнении команд в конвейере, и способы их

разрешения.

20.

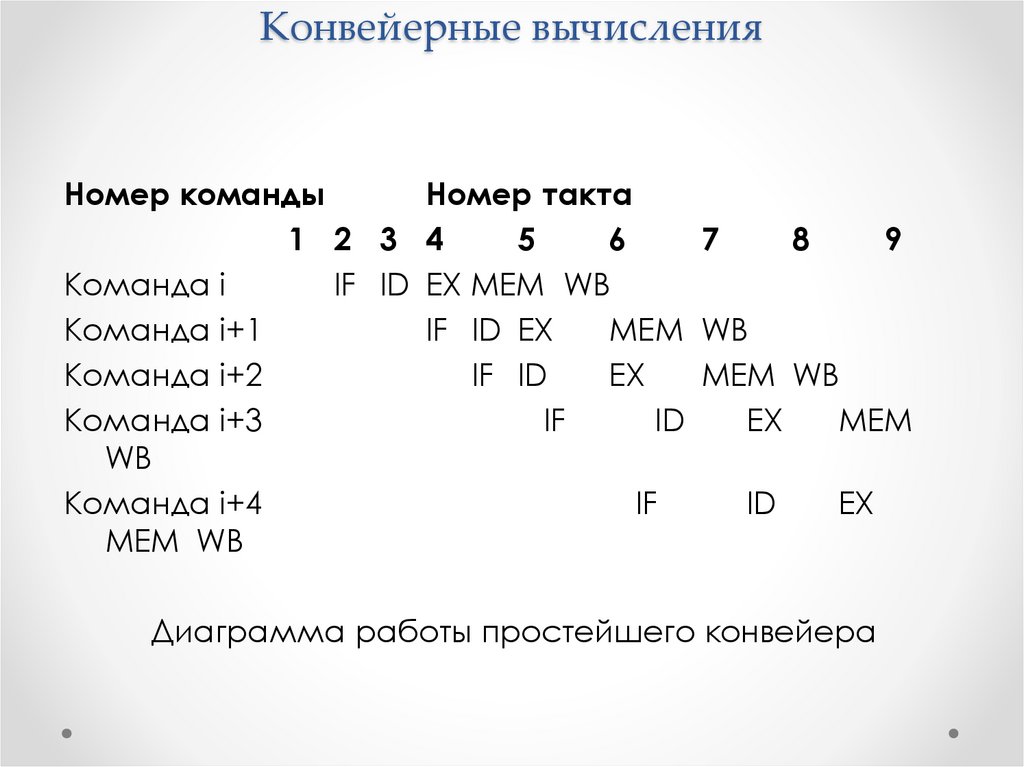

Конвейерные вычисленияНомер команды

Номер такта

1 2 3 4

5

6

7

8

9

Команда i

IF ID EX MEM WB

Команда i+1

IF ID EX

MEM WB

Команда i+2

IF ID

EX

MEM WB

Команда i+3

IF

ID

EX

MEM

WB

Команда i+4

IF

ID

EX

MEM WB

Диаграмма работы простейшего конвейера

21.

Конвейерные вычисленияЭффект конвейеризации при выполнении 3-х команд четырехкратное ускорение

22.

Конвейерные вычисленияПри реализации конвейерной обработки возникают ситуации,

которые препятствуют выполнению очередной команды из

потока команд в предназначенном для нее такте. Такие

ситуации называются конфликтами. Существуют три класса

конфликтов:

Структурные конфликты, возникают из-за конфликтов по

ресурсам,

когда

аппаратные

средства

не

могут

поддерживать все возможные комбинации команд в режиме

одновременного выполнения с совмещением.

Конфликты по данным, возникающие в случае, когда

выполнение одной команды зависит от результата выполнения

предыдущей команды.

Конфликты

по

управлению,

которые

возникают

при

конвейеризации команд переходов и других команд, которые

изменяют значение счетчика команд.

Конфликты

в

конвейере

приводят

к

необходимости

приостановки

выполнения

команд

(pipeline

stall).

В

простейших конвейерах, если приостанавливается какаялибо команда, то все следующие за ней команды также

приостанавливаются.

Команды,

предшествующие

приостановленной, могут продолжать выполняться, но во

время приостановки не выбирается ни одна новая команда.

23.

Структурные конфликты и способы их минимизацииСовмещенный режим выполнения команд в общем случае

требует конвейеризации функциональных устройств и

дублирования ресурсов для разрешения всех возможных

комбинаций команд в конвейере. Если какая-нибудь

комбинация команд не может быть принята из-за

конфликта по ресурсам, то говорят, что в машине имеется

структурный конфликт. Примером машин, в которых

возможно появление структурных конфликтов, являются

машины

с

не

полностью

конвейерными

функциональными устройствами. Время работы такого

устройства

может

составлять

несколько

тактов

синхронизации конвейера, последовательные команды не

могут поступать в него в каждом такте.

Другая возможность появления структурных конфликтов

связана с недостаточным дублированием некоторых

ресурсов, что препятствует выполнению произвольной

последовательности команд в конвейере без его

приостановки.

Когда

последовательность

команд

наталкивается

на

такой

конфликт,

конвейер

приостанавливает выполнение одной из команд до тех

пор, пока не станет доступным требуемое устройство.

24.

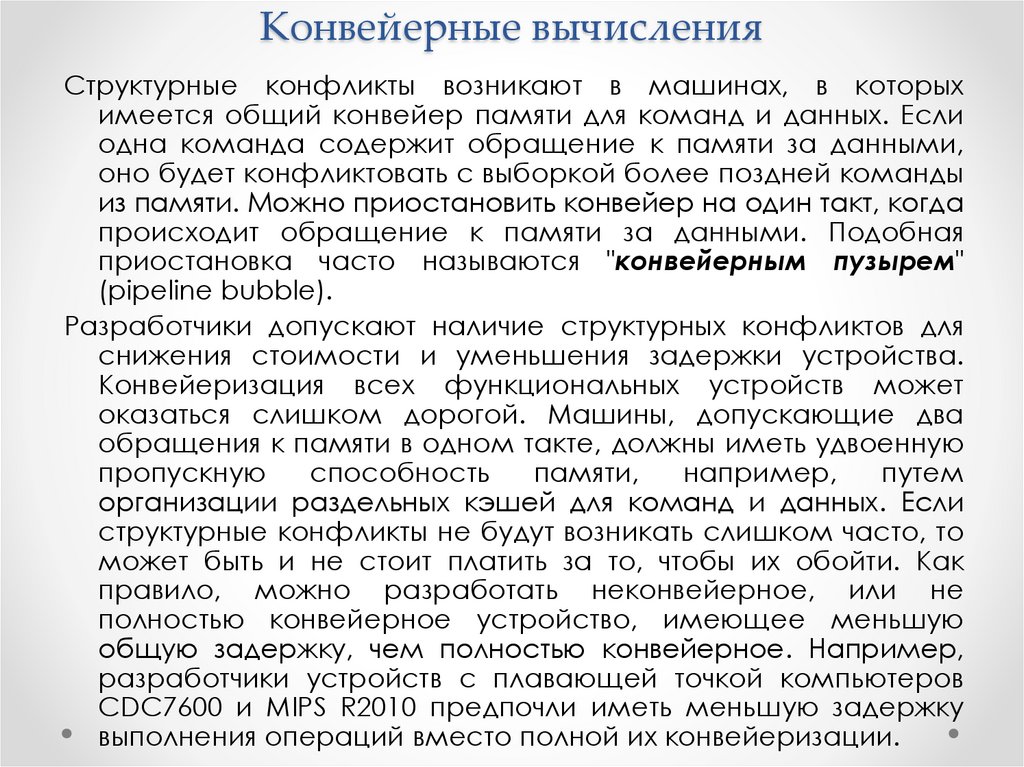

Конвейерные вычисленияСтруктурные конфликты возникают в машинах, в которых

имеется общий конвейер памяти для команд и данных. Если

одна команда содержит обращение к памяти за данными,

оно будет конфликтовать с выборкой более поздней команды

из памяти. Можно приостановить конвейер на один такт, когда

происходит обращение к памяти за данными. Подобная

приостановка часто называются "конвейерным пузырем"

(pipeline bubble).

Разработчики допускают наличие структурных конфликтов для

снижения стоимости и уменьшения задержки устройства.

Конвейеризация всех функциональных устройств может

оказаться слишком дорогой. Машины, допускающие два

обращения к памяти в одном такте, должны иметь удвоенную

пропускную

способность

памяти,

например,

путем

организации раздельных кэшей для команд и данных. Если

структурные конфликты не будут возникать слишком часто, то

может быть и не стоит платить за то, чтобы их обойти. Как

правило, можно разработать неконвейерное, или не

полностью конвейерное устройство, имеющее меньшую

общую задержку, чем полностью конвейерное. Например,

разработчики устройств с плавающей точкой компьютеров

CDC7600 и MIPS R2010 предпочли иметь меньшую задержку

выполнения операций вместо полной их конвейеризации.

25.

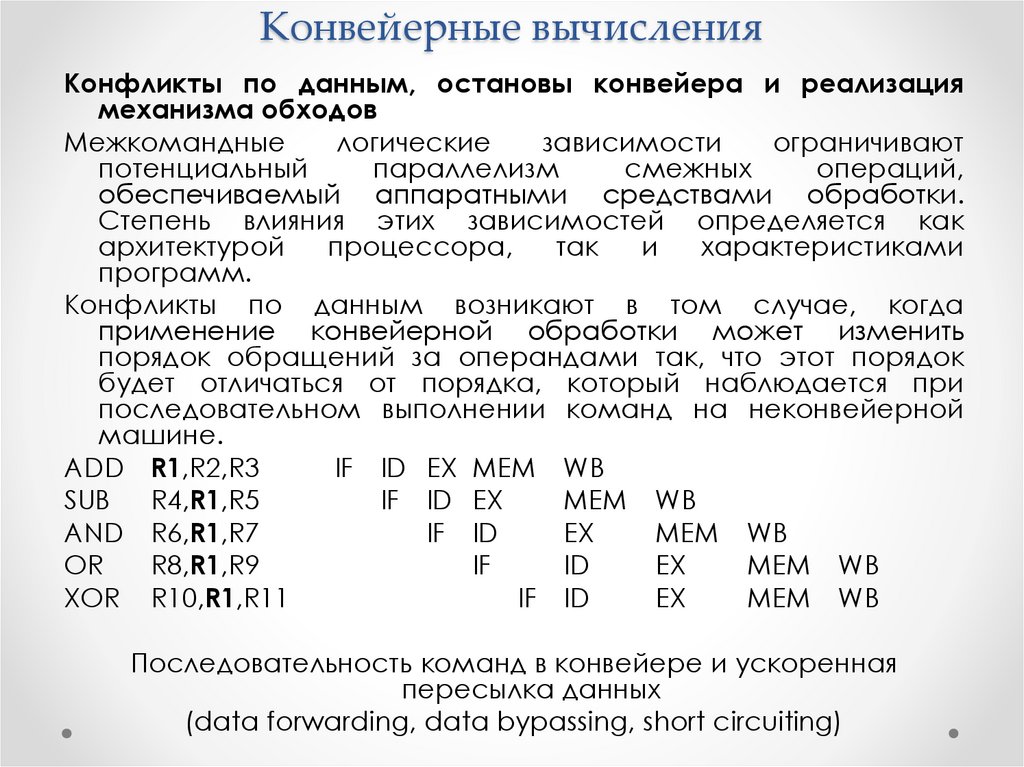

Конвейерные вычисленияКонфликты по данным, остановы конвейера и реализация

механизма обходов

Межкомандные

логические

зависимости

ограничивают

потенциальный

параллелизм

смежных

операций,

обеспечиваемый аппаратными средствами обработки.

Степень влияния этих зависимостей определяется как

архитектурой

процессора,

так

и

характеристиками

программ.

Конфликты по данным возникают в том случае, когда

применение конвейерной обработки может изменить

порядок обращений за операндами так, что этот порядок

будет отличаться от порядка, который наблюдается при

последовательном выполнении команд на неконвейерной

машине.

ADD R1,R2,R3

IF ID EX MEM WB

SUB

R4,R1,R5

IF ID EX

MEM WB

AND R6,R1,R7

IF ID

EX

MEM WB

OR

R8,R1,R9

IF

ID

EX

MEM WB

XOR R10,R1,R11

IF ID

EX

MEM WB

Последовательность команд в конвейере и ускоренная

пересылка данных

(data forwarding, data bypassing, short circuiting)

26.

Конвейерные вычисленияADD

R1,R2,R3

SUB

R4,R1,R5

AND

R6,R1,R7

OR

R8,R1,R9

XOR

R10,R1,R11

IF

ID EX MEM

R

IF ID EX

R

IF ID

R

IF

WB

W

MEM

IF

ID

EX

ID

R

WB

W

MEM

EX

EX

R

WB

W

MEM

WB

W

MEM WB

W

Совмещение чтения и записи регистров в одном такте

В этом примере все команды, следующие за командой ADD,

используют результат ее выполнения. Команда ADD записывает

результат в регистр R1, а команда SUB читает это значение. Если не

предпринять никаких мер для того, чтобы предотвратить этот

конфликт, команда SUB прочитает неправильное значение и

попытается его использовать. Если произойдет прерывание между

командами ADD и SUB, то команда ADD завершится, и значение R1 в

этой

точке

будет

соответствовать

результату

ADD.

Такое

непрогнозируемое поведение очевидно неприемлемо.

27.

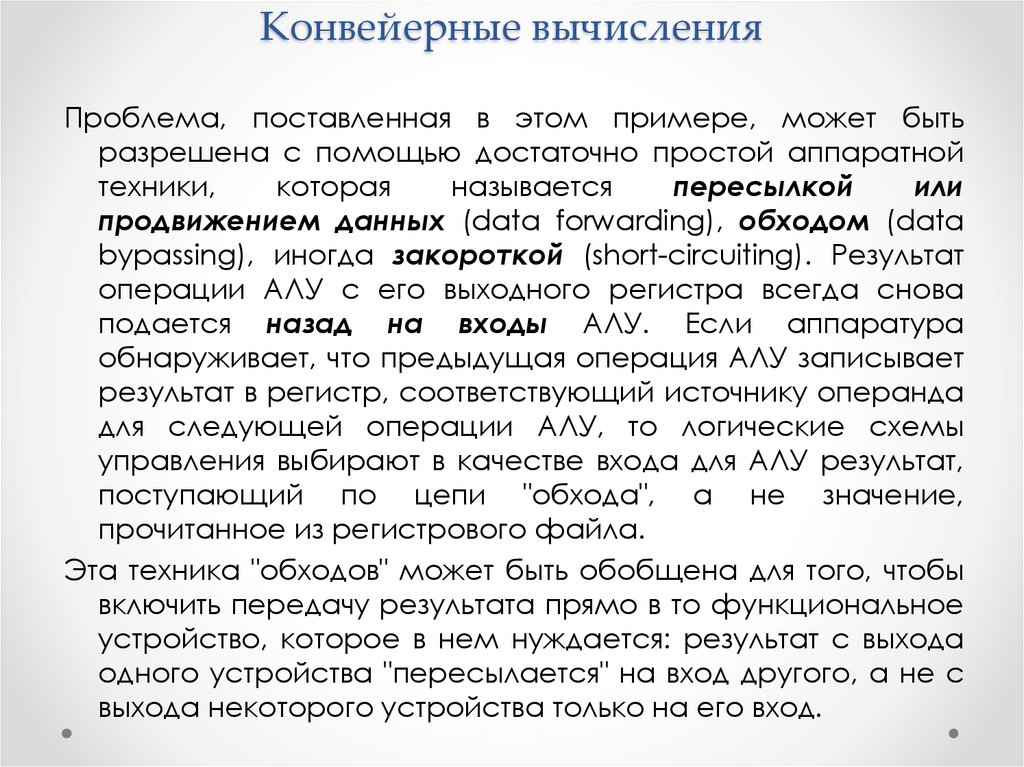

Конвейерные вычисленияПроблема, поставленная в этом примере, может быть

разрешена с помощью достаточно простой аппаратной

техники,

которая

называется

пересылкой

или

продвижением данных (data forwarding), обходом (data

bypassing), иногда закороткой (short-circuiting). Результат

операции АЛУ с его выходного регистра всегда снова

подается назад на входы АЛУ. Если аппаратура

обнаруживает, что предыдущая операция АЛУ записывает

результат в регистр, соответствующий источнику операнда

для следующей операции АЛУ, то логические схемы

управления выбирают в качестве входа для АЛУ результат,

поступающий по цепи "обхода", а не значение,

прочитанное из регистрового файла.

Эта техника "обходов" может быть обобщена для того, чтобы

включить передачу результата прямо в то функциональное

устройство, которое в нем нуждается: результат с выхода

одного устройства "пересылается" на вход другого, а не с

выхода некоторого устройства только на его вход.

28.

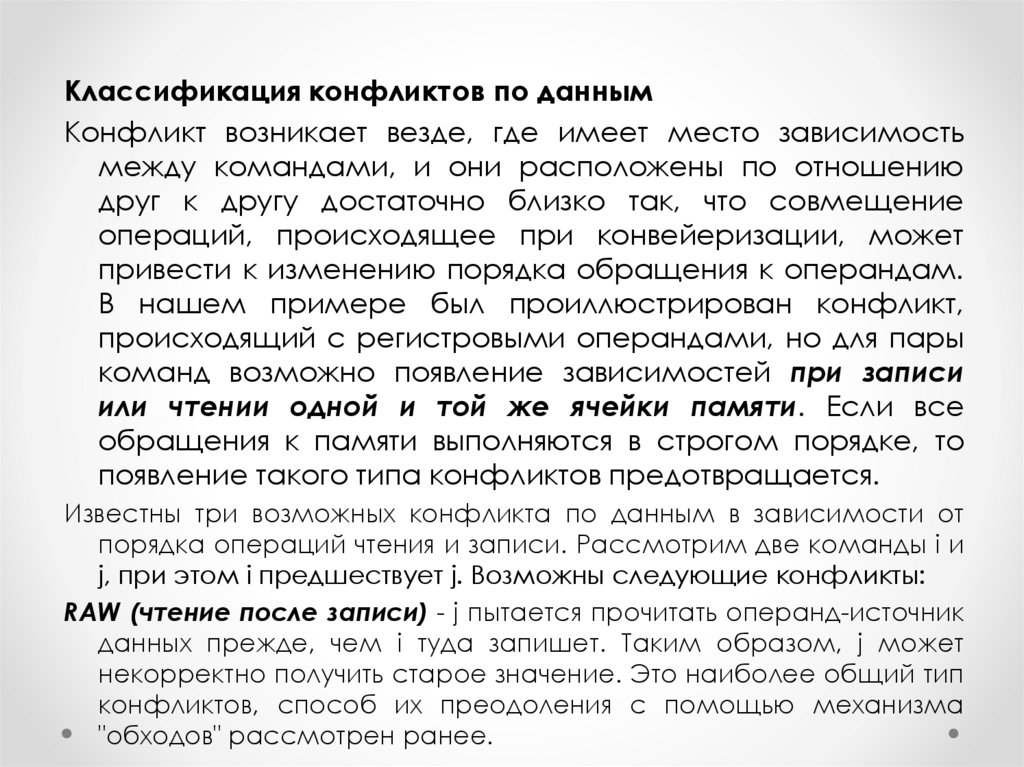

Классификация конфликтов по даннымКонфликт возникает везде, где имеет место зависимость

между командами, и они расположены по отношению

друг к другу достаточно близко так, что совмещение

операций, происходящее при конвейеризации, может

привести к изменению порядка обращения к операндам.

В нашем примере был проиллюстрирован конфликт,

происходящий с регистровыми операндами, но для пары

команд возможно появление зависимостей при записи

или чтении одной и той же ячейки памяти. Если все

обращения к памяти выполняются в строгом порядке, то

появление такого типа конфликтов предотвращается.

Известны три возможных конфликта по данным в зависимости от

порядка операций чтения и записи. Рассмотрим две команды i и

j, при этом i предшествует j. Возможны следующие конфликты:

RAW (чтение после записи) - j пытается прочитать операнд-источник

данных прежде, чем i туда запишет. Таким образом, j может

некорректно получить старое значение. Это наиболее общий тип

конфликтов, способ их преодоления с помощью механизма

"обходов" рассмотрен ранее.

29.

Конвейерные вычисленияWAR (запись после чтения) - j пытается записать результат в

приемник прежде, чем он считывается оттуда командой i,

так что i может некорректно получить новое значение. Этот

тип конфликтов как правило не возникает в системах с

централизованным

управлением

потоком

команд,

обеспечивающих выполнение команд в порядке их

поступления, так как последующая запись всегда

выполняется позже, чем предшествующее считывание.

Особенно часто конфликты такого рода могут возникать в

системах, допускающих выполнение команд не в порядке

их расположения в программном коде.

WAW (запись после записи) - j пытается записать операнд

прежде, чем будет записан результат команды i, т.е.

записи заканчиваются в неверном порядке, оставляя в

приемнике значение, записанное командой i, а не j. Этот

тип конфликтов присутствует только в конвейерах, которые

выполняют запись со многих ступеней (или позволяют

команде выполняться даже в случае, когда предыдущая

приостановлена).

30.

Конвейерные вычисленияКонфликты по данным, приводящие к приостановке конвейера

Не все потенциальные конфликты по данным могут обрабатываться

с помощью механизма "обходов":

Команда

IF

LW R1,32(R6)

ADD R4,R1,R7

SUB R5,R1,R8

AND R6,R1,R7

WB

ID EX MEM

IF ID EX

IF ID

IF

WB

MEM

stall

stall

stall

WB

EX

ID

IF

MEM

EX

ID

WB

MEM

EX

WB

MEM

Последовательность команд с приостановкой конвейера

Этот случай отличается от последовательности подряд идущих

команд АЛУ. Команда загрузки (LW) регистра R1 из памяти имеет

задержку, которая не может быть устранена обычной

"пересылкой". Вместо этого нам нужна дополнительная

аппаратура, называемая аппаратурой внутренних блокировок

конвейера (pipeline interlook), чтобы обеспечить корректное

выполнение примера. Аппаратура приостанавливает конвейер,

начиная с команды, которая хочет использовать данные в то

время, когда предыдущая команда, результат которой является

операндом для нашей, вырабатывает этот результат. Эта

аппаратура вызывает приостановку конвейера или появление

31.

Конвейерные вычисленияДля

устранения конфликтов по данным используется

специальная методика планирования компилятора.

Многие современные компиляторы используют технику

планирования команд для улучшения производительности

конвейера. В простейшем алгоритме компилятор просто

планирует распределение команд в одном и том же

базовом блоке. Базовый блок представляет собой

линейный участок последовательности программного

кода, в котором отсутствуют команды перехода, за

исключением начала и конца участка (переходы внутрь

этого участка тоже должны отсутствовать). Планирование

такой

последовательности

команд

осуществляется

достаточно просто, поскольку компилятор знает, что

каждая команда в блоке будет выполняться, если

выполняется первая из них, и можно просто построить

граф зависимостей этих команд и упорядочить их так,

чтобы минимизировать приостановки конвейера. Для

простых конвейеров стратегия планирования на основе

базовых блоков вполне удовлетворительна. Однако когда

конвейеризация

становится

более

интенсивной

и

действительные задержки конвейера растут, требуются

более сложные алгоритмы планирования.

32.

Конвейерные вычисленияСуществуют аппаратные методы, позволяющие изменить

порядок выполнения команд программы так, чтобы

минимизировать приостановки конвейера. Эти методы

получили общее название методов динамической

оптимизации (в англоязычной литературе в последнее

время часто применяются также термины "out-of-order

execution" - неупорядоченное выполнение и "out-of-order

issue" - неупорядоченная выдача). Основными средствами

динамической оптимизации являются:

Размещение схемы обнаружения конфликтов в возможно

более низкой точке конвейера команд так, чтобы

позволить команде продвигаться по конвейеру до тех пор,

пока ей реально не потребуется операнд, являющийся

также результатом логически более ранней, но еще не

завершившейся команды. Альтернативным подходом

является централизованное обнаружение конфликтов на

одной из ранних ступеней конвейера.

33.

Буферизация команд, ожидающих разрешения конфликта, ивыдача последующих, логически не связанных команд, в "обход"

буфера. В этом случае команды могут выдаваться на

выполнение не в том порядке, в котором они расположены в

программе, однако аппаратура обнаружения и устранения

конфликтов

между

логически

связанными

командами

обеспечивает получение результатов в соответствии с заданной

программой.

Организация коммутирующих магистралей, обеспечивающая

засылку результата операции непосредственно в буфер,

хранящий логически зависимую команду, задержанную из-за

конфликта, или непосредственно на вход функционального

устройства до того, как этот результат будет записан в

регистровый файл или в память (short-circuiting, data forwarding,

data bypassing - методы, которые были рассмотрены ранее).

Метод переименования регистров (register renaming). Получил свое

название от широко применяющегося в компиляторах метода

переименования

метода

размещения

данных,

способствующего сокращению числа зависимостей и тем

самым увеличению производительности при отображении

необходимых исходной программе объектов (например,

переменных) на аппаратные ресурсы (например, ячейки памяти

34.

Технологии виртуализации вычисленийВиртуализацией в ИТ называют процесс логического замещения

аппаратных ресурсов их программными моделями, с которыми

взаимодействует операционная система и прикладные задачи, что

позволяет уменьшить взаимовлияние различных программ друг на

друга через аппаратные средства и в большей степени сбалансировать

загрузку вычислительных мощностей.

На аппаратных ресурсах одного компьютера может быть развёрнуто

несколько виртуальных машин со своими дисками, памятью,

операционными системами и проч. Это упрощает управление

изменениями в системе за счет их локализации в том или ином слое

изолированных с помощью виртуализации ресурсов.

Типы виртуализации Microsoft:

Виртуализация представлений позволяет отделить процесс обработки

информации от графического интерфейса приложения и системы

ввода с клавиатуры и мыши.

Виртуализация приложения позволяет создать изолированную среду для

работы приложения, включающую специфические для приложения

библиотеки, реестр и другие системные элементы.

Виртуализация ПК (машинная виртуализация)

предоставляет

пользователям виртуальные машины: локально — на ПК и

централизованно — на сервере.

35.

Технологии виртуализации вычисленийВиртуализация ПК:

36.

Технологии виртуализацииВиртуализация представлений (рабочих мест) Виртуализация

представлений подразумевает эмуляцию интерфейса пользователя.

Т.е. пользователь видит приложение и работает с ним на своём

терминале, хотя на самом деле приложение выполняется на

удалённом сервере, а пользователю передаётся лишь картинка

удалённого приложения. В зависимости от режима работы

пользователь может видеть удалённый рабочий стол и запущенное на

нём приложение, либо только само окно приложения.

37.

Технологии виртуализации вычисленийВиртуализация серверов:

38.

Blade-серверыПо сравнению с обычными серверами при сравнимой

производительности Blade-серверы занимают в два раза меньше

места, потребляют в три раза меньше энергии и обходятся в

четыре раза дешевле

Blade-сервер - модульная одноплатная компьютерная система,

включающая процессор и память. Лезвия вставляются в

специальное шасси (или полку) с объединительной панелью

(backplane), обеспечивающей им подключение к сети и подачу

электропитания. Это шасси выполнено в конструктиве для

установки в стандартную 19-дюймовую стойку и в зависимости от

модели и производителя, занимает в ней 3U, 6U или 10U (один U unit, или монтажная единица, равен 1,75 дюйма). За счет общего

использования таких компонентов, как источники питания, сетевые

карты и жесткие диски, Blade-серверы обеспечивают более

высокую плотность размещения вычислительной мощности в

стойке по сравнению с обычными тонкими серверами высотой 1U и

2U

39.

Blade-серверы40.

Архитектура памяти вычислительных системВ наиболее развитой иерархии памяти ЭВМ можно выделить

следующие уровни.

Регистровые ЗУ — находятся внутри процессора.

Кэш-память — быстродействующая память, которая может

находиться как внутри, так и вне процессора. Она

предназначена

для

хранения

копий

информации,

находящейся в более медленной основной памяти, програмно

не доступна.

Оперативная память (RAM — Random Access Memory) или

оперативное запоминающее устройство (ОЗУ) — часть

основной памяти ЭВМ, в которой во время работы компьютера

хранится выполняемый машинный код (программы), а также

входные, выходные и промежуточные данные, обрабатываемые

процессором.

Постоянная память (ROM - Read Only Memory) или ПЗУ - вторая

часть основной памяти ЭВМ, предназначенной для хранения

редко изменяемой информации, например, кодов команд,

тестовых программ.

Специализированные виды памяти, например, видеопамять,

предназначенная для хранения информации, отображаемой

на экране дисплея и др.

Внешняя память — магнитные и оптические диски, FLASH-память,

предназначенные

для

хранения

больших

объёмов

информации.

41.

Архитектура сверхоперативной памятиРегистровые ЗУ – размещаются внутри процессора для

обеспечения промежуточного хранения информации в

ходе выполнения команды и её результатов: регистры

адреса и текущей команды, индекса, признаков результата,

счётчик команд, указатель стека, аккумулятор, буферы

адреса и данных, общего назначения. Подробно их

назначение обсуждалось в архитектуре процессора.

В общем пространстве оперативной памяти они не

отображаются,

а

имеют

собственные

номера

и

адресацию. Разрядность регистров в зависимости от

назначения может быть разной: регистр адреса имеет

разрядность адресной шины, регистр команды может

иметь длину самой длинной из принятых в системе команд,

регистры данных обычно имеют разрядность шины данных. В

зависимости

от

версии

ассемблера

могут

быть

программно доступны отдельные байты регистров.

При создании конвейера для каждой его ступени основные

регистры дублируются, и их общее количество может быть

довольно значительным (при конвейере в 21 ступень и 20

регистрах на 1 ступень имеем 420 штук, для 64-разрядной

системы = 3360 байт).

42.

Архитектура сверхоперативной памятиОсновная идея кэширования: когда нужно обратиться в память для

чтения или записи данных, сначала проверяем, доступна ли их

копия в кэше. В случае успеха операция использует кэш, что

значительно быстрее использования основной памяти.

Данные между кэшем и основной памятью передаются блоками

фиксированного размера - линиями кэша (cache line) или

блоками кэша.

Большинство современных микропроцессоров имеют три

независимых кэша: кэш инструкций для ускорения загрузки

машинного кода, кэш данных для ускорения чтения и записи

данных и буфер ассоциативной трансляции (TLB) для

ускорения трансляции виртуальных (логических) адресов в

физические, как для инструкций, так и для данных. Кэш данных

часто реализуется в виде многоуровневого кэша (L1, L2, L3).

Перед доступом процессора в память производится сравнение

адреса запроса со значениями всех тегов кэша, в которых эти

данные могут храниться. Случай совпадения с тегом какойлибо кэш-линии называется попаданием в кэш (cache hit),

обратный случай - кэш-промах (cache miss). Отношение

количества попаданий в кэш к общему количеству запросов к

памяти называют рейтингом попаданий (hit rate), это мера

эффективности кэша для выбранного алгоритма или

программы.

43.

Размер кэш-линии может различаться в разных процессорах,но для большинства x86-процессоров он составляет 64

байта. Размер кэш-линии обычно больше размера данных,

к которому возможен доступ из одной машинной команды

(типичные размеры от 1 до 16 байт). Каждая группа данных в

памяти размером в 1 кэш-линию имеет порядковый номер.

Для основной памяти этот номер является адресом памяти

с отброшенными 6-ю младшими битами. В кэше каждой

кэш-линии дополнительно ставится в соответствие тег,

который является адресом продублированных в этой кэшлинии данных в основной памяти.

44.

Архитектура сверхоперативной памятиВ случае промаха в кэше выделяется новая запись, в тег которой

записывается адрес текущего запроса, а в саму кэш-линию —

данные из памяти после их прочтения либо данные для записи в

память. Промахи по чтению задерживают исполнение,

поскольку они требуют запроса данных в более медленной

основной памяти. Промахи по записи могут не давать

задержку, поскольку записываемые данные сразу могут быть

сохранены в кэше, а запись их в основную память можно

произвести в фоновом режиме. Кэши инструкций и данных

могут быть разделены для увеличения производительности (в

Гарвардской архитектуре) или объединены для упрощения

аппаратной реализации.

Для добавления данных в кэш после кэш-промаха может

потребоваться вытеснение (evict) ранее записанных данных.

Для выбора замещаемой строки кэша используется политика

замещения (replacement policy). Основной проблемой

является предсказание, какая строка вероятнее всего не

потребуется для последующих операций. Качественные

предсказания сложны, и аппаратные кэши используют простые

правила, такие, как LRU. Пометка некоторых областей памяти

как

некэшируемых

(non

cacheable)

улучшает

производительность за счёт запрета кэширования редко

используемых данных. Промахи для такой памяти не создают

копию данных в кэше.

45.

Архитектура сверхоперативной памятиПри записи данных в кэш должен существовать определенный

момент времени, когда они будут записаны в основную память.

Это время контролируется политикой записи (write policy). Для

кэшей со сквозной записью (write-through) любая запись в кэш

приводит к немедленной записи в память. Другой тип кэшей,

обратная запись write-back (copy-back), откладывает запись на

более позднее время. В таких кэшах отслеживается состояние

кэш-линеек ещё не сброшенных в память (пометка битом

«грязный», dirty). Запись в память производится при вытеснении

подобной строки из кэша. Таким образом, промах в кэше,

использующем политику обратной записи, может потребовать

двух операций доступа в память, один для сброса состояния

старой строки и другой — для чтения новых данных.

Данные в основной памяти могут изменяться не только

процессором, но и периферией, использующей прямой

доступ

к

памяти,

или

другими

процессорами

в

многопроцессорной системе. Изменение данных приводит к

устареванию их копии в кэше (состояние stale). В другой

реализации, когда один процессор изменяет данные в кэше,

копии этих данных в кэшах других процессоров будут

помечены как stale. Для поддержания содержимого нескольких

кэшей в актуальном состоянии используется специальный

протокол кэш когерентности.

46.

Архитектура сверхоперативной памятиТипичная структура записи в кэше:

Блок данных

тег

бит актуальности

Блок данных (кэш-линия) содержит непосредственную копию

данных из основной памяти. Бит актуальности означает, что

данная запись содержит актуальную (самую свежую)

копию. Вместо бита актуальности может использоваться

счётчик возраста строки Строка, к которой обращались в

последнюю очередь, имеет возраст 0, а строка с самым

свежим

обращением

—

возраст,

определяемый

разрядностью счётчика.

Структура адреса:

Тег

индекс

смещение

Адрес памяти разделяется (от старших бит к младшим) на Тег,

индекс и смещение. Длина поля индекса равна

log2(cache\rows) бит и соответствует ряду (строке) кэша,

используемой для записи.

Длина смещения равна log2(data\blocks)

47.

Архитектура сверхоперативной памятиПонятие ассоциативности кэша

Отображение оперативной памяти на кэшпамять может

выполняться по разным правилам. Если любая строка

оперативной памяти может быть записана в любую строку

кэшпамяти, такая кэшпамять называется полностью

ассоциативной (fully associative).

48.

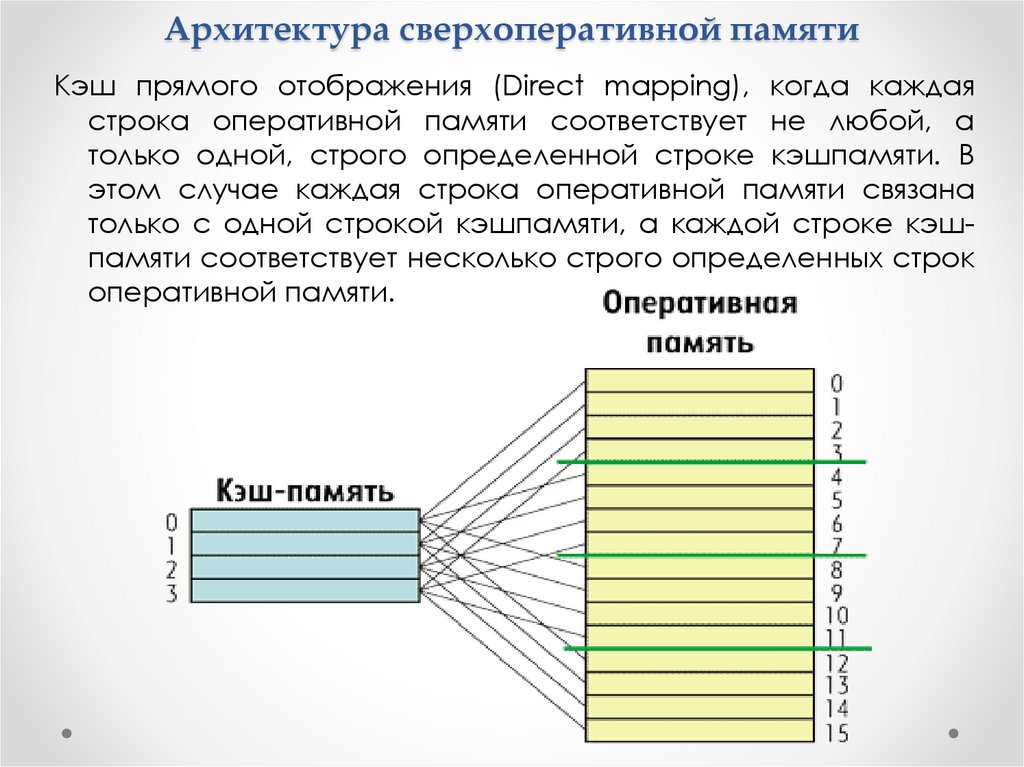

Архитектура сверхоперативной памятиКэш прямого отображения (Direct mapping), когда каждая

строка оперативной памяти соответствует не любой, а

только одной, строго определенной строке кэшпамяти. В

этом случае каждая строка оперативной памяти связана

только с одной строкой кэшпамяти, а каждой строке кэшпамяти соответствует несколько строго определенных строк

оперативной памяти.

49.

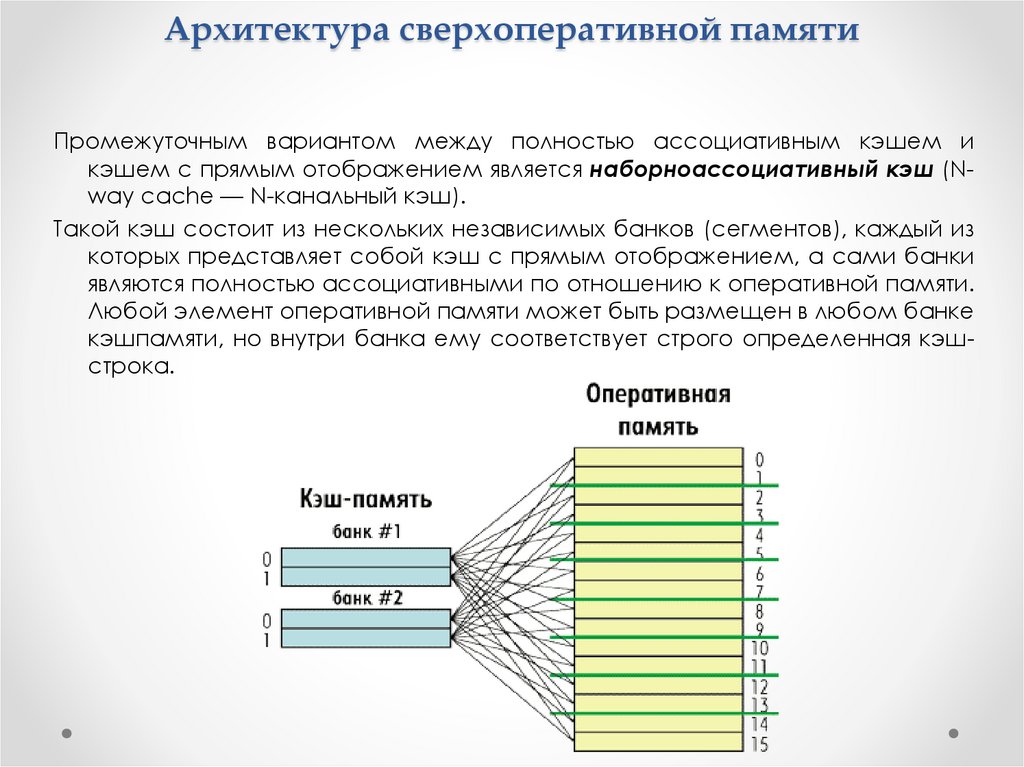

Архитектура сверхоперативной памятиПромежуточным вариантом между полностью ассоциативным кэшем и

кэшем с прямым отображением является наборноассоциативный кэш (Nway cache — N-канальный кэш).

Такой кэш состоит из нескольких независимых банков (сегментов), каждый из

которых представляет собой кэш с прямым отображением, а сами банки

являются полностью ассоциативными по отношению к оперативной памяти.

Любой элемент оперативной памяти может быть размещен в любом банке

кэшпамяти, но внутри банка ему соответствует строго определенная кэшстрока.

50.

Архитектура сверхоперативной памятиАссоциативность

является

компромиссом.

Проверка

большего числа записей требует больше энергии, площади

чипа, и, потенциально, времени. Если бы существовало 10

мест, в которые алгоритм вытеснения мог бы отобразить

место в памяти, тогда проверка наличия этого места в кэше

потребовала бы просмотра 10 записей в кэше. С другой

стороны, кэши с высокой ассоциативностью подвержены

меньшему количеству промахов, и процессор тратит

меньше времени на чтения из медленной основной памяти.

Существует эмпирическое наблюдение, что удвоение

ассоциативности (от прямого отображения к 2-канальной

или от 2- к 4-канальной) имеет примерно такое же влияние

на интенсивность попаданий (hit rate), что и удвоение

размера кэша. Увеличение ассоциативности свыше 4

каналов приносит меньший эффект для уменьшения

количества промахов (miss rate) и обычно производится по

другим

причинам,

например,

из-за

пересечения

виртуальных адресов.

51.

Архитектура сверхоперативной памятиВ порядке ухудшения (увеличения длительности проверки на

попадание)

и

улучшения

(уменьшения

количества

промахов):

кэш прямого отображения (direct mapped cache) —

наилучшее время попадания и, соответственно, лучший

вариант для больших кэшей;

2-канальный множественно-ассоциативный кэш 2-way set

associative cache;

2-канальный skewed ассоциативный кэш (the best tradeoff for

…. caches whose sizes are in the range 4K-8K bytes);

4-канальный множественно-ассоциативный кэш (4-way set

associative cache);

полностью ассоциативный кэш, fully associative cache —

наилучший (самый низкий) процент промахов (miss rate) и

лучший вариант при чрезвычайно высоких затратах при

промахе (miss penalty).

52.

Архитектура сверхоперативной памятиМногоуровневая организация кэша

Все современные процессоры имеют как минимум

двухуровневую структуру кэшпамяти, а большинство

процессоров Intel — трехуровневую кэшпамять. При этом

различают кэш первого уровня (обозначается L1), кэш

второго уровня (L2) и кэш третьего уровня (L3). Чем больше

размер кэша, тем ниже его скорость.

Кроме того, кэши разных уровней в процессоре выполняют

различные задачи. Самый быстрый и маленький кэш

первого уровня L1 всегда делится на кэш данных (L1D) и кэш

команд или инструкций (L1I). Кэш L1 всегда принадлежит

только конкретному ядру процессора.

Кэш второго уровня L2 является унифицированным (содержит

данные и команды). Кэш L2 всегда больше, чем кэш L1, но

медленнее его. В случае многоядерных процессоров кэш

L2 также принадлежит конкретному ядру процессора.

Кэш L3 является самым большим и медленным и разделяется

между всеми ядрами процессора (в архитектуре

процессоров Intel).

53.

Архитектура сверхоперативной памятиВзаимодействие между кэшами разных уровней.

Двухуровневая система кэша строится на базе одной из двух

архитектур: включающей (inclusive), и исключающей (exclusive).

Кэш L2 по включающей архитектуре дублирует содержимое

кэша L1, эффективная емкость кэшпамяти равна емкости

кэша L2.

Кэш L2 по исключающей архитектуре никогда не дублирует кэш

L1, эффективная емкость равна суммарной емкости кэшей L1

и L2.

Включающая архитектура. Если при полностью заполненном

кэше L2 процессор пытается загрузить еще одну кэшстроку, то

обнаружив, что все кэшстроки заняты, кэш L2 избавляется от

наименее ценной из них, стремясь при этом найти линейку,

которая еще не была модифицирована (ее придется

выгружать в оперативную память).

Затем кэш L2 передает полученные из памяти данные кэшу L1.

Если кэш первого уровня также заполнен, ему приходится

избавляться от одной из кэшстрок по тому же сценарию.

Загруженная порция данных присутствует и в кэше L1, и в кэше

L2.

В исключающей архитектуре, кэш L1 никогда не уничтожает кэшстроки при нехватке места, они вытесняются в кэш L2 на то

место, где находилась только что переданная кэшу L1 кэшстрока.

54.

Архитектура сверхоперативной памятиИерархия кэшпамяти в микроархитектуре Intel Core

Кэшпамять первого уровня L1 делится на 8-канальный 32килобайтный кэш данных (L1D) и 4-канальный 32-килобайтный

кэш инструкций (L1I).

Каждое ядро процессора имеет унифицированный (единый для

инструкций и данных) кэш второго уровня (L2) размером 256

Кбайт. Кэш L2 является также 8-канальным, а размер строки

кэша составляет 64 байт.

Кэш третьего уровня (L3) разделяется между всеми ядрами

процессора. Его размер зависит от количества ядер

процессора. Кэш L3 является 16-канальным.

Кэш L3 — включающий по своей архитектуре по отношению к

кэшам L1 и L2, то есть в кэше L3 всегда дублируется

содержимое кэшей L1 и L2. А вот кэши L1 и L2 не являются ни

включающими, ни исключающими по отношению друг к другу,

то есть кэш L2 может содержать, а может и не содержать

копию данных кэша L1.

Применение именно включающего кэша L3 имеет свои

преимущества по сравнению с исключающей архитектурой.

Предположим сначала, что ядро процессора Core 0, обнаружив,

что требуемых ему данных нет ни в кэше L1, ни в кэше L2,

обращается к кэшу L3. Если необходимых данных нет также и в

кэше L3, инициируется обращение к основной памяти.

55.

Архитектура сверхоперативной памятиЕсли же требуемые ядру Core 0 данные обнаруживаются в

кэше L3, то при исключающей архитектуре кэша больше не

нужно выполнять никаких действий, поскольку данная

архитектура гарантирует их отсутствие в кэшах L1 и L2 ядер

Core 1, Core 2 и Core 3.

Однако при включающей архитектуре кэша L3 наличие

требуемых данных в кэше L3 означает, что они также

содержатся в какомнибудь из кэшей ядер Core 1, Core 2 или

Core 3. Но в этом случае не нужна дополнительная

проверка кэшей L1 и L2 всех остальных ядер. Достигается

это тем, что в теге кэшстроки L3-кэша записывается, к

какому из ядер принадлежат данные, поэтому достаточно

лишь прочитать содержимое этого тега.

56.

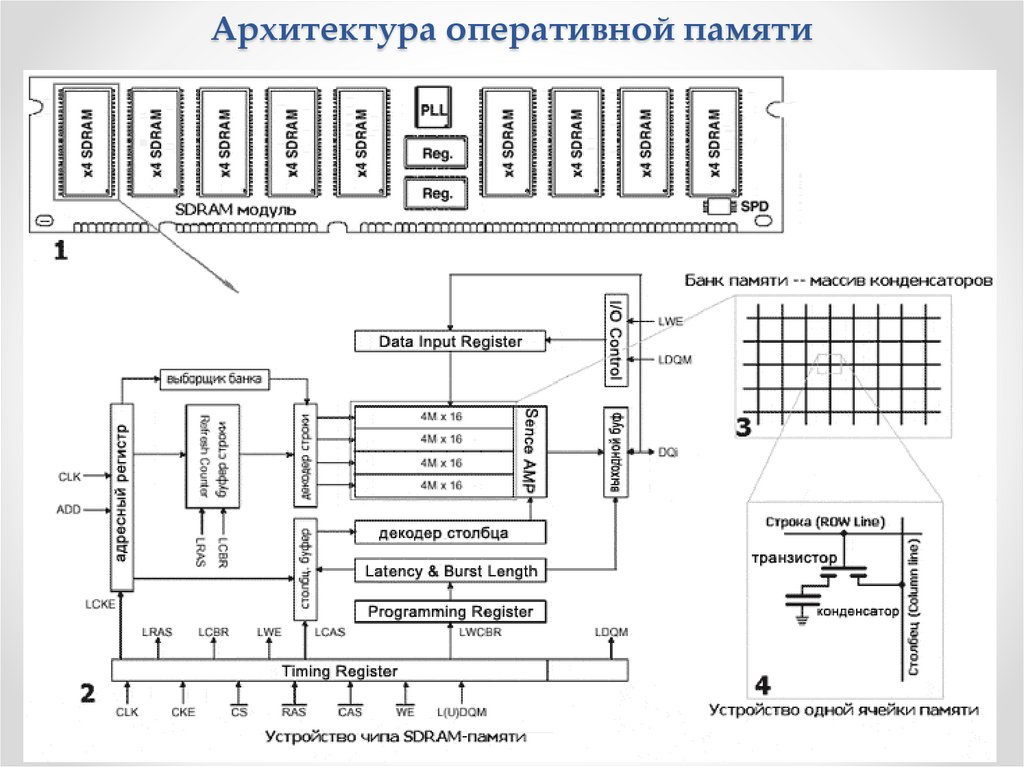

Архитектура оперативной памятиЗУ адресного типа состоят из трёх основных блоков:

- Массив элементов памяти,

- Блок адресной выборки,

- Блок управления.

Варианты ЗУ имеют много общего с точки зрения структурных

схем. Общность структур особенно проявляется для

статических ОЗУ и памяти ROM; для них характерны структуры

2D, 3D и 2DM.

Структура 2D

В ЗУ, с информационной ёмкостью M, запоминающие элементы

организованы в матрицу размерностью k·m:

M = k·m,

где k — количество хранимых слов,

m — их разрядность.

Дешифратор адресного кода имеет k выходов и активизирует

одну из выходных линий, разрешая одновременный доступ ко

всем элементам выбранной строки, хранящей слово.

Элементы каждого из столбцов соединены вертикальными

разрядными линиями и хранят одноимённые биты всех слов.

Таким образом, при наличии разрешающего сигнала CS,

выбранная дешифратором ячейка памяти подключается к

разрядным шинам, по которым производится запись или

считывание адресованного слова.

57.

Архитектура оперативной памяти58.

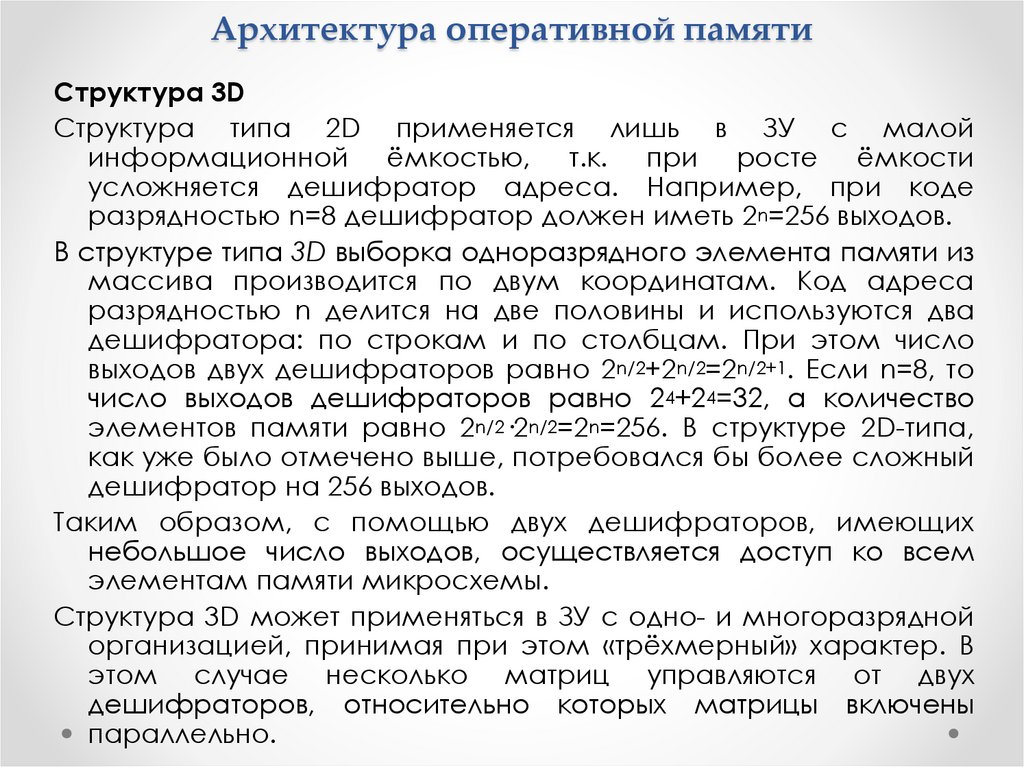

Архитектура оперативной памятиСтруктура 3D

Структура типа 2D применяется лишь в ЗУ с малой

информационной ёмкостью, т.к. при росте ёмкости

усложняется дешифратор адреса. Например, при коде

разрядностью n=8 дешифратор должен иметь 2n=256 выходов.

В структуре типа 3D выборка одноразрядного элемента памяти из

массива производится по двум координатам. Код адреса

разрядностью n делится на две половины и используются два

дешифратора: по строкам и по столбцам. При этом число

выходов двух дешифраторов равно 2n/2+2n/2=2n/2+1. Если n=8, то

число выходов дешифраторов равно 24+24=32, а количество

элементов памяти равно 2n/2·2n/2=2n=256. В структуре 2D-типа,

как уже было отмечено выше, потребовался бы более сложный

дешифратор на 256 выходов.

Таким образом, с помощью двух дешифраторов, имеющих

небольшое число выходов, осуществляется доступ ко всем

элементам памяти микросхемы.

Структура 3D может применяться в ЗУ с одно- и многоразрядной

организацией, принимая при этом «трёхмерный» характер. В

этом случае несколько матриц управляются от двух

дешифраторов, относительно которых матрицы включены

параллельно.

59.

Архитектура оперативной памяти60.

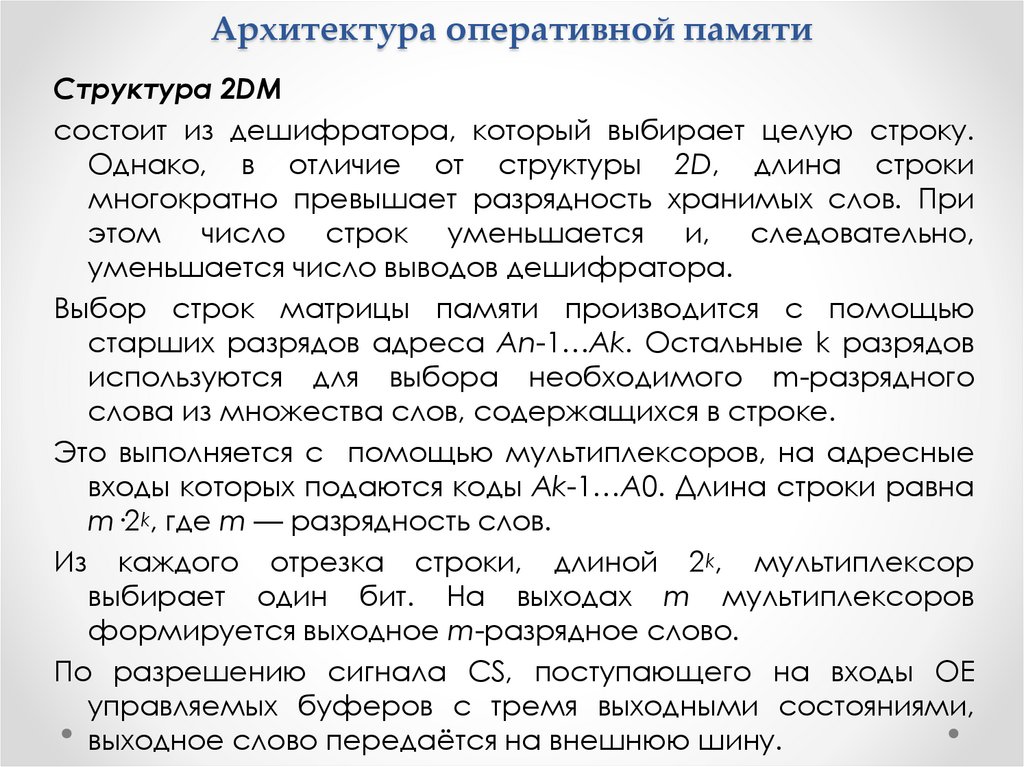

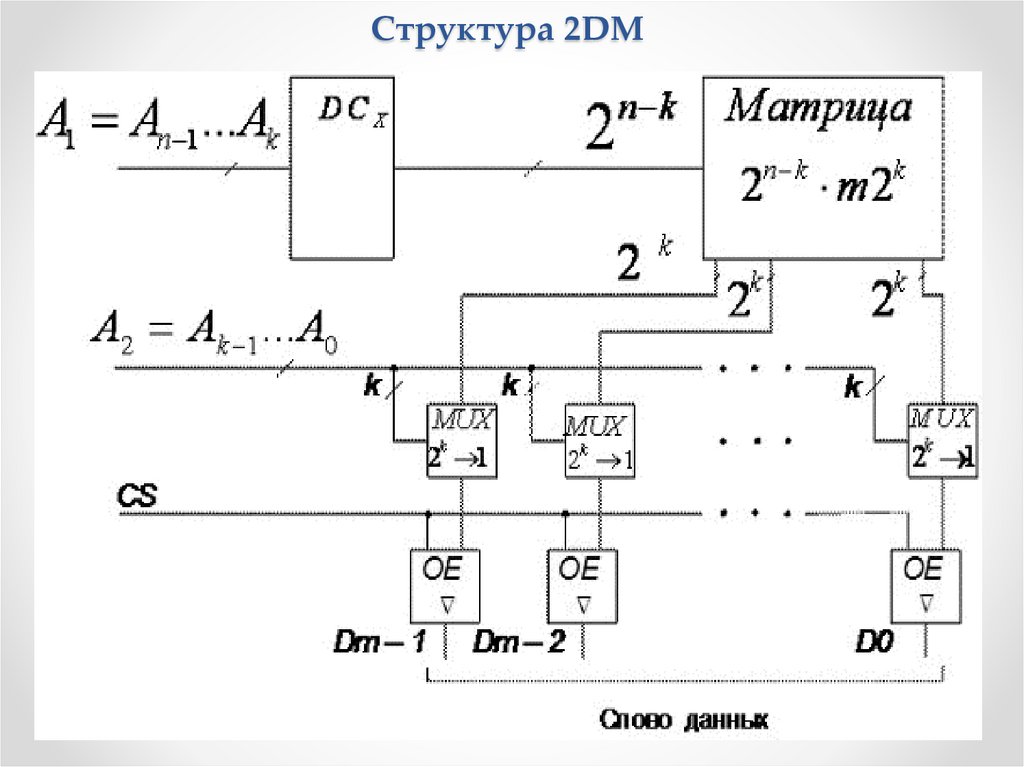

Архитектура оперативной памятиСтруктура 2DM

состоит из дешифратора, который выбирает целую строку.

Однако, в отличие от структуры 2D, длина строки

многократно превышает разрядность хранимых слов. При

этом число строк уменьшается и, следовательно,

уменьшается число выводов дешифратора.

Выбор строк матрицы памяти производится с помощью

старших разрядов адреса An-1…Ak. Остальные k разрядов

используются для выбора необходимого m-разрядного

слова из множества слов, содержащихся в строке.

Это выполняется с помощью мультиплексоров, на адресные

входы которых подаются коды Ak-1…A0. Длина строки равна

m·2k, где m — разрядность слов.

Из каждого отрезка строки, длиной 2k, мультиплексор

выбирает один бит. На выходах m мультиплексоров

формируется выходное m-разрядное слово.

По разрешению сигнала CS, поступающего на входы OE

управляемых буферов с тремя выходными состояниями,

выходное слово передаётся на внешнюю шину.

61.

Структура 2DM62.

Архитектура оперативной памятиОсновные параметры ЗУ

Информационная ёмкость — максимально возможный объём

хранимой информации. Выражается в битах или словах (в

частности, в байтах). Бит хранится запоминающим элементом

(ЗЭ), а слово — запоминающей ячейкой (ЗЯ), т.е. группой ЗЭ, к

которой возможно лишь одновременное обращение.

Быстродействие (производительность) ЗУ оценивают временами

записи, считывания и длительностями циклов записи/чтения.

Время записи — интервал после появления сигнала записи и

установлением ЗЯ в состояние, задаваемое входным словом.

Время считывания — интервал между моментами появления

сигнала чтения и слова на выходе ЗУ. Циклы записи и чтения —

это время между двумя последовательностями записи или

чтения. Длительности циклов могут превышать времена записи

и чтения, так как после этих операций может потребоваться

время для восстановления начального состояния ЗУ.

Кроме

основных

(эксплуатационных

или

измеряемых)

параметров,

ЗУ

характеризуются

рядом

режимных параметров, обеспечение которых необходимо для

нормального функционирования ЗУ. Для управляющих

сигналов задаются не только длительности, но и взаимное

положение во времени.

63.

Архитектура оперативной памятиФункционирование ЗУ во времени регламентируется

изготовителями. Чтобы исключить возможность обращения к

другой ячейке, адрес подаётся раньше, чем другие

сигналы, с опережением на время декодирования и должен

держаться в течение всего цикла обращения к памяти.

Затем следуют сигналы, определяющие направление

передачи данных и, если предполагается запись, то данные,

а также сигнал выборки кристалла. Затем следует

стробирующий сигнал. Всю эту информацию дают

временные диаграммы циклов записи в память и чтения

(считывания) из памяти, приводимые в справочниках.

Самые главные временные параметры:

- время выборки адреса (задержка между изменением

адреса и выдачей данных);

- время выборки микросхемы (задержка выдачи данных по

выставлению сигнала -CS);

- минимальная длительность сигнала записи -WR;

- минимальная длительность сигнала -CS.

Всего же количество временных параметров может достигать

двух-трех десятков, вся подобная информация имеется в

справочниках.

64.

Архитектура оперативной памятиТипичные временные диаграммы записи в память (а) и чтения из

памяти (б)

Для записи информации в память надо выставить код адреса на

адресных входах, выставить код записываемых в этот адрес

данных на входах данных, подать сигнал записи –WR и подать

сигнал выбора микросхемы –CS. Порядок выставления

сигналов бывает различным, он может быть существенным или

несущественным (например, можно выставлять или снимать –

CS раньше или позже выставления или снятия –WR). Собственно

запись обычно производится сигналом -WR или –CS, причем

данные должны удерживаться в течение всего сигнала –WR (или

–CS) и заданное время после его окончания.

65.

Архитектура оперативной памятиВ зависимости от того, в каком порядке может записываться или

читаться информация, существуют две разновидности ЗУ:

ОЗУ с параллельным или произвольным доступом;

ОЗУ с последовательным доступом.

Параллельный или произвольный доступ: можно записывать

информацию в любой адрес ОЗУ и читать информацию из

любого адреса ОЗУ в произвольном порядке. Требует

формирования

сложных

последовательностей

входных

сигналов памяти. Этот режим применяется в компьютерах и

контроллерах, где самыми главными факторами являются

универсальность и гибкость использования памяти.

Последовательный доступ предполагает более простой порядок

общения с памятью. Адрес памяти формируется схемой

автоматически. Для записи информации надо всего лишь

подать код записываемых данных и сопроводить его стробом

записи. Для чтения информации надо подать строб чтения и

получить читаемые данные. Автоматическое задание адреса

осуществляется внутренними счетчиками, меняющими свое

состояние по каждому обращению к памяти. Недостаток

подхода: нет возможности записывать или читать ячейки с

произвольными адресами в любом порядке. Зато упрощается

и ускоряется процедура обмена с памятью (запись и чтение).

66.

Архитектура оперативной памятиМожно выделить три основных типа оперативной памяти с

последовательным доступом:

- память типа "первым вошел - первым вышел" ( FIFO, First In - First

Out);

- память магазинного, стекового типа, работающая по принципу

"последним вошел - первым вышел" (LIFO, Last In - First Out).

- память для хранения массивов данных.

Два

первых

типа

памяти

подразумевают

возможность

чередования операций записи и чтения в памяти. Память с

принципом LIFO используется, в частности, в компьютерах

(стек), где она хранит информацию о параметрах программ

и подпрограмм.

Для памяти FIFO требуется хранение двух кодов адреса (адрес

для записи и адрес для чтения), для памяти LIFO достаточно

одного кода адреса.

Хранение массивов в памяти предполагает, что сначала в память

записывается целиком большой массив данных, а потом этот

же массив целиком читается из памяти. Эта память также

может быть устроена по двум принципам (FIFO и LIFO). В обоих

этих случаях для общения с памятью требуется хранить только

один код адреса памяти.

67.

Архитектура оперативной памятиПовышение быстродействия

Самое распространенное и самое простое решение применение сдвиговых регистров. Частота тактовых импульсов

этих регистров может достигать десятков и сотен мегагерц.

Если необходимо в 8 раз увеличить частоту чтения информации из

памяти, то надо соединить нужное количество микросхем

памяти для увеличения разрядности шины данных в 8 раз, а

затем применить на выходах данных схему на основе 8разрядного регистра сдвига. 8-разрядный код, читаемый из

памяти, записывается в сдвиговый регистр, а затем сдвигается

семь раз с частотой, в 8 раз большей, чем частота опроса

памяти. И запись, и сдвиг производятся одним тактовым

сигналом с генератора. Восемь тактовых импульсов

отсчитываются синхронным счетчиком. Для управления работой

регистра сдвига применен элемент 3ИЛИ-НЕ, выдающий

положительный импульс в течение первой 1/8 периода опроса

памяти. Этот же сигнал используется как строб чтения из памяти

(своим задним фронтом он переключает адреса памяти).

Поскольку информация в память записывается не по фронту

сигнала, а по уровню, код с выхода сдвигового регистра

необходимо перед записью в память переписать в

параллельный регистр, где он будет затем храниться в течение

всего периода записи в память.

68.

Архитектура оперативной памятиУвеличение частоты чтения информации

69.

Архитектура оперативной памятиУвеличение частоты записи информации

70.

Архитектура оперативной памяти71.

Архитектура оперативной памятиОсновные особенности SDRAM

Все операции синхронизированы с тактовой частотой системной

шины и процессора.

SDRAM-модуль разделен на два или более банков, что позволяет

иметь одновременно две и более открытые страницы. Доступ

чередуется (bank interleaving), что позволяет исключить

задержки, связанные с регенерацией памяти.

Конвейерная

обработка

данных

позволяет

производить

обращение по новому адресу столбца ячейки памяти на

каждом тактовом цикле. Микросхема SDRAM имеет счетчик

потока, который используется для наращивания адресов

столбцов ячеек памяти с целью обеспечения очень быстрого

доступа к ним.

На чипе памяти размещен регистр режимов, который

применяется

для

настройки

основных

параметров

микросхемы, в том числе длины и типа потока.

SDRAM позволяет устанавливать задержку вывода данных,

которые определяется числом тактовых импульсов между

моментом получения адреса столбца и выводом данных.

Значение этого параметра может быть 2 или 3 (латентность).

Теоретической границей, при которой устойчиво функционирует

SDRAM, является частота 125 МГц, хотя технологический запас

может позволить работу и на частоте 133 МГц.

72.

Архитектура оперативной памятиОсновные временные характеристики SDRAM

73.

Архитектура оперативной памятиDDR SDRAM

По сравнению с обычной памятью типа SDR SDRAM, в памяти

SDRAM с удвоенной скоростью передачи данных (double

data rate SDRAM, DDR SDRAM или SDRAM II) была вдвое

увеличена пропускная способность.

У всех предыдущих DRAM были разделены линии адреса,

данных и управления, которые накладывают ограничения на

скорость работы устройств. Для преодоления этого

ограничения ввсе сигналы стали выполняться на одной шине:

технологии DRDRAM и SLDRAM. Стандарт SLDRAM является

открытым и, подобно предыдущей технологии, SLDRAM

использует оба перепада тактового сигнала.

Память DDR SDRAM работает на частотах в 100, 133, 166 и 200

МГц, её время полного доступа — 30 и 22,5 нс, а время

рабочего цикла — 5, 3,75, 3 и 2,5 нс.

Так как частота синхронизации лежит в пределах от 100 до 200

МГц, а данные передаются по 2 бита на один

синхроимпульс, как по фронту, так и по спаду тактового

импульса, то эффективная частота передачи данных лежит

в пределах от 200 до 400 МГц. Такие модули памяти

обозначаются DDR200, DDR266, DDR333, DDR400.

74.

Архитектура оперативной памятиDDR2 SDRAM

Конструктивно новый тип оперативной памяти DDR2 SDRAM был

выпущен в 2004 году. Основываясь на технологии DDR SDRAM,

этот тип памяти за счёт технических изменений показывает

более высокое быстродействие

и предназначен

для

использования на более современных компьютерах. Память

может работать с тактовой частотой шины 200, 266, 333, 337,

400, 533, 575 и 600 МГц. При этом эффективная частота

передачи данных соответственно будет 400, 533, 667, 675, 800,

1066, 1150 и 1200 МГц. Некоторые производители модулей

памяти помимо стандартных частот выпускают и образцы,

работающие на нестандартных (промежуточных) частотах.

Они предназначены для использования в разогнанных

системах, где требуется запас по частоте. Время полного

доступа — 25, 11,25, 9, 7,5 нс и менее. Время рабочего цикла —

от 5 до 1,67 нс.

DDR3 SDRAM

Основан на технологиях DDR2 SDRAM со вдвое увеличенной

частотой передачи данных по шине памяти. Отличается

пониженным

энергопотреблением.

Частота

полосы

пропускания лежит в пределах от 800 до 2400 МГц (рекорд

частоты — более 3000 МГц), что обеспечивает большую

пропускную способность.

75.

Архитектура оперативной памятиDDR4 SDRAM (double-data-rate four synchronous dynamic random

access memory) - развитие предыдущих поколений DDR.

Отличается повышенными частотными характеристиками и

пониженным напряжением питания.

Основное отличие DDR4 заключается в удвоенном до 16 числе

банков (в 2 группах банков). Пропускная способность памяти

DDR4 может достигать 25,6 ГБ/c в случае повышения

максимальной эффективной частоты до 3200 МГц. Повышена

надёжность работы за счёт введения механизма контроля

чётности на шинах адреса и команд.

В массовое производство вышла во 2 квартале 2014 года, вместе

с процессорами Intel Haswell-E/Haswell-EP, требующих DDR4

Для расчёта максимальной пропускной способности памяти

DDR4 необходимо её эффективную частоту умножить на 64

бита (8 байт), то есть размер данных, который может быть

передан за 1 такт работы памяти. Таким образом, для

эффективной частоты:

1600 Мгц пропускная способность составит 1600 × 8 = 12 800 МБ/c

2133 МГц пропускная способность составит 2133 × 8 = 17 064 МБ/c

3200 МГц пропускная способность составит 3200 × 8 = 25 600 МБ/c

Из-за

временных

ограничений

по

взаимодействию

с

микросхемами памяти реальная пропускная способность

меньше на 5—10 %.

76.

Архитектура оперативной памятиОбъём модулей

Объем кристалла DDR4 составляет от 2 до 16 Гбит,

организация модулей памяти - ×4, ×8 или ×16 банков.

Минимальный объём одного модуля DDR4 составляет 4 ГБ,

максимальный — 128 ГБ (кристаллы по 8 Гбит, упаковка 4

кристаллов в чип). Не исключается производство модулей

объёмом в 512 ГБ на базе кристаллов 16 Гбит и упаковке 8

кристаллов в чип.

Размеры модулей

DDR4 имеет 288-контактные DIMM-модули, схожие по

внешнему виду с 240-контактными DIMM DDR-2/DDR-3.

Контакты расположены плотнее (0,85 мм вместо 1,0), чтобы

разместить их на стандартном 5¼-дюймовом (133,35 мм)

слоте DIMM. Высота увеличивается незначительно (31,25 мм

вместо 30,35).

DDR4 модули SO-DIMM имеют 260 контактов[35] (а не 204),

которые расположены ближе друг к другу (0,5 мм, а не 0,6).

Модуль стал на 1,0 мм шире (68,6 мм вместо 67,6), но

сохранил ту же высоту — 30 мм.

77.

Архитектура оперативной памятиУвеличения пропускной способности можно добиться не только с

помощью расширения шины памяти, увеличения её частоты и

количества банков, т.е. на уровне отдельного модуля, но и

организацией многоканальной системы на уровне чипсета.

Многоканальный

режим

(Multi-channel)

использование

нескольких каналов для доступа к объединённому банку

памяти

Двухканальный режим — режим параллельной работы двух

каналов памяти. Позволяет увеличить пропускную способность

до 2 раз по сравнению с одноканальным режимом.

Трёхканальный режим — параллельно работают 3 модуля или три

пары модулей.

Четырёхканальный режим — параллельно работают 4 модуля или

четыре пары модулей. Поддерживается на платформах LGA

2011, LGA 2011v3, TR4, SP3.

Для включения многоканального режима необходимо:

Одинаковая конфигурация модулей DIMM на каждом канале

Одинаковая плотность (128 Мбит, 256 Мбит, и т. п.)

Каналы памяти должны быть идентичны

На большинстве материнских плат должны быть заполнены

симметричные разъемы памяти (разъем 0 или разъем 1)

Желательно, чтобы был один производитель, одинаковые

спецификации

синхронизации,

одинаковая

производительность.

78.

Архитектура памяти на магнитных дискахНакопи́тель на жёстких магни́тных ди́сках или НЖМД (hard

(magnetic) disk drive, HDD, HMDD), жёсткий диск —

запоминающее

устройство

произвольного

доступа,

основанное на принципе магнитной записи. Является

основным

накопителем

данных

в

большинстве

компьютеров.

Информация

в

НЖМД

записывается

на

жёсткие

(алюминиевые или стеклянные) пластины, покрытые слоем

ферромагнитного материала, чаще всего двуокиси

хрома — магнитные диски. В НЖМД используется одна или

несколько пластин на одной оси. Считывающие головки в

рабочем режиме не касаются поверхности пластин

благодаря прослойке набегающего потока воздуха,

образующейся у поверхности при быстром вращении.

Расстояние между головкой и диском составляет несколько

нанометров (в современных дисках около 10 нм), а

отсутствие механического контакта обеспечивает долгий

срок службы устройства. При отсутствии вращения дисков

головки находятся у шпинделя или за пределами диска в

безопасной («парковочной») зоне, где исключён их

нештатный контакт с поверхностью дисков.

79.

Архитектура памяти на магнитных дисках80.

Архитектура памяти на магнитных дискахС середины 1990-х начали применяться головки на основе

эффекта гигантского магнитного сопротивления (ГМС), затем

- головки на основе туннельного магниторезистивного

эффекта (в них изменение магнитного поля приводит к

изменению сопротивления в зависимости от изменения

напряжённости магнитного поля; подобные головки позволяют

увеличить вероятность достоверности считывания информации,

особенно при больших плотностях записи информации). В

2007

году

устройства

на

основе

туннельного

магниторезистивного эффекта с оксидом магния (эффект

открыт в 2005) полностью заменили устройства на основе

эффекта ГМС.

Метод продольной записи. Биты информации записываются с

помощью

маленькой

головки,

которая,

проходя

над

поверхностью

вращающегося

диска,

намагничивает

миллиарды горизонтальных дискретных областей — доменов.

При этом вектор намагниченности домена расположен

продольно, то есть параллельно поверхности диска. Каждая из

этих областей является логическим нулём или единицей, в

зависимости от направления намагниченности. Максимально

достижимая при использовании данного метода плотность

записи составляет около 23 Гбит/см². К 2010 году этот метод

был практически вытеснен методом перпендикулярной записи.

81.

Архитектура памяти на магнитных дискахМетод перпендикулярной записи — технология, при которой биты

информации сохраняются в вертикальных доменах. Это

позволяет использовать более сильные магнитные поля и

снизить площадь материала, необходимую для записи 1 бита.

Плотность записи при этом методе резко подскочила — на

свыше 30 % еще на первых образцах (на 2009 год — 400

Гбит/дюйм² / 62 Гбит/см²). А теоретический предел отодвинулся

на порядки и составляет 1 Тбит на квадратный дюйм. Жёсткие

диски с перпендикулярной записью стали доступны на рынке с

2006 года. Благодаря перпендикулярной записи, винчестеры

продолжают бить рекорды ёмкости, вмещая уже по 8 и даже

10 Терабайт.

Метод черепичной магнитной записи (Shingled Magnetic

Recording, SMR) был реализован в начала 2010-х. В нём

используется тот факт, что ширина области чтения меньше, чем

ширина записывающей головки. Запись дорожек в этом

методе производится с частичным наложением в рамках групп

дорожек (пакетов). Каждая следующая дорожка пакета

частично закрывает предыдущую (подобно черепичной

кровле), оставляя от нее узкую часть, достаточную для

считывающей

головки.

Черепичная

запись

увеличивает

плотность записанной информации, однако осложняет

перезапись - при каждом изменении требуется полностью

перезаписать весь пакет перекрывающихся дорожек.

82.

Архитектура памяти на магнитных дискахМетод тепловой магнитной записи (Heat-assisted magnetic

recording, HAMR) остается перспективным, продолжаются

его доработки и внедрение. При использовании этого

метода используется точечный подогрев диска, который

позволяет головке намагничивать очень мелкие области его

поверхности.

После

того,

как

диск

охлаждается,

намагниченность «закрепляется». На 2009 год были доступны

только экспериментальные образцы, плотность записи

которых составляла 150 Гбит/см². Специалисты Hitachi

называют предел для этой технологии в 2,3−3,1 Тбит/см², а

представители Seagate Technology — 7,75 Тбит/см².

Структурированный (паттернированный) носитель данных

(Bit patterned media), — перспективная технология хранения

данных на магнитном носителе, использующая для записи

данных массив одинаковых магнитных ячеек, каждая из

которых соответствует одному биту информации, в отличие

от современных технологий магнитной записи, в которых бит

информации записывается на нескольких магнитных

доменах.

83.

Характеристики дисковых накопителейИнтерфейс. Современные серийно выпускаемые внутренние

жёсткие диски могут использовать интерфейсы ATA (он же IDE

и PATA), SATA, eSATA, SCSI, SAS, FireWire, SDIO и Fibre Channel.

Ёмкость — количество данных, которые могут храниться

накопителем. С момента создания первых жёстких дисков в

результате непрерывного совершенствования технологии

записи данных их максимально возможная ёмкость

непрерывно увеличивается. Ёмкость современных жёстких

дисков (с форм-фактором 3,5 дюйма) на начало 2015 года

достигает 6000 Гб (6 терабайт). В отличие от принятой в

информатике системы приставок, обозначающих кратную

1024 величину (см.: двоичные приставки), производителями при

обозначении ёмкости жёстких дисков используются величины,

кратные 1000. Так, ёмкость жёсткого диска, маркированного

как «200 ГБ», составляет 186,2 ГиБ.

Физический размер (форм-фактор; dimension) — почти все

накопители 2001—2008 годов для персональных компьютеров и

серверов имеют ширину либо 3,5, либо 2,5 дюйма — под

размер стандартных креплений для них соответственно в

настольных компьютерах и ноутбуках. Также получили

распространение форматы 1,8, 1,3, 1 и 0,85 дюйма.

Прекращено производство накопителей в форм-факторах 8 и

5,25 дюймов.

84.

Характеристики дисковых накопителейВремя произвольного доступа (random access time) —

среднее время, за которое винчестер выполняет операцию

позиционирования головки чтения/записи на произвольный

участок магнитного диска. Диапазон этого параметра — от

2,5 до 16 мс. Как правило, минимальным временем

обладают диски для серверов (например, у Hitachi Ultrastar

15K147 — это 3,7 мс), самым большим из актуальных —