Похожие презентации:

Вычислительные машины, системы и сети. Лекция 3. Тема 4. Система команд процессора

1.

Вычислительные машины, системыи сети

Лекция 3

Система команд процессора.

Способы адресации.

к.т.н., доцент, Тычинина Юлия Александровна

2.

4 Система команд процессора.4.1 Структуры и типы команд

Обработка информации и функционирование процессора

обеспечиваются с помощью программного управления.

Программа записывается в ОЗУ в виде последовательности

команд. Каждая команда определяет:

• вид операции, исполняемой в данном цикле работы;

• адреса операндов, участвующих в операции;

• место расположения результата операции;

• адрес расположения следующей команды.

3.

4 Система команд процессора.4.1 Структуры и типы команд

Набор команд процессора – ограниченный по размеру

список – называется системой команд.

Совокупность сведений, которые задают для каждой

команды процессора её длину, состав, назначение и взаимное

расположение её частей, называется форматом команды.

• Команды можно классифицировать

• по функциональному назначению;

• по числу адресов;

• по способу кодирования команд;

• по длине команды;

• по способу адресации.

4.

4 Система команд процессора.4.1 Структуры и типы команд

По функциональному назначению различаются команды:

• передачи данных (команды передачи данных между регистрами

процессора, пересылки данных между процессором и памятью,

передачи данных между процессором и внешними устройствами (MOV,

LEA) );

• обработки данных (арифметические (ADD, SUB, MUL, DIV), логические

(NOT, AND, OR, XOR) и команды сдвига (SHR, SHL, ROL, ROR, для dsPic LSR

логический сдвиг вправо);

• передачи управления (команды условного и безусловного переходов

(JMP, JA, JAE, JE, JLE, JL, JNE для dsPic GOTO), организации циклов (LOOP,

для dsPic DO, REPEAT). Команды условного перехода проверяют

указанное в команде условие, и модифицируют программный счётчик,

если условие истинно;

• дополнительные команды (останов программы, начальная установка

аппаратных средств, реализация ожидания).

5.

4 Система команд процессора.4.1 Структуры и типы команд

По числу адресов различают безадресные, одноадресные,

двухадресные, многоадресные команды. Код операции

позволяет определить длину каждой команды.

ADD #15, W1 // 2 адреса;

ADD W2, #15, W1 // 3 адреса;

По способу кодирования различают команды с

фиксированным и расширяющимся полем кода операций.

По длине различают команду длиной в одно, два и три

слова (для dsPic DO и GOTO имеют длину 2 слова, остальные в

основном одно слово).

6.

4 Система команд процессора.4.2 Способы адресации

Часть способов адресации можно проиллюстрировать с помощью

команд процессора Intel 8086. Однако, не все способы адресации

реализованы в системе команд данного процессора.

Регистры делятся на пять категорий:

Регистры общего назначения (ax, bx, cx, dx)

Регистровые указатели и индексные регистры (sp, bp, si, di)

Сегментные регистры (cs, ds, ss, es)

Регистр командного указателя (ip)

Регистр флагов

Все регистры процессора 8086 являются 16-битовыми. Кроме того,

четыре регистра общего назначения – ax, bx, cd, dx - разделены на старшую

(high) и младшую (low) 8-битовые половины. Это позволяет оперировать

либо всем 16-битовым регистром (например, ax), либо обращаться

отдельно к старшей (ah) или младшей (al) половинам регистра.

7.

4 Система команд процессора.4.2 Способы адресации

Регистры общего назначения — это регистры данных, каждый из

которых помимо хранения операндов и результатов операций имеет еще и

свое специфическое назначение:

регистр AX (accumulator) — умножение, деление, обмен с устройствами

ввода/вывода (команды ввода и вывода) для dsPic W0;

регистр BX (base) — базовый регистр в вычислениях адреса, часто

указывает на начальный адрес (называемый базой) структуры в памяти;

регистр CX (count) — счетчик циклов, определяет количество повторов

некоторой оперции;

регистр DX (data) — определение адреса ввода/вывода, так же может

содержать данные, передаваемые для обработки в подпрограммы.

8.

4 Система команд процессора.4.2 Способы адресации

Регистровая адресация. Операнд находится в одном из регистров

процессора. операнды располагаются в любых регистрах общего

назначения или сегментных регистрах.

MOV Ax, Bx. // Ax:=Bx

Add $a0, $v0, $v1 // a0:=v0+v1

9.

4 Система команд процессора.4.2 Способы адресации

Непосредственная адресация позволяет задавать значение операнда в

команде.

В команде содержится не адрес операнда, а непосредственно сам

операнд. При непосредственной адресации не требуется обращения к

памяти для выборки операнда и ячейки памяти для его хранения. Это

способствует уменьшению времени выполнения программы и

занимаемого ею объёма памяти. Непосредственная адресация удобна для

хранения различного рода констант.

MOV Ax, 5 ;Число 5 загружается в Ах

mov AL,'*' ; Код ASCII символа "*' загружается в AL

add ax, 2

для dsPic: ADD #3, W1 // W1:=W1+3

для Pic32: li v0, 123 // v0:=123

ori t0, t0, 0x400

10.

4 Система команд процессора.4.2 Способы адресации

Прямая адресация. Часть команды является адресом операнда

(обрабатываемого слова) в памяти. Если известен адрес операнда

располагающегося в памяти

MOV Ax, a;

ADD Ax, a.

для dsPic

.equ a, 0x802

…

Mov W1, a

11.

4 Система команд процессора.4.2 Способы адресации

Регистровая косвенная адресация. Адрес операнда извлекается из

регистра процессора (MOV Ax, [Bx]. В системе команд процессора Intel 8086

для косвенной регистровой адресации могут использоваться только

регистры Вх, ВР, SI, DI).

для dsPic

mov W1, [W2]

для Pic32

lw s0, (t0)

12.

4 Система команд процессора.4.2 Способы адресации

Автоинкрементная косвенная адресация основана на вычислении

исполнительного адреса так же, как и при регистровой косвенной

адресации, затем осуществляется увеличение содержимого регистра на

некоторую константу.

MOV Ax,[ Bx++].

mov ax, [bp]+2

для dsPic

mov W1, [W2++]

13.

4 Система команд процессора.4.2 Способы адресации

Автоинкрементная косвенная адресация основана на вычислении

исполнительного адреса так же, как и при регистровой косвенной

адресации, затем осуществляется увеличение содержимого регистра на

некоторую константу.

MOV Ax,[ Bx++].

mov ax, [bp]+2

для dsPic

mov W1, [W2++]

Автодекрементная адресация: сначала из содержимого регистра

вычитается константа, затем полученный результат используется в качестве

исполнительного адреса.

14.

4 Система команд процессора.4.2 Способы адресации

Совместное использование автоинкрементной и автодекрементной

адресации обеспечивает применение регистра в качестве указателя

стека. Поскольку регистровая косвенная адресация требует

предварительной загрузки регистра косвенным адресом из оперативной

памяти, что связано с потерей времени, такой тип адресации особенно

эффективен при обработке массива данных, если имеется механизм

автоматического приращения или уменьшения содержимого регистра

при каждом обращении к нему. Такой механизм называется

соответственно автоинкрементной и автодекрементной адресацией. В

этом случае достаточно один раз загрузить в регистр адрес первого

обрабатываемого элемента массива, а затем при каждом обращении к

регистру в нём будет формироваться адрес следующего элемента

массива.

15.

4 Система команд процессора.4.2 Способы адресации

При автоинкрементной адресации сначала содержимое регистра

используется как адрес операнда, а затем получает приращение, равное

числу байт в элементе массива. При автодекрементной адресации сначала

содержимое указанного в команде регистра уменьшается на число байт в

элементе массива, а затем используется как адрес операнда.

для dsPic

mov W1, [W2--]

Важно различать варианты префиксной автоинкрементной адресации и

постфиксной.

mov W1, [--W2]

mov W1, [W2--]

16.

4 Система команд процессора.4.2 Способы адресации

Неявная или подразумеваемая адресация. При таком способе

адресации в команде явно не указывается адрес одного или нескольких

операндов. Операнды в командах с неявной адресацией находятся в

выделенных для этой команды регистрах процессора или некоторый

специально выделенный регистр процессора содержит адрес операнда.

(LOOP @Cycl, MUL Cx).

CBW ; преобразование байта в слово.

Mul Cx; у команды MUL фиксировано положение первого множителя и

результата. Ax*Cx=Dx:Ax

для dsPic

Div W4, W2 // [W1:W0]=W4/W2

для Pic32

Div s2, s0 // L0=s2/s0, Hi=s2 mod s0 (L0 и Hi младшая и старшая чать

аккумулятора)

17.

4 Система команд процессора.4.2 Способы адресации

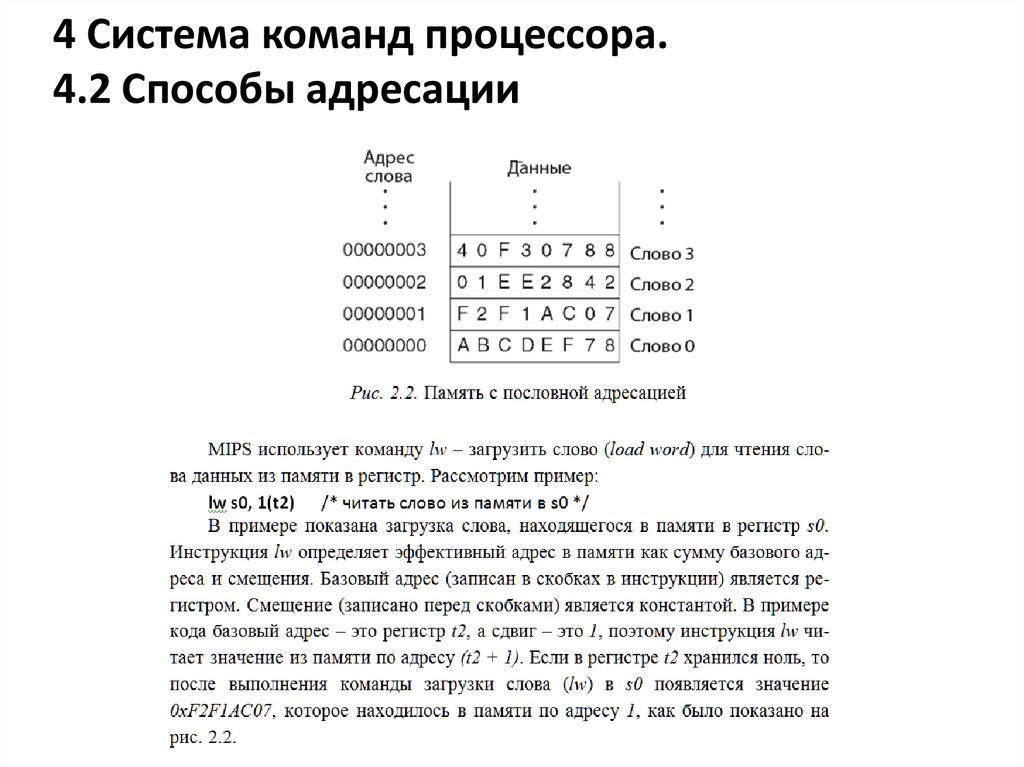

18.

4 Система команд процессора.4.2 Способы адресации

Относительная адресация. В команде указывается не полный адрес

операнда, а сокращённый адрес, обычно называемый смещением. В

процессе выполнения команды полный адрес операнда вычисляется

путём суммирования смещения, указанного в команде с некоторой

величиной, которая называется базовым адресом. Существует два

способа расширения адреса, указанного в короткой форме.

Первый способ адресации называется неявным базированием. В этом

случае смещение, указанное в команде складывается с адресом самой

команды (текущее содержимое программного счётчика). Такой способ

широко используется в командах условной передачи управления многих

процессоров. (JMP @label1).

Lw t1, 4(s0)

19.

4 Система команд процессора.4.2 Способы адресации

Второй вид относительной адресации называется базовой

адресацией. При базовой адресации смещение,

указываемое в команде, складывается с базовым адресом,

хранящимся в регистре базы процессора (в качестве

базового регистра системе команд процессора Intel 8086

могут выступать регистры Bx и BP: MOV Ax, [Bx]+2) Вообще,

сегментная адресация является разновидностью базовой

адресации.

20.

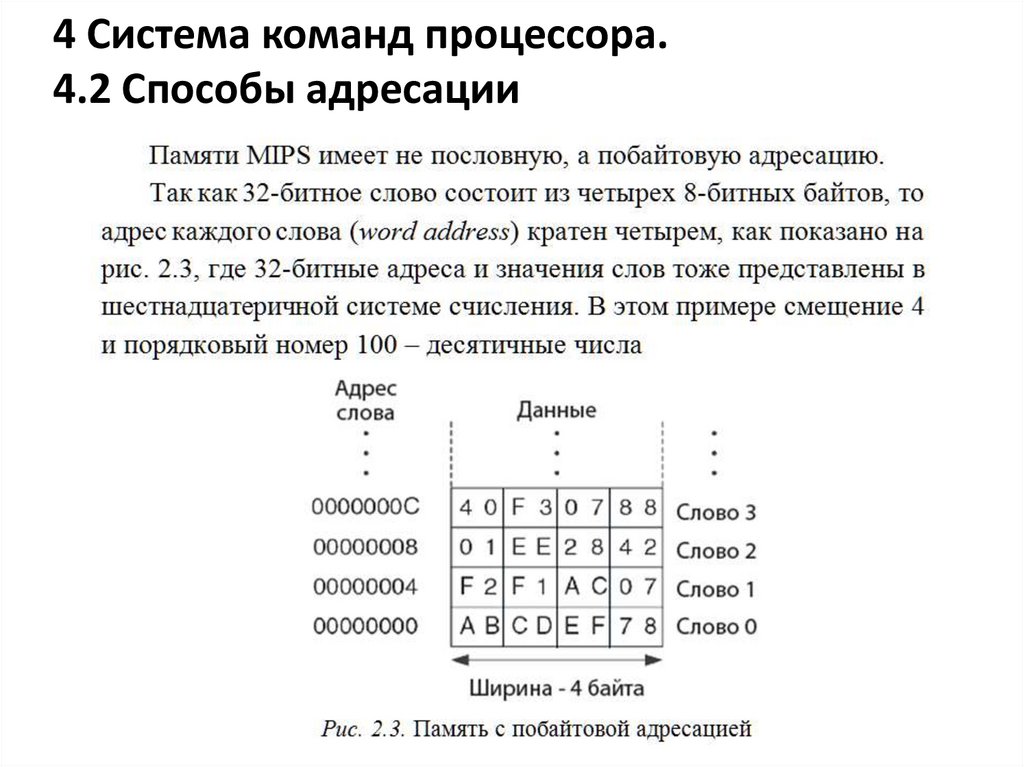

4 Система команд процессора.4.2 Способы адресации

21.

4 Система команд процессора.4.2 Способы адресации

22.

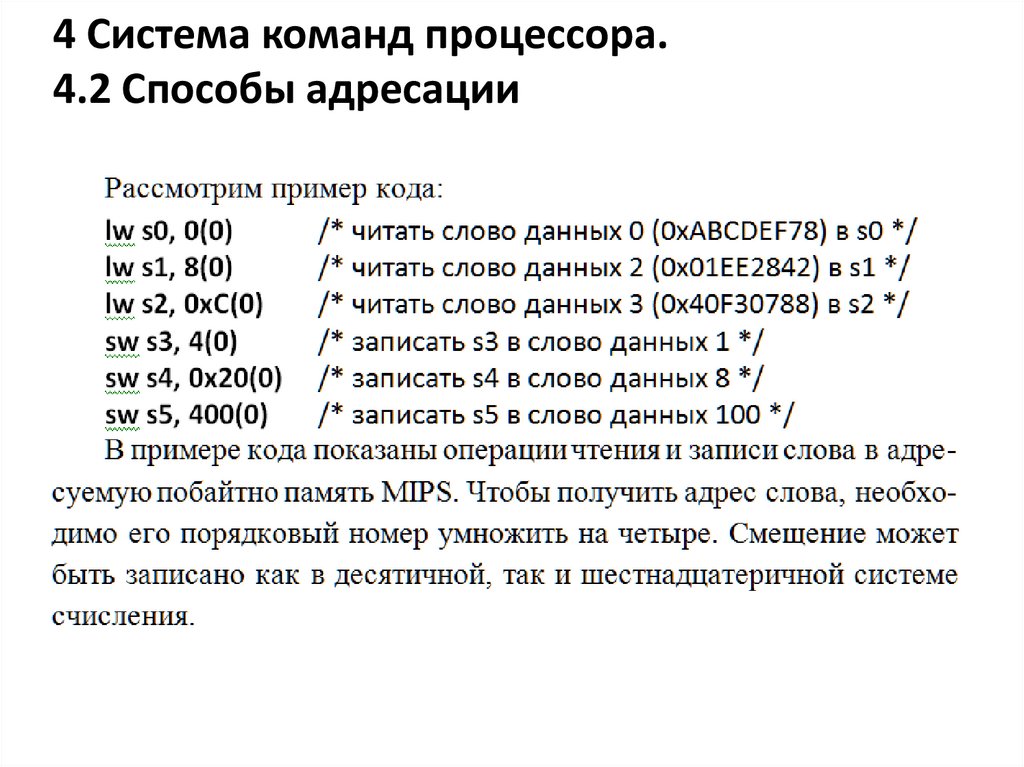

4 Система команд процессора.4.2 Способы адресации

23.

4 Система команд процессора.4.2 Способы адресации

Информатика

Информатика