Похожие презентации:

Разработка модуля приёма цифрового видеопотока на ПЛИС

1.

Разработка модуляприёма цифрового

видеопотока на ПЛИС

Студент гр. РТ-91

Лебедев

Ст. пр.

А.К.

2.

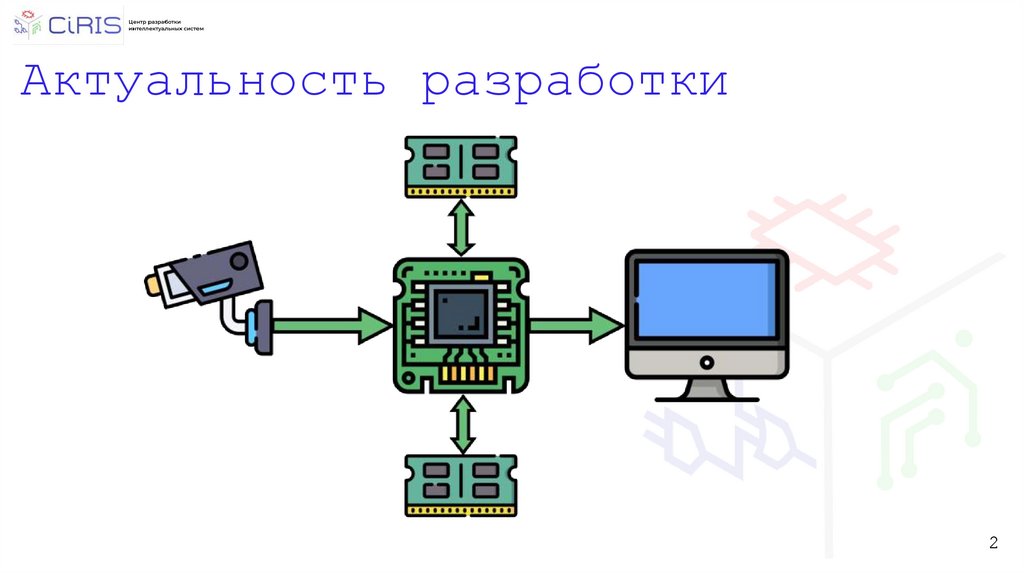

Актуальность разработки2

3.

Цель работыРазработать модуль приёма

цифрового видеопотока на ПЛИС

Задачи

-

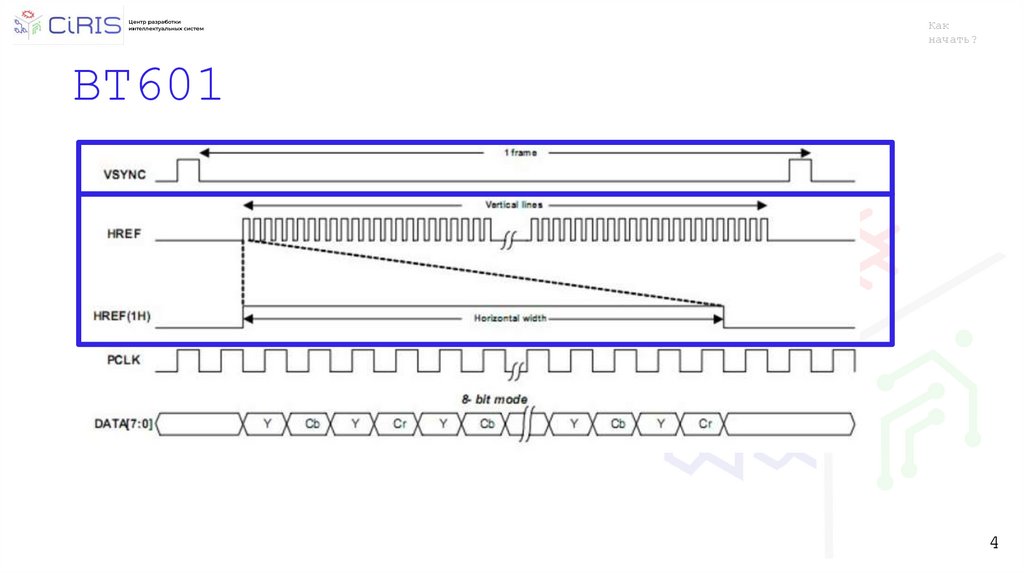

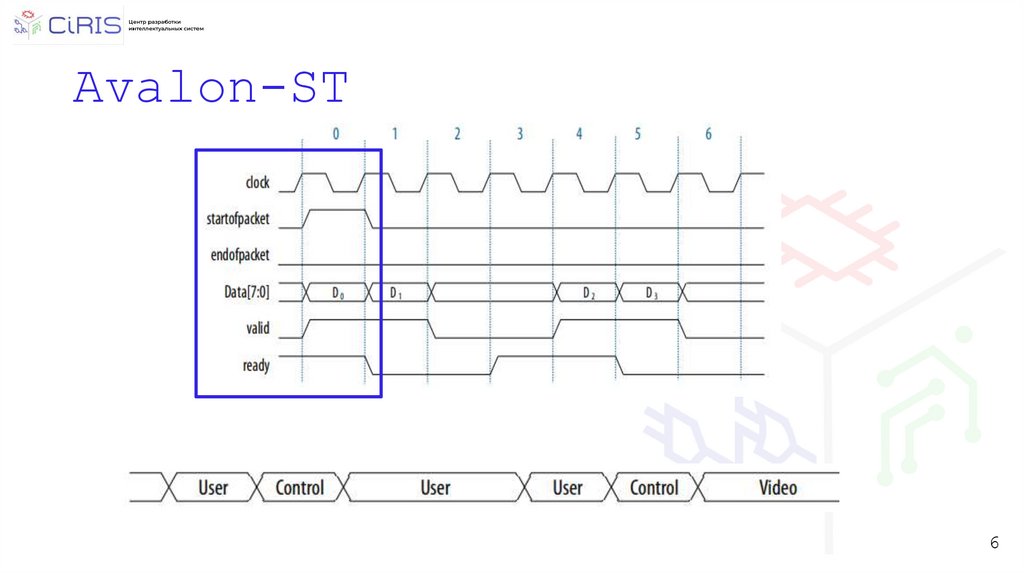

Изучение особенностей стандартов BT601, BT656, AvalonST;

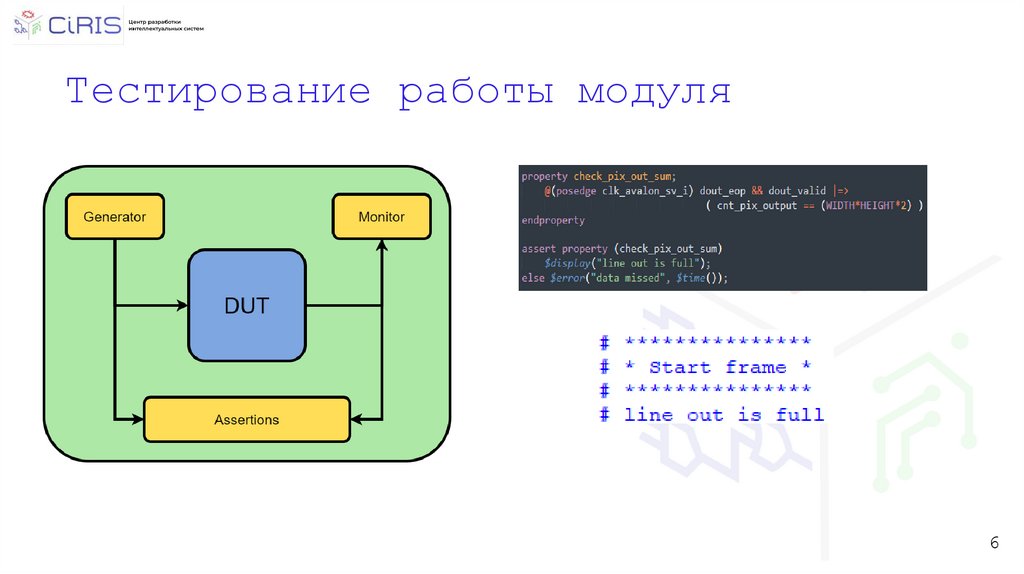

Разработка модуля на языке System Verilog для ПЛИС;

Написание testbench для проверки корректности работы

модуля;

Сравнить результаты работы с существующими модулями

основных вендоров;

3

4.

Какначать?

BT601

4

5.

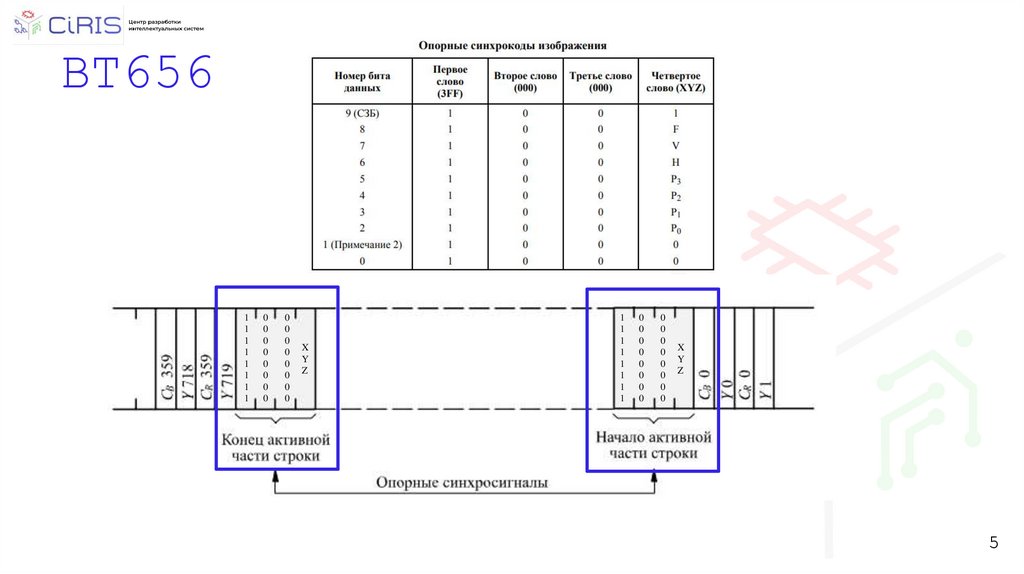

BT6561

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

X

Y

Z

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

X

Y

Z

5

5

6.

Avalon-ST6

7.

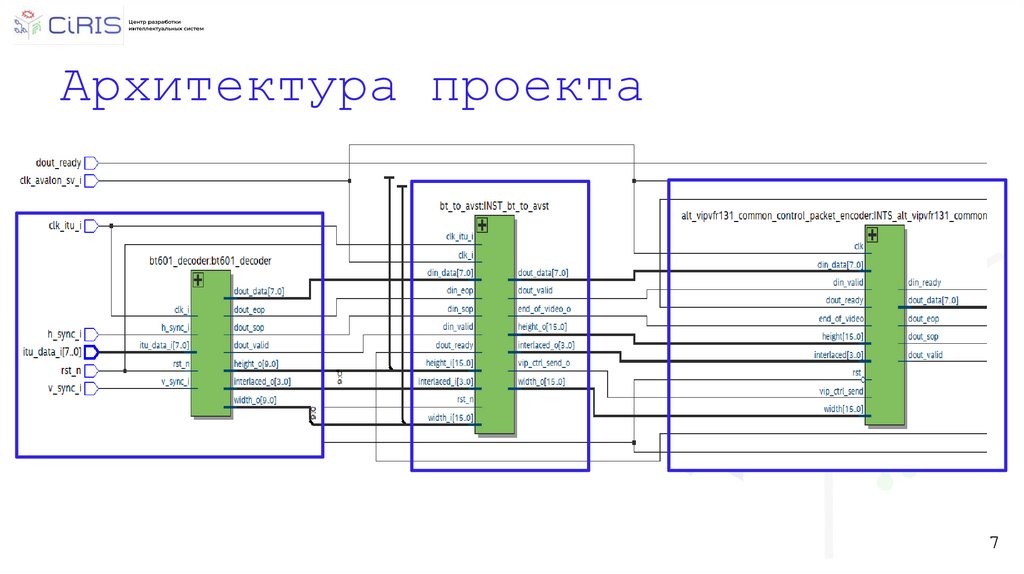

Архитектура проекта7

8.

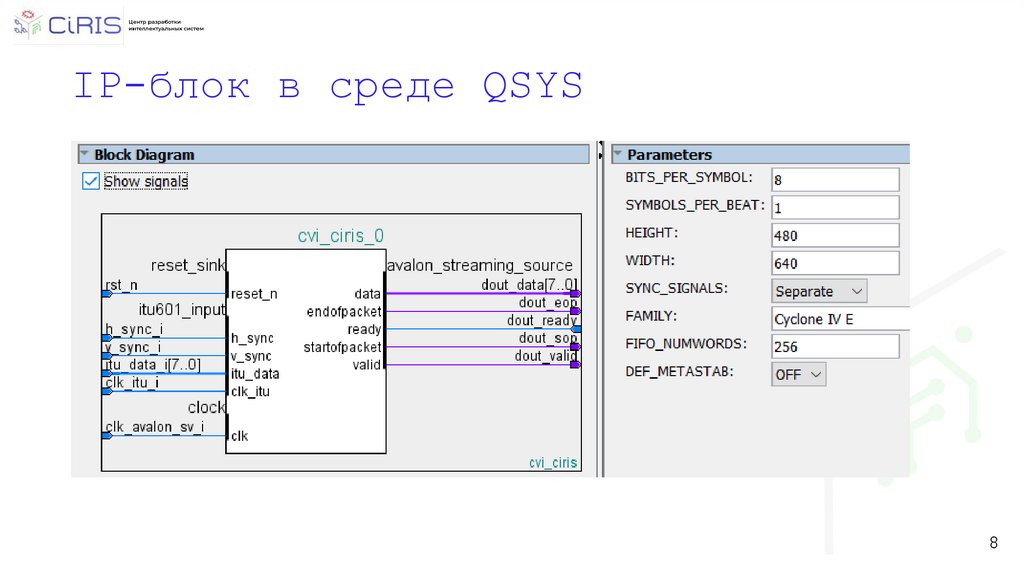

IP-блок в среде QSYS8

8

9.

Тестирование работы модуля6

10.

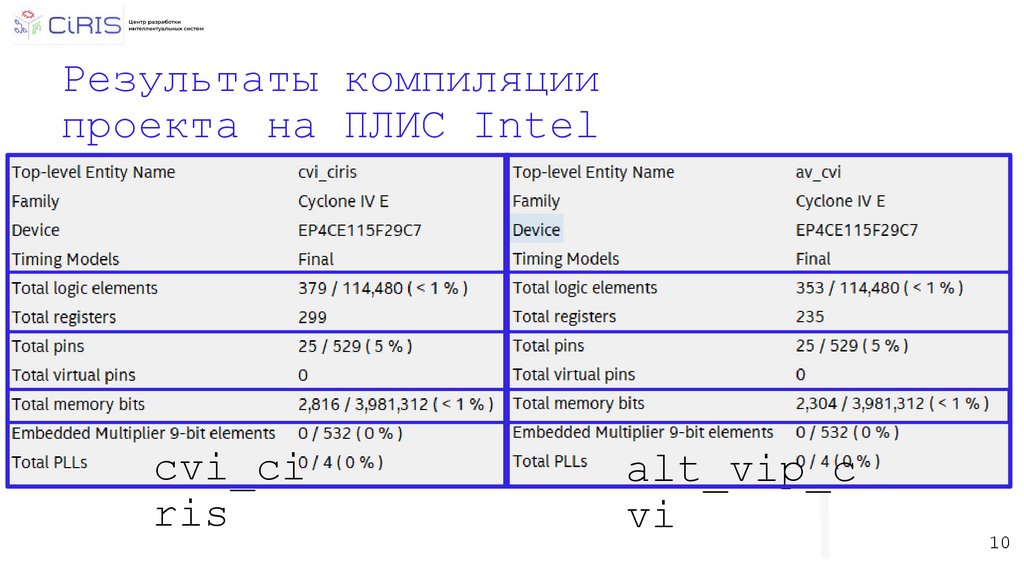

Результаты компиляциипроекта на ПЛИС Intel

cvi_ci

ris

alt_vip_c

vi

10

11.

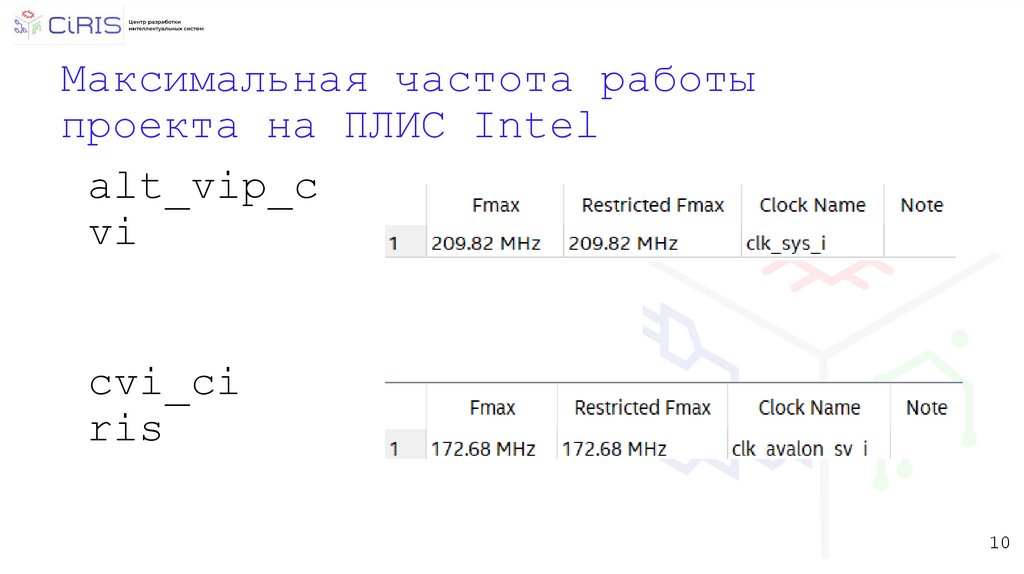

Максимальная частота работыпроекта на ПЛИС Intel

alt_vip_c

vi

cvi_ci

ris

10

12.

Результаты компиляциипроекта на ПЛИС Xilinx

cvi_ci

ris

vid_in_ax

i

10

13.

Максимальная частота работыпроекта на ПЛИС Xilinx

vid_in_ax

i

cvi_ci

ris

10

14.

Заключение- Изучены особенности стандартов BT601,

BT656, Avalon-ST;

- Разработан модуль на языке System Verilog

для ПЛИС;

- Проверена корректность работы модуля с

помощью testbench;

- Проведено сравнение модулей на ПЛИС разных

вендоров

Интернет

Интернет