Похожие презентации:

Организация ЭВМ и систем

1.

Министерство образования и науки Российской ФедерацииФедеральное государственное бюджетное образовательное

учреждение высшего образования

«Оренбургский государственный университет»

Кафедра вычислительной техники и защиты информации

Е.В. БУРЬКОВА

ОРГАНИЗАЦИЯ ЭВМ И СИСТЕМ

ЭЛЕКТРОННЫЙ КУРС ЛЕКЦИЙ

2.

Список рекомендуемой литературы1. Чередов А.Д. , Мальчуков А.Н. Организация ЭВМ и систем:

учебное пособие. – Томск: Изд-во Томского политехнического

университета, 2016. – 236 с.

2. Рыбальченко М.В. Организация ЭВМ и периферийные

устройства: учебное пособие. – Таганрог: Изд-во Южного

федерального университета, 2017. – 84 с.

3. Цилькер Б.Я., Орлов С.А.Организация ЭВМ и систем: учебник

– СПб.: Питер, 2006. - 668 с.

4. Мелехин В.Ф., Павловский Е.Г. Вычислительные машины,

системы и сети: учебник - 2-е изд., стер. – М.: Академия, 2007. 560с.

5. Пятибратов А.П., Гудыно, А.А. Кириченко. Вычислительные

системы, сети и телекоммуникации: учебник. - М.: Финансы и

статистика, 2008. -736 с.

6. Таненбаум , Э. Архитектура компьютера. – СПб.: Питер, 2006.

- 704 с.

7. Магда, Ю.С. Микроконтроллеры серии 8051: практический

подход. Москва, 2008. – 228 с.

2

3.

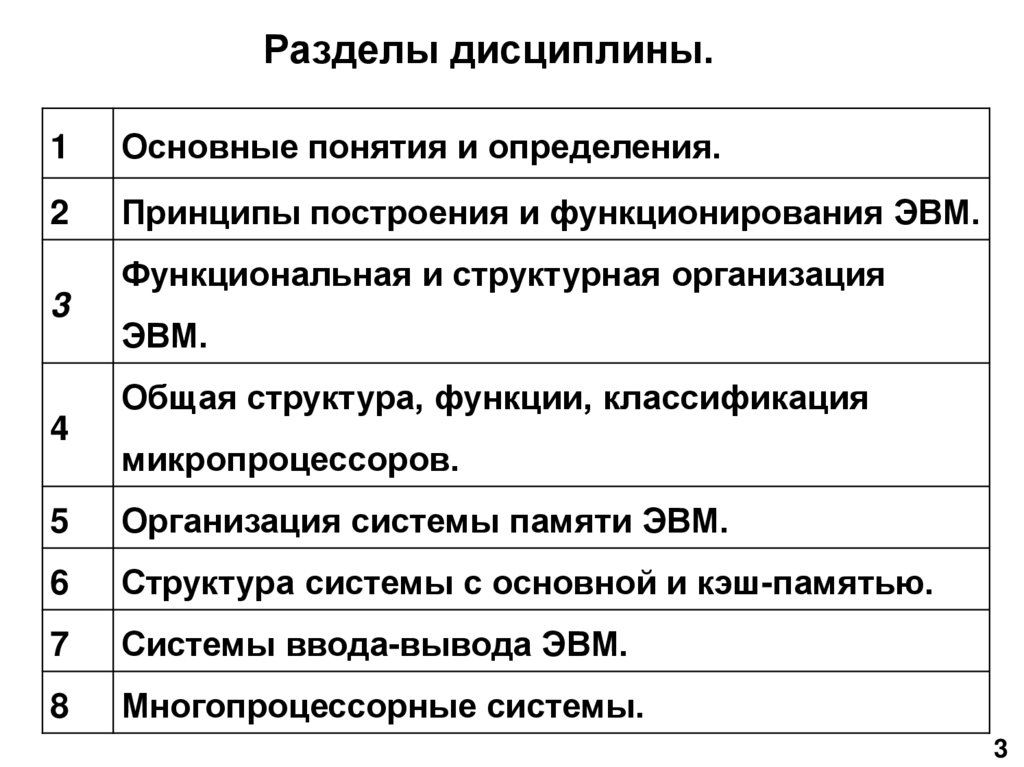

Разделы дисциплины.1

Основные понятия и определения.

2

Принципы построения и функционирования ЭВМ.

3

4

Функциональная и структурная организация

ЭВМ.

Общая структура, функции, классификация

микропроцессоров.

5

Организация системы памяти ЭВМ.

6

Структура системы с основной и кэш-памятью.

7

Системы ввода-вывода ЭВМ.

8

Многопроцессорные системы.

3

4.

Лекция 1. Основные понятия и определения.Вычислительная машина (ВМ) – это комплекс

технических и программных средств, предназначенный

для обработки данных, в том числе арифметических и

логических

операций,

получения

результатов

в

необходимой форме, выполняемых под управлением

системы команд.

Микропроцессор – микроэлектронное программноуправляемое

устройство, осуществляющее процесс

обработки информации и управляющее этим процессом.

Вычислительный комплекс (ВК) – несколько ЭВМ,

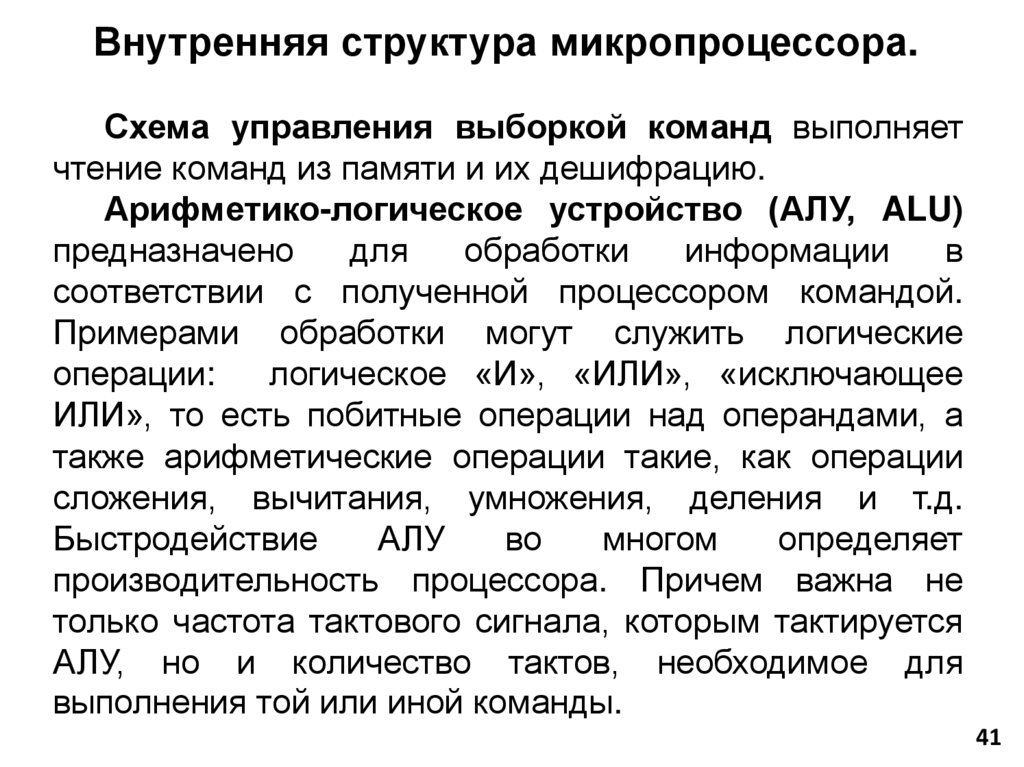

имеющих общие функциональные блоки, например,

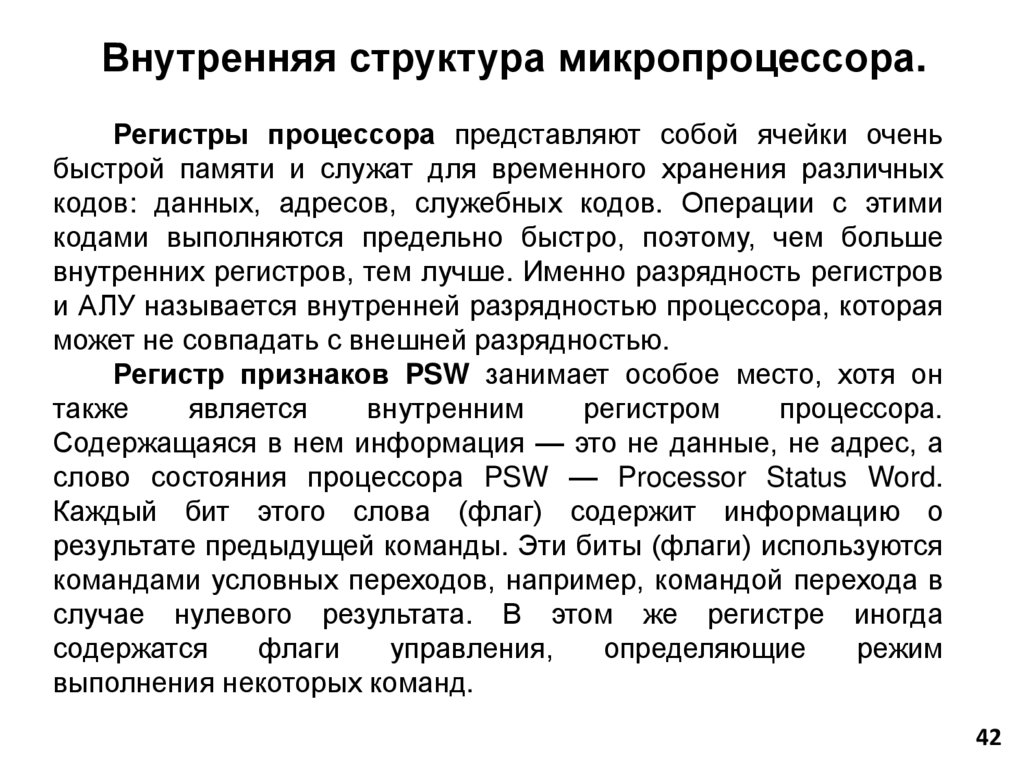

общую память.

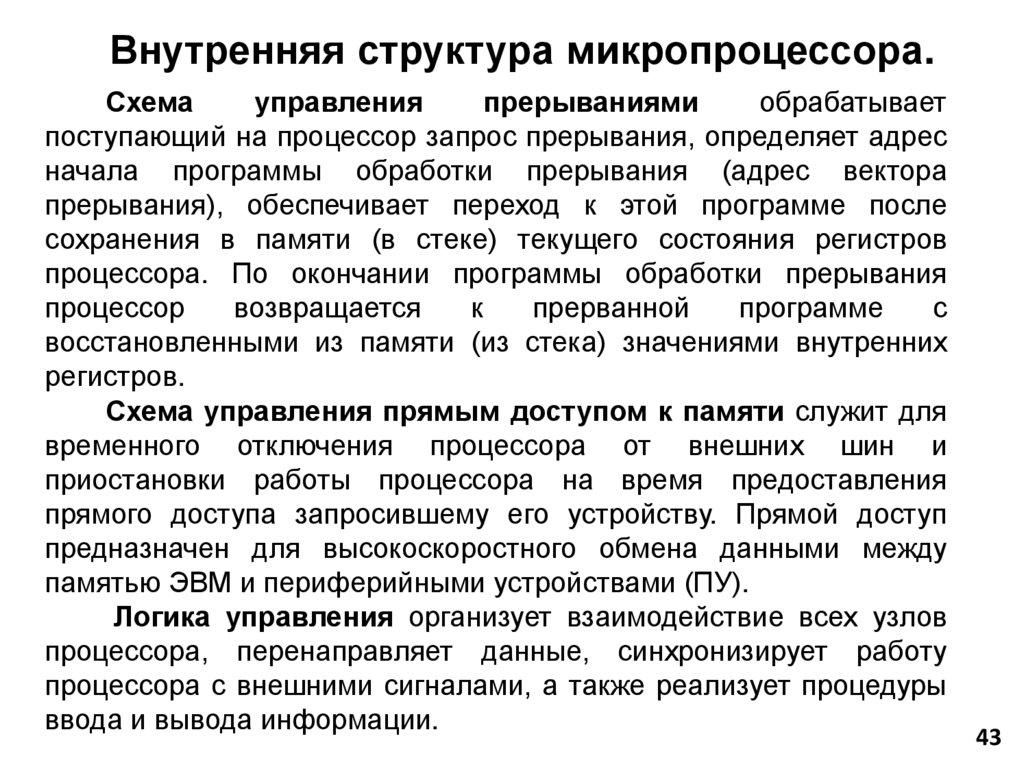

4

5.

Основные понятия и определения.Вычислительная система (ВС) – аппаратнопрограммная система из нескольких ЭВМ и

периферийного оборудования, взаимосвязанных и

взаимодействующих

аппаратно

и

логически,

локализованных в пространстве.

Вычислительная сеть (ВСТ) – система из

нескольких ЭВМ, функционирующих автономно, но

связанных между собой каналами передачи данных,

которые могут использоваться для обмена данными,

для синхронизации работы ЭВМ и для организации

совместного решения единой задачи.

5

6.

Основные понятия и определения.Архитектура ЭВМ – описание способа обработки

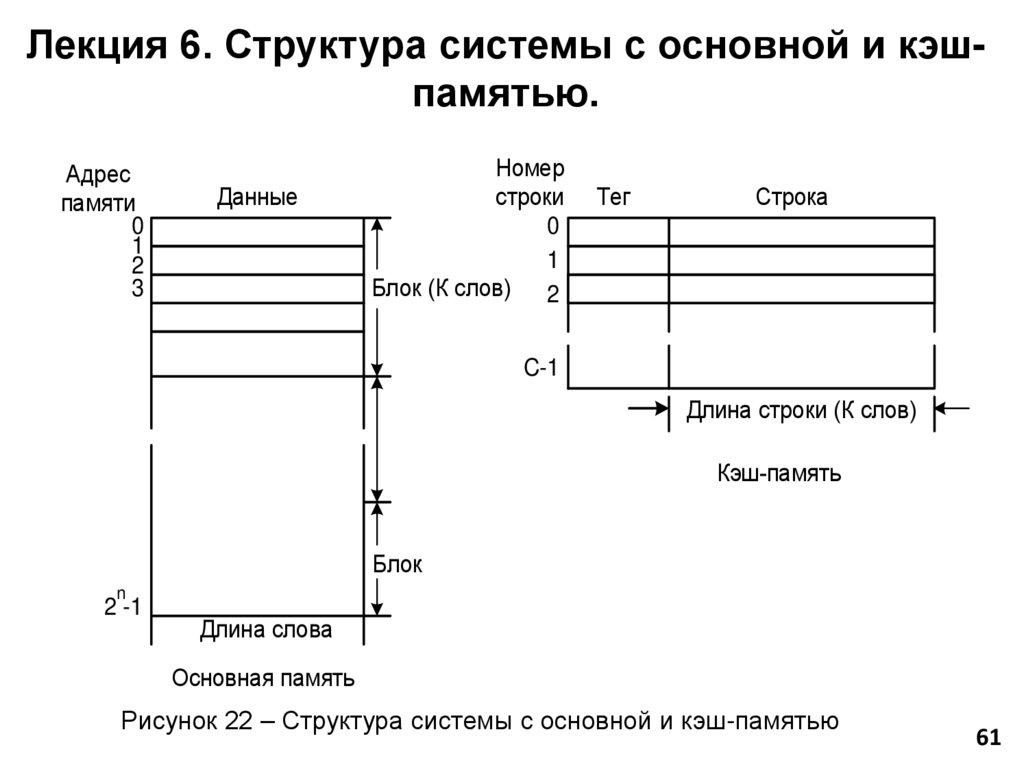

данных, логическое построение ВМ (например,

потоковая или циклическая обработка). Исходя из

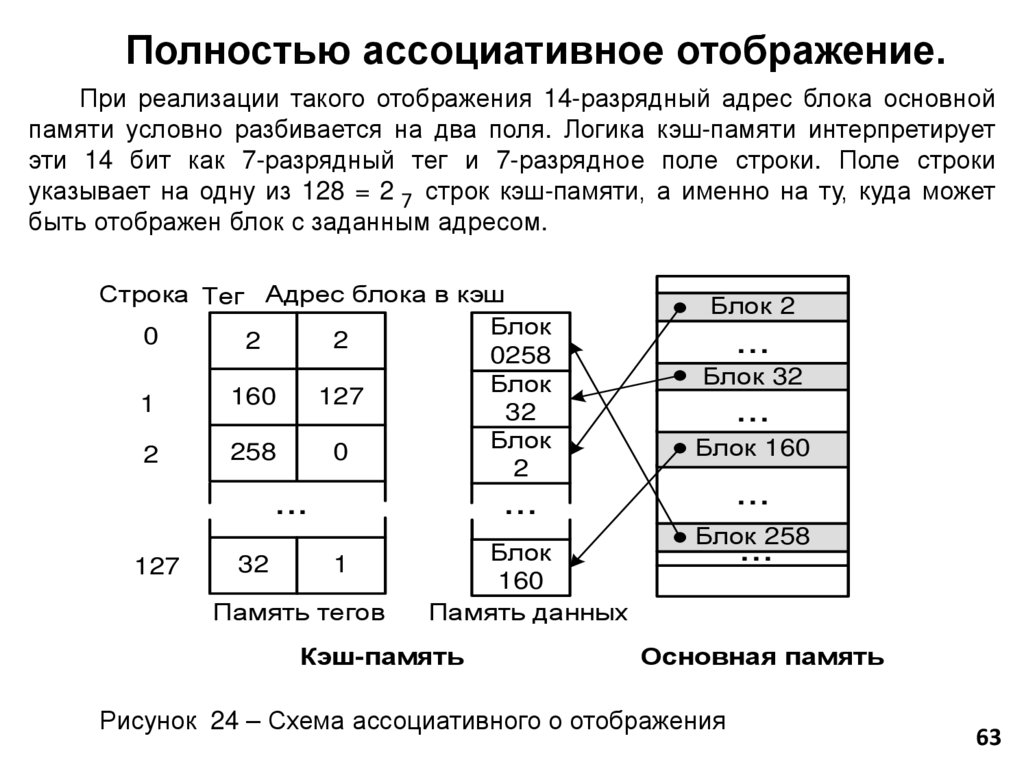

этого способа выбирают ту или иную организацию

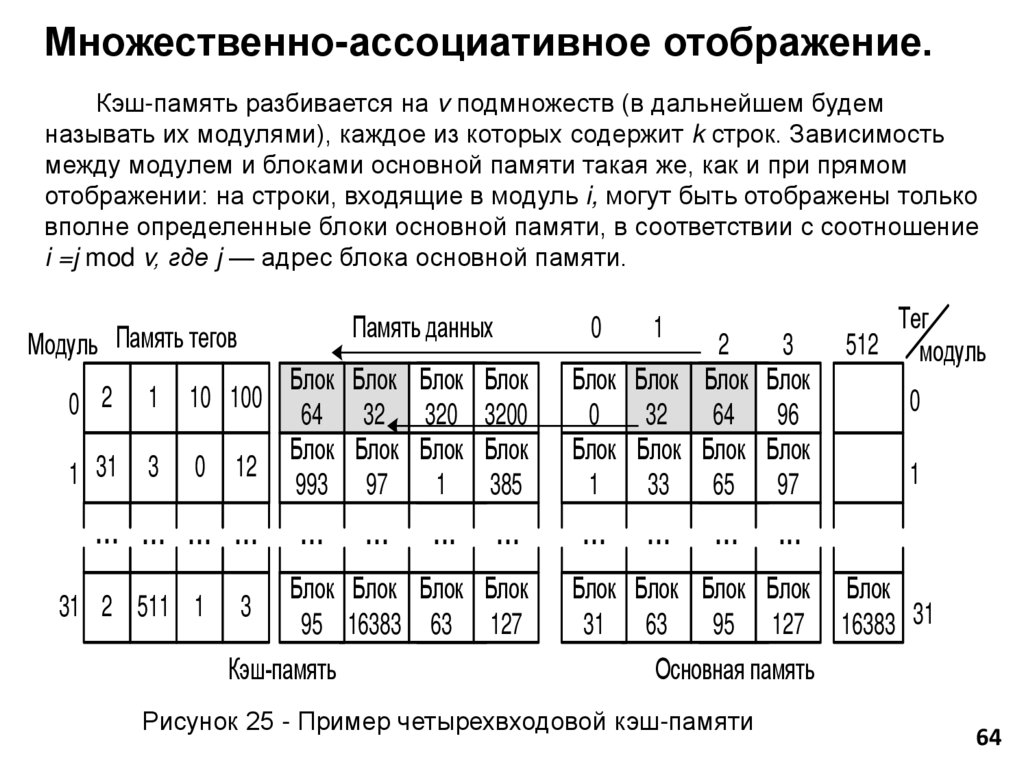

ЭВМ.

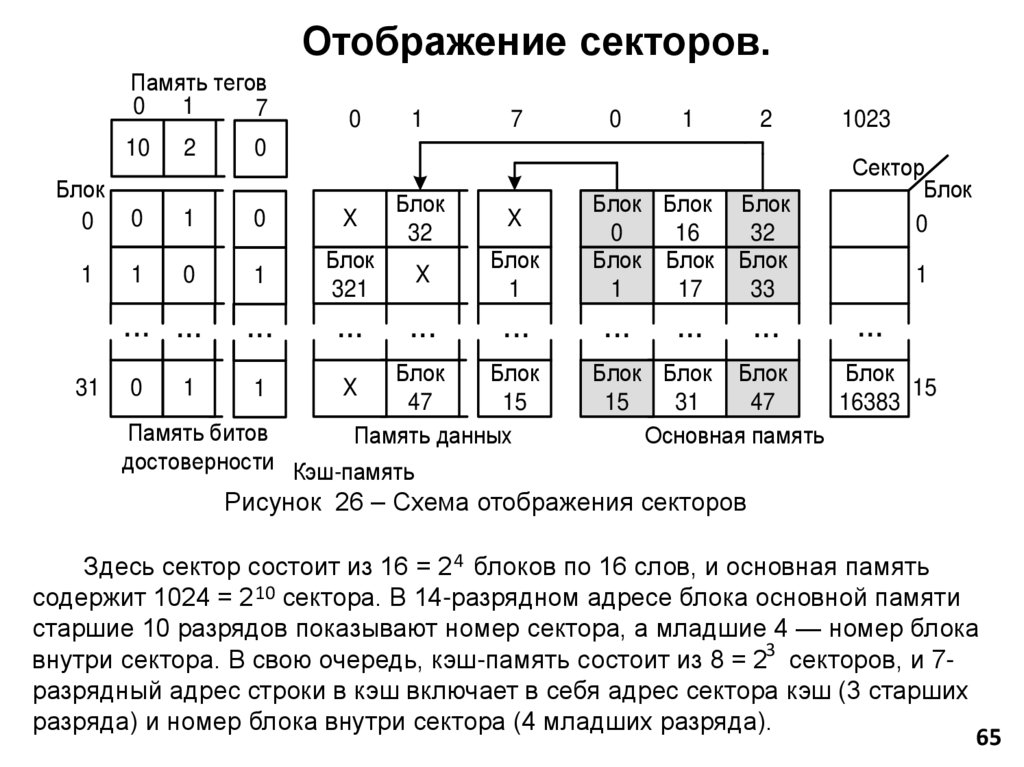

Организация ЭВМ – физическое построение ВМ,

описание устройства ЭВМ в виде совокупности

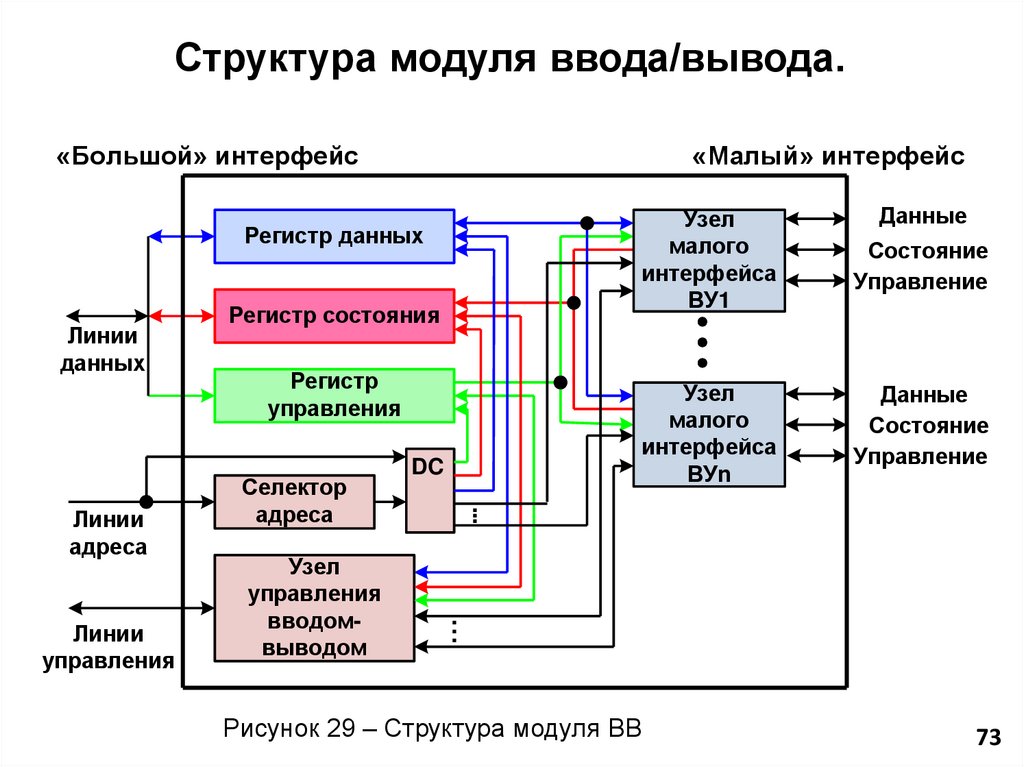

аппаратных блоков, или в виде совокупности функций

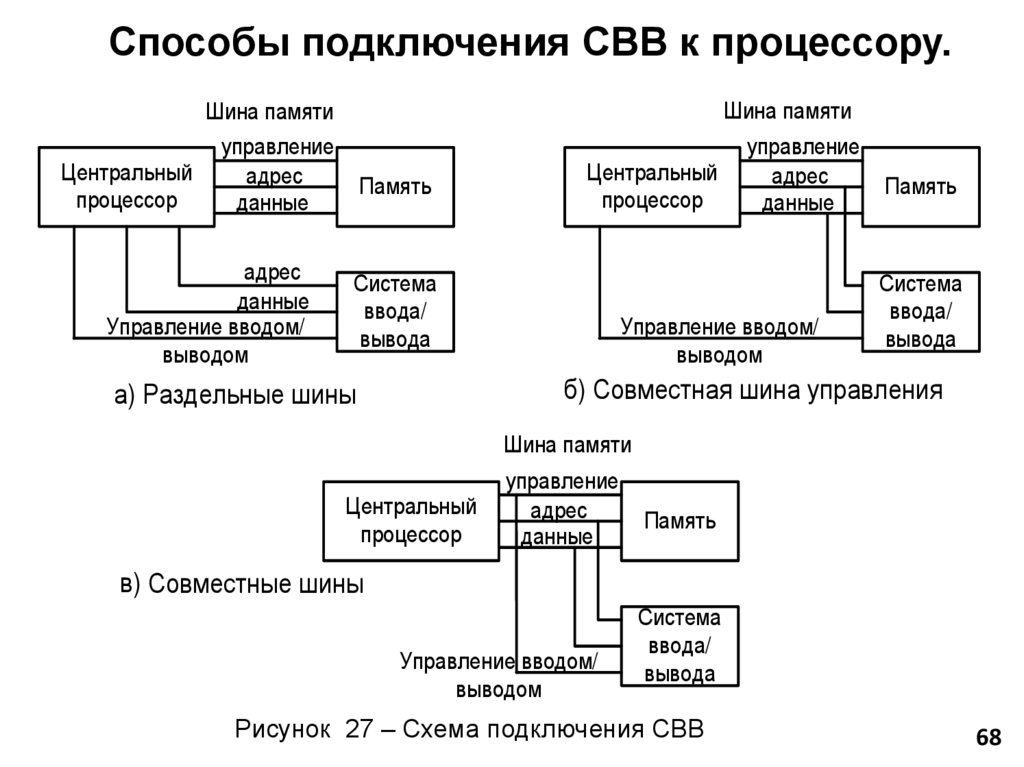

и подсистем обработки данных.

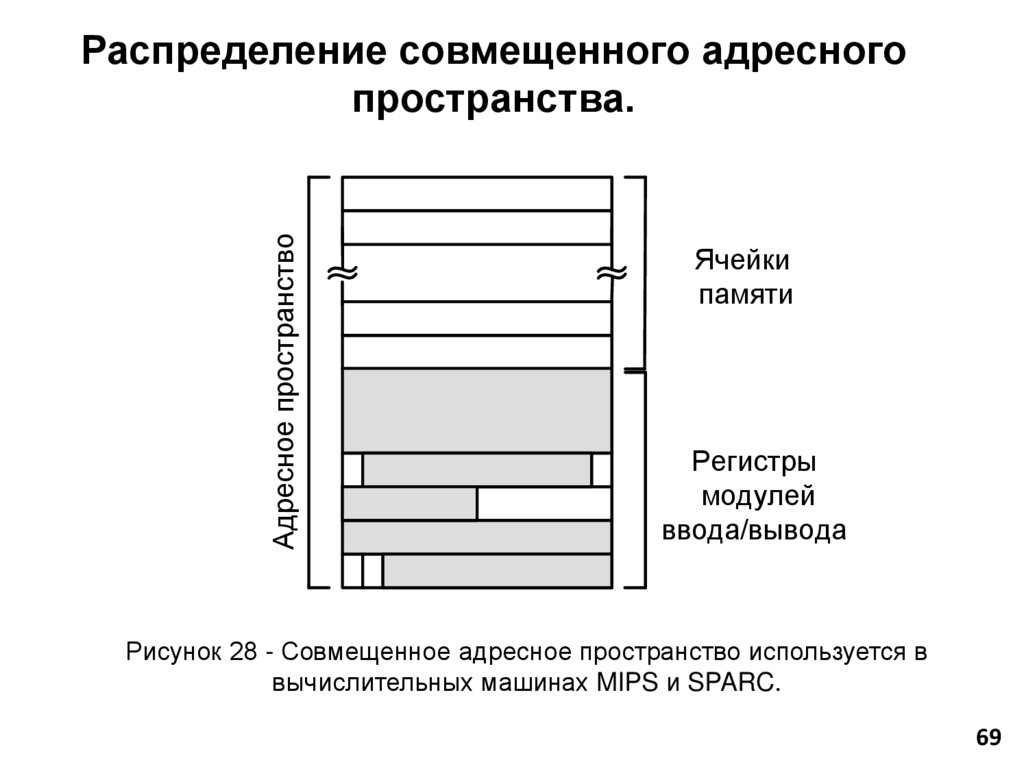

6

7.

Широкий и узкий взгляды на архитектуру иорганизацию ЭВМ.

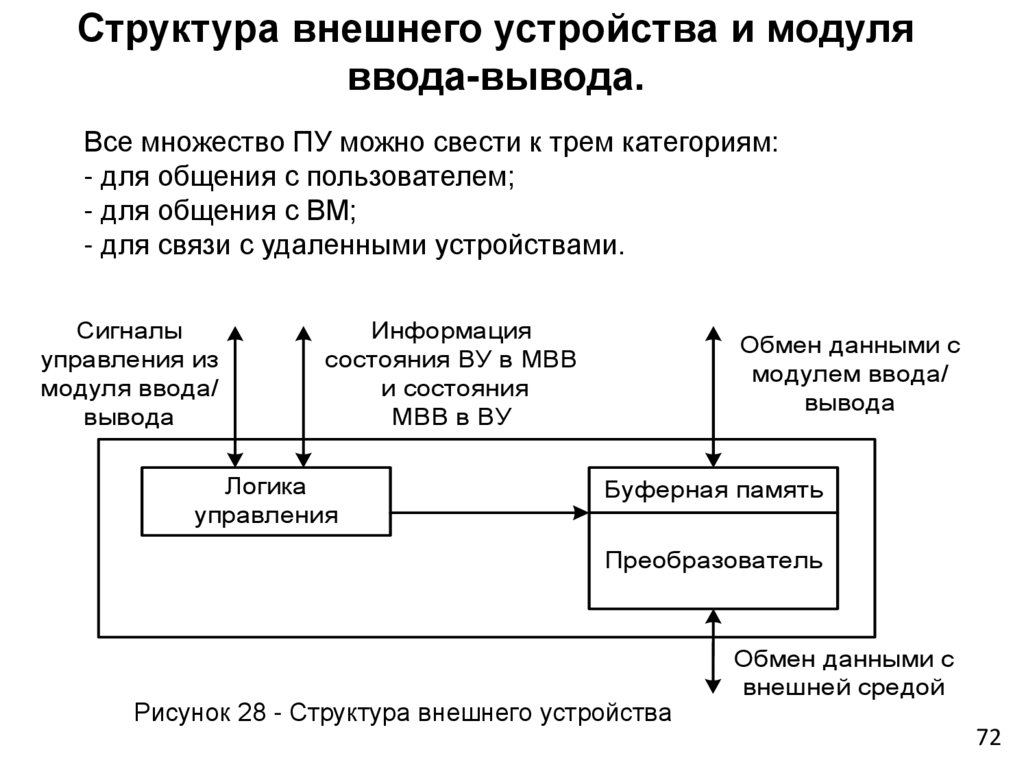

Узкий взгляд архитектура и организация

определяют и описывают внутреннее устройство ЭВМ

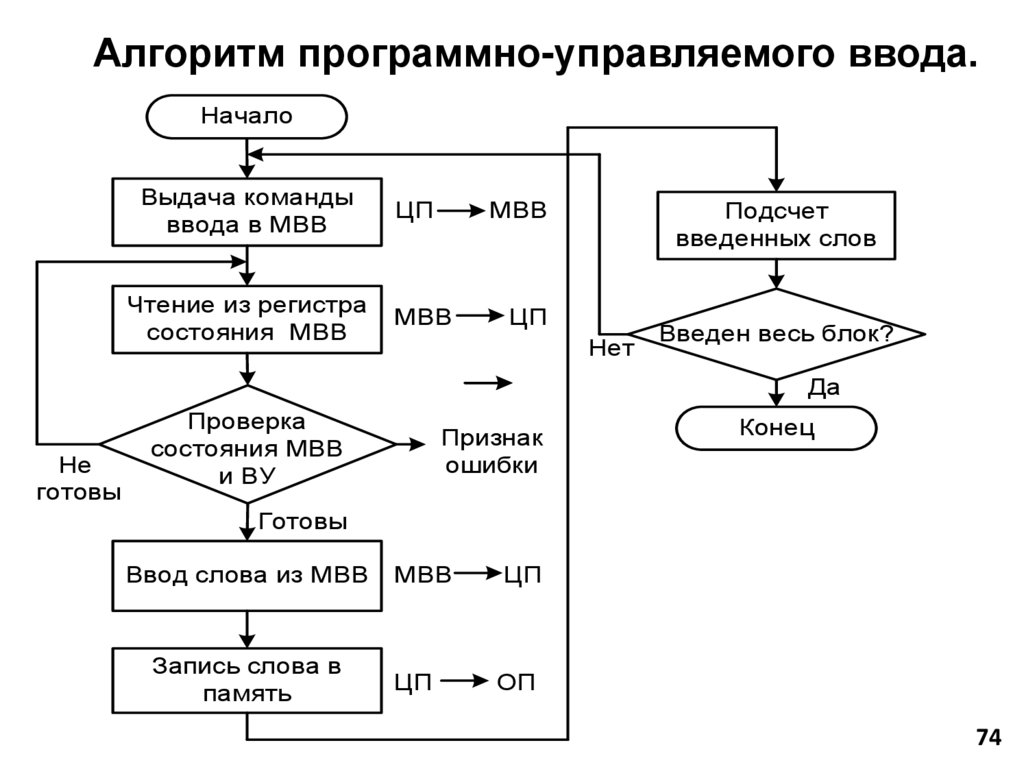

и ее свойства.

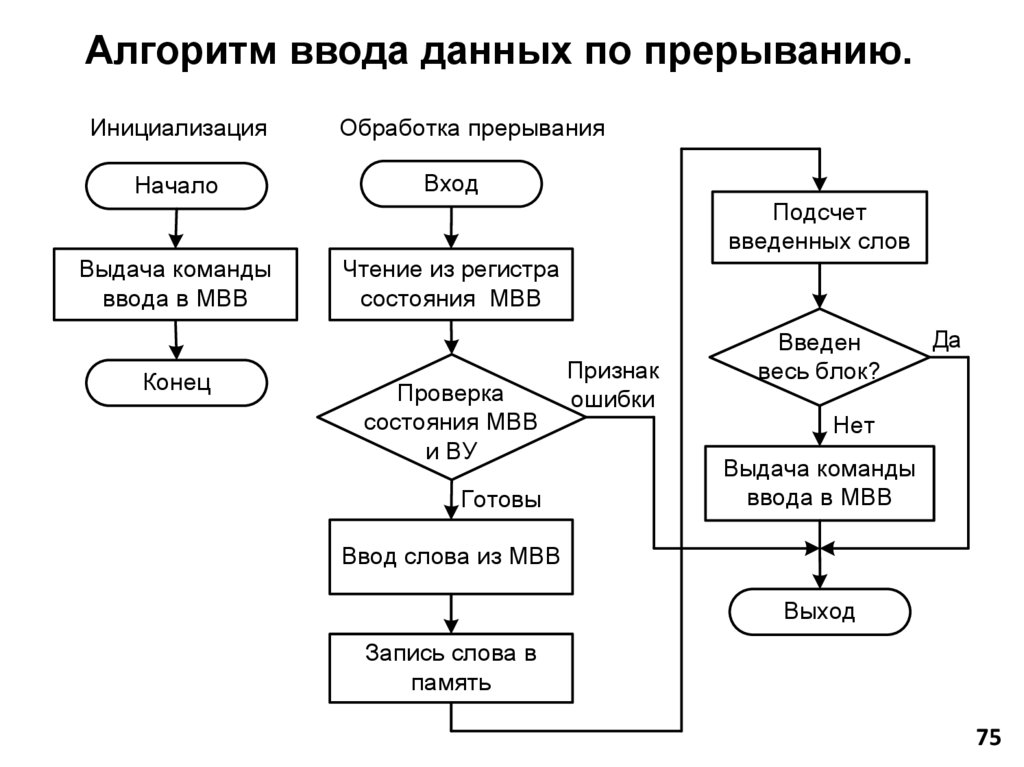

Широкий взгляд – архитектура и организация

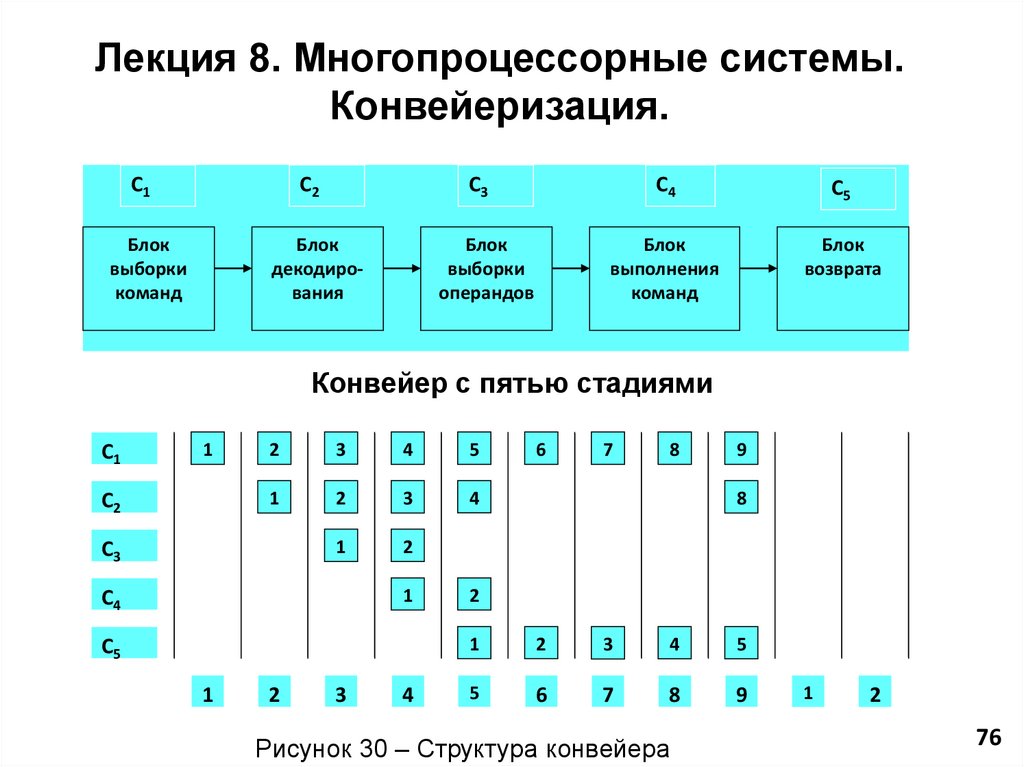

определяют не только устройство и свойства ЭВМ, но

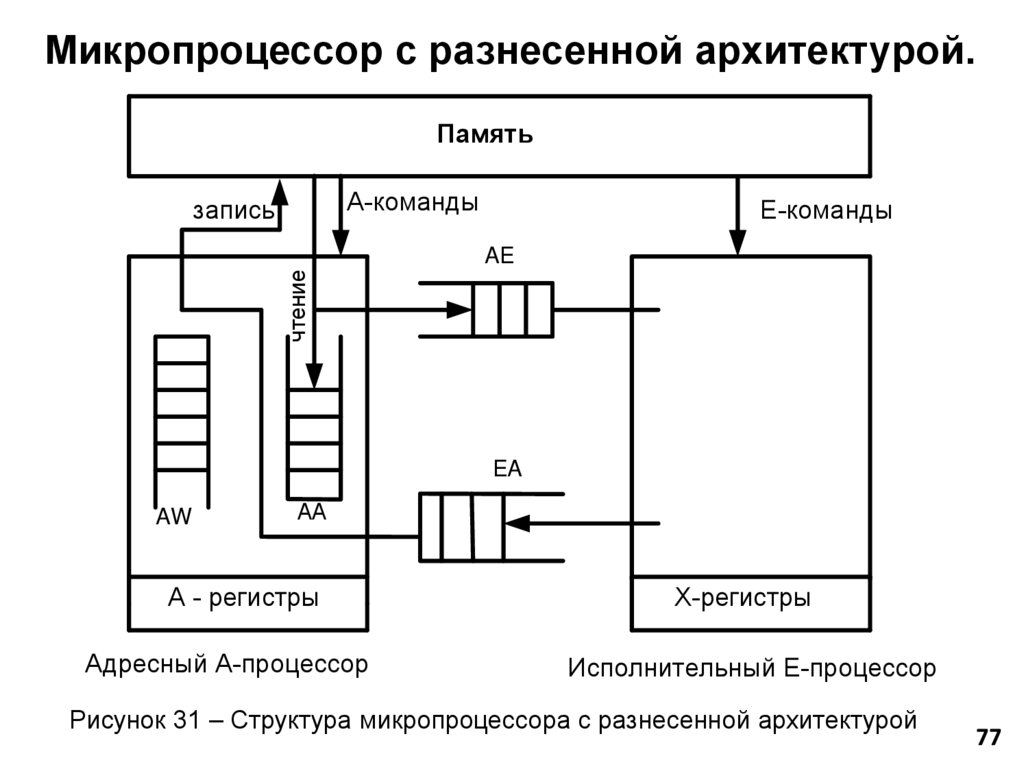

и процесс проектирования ЭВМ; указывают те

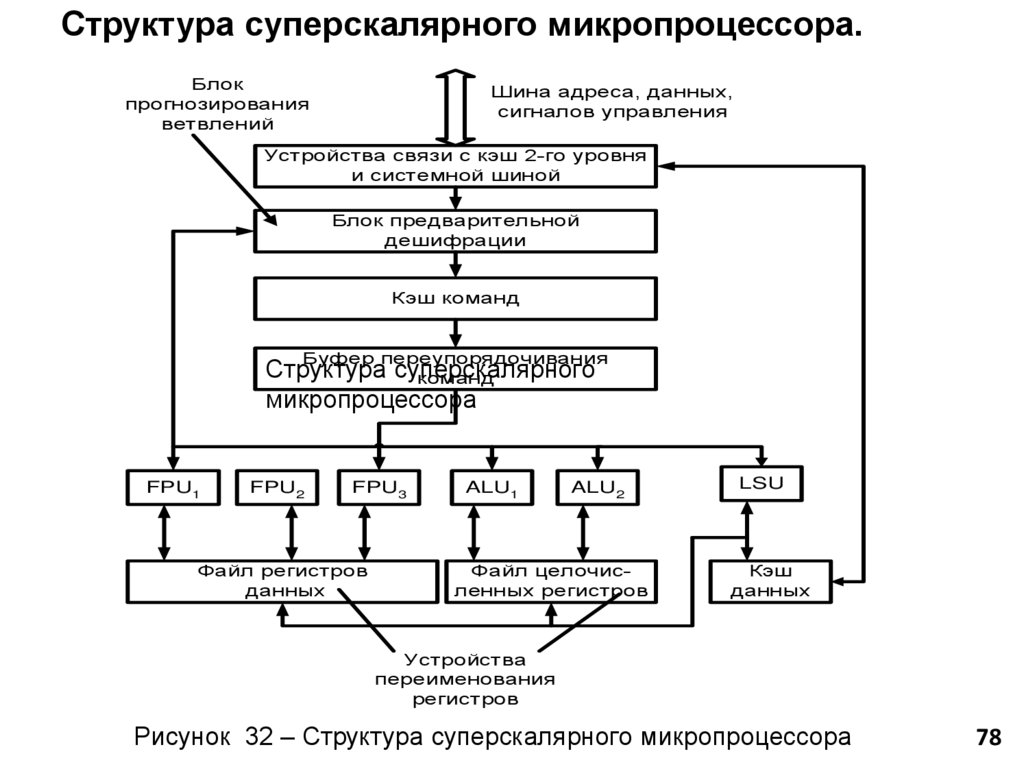

обязательные аспекты, этапы и задачи, которые

должны быть выполнены и решены при создании ЭВМ

или ВС.

7

8.

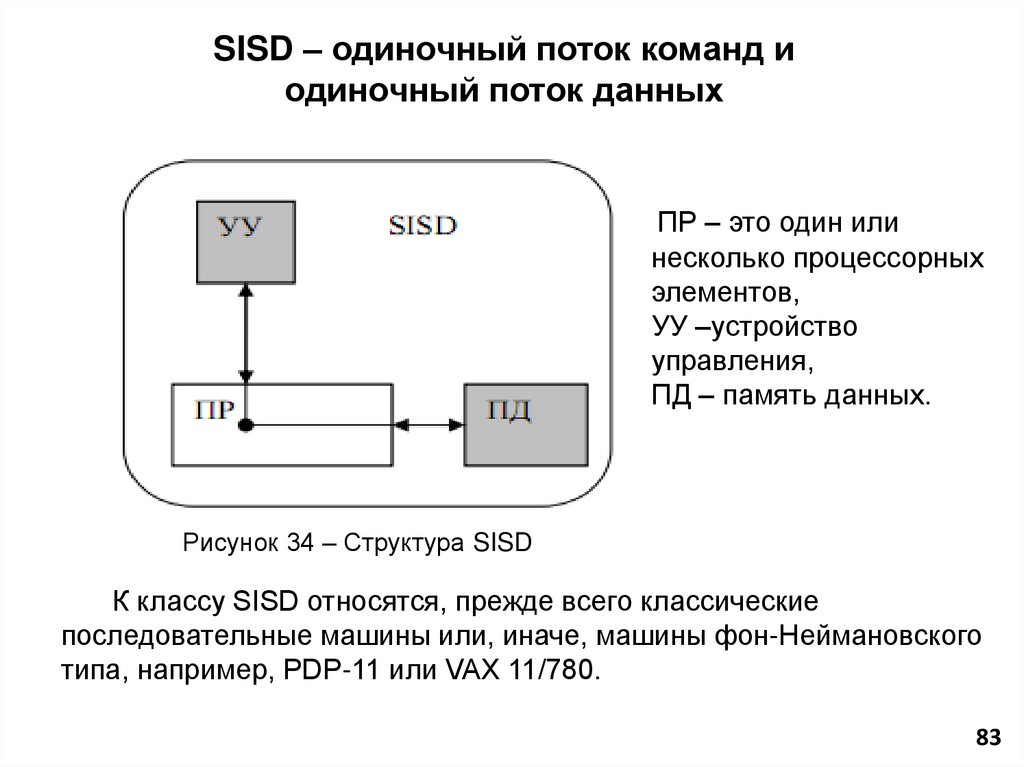

Архитектура ЭВМ.Широкий взгляд:

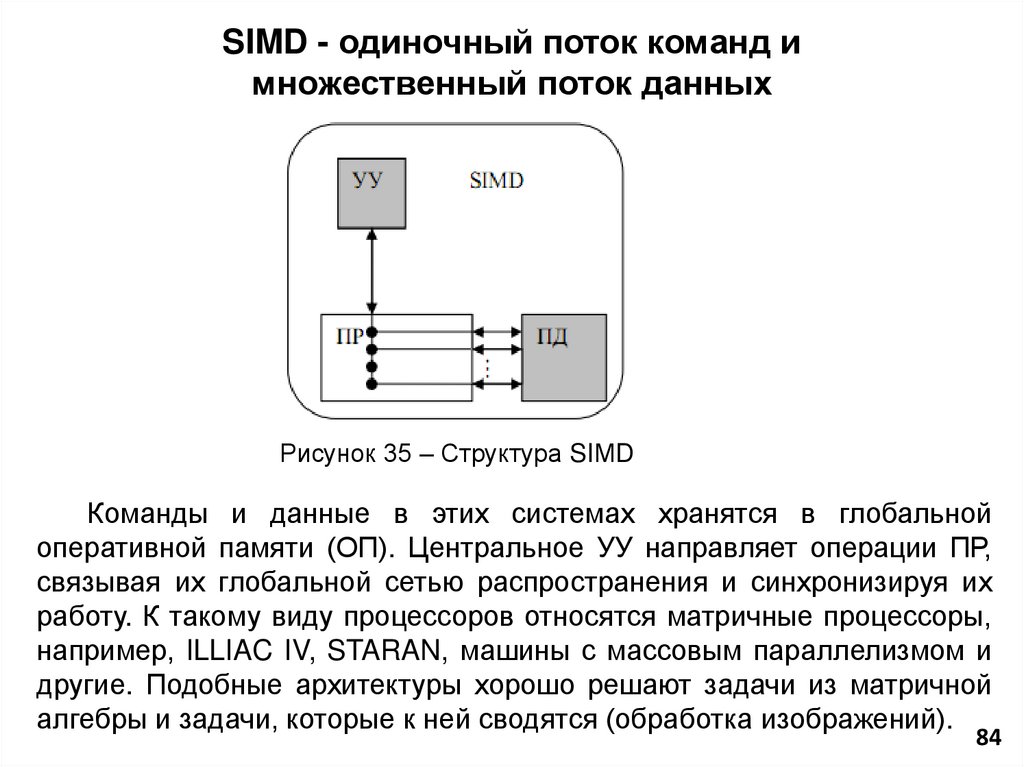

1. Концептуальная

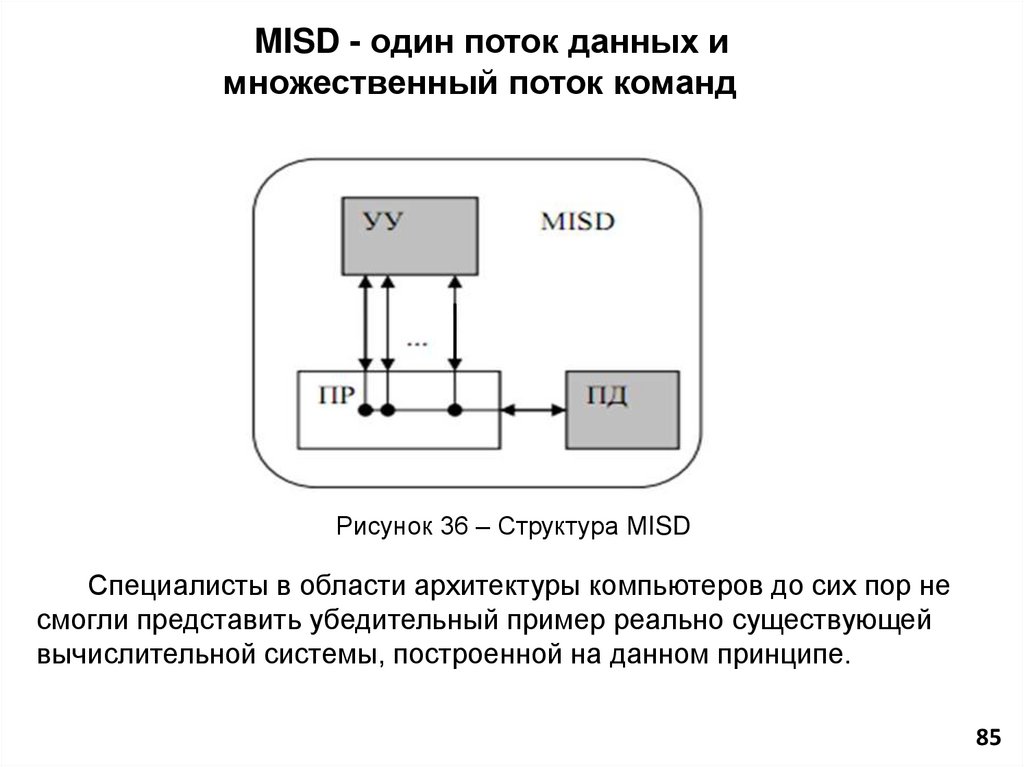

структура

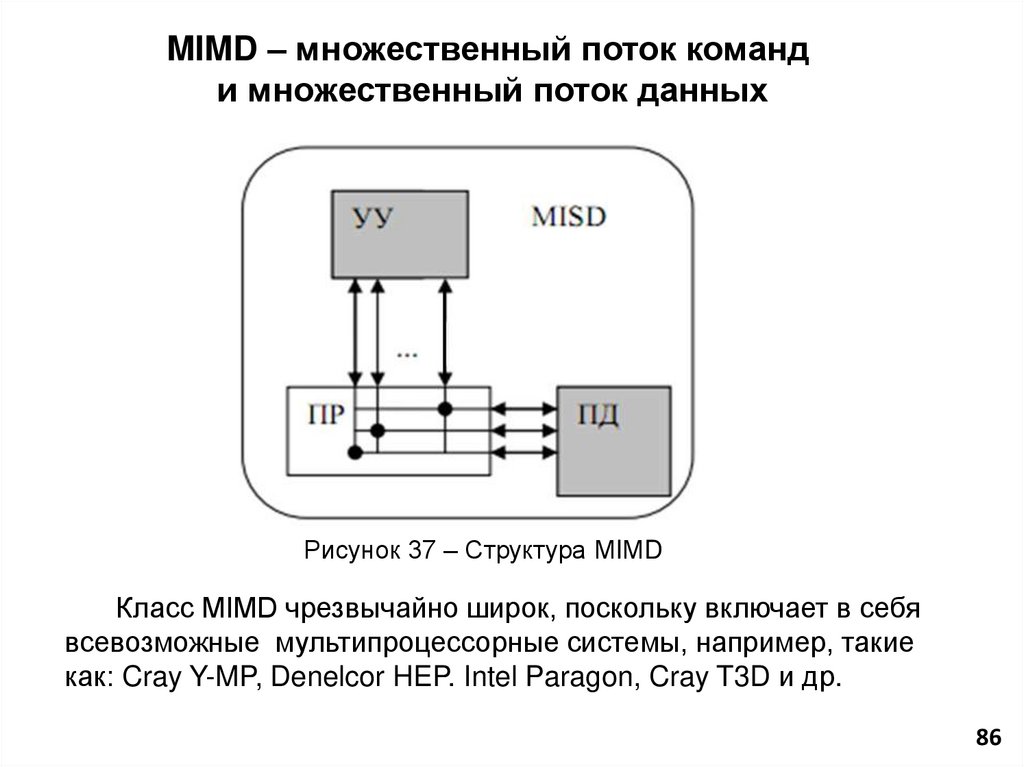

ВМ,

определяющая

проведение обработки информации, включая принципы

взаимодействия технических средств и программного

обеспечения.

2. Совокупность согласованных проектных решений на

уровнях системы команд, организации, программноаппаратной реализации.

Узкий взгляд:

Определяет представление и описание возможностей

ЭВМ видимых и доступных пользователю ЭВМ, например,

программисту.

Пример: архитектура системы команд (ISA), которая

описывает систему команд, форматы данных, регистры

и области памяти для хранения данных, т.е. то, что

нужно знать программисту.

8

9.

Организация ЭВМ.Широкий взгляд:

1. Организация

ЭВМ

определяет

устройство

и

проектирование

ЭВМ

на

уровне

крупных

функциональных блоков и подсистем ЭВМ (процессора,

блоков памяти, периферийных устройств, шин и т.п.).

2. Кроме

аппаратных

блоков

рассматривают

и

программные

функциональные

блоки

ЭВМ:

супервизоры, операционные системы, драйверы.

3. Не рассматривают электрические схемы и программный

код.

Узкий взгляд:

Организация ЭВМ определяет все аспекты внутреннего

устройства ЭВМ (аппаратуры и программных компонент),

которые «не видимы» для пользователя ЭВМ, то есть не

относятся к описанию архитектуры ЭВМ.

Пример: структурно-функциональная схема ЭВМ.

9

10.

Виды организации ЭВМ.• Структурная организация – модель ЭВМ в виде

совокупности функциональных блоков и связей между

ними. В качестве функциональных блоков рассматривают

как аппаратные блоки (процессор, память, шины), так и

программные компоненты (переключатель задач, драйвер

внешнего ЗУ, сетевой порт).

• Функциональная организация ЭВМ – абстрактная

модель совокупности функциональных возможностей ЭВМ

(кодирование исходных данных, программирование, ввод

и хранение программ и данных, управление ходом

обработки данных, контроль

за состоянием ЭВМ и

другие).

10

11.

Виды архитектурных описаний.1. Программная архитектура – совокупность аспектов

устройства ЭВМ значимых для программного

обеспечения (система команд, форматы данных, API

операционной системы и т.д.).

2. Аппаратная

архитектура

–

принципы

функционирования аппаратных блоков и подсистем

ЭВМ и интерфейсов между ними.

Виды программной архитектуры.

1. Прикладная программная архитектура – аспекты

связанные с организацией программной обработки

данных (система команд, форматы данных, модель

памяти, организация операционной системы).

2. Системная программная архитектура – аспекты

связанные с программным управлением блоками и

подсистемами ЭВМ (управление контроллерами

ввода вывода, использование системы прерываний ). 11

12.

Организацияи

архитектура

–

дополняющие и пересекающиеся друг с

другом

представления

рассматривают

единый

ЭВМ.

набор

Они

аспектов

устройства ЭВМ, но с разных точек зрения.

12

13.

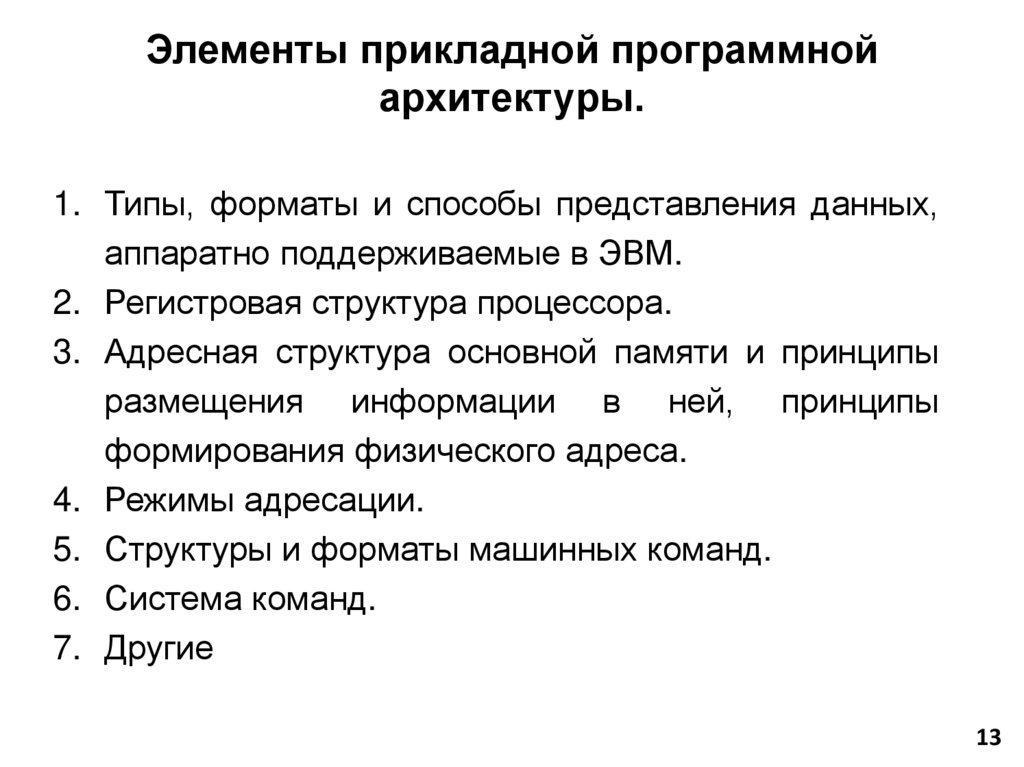

Элементы прикладной программнойархитектуры.

1. Типы, форматы и способы представления данных,

аппаратно поддерживаемые в ЭВМ.

2. Регистровая структура процессора.

3. Адресная структура основной памяти и принципы

размещения информации в ней, принципы

формирования физического адреса.

4. Режимы адресации.

5. Структуры и форматы машинных команд.

6. Система команд.

7. Другие

13

14.

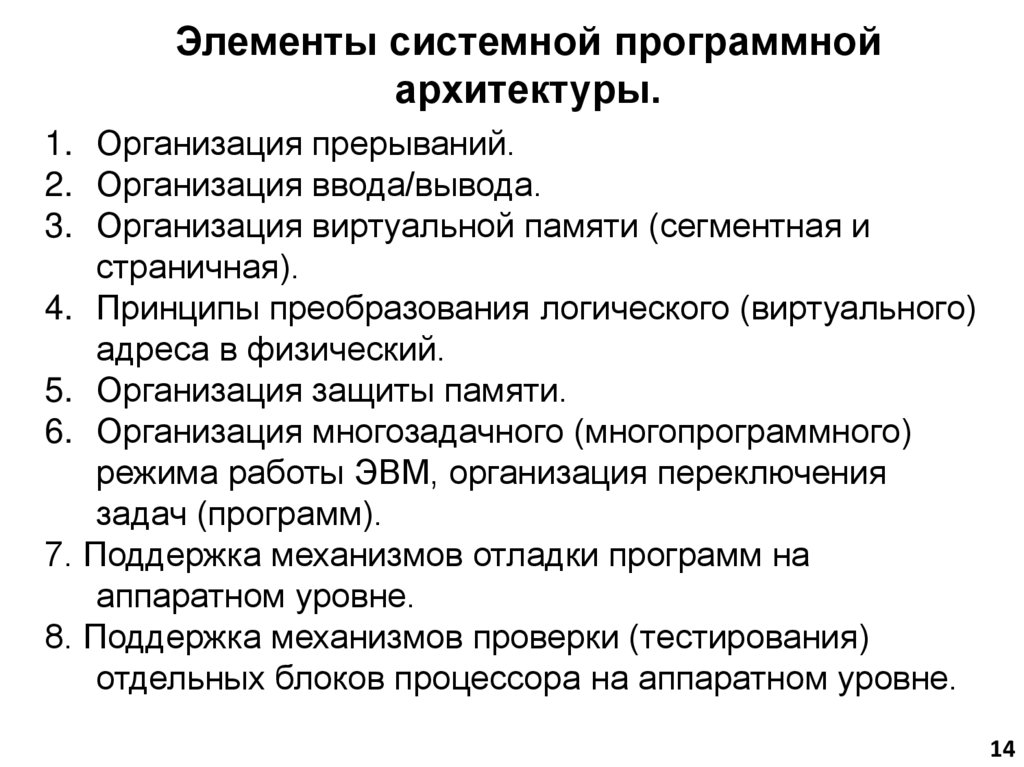

Элементы системной программнойархитектуры.

1. Организация прерываний.

2. Организация ввода/вывода.

3. Организация виртуальной памяти (сегментная и

страничная).

4. Принципы преобразования логического (виртуального)

адреса в физический.

5. Организация защиты памяти.

6. Организация многозадачного (многопрограммного)

режима работы ЭВМ, организация переключения

задач (программ).

7. Поддержка механизмов отладки программ на

аппаратном уровне.

8. Поддержка механизмов проверки (тестирования)

отдельных блоков процессора на аппаратном уровне.

14

15.

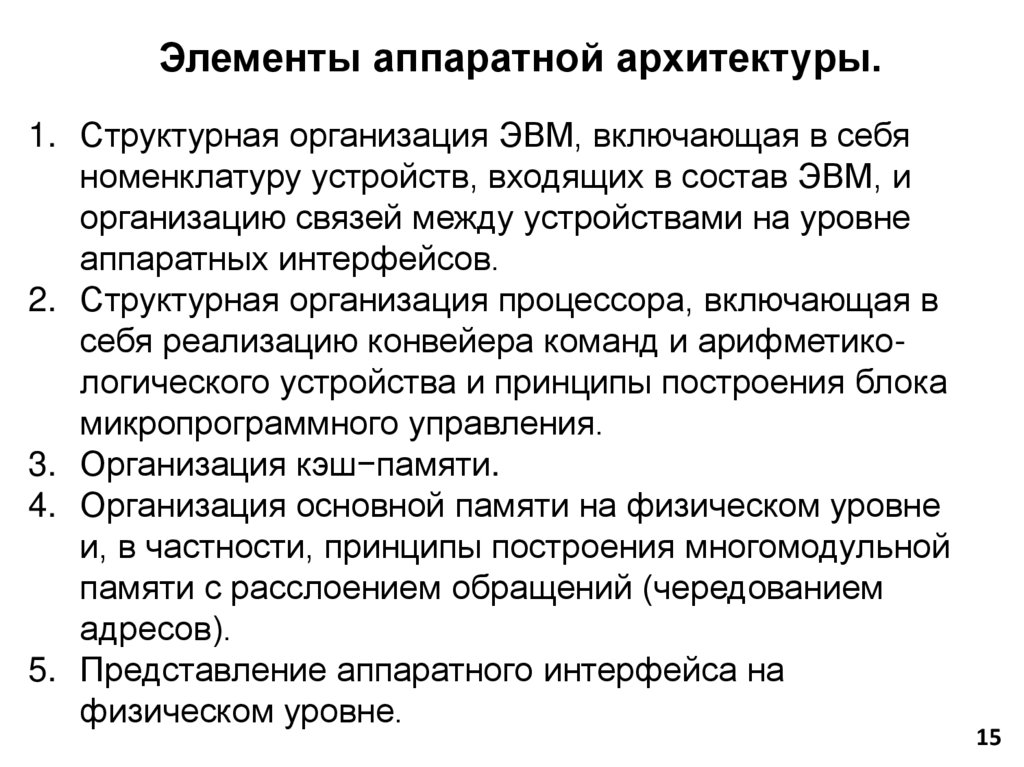

Элементы аппаратной архитектуры.1. Структурная организация ЭВМ, включающая в себя

номенклатуру устройств, входящих в состав ЭВМ, и

организацию связей между устройствами на уровне

аппаратных интерфейсов.

2. Структурная организация процессора, включающая в

себя реализацию конвейера команд и арифметикологического устройства и принципы построения блока

микропрограммного управления.

3. Организация кэш−памяти.

4. Организация основной памяти на физическом уровне

и, в частности, принципы построения многомодульной

памяти с расслоением обращений (чередованием

адресов).

5. Представление аппаратного интерфейса на

физическом уровне.

15

16.

Основные характеристикии классификация компьютеров

Архитектура компьютера – это многоуровневая

иерархия аппаратурно-программных средств, из

которых строится ЭВМ.

Каждый из уровней допускает многовариантное

построение и применение.

Современный компьютер

относится к классу открытых систем. Конкретная

реализация каждого из уровней таких систем определяет

особенности структурного построения, что может менять

характеристики в широких пределах.

Именно архитектура отражает основные принципы,

положенные

в

основу

построения

компьютеров.

Детализацией архитектурного и структурного построения

ЭВМ занимаются различные категории специалистов

вычислительной техники.

17.

Инженеры-схемотехники проектируют отдельныетехнические устройства и разрабатывают методы их

сопряжения друг с другом.

Системные программисты создают программы

управления техническими средствами, информационного

взаимодействия

между

уровнями,

организации

вычислительного процесса.

Программисты-прикладники разрабатывают пакеты

программ более высокого уровня, которые обеспечивают

взаимодействие пользователей с ЭВМ и необходимый

сервис при решении ими своих задач.

Указанные специалисты рассматривают понятие

архитектуры в более узком смысле. Для них наиболее

важные структурные особенности сосредоточены в

наборе команд ЭВМ, являющемся границей между

аппаратными и программными средствами.

18.

ПользователиЭВМ,

которые

обычно

не

являются

профессионалами

в

области

вычислительной

техники,

рассматривают архитектуру через более сложные аспекты,

касающиеся их взаимодействия с ЭВМ (человеко-машинного

интерфейса), начиная со следующих групп характеристик ЭВМ,

определяющих ее структуру:

• технические и эксплуатационные характеристики ЭВМ

(быстродействие и производительность; показатели надежности,

достоверности, точности; емкость оперативной и внешней памяти;

габаритные размеры; стоимость технических и программных средств;

особенности эксплуатации и др.);

• характеристики и состав функциональных модулей базовой

конфигурации ЭВМ;

возможность расширения состава технических и программных

средств; возможность изменения структуры;

• состав программного обеспечения ЭВМ и сервисных услуг

(операционная система

или

среда,

пакеты

прикладных

программ,

средства

автоматизации программирования).

19.

Важнейшими характеристиками компьютеров служатбыстродействие и производительность.

Быстродействие

характеризуется

числом

определенного типа команд, выполняемых ЭВМ за одну

секунду.

Производительность

–

это

объем

работ

(например, число стандартных программ), выполняемый

ЭВМ в единицу времени.

Определение характеристик быстродействия и

производительности представляет собой очень сложную

инженерную и научную задачу, до настоящего времени

не имеющую единых подходов и методов решения.

Очень часто вместо конкретных значений этих

характеристик указывают только тактовую частоту

микропроцессора, поскольку она непосредственно

связана со скоростью вычислений.

20.

Другой важнейшей характеристикой ЭВМ являетсяемкость запоминающих устройств.

Емкость

памяти

измеряется

количеством

структурных единиц информации, которое может

одновременно находиться в памяти. Этот показатель

позволяет определить, какой набор программ и данных

может быть одновременно размещен в памяти.

Наименьшей структурной единицей информации

является бит – одна двоичная цифра. Как правило,

емкость памяти оценивается в более крупных единицах

измерения

– байтах (байт равен 8 битам). Следующими

единицами измерения служат

21.

22.

23.

24.

25.

1. MIPS (Mega Instruction Per Second) – миллион команд всекунду;

2. MFLOPS (Mega Floating Operations Per Second) –

миллион операций над числами с плавающей запятой

в секунду;

3. GFLOPS (Giga Floating Operations Per Second) –

миллиард операций над числами с плавающей запятой

в секунду;

4. TFLOPS (Tera Floating Operations Per Second) –

триллион операций над числами с плавающей запятой

в секунду;

5. PFLOPS (Peta Floating Operations Per Second) –

квадриллион операций над числами с плавающей

запятой в секунду.

26.

27.

28.

Энергоэффективность процессораВ последнее время при сравнении процессоров пользуются

отношением производительности к энергопотреблению, которое

получило

название

энергоэффективность

процессора.

Разработчики

процессоров

предложили

оценивать

производительность (Р) как произведение тактовой (рабочей)

частоты процессора (f) на величину k, определяющую

количество инструкций, исполняемых процессором за один

такт:

P = f · k.

Получается, что увеличить производительность можно,

поднимая частоту и/или увеличивая количество инструкций,

выполняемых за один такт. Первый подход ведет к увеличению

энергопотребления, а второй требует использования определенной

микроархитектуры процессора (многоядерной), в которой заложены

различные технологии, направленные на повышение количества

инструкций, выполняемых процессором за один такт.

29.

Что касается энергопотребления (W), то оно вычисляется какпроизведение тактовой частоты (f) процессора на квадрат

напряжения U, при котором функционирует процессорное ядро, и

некоторую величину Cd (динамическая емкость), определяемую

микроархитектурой процессора и зависящую от количества

транзисторов в кристалле и их активности во время работы

процессора:

Из приведенных формул вытекает следующее соотношение,

определяющее энергоэффективность процессора:

Из формулы следует, что для получения наилучшего показателя

разработчикам

необходимо

работать

над

оптимизацией

микроархитектуры

с

целью

улучшения

функциональности

исполнительных блоков, при этом не допуская чрезмерного

увеличения динамической емкости. Что касается тактовой частоты, то,

как показывают приведенные выкладки, на рассматриваемое

соотношение она вообще не влияет. Напряжение питания ядра

зависит не столько от микроархитектуры, сколько от технологических

особенностей изготовления процессора.

30.

Частовместо

характеристики

энергопотребление

используют

характеристику рассеиваемая тепловая мощность процессора. Для этого

используется специальный термин TDP, который расшифровывается как

термопакет (thermal design package) – это величина, показывающая, на

отвод какой тепловой мощности должна быть рассчитана система

охлаждения процессора.

Как правило, TDP показывает не максимальное теоретическое

тепловыделение процессора, а типичное тепловыделение в реальных

приложениях. Иногда, при длительных нагрузках на процессор (например, при

кодировании видео), температура процессора может превысить заданный TDP.

В этих случаях современные процессоры или дают сигнал выключения

компьютера, или переходят в так называемый режим троттлинга (trottling), когда

процессор пропускает часть циклов.

К другим технико-эксплуатационным характеристикам ЭВМ относятся:

1. разрядность обрабатываемых слов и кодовых шин интерфейса;

2. типы системного и локального интерфейсов;

3. тип и емкость оперативной памяти;

4. тип и емкость накопителя на жестком магнитном диске;

5. тип и емкость кэш-памяти;

6. тип видеоадаптера и видеомонитора;

7. наличие средств для работы в компьютерной сети;

8. наличие и тип программного обеспечения;

9. надежность ЭВМ;

10. стоимость;

11. габариты и масса.

31.

Лекция 2. Принципы построения ифункционирования ЭВМ.

Эволюция вычислительных машин.

Историю развития ЭВМ можно представить в виде

трех этапов:

1. донеймановского периода;

2. эры вычислительных машин и систем с фоннеймановской архитектурой;

3. постнеймановской эпохи — эпохи параллельных и

распределенных

вычислений,

где

наряду

с

традиционным подходом все большую роль начинают

играть отличные от фон-неймановских принципы

организации вычислительного процесса.

16

32.

Эволюция вычислительных машин.Первые четыре поколения традиционно связывают с

элементной базой вычислительных систем: электронные

лампы, полупроводниковые приборы, интегральные схемы

малой степени интеграции (ИМС), большие (БИС),

сверхбольшие

(СБИС)

и

ультрабольшие

(УБИС)

интегральные микросхемы.

Пятое поколение ассоциируют не столько с новой

элементной базой, сколько с интеллектуальными

возможностями ВС (векторные суперЭВМ).

Шестое поколение (от 1990-):

- параллельные вычисления;

- резко возросший уровень рабочих станций. В

процессорах

новых

рабочих

станций

успешно

совмещаются

RISC-архитектура,

конвейеризация

и

параллельная обработка;

- рост глобальных сетей.

17

33.

Принцип программного управления фон-Неймана.Согласно стандарту ISO 2382/1-84 (Международная

организация по стандартизации, International Organization

for Standardization), программа для ВМ — это

«упорядоченная последовательность команд, подлежащая

обработке».

ВМ, где определенным образом закодированные

команды программы хранятся в памяти, известна под

названием вычислительной машины с хранимой в

памяти программой (ВМ фон Неймана). Сущность фоннеймановской концепции ВМ сводится к четырем

принципам:

• двоичного кодирования;

• программного управления;

• однородности памяти;

• адресности.

18

34.

Принцип двоичного кодирования.Согласно этому принципу, вся информация, как данные,

так и команды, кодируются двоичными цифрами 0 и 1.

Каждый тип информации представляется двоичной

последовательностью и имеет свой формат.

Последовательность битов в формате, имеющая

определенный смысл, называется полем.

В числовой информации обычно выделяют поле знака

и поле значащих разрядов.

В формате команды можно выделить два поля:

1) поле кода операции (КОп);

2) поле адресов (адресную часть — АЧ).

19

35.

Принцип двоичного кодирования.Код операции представляет собой указание, какая

операция должна быть выполнена, и задается с помощью

r-разрядной двоичной комбинации.

Вид адресной части и число составляющих ее адресов

зависят типа команды:

- в командах преобразования данных АЧ содержит

адреса объектов обработки (операндов) и результата;

- в командах изменения порядка вычислений — адрес

следующей команды программы;

- в командах ввода/вывода - номер устройства

ввода/вывода.

Адресная часть также представляется двоичной

последовательностью, длину которой обозначим через p.

Таким образом, команда в вычислительной машине

имеет вид

(r + р )-разрядной двоичной комбинации.

20

36.

Принцип программного управления.Все вычисления, предусмотренные алгоритмом

решения задачи, должны быть представлены в виде

программы,

состоящей

из

последовательности

управляющих слов - команд. Каждая команда

предписывает некоторую операцию из набора операций,

реализуемых вычислительной машиной.

Команды программы хранятся в последовательных

ячейках памяти вычислительной машины и выполняются

в естественной последовательности, то есть в порядке

их положения в программе.

При необходимости, с помощью специальных команд,

эта последовательность может быть изменена. Решение

об изменении порядка выполнения команд программы

принимается либо на основании анализа результатов

предшествующих вычислений, либо безусловно.

21

37.

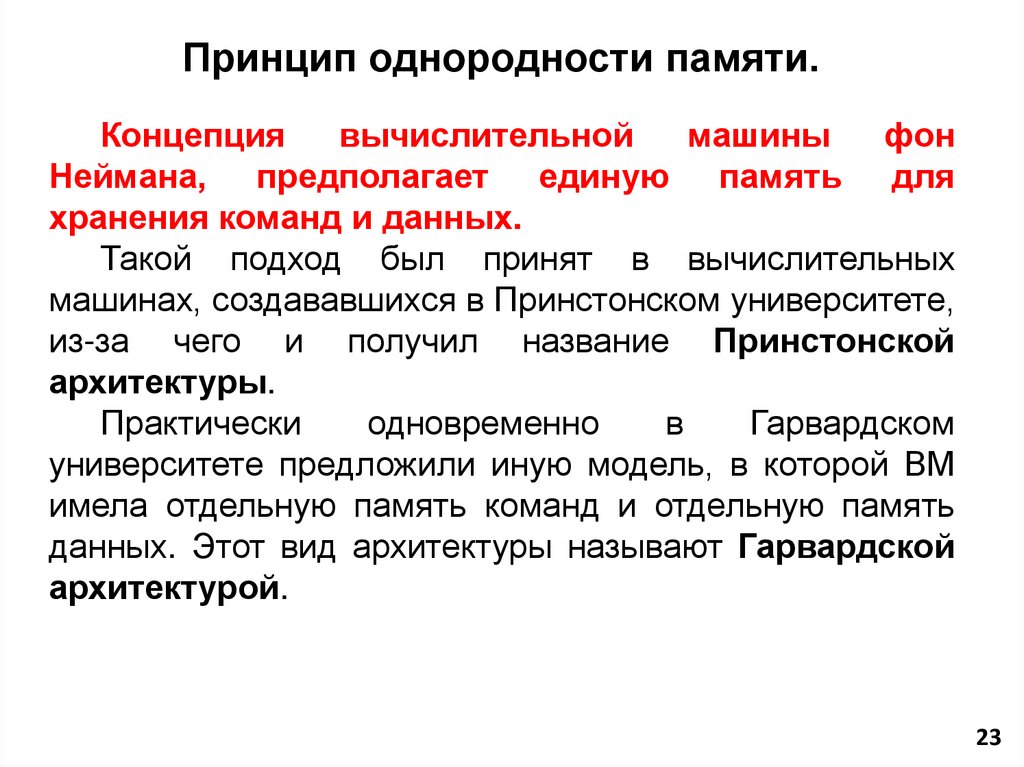

Принцип однородности памяти.Команды и данные хранятся в одной и той же памяти

и внешне в памяти неразличимы. Распознать их можно

только по способу использования. Это позволяет

производить над командами те же операции, что и над

числами,

и,

соответственно,

открывает

ряд

возможностей. Так, циклически изменяя адресную часть

команды,

можно

обеспечить

обращение

к

последовательным элементам массива данных.

Такой прием носит название модификации команд.

Полезным является другое следствие принципа

однородности, когда команды одной программы могут

быть получены как результат исполнения другой

программы.

Эта возможность лежит в основе трансляции —

перевода текста программы с языка высокого уровня

на язык конкретной ВМ.

22

38.

Принцип однородности памяти.Концепция

вычислительной

машины

фон

Неймана, предполагает единую память для

хранения команд и данных.

Такой подход был принят в вычислительных

машинах, создававшихся в Принстонском университете,

из-за чего и получил название Принстонской

архитектуры.

Практически

одновременно

в

Гарвардском

университете предложили иную модель, в которой ВМ

имела отдельную память команд и отдельную память

данных. Этот вид архитектуры называют Гарвардской

архитектурой.

23

39.

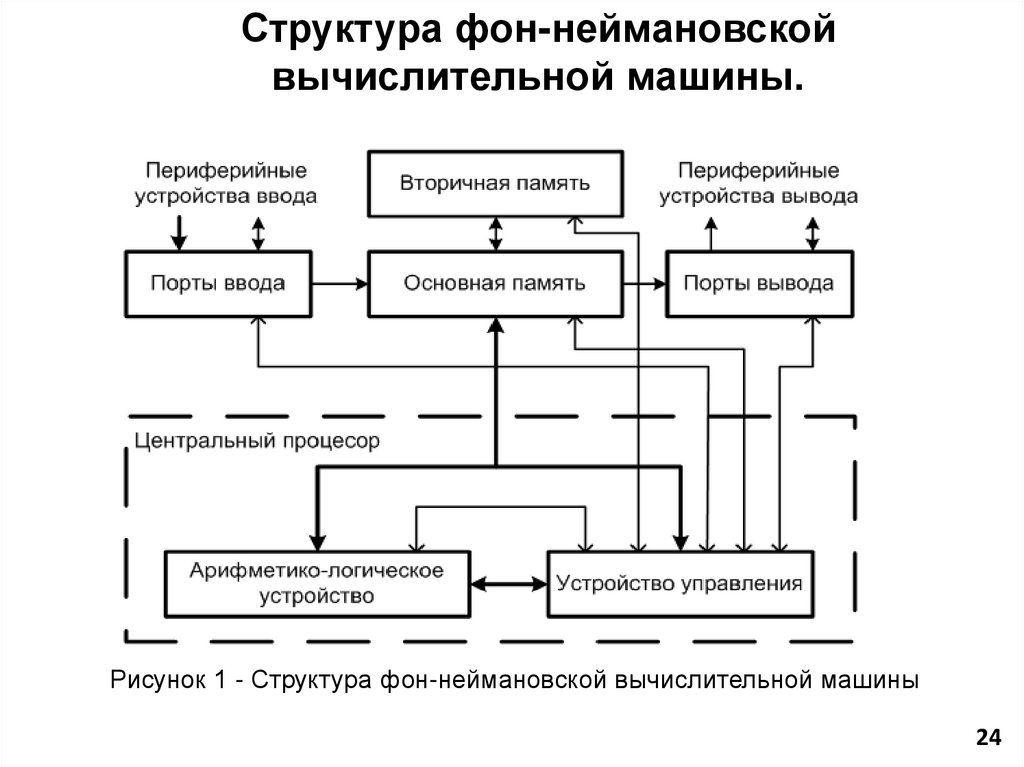

Структура фон-неймановскойвычислительной машины.

Рисунок 1 - Структура фон-неймановской вычислительной машины

24

40.

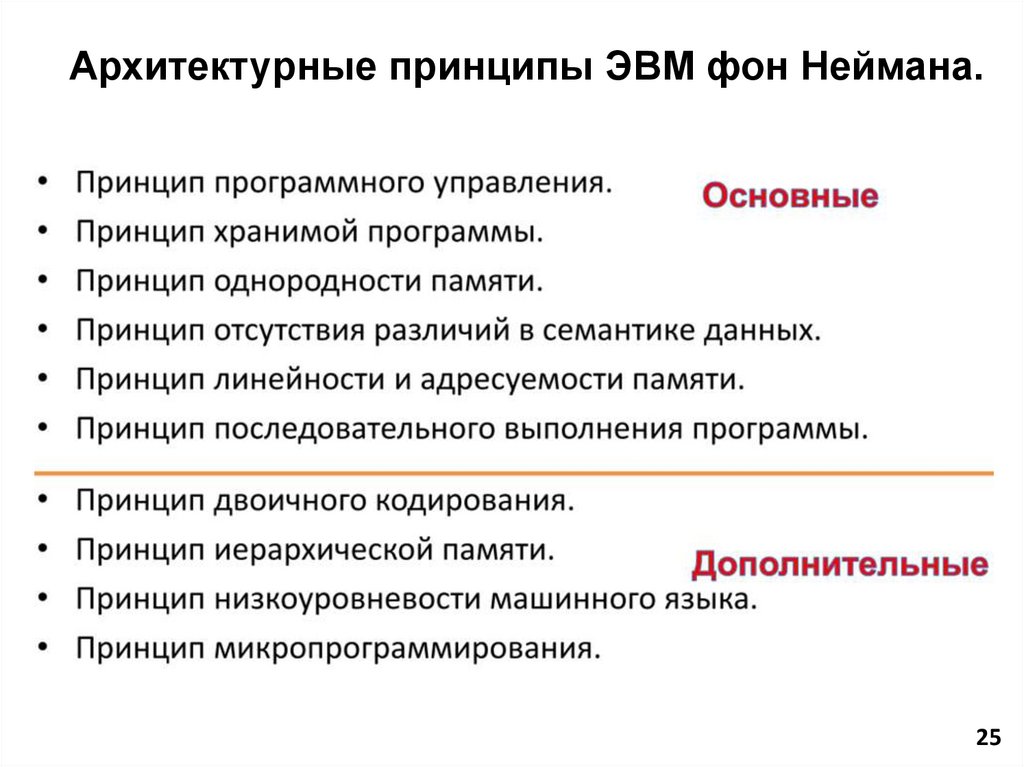

Архитектурные принципы ЭВМ фон Неймана.25

41.

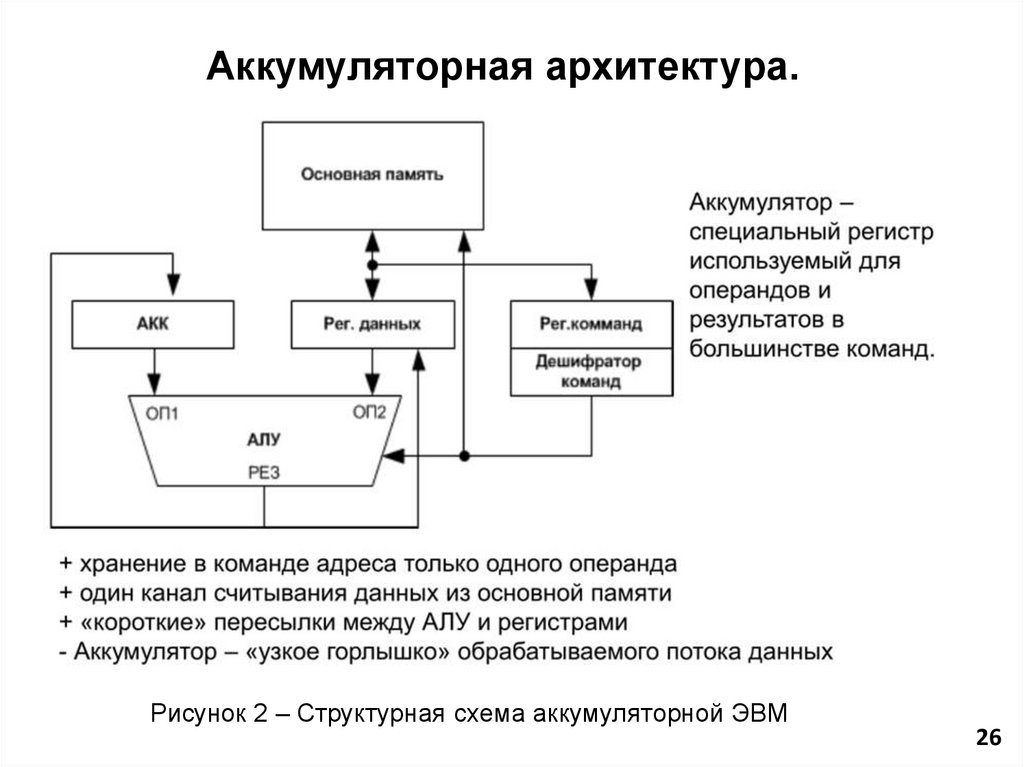

Аккумуляторная архитектура.Рисунок 2 – Структурная схема аккумуляторной ЭВМ

26

42.

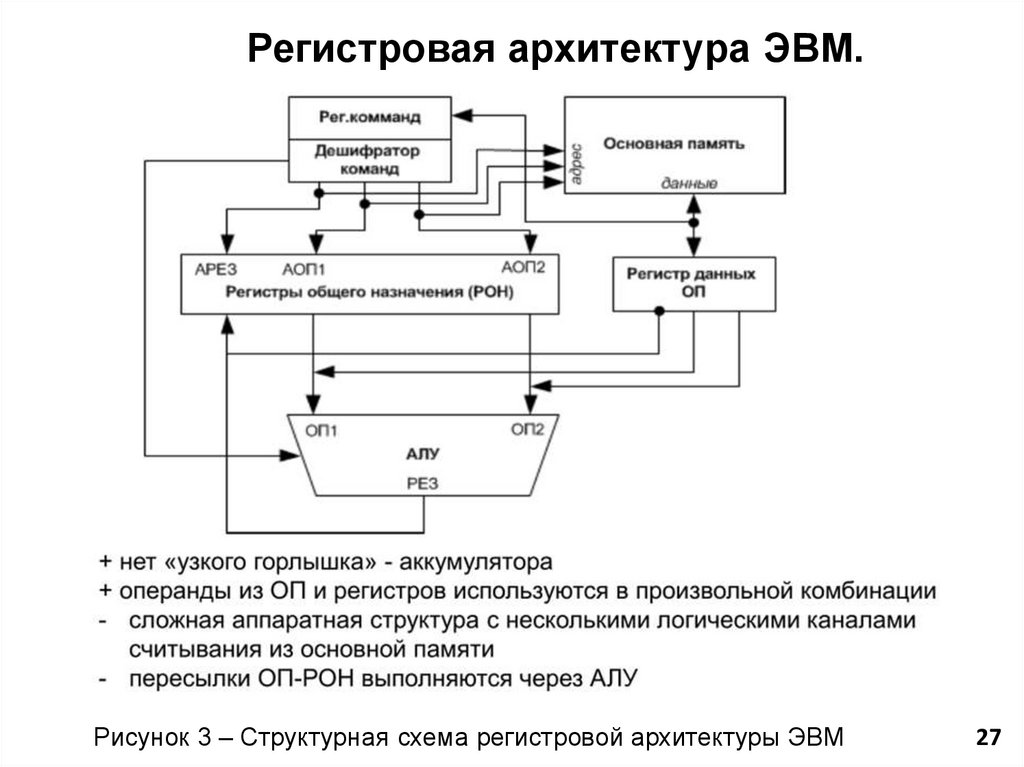

Регистровая архитектура ЭВМ.Рисунок 3 – Структурная схема регистровой архитектуры ЭВМ

27

43.

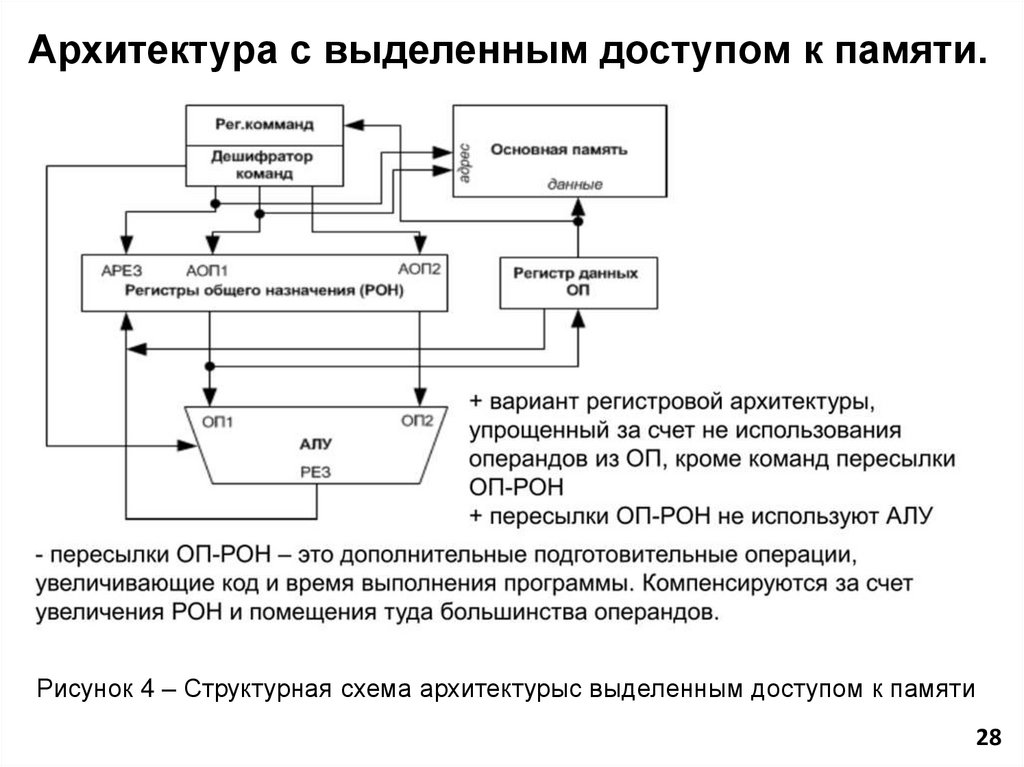

Архитектура с выделенным доступом к памяти.Рисунок 4 – Структурная схема архитектурыс выделенным доступом к памяти

28

44.

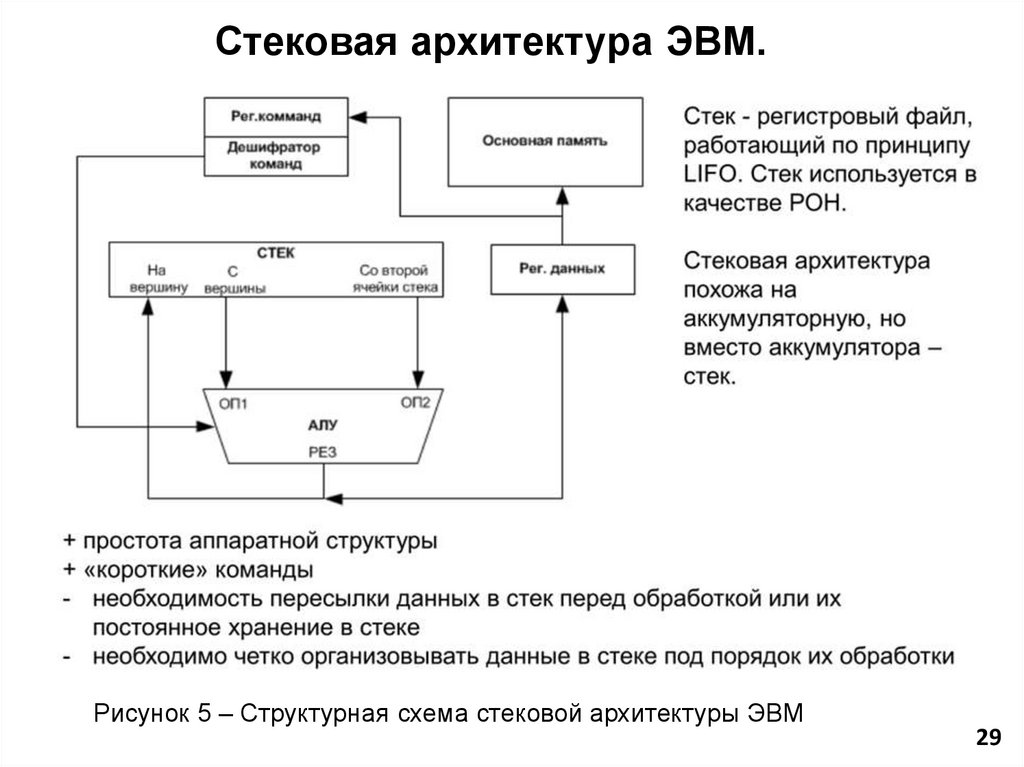

Стековая архитектура ЭВМ.Рисунок 5 – Структурная схема стековой архитектуры ЭВМ

29

45.

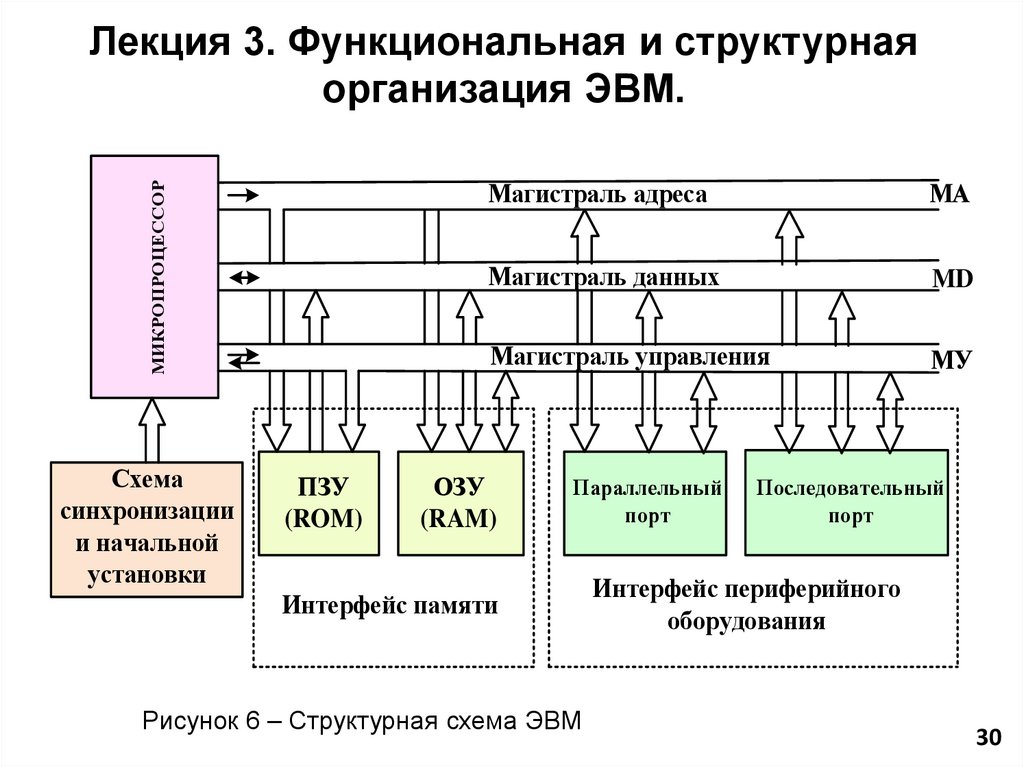

МИКРОПРОЦЕССОРЛекция 3. Функциональная и структурная

организация ЭВМ.

Схема

синхронизации

и начальной

установки

ПЗУ

(ROM)

Магистраль адреса

МА

Магистраль данных

MD

Магистраль управления

МУ

ОЗУ

(RAM)

Параллельный

порт

Интерфейс памяти

Рисунок 6 – Структурная схема ЭВМ

Последовательный

порт

Интерфейс периферийного

оборудования

30

46.

Функциональная и структурнаяорганизация ЭВМ.

Представленная структура отражает магистральномодульный принцип организации микропроцессорных

устройств и систем.

Отдельные

блоки

являются

функциональнозаконченными модулями со своими встроенными

схемами управления.

Межмодульные связи осуществляются посредством

коллективных шин (магистралей), к которым имеют

доступ все основные модули системы. Обмен

информацией производится путём разделения во

времени модулями систем коллективных шин.

31

47.

Интерфейс памяти.1. Постоянное запоминающее устройство (ПЗУ) память для чтения и хранения констант, программ.

Во время функционирования ЭВМ память ПЗУ

можно

только

считывать.

ПЗУ

является

энергонезависимой памятью.

2. Оперативное запоминающее устройство (ОЗУ) память с произвольным доступом, позволяет

оперативно изменять информацию во время

работы. ОЗУ предназначено для хранения данных,

является энергозависимой.

32

48.

Типы магистралей.1. Магистраль адреса (МА), по которой передается информация о

номере ячейки памяти, порта интерфейса или периферийного

устройства, с которым МП обменивается данными.

2. Магистраль управления (МУ), по которой передаются сигналы

определяющие характер и последовательность действий

различных узлов микропроцессорной системы, направление и

вид информации, передаваемой по магистрали адреса и

магистрали данных, кроме того для передачи признаков

состояния процессора и периферийных устройств.

3. Магистраль данных (МД), по которой осуществляется обмен

информацией внутри микропроцессорной системы и вне её,

определяет формат обрабатываемых данных. Разделение

потоков данных производится с помощью буферных регистров с

переключающими логическими вентилями.

33

49.

Интерфейс периферийных устройств.Периферийные

устройства

подсоединяются

к

шинам

интерфейса (шинам МП) не непосредственно, а через

программируемый

периферийный

адаптер

(ППА)

и

программируемый связной адаптер (ПСА), обслуживающие

периферийные устройства соответственно с передачей информации

параллельным и последовательным кодом.

Каждый регистр устройства ввода/вывода (УВВ), связывающий

МП с одним внешним устройством называется портом.

Взаимодействие элементов микропроцессорной системы между

собой и с внешними устройствами осуществляется с помощью

специальных аппаратных средств. Они являются программноуправляемыми и подчиняются командам центрального процессора.

Совокупность этих аппаратных средств и управляющих программ

называется интерфейсом.

34

50.

Схема синхронизации.Система

синхронизации

предназначена

для

обеспечения синхронной работы всех узлов ЭВМ. В ее

состав входит блок синхронизации (БС), местные схемы

тактирования и блок начальной установки (БНУ).

В

задачи

БС

входит

генерация

опорной

синхропоследовательности заданной формы и частоты.

Частота тактового сигнала задает темп работы

системы и определяется ее быстродействием. Форма

тактирующего

сигнала

зависит

от

структуры

управляемого узла, и поэтому не может быть

одинаковой для всех устройств системы.

Для формирования синхроимпульсов заданной

фазности и скважности внутри каждого узла могут

использоваться местные схемы тактирования.

35

51.

Схема начального запуска.При включении питания, при аварийной ситуации или

зависании процессора подача сигнала RESET приводит к

инициализации процессора, заставляет его приступить к

выполнению программы начального запуска.

Аварийная ситуация может быть вызвана помехами по

цепям питания и «земли», сбоями в работе памяти, внешними

ионизирующими излучениями и др. В результате процессор

может потерять контроль над выполнением программы и

остановиться на каком либо адресе. Для выхода из этого

состояния используется сигнал начального сброса. Этот же вход

начального сброса может использоваться для оповещения

процессора о том, что напряжение питания стало ниже

установленного предела. В этом случае процессор переходит к

выполнению программы сохранения важных данных. По сути,

этот

вход

представляет

собой

особую

разновидность

радиального прерывания. Иногда у микросхемы процессора есть

еще 1-2 входа прерываний для обработки особых ситуаций

(например, от внешнего таймера).

36

52.

Обобщенная структура ЭВМРазвитие архитектуры неизбежно ведет к развитию структуры

ЭВМ. Реализация принципов интеллектуализации, которые все

больше определяют развитие архитектуры ЭВМ, возможна при

совершенствовании структурной организации, обеспечивающей

повышение эффективности вычислительного процесса и, как

следствие этого, рост производительности ЭВМ. В конечном счёте

условием и критерием развития структуры является рост

производительности ЭВМ.

Основной тенденцией в развитии структуры ЭВМ является

разделение функций системы и максимальная специализация

подсистем для выполнения этих функций.

Обобщенная структура ЭВМ состоит из следующих составных

частей:

1. обрабатывающей подсистемы;

2. подсистемы памяти;

3. подсистемы ввода/вывода;

4. подсистемы управления и обслуживания.

53.

Обобщенная структура ЭВМ54.

Обрабатывающая подсистема.Развитие обрабатывающей подсистемы в большей

степени, чем всех остальных подсистем, идет по пути

разделения функций и повышения специализации

составляющих ее устройств. Создаются специальные

средства, которые осуществляют функции управления

системой, освобождая от этих функций средства

обработки.

Такое

распределение

функций

сокращает

эффективное время обработки информации и повышает

производительность ЭВМ. В то же время, средства

управления, как и средства обработки, становятся более

специализированными. Устройство управления памятью

реализует эффективные методы передачи данных между

средствами обработки и подсистемой памяти. Меняются

функции центрального устройства управления.

55.

С одной стороны, ряд функций передается в другие подсистемы(например, функции ввода/вывода), с другой – развиваются средства

организации

параллельной

обработки

нескольких

команд

(суперскалярная обработка, конвейерная технология выполнения

команд, многоядерные структуры, многопотоковая обработка команд,

динамическое

изменение

последовательности

команд,

предварительная выборка данных, предсказание направления

ветвлений и т.д.). Бурно развивается управление межпроцессорным

обменом как эффективное средство передачи информации между

несколькими центральными процессорами, входящими в состав

вычислительной системы или комплекса.

Операционные устройства обрабатывающей подсистемы, кроме

традиционных средств скалярной (суперскалярной) и логической

обработки, все шире стали включать специальные средства векторной

обработки. При этом время выполнения операций можно резко

сократить за счет увеличения частоты работы операционных

устройств.

В устройствах скалярной обработки все шире появляются

специальные

операционные

блоки,

оптимизированные

на

эффективное

выполнение

отдельных

операций,

разрядность

обрабатываемых слов возрастает.

56.

Подсистема памятиПодсистема памяти современных компьютеров имеет

иерархическую структуру, состоящую из нескольких

уровней:

1. сверхоперативный уровень (память процессора, кэшпамять);

2. оперативный уровень (оперативная память);

3. внешний уровень (внешние ЗУ на дисках, лентах и

т.д.).

Эффективными

методами

повышения

производительности

ЭВМ

являются

увеличение

количества регистров общего назначения процессора,

использование многоуровневой кэш-памяти, увеличение

объема и пропускной способности оперативной памяти

(ОП), буферизация передачи информации между ОП и

внешней памятью.

57.

Подсистема ввода/выводаВ состав подсистемы ввода/вывода входит набор

специализированных устройств, между которыми

распределены функции ввода/вывода, что позволяет

свести к минимуму потери производительности

системы при операциях ввода/вывода. Эти устройства

определяют пропускную способность подсистемы

ввода/вывода.

Основными направлениями развития подсистем

ввода/вывода

являются

совершенствование

системных

контроллеров

и

контроллеров

ввода/вывода, увеличение частоты и пропускной

способности

интер-фейсов,

совершенствование

шинной архитектуры.

58.

Подсистема управления и обслуживанияПодсистема управления и обслуживания – это совокупность

аппаратно-программных средств, предназначенных для обеспечения

максимальной

производительности,

заданной

надежности,

ремонтопригодности, удобства настройки и эксплуатации. Она

обеспечивает проблемную ориентацию и заданное время наработки на

отказ, подготовку и накопление статистических сведений о загрузке и

прохождении

вычислительного

процесса,

выполняет

функции

«интеллектуального»

интерфейса

с

различными

категориями

обслуживающего

персонала,

осуществляет

инициализацию,

тестирование и отладку. Подсистема управления и обслуживания

позволяет поднять на качественно новый уровень эксплуатацию

современных ЭВМ.

При разработке структуры ЭВМ все подсистемы должны быть

сбалансированы между собой. Только оптимальное согласование

быстродействия обрабатывающей подсистемы с объемами и скоростью

передачи информации подсистемой памяти, с пропускной способностью

подсистемы

ввода/вывода

позволяет

добиться

максимальной

эффективности использования ЭВМ.

59.

60.

Лекция 4. Общая структура, функции,классификация микропроцессоров.

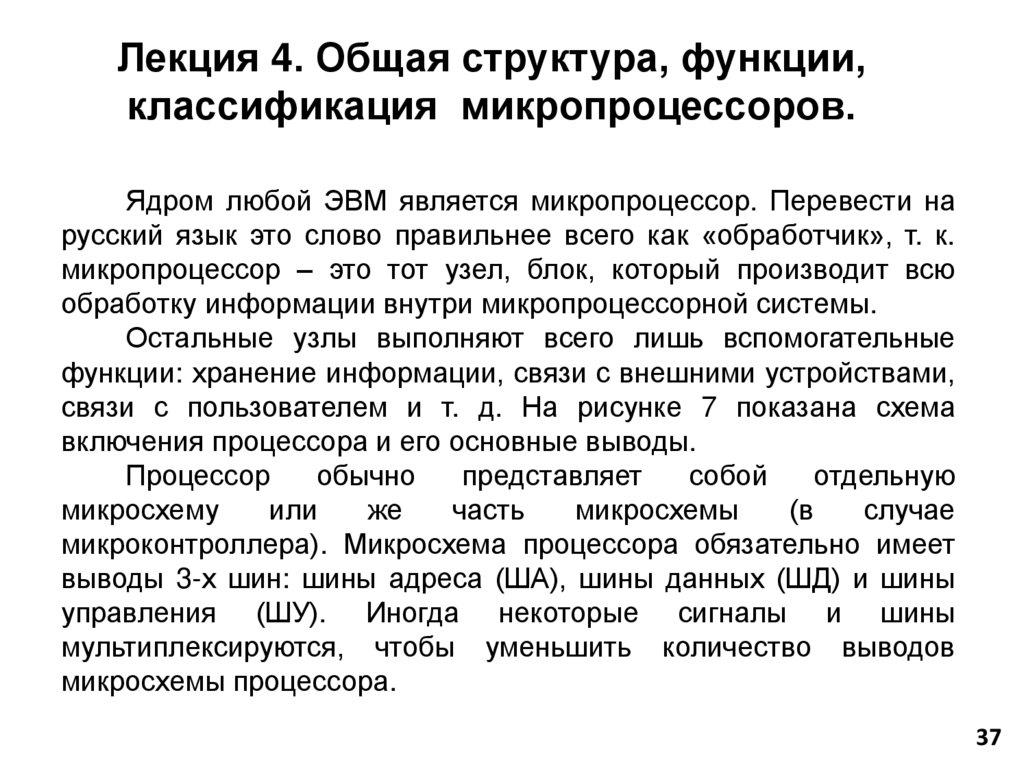

Ядром любой ЭВМ является микропроцессор. Перевести на

русский язык это слово правильнее всего как «обработчик», т. к.

микропроцессор – это тот узел, блок, который производит всю

обработку информации внутри микропроцессорной системы.

Остальные узлы выполняют всего лишь вспомогательные

функции: хранение информации, связи с внешними устройствами,

связи с пользователем и т. д. На рисунке 7 показана схема

включения процессора и его основные выводы.

Процессор

обычно

представляет

собой

отдельную

микросхему

или

же

часть

микросхемы

(в

случае

микроконтроллера). Микросхема процессора обязательно имеет

выводы 3-х шин: шины адреса (ША), шины данных (ШД) и шины

управления (ШУ). Иногда некоторые сигналы и шины

мультиплексируются, чтобы уменьшить количество выводов

микросхемы процессора.

37

61.

Схема включения процессора.Рисунок 7 – Схема включения процессора

38

62.

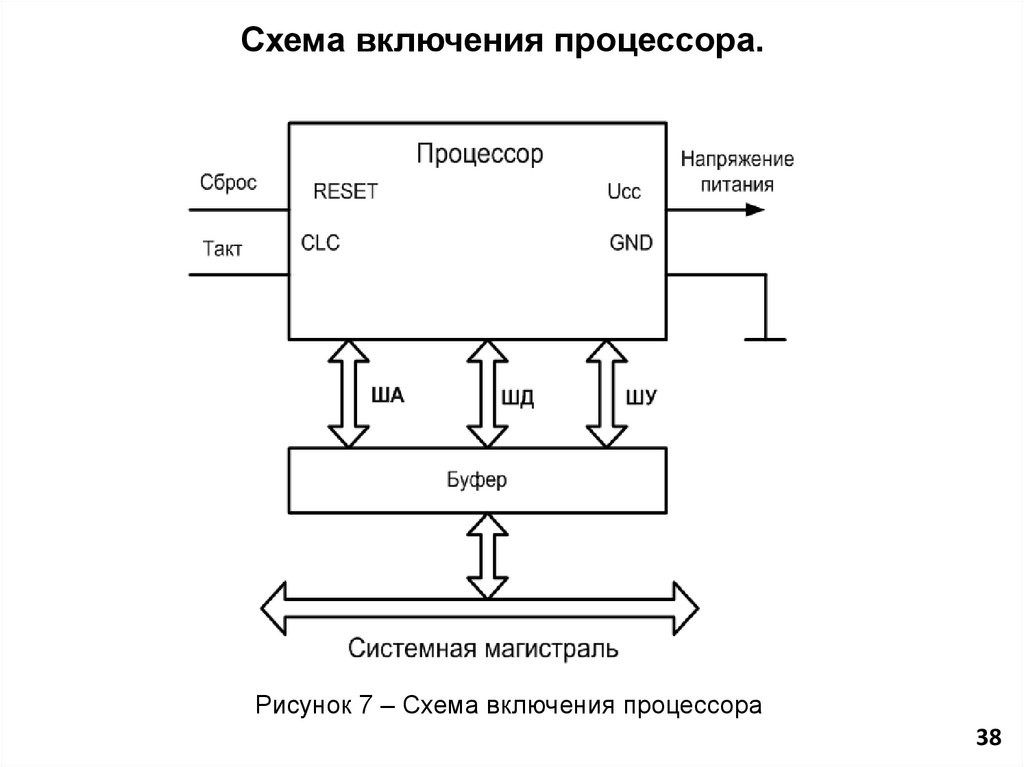

Основные функции процессора.1. выборка (чтение) выполняемых команд;

2. ввод (чтение) данных из памяти или УВВ;

3. вывод (запись) данных в память или УВВ;

4. обработка данных (операндов), в том числе

арифметические операции над ними;

5. адресация памяти, т. е. задание адреса

памяти, с которым будет производиться

обмен;

6. обработка прерываний и режима прямого

доступа к памяти (ПДП).

39

63.

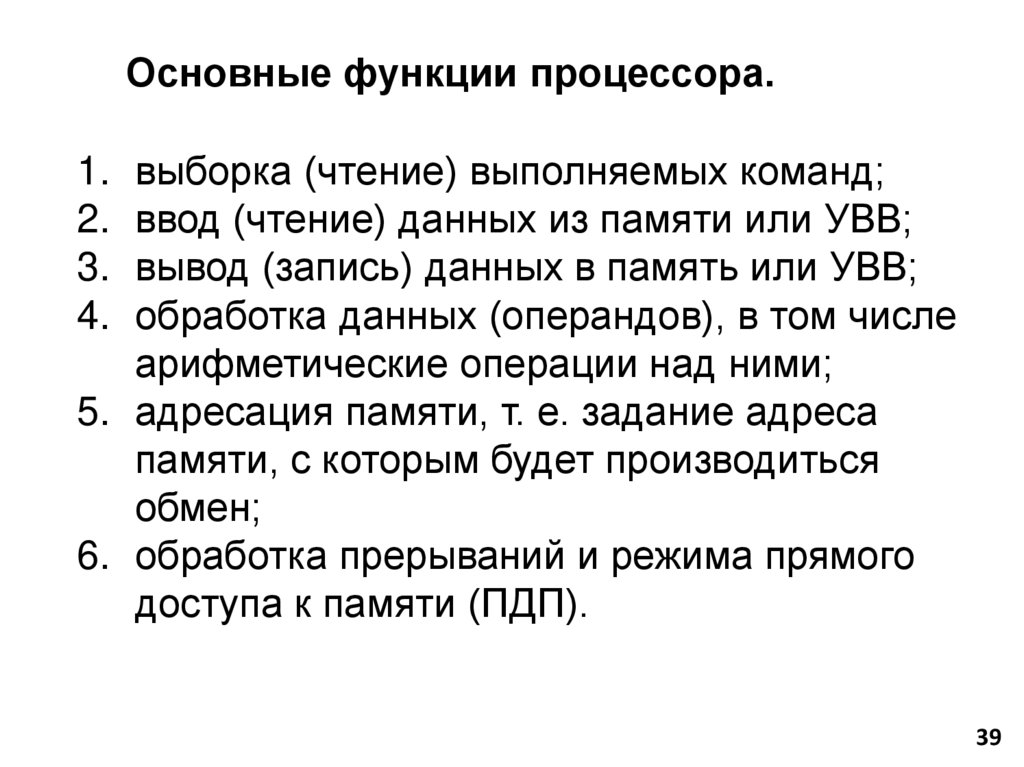

Внутренняя структура микропроцессора.ПРОЦЕССОР

Арифметикологическое устройство

(АЛУ)

PC

SP

Логика

управления

RG

RG

...

RG

Шина

данных

Шина

адреса

Регистр

признаков

Схема

управления

выборкой команд

Схема

управления

прерыванием

PSW

Схема

управления ПДП

Шина

управления

Шина Тактовый Сброс

питания сигнал

Рисунок 8 – Внутренняя структура микропроцессора

40

64.

Внутренняя структура микропроцессора.Схема управления выборкой команд выполняет

чтение команд из памяти и их дешифрацию.

Арифметико-логическое устройство (АЛУ, ALU)

предназначено

для

обработки

информации

в

соответствии с полученной процессором командой.

Примерами обработки могут служить логические

операции:

логическое «И», «ИЛИ», «исключающее

ИЛИ», то есть побитные операции над операндами, а

также арифметические операции такие, как операции

сложения, вычитания, умножения, деления и т.д.

Быстродействие

АЛУ

во

многом

определяет

производительность процессора. Причем важна не

только частота тактового сигнала, которым тактируется

АЛУ, но и количество тактов, необходимое для

выполнения той или иной команды.

41

65.

Внутренняя структура микропроцессора.Регистры процессора представляют собой ячейки очень

быстрой памяти и служат для временного хранения различных

кодов: данных, адресов, служебных кодов. Операции с этими

кодами выполняются предельно быстро, поэтому, чем больше

внутренних регистров, тем лучше. Именно разрядность регистров

и АЛУ называется внутренней разрядностью процессора, которая

может не совпадать с внешней разрядностью.

Регистр признаков PSW занимает особое место, хотя он

также

является

внутренним

регистром

процессора.

Содержащаяся в нем информация — это не данные, не адрес, а

слово состояния процессора PSW — Processor Status Word.

Каждый бит этого слова (флаг) содержит информацию о

результате предыдущей команды. Эти биты (флаги) используются

командами условных переходов, например, командой перехода в

случае нулевого результата. В этом же регистре иногда

содержатся

флаги

управления,

определяющие

режим

выполнения некоторых команд.

42

66.

Внутренняя структура микропроцессора.Схема

управления

прерываниями

обрабатывает

поступающий на процессор запрос прерывания, определяет адрес

начала программы обработки прерывания (адрес вектора

прерывания), обеспечивает переход к этой программе после

сохранения в памяти (в стеке) текущего состояния регистров

процессора. По окончании программы обработки прерывания

процессор

возвращается

к

прерванной

программе

с

восстановленными из памяти (из стека) значениями внутренних

регистров.

Схема управления прямым доступом к памяти служит для

временного отключения процессора от внешних шин и

приостановки работы процессора на время предоставления

прямого доступа запросившему его устройству. Прямой доступ

предназначен для высокоскоростного обмена данными между

памятью ЭВМ и периферийными устройствами (ПУ).

Логика управления организует взаимодействие всех узлов

процессора, перенаправляет данные, синхронизирует работу

процессора с внешними сигналами, а также реализует процедуры

ввода и вывода информации.

43

67.

Классификация микропроцессоровПо технологии изготовления:

1. PMOS - P – Channel Metal Oxide Semiconductor – i4004, 8008;

2. NMOS - N – Channel Metal Oxide Semiconductor – i8080, i8085;

3. HMOS (N – Channel high-performance Metal Oxide

Semiconductor) - 8086, 80186, 80286, 80386, 80486, Pentium;

4. CMOS (КМОП) – сигнальные и медийные МП - семейство

TMS320C2X, cyrix6x86, Athlon , Pentium и т.д.

По типу архитектуры:

1. однокристальные МП;

2. однокристальные микроконтроллеры;

3. разрядно – модульные МП;

4. CISC и RISC процессоры;

5. Транспьютеры.

44

68.

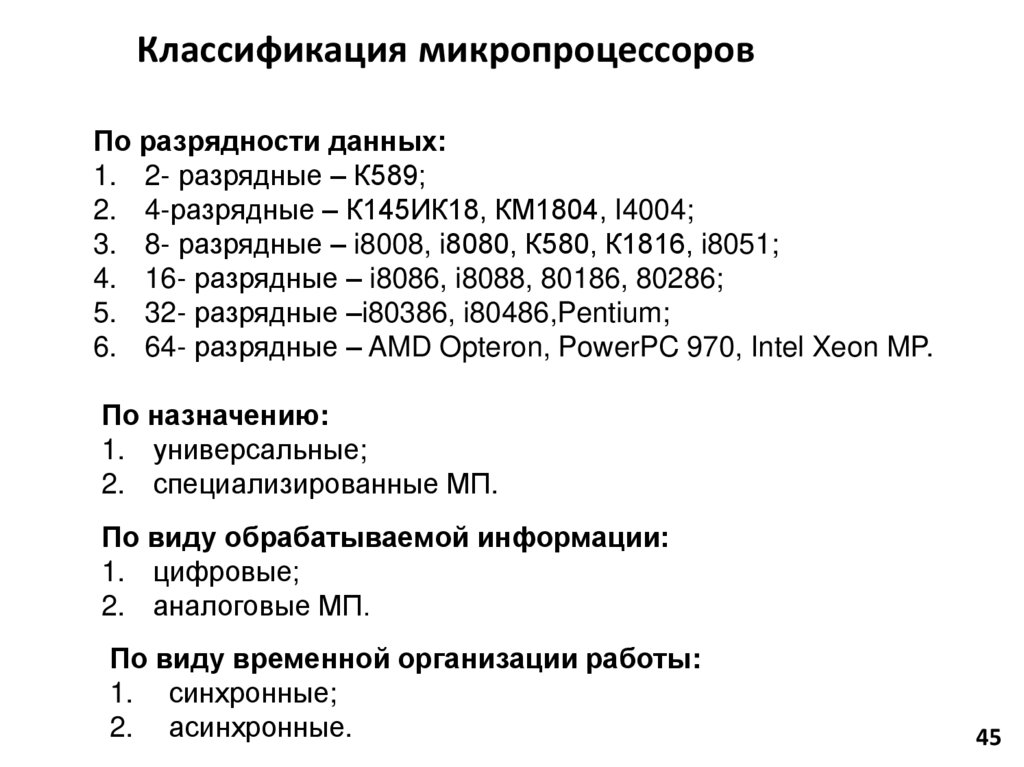

Классификация микропроцессоровПо разрядности данных:

1. 2- разрядные – К589;

2. 4-разрядные – К145ИК18, КМ1804, I4004;

3. 8- разрядные – i8008, i8080, К580, К1816, i8051;

4. 16- разрядные – i8086, i8088, 80186, 80286;

5. 32- разрядные –i80386, i80486,Pentium;

6. 64- разрядные – AMD Opteron, PowerPC 970, Intel Xeon MP.

По назначению:

1. универсальные;

2. специализированные МП.

По виду обрабатываемой информации:

1. цифровые;

2. аналоговые МП.

По виду временной организации работы:

1. синхронные;

2. асинхронные.

45

69.

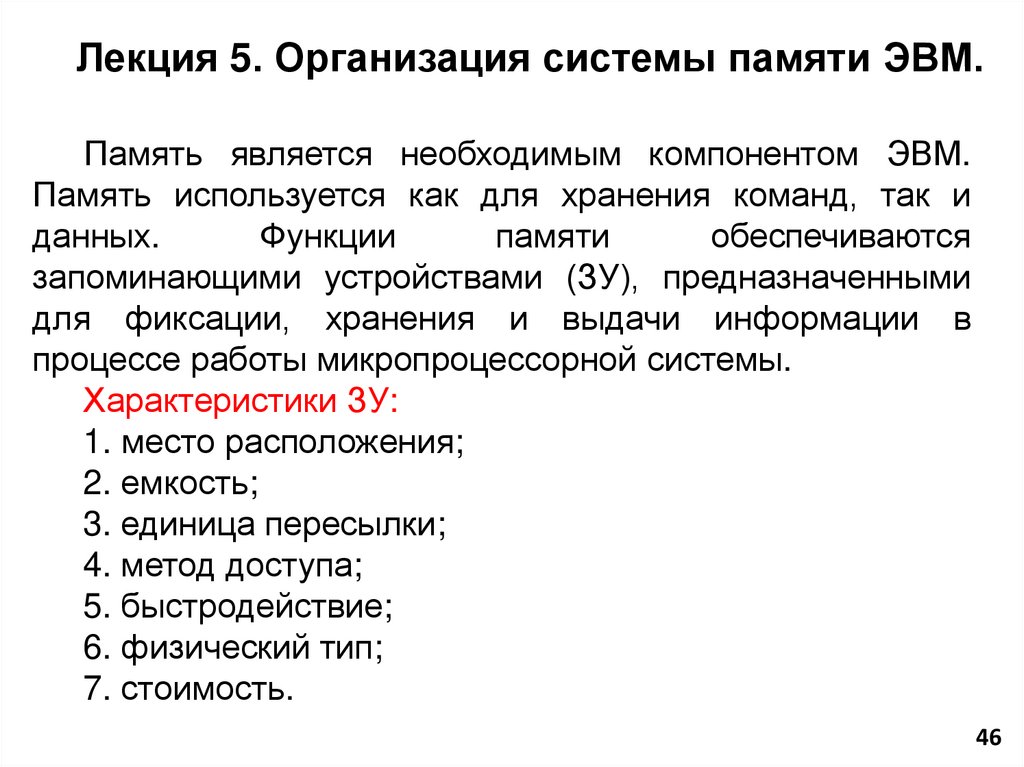

Лекция 5. Организация системы памяти ЭВМ.Память является необходимым компонентом ЭВМ.

Память используется как для хранения команд, так и

данных.

Функции

памяти

обеспечиваются

запоминающими устройствами (ЗУ), предназначенными

для фиксации, хранения и выдачи информации в

процессе работы микропроцессорной системы.

Характеристики ЗУ:

1. место расположения;

2. емкость;

3. единица пересылки;

4. метод доступа;

5. быстродействие;

6. физический тип;

7. стоимость.

46

70.

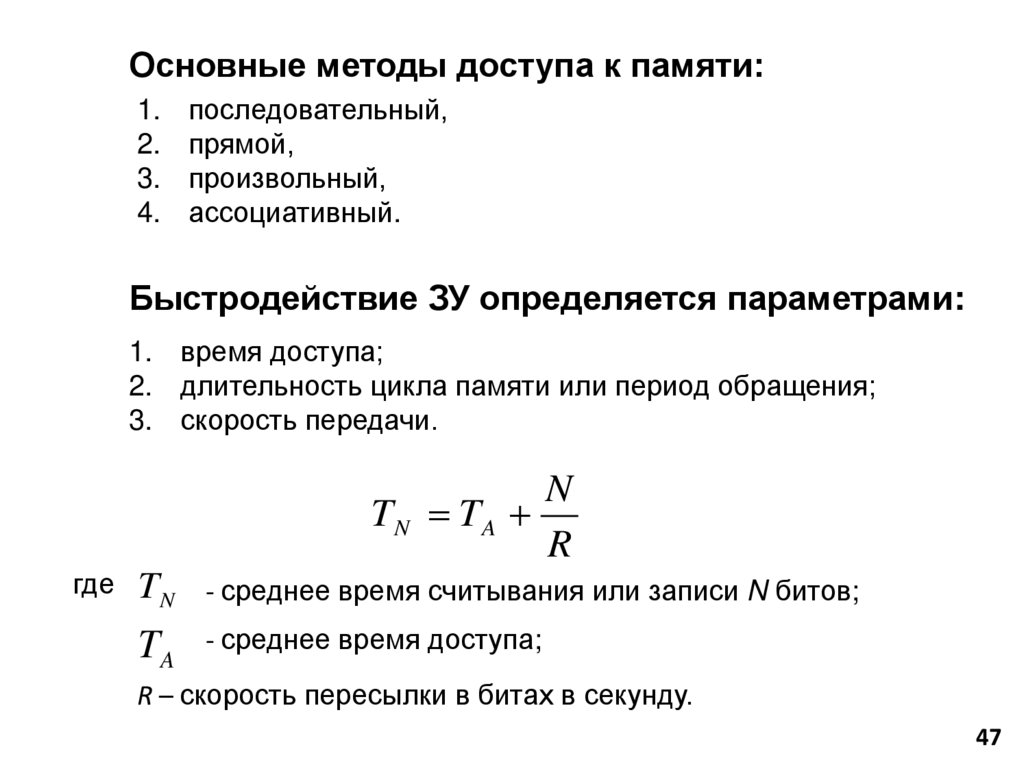

Основные методы доступа к памяти:1.

2.

3.

4.

последовательный,

прямой,

произвольный,

ассоциативный.

Быстродействие ЗУ определяется параметрами:

1. время доступа;

2. длительность цикла памяти или период обращения;

3. скорость передачи.

N

TN T A

R

где

TN

- среднее время считывания или записи N битов;

TA

- среднее время доступа;

R – скорость пересылки в битах в секунду.

47

71.

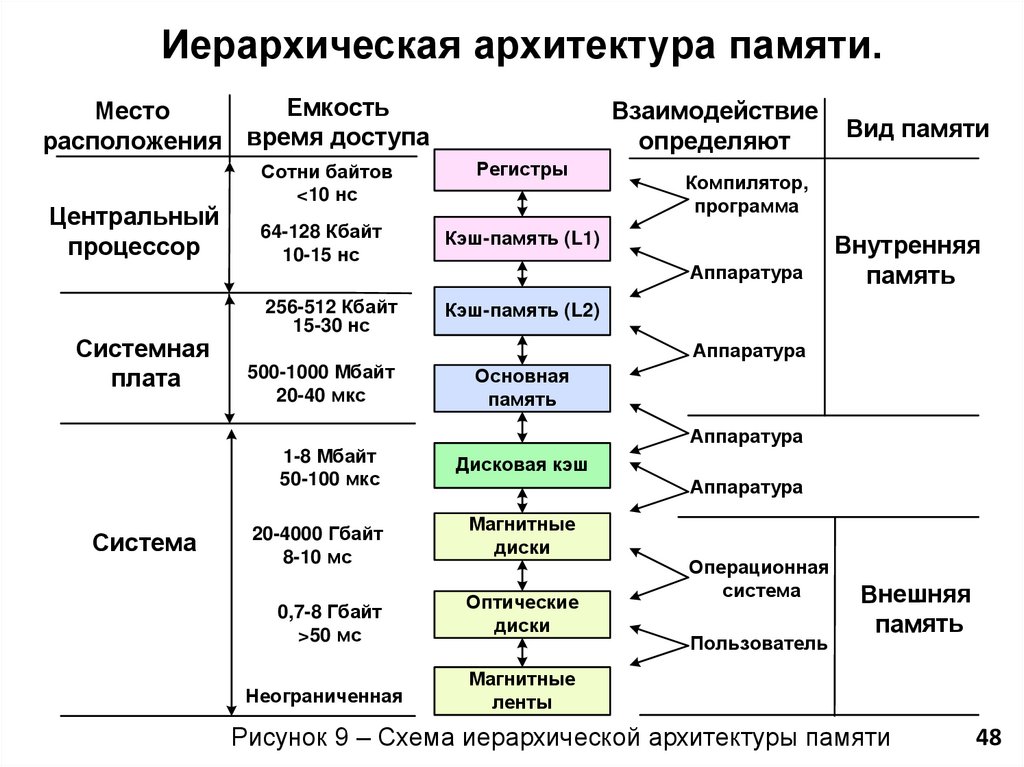

Иерархическая архитектура памяти.Емкость

Место

расположения время доступа

Центральный

процессор

Системная

плата

Сотни байтов

<10 нс

Регистры

64-128 Кбайт

10-15 нс

Кэш-память (L1)

256-512 Кбайт

15-30 нс

Кэш-память (L2)

500-1000 Мбайт

20-40 мкс

1-8 Мбайт

50-100 мкс

Система

Взаимодействие

определяют

20-4000 Гбайт

8-10 мс

0,7-8 Гбайт

>50 мс

Неограниченная

Вид памяти

Компилятор,

программа

Аппаратура

Внутренняя

память

Аппаратура

Основная

память

Аппаратура

Дисковая кэш

Аппаратура

Магнитные

диски

Оптические

диски

Операционная

система

Пользователь

Внешняя

память

Магнитные

ленты

Рисунок 9 – Схема иерархической архитектуры памяти

48

72.

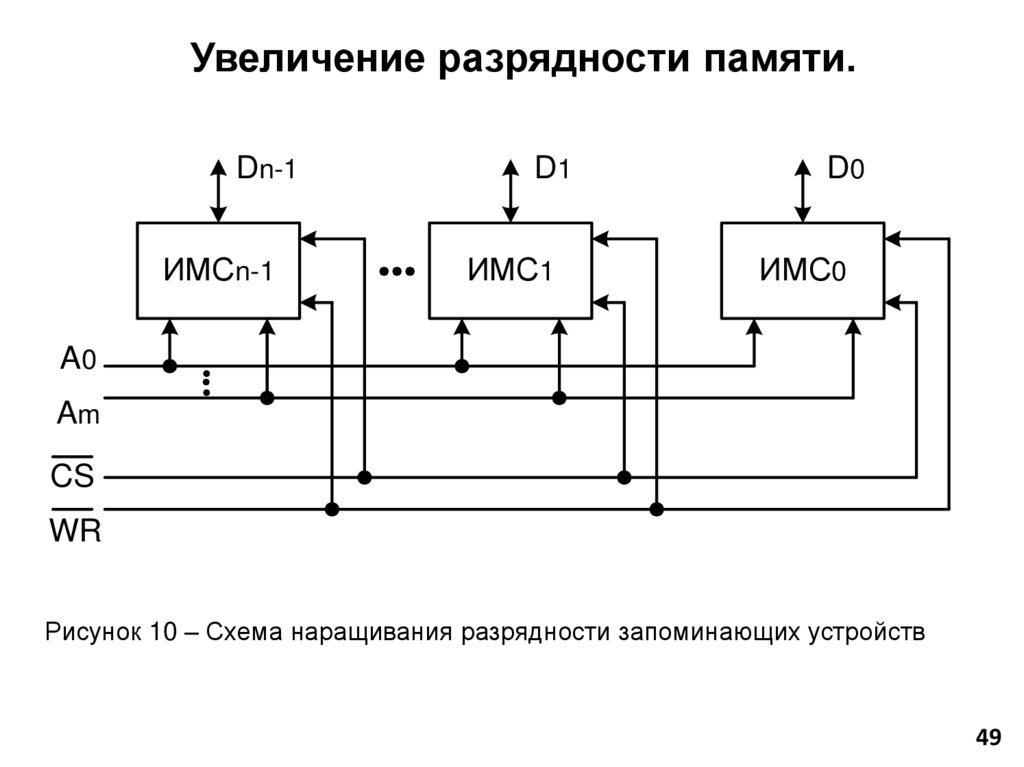

Увеличение разрядности памяти.Dn-1

ИМСn-1

D1

D0

ИМС1

ИМС0

A0

Am

CS

WR

Рисунок 10 – Схема наращивания разрядности запоминающих устройств

49

73.

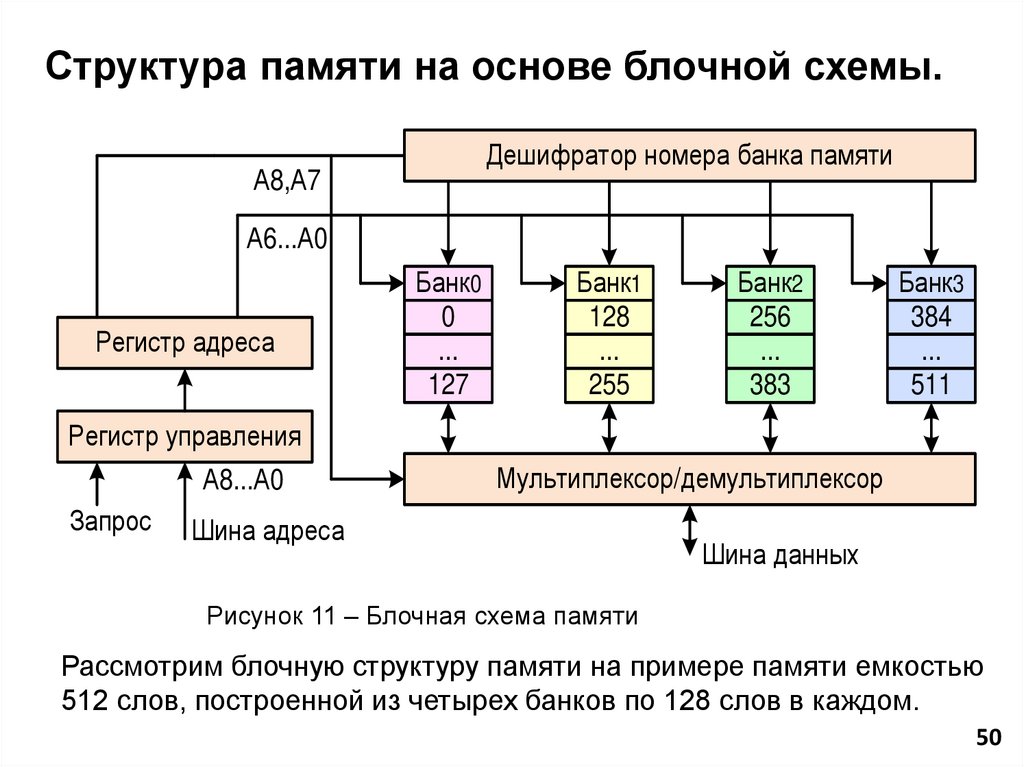

Структура памяти на основе блочной схемы.Дешифратор номера банка памяти

А8,А7

А6...А0

Регистр адреса

Банк0

0

...

127

Банк1

128

...

255

Банк2

256

...

383

Банк3

384

...

511

Регистр управления

А8...А0

Запрос

Мультиплексор/демультиплексор

Шина адреса

Шина данных

Рисунок 11 – Блочная схема памяти

Рассмотрим блочную структуру памяти на примере памяти емкостью

512 слов, построенной из четырех банков по 128 слов в каждом.

50

74.

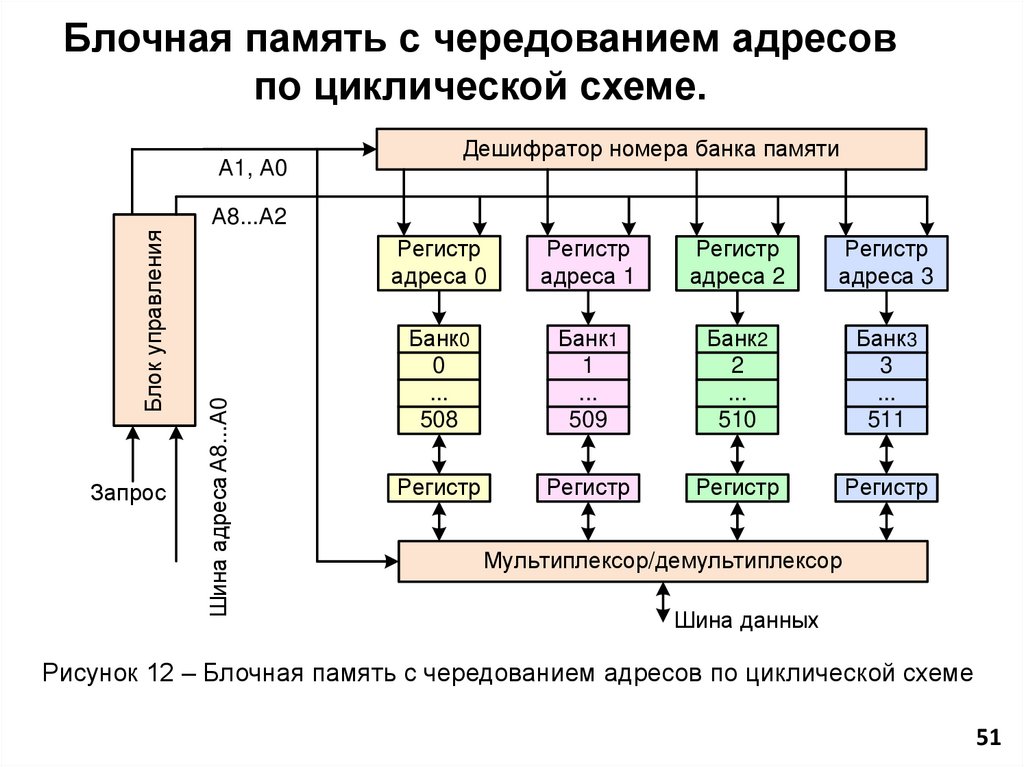

Блочная память с чередованием адресовпо циклической схеме.

А1, А0

Дешифратор номера банка памяти

Запрос

Шина адреса А8...А0

Блок управления

А8...А2

Регистр

адреса 0

Регистр

адреса 1

Регистр

адреса 2

Регистр

адреса 3

Банк0

0

...

508

Банк1

1

...

509

Банк2

2

...

510

Банк3

3

...

511

Регистр

Регистр

Регистр

Регистр

Мультиплексор/демультиплексор

Шина данных

Рисунок 12 – Блочная память с чередованием адресов по циклической схеме

51

75.

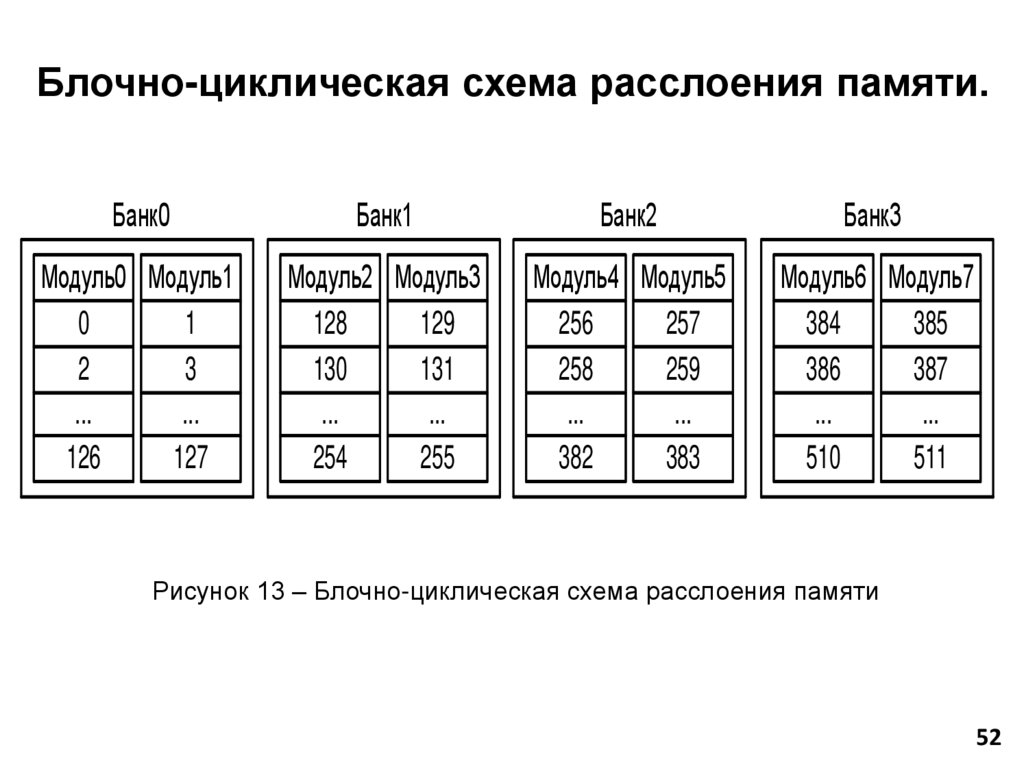

Блочно-циклическая схема расслоения памяти.Банк0

Банк1

Банк2

Банк3

Модуль0 Модуль1

0

1

2

3

...

...

126

127

Модуль2 Модуль3

128

129

130

131

...

...

254

255

Модуль4 Модуль5

256

257

258

259

...

...

382

383

Модуль6 Модуль7

384

385

386

387

...

...

510

511

Рисунок 13 – Блочно-циклическая схема расслоения памяти

52

76.

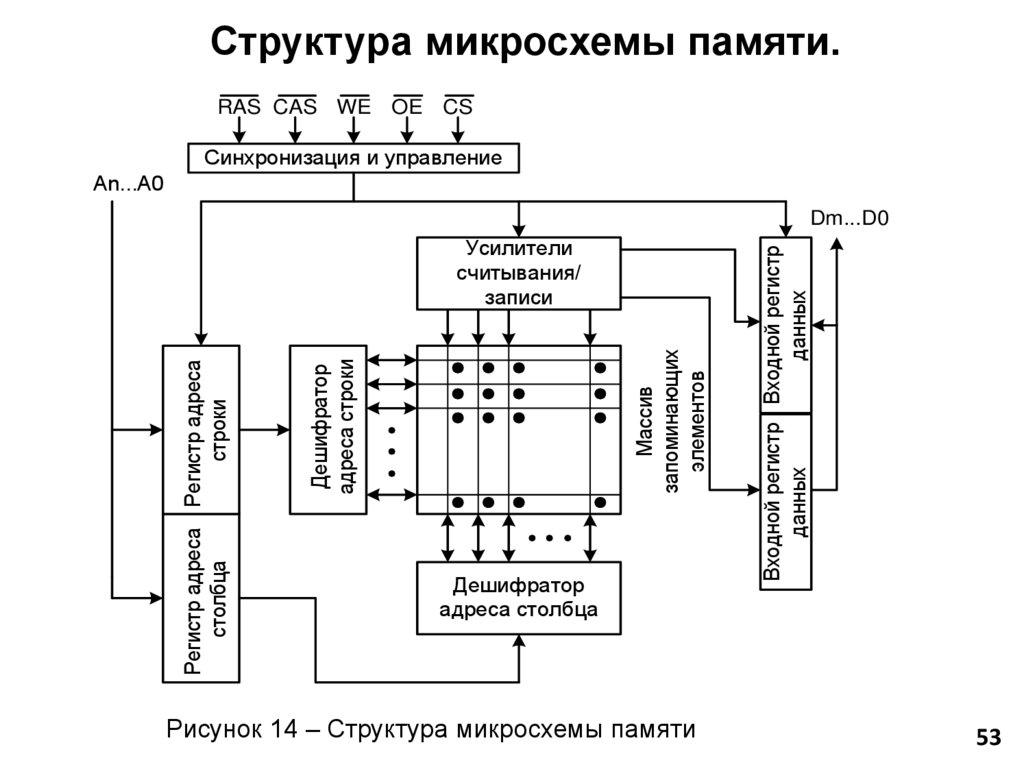

Структура микросхемы памяти.RAS CAS WE OE CS

Синхронизация и управление

Аn...А0

Массив

запоминающих

элементов

Дешифратор

адреса строки

Регистр адреса Регистр адреса

столбца

строки

Усилители

считывания/

записи

Дешифратор

адреса столбца

Рисунок 14 – Структура микросхемы памяти

Входной регистр Входной регистр

данных

данных

Dm...D0

53

77.

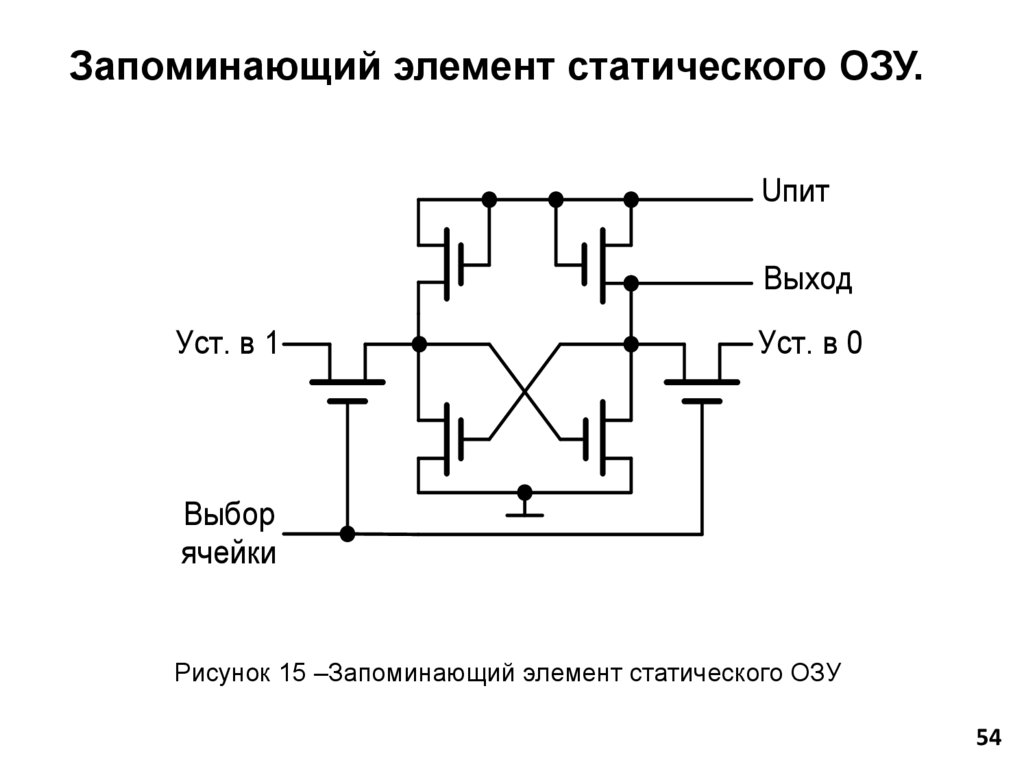

Запоминающий элемент статического ОЗУ.Uпит

Выход

Уст. в 1

Уст. в 0

Выбор

ячейки

Рисунок 15 –Запоминающий элемент статического ОЗУ

54

78.

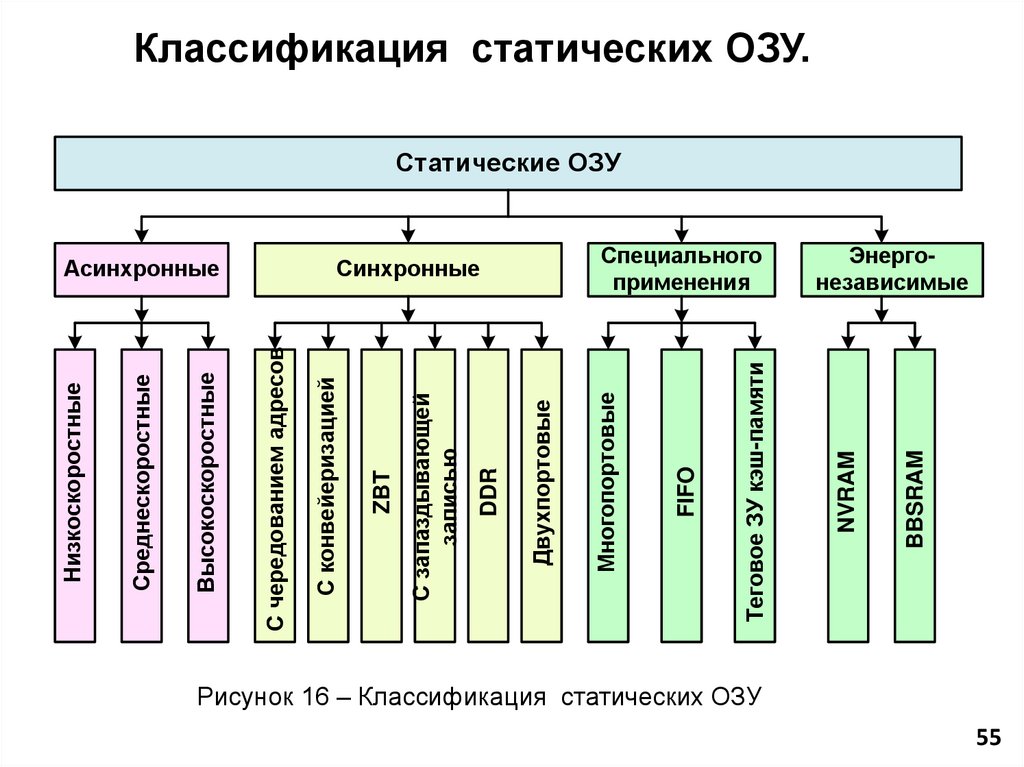

BBSRAMСпециального

применения

NVRAM

Теговое ЗУ кэш-памяти

FIFO

Синхронные

Многопортовые

Двухпортовые

DDR

С запаздывающей

записью

ZBT

Асинхронные

С конвейеризацией

С чередованием адресов

Высокоскоростные

Среднескоростные

Низкоскоростные

Классификация статических ОЗУ.

Статические ОЗУ

Энергонезависимые

Рисунок 16 – Классификация статических ОЗУ

55

79.

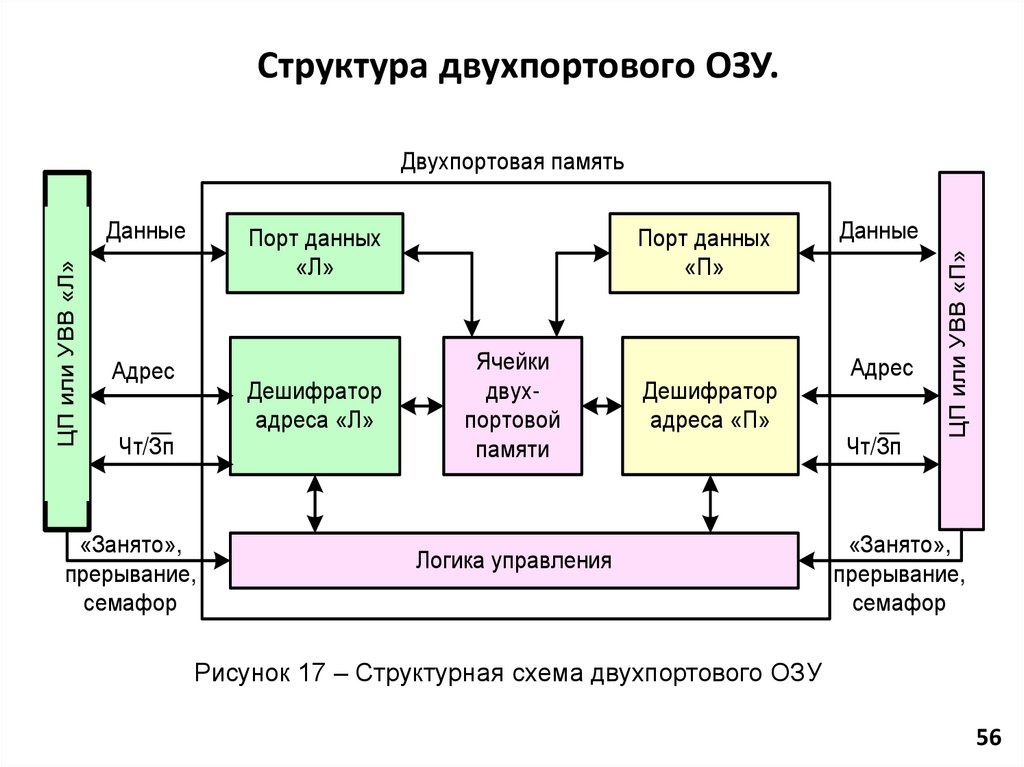

Структура двухпортового ОЗУ.Двухпортовая память

Порт данных

«Л»

Адрес

Дешифратор

адреса «Л»

Чт/Зп

«Занято»,

прерывание,

семафор

Порт данных

«П»

Ячейки

двухпортовой

памяти

Дешифратор

адреса «П»

Логика управления

Данные

Адрес

Чт/Зп

ЦП или УВВ «П»

ЦП или УВВ «Л»

Данные

«Занято»,

прерывание,

семафор

Рисунок 17 – Структурная схема двухпортового ОЗУ

56

80.

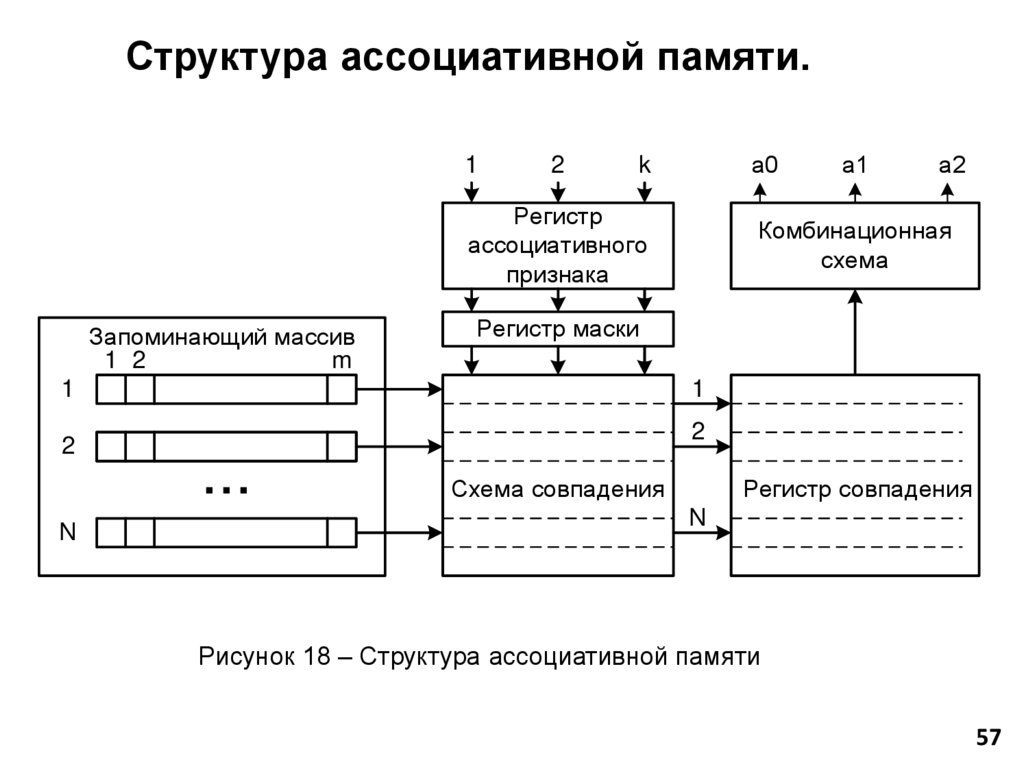

Структура ассоциативной памяти.1

2

а0

k

Регистр

ассоциативного

признака

Запоминающий массив

1 2

m

N

а2

Комбинационная

схема

Регистр маски

1

2

а1

1

2

...

Схема совпадения

Регистр совпадения

N

Рисунок 18 – Структура ассоциативной памяти

57

81.

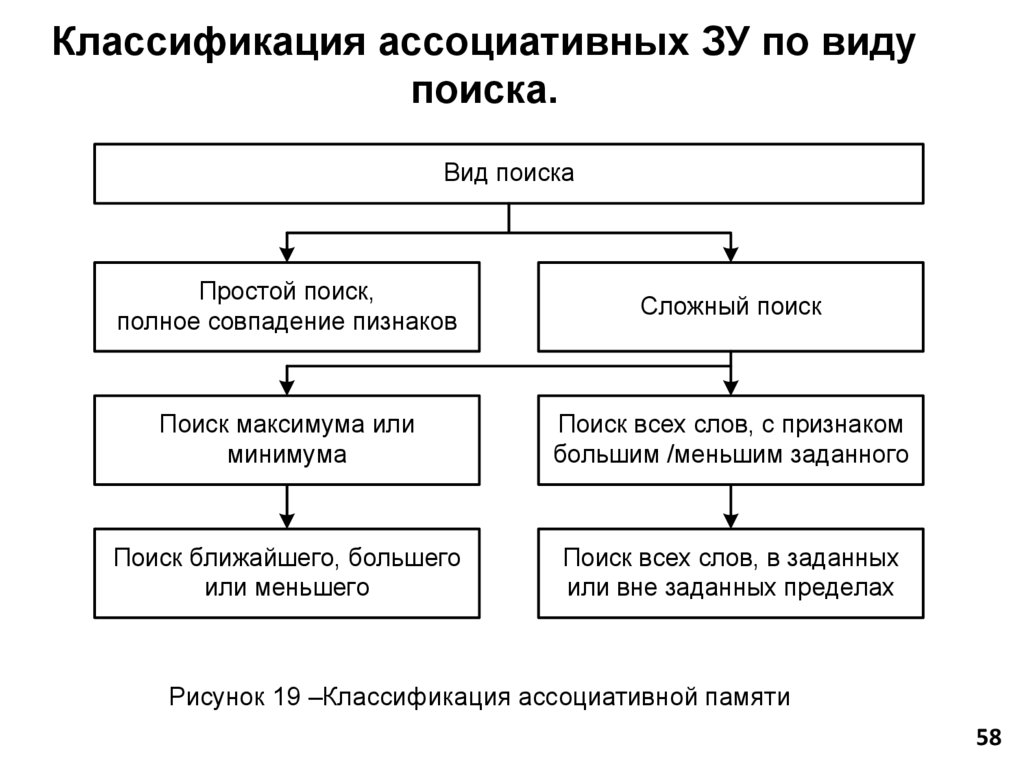

Классификация ассоциативных ЗУ по видупоиска.

Вид поиска

Простой поиск,

полное совпадение пизнаков

Сложный поиск

Поиск максимума или

минимума

Поиск всех слов, с признаком

большим /меньшим заданного

Поиск ближайшего, большего

или меньшего

Поиск всех слов, в заданных

или вне заданных пределах

Рисунок 19 –Классификация ассоциативной памяти

58

82.

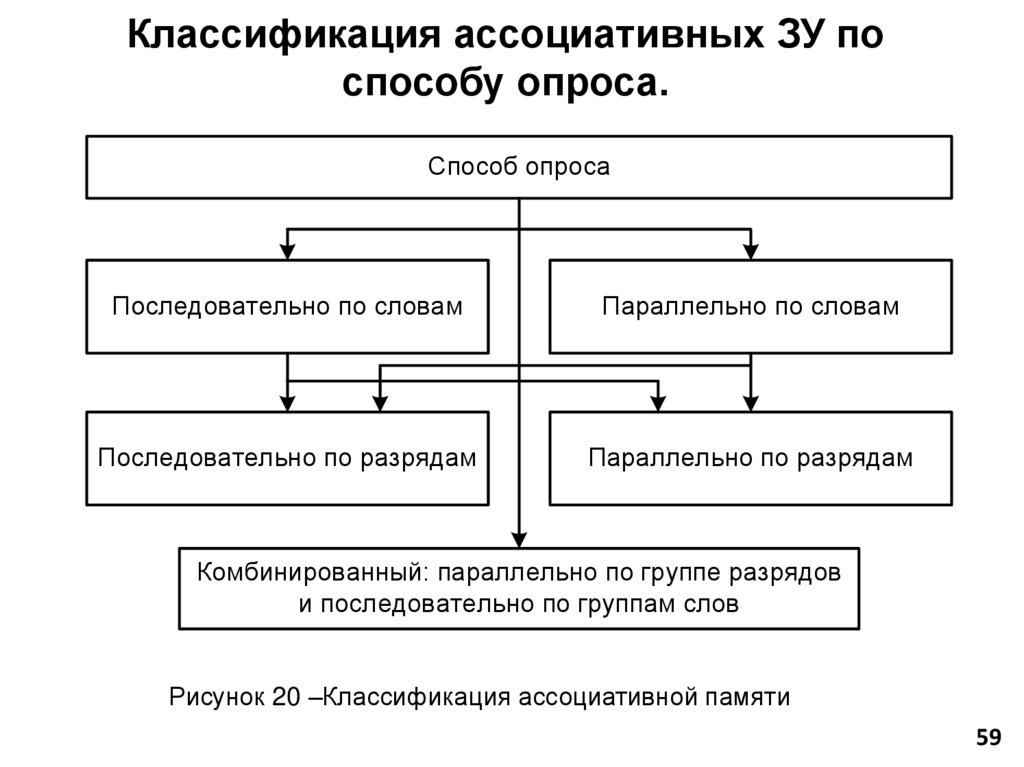

Классификация ассоциативных ЗУ поспособу опроса.

Способ опроса

Последовательно по словам

Параллельно по словам

Последовательно по разрядам

Параллельно по разрядам

Комбинированный: параллельно по группе разрядов

и последовательно по группам слов

Рисунок 20 –Классификация ассоциативной памяти

59

83.

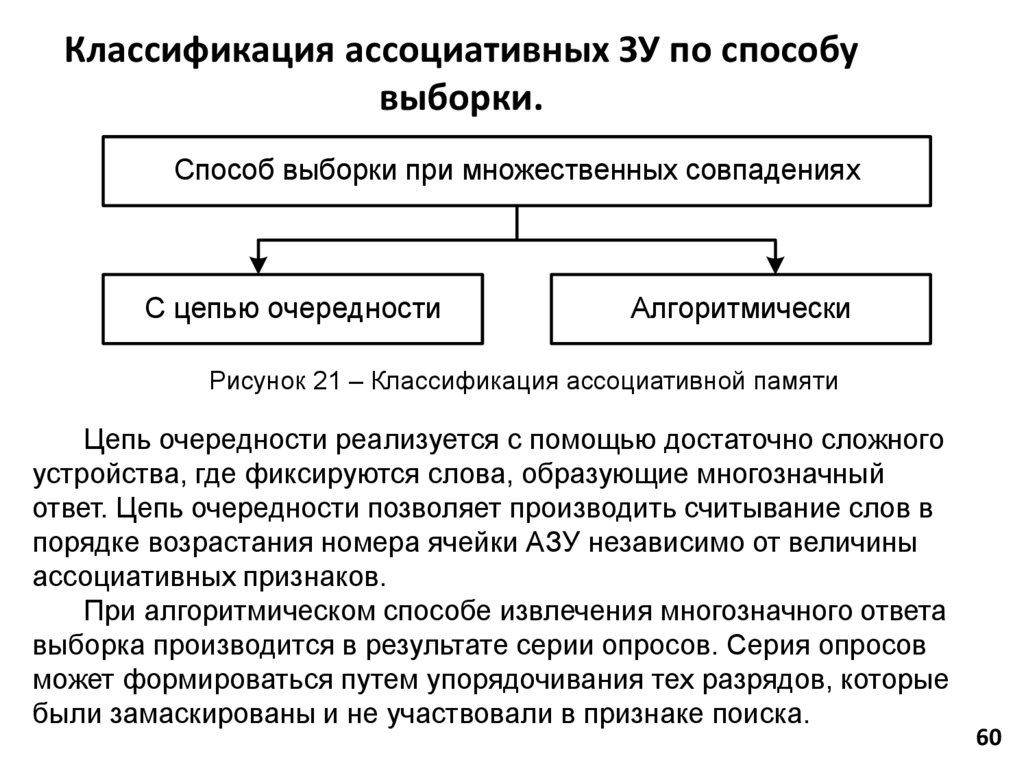

Классификация ассоциативных ЗУ по способувыборки.

Способ выборки при множественных совпадениях

С цепью очередности

Алгоритмически

Рисунок 21 – Классификация ассоциативной памяти

Цепь очередности реализуется с помощью достаточно сложного

устройства, где фиксируются слова, образующие многозначный

ответ. Цепь очередности позволяет производить считывание слов в

порядке возрастания номера ячейки АЗУ независимо от величины

ассоциативных признаков.

При алгоритмическом способе извлечения многозначного ответа

выборка производится в результате серии опросов. Серия опросов

может формироваться путем упорядочивания тех разрядов, которые

были замаскированы и не участвовали в признаке поиска.

60

84.

Лекция 6. Структура системы с основной и кэшпамятью.Адрес

памяти

0

1

2

3

Данные

Номер

строки

0

1

Блок (К слов) 2

Тег

Строка

C-1

Длина строки (К слов)

Кэш-память

Блок

n

2 -1

Длина слова

Основная память

Рисунок 22 – Структура системы с основной и кэш-памятью

61

85.

Прямое отображение основной памяти.При прямом отображении адрес строки i кэш-памяти, на которую

может быть отображен блок из ОП, определяется выражением: i =j mod

m, где m — общее число строк в кэш-памяти. В нашем примере i =j mod

128, где i может принимать значения от 0 до 127, а адрес блока j — от 0

до 16 383. Иными словами, на строку кэша с номером i отображается

каждый 128-й блок ОП, если отсчет начинать с блока, номер которого i.

Память

Строка тегов

0

0

1

1

2

2

127

Память

данных

Блок

0

Блок

257

Блок

130

...

...

127

Блок

16383

Кэш-память

0

Блок

0

Блок

1

Блок

2

1

2

Блок

128

0

Блок

257

129

Блок

130

Блок

256

Блок

257

Блок

258

127

Тег

Строка

0

1

2

...

Блок

127

Блок

16383

255

Блок

383

Блок

16383 127

Основная память

Рисунок 23 – Схема прямого отображения

62

86.

Полностью ассоциативное отображение.При реализации такого отображения 14-разрядный адрес блока основной

памяти условно разбивается на два поля. Логика кэш-памяти интерпретирует

эти 14 бит как 7-разрядный тег и 7-разрядное поле строки. Поле строки

указывает на одну из 128 = 2 7 строк кэш-памяти, а именно на ту, куда может

быть отображен блок с заданным адресом.

Строка Тег Адрес блока в кэш

Блок

0

2

2

0258

Блок

160

127

1

32

Блок

258

0

2

2

127

...

...

Память тегов

Блок

160

Память данных

32

1

Кэш-память

Блок 2

...

Блок 32

...

Блок 160

...

Блок 258

...

Основная память

Рисунок 24 – Схема ассоциативного о отображения

63

87.

Множественно-ассоциативное отображение.Кэш-память разбивается на v подмножеств (в дальнейшем будем

называть их модулями), каждое из которых содержит k строк. Зависимость

между модулем и блоками основной памяти такая же, как и при прямом

отображении: на строки, входящие в модуль i, могут быть отображены только

вполне определенные блоки основной памяти, в соответствии с соотношение

i =j mod v, где j — адрес блока основной памяти.

Память данных

Модуль Память тегов

0

1

Блок Блок

Блок Блок Блок

257 3200

64 32 320

Блок Блок

Блок Блок Блок

1 385

130

993 97

3

2

Блок Блок

Блок Блок Блок

257 96

64

32

0

Блок Блок

Блок Блок Блок

130 97

33 65

1

... ... ... ... ... ... ... ...

... ... ... ...

Блок Блок

Блок Блок Блок

63 127

95 16383 16383

Блок Блок

Блок Блок Блок

95 127

31 63 16383

0 2

1

10 100

1 31

3

0

31 2 511 1

12

3

Кэш-память

Тег

512 модуль

0

1

Блок

16383 31

Основная память

Рисунок 25 - Пример четырехвходовой кэш-памяти

64

88.

Отображение секторов.Память тегов

0

1

7

0

1

7

0

1

2

10

2

0

Блок

0

0

1

0

X

Блок

32

X

1

1

0

1

Блок

321

X

Блок

1

Блок Блок Блок

0

16

32

Блок Блок Блок

1

17

33

... ...

...

...

...

...

...

0

1

X

31

1

Блок

Блок

47

15

Память данных

Память битов

достоверности Кэш-память

...

...

1023

Сектор

Блок

0

1

...

Блок Блок Блок

Блок

15

15

31

47

16383

Основная память

Рисунок 26 – Схема отображения секторов

Здесь сектор состоит из 16 = 2 4 блоков по 16 слов, и основная память

содержит 1024 = 2 10 сектора. В 14-разрядном адресе блока основной памяти

старшие 10 разрядов показывают номер сектора, а младшие 4 — номер блока

внутри сектора. В свою очередь, кэш-память состоит из 8 = 23 секторов, и 7разрядный адрес строки в кэш включает в себя адрес сектора кэш (3 старших

разряда) и номер блока внутри сектора (4 младших разряда).

65

89.

Алгоритмы замещения информации в кэш-памяти.1. Алгоритм замещения на основе наиболее давнего использования

(LRU — Least Recently Used). Замещается та строка кэш-памяти, к

которой дольше всего не было обращения. Проводившиеся

исследования показали, что алгоритм LRU работает достаточно

хорошо в сравнении с оптимальным алгоритмом.

2. Алгоритм, работающий по принципу «первый вошел, первый

вышел» (FIFO — First In First Out). Заменяется строка, дольше

всего находившаяся в кэш-памяти.

3. Замена наименее часто использовавшейся строки (LFU — Least

Frequently Used). Заменяется строка в кэш-памяти, к которой было

меньше всего обращений. Связывают каждую строку со счетчиком

обращений, к содержимому которого после каждого обращения

добавляется единица. Главным претендентом на замещение

является строка, счетчик которой содержит наименьшее число.

4. Произвольный выбор строки для замены. Замещаемая строка

выбирается случайно. Реализовано с помощью счетчика,

содержимое которого увеличивается на единицу с каждым

тактовым импульсом, независимо от того, имело место попадание

или промах. Значение в счетчике определяет заменяемую строку. 66

90.

Лекция 7.Системы ввода/вывода ЭВМ.

Технически система ввода/вывода в рамках

микропроцессорной системы реализуется комплексом

модулей ввода/вывода (МВВ).

Модуль ввода/вывода выполняет сопряжение ВУ с

ядром микропроцессорной системы и различные

коммуникационные операции между ними.

Две основные функции МВВ:

обеспечение интерфейса с ЦП и памятью

(«большой» интерфейс);

2. обеспечение интерфейса с одним или несколькими

периферийными устройствами («малый» интерфейс).

1.

67

91.

Способы подключения СВВ к процессору.Центральный

процессор

Шина памяти

Шина памяти

управление

адрес

данные

управление

адрес

данные

адрес

данные

Управление вводом/

выводом

Память

Центральный

процессор

Система

ввода/

вывода

Управление вводом/

выводом

Память

Система

ввода/

вывода

б) Совместная шина управления

а) Раздельные шины

Шина памяти

Центральный

процессор

управление

адрес

данные

Память

в) Совместные шины

Управление вводом/

выводом

Система

ввода/

вывода

Рисунок 27 – Схема подключения СВВ

68

92.

Адресное пространствоРаспределение совмещенного адресного

пространства.

Ячейки

памяти

Регистры

модулей

ввода/вывода

Рисунок 28 - Совмещенное адресное пространство используется в

вычислительных машинах MIPS и SPARC.

69

93.

Достоинства совмещенного адресного пространства:1. расширение набора команд для обращения к внешним

устройствам позволяет сократить длину программы и повысить

быстродействие;

2. значительное увеличение количества подключаемых внешних

устройств;

3. возможность внепроцессорного обмена данными между внешними

устройствами, если в системе команд есть команды пересылки между

ячейками памяти;

4. возможность обмена информацией не только с аккумулятором, но

и с любым регистром центрального процессора.

Недостатки совмещенного адресного пространства:

1. сокращение области адресного пространства памяти;

2. усложнение декодирующих схем адресов в СВВ;

3. трудности распознавания операций передачи информации при

вводе/выводе среди других операций. Сложности в чтении и отладке

программы;

4. трудности при построении СВВ на простых модулях ввода/вывода:

сигналы управления не смогут координировать сложную процедуру

ввода/вывода.

Поэтому

МВВ

часто

должны

генерировать

дополнительные сигналы под управлением программы.

70

94.

Достоинства выделенного адресного пространства:1. адрес внешнего устройства в команде ввода/вывода может быть

коротким. В большинстве СВВ количество внешних устройств намного

меньше количества ячеек памяти. Короткий адрес ВУ подразумевает

такие же короткие команды ввода/вывода и простые дешифраторы;

2. программы становятся более наглядными, так как операции

ввода/вывода выполняются с помощью специальных команд;

3. разработка СВВ может проводиться отдельно от разработки

памяти.

Недостатки выделенного адресного пространства:

1. ввод/вывод производится только через аккумулятор центрального

процессора. Для передачи информации от ВУ в РОН, если

аккумулятор занят, требуется выполнение четырех команд

(сохранение содержимого аккумулятора, ввод из ВУ, пересылка из

аккумулятора в РОН, восстановление содержимого аккумулятора);

2. перед обработкой содержимого ВУ это содержимое нужно

переслать в ЦП.

71

95.

Структура внешнего устройства и модуляввода-вывода.

Все множество ПУ можно свести к трем категориям:

- для общения с пользователем;

- для общения с ВМ;

- для связи с удаленными устройствами.

Сигналы

управления из

модуля ввода/

вывода

Информация

состояния ВУ в МВВ

и состояния

МВВ в ВУ

Логика

управления

Обмен данными с

модулем ввода/

вывода

Буферная память

Преобразователь

Рисунок 28 - Структура внешнего устройства

Обмен данными с

внешней средой

72

96.

Структура модуля ввода/вывода.«Малый» интерфейс

«Большой» интерфейс

Регистр данных

Линии

данных

Линии

адреса

Линии

управления

Регистр состояния

Регистр

управления

Селектор

адреса

Узел

управления

вводомвыводом

DC

Данные

Узел

малого

интерфейса

ВУ1

Состояние

Управление

Узел

малого

интерфейса

ВУn

Данные

Состояние

Управление

..

..

.

Рисунок 29 – Структура модуля ВВ

73

97.

Алгоритм программно-управляемого ввода.Начало

Выдача команды

ввода в МВВ

ЦП

МВВ

Чтение из регистра

состояния МВВ

МВВ

ЦП

Подсчет

введенных слов

Нет

Введен весь блок?

Да

Не

готовы

Проверка

состояния МВВ

и ВУ

Признак

ошибки

Конец

Готовы

Ввод слова из МВВ

МВВ

ЦП

Запись слова в

память

ЦП

ОП

74

98.

Алгоритм ввода данных по прерыванию.Инициализация

Обработка прерывания

Начало

Вход

Выдача команды

ввода в МВВ

Чтение из регистра

состояния МВВ

Конец

Подсчет

введенных слов

Проверка

состояния МВВ

и ВУ

Готовы

Признак

ошибки

Введен

весь блок?

Да

Нет

Выдача команды

ввода в МВВ

Ввод слова из МВВ

Выход

Запись слова в

память

75

99.

Лекция 8. Многопроцессорные системы.Конвейеризация.

С1

С2

С3

С4

С5

Блок

выборки

команд

Блок

декодирования

Блок

выборки

операндов

Блок

выполнения

команд

Блок

возврата

Конвейер с пятью стадиями

С1

1

С2

2

3

4

5

1

2

3

4

1

2

С3

1

С4

С5

1

2

3

4

6

7

8

9

8

2

1

2

3

4

5

5

6

7

8

9

Рисунок 30 – Структура конвейера

1

2

76

100.

Микропроцессор с разнесенной архитектурой.Память

А-команды

запись

E-команды

чтение

AE

EA

AW

АА

А - регистры

X-регистры

Адресный А-процессор

Исполнительный Е-процессор

Рисунок 31 – Структура микропроцессора с разнесенной архитектурой

77

101.

Структура суперскалярного микропроцессора.Блок

прогнозирования

ветвлений

Шина адреса, данных,

сигналов управления

Устройства связи с кэш 2-го уровня

и системной шиной

Блок предварительной

дешифрации

Кэш команд

Буфер переупорядочивания

Структура суперскалярного

команд

микропроцессора

FPU1

FPU2

FPU3

Файл регистров

данных

ALU1

ALU2

Файл целочисленных регистров

LSU

Кэш

данных

Устройства

переименования

регистров

Рисунок 32 – Структура суперскалярного микропроцессора

78

102.

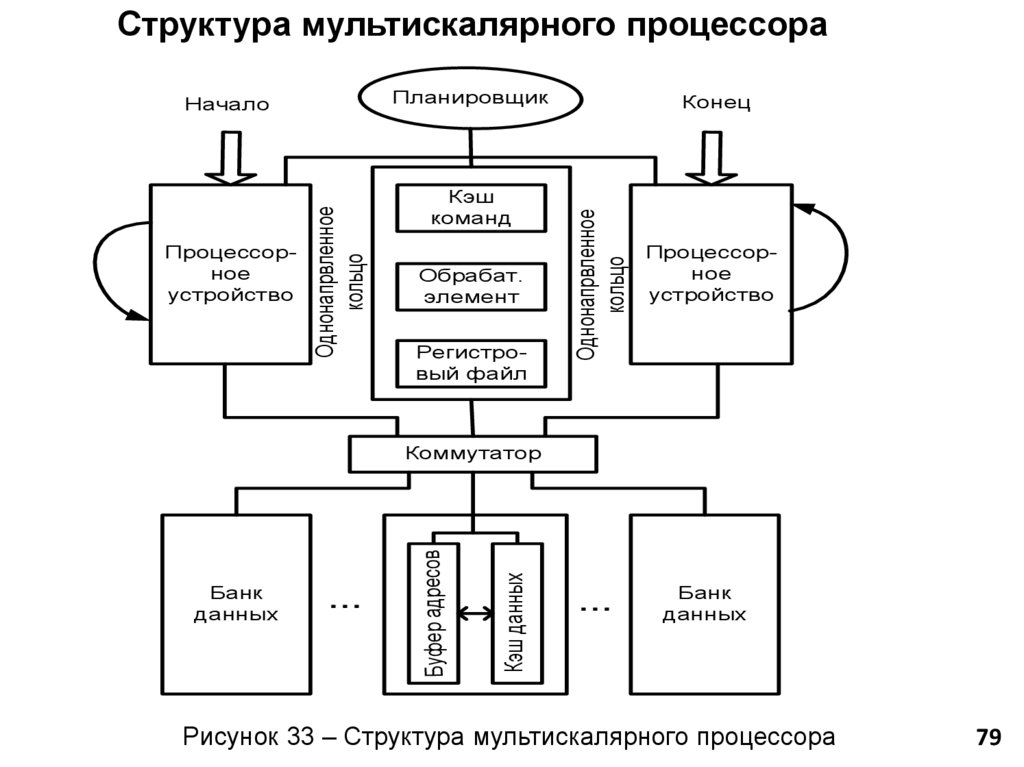

Структура мультискалярного процессораПланировщик

Кэш

команд

Обрабат.

элемент

Регистровый файл

Конец

Однонапрвленное

кольцо

Процессорное

устройство

Однонапрвленное

кольцо

Начало

Процессорное

устройство

...

Кэш данных

Банк

данных

Буфер адресов

Коммутатор

...

Банк

данных

Рисунок 33 – Структура мультискалярного процессора

79

103.

Классификация архитектурпараллельных ЭВМ.

В научной литературе и технической документации можно найти

более десятка различных названий, характеризующих лишь общие

принципы функционирования параллельных машин: векторноконвейерные, массивно-параллельные, компьютеры с широким

командным

словом,

систолические

массивы,

гиперкубы,

спецпроцессоры и мультипроцессоры, иерархические и кластерные

компьютеры, dataflow, матричные ЭВМ и многие другие.

Для классификации систем с микропроцессорной обработкой за

основу могут быть выбраны такие характеристики как:

1. тип и число компонент в ВС;

2. топология связи;

3. принцип построения переключения память–процессор;

4. возможность конвейерной и параллельной обработки.

Выбор конкретной классификации, в основном, определяется

стремлением разработчиков отразить потенциальные возможности

той или иной архитектуры ВС.

80

104.

Существующие на сегодняшний день классификации1. Классификация М. Флинна

2. Классификация Р. Хокни

3. Классификация Джонса

4. Классификация Энслоу

5. Классификации xPxM/xPxC

6. Классификация Т. Фенга

7. Классификация В. Хендлера

8. Классификация Д. Скилликорна

9. Классификация Фенга

10. Классификация Шора

11. Классификация Шнайдера

12. Классификация Джонсона

13. Классификация Базу

14. Классификация Кришнамарфи

15. Классификация Дазгупты

16. Классификация Дункана

81

105.

Классификация М. Флинна.На основе числа потоков команд и потоков данных Флинн

выделяет четыре класса архитектур:

SISD, MISD, SIMD, MIMD

SISD (single instruction stream / single data stream) –

одиночный поток команд и одиночный поток данных;

SIMD (single instruction stream / multiple data stream) –

одиночный поток команд и множественный поток данных.

MISD (multiple instruction stream / single data stream) –

множественный поток команд и одиночный поток данных.

MIMD (multiple instruction stream / multiple data stream) –

множественный поток команд и множественный поток

данных.

82

106.

SISD – одиночный поток команд иодиночный поток данных

ПР – это один или

несколько процессорных

элементов,

УУ –устройство

управления,

ПД – память данных.

Рисунок 34 – Структура SISD

К классу SISD относятся, прежде всего классические

последовательные машины или, иначе, машины фон-Неймановского

типа, например, PDP-11 или VAX 11/780.

83

107.

SIMD - одиночный поток команд имножественный поток данных

Рисунок 35 – Структура SIМD

Команды и данные в этих системах хранятся в глобальной

оперативной памяти (ОП). Центральное УУ направляет операции ПР,

связывая их глобальной сетью распространения и синхронизируя их

работу. К такому виду процессоров относятся матричные процессоры,

например, ILLIAC IV, STARAN, машины с массовым параллелизмом и

другие. Подобные архитектуры хорошо решают задачи из матричной

алгебры и задачи, которые к ней сводятся (обработка изображений).

84

108.

MISD - один поток данных имножественный поток команд

Рисунок 36 – Структура МISD

Специалисты в области архитектуры компьютеров до сих пор не

смогли представить убедительный пример реально существующей

вычислительной системы, построенной на данном принципе.

85

109.

MIMD – множественный поток команди множественный поток данных

Рисунок 37 – Структура МIМD

Класс MIMD чрезвычайно широк, поскольку включает в себя

всевозможные мультипроцессорные системы, например, такие

как: Cray Y-MP, Denelcor HEP. Intel Paragon, Cray T3D и др.

86

110.

Расширенная классификация ФлиннаАрхитектуры компьютеров

параллельного действия

SISD

SIMD

MISD

(Фон Нейман)

?

Массивнопараллельный

процессор

Векторный

процессор

UMA

С шинной

организацией

MIMD

Мультипроцессоры

COMA

С координатными

коммутаторами

NUMA

CCNUMA

Совместно используемая память

NCNUMA

Мультикомпьютеры

MPP

COW

В виде

решетки

В виде

гиперкуба

Передача сообщений

Рисунок 38 – Расширенная классификация Флинна

87

111.

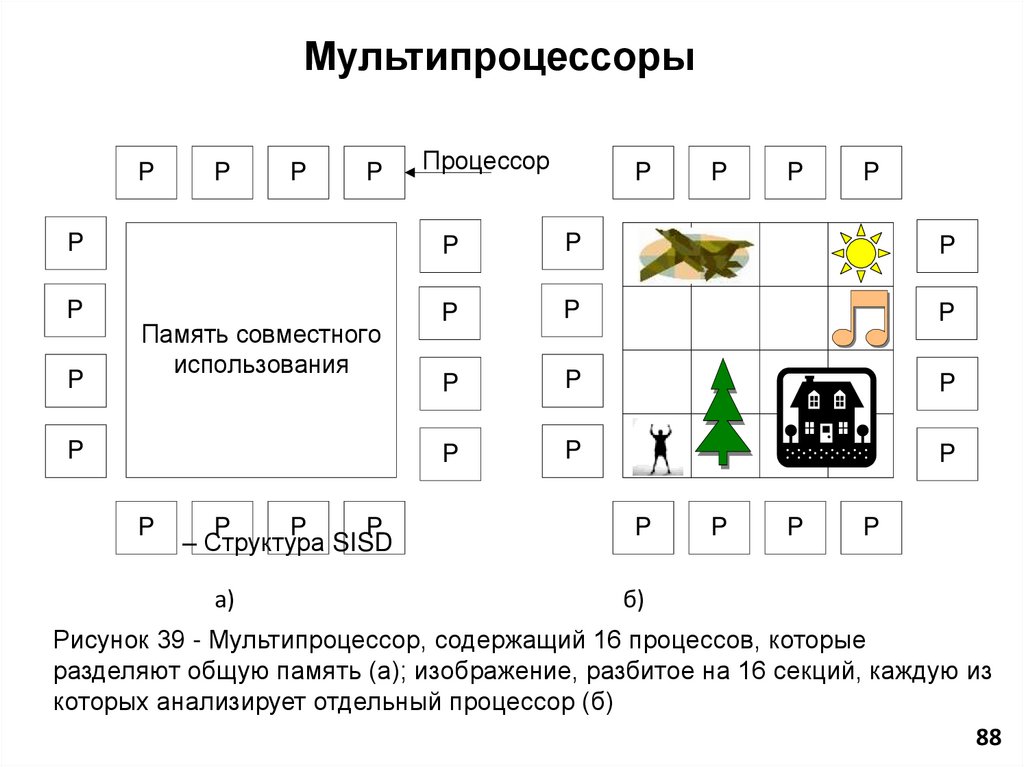

МультипроцессорыP

P

P

P

Процессор

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

P

Память совместного

использования

P

P

P

P

P

– Структура SISD

а)

P

P

P

P

б)

Рисунок 39 - Мультипроцессор, содержащий 16 процессов, которые

разделяют общую память (а); изображение, разбитое на 16 секций, каждую из

которых анализирует отдельный процессор (б)

88

112.

МультикомпьютерыM

P

M

P

M

P

M

P

M

M

M

M

P

P

P

P

Сеть с

передачей

сообщений

P

P

P

P

M

M

M

M

а)

Собственая память

Процессор

P

P

M

P

P

M

P

P

M

P

P

M

P

P

P

P

Процессор

P

Сеть с

передачей

сообщений

P

P

P

P

P

P

P

б)

Рисунок 40 - Мультикомпьютер, содержащий 16 процессоров, каждый из

которых имеет свою собственную память (а); битовое отображение

рисунка предыдущего слайда, разделенное между 16 участками памяти (б)

89

113.

Мультикомпьютеры1. UMA - Uniform Memory Access – архитектура с однородным

доступом к памяти

2. NUMA - Non Uniform Memory Access – архитектура с

неоднородным доступом к памяти

3. COMA - Cashe Only Memory Access – архитектура с доступом

только к кэш-памяти

Так как мультикомпьютеры не имеют прямого доступа к

отдельным модулям памяти, они иногда называются машинами

NORMA - NO Remote Memory Access – без доступа к отдаленным

модулям памяти

Мультикомпьютеры можно разделить на две категории:

1. Первая категория содержит процессоры MPP (Massively Parallel

Processors – процессоры с массивным параллелизмом);

2. Вторая категория мультикомпьютеров включает рабочие станции,

которые связываются с помощью уже имеющихся технологий

соединений. Эти примитивные машины называются NOW (Network

of Workstations – сеть рабочих станций) и COW (Cluster of

Workstattions – кластер рабочих станций).

90

Электроника

Электроника