Похожие презентации:

Этапы проектирования изделий электронной техники с использованием языка VHDL

1.

Этапы проектирования изделийэлектронной техники с

использованием языка VHDL

Кафедра АВС 2010

2. Кратко о VHDL

VHDL - Very high-speed integrated circuitsHardware Description Language

VHDL-87 - ANSI/IEEE Std 1076-1987

VHDL-93 - ANSI/IEEE Std 1076-1993

VHDL-AMS - ANSI/IEEE Std 1076.1-1999

VHDL синтезируемое подмножество - IEEE

P1076.6/D1.12 Draft Standard For VHDL Register

Transfer Level Synthesis,1998

Кафедра АВС 2010

3. VHDL- проект

Проектирование сложных вычислительныхустройств (ВУ)

Объединение структуры ВУ и алгоритма его

функционирования.

Высокая надежность проекта.

VHDL-проект - универсальное средство

описания ВУ на различных уровнях

детализации.

Кафедра АВС 2010

4. Уровни описания на языке VHDL

Алгоритмический.Структурный.

Регистровых передач (RTL) и потоков

данных (dataflow).

Логический.

Аналоговые схемы.

Кафедра АВС 2010

5. Процесс проектирования на языке VHDL

Моделирование на языке VHDLПоведенческая

модель ВУ

САПР ПЛИС

Синтезируемая

модель ВУ

Компилятор

синтезатор

Моделирование

синтезированной

модели

ВУ на уровне

вентилей

Размещение,

трассировка

Тесты

Моделирование с

учётом топологии

ВУ, готовое

к реализации

Конфигурирование

ПЛИС

Кафедра АВС 2010

Страница 1

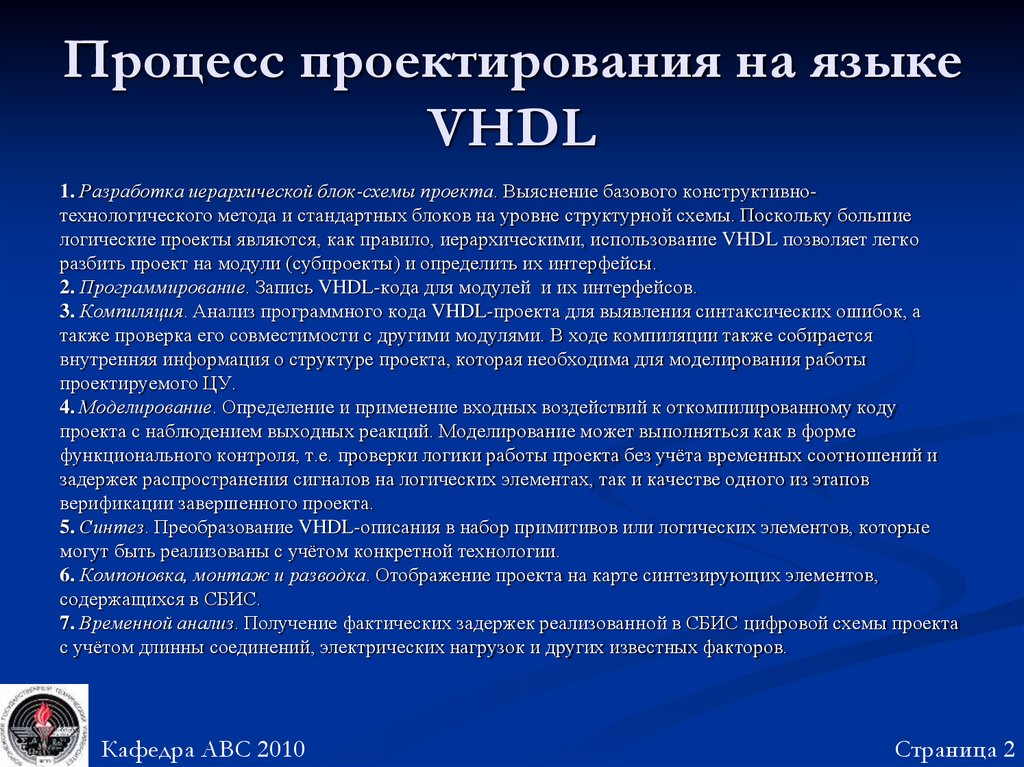

6. Процесс проектирования на языке VHDL

1. Разработка иерархической блок-схемы проекта. Выяснение базового конструктивнотехнологического метода и стандартных блоков на уровне структурной схемы. Поскольку большиелогические проекты являются, как правило, иерархическими, использование VHDL позволяет легко

разбить проект на модули (субпроекты) и определить их интерфейсы.

2. Программирование. Запись VHDL-кода для модулей и их интерфейсов.

3. Компиляция. Анализ программного кода VHDL-проекта для выявления синтаксических ошибок, а

также проверка его совместимости с другими модулями. В ходе компиляции также собирается

внутренняя информация о структуре проекта, которая необходима для моделирования работы

проектируемого ЦУ.

4. Моделирование. Определение и применение входных воздействий к откомпилированному коду

проекта с наблюдением выходных реакций. Моделирование может выполняться как в форме

функционального контроля, т.е. проверки логики работы проекта без учёта временных соотношений и

задержек распространения сигналов на логических элементах, так и качестве одного из этапов

верификации завершенного проекта.

5. Синтез. Преобразование VHDL-описания в набор примитивов или логических элементов, которые

могут быть реализованы с учётом конкретной технологии.

6. Компоновка, монтаж и разводка. Отображение проекта на карте синтезирующих элементов,

содержащихся в СБИС.

7. Временной анализ. Получение фактических задержек реализованной в СБИС цифровой схемы проекта

с учётом длинны соединений, электрических нагрузок и других известных факторов.

Кафедра АВС 2010

Страница 2

7. Преимущества VHDL как языка САПР ВУ

Гибкость.Универсальность.

Моделирование с учетом задержек.

Унифицированное подключение блоков.

Стандартное тестирование.

Кафедра АВС 2010

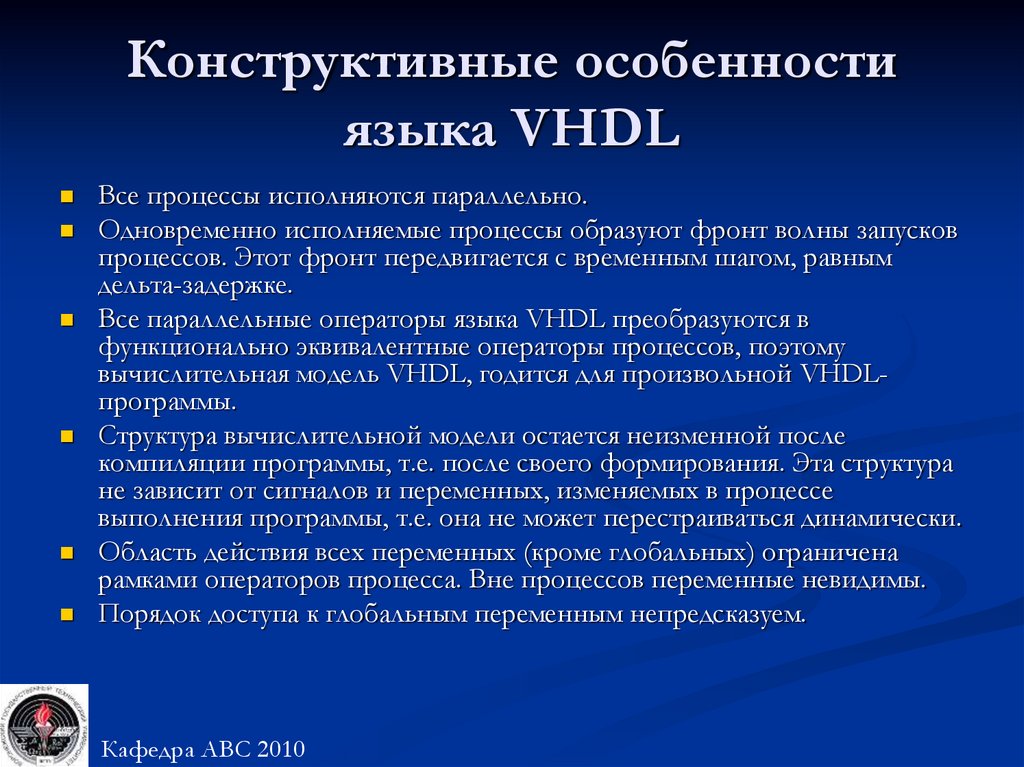

8. Конструктивные особенности языка VHDL

Все процессы исполняются параллельно.Одновременно исполняемые процессы образуют фронт волны запусков

процессов. Этот фронт передвигается с временным шагом, равным

дельта-задержке.

Все параллельные операторы языка VHDL преобразуются в

функционально эквивалентные операторы процессов, поэтому

вычислительная модель VHDL, годится для произвольной VHDLпрограммы.

Структура вычислительной модели остается неизменной после

компиляции программы, т.е. после своего формирования. Эта структура

не зависит от сигналов и переменных, изменяемых в процессе

выполнения программы, т.е. она не может перестраиваться динамически.

Область действия всех переменных (кроме глобальных) ограничена

рамками операторов процесса. Вне процессов переменные невидимы.

Порядок доступа к глобальным переменным непредсказуем.

Кафедра АВС 2010

9.

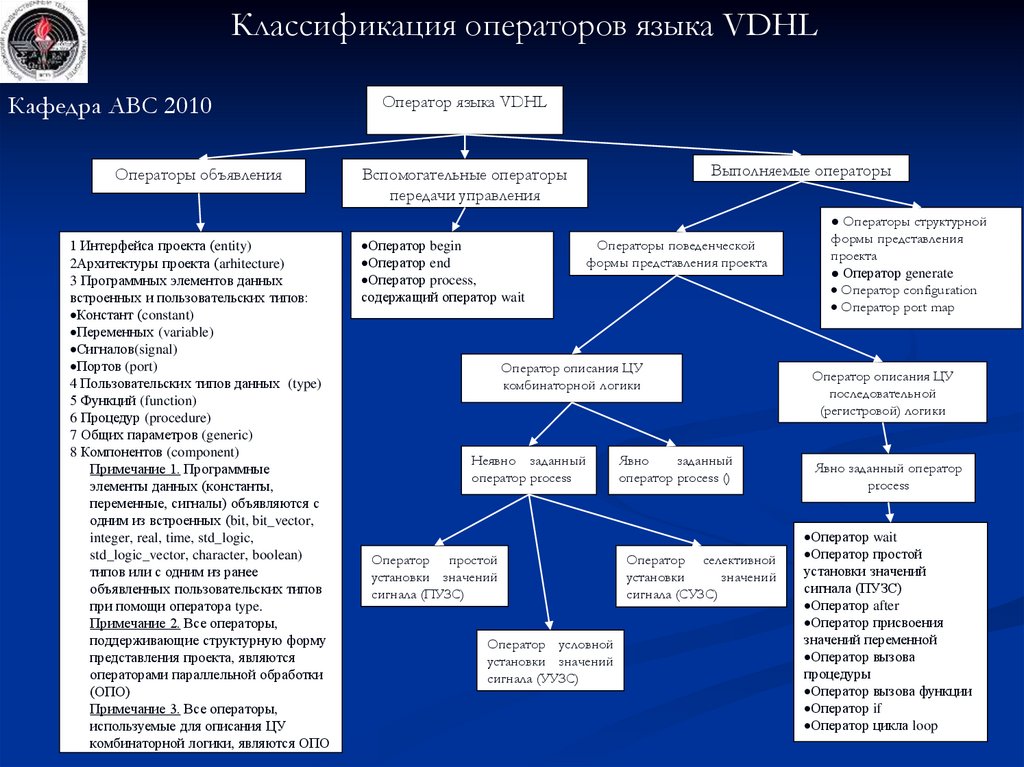

Классификация операторов языка VDHLКафедра АВС 2010

Операторы объявления

1 Интерфейса проекта (entity)

2Архитектуры проекта (arhitecture)

3 Программных элементов данных

встроенных и пользовательских типов:

Констант (constant)

Переменных (variable)

Сигналов(signal)

Портов (port)

4 Пользовательских типов данных (type)

5 Функций (function)

6 Процедур (procedure)

7 Общих параметров (generic)

8 Компонентов (component)

Примечание 1. Программные

элементы данных (константы,

переменные, сигналы) объявляются с

одним из встроенных (bit, bit_vector,

integer, real, time, std_logic,

std_logic_vector, character, boolean)

типов или с одним из ранее

объявленных пользовательских типов

при помощи оператора type.

Примечание 2. Все операторы,

поддерживающие структурную форму

представления проекта, являются

операторами параллельной обработки

(ОПО)

Примечание 3. Все операторы,

используемые для описания ЦУ

комбинаторной логики, являются ОПО

Оператор языка VDHL

Выполняемые операторы

Вспомогательные операторы

передачи управления

Оператор begin

Оператор end

Оператор process,

содержащий оператор wait

Операторы поведенческой

формы представления проекта

Оператор описания ЦУ

комбинаторной логики

Неявно заданный

оператор process

Оператор простой

установки значений

сигнала (ПУЗС)

Оператор условной

установки значений

сигнала (УУЗС)

Явно

заданный

оператор process ()

Оператор селективной

установки

значений

сигнала (СУЗС)

● Операторы структурной

формы представления

проекта

● Оператор generate

Оператор configuration

Оператор port map

Оператор описания ЦУ

последовательной

(регистровой) логики

Явно заданный оператор

process

Оператор wait

Оператор простой

установки значений

сигнала (ПУЗС)

Оператор after

Оператор присвоения

значений переменной

Оператор вызова

процедуры

Оператор вызова функции

Оператор if

Оператор цикла loop

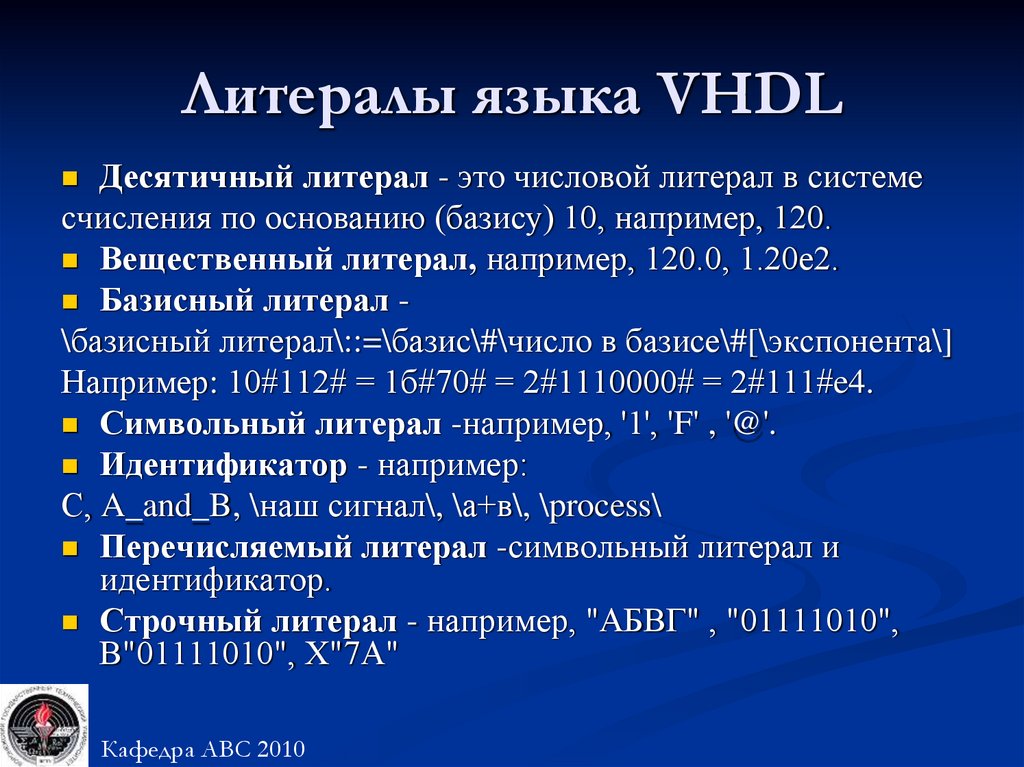

10. Литералы языка VHDL

Десятичный литерал - это числовой литерал в системесчисления по основанию (базису) 10, например, 120.

Вещественный литерал, например, 120.0, 1.20е2.

Базисный литерал \базисный литерал\::=\базис\#\число в базисе\#[\экспонента\]

Например: 10#112# = 1б#70# = 2#1110000# = 2#111#e4.

Символьный литерал -например, '1', 'F' , '@'.

Идентификатор - например:

С, A_and_B, \наш сигнал\, \а+в\, \process\

Перечисляемый литерал -символьный литерал и

идентификатор.

Строчный литерал - например, "АБВГ" , "01111010",

В"01111010", Х"7А"

Кафедра АВС 2010

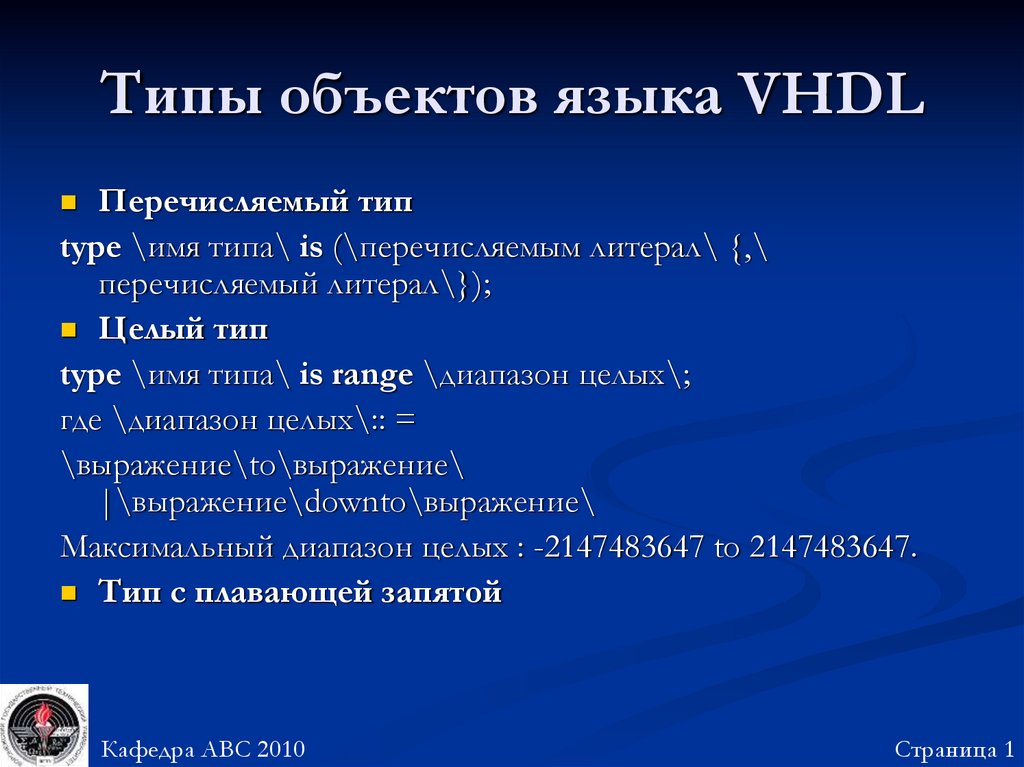

11. Типы объектов языка VHDL

Перечисляемый типtype \имя типа\ is (\перечисляемым литерал\ {,\

перечисляемый литерал\});

Целый тип

type \имя типа\ is range \диапазон целых\;

где \диапазон целых\:: =

\выражение\to\выражение\

|\выражение\downto\выражение\

Максимальный диапазон целых : -2147483647 to 2147483647.

Тип с плавающей запятой

Кафедра АВС 2010

Страница 1

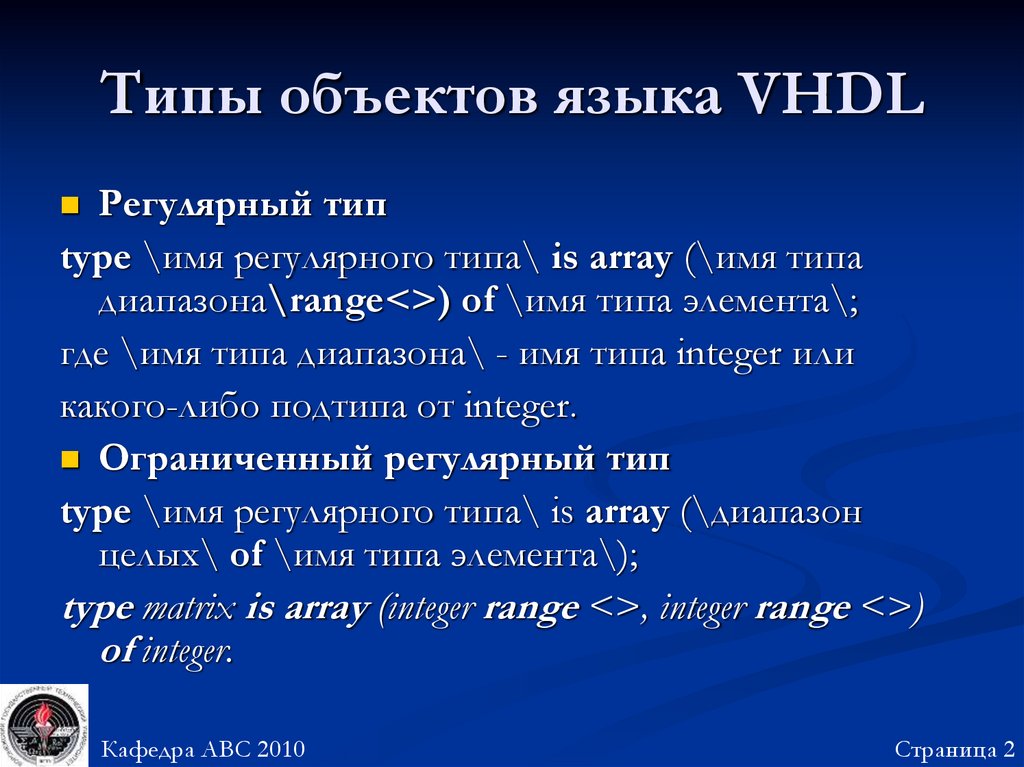

12. Типы объектов языка VHDL

Регулярный типtype \имя регулярного типа\ is array (\имя типа

диапазона\range<>) of \имя типа элемента\;

где \имя типа диапазона\ - имя типа integer или

какого-либо подтипа от integer.

Ограниченный регулярный тип

type \имя регулярного типа\ is array (\диапазон

целых\ of \имя типа элемента\);

type matrix is array (integer range <>, integer range <>)

of integer.

Кафедра АВС 2010

Страница 2

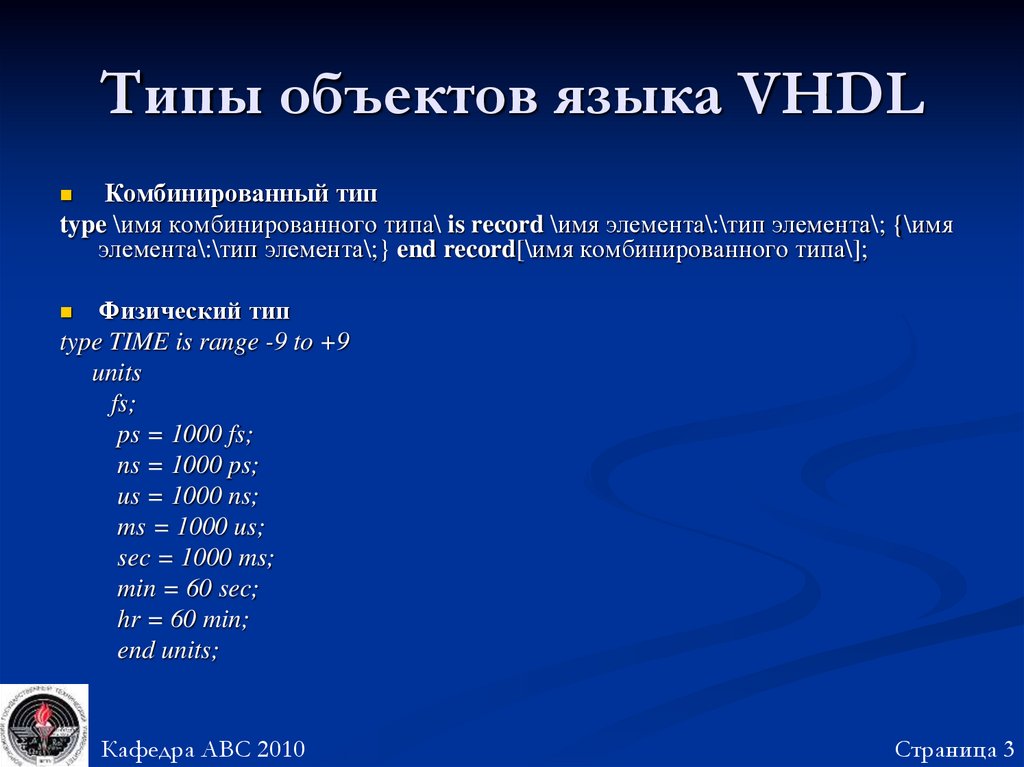

13. Типы объектов языка VHDL

Комбинированный типtype \имя комбинированного типа\ is record \имя элемента\:\тип элемента\; {\имя

элемента\:\тип элемента\;} end record[\имя комбинированного типа\];

Физический тип

type TIME is range -9 to +9

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

Кафедра АВС 2010

Страница 3

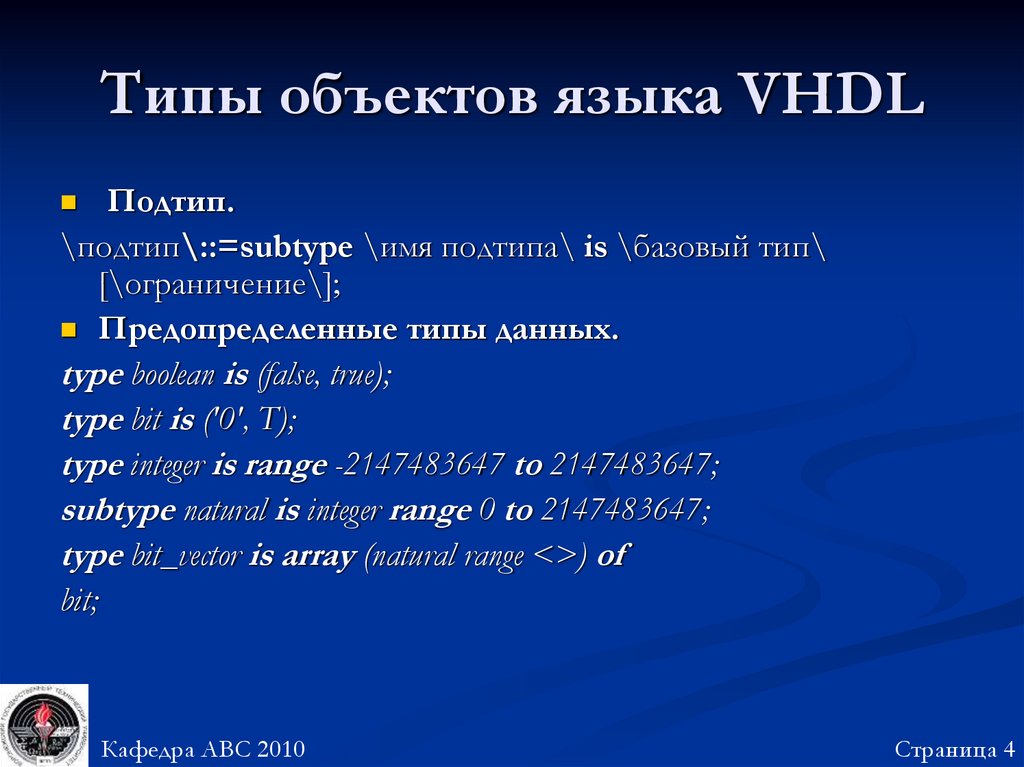

14. Типы объектов языка VHDL

Подтип.\подтип\::=subtype \имя подтипа\ is \базовый тип\

[\ограничение\];

Предопределенные типы данных.

type boolean is (false, true);

type bit is ('0', T);

type integer is range -2147483647 to 2147483647;

subtype natural is integer range 0 to 2147483647;

type bit_vector is array (natural range <>) of

bit;

Кафедра АВС 2010

Страница 4

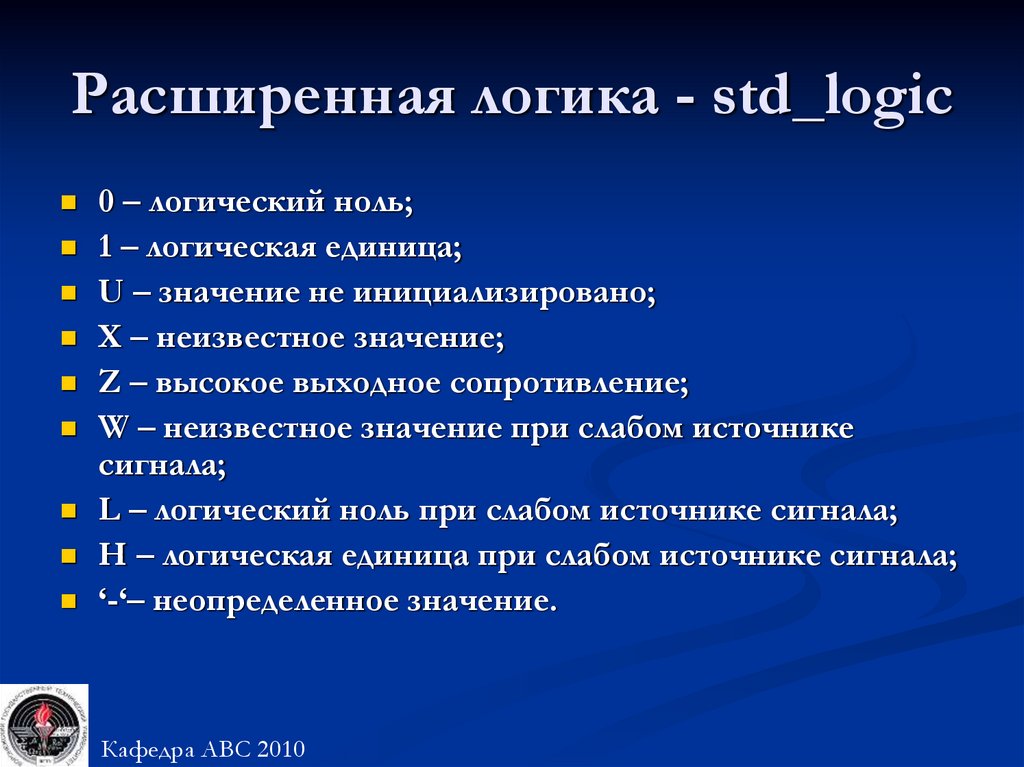

15. Расширенная логика - std_logic

0 – логический ноль;1 – логическая единица;

U – значение не инициализировано;

X – неизвестное значение;

Z – высокое выходное сопротивление;

W – неизвестное значение при слабом источнике

сигнала;

L – логический ноль при слабом источнике сигнала;

H – логическая единица при слабом источнике сигнала;

‘-‘– неопределенное значение.

Кафедра АВС 2010

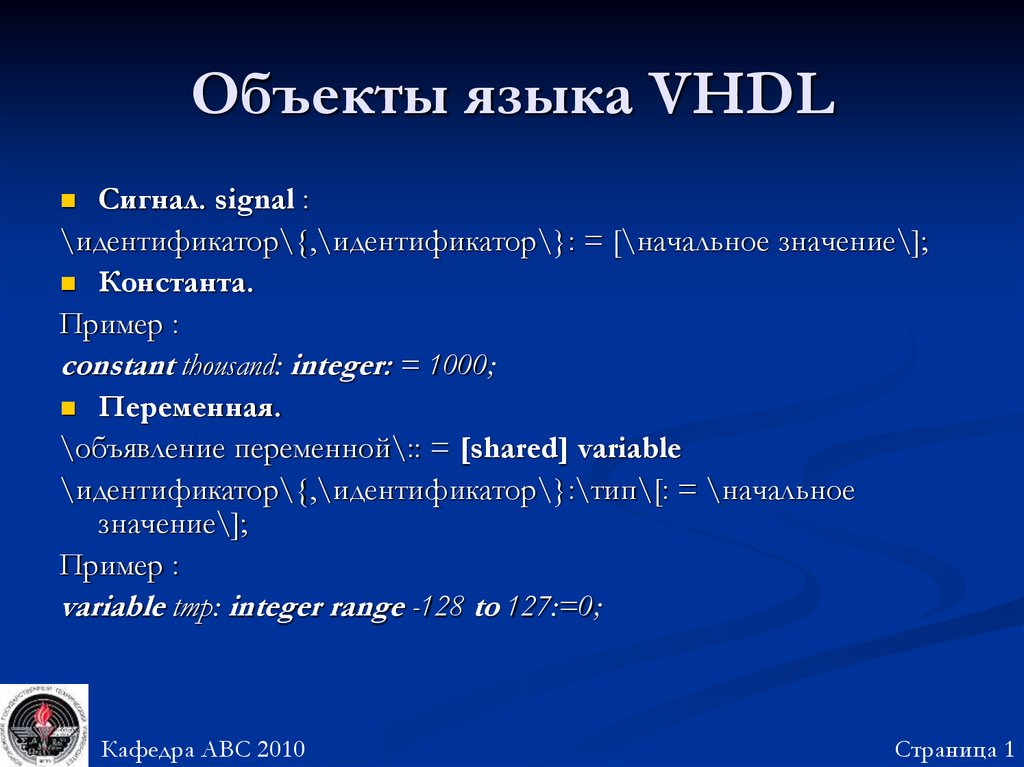

16. Объекты языка VHDL

Сигнал. signal :\идентификатор\{,\идентификатор\}: = [\начальное значение\];

Константа.

Пример :

constant thousand: integer: = 1000;

Переменная.

\объявление переменной\:: = [shared] variable

\идентификатор\{,\идентификатор\}:\тип\[: = \начальное

значение\];

Пример :

variable tmp: integer range -128 to 127:=0;

Кафедра АВС 2010

Страница 1

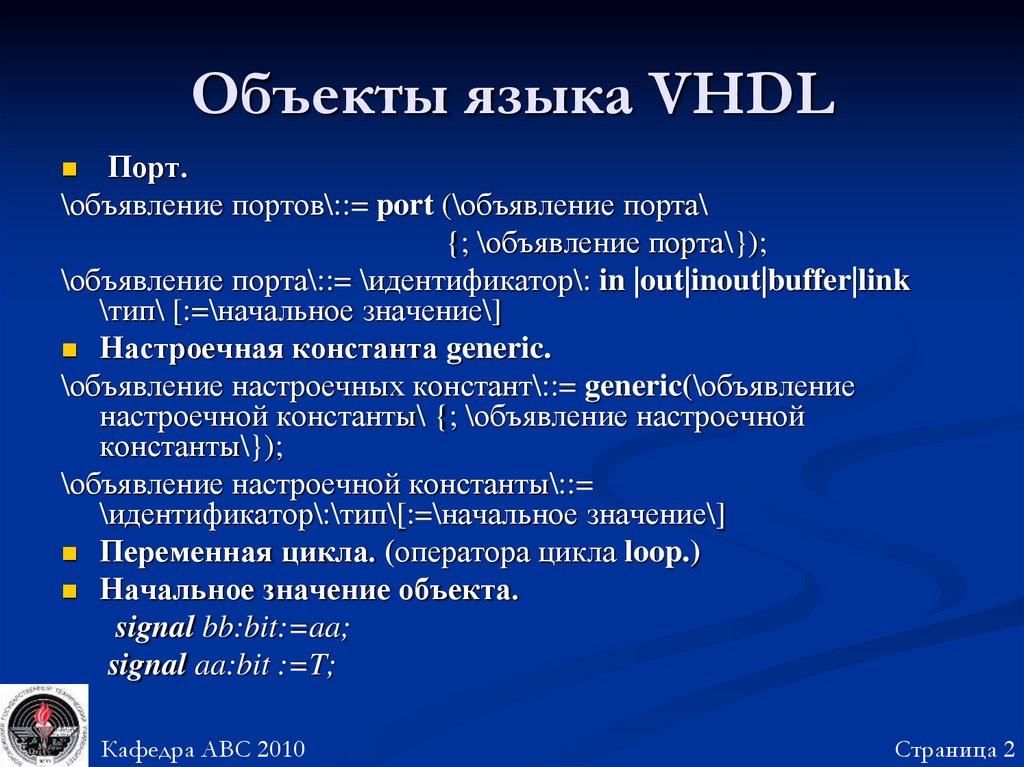

17. Объекты языка VHDL

Порт.\объявление портов\::= port (\объявление порта\

{; \объявление порта\});

\объявление порта\::= \идентификатор\: in |out|inout|buffer|link

\тип\ [:=\начальное значение\]

Настроечная константа generic.

\объявление настроечных констант\::= generic(\объявление

настроечной константы\ {; \объявление настроечной

константы\});

\объявление настроечной константы\::=

\идентификатор\:\тип\[:=\начальное значение\]

Переменная цикла. (оператора цикла loop.)

Начальное значение объекта.

signal bb:bit:=aa;

signal aa:bit :=T;

Кафедра АВС 2010

Страница 2

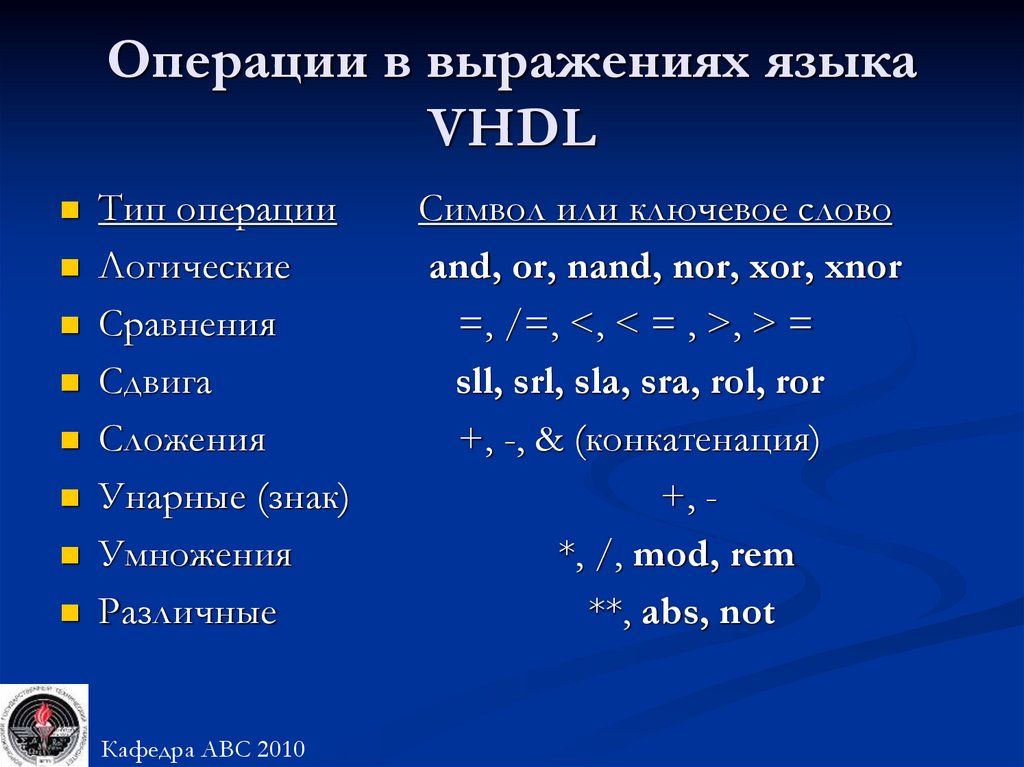

18. Операции в выражениях языка VHDL

Тип операцииЛогические

Сравнения

Сдвига

Сложения

Унарные (знак)

Умножения

Различные

Кафедра АВС 2010

Символ или ключевое слово

and, or, nand, nor, xor, xnor

=, /=, <, < = , >, > =

sll, srl, sla, sra, rol, ror

+, -, & (конкатенация)

+, *, /, mod, rem

**, abs, not

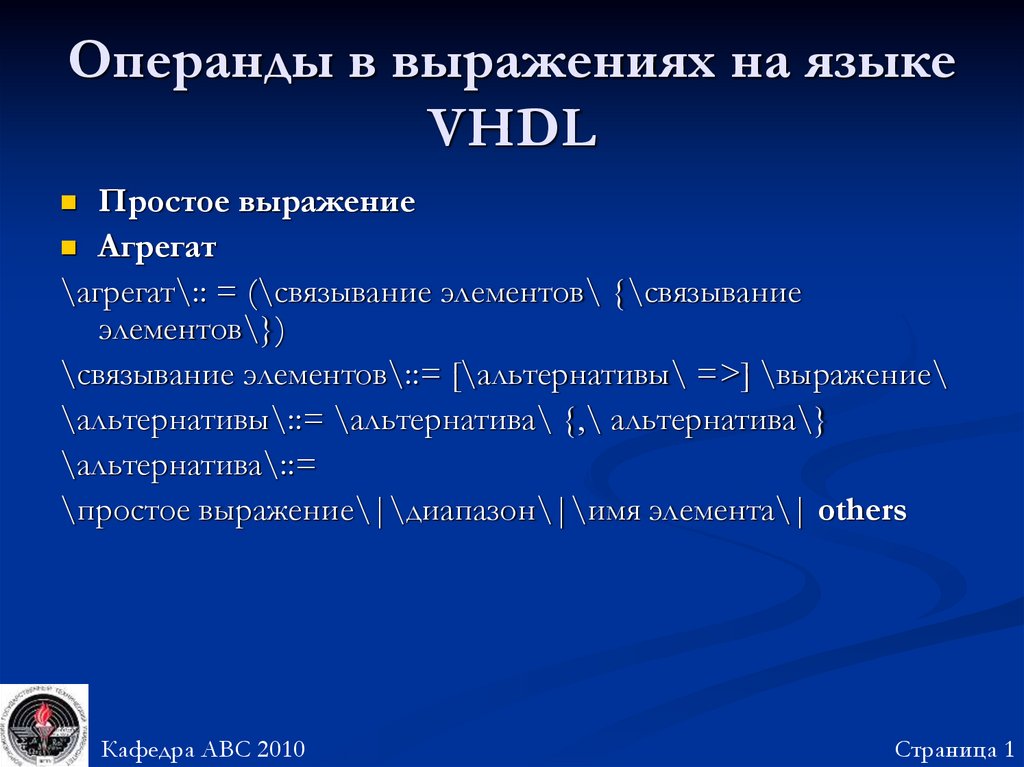

19. Операнды в выражениях на языке VHDL

Простое выражениеАгрегат

\агрегат\:: = (\связывание элементов\ {\связывание

элементов\})

\связывание элементов\::= [\альтернативы\ =>] \выражение\

\альтернативы\::= \альтернатива\ {,\ альтернатива\}

\альтернатива\::=

\простое выражение\|\диапазон\|\имя элемента\| others

Кафедра АВС 2010

Страница 1

20. Операнды в выражениях на языке VHDL

variable v_5: bit_vector (0 to 4): = ('0', '0', '0', '1', '1')Эквивалентные агрегаты :

(3 |4 => 'i' , others => '0');

или (0 to 2 => '0'; 3 to 4 => 'i');

или ('0', '0',3 to 4 => 'i' , others => '0')

Для регулярных типов : (i => 'i', others => '0')

Для комбинированных типов :

type complex is record

( Re : integer; Im : integer );

end record;

variable X is complex: = (Re => i000, Im => 0);

Кафедра АВС 2010

Страница 2

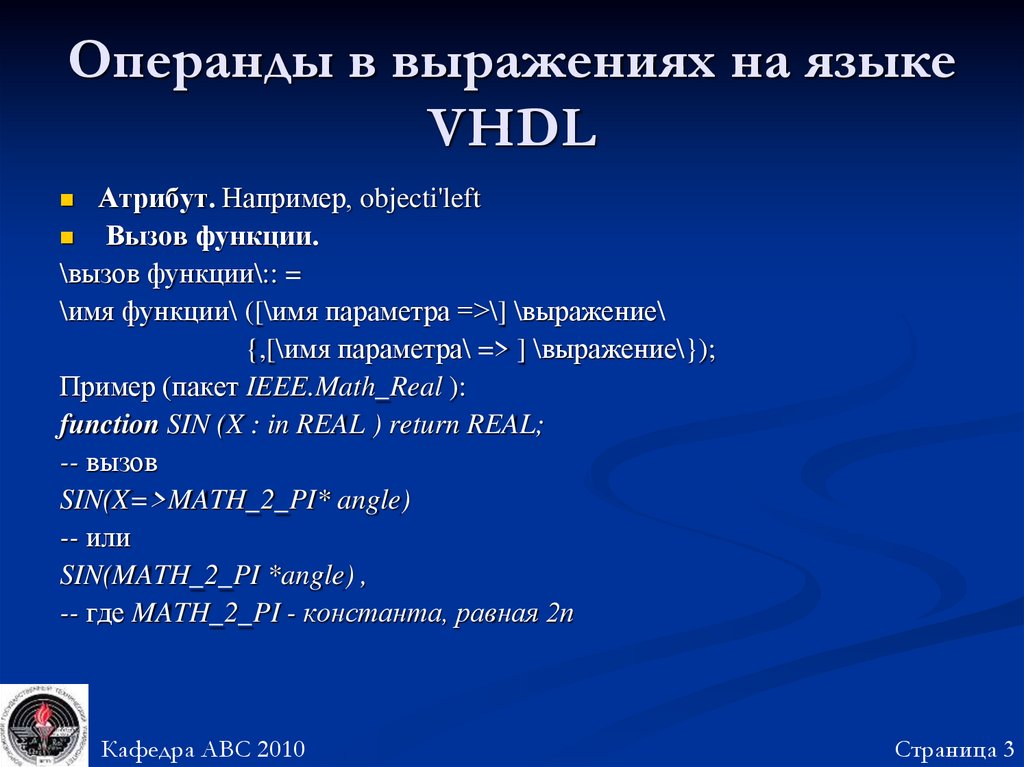

21. Операнды в выражениях на языке VHDL

Атрибут. Например, objecti'leftВызов функции.

\вызов функции\:: =

\имя функции\ ([\имя параметра =>\] \выражение\

{,[\имя параметра\ => ] \выражение\});

Пример (пакет IEEE.Math_Real ):

function SIN (X : in REAL ) return REAL;

-- вызов

SIN(X=>MATH_2_PI* angle)

-- или

SIN(MATH_2_PI *angle) ,

-- где MATH_2_PI - константа, равная 2п

Кафедра АВС 2010

Страница 3

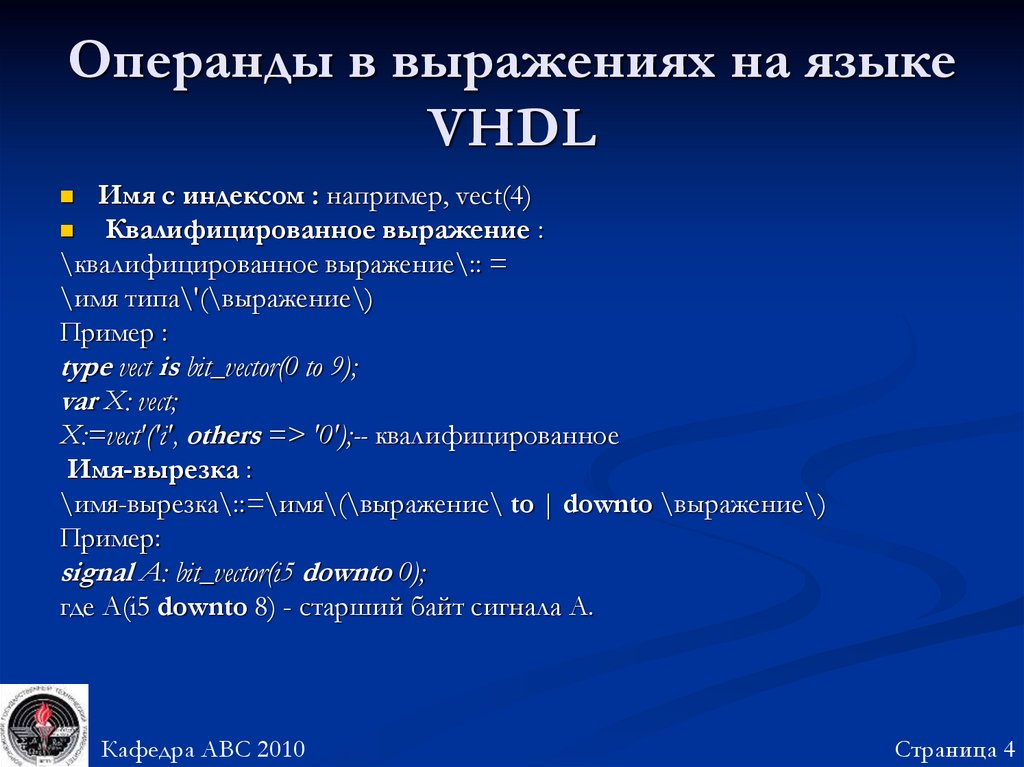

22. Операнды в выражениях на языке VHDL

Имя с индексом : например, vect(4)Квалифицированное выражение :

\квалифицированное выражение\:: =

\имя типа\'(\выражение\)

Пример :

type vect is bit_vector(0 to 9);

var X: vect;

X:=vect'('i', others => '0');-- квалифицированное

Имя-вырезка :

\имя-вырезка\::=\имя\(\выражение\ to | downto \выражение\)

Пример:

signal A: bit_vector(i5 downto 0);

где A(i5 downto 8) - старший байт сигнала A.

Кафедра АВС 2010

Страница 4

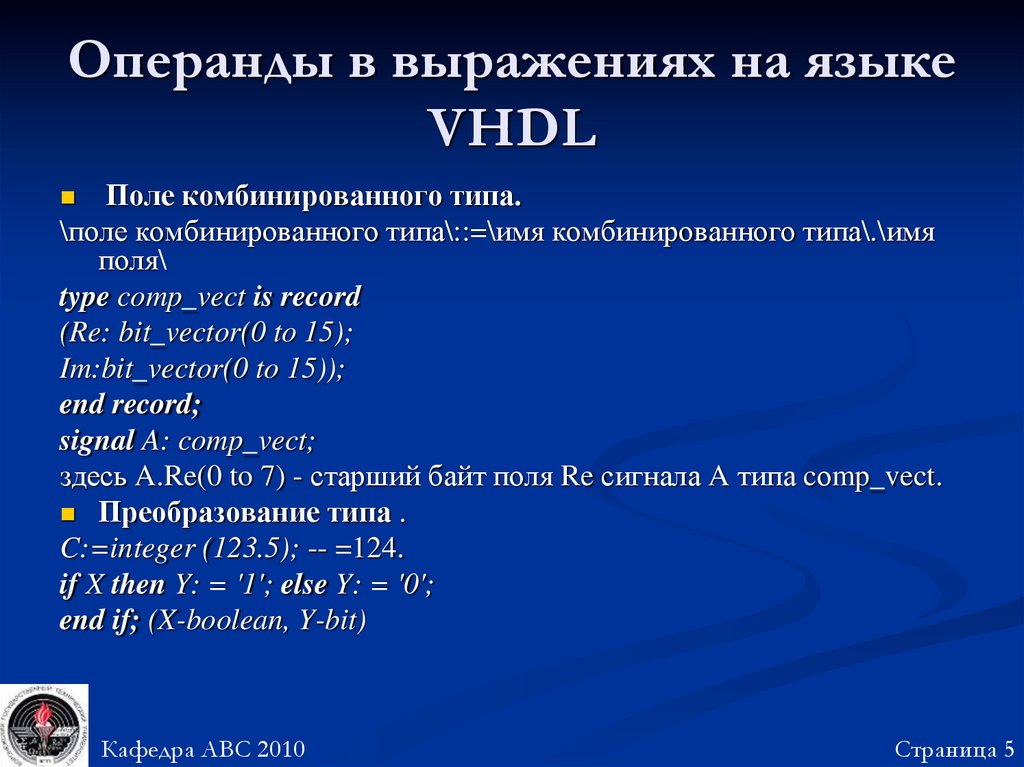

23. Операнды в выражениях на языке VHDL

Поле комбинированного типа.\поле комбинированного типа\::=\имя комбинированного типа\.\имя

поля\

type comp_vect is record

(Re: bit_vector(0 to 15);

Im:bit_vector(0 to 15));

end record;

signal A: comp_vect;

здесь A.Re(0 to 7) - старший байт поля Re сигнала A типа cоmp_vect.

Преобразование типа .

C:=integer (123.5); -- =124.

if X then Y: = '1'; else Y: = '0';

end if; (X-boolean, Y-bit)

Кафедра АВС 2010

Страница 5

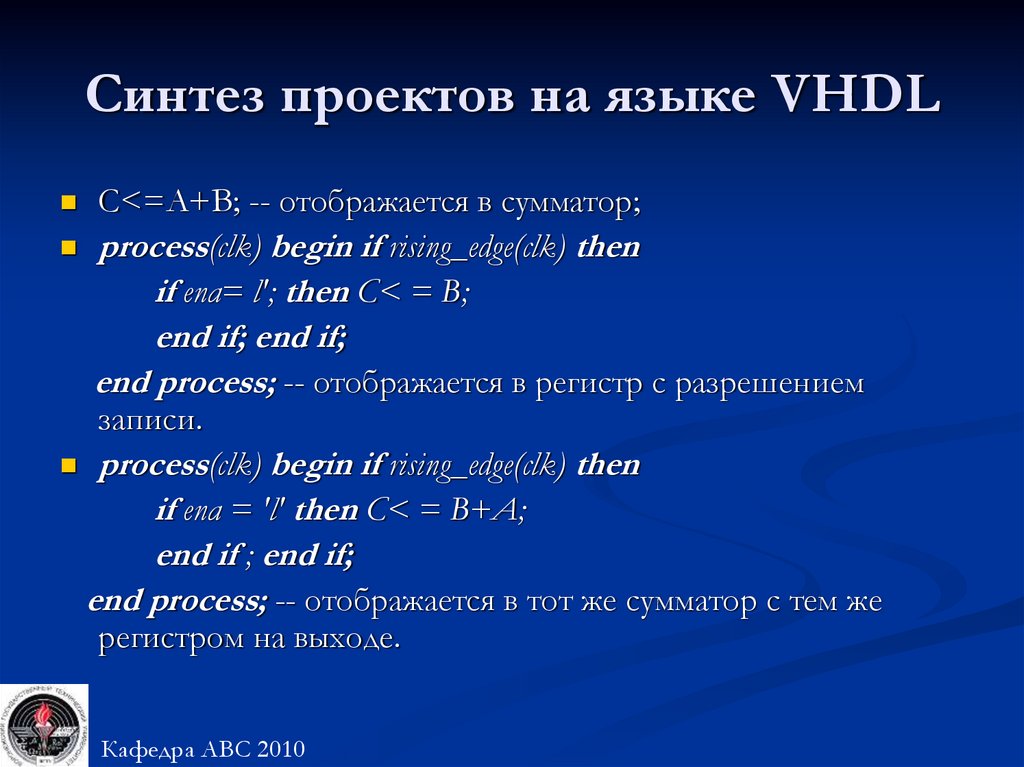

24. Синтез проектов на языке VHDL

С<=А+В; -- отображается в сумматор;process(clk) begin if rising_edge(clk) then

if ena= l'; then С< = В;

end if; end if;

end process; -- отображается в регистр с разрешением

записи.

process(clk) begin if rising_edge(clk) then

if ena = 'l' then С< = В+А;

end if ; end if;

end process; -- отображается в тот же сумматор с тем же

регистром на выходе.

Кафедра АВС 2010

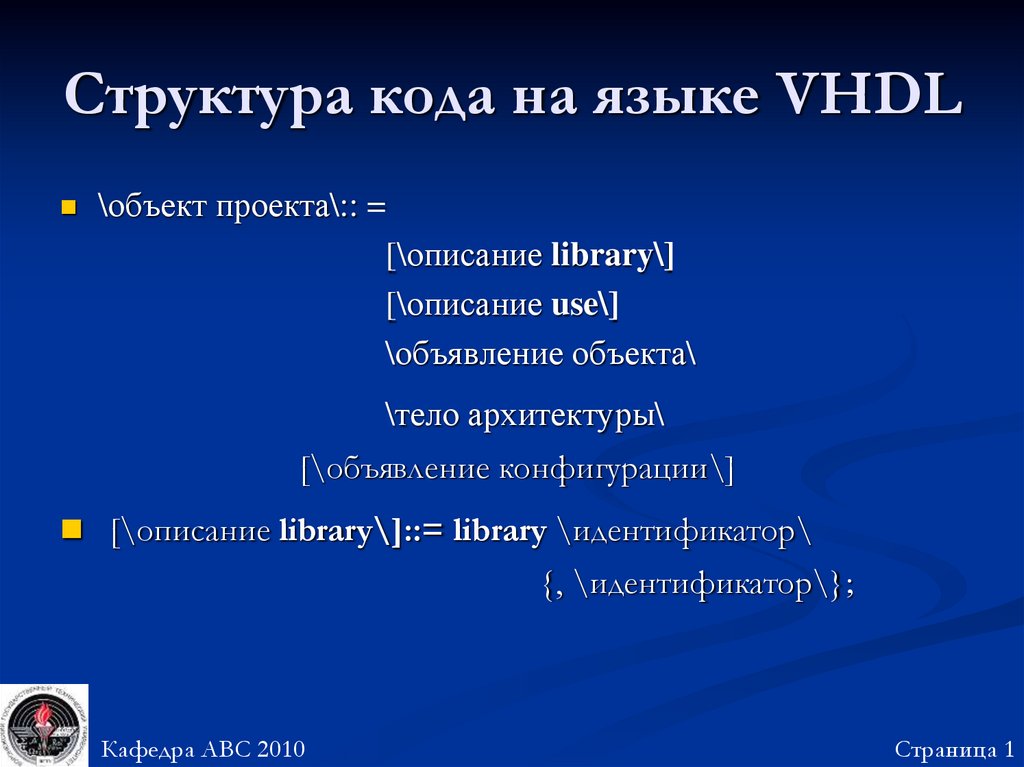

25. Структура кода на языке VHDL

\объект проекта\:: =[\описание library\]

[\описание use\]

\объявление объекта\

\тело архитектуры\

[\объявление конфигурации\]

[\описание library\]::= library \идентификатор\

{, \идентификатор\};

Кафедра АВС 2010

Страница 1

26. Структура кода на языке VHDL

Описание use.\описание use\::= use \селективное имя\

{, \селективное имя\ };

\селективное имя\::= \имя1\. \имя2\

\имя2\::= \идентификатор\ | \символьный литерал\ |all

Примеры :

use IEEE.std_logic_arith."-", IEEE.std_logic_arith."+" ;

use IEEE.std_logic_arith.all;

Кафедра АВС 2010

Страница 2

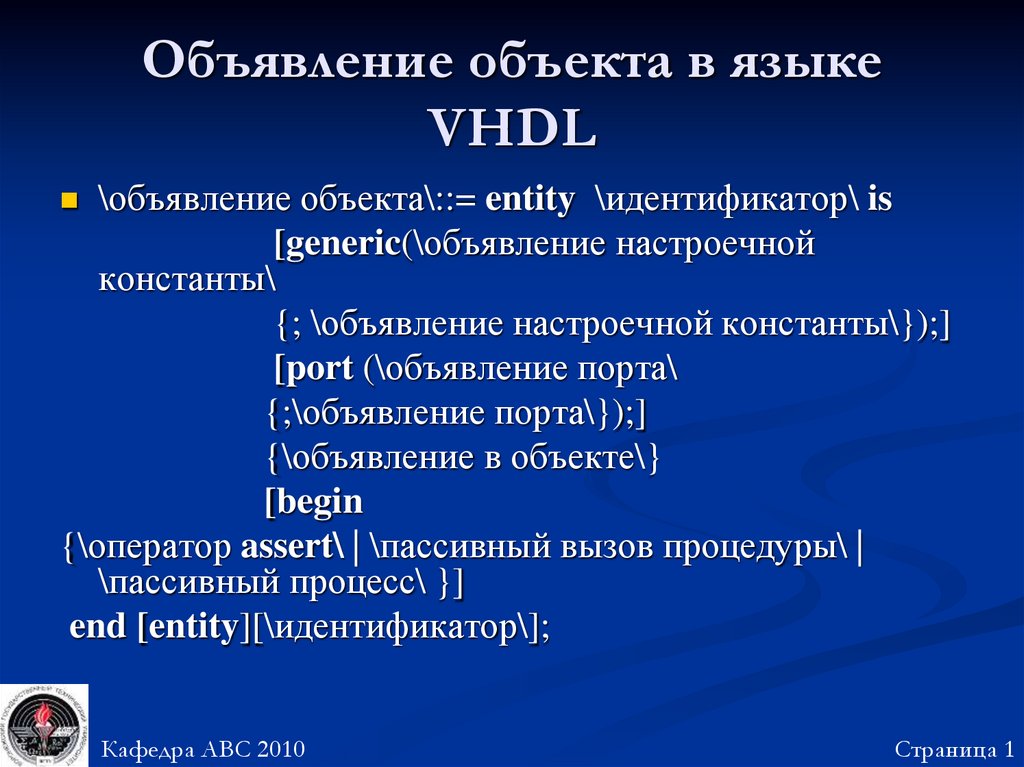

27. Объявление объекта в языке VHDL

\объявление объекта\::= entity \идентификатор\ is[generic(\объявление настроечной

константы\

{; \объявление настроечной константы\});]

[port (\объявление порта\

{;\объявление порта\});]

{\объявление в объекте\}

[begin

{\оператор assert\ | \пассивный вызов процедуры\ |

\пассивный процесс\ }]

end [entity][\идентификатор\];

Кафедра АВС 2010

Страница 1

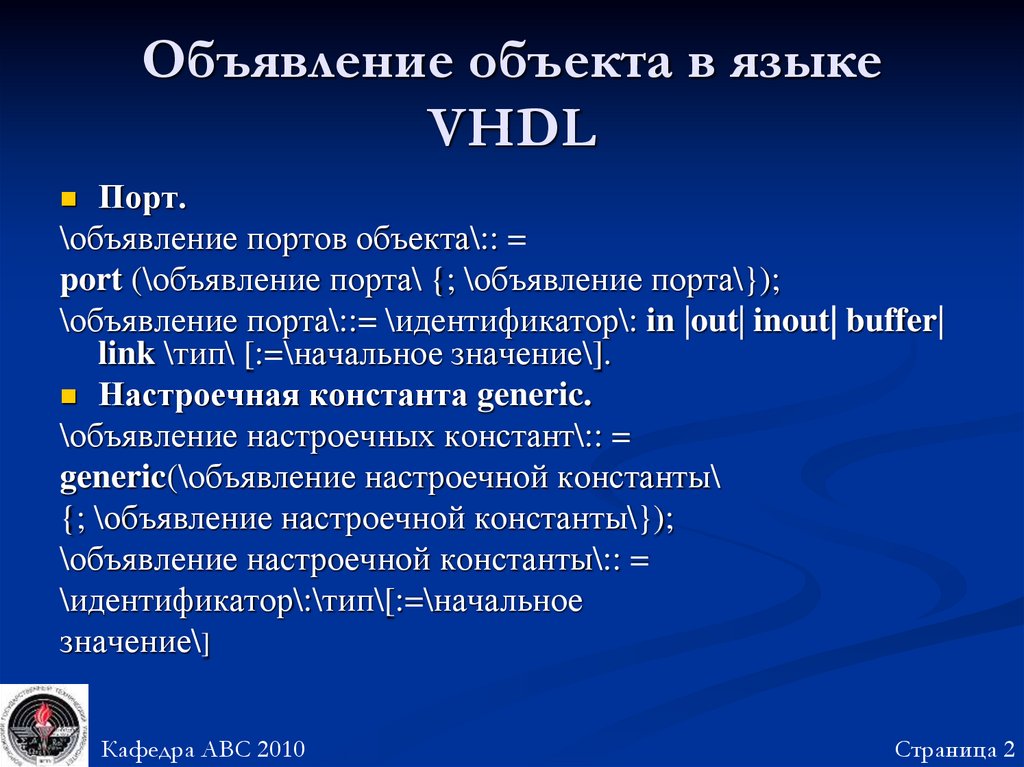

28. Объявление объекта в языке VHDL

Порт.\объявление портов объекта\:: =

port (\объявление порта\ {; \объявление порта\});

\объявление порта\::= \идентификатор\: in |out| inout| buffer|

link \тип\ [:=\начальное значение\].

Настроечная константа generic.

\объявление настроечных констант\:: =

generic(\объявление настроечной константы\

{; \объявление настроечной константы\});

\объявление настроечной константы\:: =

\идентификатор\:\тип\[:=\начальное

значение\]

Кафедра АВС 2010

Страница 2

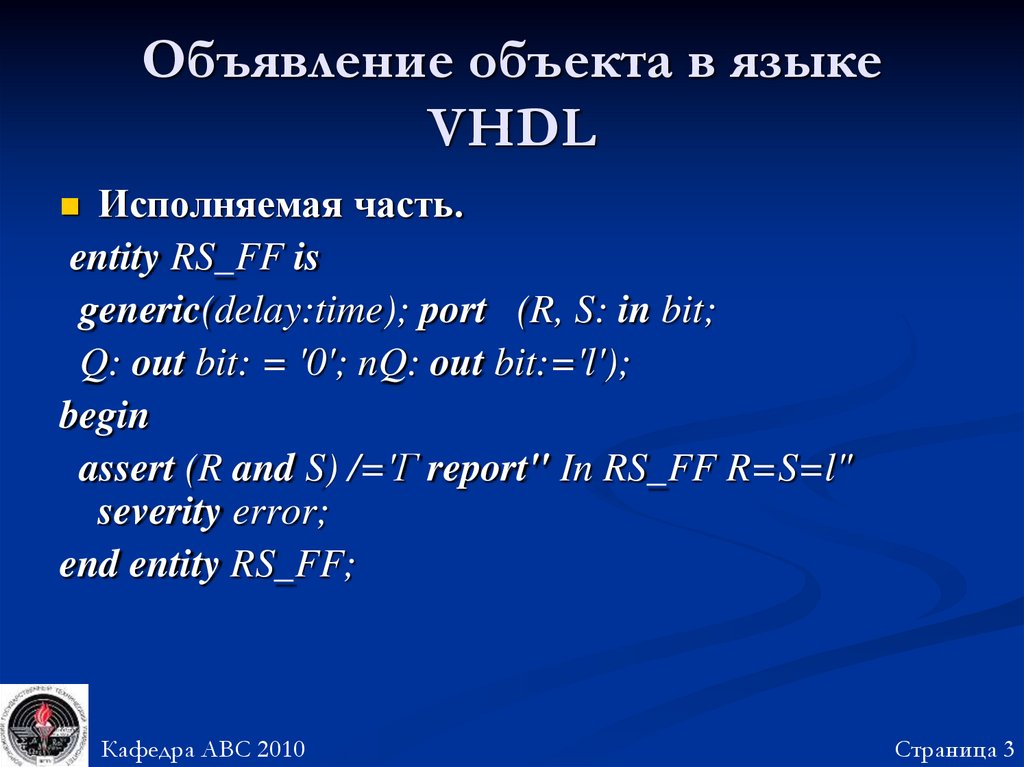

29. Объявление объекта в языке VHDL

Исполняемая часть.entity RS_FF is

generic(delay:time); port (R, S: in bit;

Q: out bit: = '0'; nQ: out bit:='l');

begin

assert (R and S) /='Г report" In RS_FF R=S=l"

severity error;

end entity RS_FF;

Кафедра АВС 2010

Страница 3

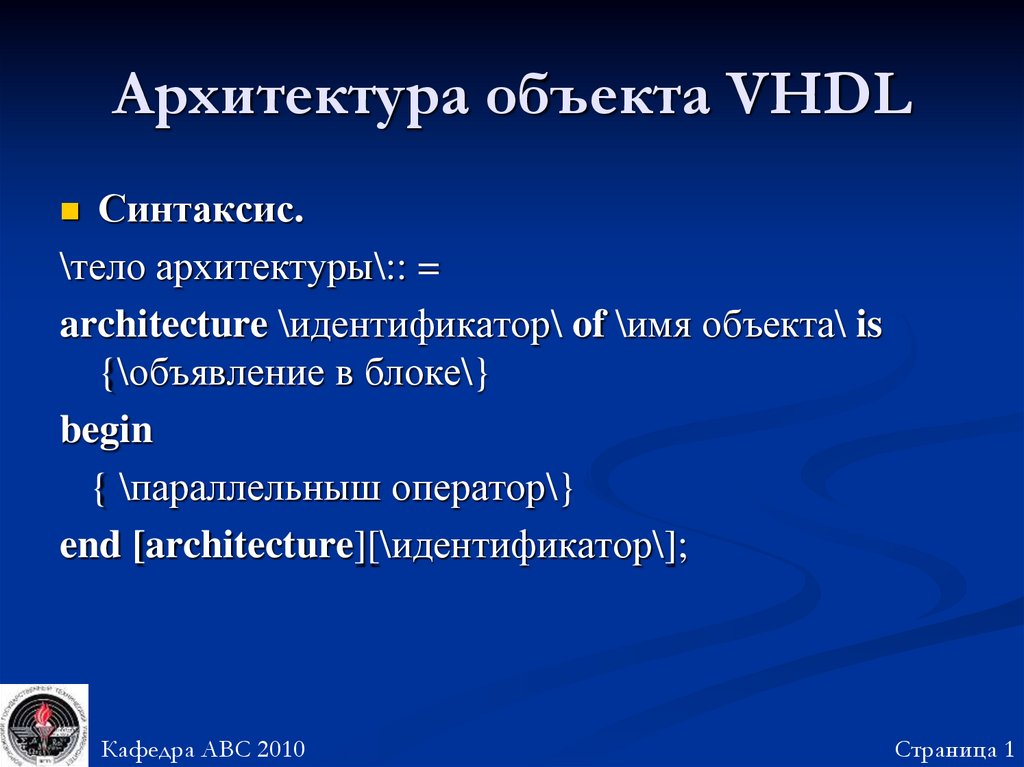

30. Архитектура объекта VHDL

Синтаксис.\тело архитектуры\:: =

architecture \идентификатор\ of \имя объекта\ is

{\объявление в блоке\}

begin

{ \параллельныш оператор\}

end [architecture][\идентификатор\];

Кафедра АВС 2010

Страница 1

31. Архитектура объекта VHDL

entity RS_FF is —объявление объектаgeneric(delay:time);

port(R, S: in bit;

Q: out bit: = '0';

nQ: out bit:='l');

begin

assert (R and S) /='Г report" In RS_FF R=S=l" severity error;

end entity RS_FF;

architecture BEHAV of RS_FF is —описание архитектуры объекта

begin

process(S,R)

variable qi: bit;

begin

if S=l' then

qi: = 'l* ;

elsif R= l' then

qi: = '0';

end if;

Q<=qi after delay;

nQ< = not qi after delay;

end process;

end architecture BEHAV;

Кафедра АВС 2010

Страница 2

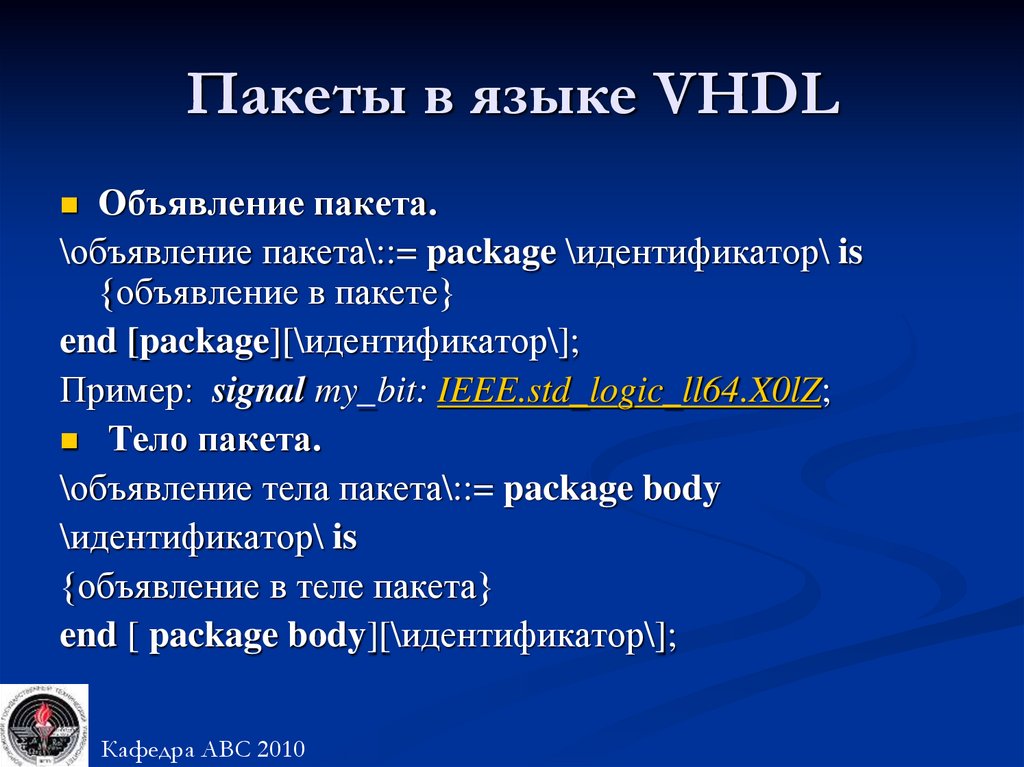

32. Пакеты в языке VHDL

Объявление пакета.\объявление пакета\::= package \идентификатор\ is

{объявление в пакете}

end [package][\идентификатор\];

Пример: signal my_bit: IEEE.std_logic_ll64.X0lZ;

Тело пакета.

\объявление тела пакета\::= package body

\идентификатор\ is

{объявление в теле пакета}

end [ package body][\идентификатор\];

Кафедра АВС 2010

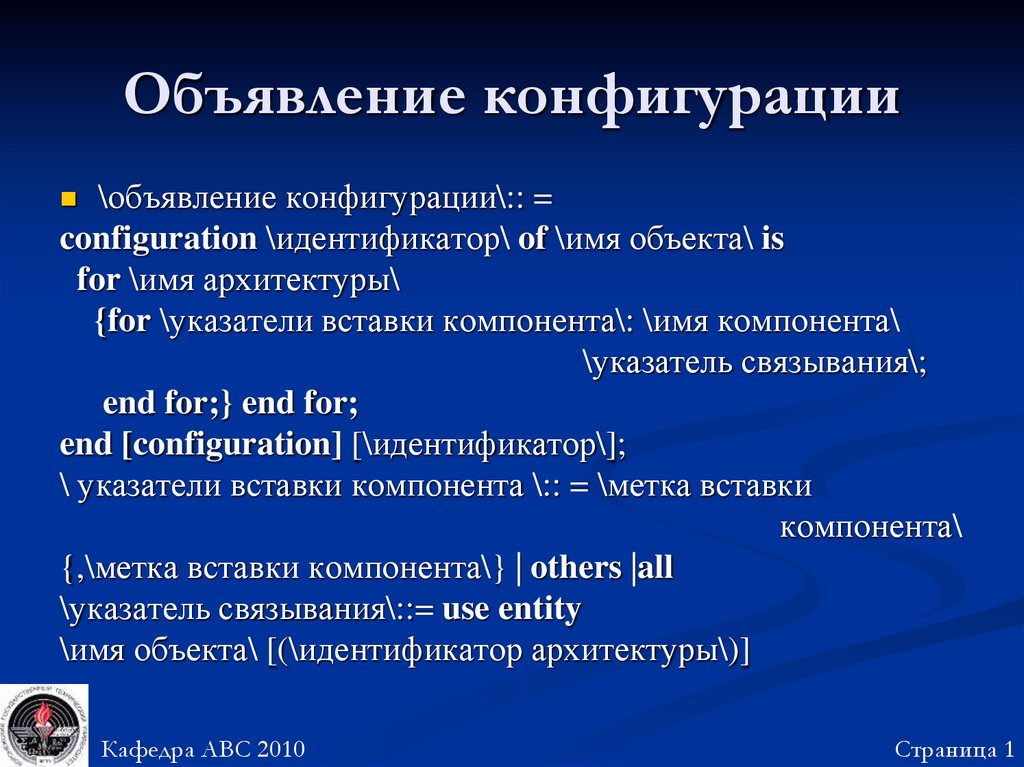

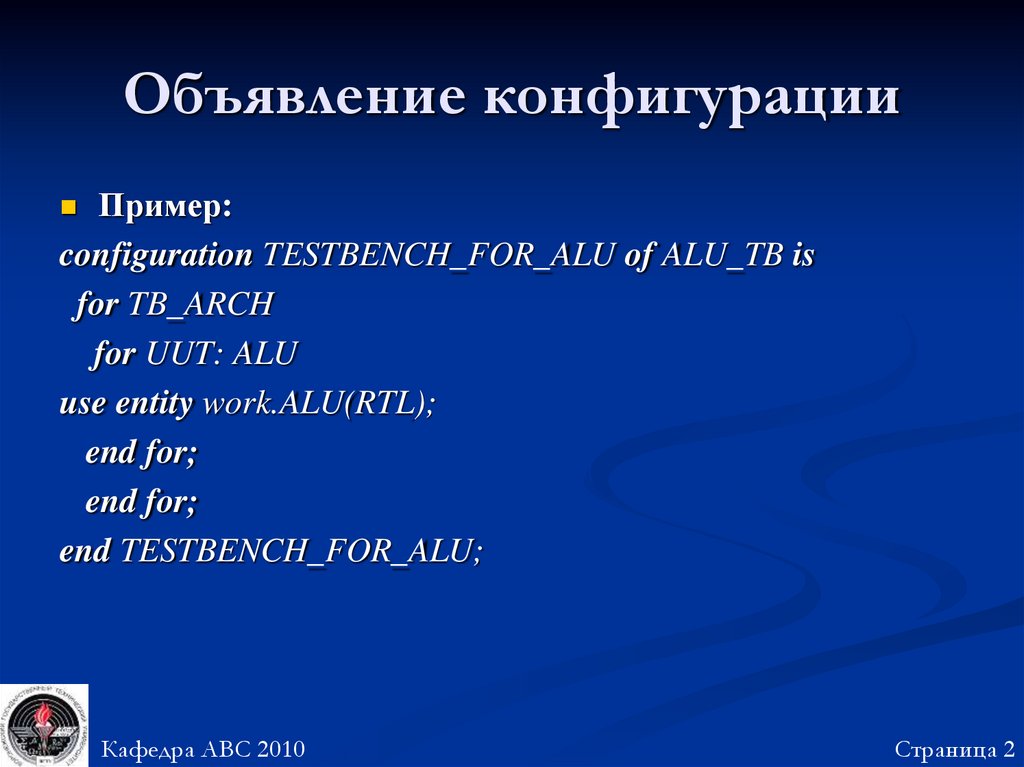

33. Объявление конфигурации

\объявление конфигурации\:: =configuration \идентификатор\ of \имя объекта\ is

for \имя архитектуры\

{for \указатели вставки компонента\: \имя компонента\

\указатель связывания\;

end for;} end for;

end [configuration] [\идентификатор\];

\ указатели вставки компонента \:: = \метка вставки

компонента\

{,\метка вставки компонента\} | others |all

\указатель связывания\::= use entity

\имя объекта\ [(\идентификатор архитектуры\)]

Кафедра АВС 2010

Страница 1

34. Объявление конфигурации

Пример:configuration TESTBENCH_FOR_ALU of ALU_TB is

for TB_ARCH

for UUT: ALU

use entity work.ALU(RTL);

end for;

end for;

end TESTBENCH_FOR_ALU;

Кафедра АВС 2010

Страница 2

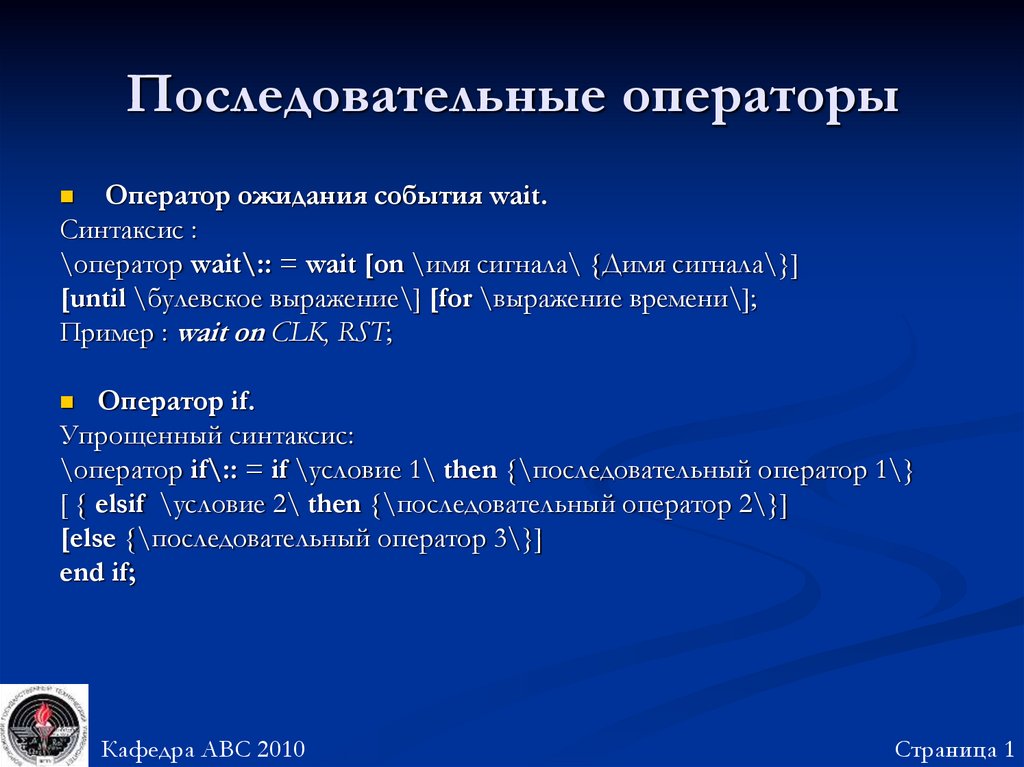

35. Последовательные операторы

Оператор ожидания события wait.Синтаксис :

\оператор wait\:: = wait [on \имя сигнала\ {Димя сигнала\}]

[until \булевское выражение\] [for \выражение времени\];

Пример : wait on CLK, RST;

Оператор if.

Упрощенный синтаксис:

\оператор if\:: = if \условие 1\ then {\последовательный оператор 1\}

[ { elsif \условие 2\ then {\последовательный оператор 2\}]

[else {\последовательный оператор 3\}]

end if;

Кафедра АВС 2010

Страница 1

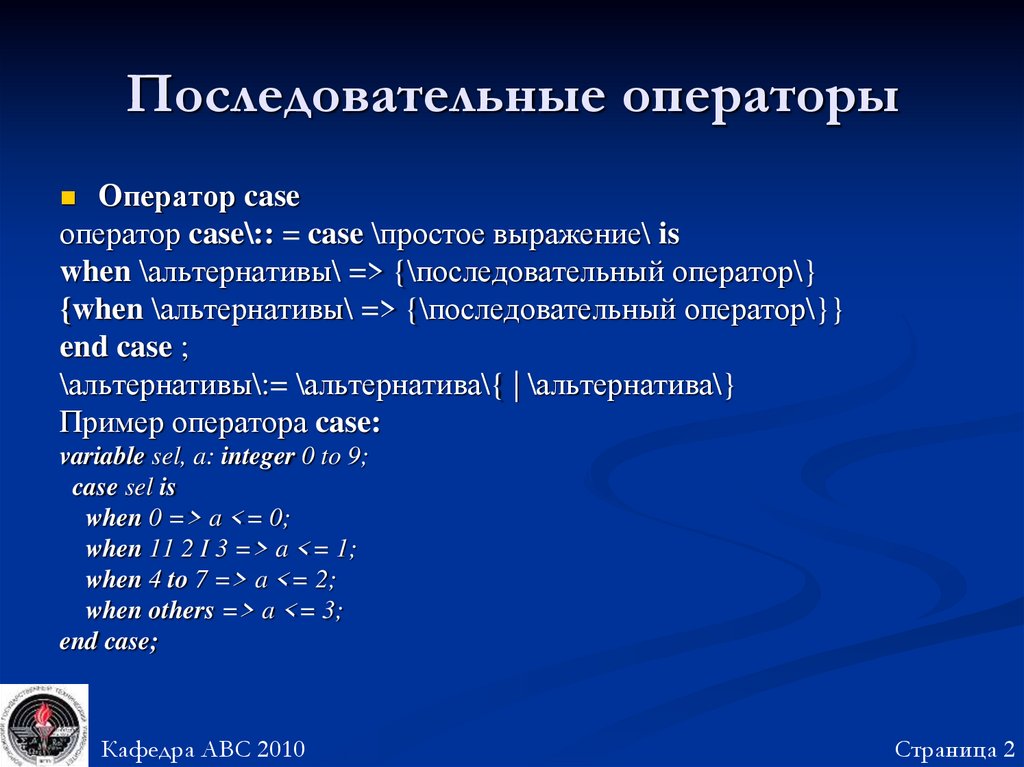

36. Последовательные операторы

Оператор caseоператор case\:: = case \простое выражение\ is

when \альтернативы\ => {\последовательный оператор\}

{when \альтернативы\ => {\последовательный оператор\}}

end case ;

\альтернативы\:= \альтернатива\{ | \альтернатива\}

Пример оператора case:

variable sel, a: integer 0 to 9;

case sel is

when 0 => a <= 0;

when 11 2 I 3 => a <= 1;

when 4 to 7 => a <= 2;

when others => a <= 3;

end case;

Кафедра АВС 2010

Страница 2

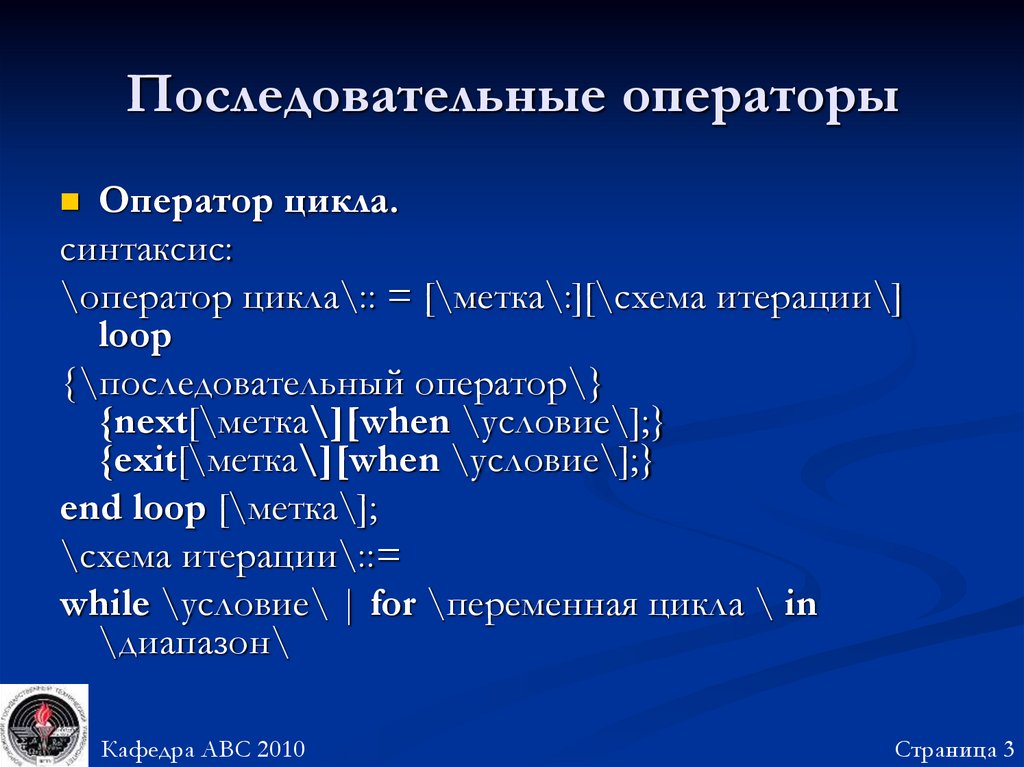

37. Последовательные операторы

Оператор цикла.синтаксис:

\оператор цикла\:: = [\метка\:][\схема итерации\]

loop

{\последовательный оператор\}

{next[\метка\][when \условие\];}

{exit[\метка\][when \условие\];}

end loop [\метка\];

\схема итерации\::=

while \условие\ | for \переменная цикла \ in

\диапазон\

Кафедра АВС 2010

Страница 3

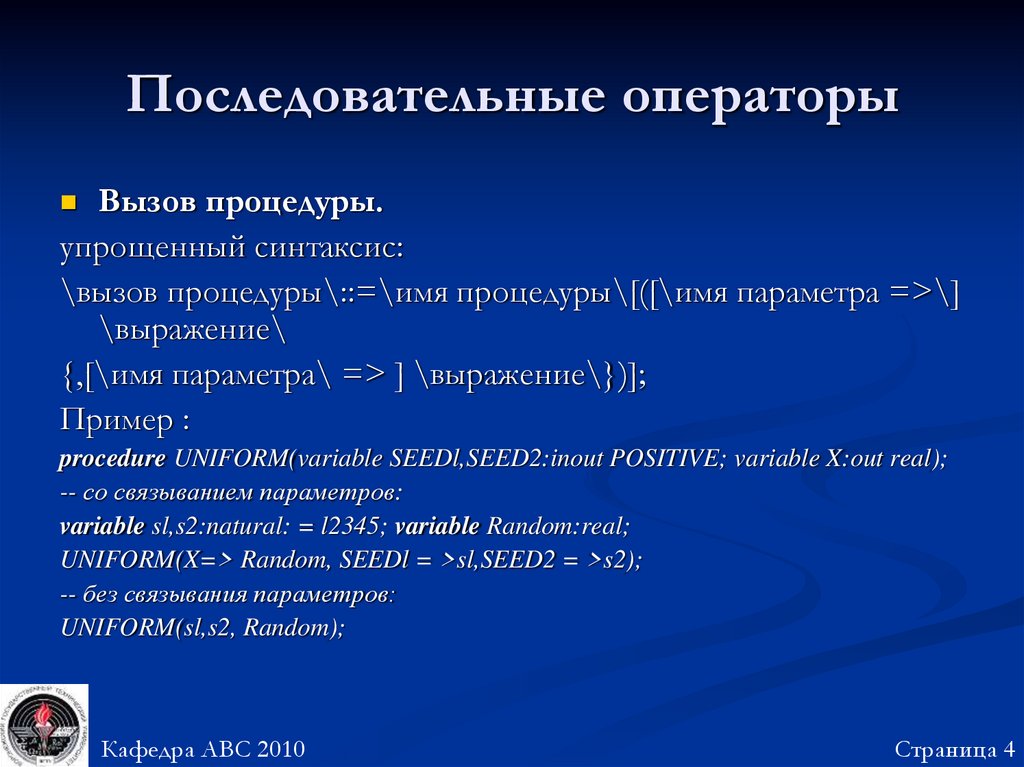

38. Последовательные операторы

Вызов процедуры.упрощенный синтаксис:

\вызов процедуры\::=\имя процедуры\[([\имя параметра =>\]

\выражение\

{,[\имя параметра\ => ] \выражение\})];

Пример :

procedure UNIFORM(variable SEEDl,SEED2:inout POSITIVE; variable X:out real);

-- со связыванием параметров:

variable sl,s2:natural: = l2345; variable Random:real;

UNIFORM(X=> Random, SEEDl = >sl,SEED2 = >s2);

-- без связывания параметров:

UNIFORM(sl,s2, Random);

Кафедра АВС 2010

Страница 4

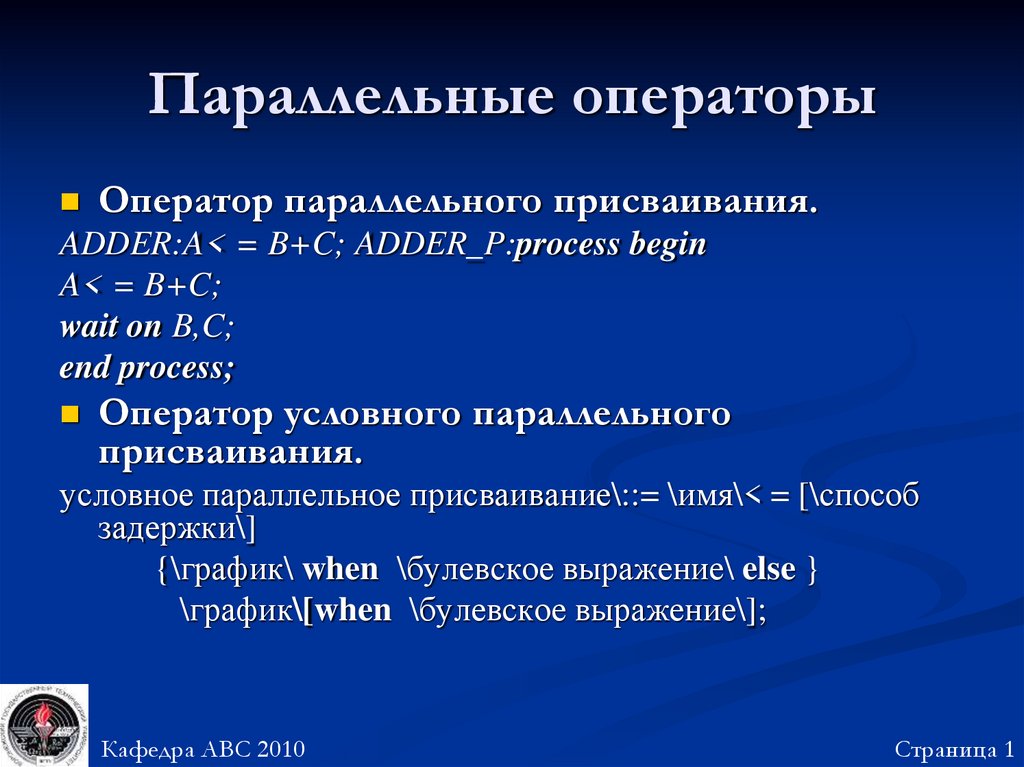

39. Параллельные операторы

Оператор параллельного присваивания.ADDER:A< = B+C; ADDER_P:process begin

A< = B+C;

wait on B,C;

end process;

Оператор условного параллельного

присваивания.

условное параллельное присваивание\::= \имя\< = [\способ

задержки\]

{\график\ when \булевское выражение\ else }

\график\[when \булевское выражение\];

Кафедра АВС 2010

Страница 1

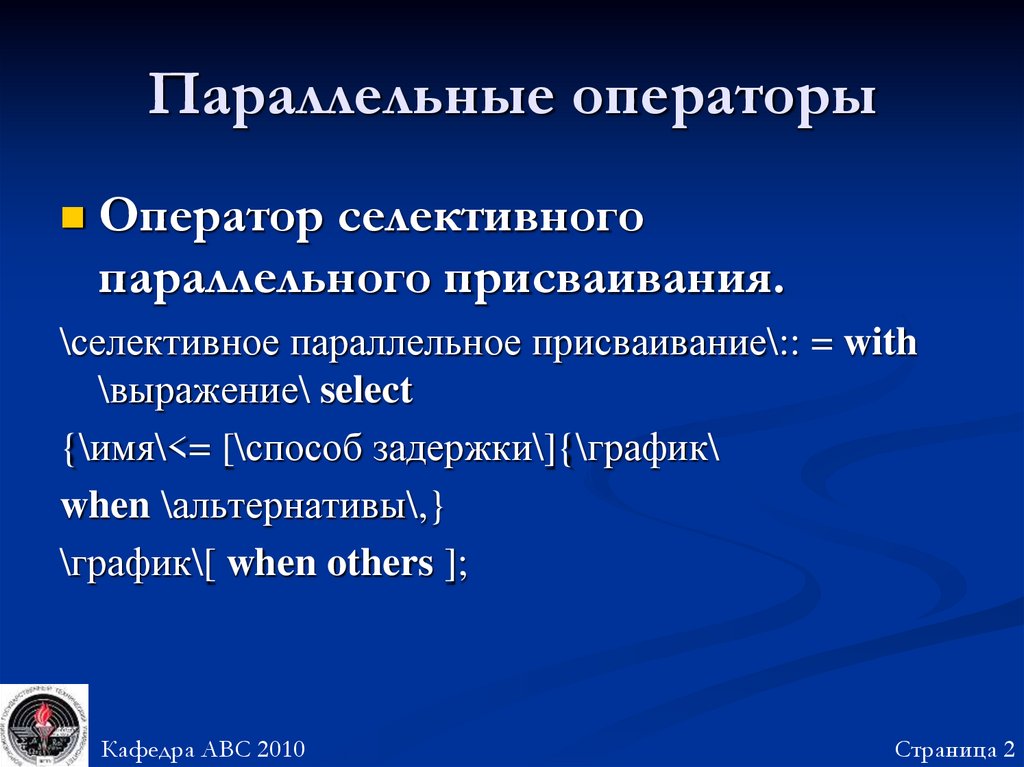

40. Параллельные операторы

Оператор селективногопараллельного присваивания.

\селективное параллельное присваивание\:: = with

\выражение\ select

{\имя\<= [\способ задержки\]{\график\

when \альтернативы\,}

\график\[ when others ];

Кафедра АВС 2010

Страница 2

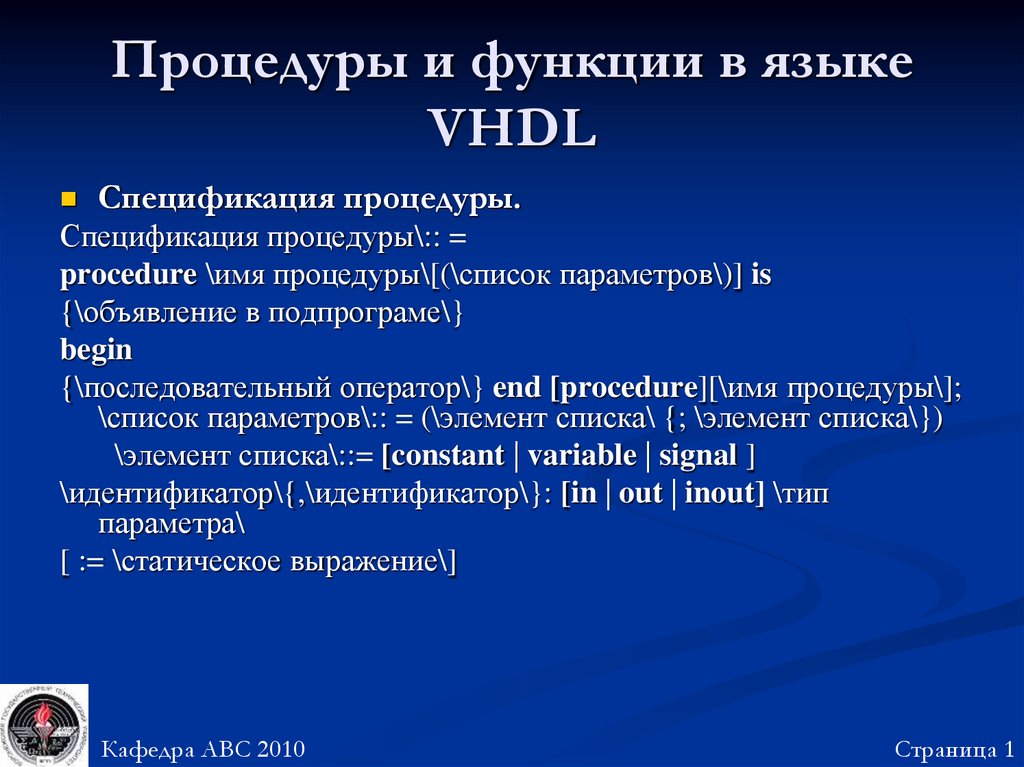

41. Процедуры и функции в языке VHDL

Спецификация процедуры.Спецификация процедуры\:: =

procedure \имя процедуры\[(\список параметров\)] is

{\объявление в подпрограме\}

begin

{\последовательный оператор\} end [procedure][\имя процедуры\];

\список параметров\:: = (\элемент списка\ {; \элемент списка\})

\элемент списка\::= [constant | variable | signal ]

\идентификатор\{,\идентификатор\}: [in | out | inout] \тип

параметра\

[ := \статическое выражение\]

Кафедра АВС 2010

Страница 1

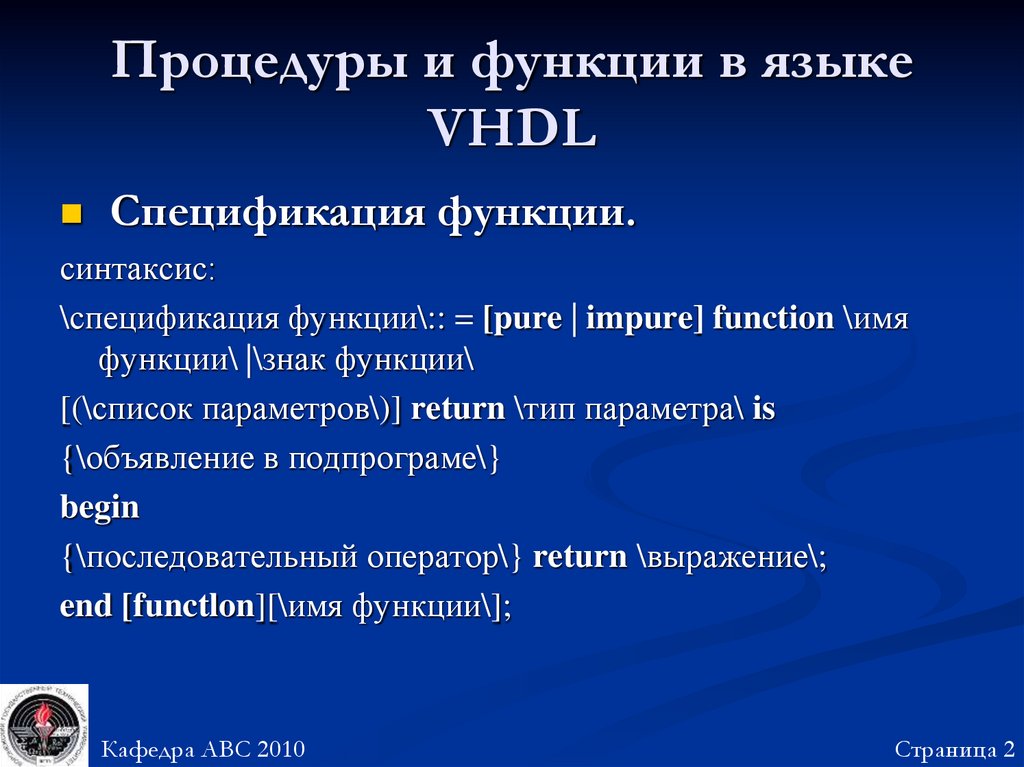

42. Процедуры и функции в языке VHDL

Спецификация функции.синтаксис:

\спецификация функции\:: = [pure | impure] function \имя

функции\ |\знак функции\

[(\список параметров\)] return \тип параметра\ is

{\объявление в подпрограме\}

begin

{\последовательный оператор\} return \выражение\;

end [functlon][\имя функции\];

Кафедра АВС 2010

Страница 2

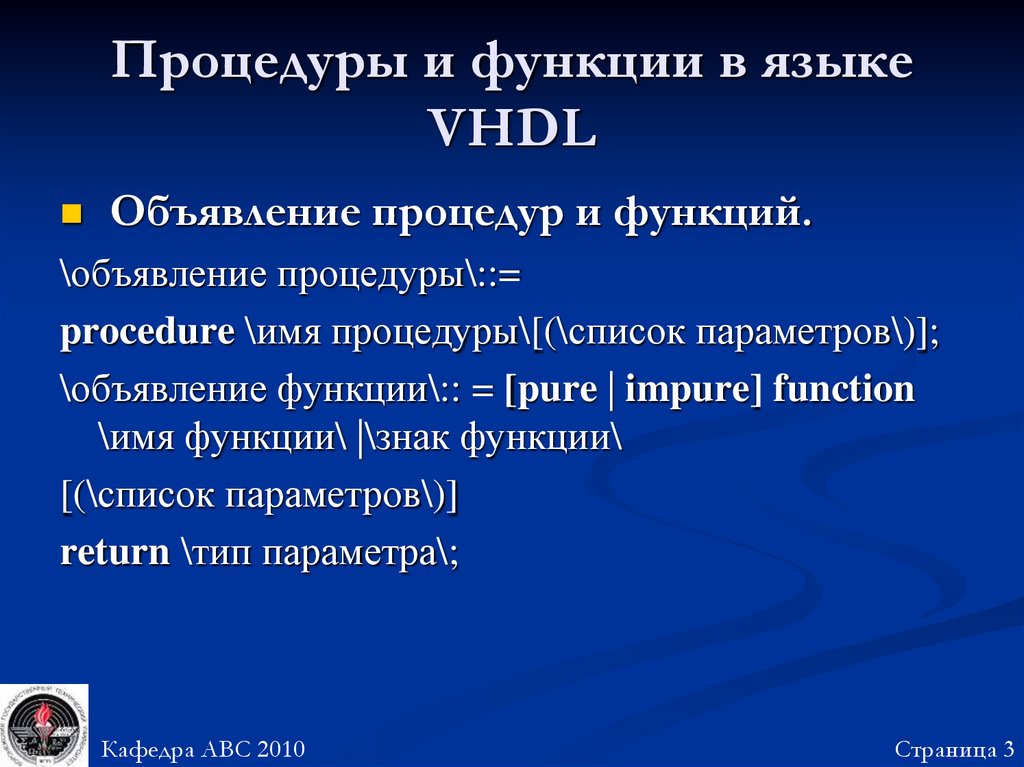

43. Процедуры и функции в языке VHDL

Объявление процедур и функций.\объявление процедуры\::=

procedure \имя процедуры\[(\список параметров\)];

\объявление функции\:: = [pure | impure] function

\имя функции\ |\знак функции\

[(\список параметров\)]

return \тип параметра\;

Кафедра АВС 2010

Страница 3

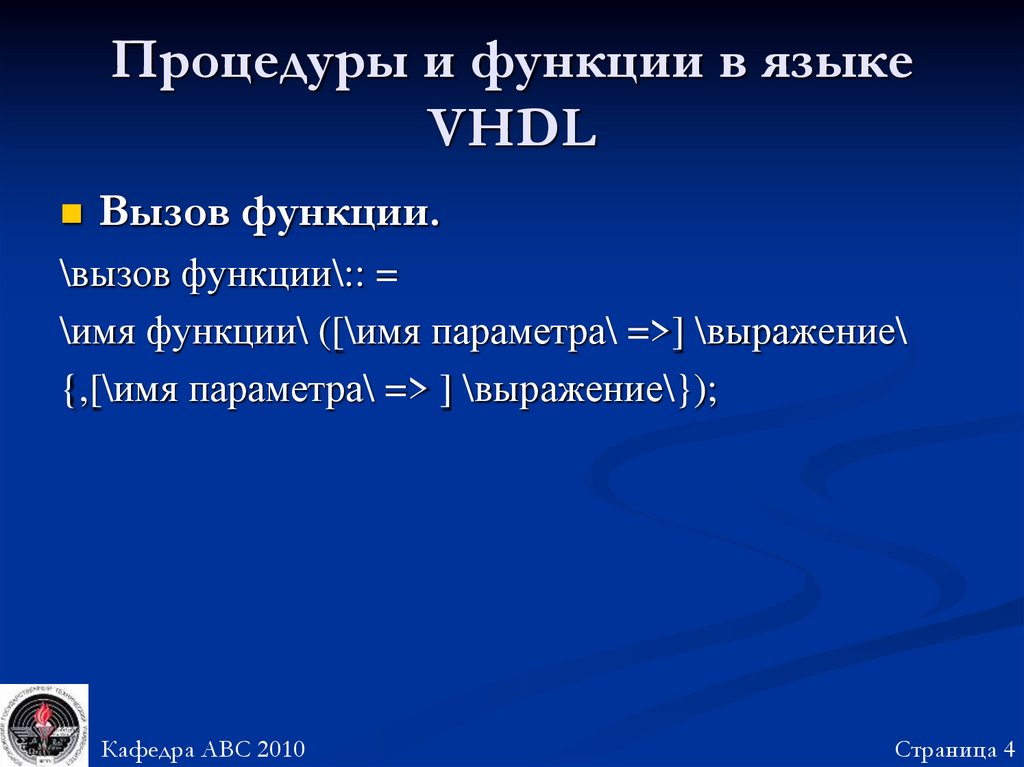

44. Процедуры и функции в языке VHDL

Вызов функции.\вызов функции\:: =

\имя функции\ ([\имя параметра\ =>] \выражение\

{,[\имя параметра\ => ] \выражение\});

Кафедра АВС 2010

Страница 4

45. Процедуры и функции в языке VHDL

Перезагрузка процедур и функций.function nand"(x1,x2:bit) return boolean is

begin

return (x1 and x2) ='1';

end;

---------------------------------variable a,b,c: bit;

if (a and b and c) then

--------------------------end if;

Кафедра АВС 2010

Страница 5

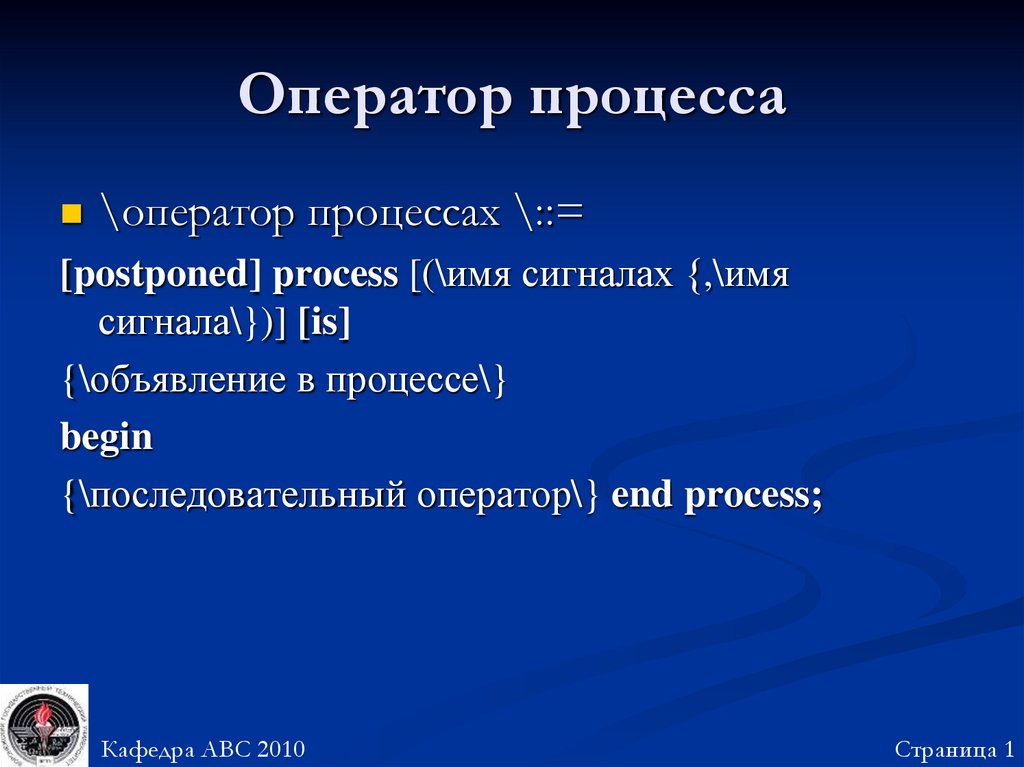

46. Оператор процесса

\оператор процессах \::=[postponed] process [(\имя сигналах {,\имя

сигнала\})] [is]

{\объявление в процессе\}

begin

{\последовательный оператор\} end process;

Кафедра АВС 2010

Страница 1

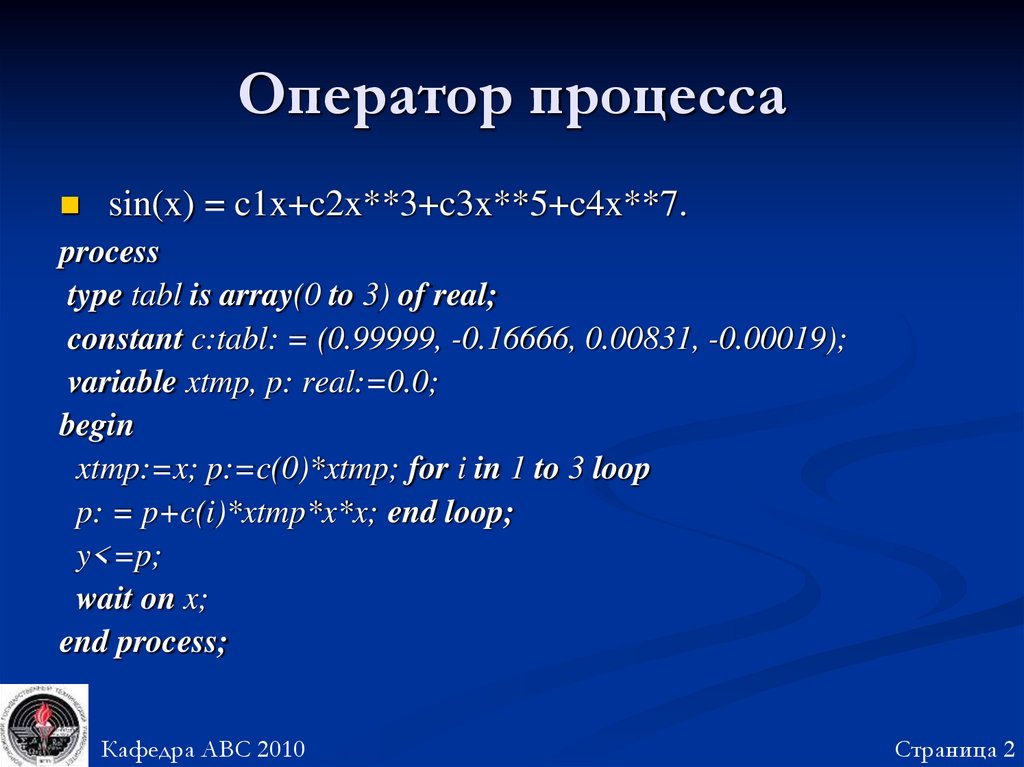

47. Оператор процесса

sin(x) = c1x+c2x**3+c3x**5+c4x**7.process

type tabl is array(0 to 3) of real;

constant c:tabl: = (0.99999, -0.16666, 0.00831, -0.00019);

variable xtmp, p: real:=0.0;

begin

xtmp:=x; p:=c(0)*xtmp; for i in 1 to 3 loop

p: = p+c(i)*xtmp*x*x; end loop;

y<=p;

wait on x;

end process;

Кафедра АВС 2010

Страница 2

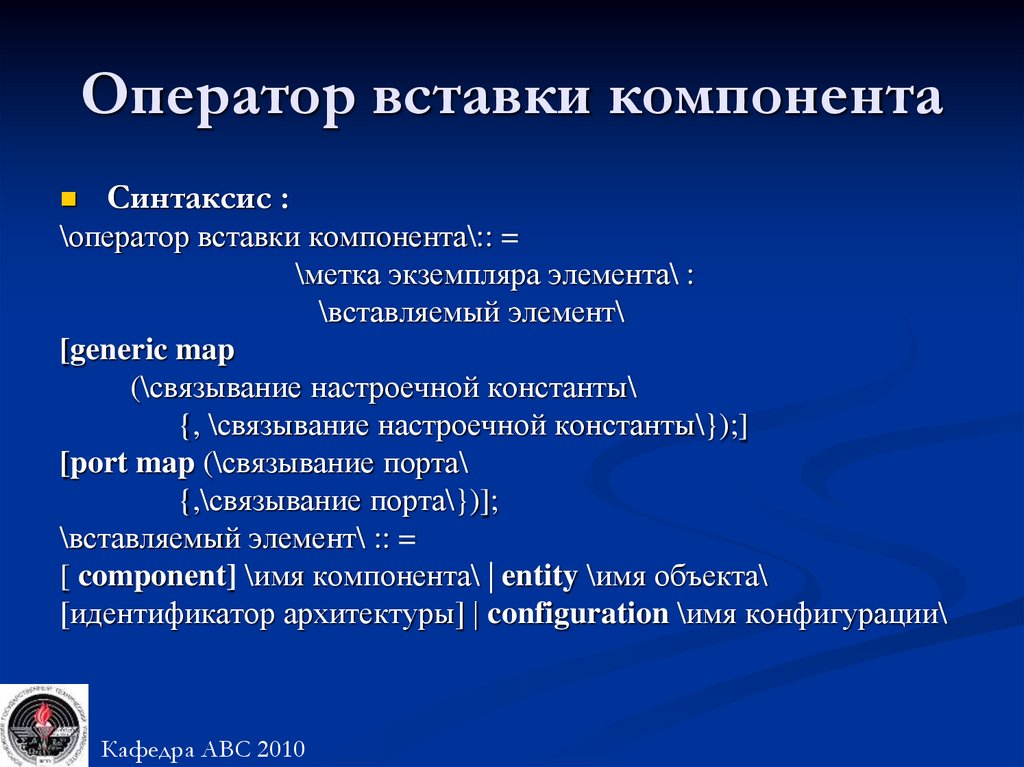

48. Оператор вставки компонента

Синтаксис :\оператор вставки компонента\:: =

\метка экземпляра элемента\ :

\вставляемый элемент\

[generic map

(\связывание настроечной константы\

{, \связывание настроечной константы\});]

[port map (\связывание порта\

{,\связывание порта\})];

\вставляемый элемент\ :: =

[ component] \имя компонента\ | entity \имя объекта\

[идентификатор архитектуры] | configuration \имя конфигурации\

Кафедра АВС 2010

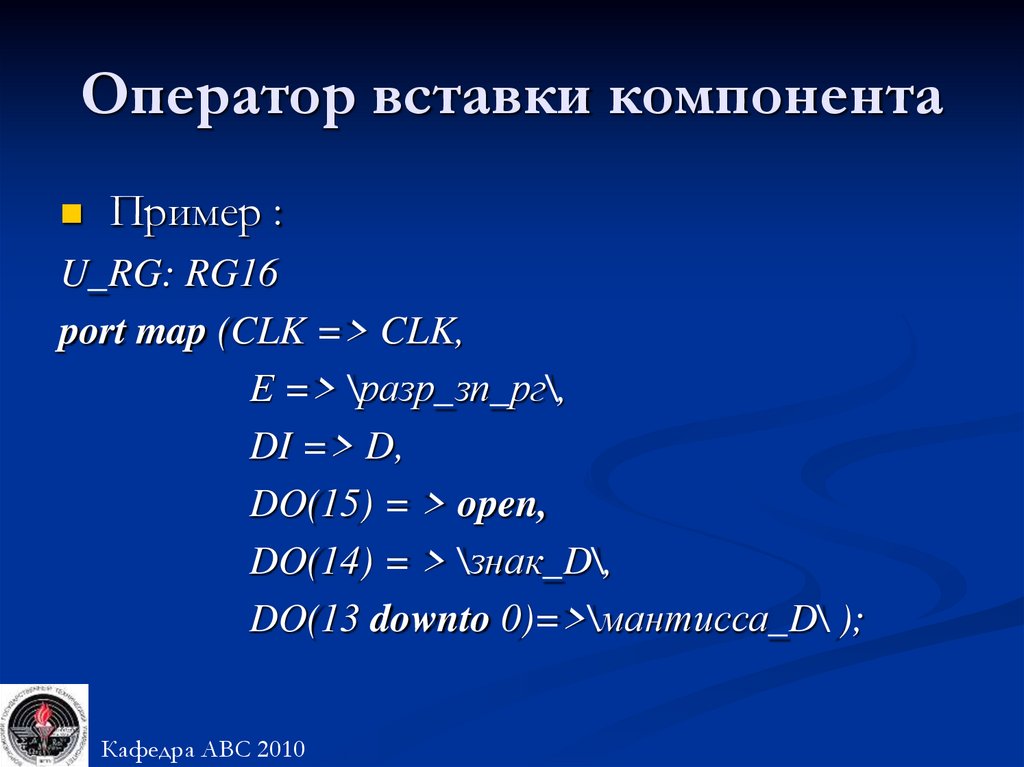

49. Оператор вставки компонента

Пример :U_RG: RG16

port map (CLK => CLK,

E => \разр_зп_рг\,

DI => D,

DO(15) = > open,

DO(14) = > \знак_D\,

DO(13 downto 0)=>\мантисса_D\ );

Кафедра АВС 2010

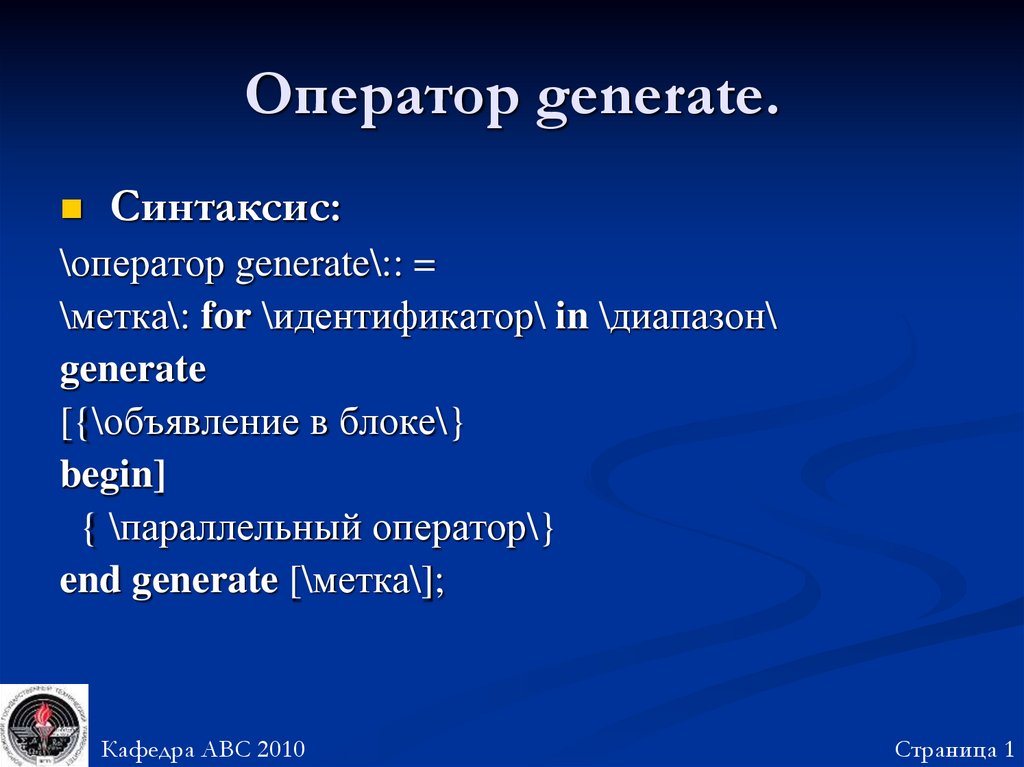

50. Оператор generate.

Синтаксис:\оператор generate\:: =

\метка\: for \идентификатор\ in \диапазон\

generate

[{\объявление в блоке\}

begin]

{ \параллельный оператор\}

end generate [\метка\];

Кафедра АВС 2010

Страница 1

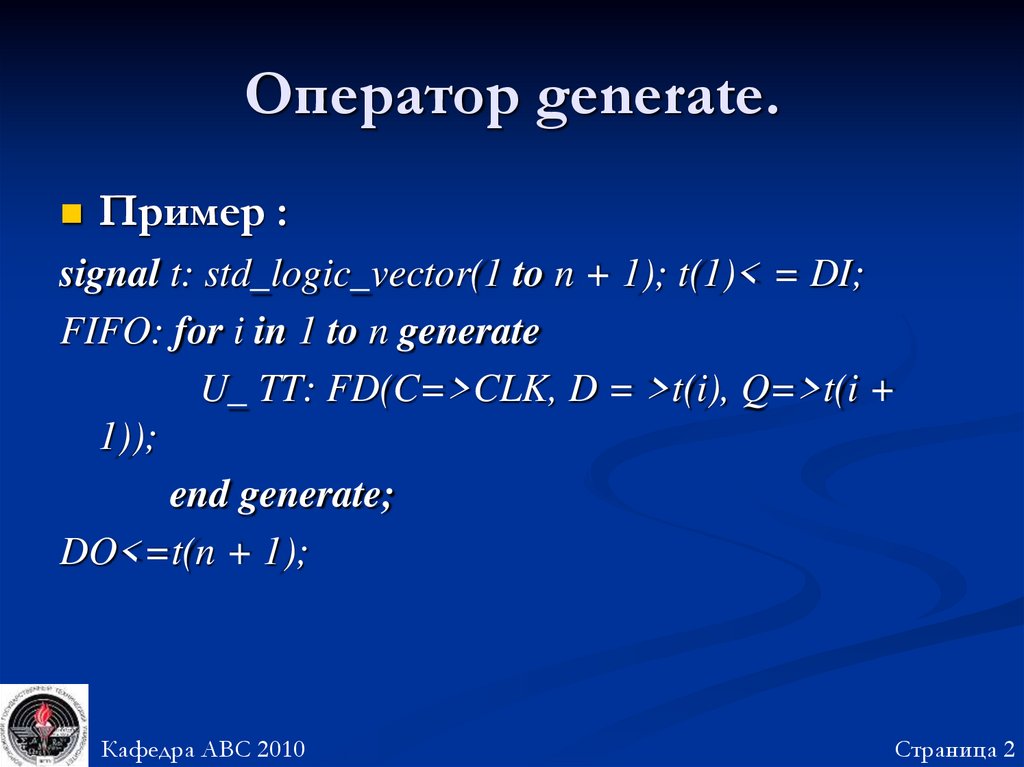

51. Оператор generate.

Пример :signal t: std_logic_vector(1 to n + 1); t(1)< = DI;

FIFO: for i in 1 to n generate

U_ TT: FD(C=>CLK, D = >t(i), Q=>t(i +

1));

end generate;

DO<=t(n + 1);

Кафедра АВС 2010

Страница 2

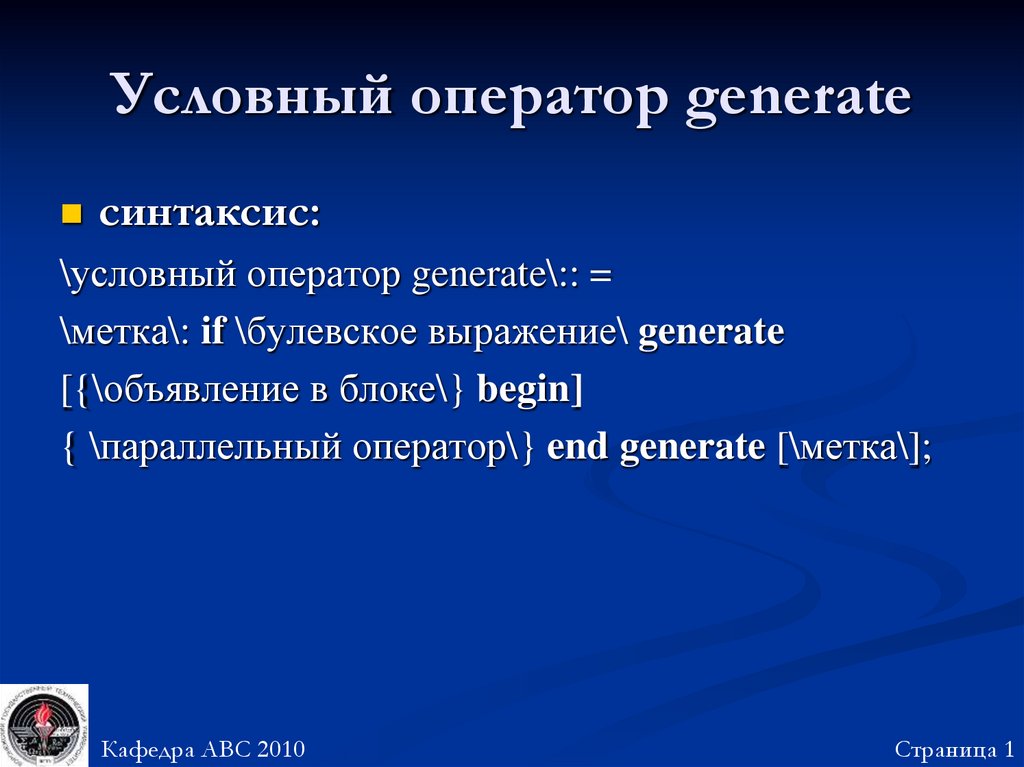

52. Условный оператор generate

синтаксис:\условный оператор generate\:: =

\метка\: if \булевское выражение\ generate

[{\объявление в блоке\} begin]

{ \параллельный оператор\} end generate [\метка\];

Кафедра АВС 2010

Страница 1

53. Условный оператор generate

Пример :RESn: if \подключить_РULLUР\=1 generate RESl:for

i in DATA_BUS'range generate

U_ RES: PULLUP(DATA_BUS(i));

end generate;

end generate;

Кафедра АВС 2010

Страница 2

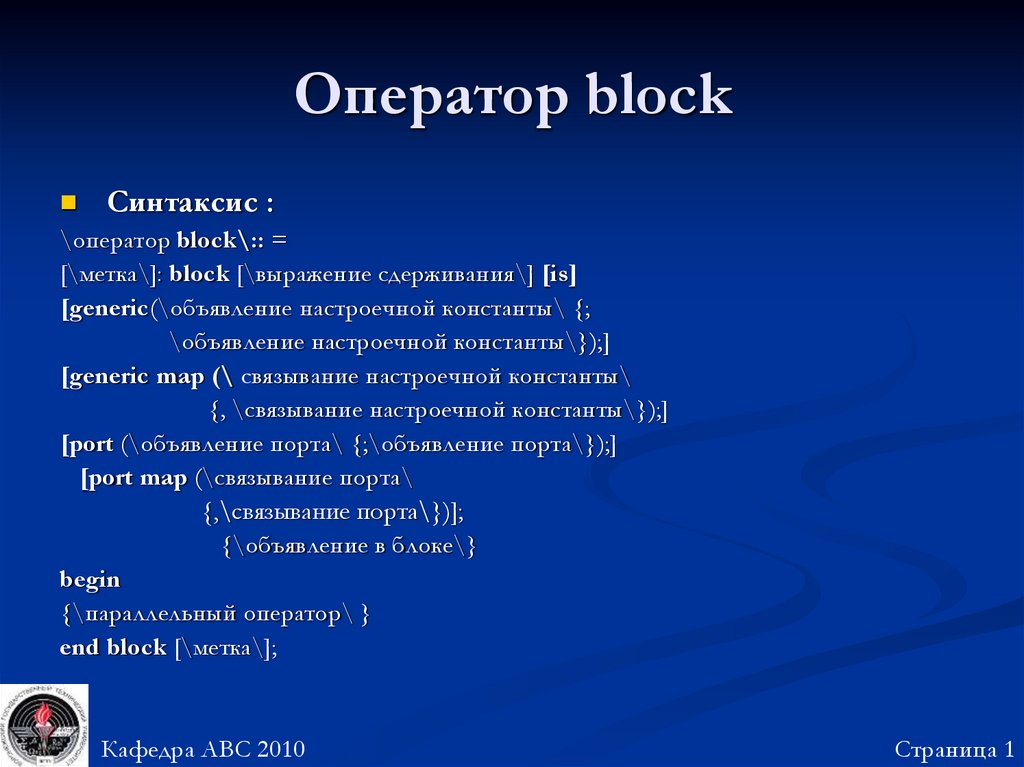

54. Оператор block

Синтаксис :\оператор block\:: =

[\метка\]: block [\выражение сдерживания\] [is]

[generic(\объявление настроечной константы\ {;

\объявление настроечной константы\});]

[generic map (\ связывание настроечной константы\

{, \связывание настроечной константы\});]

[port (\объявление порта\ {;\объявление порта\});]

[port map (\связывание порта\

{,\связывание порта\})];

{\объявление в блоке\}

begin

{\параллельный оператор\ }

end block [\метка\];

Кафедра АВС 2010

Страница 1

55. Оператор block

Пример:signal А,В,С: out integer bus :=0;

disconnect C:integer after 2 ns;

---------------------------В1: block (sel = 1) is begin

C <= guarded A;

end block В1;

В2: block (sel = 2) is begin

C <= guarded D;

end block В2;

Кафедра АВС 2010

Страница 2

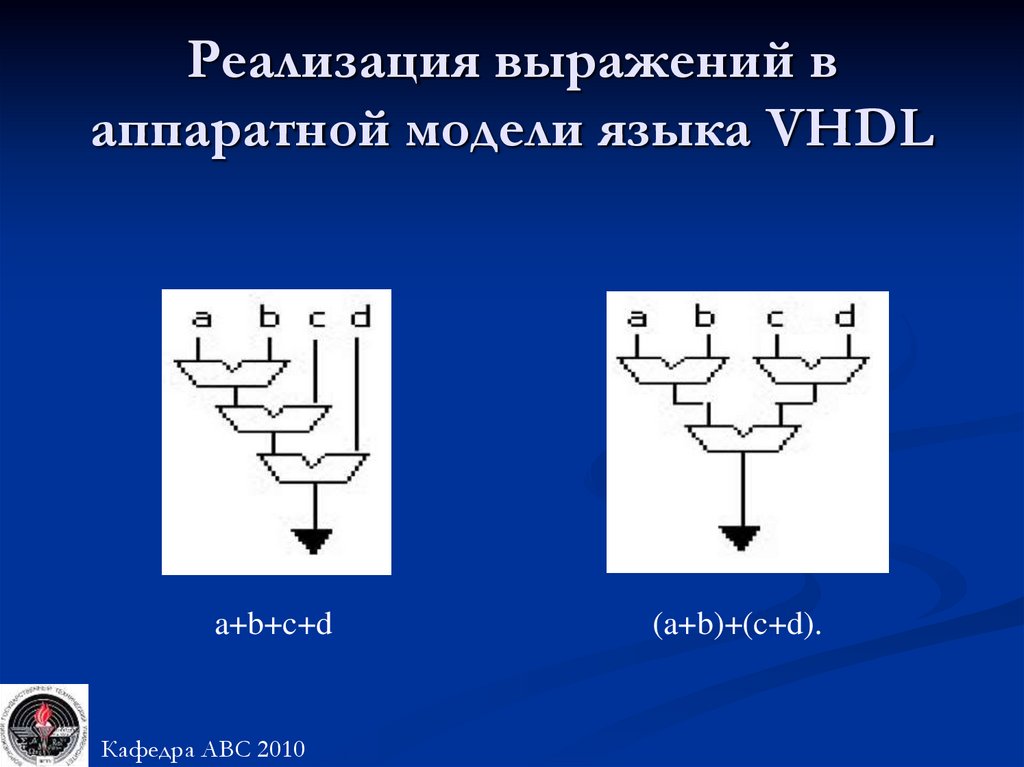

56. Реализация выражений в аппаратной модели языка VHDL

a+b+c+dКафедра АВС 2010

(a+b)+(c+d).

57. Мультиплексор 4х1

entity MUX isport (A, B, C, D: in BIT; CTRL: in BIT_VECTOR(0 to 1);

Z: out BIT);

end MUX;

architecture MUX_BEHAVIOR of MUX is

begin

PMUX: process (A, B, C, D, CTRL)

variable TEMP: BIT;

begin

case CTRL is

when "00" => TEMP := A:

when "01" => TEMP := B;

when "10" => TEMP := C;

when "11" => TEMP := D;

end case;

Z <= TEMP;

end process PMUX;

end MUX_BEHAVIOR;

Кафедра АВС 2010

A

0

B

1

C

2

D

3

CTRL[1…0]

V

MS

Z

Пример проекта

Страница 1

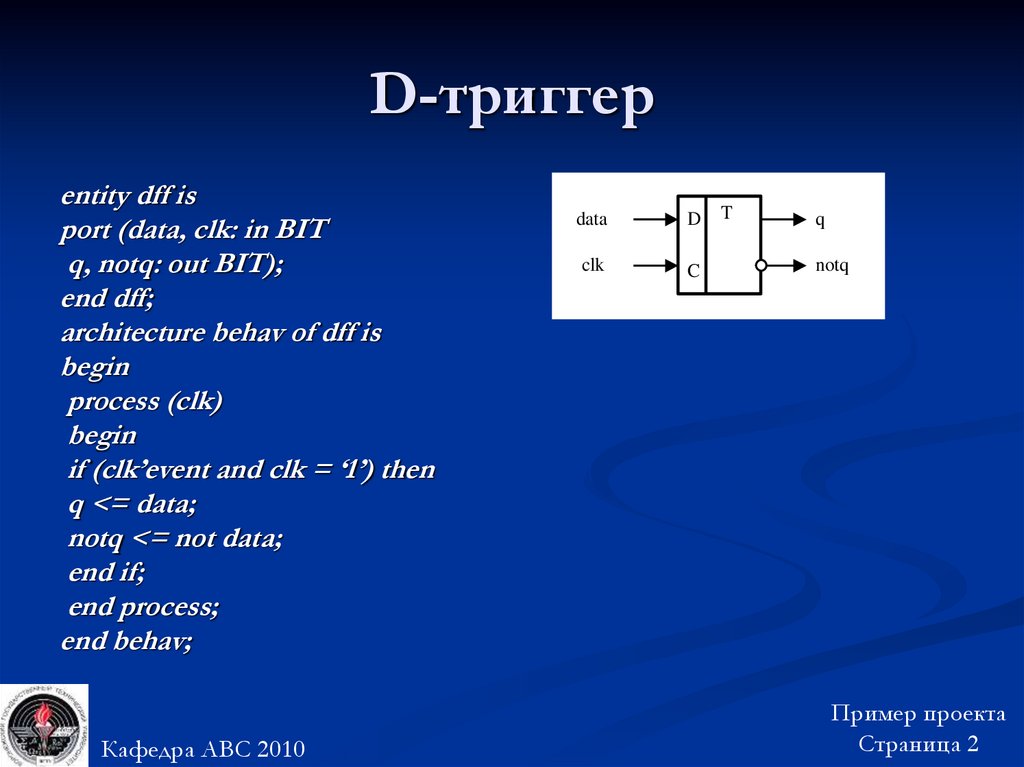

58. D-триггер

entity dff isport (data, clk: in BIT

q, notq: out BIT);

end dff;

architecture behav of dff is

begin

process (clk)

begin

if (clk’event and clk = ‘1’) then

q <= data;

notq <= not data;

end if;

end process;

end behav;

Кафедра АВС 2010

data

D

clk

C

T

q

notq

Пример проекта

Страница 2

59. Одноразрядный сумматор

aSM

entity full_adder is

b

cin

port (a, b, cin: in BIT;

sum, cout: out BIT);

end full_adder;

architecture full_ad_conc of full_adder is

begin

sum <= (a xor b) xor cin after 15 ns;

cout <= (a and b)or(b and cin)or(cin and a) after 10ns;

end full_ad_conc;

Кафедра АВС 2010

sum

cout

Пример проекта

Страница 3

60. Краткий обзор программной составляющей курса

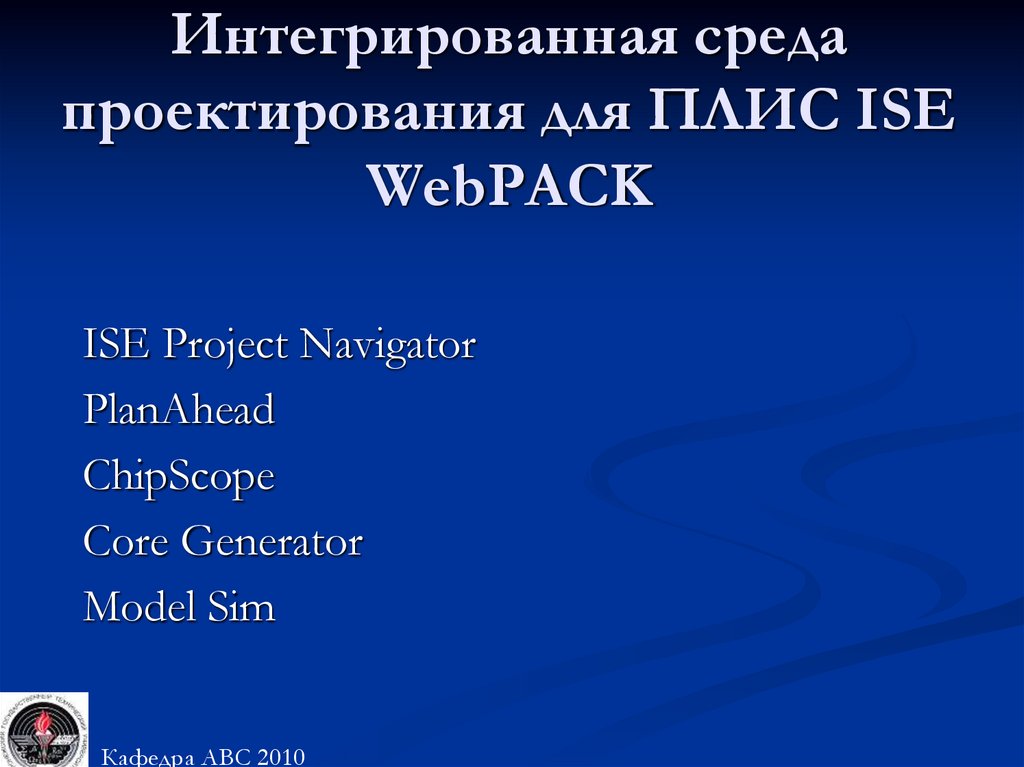

Кафедра АВС 201061. Интегрированная среда проектирования для ПЛИС ISE WebPACK

ISE Project NavigatorPlanAhead

ChipScope

Core Generator

Model Sim

Кафедра АВС 2010

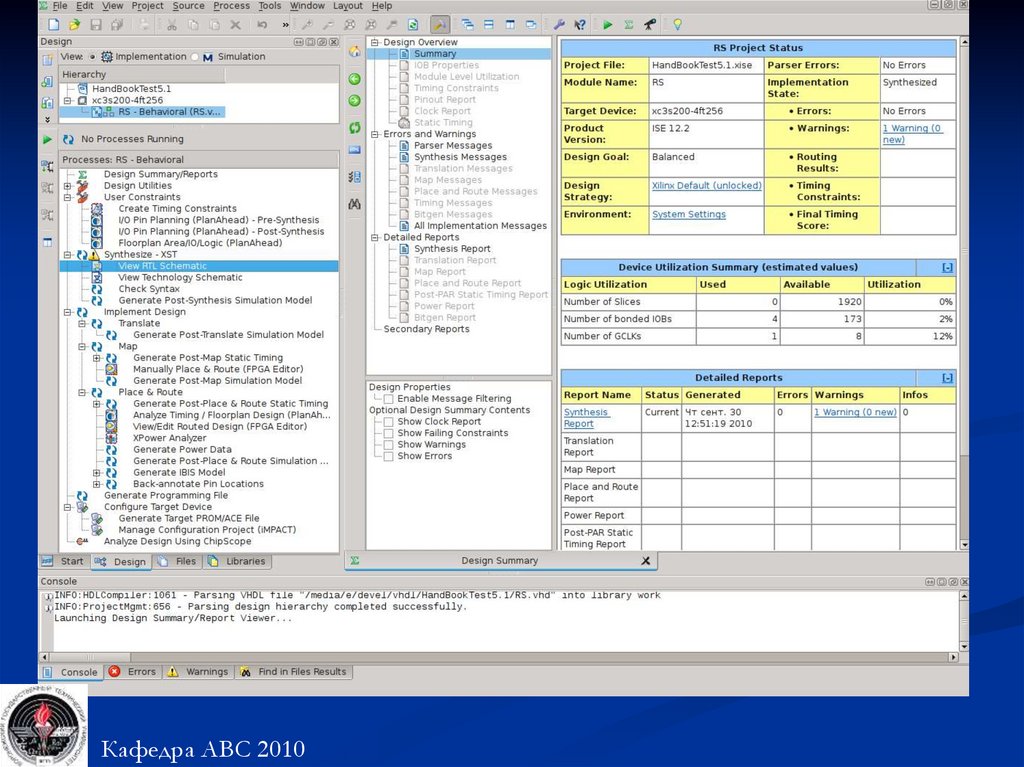

62.

Кафедра АВС 201063. Shematic

Проектирование на структурном уровне спомощью редактора схем

Кафедра АВС 2010

64.

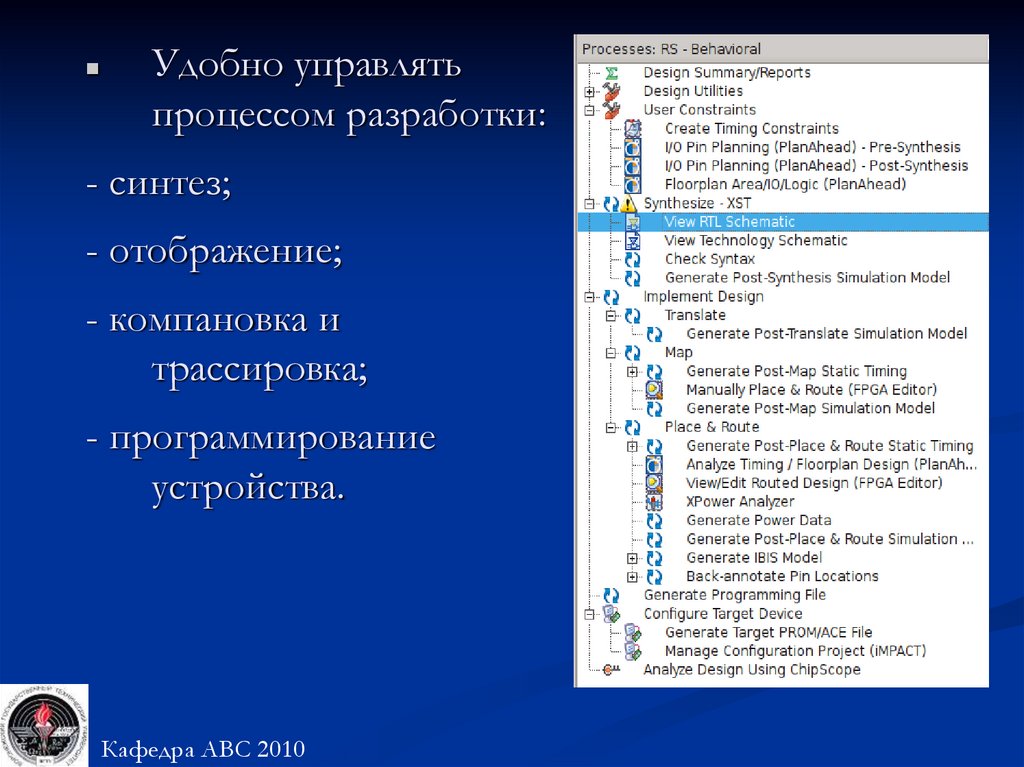

Удобно управлятьпроцессом разработки:

- синтез;

- отображение;

- компановка и

трассировка;

- программирование

устройства.

Кафедра АВС 2010

65.

Просмотр сгенерированной из HDL схемыКафедра АВС 2010

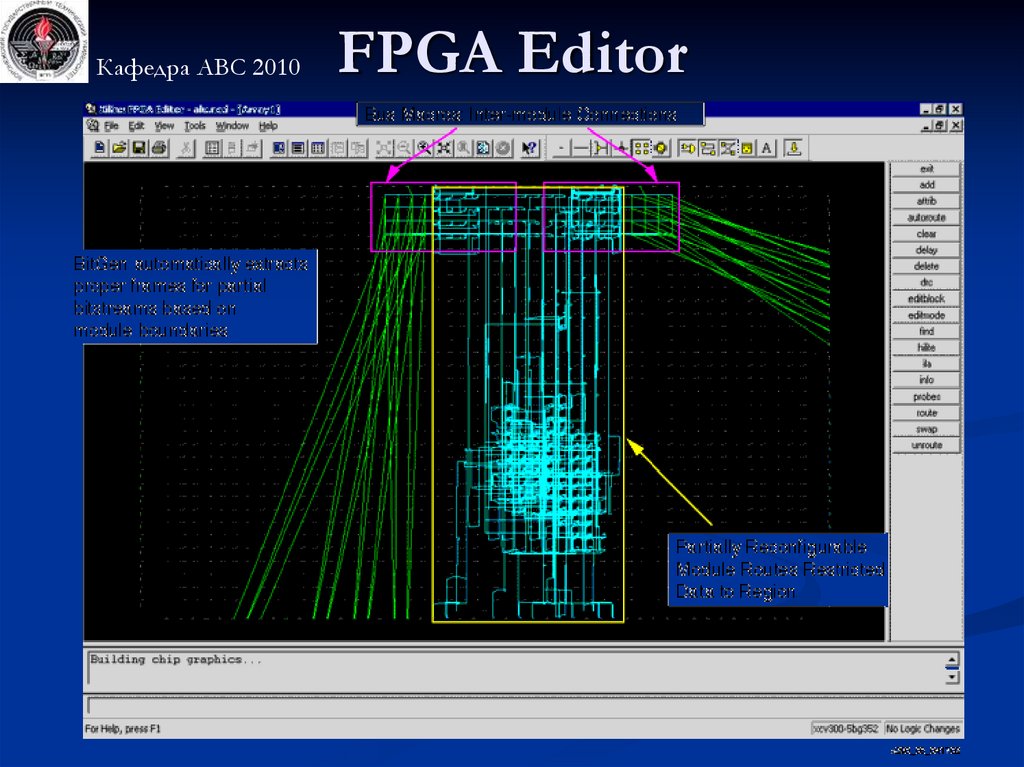

66. FPGA Editor

Кафедра АВС 2010FPGA Editor

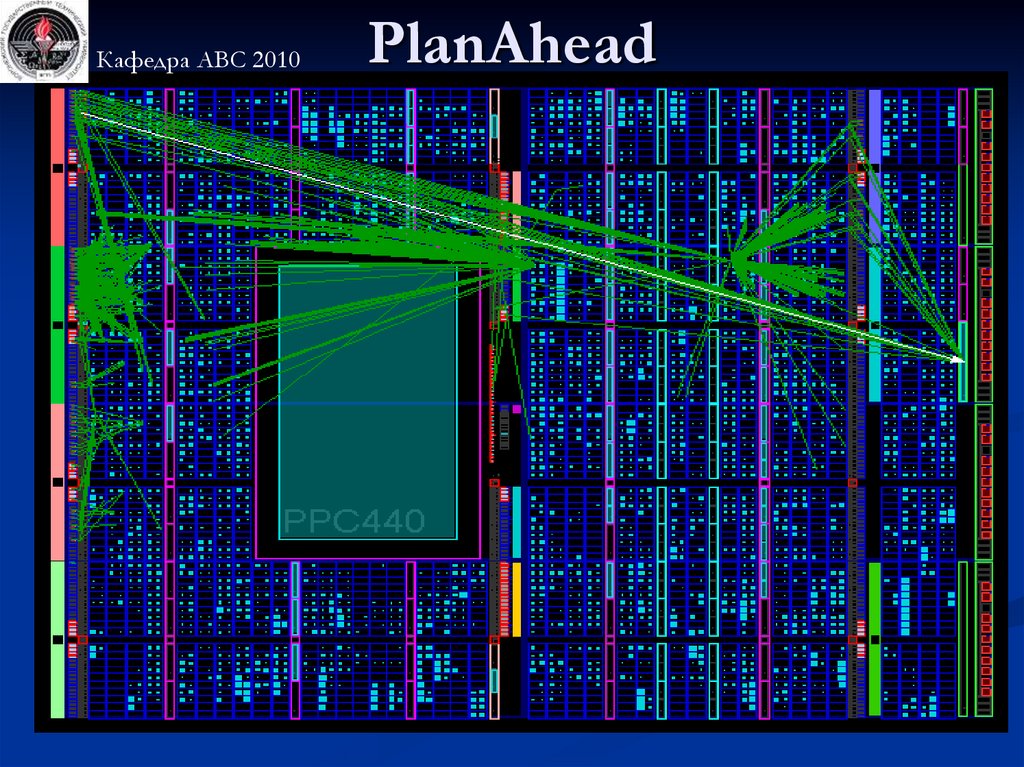

67. PlanAhead

Кафедра АВС 2010PlanAhead

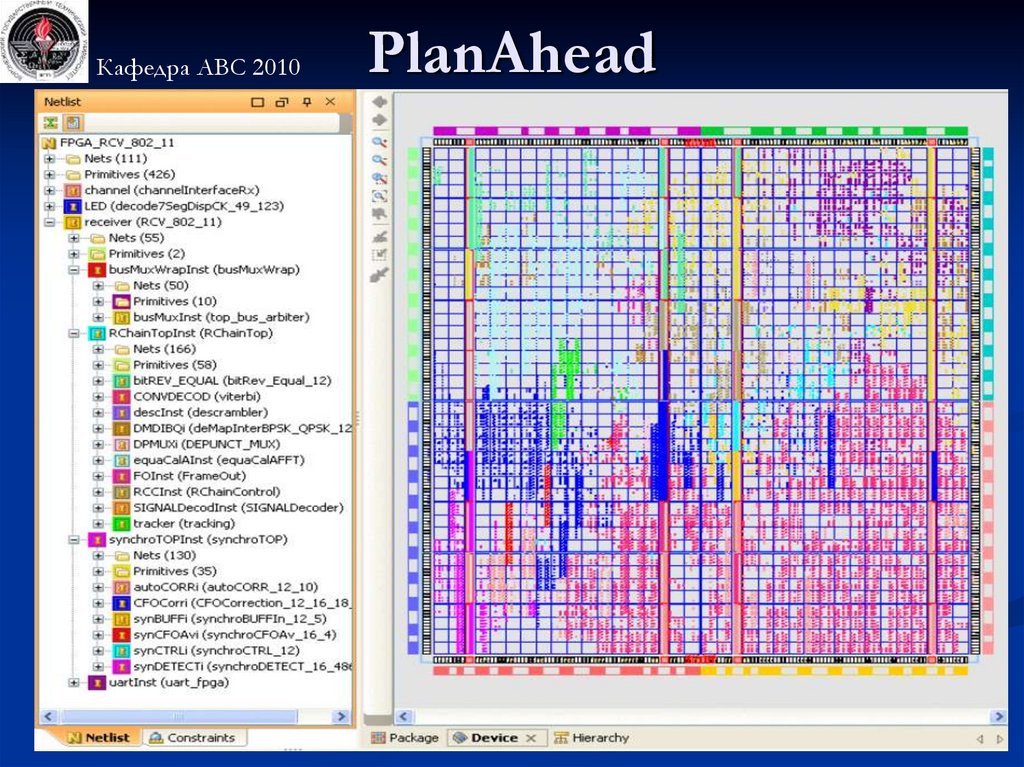

68. PlanAhead

Кафедра АВС 2010PlanAhead

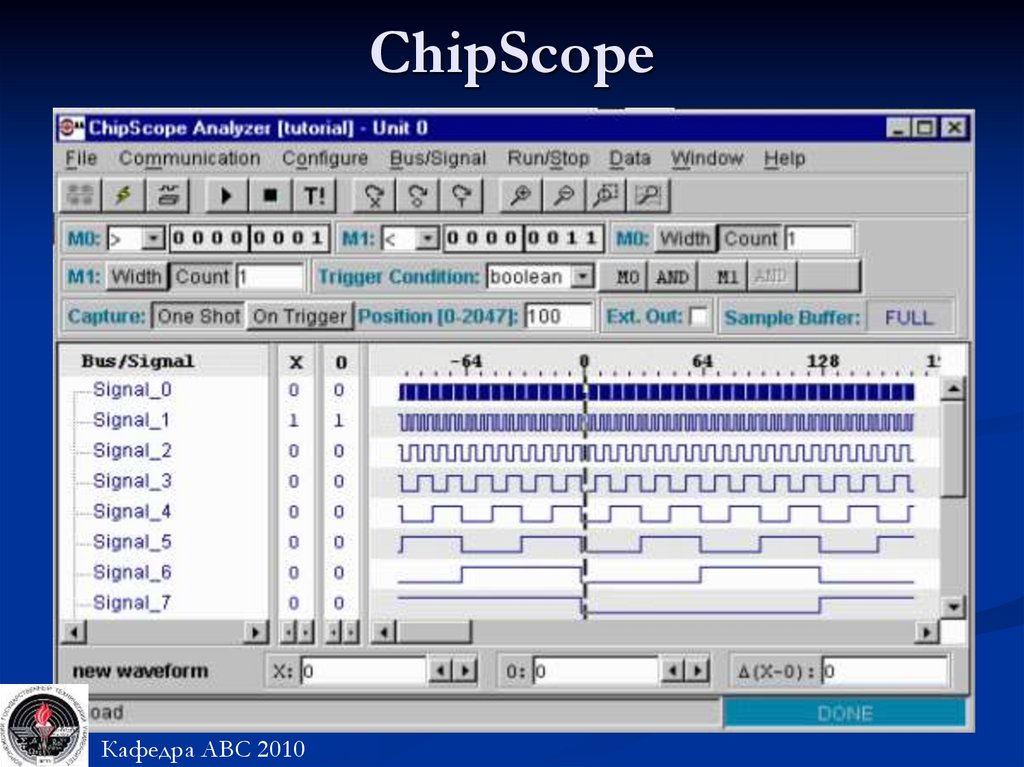

69. ChipScope

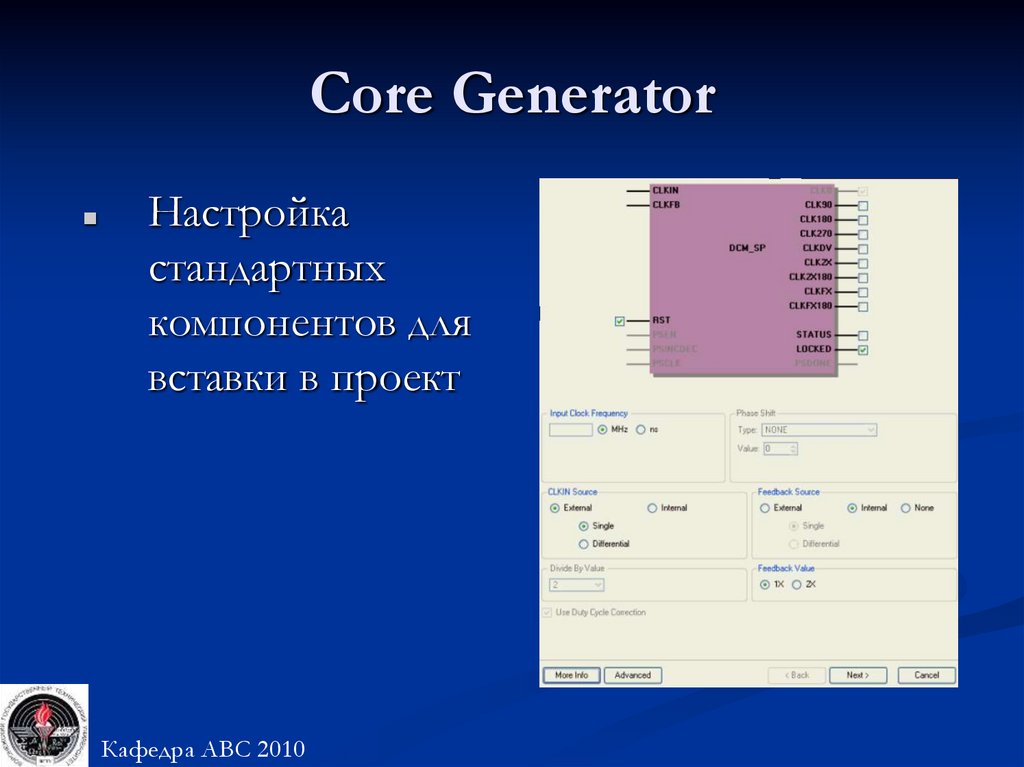

Кафедра АВС 201070. Core Generator

Настройкастандартных

компонентов для

вставки в проект

Кафедра АВС 2010

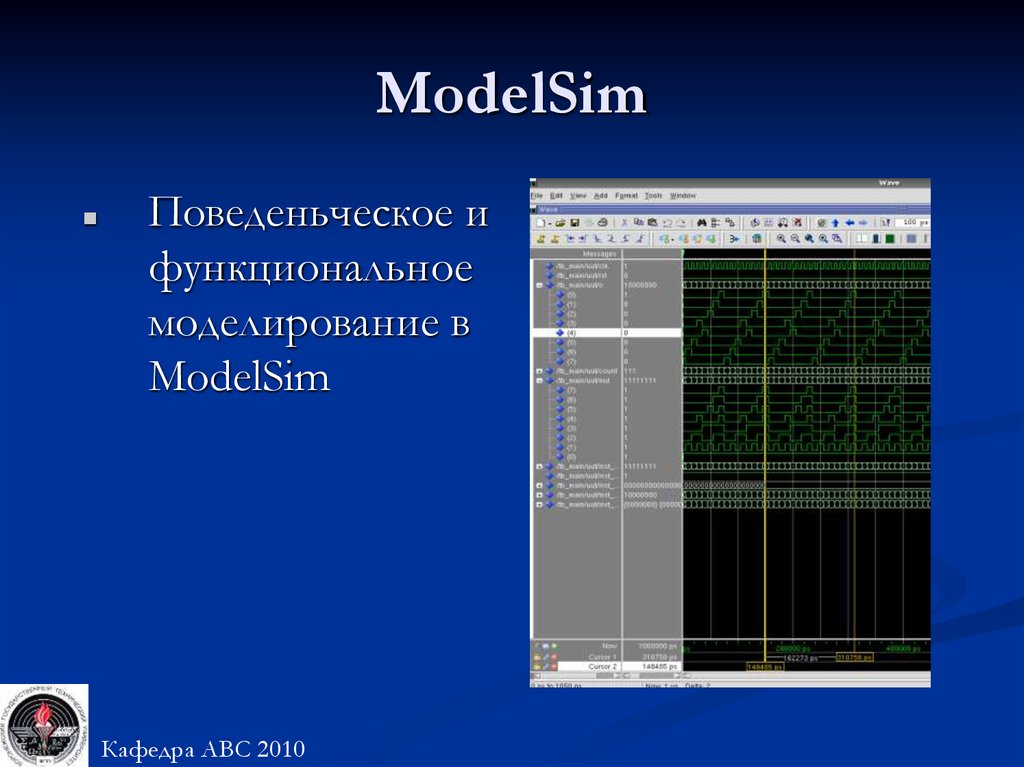

71. ModelSim

Поведеньческое ифункциональное

моделирование в

ModelSim

Кафедра АВС 2010

72.

Спасибо за внимание.Кафедра АВС 2010

Программирование

Программирование