Похожие презентации:

Одноплатная ЭВМ «Arduino»

1.

Одноплатная ЭВМ«Arduino»

Микроконтроллер

ATMega328

2.

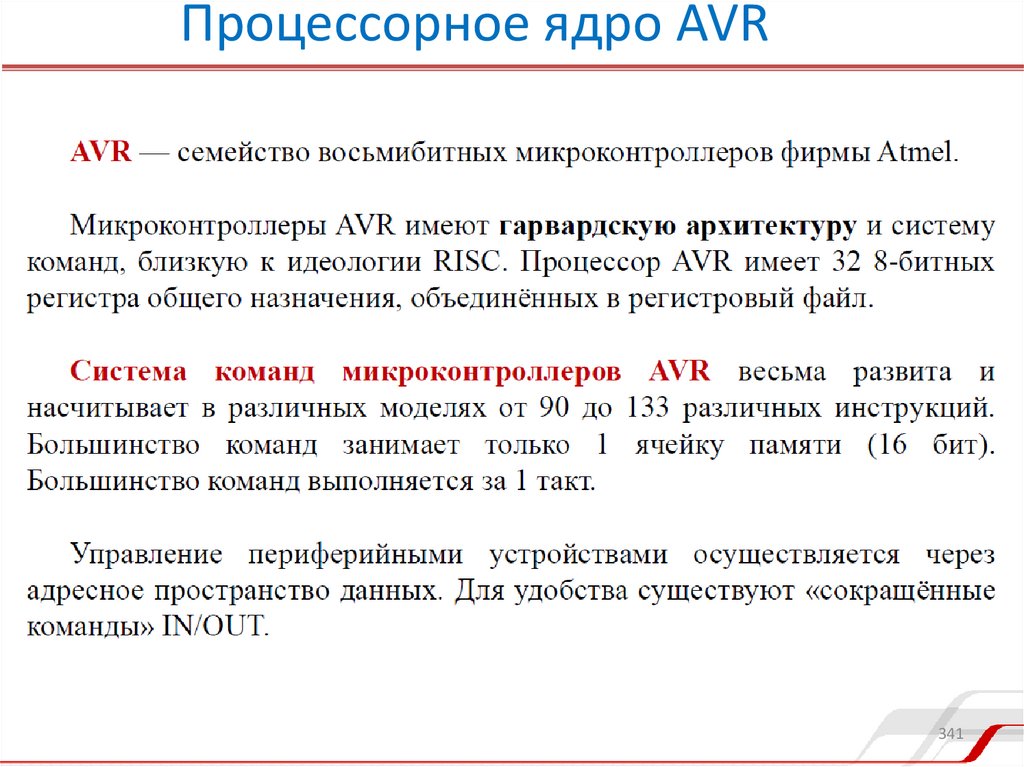

Семейство AVR-контроллеровУ АVR-контроллеров есть две особенности, которые

отличают это семейство от остальных МК.

1. Система команд и архитектура ядра АVR

разрабатывались совместно с фирмой-разработчиком

компиляторов с языков программирования высокого уровня IAR

Systems. В результате появилась возможность писать АVRпроrраммы на языке С без большой потери в производительности

по сравнению с программами, написанными на ассемблере.

2. Одним из существенных преимуществ АVR стало

применение конвейера. В результате для АVR не существует

понятия машинного цикла: большинство команд выполняется за

один такт. Для сравнения отметим, что пользующиеся большой

популярностью МК семейства PIC выполняют команду за 4 такта, а

классические 8051 - 12 тактов.

3.

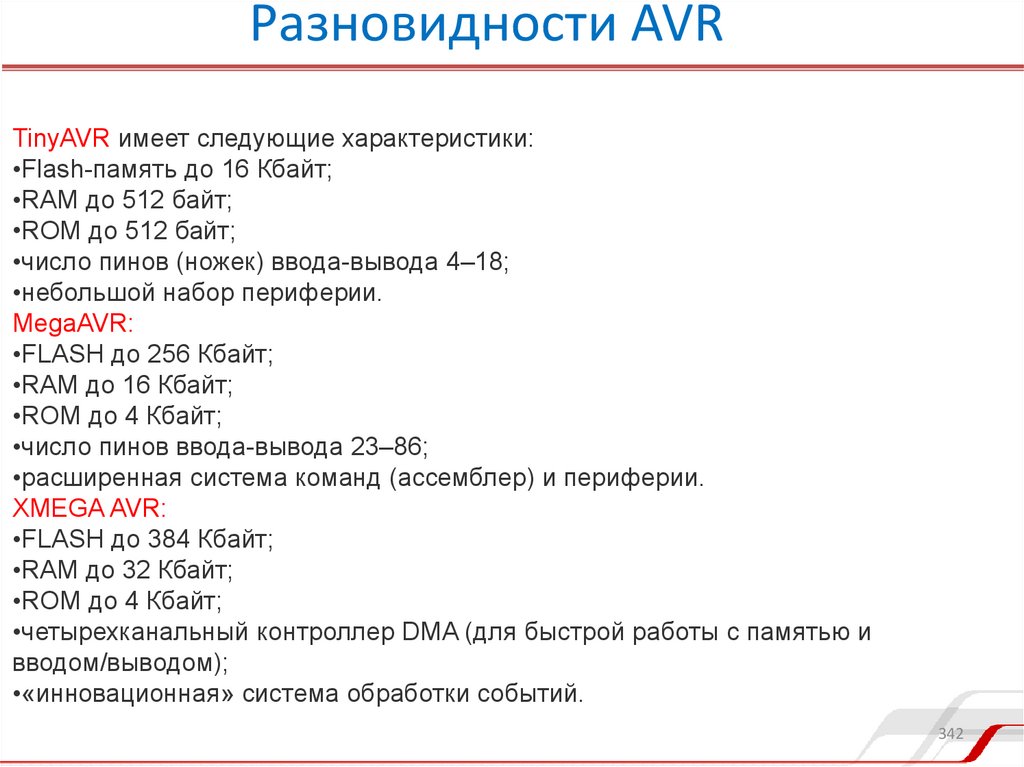

Семейство AVR-контроллеровТри самых распространенных семейств контроллеров.

1. Контроллеры классической архитектуры х51 (первые

микросхемы семейства 8051 были выпущены еще в начале 1980'-х)

лучше всего подходят для общего изучения предмета. Отметим, что

кроме Atmel, х51-совместимые изделия выпускают еще порядка

десятка фирм, включая такие гиганты, как Philips и Siemens, есть и

отечественные аналоги (серии 1816, 1830 и др.), что делает эту

архитектуру наиболее универсальной.

2. Семейство АVR рекомендуется для начинающих

электронщиков-практиков, в силу простоты и универсальности

устройства, преемственности структуры для различных типов

контроллеров, простоты схемотехники и программирования (в

данном случае под «программированием» понимается процесс

записи программ в микросхему).

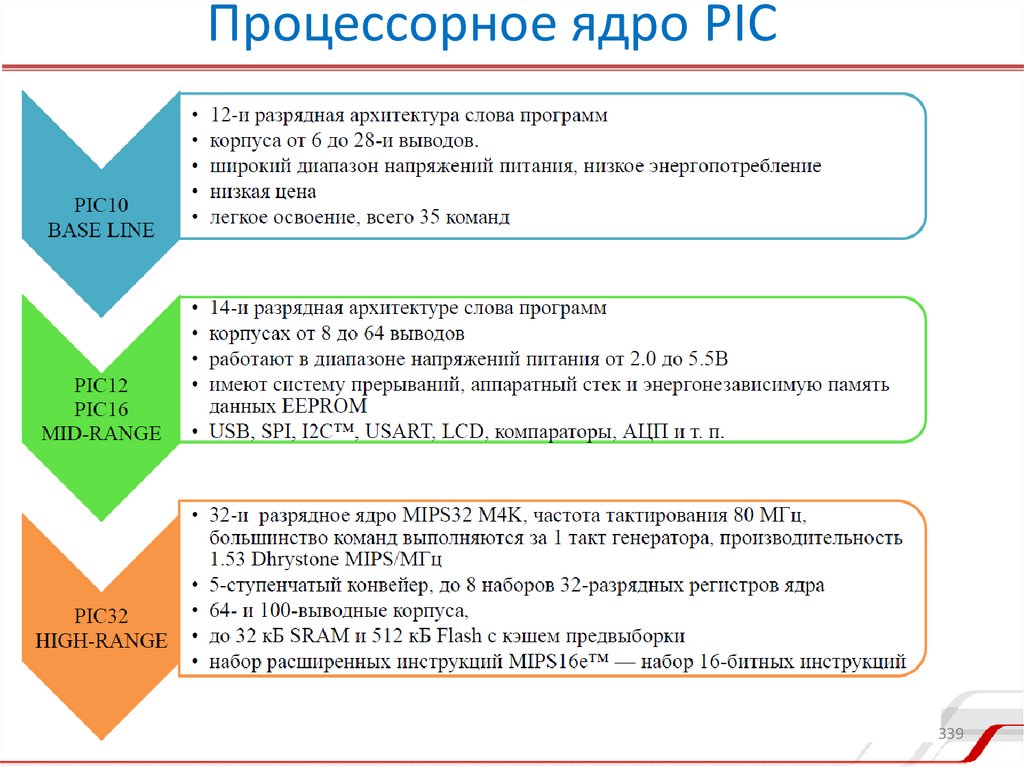

3. PIC фирмы Microchip идеально подходят для

проектирования несложных устройств, особенно предназначенных

для тиражирования.

4.

Корпус микроконтроллерасемейства ATMega

5.

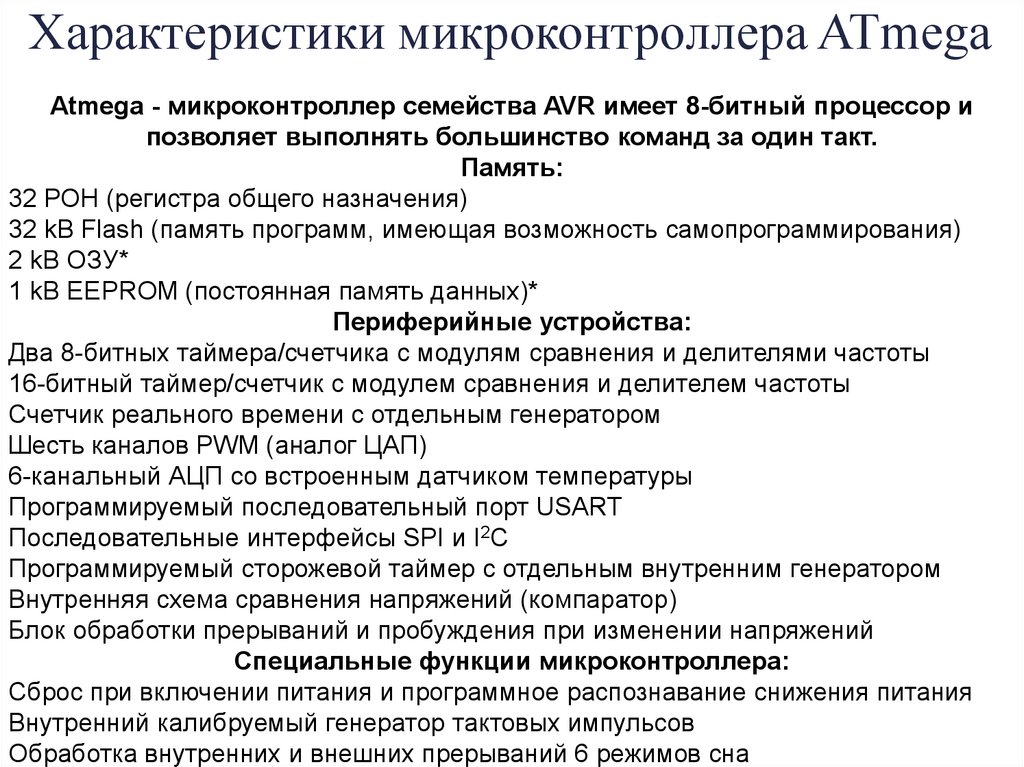

Характеристики микроконтроллера ATmegaAtmega - микроконтроллер семейства AVR имеет 8-битный процессор и

позволяет выполнять большинство команд за один такт.

Память:

32 РОН (регистра общего назначения)

32 kB Flash (память программ, имеющая возможность самопрограммирования)

2 kB ОЗУ*

1 kB EEPROM (постоянная память данных)*

Периферийные устройства:

Два 8-битных таймера/счетчика с модулям сравнения и делителями частоты

16-битный таймер/счетчик с модулем сравнения и делителем частоты

Счетчик реального времени с отдельным генератором

Шесть каналов PWM (аналог ЦАП)

6-канальный АЦП со встроенным датчиком температуры

Программируемый последовательный порт USART

Последовательные интерфейсы SPI и I2C

Программируемый сторожевой таймер с отдельным внутренним генератором

Внутренняя схема сравнения напряжений (компаратор)

Блок обработки прерываний и пробуждения при изменении напряжений

Специальные функции микроконтроллера:

Сброс при включении питания и программное распознавание снижения питания

Внутренний калибруемый генератор тактовых импульсов

Обработка внутренних и внешних прерываний 6 режимов сна

6.

Выводы микроконтроллера ATMega7.

Назначение выводов ATMega8.

Программаторы ATMEL, параллельныйпорт LPT

9.

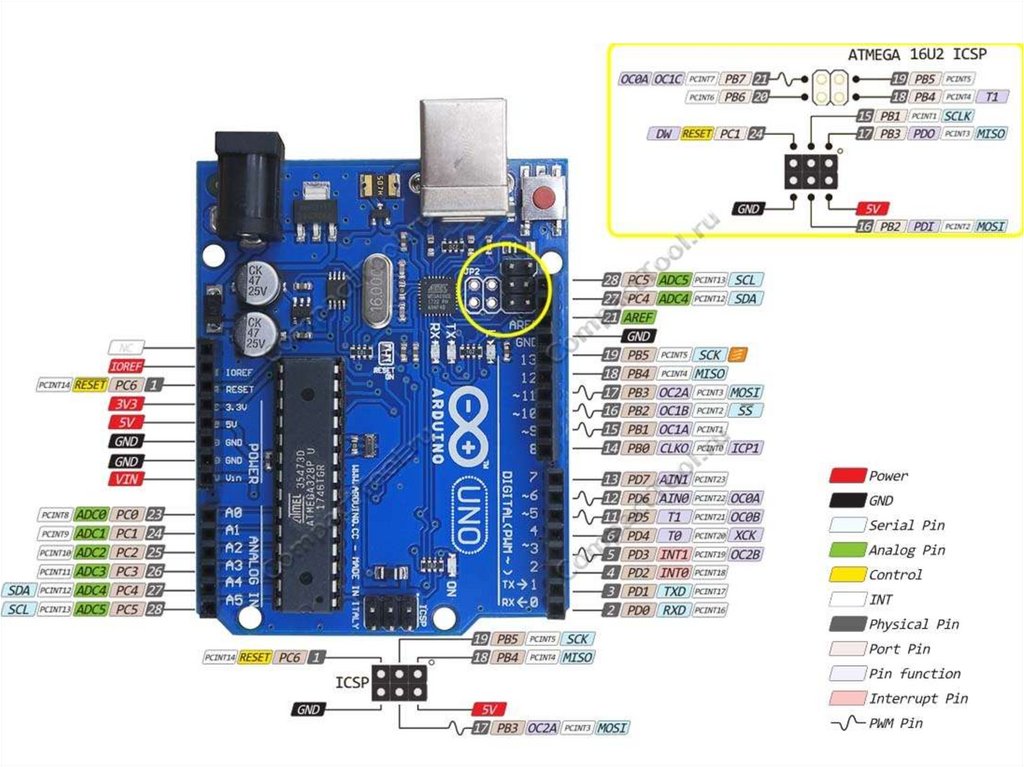

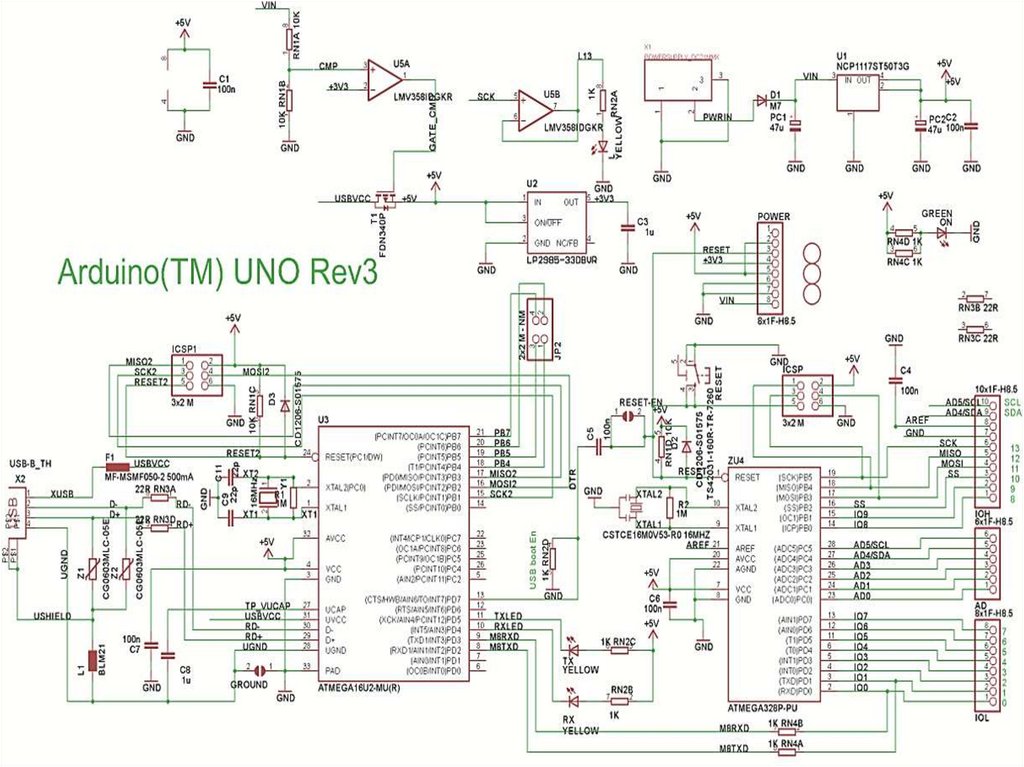

Одноплатная ЭВМ Arduino UNO10.

11.

12.

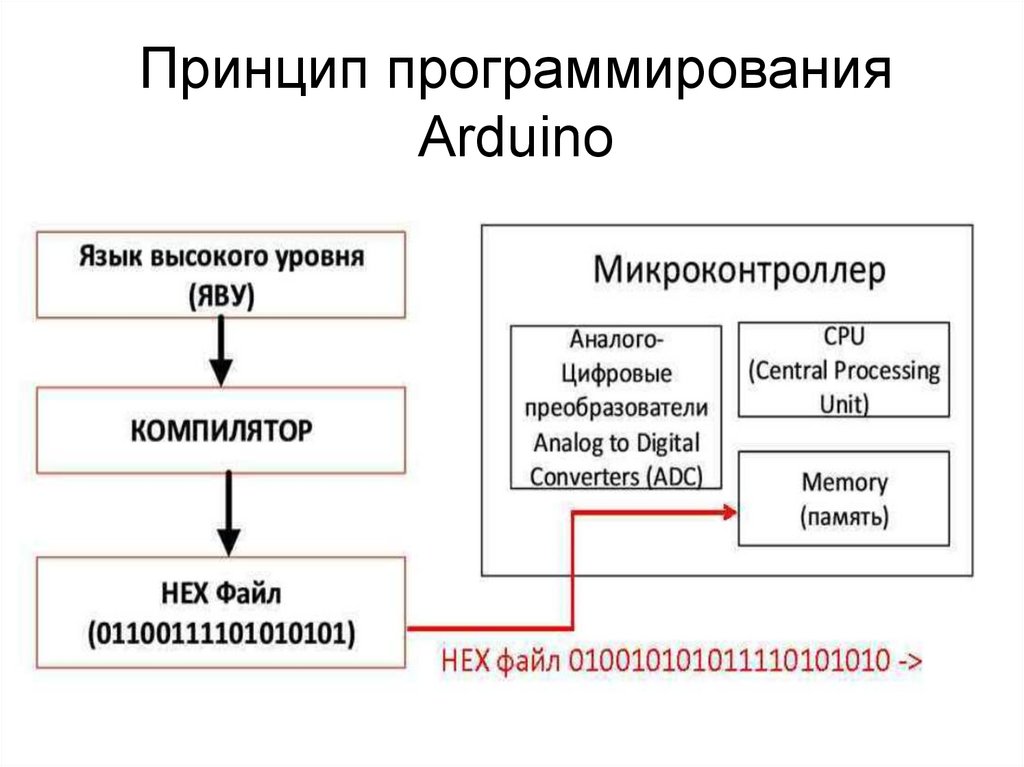

Принцип программированияArduino

13.

14.

Архитектура контроллеров семейства AVR15.

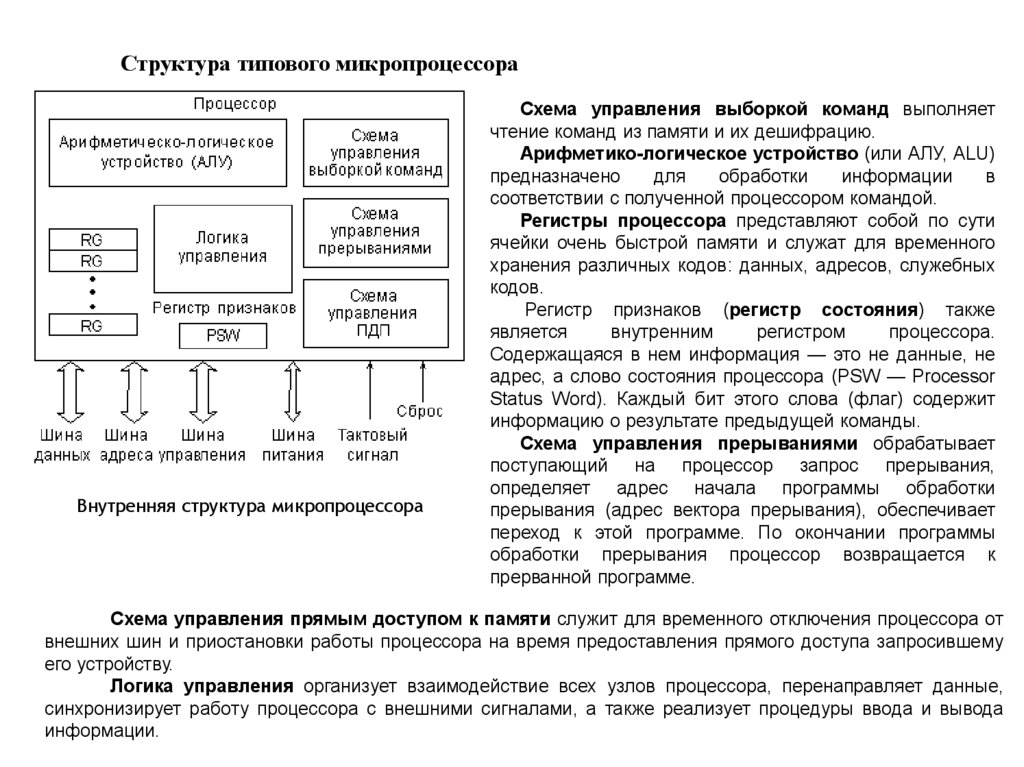

Архитектура контроллеров семейства AVRПроцессорное ядро (Central Processing Unit – CPU)

AVR-микроконтроллеров содержит:

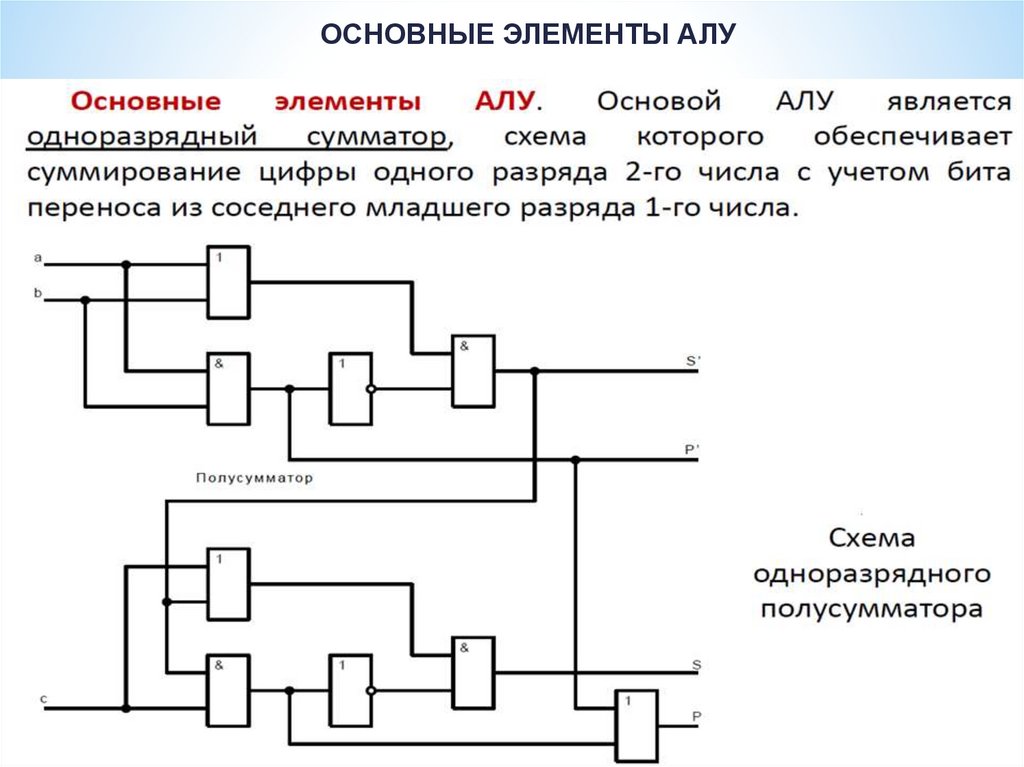

1. Арифметико-логическое устройство (АЛУ).

2. Регистры общего назначения (РОН).

3. Программный счётчик.

4. Указатель стека.

5. Регистр состояния.

6. Регистр команд.

7. Дешифратор команд.

8. Схему управления выполнением команд.

16.

Архитектура контроллеров семейства AVRВ АЛУ выполняются все вычислительные операции. Операции

производятся только над содержимым РОН. На выборку содержимого

регистров, выполнение операции и запись результата обратно в РОН

затрачивается один машинный такт (один период тактовой частоты).

Регистры общего назначения представляют собой 8-разрядные

ячейки памяти с быстрым доступом, непосредственно доступные АЛУ. В

AVR-микро-контроллерах имеется 32 РОН.

Программный счётчик (Program Counter – PC) содержит адрес

следующей выполняемой команды.

Указатель стека (Stack Pointer – SP) служит для хранения адреса

вершины стека.

Регистр состояния (Status Register – SREG) содержит слово состояния

процессора.

Регистр команд, дешифратор команд и схема управления

выполнением команд обеспечивают выборку из памяти программ

команды, адрес которой содержится в программном счётчике, её

декодирование, определение способа доступа к указанным в команде

аргументам и собственно выполнение команды.

17.

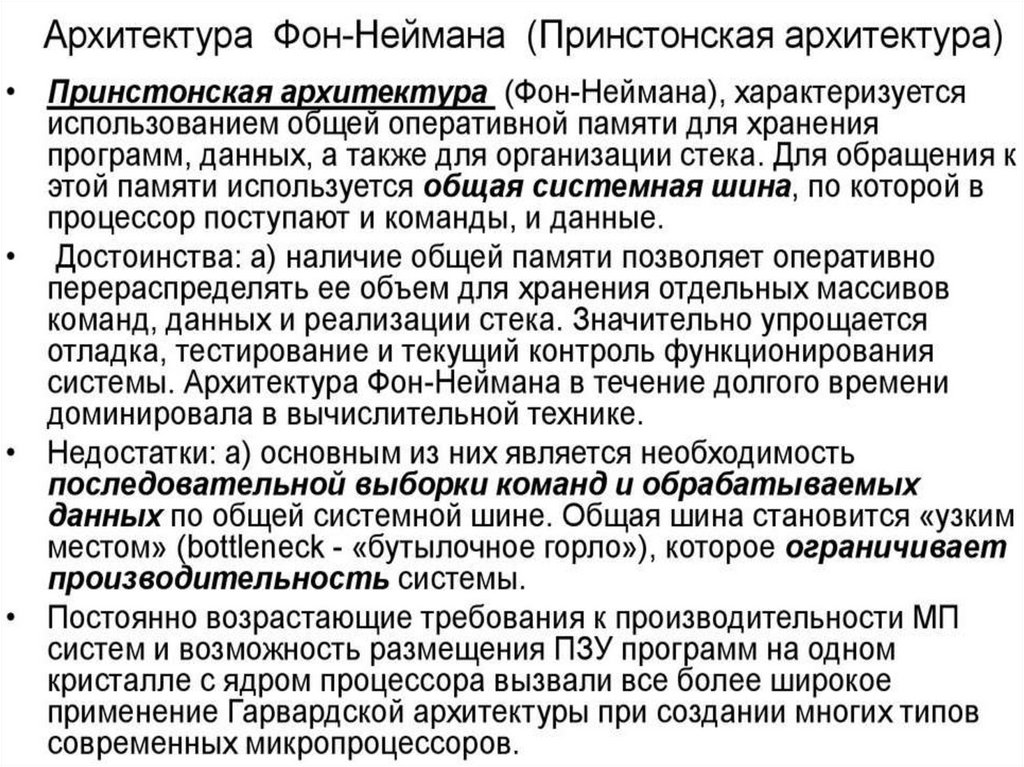

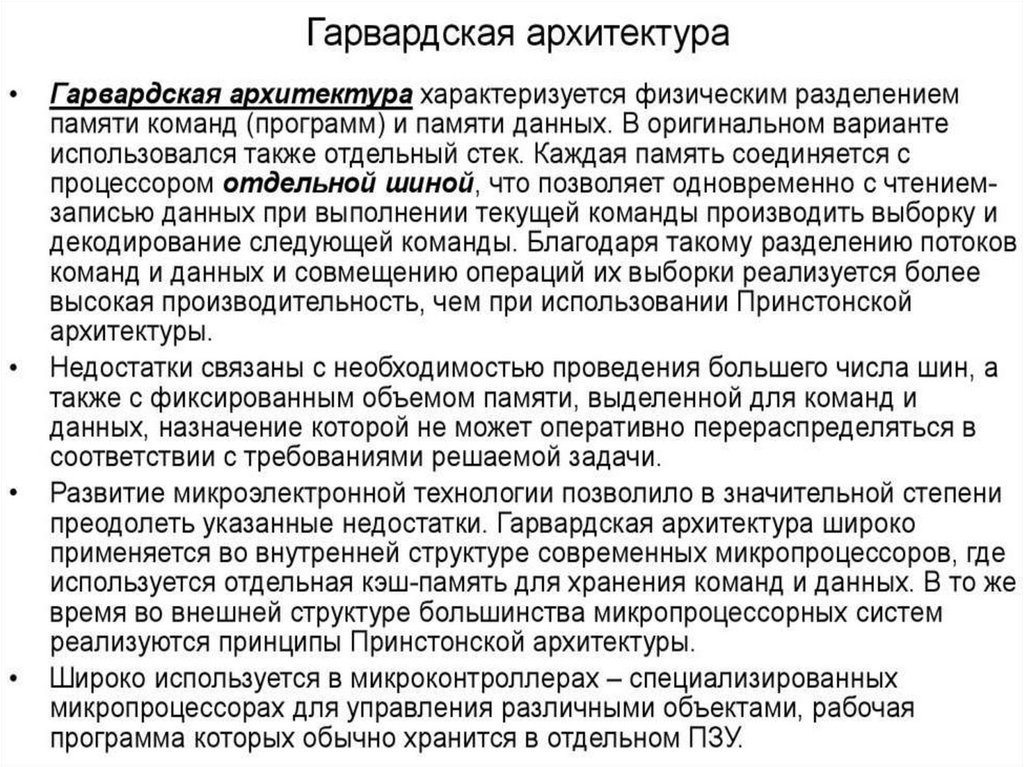

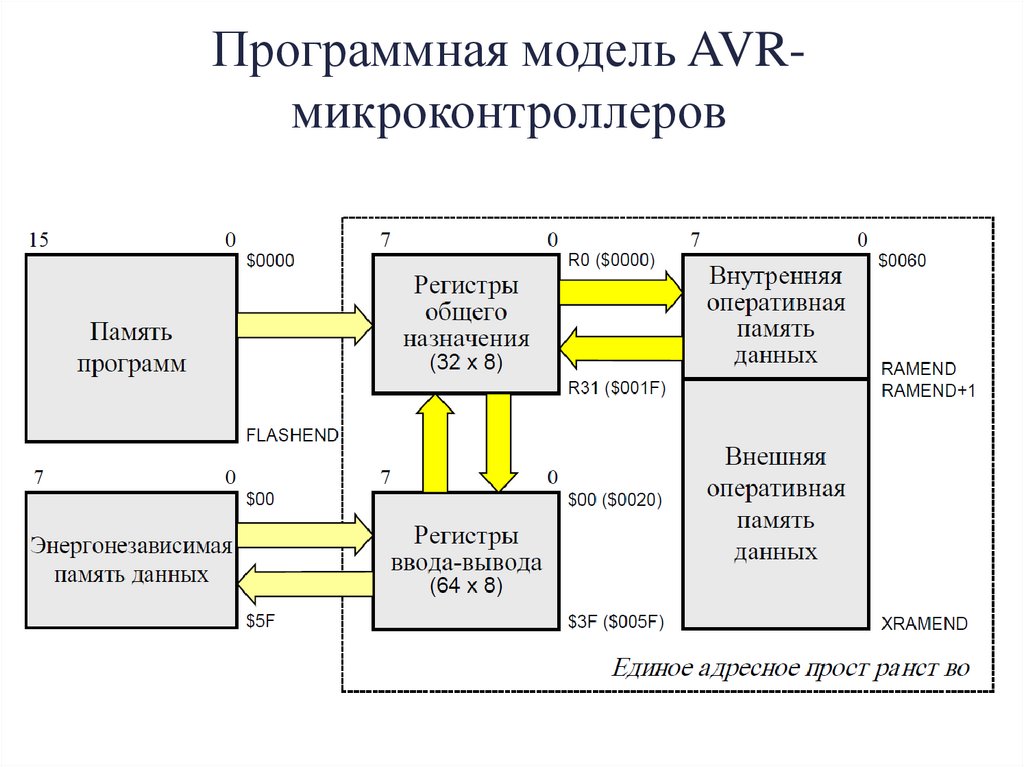

Архитектура контроллеров семейства AVRПамять AVR-микроконтроллеров организована по схеме гарвардского

типа – адресные пространства памяти программ и памяти данных

разделены.

Память программ представляет собой перепрограммируемое ПЗУ типа

FLASH и выполнена в виде последовательности 16-разрядных ячеек, так

как большинство команд AVR-микроконтроллера являются 16разрядными словами.

Оперативная память данных представляет собой статическое ОЗУ

(SRAM – Static Random-Access Memory) и организована как

последовательность 8-разрядных ячеек. Оперативная память данных

может быть внутренней (до 16 Kбайт) и внешней (до 64 Кбайт).

Энергонезависимая (nonvolatile) память данных организована как

последовательность 8-разрядных ячеек и представляет собой перепрограммируемое ПЗУ с электрическим стиранием (РПЗУ-ЭС, или EEPROM –

Electrically Erasable Programmable Read-only Memory). Энергонезависимая

память данных имеет размер до 64 Кбайт.

Регистры ввода-вывода предназначены для управления процессорным ядром и периферийными устройствами AVR-микроконтроллера.

Схема прерываний обеспечивает возможность асинхронного прерывания процесса выполнения программы при определённых условиях.

18.

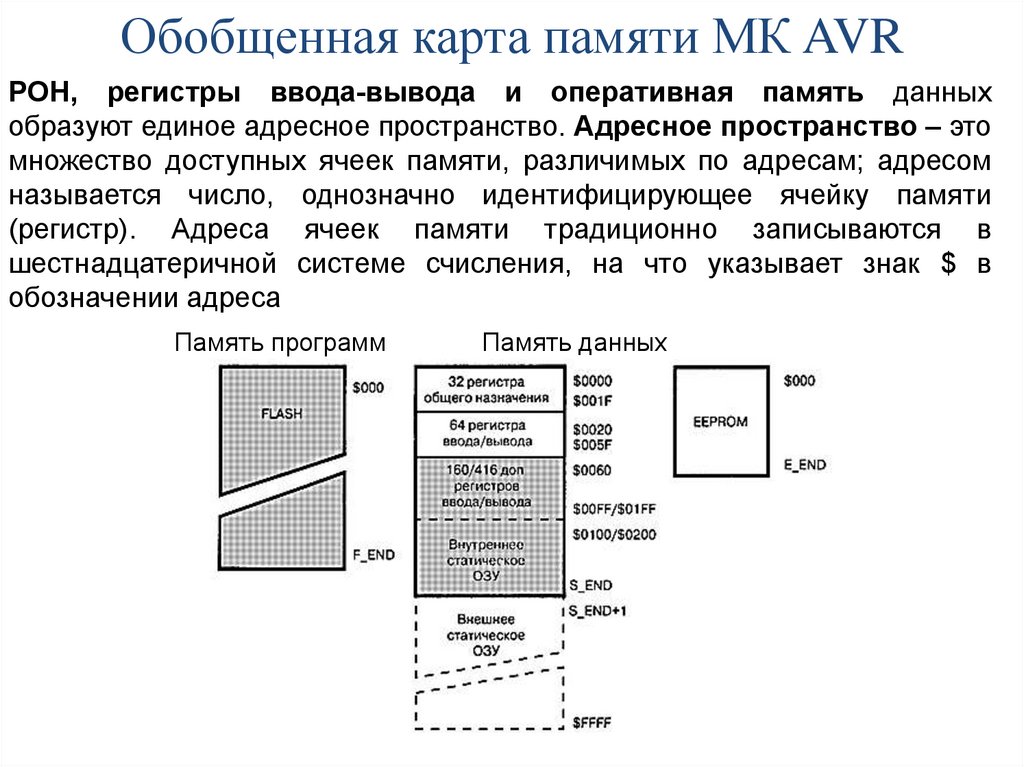

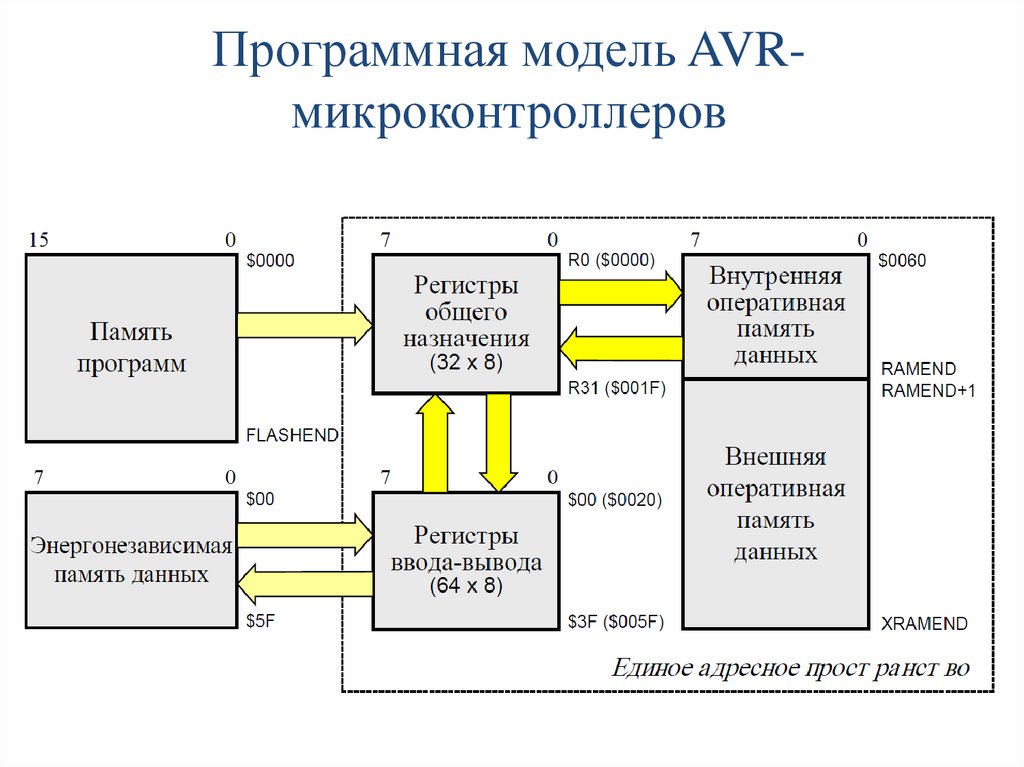

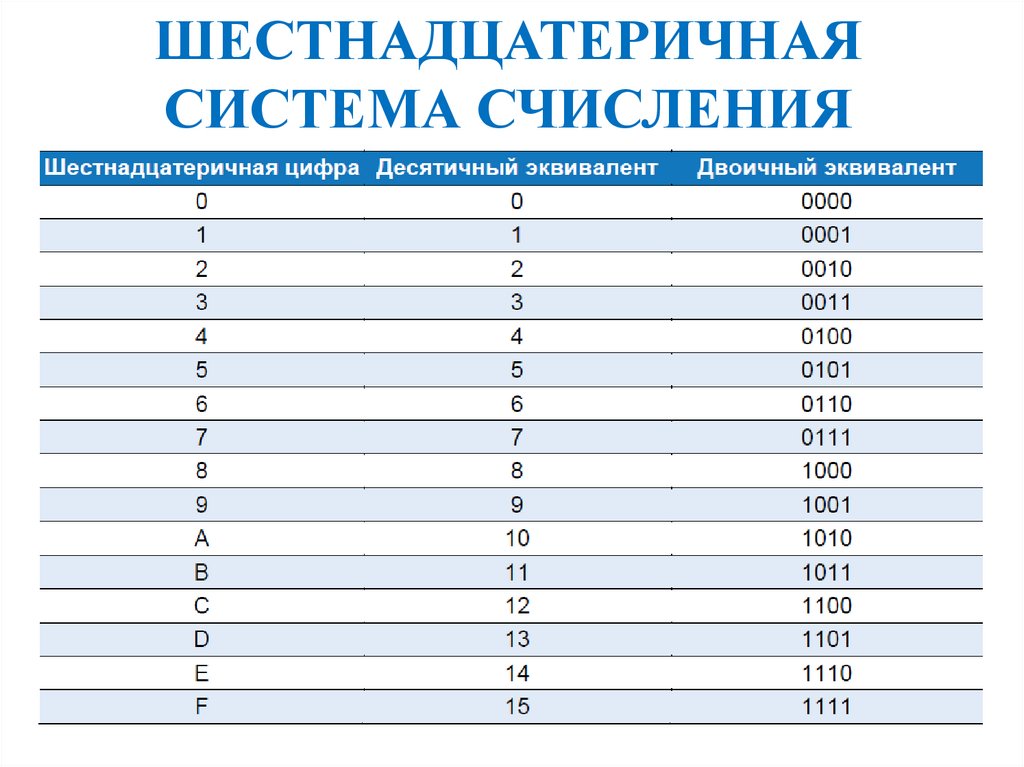

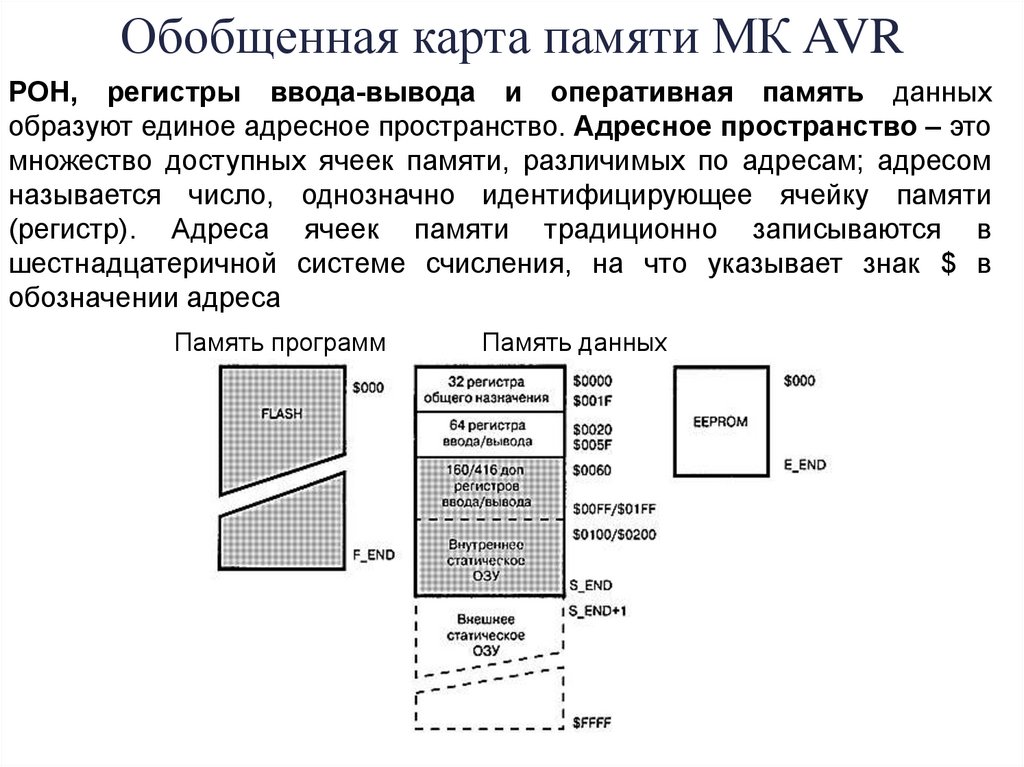

Обобщенная карта памяти МК AVRРОН, регистры ввода-вывода и оперативная память данных

образуют единое адресное пространство. Адресное пространство – это

множество доступных ячеек памяти, различимых по адресам; адресом

называется число, однозначно идентифицирующее ячейку памяти

(регистр). Адреса ячеек памяти традиционно записываются в

шестнадцатеричной системе счисления, на что указывает знак $ в

обозначении адреса

Память программ

Память данных

19.

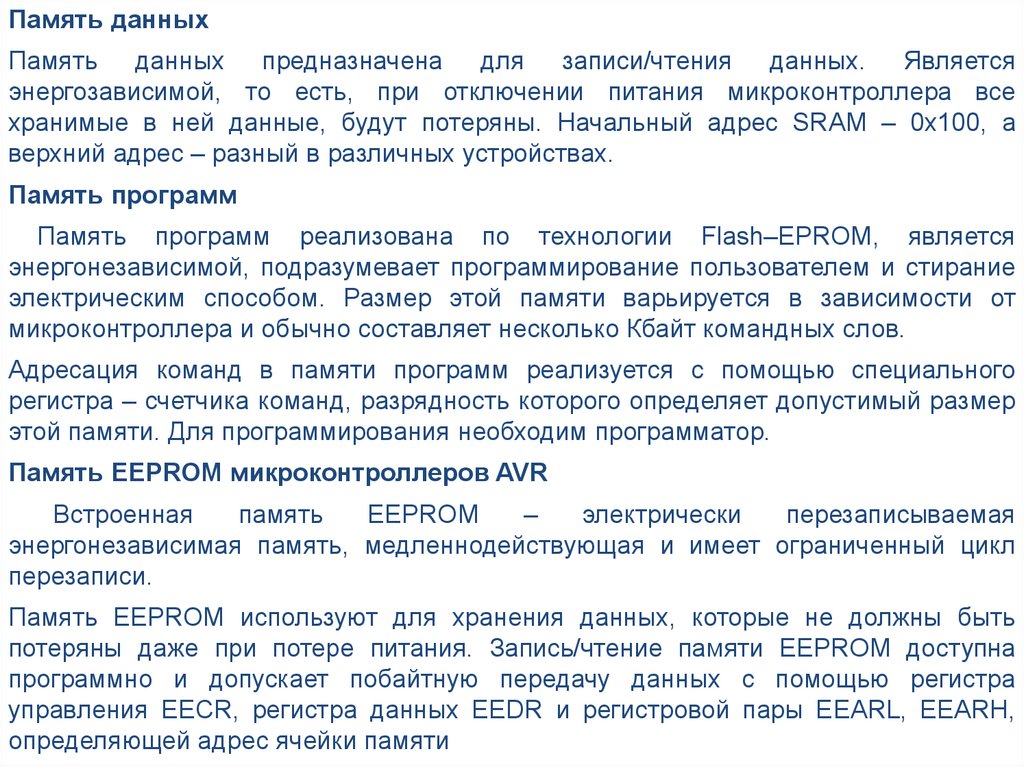

Память данныхПамять данных предназначена для записи/чтения данных. Является

энергозависимой, то есть, при отключении питания микроконтроллера все

хранимые в ней данные, будут потеряны. Начальный адрес SRAM – 0x100, а

верхний адрес – разный в различных устройствах.

Память программ

Память программ реализована по технологии Flash–EPROM, является

энергонезависимой, подразумевает программирование пользователем и cтирание

электрическим способом. Размер этой памяти варьируется в зависимости от

микроконтроллера и обычно составляет несколько Кбайт командных слов.

Адресация команд в памяти программ реализуется с помощью специального

регистра – счетчика команд, разрядность которого определяет допустимый размер

этой памяти. Для программирования необходим программатор.

Память EEPROM микроконтроллеров AVR

Встроенная

память

EEPROM

–

электрически

перезаписываемая

энергонезависимая память, медленнодействующая и имеет ограниченный цикл

перезаписи.

Память EEPROM используют для хранения данных, которые не должны быть

потеряны даже при потере питания. Запись/чтение памяти EEPROM доступна

программно и допускает побайтную передачу данных с помощью регистра

управления EECR, регистра данных EEDR и регистровой пары EEARL, EEARH,

определяющей адрес ячейки памяти

20.

Регистры общего назначения (РОН)РОН

(R0…R31)

могут

использоваться в программе для

хранения данных, адресов, констант и

другой информации. Шесть старших

регистров объединены попарно и

составляют

три

16-разрядных

регистра Х [R27:R26], Y [R29:R28] и Z

[R31:R30]

В микроконтроллерах AVR она

состоит из 32 восьмиразрядных

регистров (диапазон адресов 0x000 –

0x01F).

В программах, написанных на

языке

С,

непосредственное

обращение к регистрам общего

назначения обычно не требуется.

21.

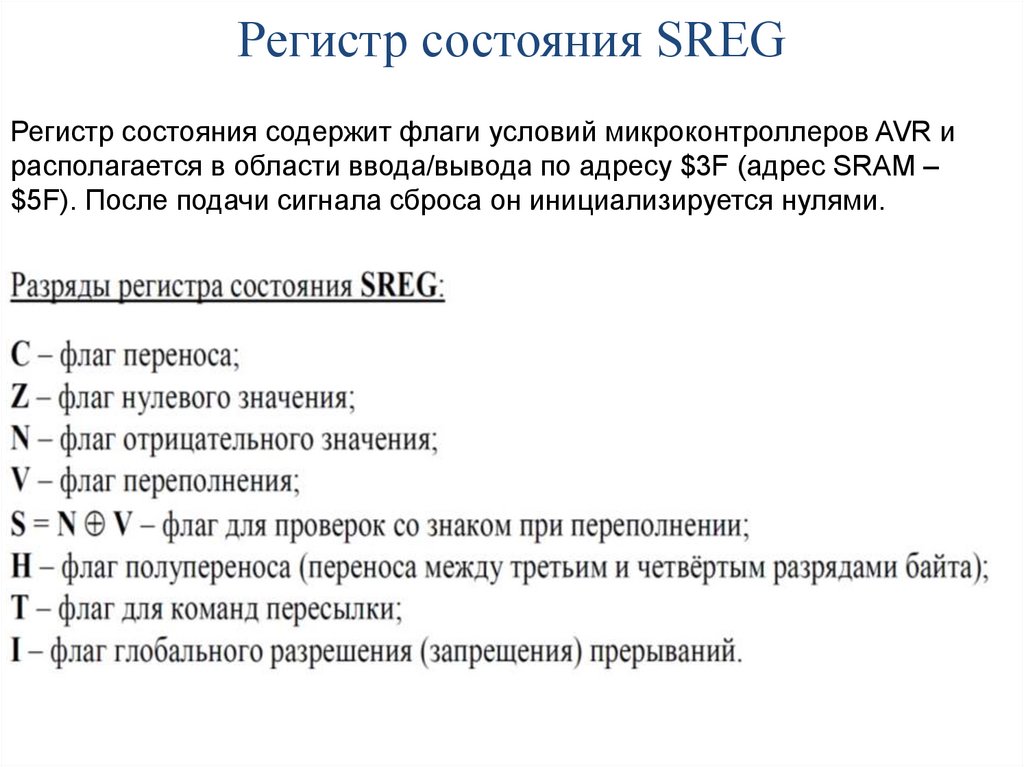

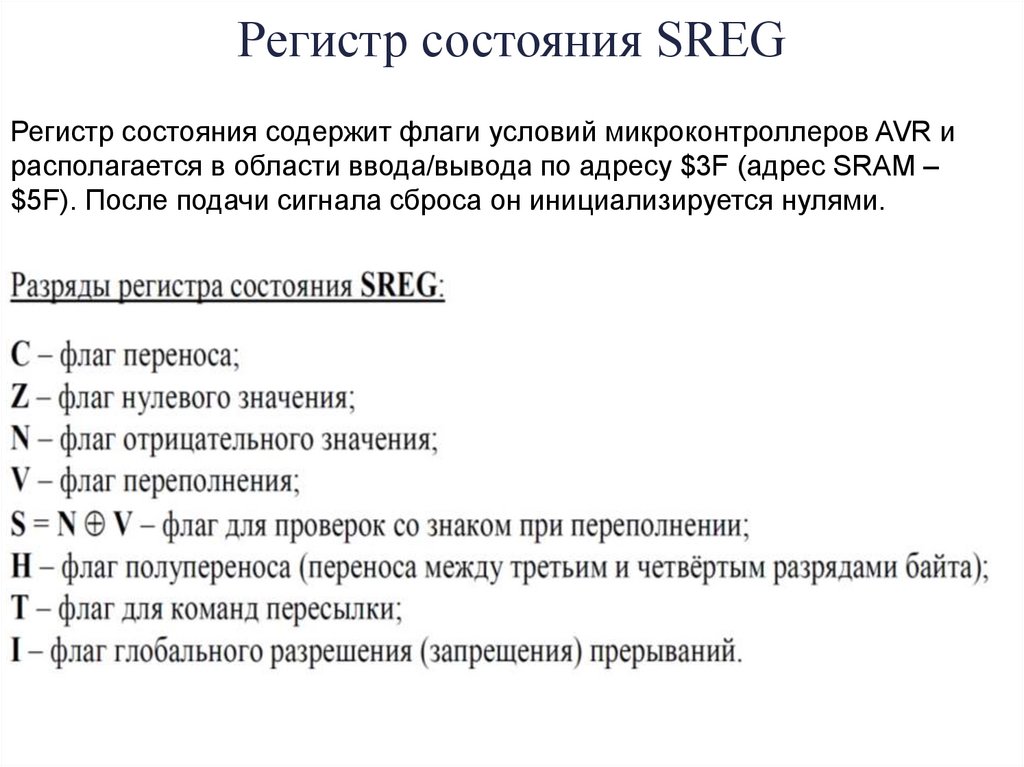

Регистр состояния SREGРегистр состояния содержит флаги условий микроконтроллеров AVR и

располагается в области ввода/вывода по адресу $3F (адрес SRAM –

$5F). После подачи сигнала сброса он инициализируется нулями.

22.

разряд 0 (С) – флаг переноса (Carry); указывает на переполнение(перенос)после выполнения арифметической или логической операции;

разряд 1 (Z) – нулевой флаг (Zero); всегда устанавливается, если результат

арифметической или логической операции равен нулю; сбрасывается, если

результат операции не равен нулю;

разряд 2 (N) – флаг отрицательного результата (Negative); указывает на

отрицательный результат после выполнения арифметической или логической

операции;

• разряд 3 (V) – флаг переполнения при вычислениях в дополнительных кодах

(Two's complement Overflow); поддерживает арифметику дополнительных

кодов (арифметика кодов с дополнением до двух); устанавливается, если при

выполнении соответствующей операции происходит переполнение, в противном

случае – сбрасывается;

• разряд 4 (S) – флаг знака (Sign); S = N V – связь флагов N и V с помощью

операции "Исключающее ИЛИ"; флаг знака может применяться для

определения фактического результата арифметической операции;

• разряд 5 (Н) – флаг половинного переноса (Half Carry); указывает на

переполнение в младшем полубайте (разряды 0...3 байта данных);

устанавливается, когда происходит перенос из младшего полубайта в старший,

в противном случае – сбрасывается;

• разряд 6 (Т) – флаг копирования (Transfer or Copy); предназначен для

свободного применения программистом (например, в качестве буфера);

• разряд 7 (I) – общее разрешение прерываний (Global Interrupt); если

прерывания, как таковые, должны быть разрешены, то должен быть установлен

разряд 7 регистра состояния (в лог. 1).

23.

СтекСтек – это особая область памяти данных, используемая

процессором для временного хранения адресов возврата из подпрограмм,

промежуточных результатов вычислений и др. Для микроконтроллеров

AVR компиляторы языка С (например, при обращении к подпрограммам)

могут также создавать один или более стеков программно, начиная с

верхних адресов области SRAM.

Стек действует по принципу LIFO – "Last In, First Out", что означает

"последним вошел, первым вышел". Это означает, что новые данные

вначале помещаются на вершину (первый уровень) стека, а затем, с

поступлением следующих данных, "проталкиваются" на его нижние

уровни. Извлечение из стека происходит в обратном порядке: вначале

считываются данные, помещенные последними на вершину, после чего

данные, размещенные на нижних уровнях, как бы "выталкиваются" на один

уровень вверх.

Ячейка памяти, которая является в данный момент вершиной

стека, адресуется указателем стека (для AVR – регистровой парой SPL,

SPH).

24.

Архитектура контроллеров семейства AVRК периферийным устройствам AVR-микроконтроллера относятся:

1. Порты ввода-вывода (I/O).

2. Таймеры (TIMERS).

3. Счётчики (COUNTERS).

4. Сторожевой таймер (WDT).

5. Аналоговый компаратор (AC).

6. Аналого-цифровой преобразователь (A/D CONVERTER, ADC).

7. Универсальный асинхронный (синхронно-асинхронный)

приёмопередатчик – УАПП (УСАПП) (UART или USART),

8. Последовательный периферийный интерфейс SPI.

9. Двухпроводной последовательный интерфейс I2C.

25.

Порты ввода-выводаВсе периферийные устройства адресуются через регистры

ввода-вывода (, IO registers). В архитектуре АVR, как и в других

архитектурах МК, термин «порты ввода-вывода» обозначает

параллельные порты для обмена данными с внешними устройствами.

Портов ввода-вывода в разных моделях может быть от 1 до 7.

Номинально порты 8-разрядные.

Для сокращения числа контактов корпуса в подавляющем

большинстве случаев внешние выводы, соответствующие портам,

кроме своей основной функции (двунаправленного ввода-вывода) несут

также и дополнительную, переключаются программным способом.

Выводы портов в достаточной степени автономны, и их режим может

устанавливаться независимо друг от друга. По умолчанию при

включении питания все дополнительные устройства отключены, а порты

работают на вход, причем находятся в состоянии с высоким

импедансом.

26.

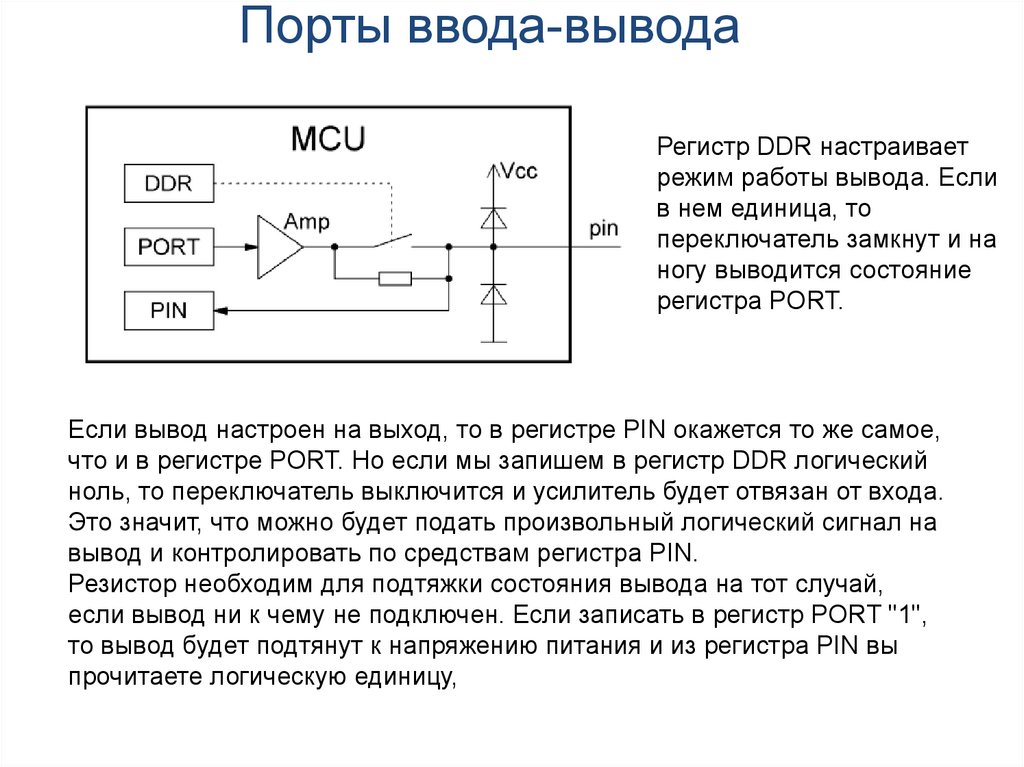

Порты ввода-выводаРегистр DDR настраивает

режим работы вывода. Если

в нем единица, то

переключатель замкнут и на

ногу выводится состояние

регистра PORT.

Если вывод настроен на выход, то в регистре PIN окажется то же самое,

что и в регистре PORT. Но если мы запишем в регистр DDR логический

ноль, то переключатель выключится и усилитель будет отвязан от входа.

Это значит, что можно будет подать произвольный логический сигнал на

вывод и контролировать по средствам регистра PIN.

Резистор необходим для подтяжки состояния вывода на тот случай,

если вывод ни к чему не подключен. Если записать в регистр PORT "1",

то вывод будет подтянут к напряжению питания и из регистра PIN вы

прочитаете логическую единицу,

27.

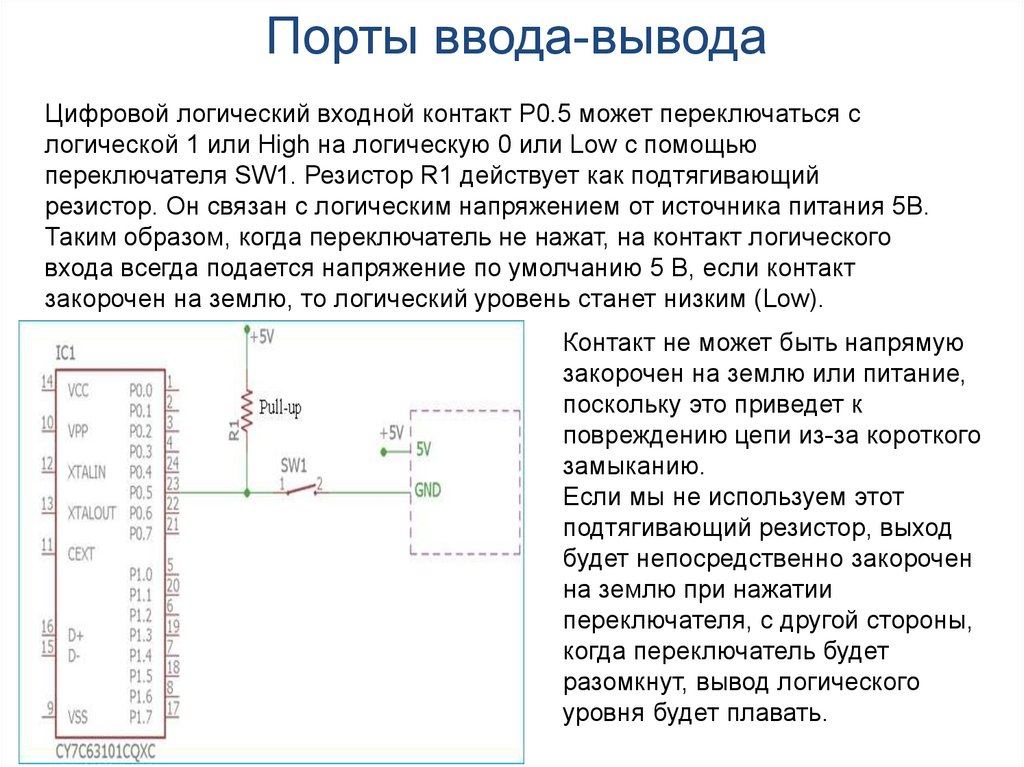

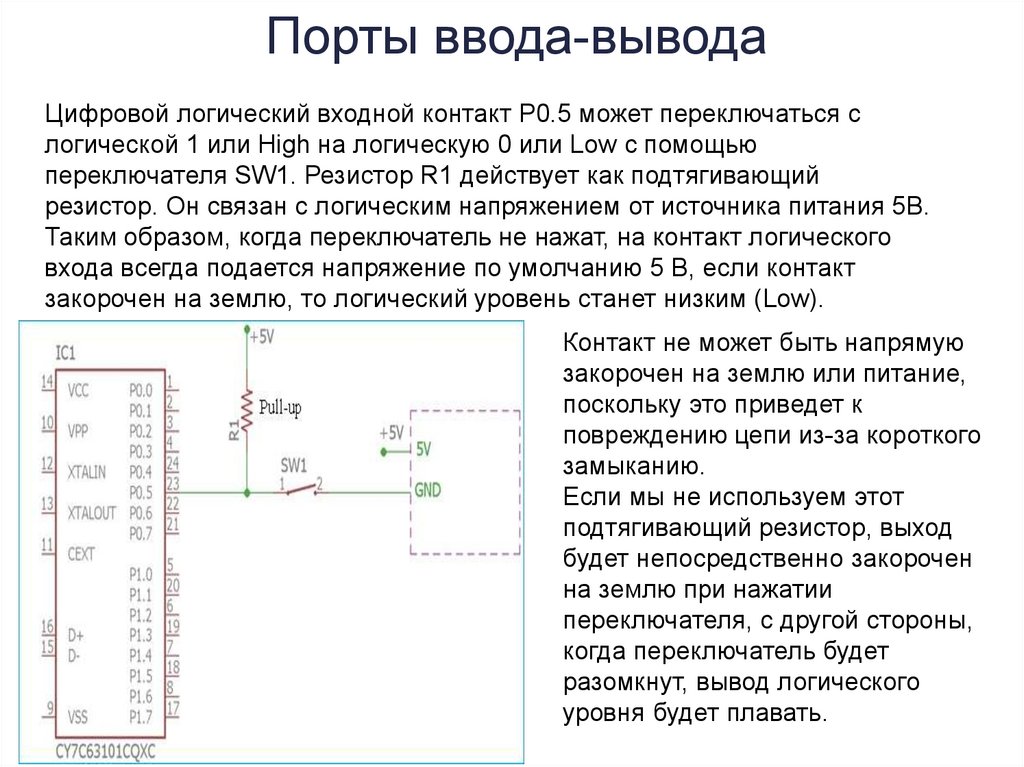

Порты ввода-выводаЦифровой логический входной контакт P0.5 может переключаться с

логической 1 или High на логическую 0 или Low с помощью

переключателя SW1. Резистор R1 действует как подтягивающий

резистор. Он связан с логическим напряжением от источника питания 5В.

Таким образом, когда переключатель не нажат, на контакт логического

входа всегда подается напряжение по умолчанию 5 В, если контакт

закорочен на землю, то логический уровень станет низким (Low).

Контакт не может быть напрямую

закорочен на землю или питание,

поскольку это приведет к

повреждению цепи из-за короткого

замыканию.

Если мы не используем этот

подтягивающий резистор, выход

будет непосредственно закорочен

на землю при нажатии

переключателя, с другой стороны,

когда переключатель будет

разомкнут, вывод логического

уровня будет плавать.

28.

Таймеры-счетчикиСчетчики предназначены для подсчета импульсов,

поступающих на отдельные входы.

Таймеры предназначены для формирования импульсов

заданной длины.

При переполнении счетчика возникает событие, которое может

вызывать соответствующее прерывание. 8-разрядный счетчик Timer0 в

большинстве случаев этой функцией и ограничивается. Счетчик Timer2,

если он имеется, может также вызывать прерывание по совпадению

подсчитанного значения с некоторой заранее заданной

величиной. 16-разрядные счетчики - более «продвинутая» штука, и

могут вызывать прерывания по совпадению с двумя независимо

заданными .числами А и В. При этом счетчики могут обнуляться или

продолжать счет, а на специальных выводах- генерироваться импульсы

(аппаратно, без участия программы).

Все счетчики-таймеры допускают работу в так называемых

режимах РWМ (ШИМ).

Кроме таймеров-счетчиков, во всех без исключения АVRконтроллерах есть сторожевой (WatchDog) таймер. Он предназначен в

основном для вывода МК из режима энергосбережения через

определенный интервал времени, но может служить и для аварийного

перезапуска МК.

29.

Таймеры-счетчикиВ принципе таймер это простой счетчик. Его достоинство в том, что он может

считать импульсы входной частоты и работать независимо от основного потока

выполнения программы. Строго заданная частота тактирования делает

возможным измерять интервалы времени в единицах периода тактов таймера.

Почему существуют разные таймеры? Ответ очень прост: для создания

подходящего таймера для разных задач нужны некоторые разные (аппаратные)

ресурсы.

Обычно в микроконтроллерах серий 90S, megaAVR и tinyAVR имеется два 8битных таймера и один 16-битный. Таймер, у которого 16-битное разрешение,

обычно более гибок в настройке и обладает расширенным функционалом в

сравнении с 8-битным таймером. Однако правило "чем больше тем лучше" не

всегда справедливо для мира микроконтроллеров, когда нужно решить

узкоспециализированную задачу. Для многих приложений достаточно 8разрядной разрешающей способности. Использование разрядности выше

означает увеличение затрат на вычисления, увеличение времени обработки, и

этого нужно пытаться избегать путем оптимизации кода по скорости. Это также

означает, что нужно применять более дорогой микроконтроллер. Гибкость

таймеров AVR позволяет приспособить их для решения различных задач.

Количество таймеров определяет количество различных конфигураций.

30.

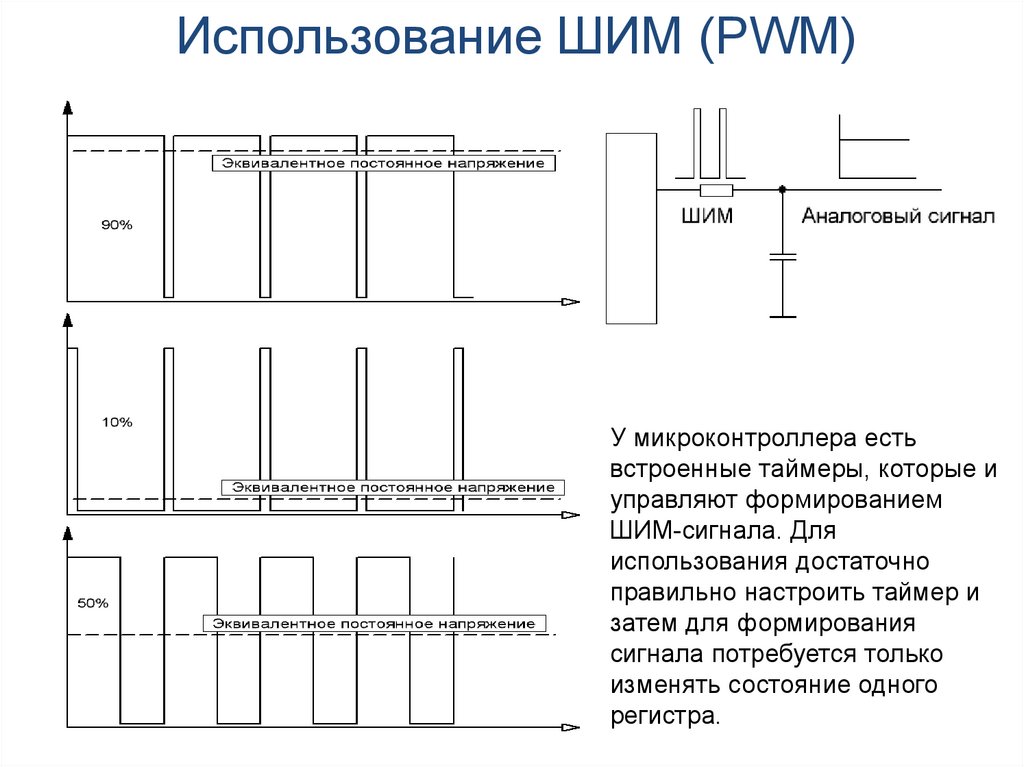

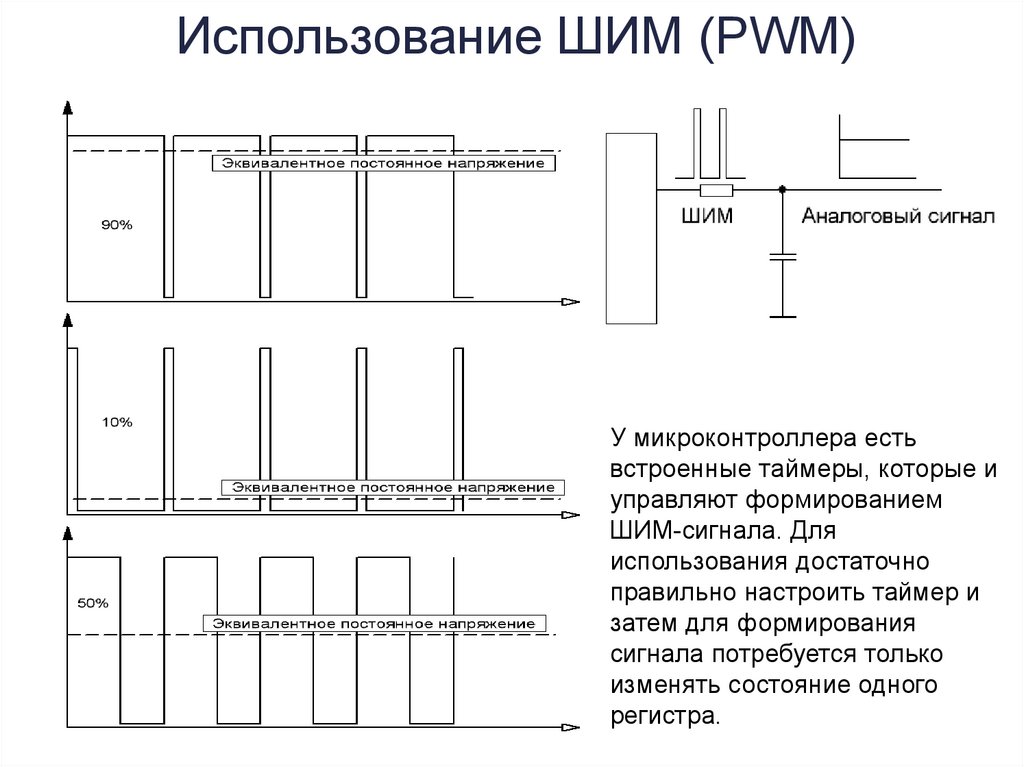

Использование ШИМ (PWM)У микроконтроллера есть

встроенные таймеры, которые и

управляют формированием

ШИМ-сигнала. Для

использования достаточно

правильно настроить таймер и

затем для формирования

сигнала потребуется только

изменять состояние одного

регистра.

31.

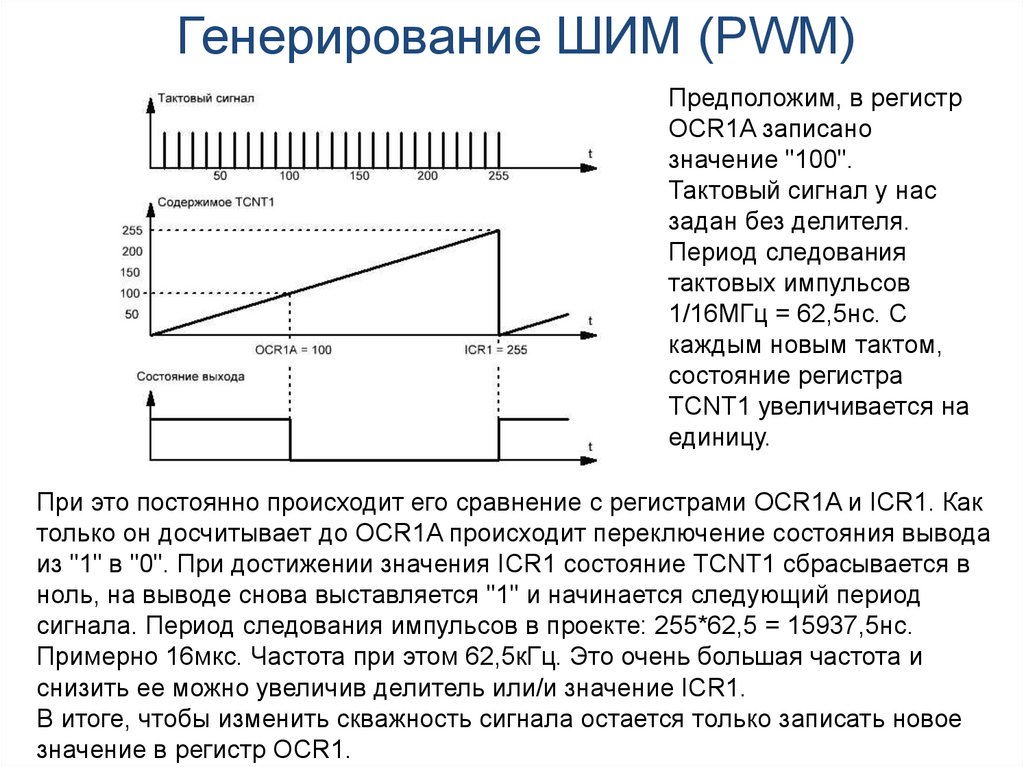

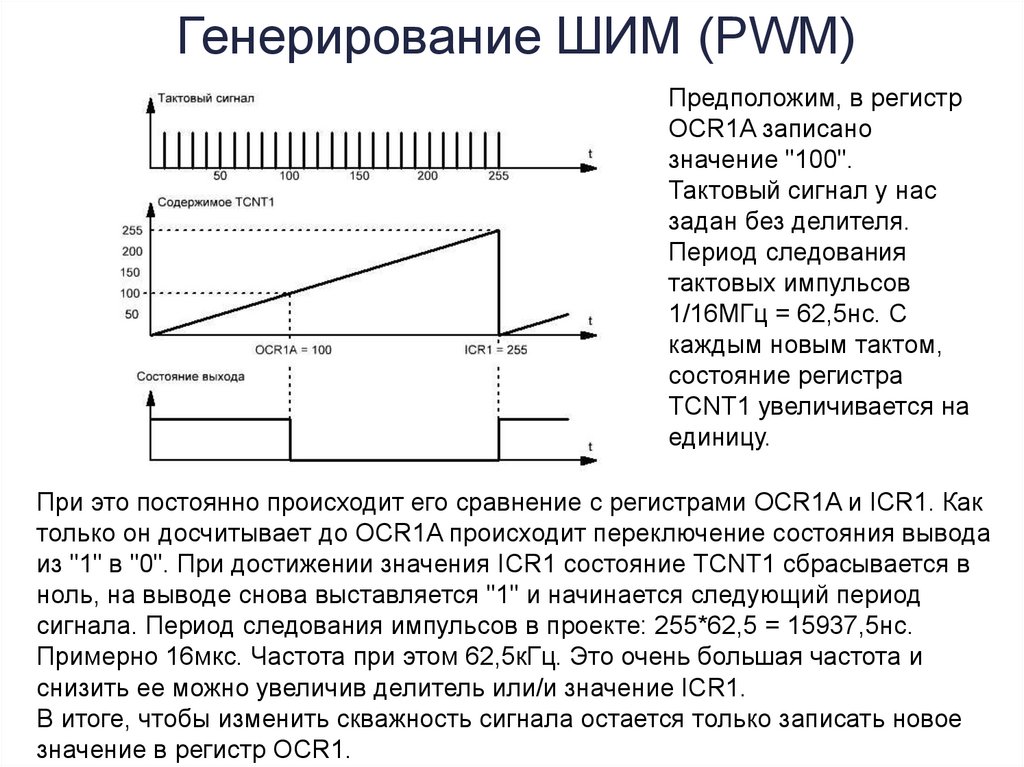

Генерирование ШИМ (PWM)Предположим, в регистр

OCR1A записано

значение "100".

Тактовый сигнал у нас

задан без делителя.

Период следования

тактовых импульсов

1/16МГц = 62,5нс. С

каждым новым тактом,

состояние регистра

TCNT1 увеличивается на

единицу.

При это постоянно происходит его сравнение с регистрами OCR1A и ICR1. Как

только он досчитывает до OCR1A происходит переключение состояния вывода

из "1" в "0". При достижении значения ICR1 состояние TCNT1 сбрасывается в

ноль, на выводе снова выставляется "1" и начинается следующий период

сигнала. Период следования импульсов в проекте: 255*62,5 = 15937,5нс.

Примерно 16мкс. Частота при этом 62,5кГц. Это очень большая частота и

снизить ее можно увеличив делитель или/и значение ICR1.

В итоге, чтобы изменить скважность сигнала остается только записать новое

значение в регистр OCR1.

32.

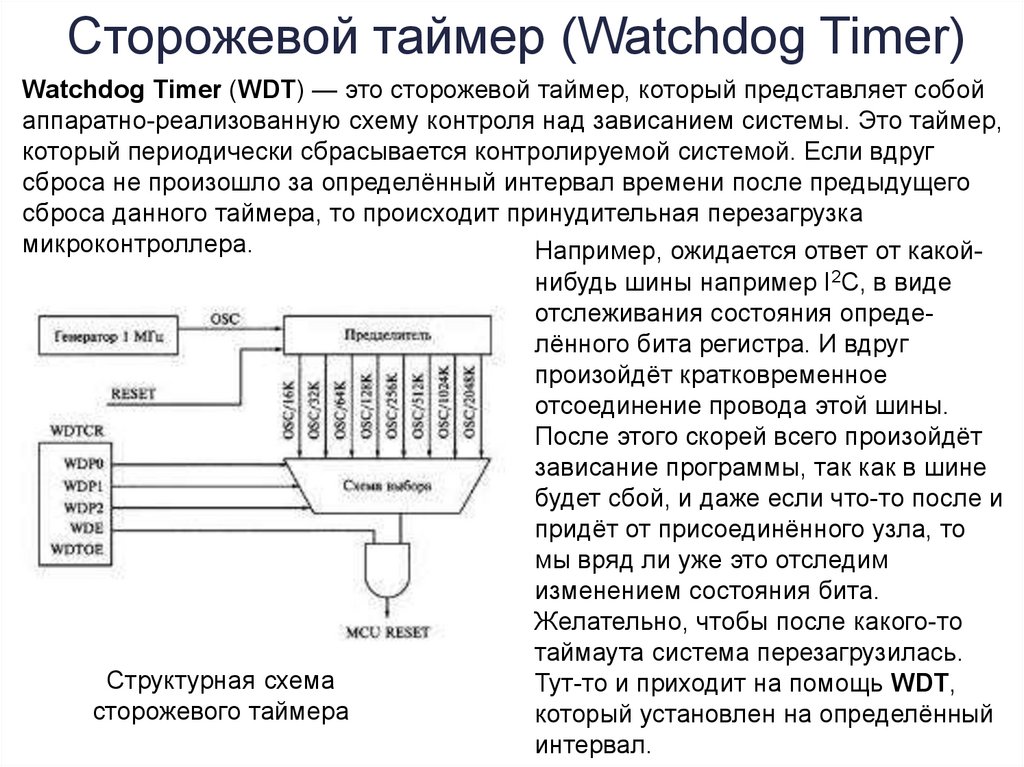

Сторожевой таймер (Watchdog Timer)Watchdog Timer (WDT) — это сторожевой таймер, который представляет собой

аппаратно-реализованную схему контроля над зависанием системы. Это таймер,

который периодически сбрасывается контролируемой системой. Если вдруг

сброса не произошло за определённый интервал времени после предыдущего

сброса данного таймера, то происходит принудительная перезагрузка

микроконтроллера.

Например, ожидается ответ от какойнибудь шины например I2C, в виде

отслеживания состояния определённого бита регистра. И вдруг

произойдёт кратковременное

отсоединение провода этой шины.

После этого скорей всего произойдёт

зависание программы, так как в шине

будет сбой, и даже если что-то после и

придёт от присоединённого узла, то

мы вряд ли уже это отследим

изменением состояния бита.

Желательно, чтобы после какого-то

таймаута система перезагрузилась.

Структурная схема

Тут-то и приходит на помощь WDT,

сторожевого таймера

который установлен на определённый

интервал.

33.

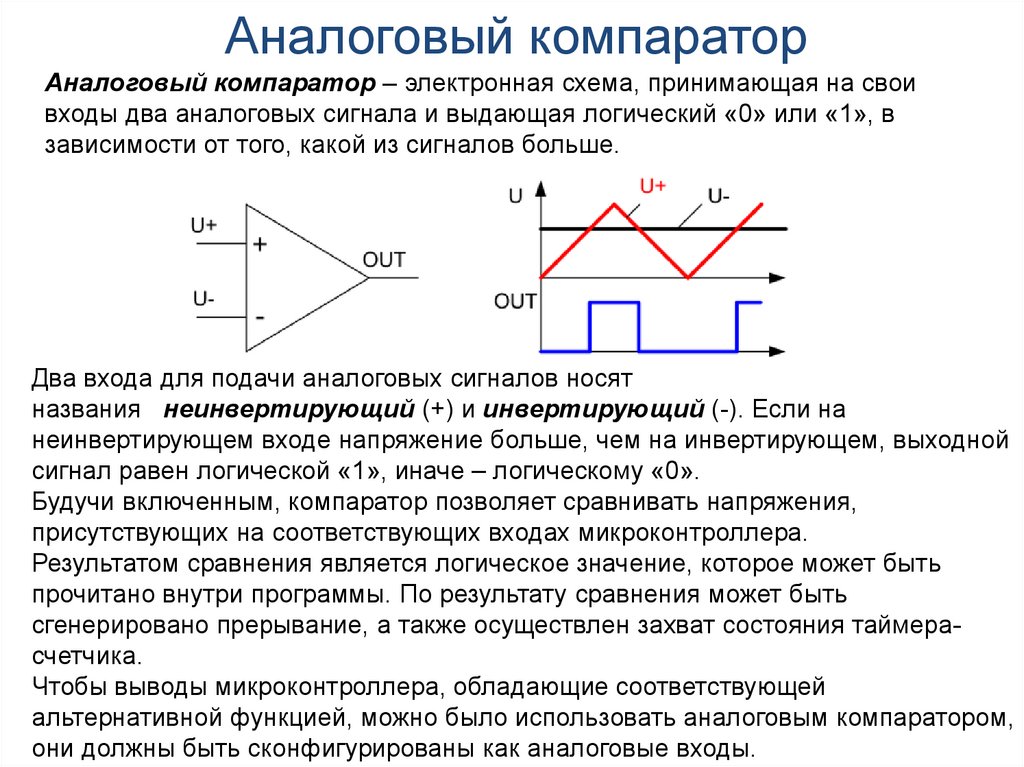

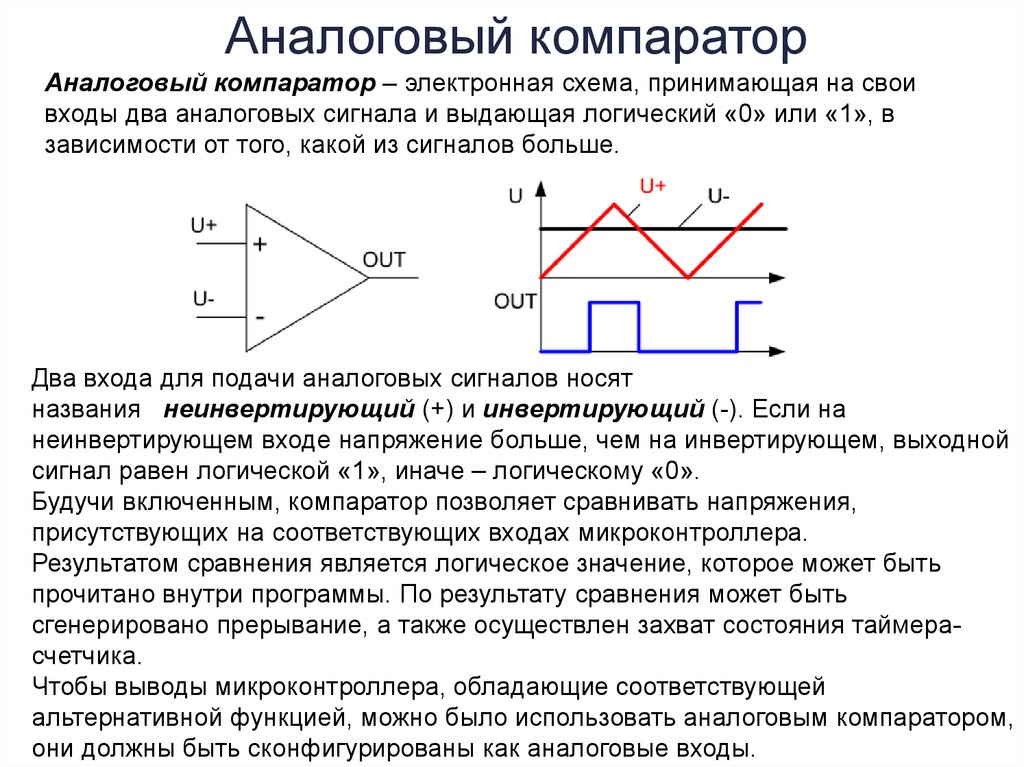

Аналоговый компараторАналоговый компаратор – электронная схема, принимающая на свои

входы два аналоговых сигнала и выдающая логический «0» или «1», в

зависимости от того, какой из сигналов больше.

Два входа для подачи аналоговых сигналов носят

названия неинвертирующий (+) и инвертирующий (-). Если на

неинвертирующем входе напряжение больше, чем на инвертирующем, выходной

сигнал равен логической «1», иначе – логическому «0».

Будучи включенным, компаратор позволяет сравнивать напряжения,

присутствующих на соответствующих входах микроконтроллера.

Результатом сравнения является логическое значение, которое может быть

прочитано внутри программы. По результату сравнения может быть

сгенерировано прерывание, а также осуществлен захват состояния таймерасчетчика.

Чтобы выводы микроконтроллера, обладающие соответствующей

альтернативной функцией, можно было использовать аналоговым компаратором,

они должны быть сконфигурированы как аналоговые входы.

34.

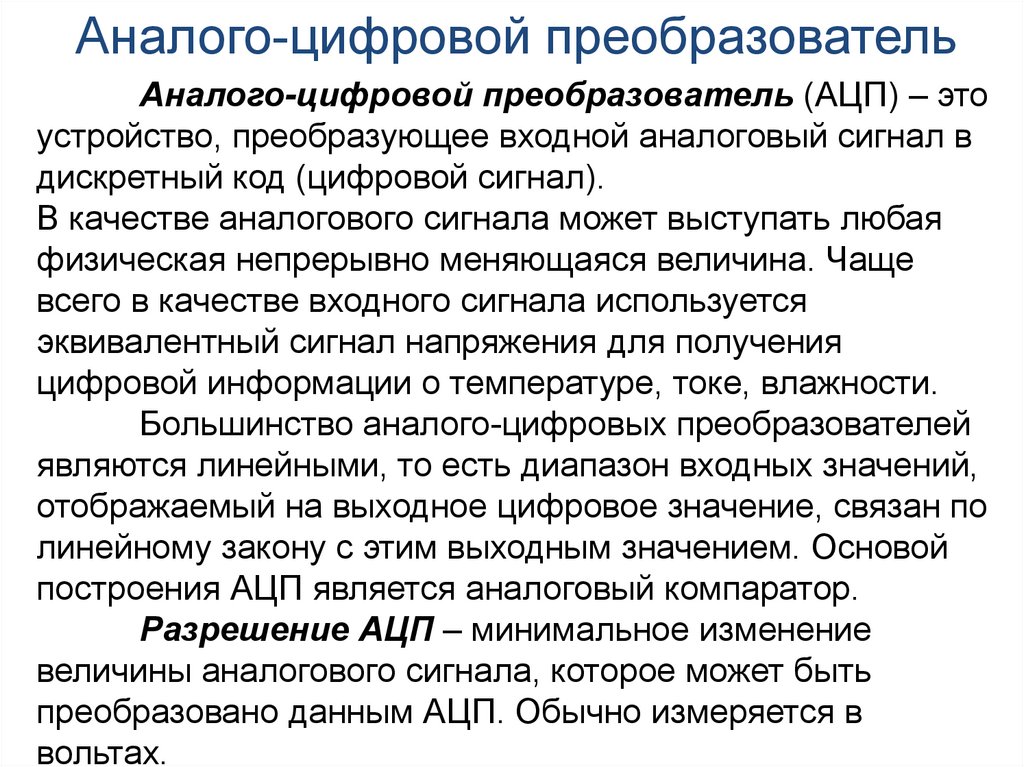

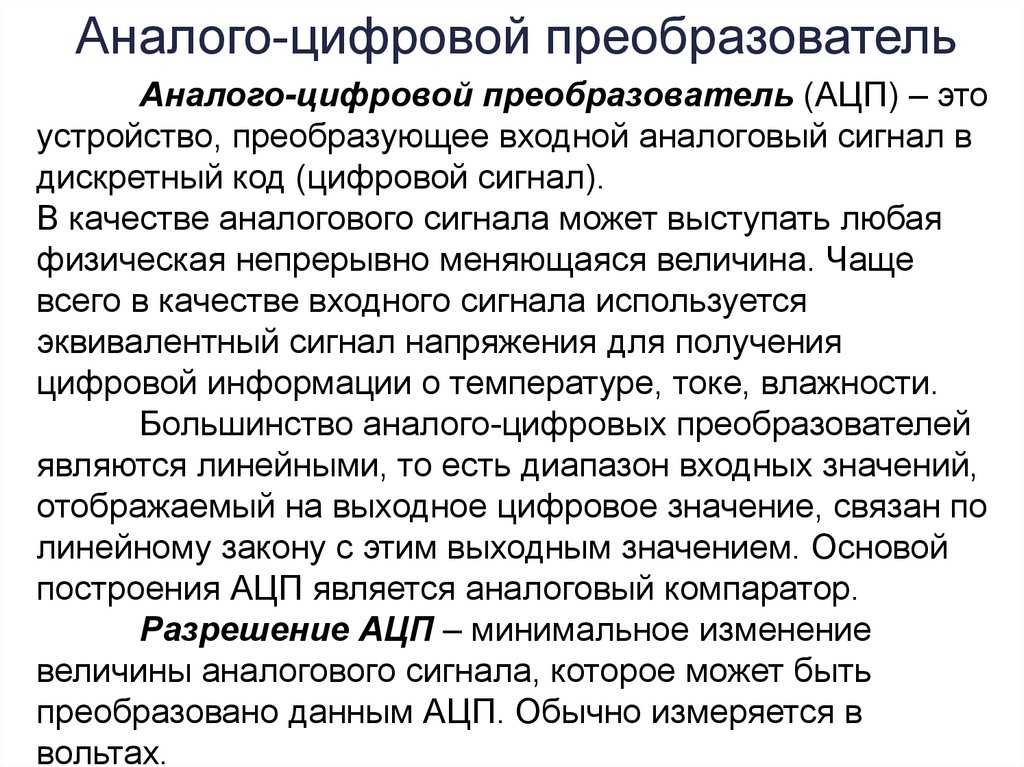

Аналого-цифровой преобразовательАналого-цифровой преобразователь (АЦП) – это

устройство, преобразующее входной аналоговый сигнал в

дискретный код (цифровой сигнал).

В качестве аналогового сигнала может выступать любая

физическая непрерывно меняющаяся величина. Чаще

всего в качестве входного сигнала используется

эквивалентный сигнал напряжения для получения

цифровой информации о температуре, токе, влажности.

Большинство аналого-цифровых преобразователей

являются линейными, то есть диапазон входных значений,

отображаемый на выходное цифровое значение, связан по

линейному закону с этим выходным значением. Основой

построения АЦП является аналоговый компаратор.

Разрешение АЦП – минимальное изменение

величины аналогового сигнала, которое может быть

преобразовано данным АЦП. Обычно измеряется в

вольтах.

35.

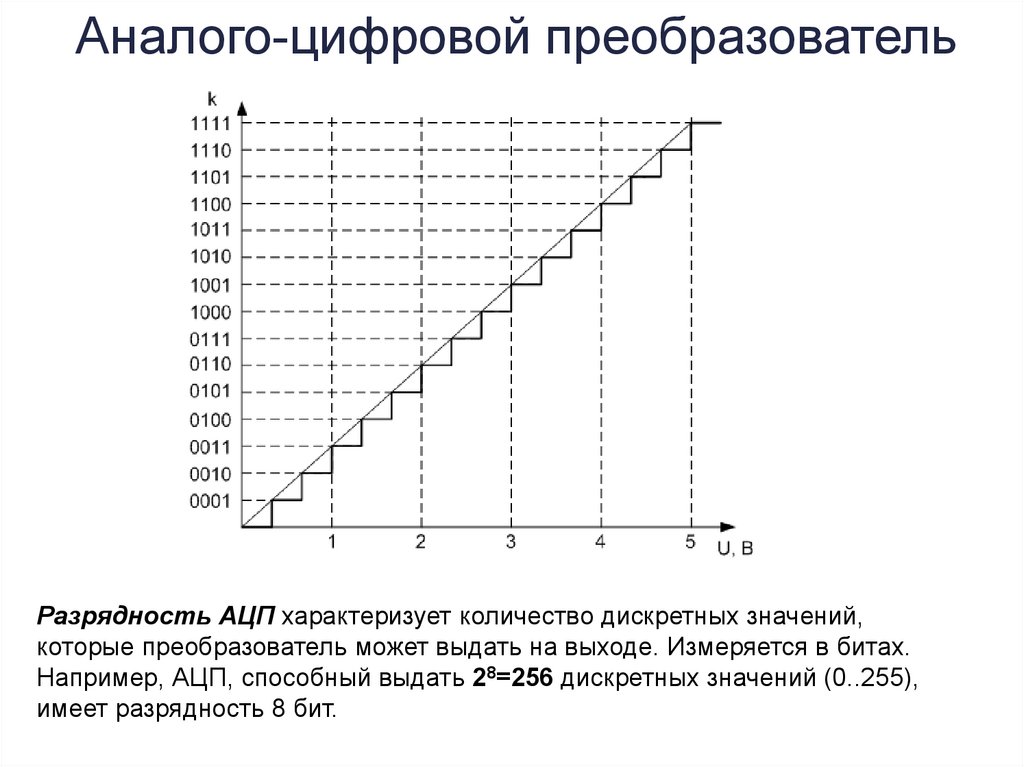

Аналого-цифровой преобразовательРазрядность АЦП характеризует количество дискретных значений,

которые преобразователь может выдать на выходе. Измеряется в битах.

Например, АЦП, способный выдать 28=256 дискретных значений (0..255),

имеет разрядность 8 бит.

36.

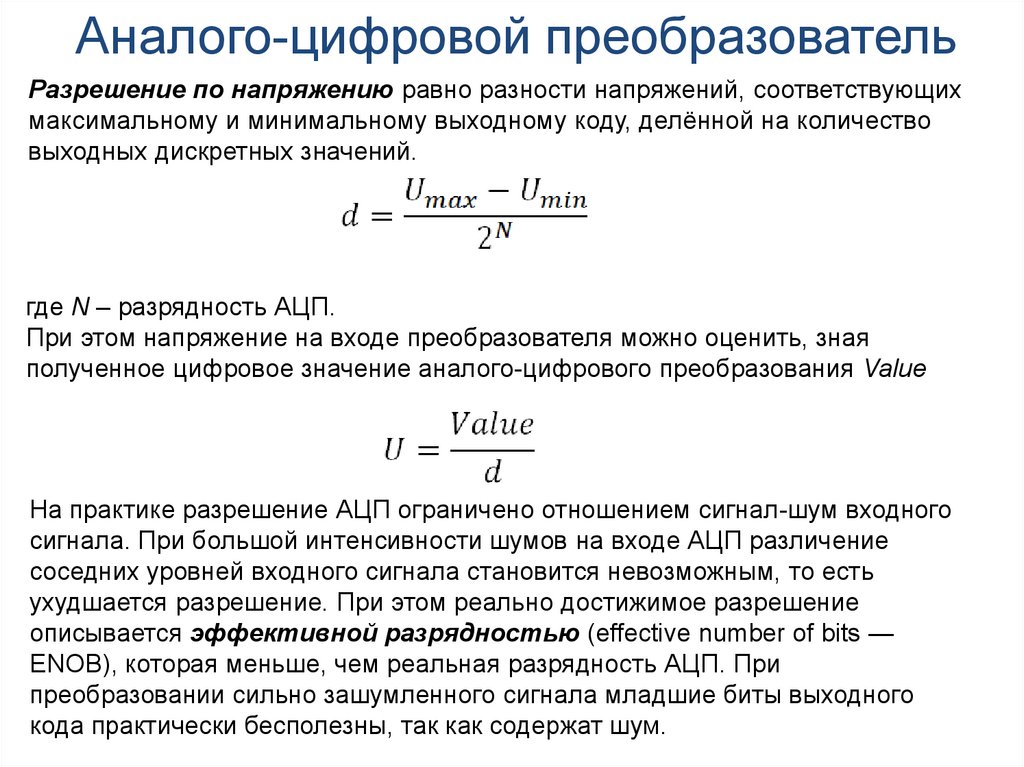

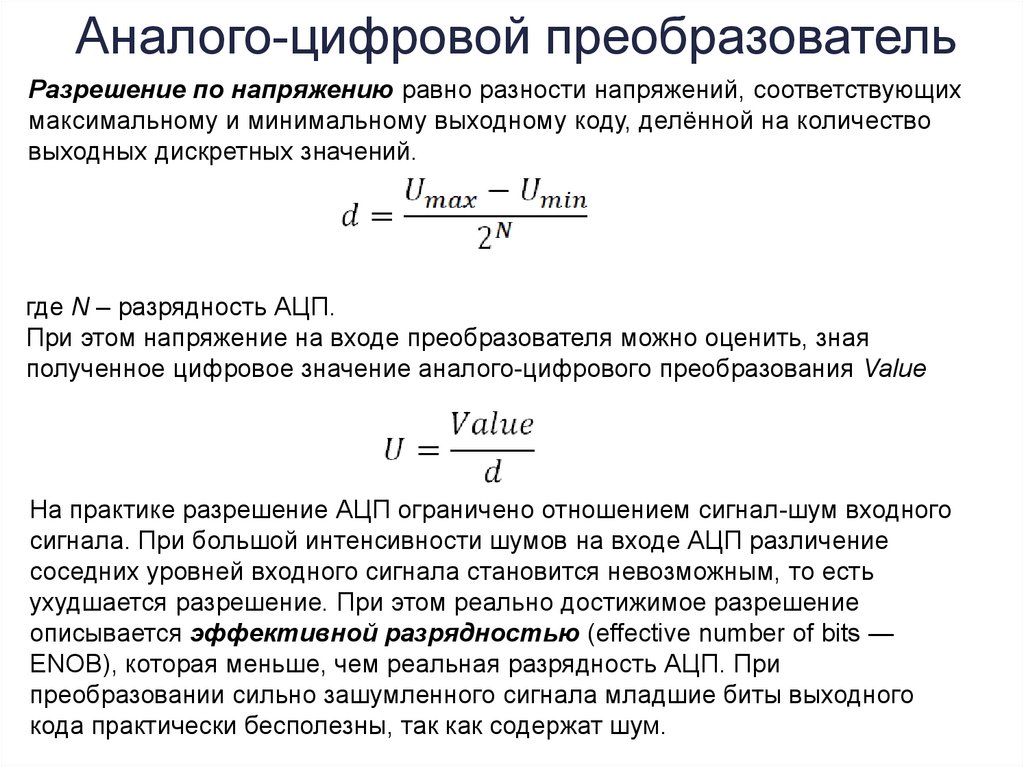

Аналого-цифровой преобразовательРазрешение по напряжению равно разности напряжений, соответствующих

максимальному и минимальному выходному коду, делённой на количество

выходных дискретных значений.

где N – разрядность АЦП.

При этом напряжение на входе преобразователя можно оценить, зная

полученное цифровое значение аналого-цифрового преобразования Value

На практике разрешение АЦП ограничено отношением сигнал-шум входного

сигнала. При большой интенсивности шумов на входе АЦП различение

соседних уровней входного сигнала становится невозможным, то есть

ухудшается разрешение. При этом реально достижимое разрешение

описывается эффективной разрядностью (effective number of bits —

ENOB), которая меньше, чем реальная разрядность АЦП. При

преобразовании сильно зашумленного сигнала младшие биты выходного

кода практически бесполезны, так как содержат шум.

37.

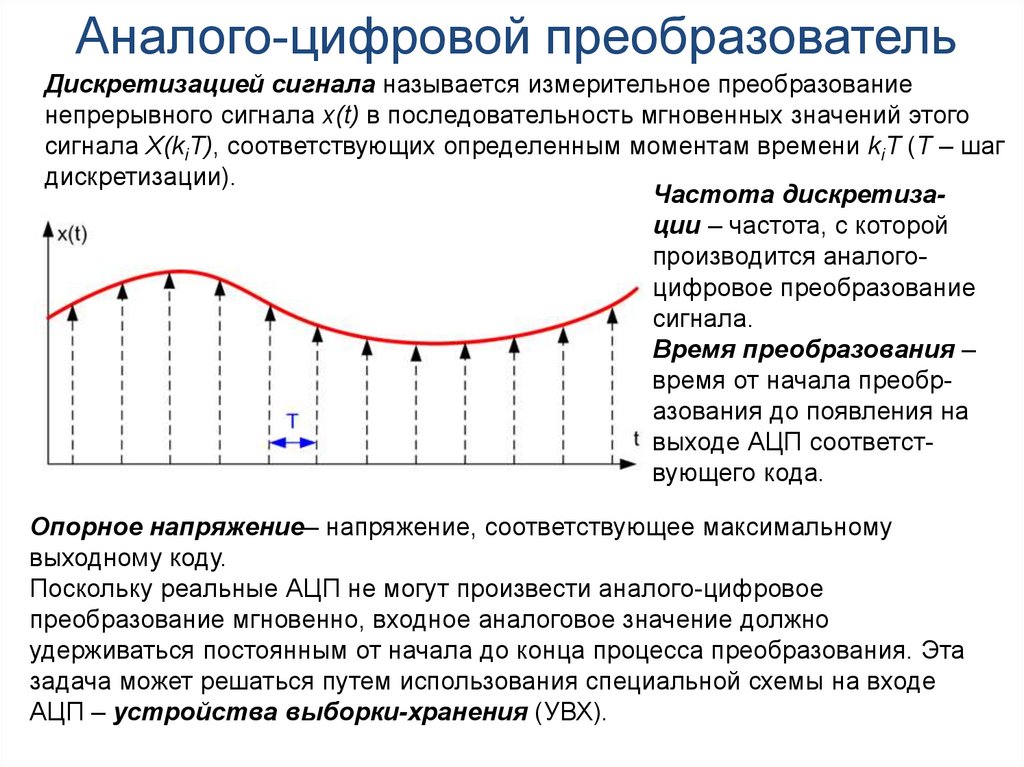

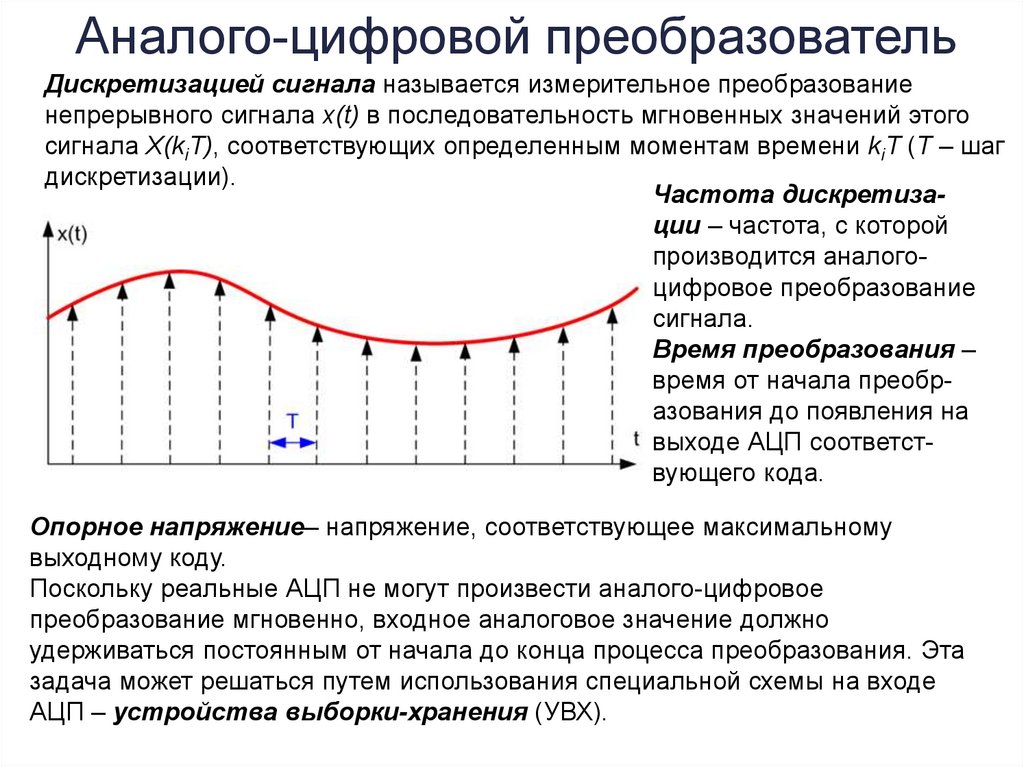

Аналого-цифровой преобразовательДискретизацией сигнала называется измерительное преобразование

непрерывного сигнала x(t) в последовательность мгновенных значений этого

сигнала X(kiT), соответствующих определенным моментам времени kiT (T – шаг

дискретизации).

Частота дискретизации – частота, с которой

производится аналогоцифровое преобразование

сигнала.

Время преобразования –

время от начала преобразования до появления на

выходе АЦП соответствующего кода.

Опорное напряжение– напряжение, соответствующее максимальному

выходному коду.

Поскольку реальные АЦП не могут произвести аналого-цифровое

преобразование мгновенно, входное аналоговое значение должно

удерживаться постоянным от начала до конца процесса преобразования. Эта

задача может решаться путем использования специальной схемы на входе

АЦП – устройства выборки-хранения (УВХ).

38.

Аналого-цифровой преобразовательАЦП входит во многие современные модели МК

АVR, и в том числе может использоваться для замены

функций более простого в обращении, но менее

функционального аналогового компаратора. АЦП в

АVR - многоканальный.

Разрешающая способность АЦП в МК АVR - 10

двоичных разрядов, чего для большинства типовых

применений достаточно (около 0,1% шкалы).

Отметим также, что АЦП может работать в двух

режимах: одиночного и непрерывного

преобразования.

39.

Последовательные портыПоследовательные порты называют так потому,

что в них в каждый момент времени передается

только один бит. Самое главное преимущество

последовательных портов перед параллельными снижение числа соединений.

В микроконтроллерных устройствах с малыми

объемами данных скорость передачи.

Практически любой последовательный порт можно

имитировать программно, используя

обычные выводы МК. Когда-то так и поступали даже в

случае самого популярного из таких портов - UART.

Однако с тех пор МК обзавелись аппаратными

последовательными портами.

40.

UART (Universal Asynchronous Receiver-Transmitter)В компьютерах есть СОМ-порт, часто ошибочно

называемый портом RS-232. Правильно сказать так:

СОМ-порт передает данные, основываясь на

стандарте последовательного интерфейса RS-232.

Последний, кроме собственно протокола

передачи, стандартизирует также и электрические

параметры, и разъемы DB-9 и DB-25. UART основная часть любого устройства, поддерживающего

RS-232, но и не только его - например, стандарты RS485 и RS-422 также реализовываются через UART, т.

к. они отличаются от RS-232 только электрическими

параметрами и допустимыми скоростями.

Кроме UART, в конкретный порт (в том числе в

СОМ-порт ПК) обычно входит схема преобразования

логических уровней в уровни соответствующего

стандарта.

41.

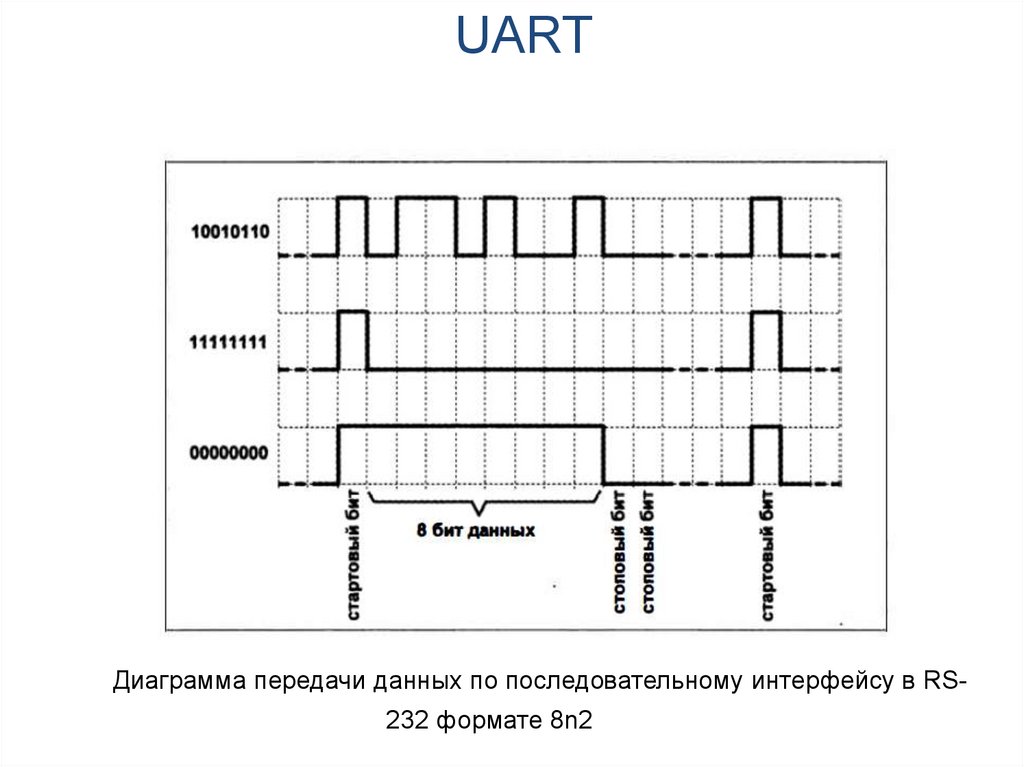

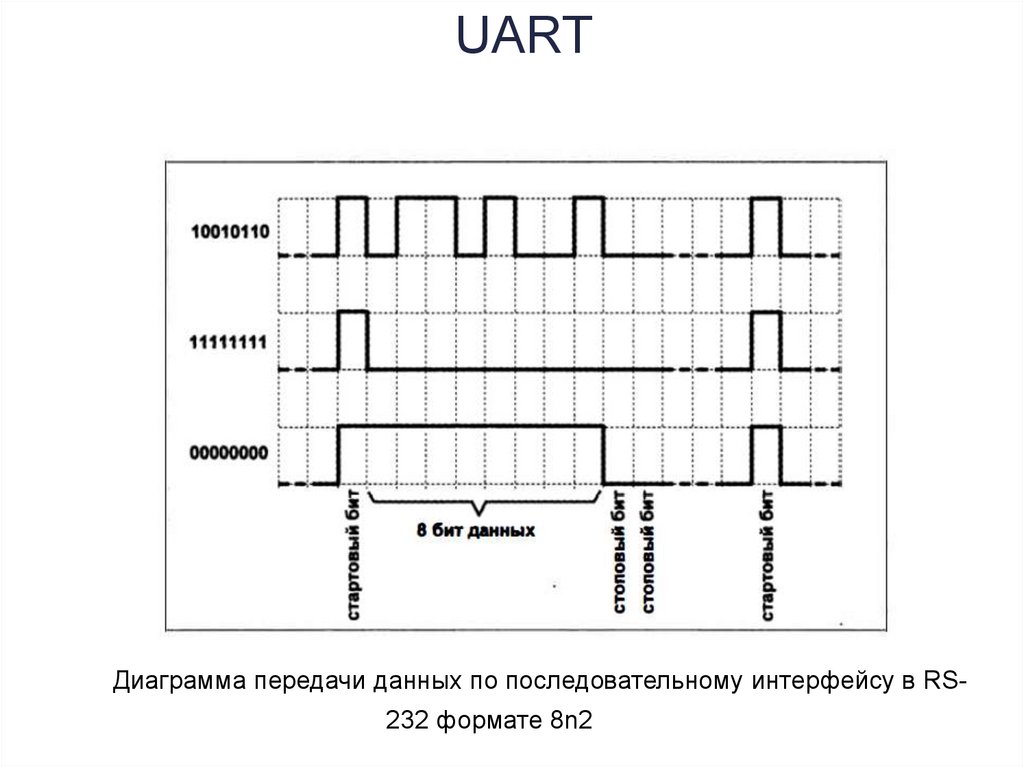

UARTДиаграмма передачи данных по последовательному интерфейсу в RS232 формате 8n2

42.

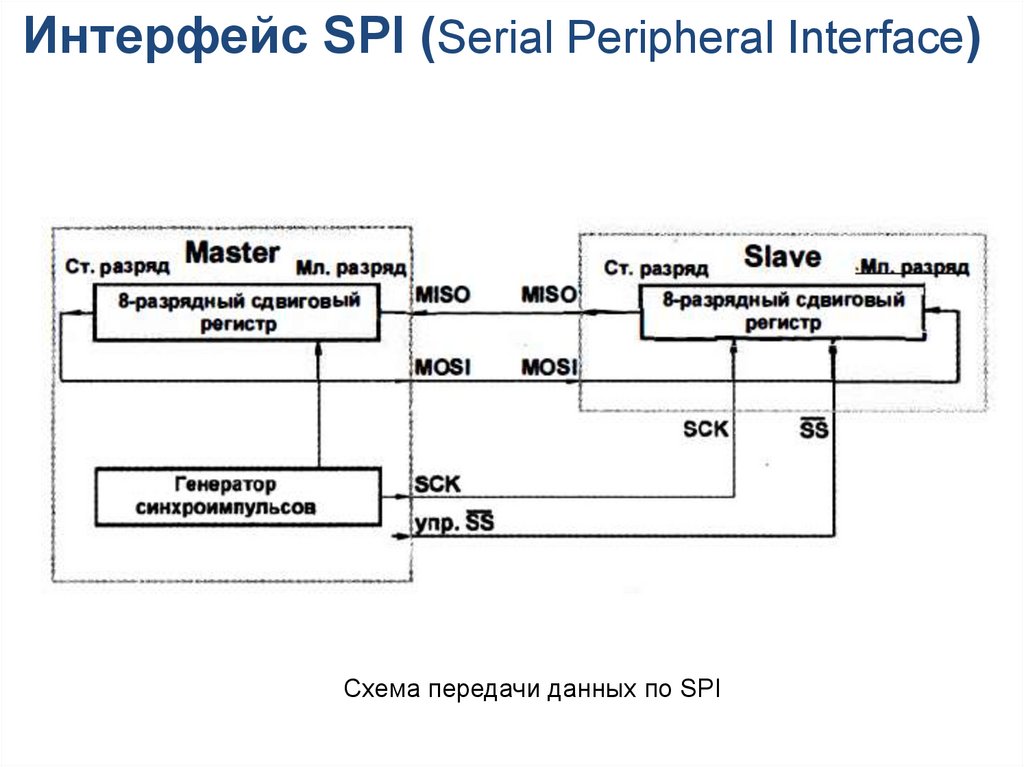

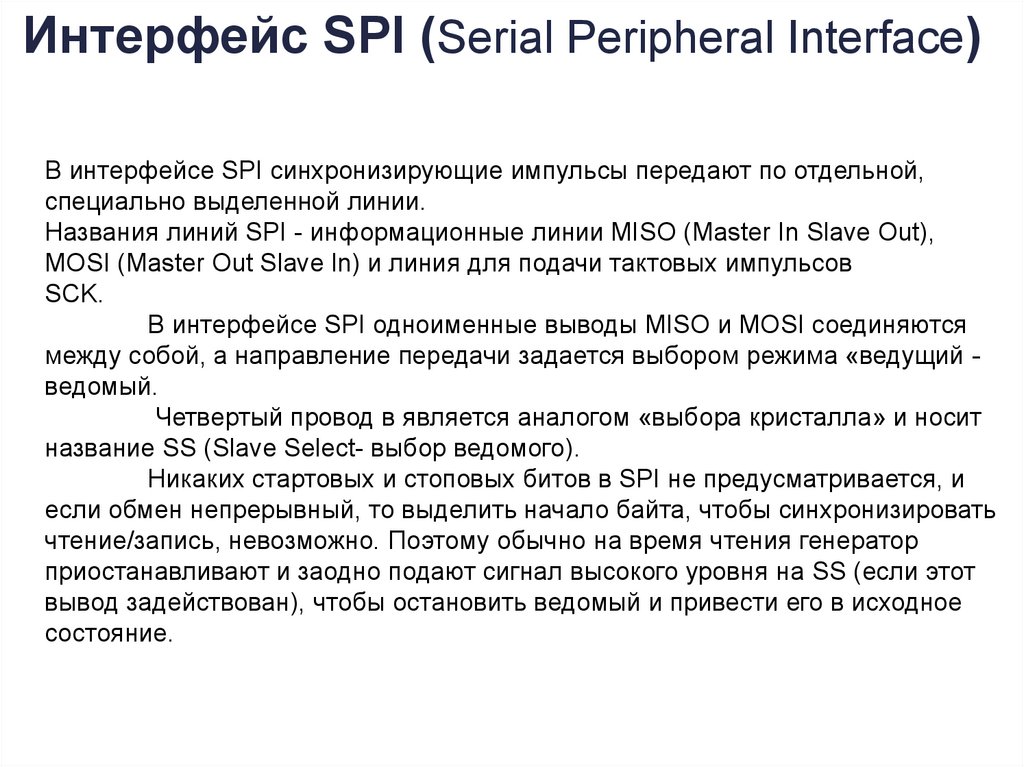

Интерфейс SPI (Serial Peripheral Interface)В интерфейсе SPI синхронизирующие импульсы передают по отдельной,

специально выделенной линии.

Названия линий SPI - информационные линии MISO (Master In Slave Out),

MOSI (Master Out Slave ln) и линия для подачи тактовых импульсов

SCK.

В интерфейсе SPI одноименные выводы MISO и MOSI соединяются

между собой, а направление передачи задается выбором режима «ведущий ведомый.

Четвертый провод в является аналогом «выбора кристалла» и носит

название SS (Slave Select- выбор ведомого).

Никаких стартовых и стоповых битов в SPI не предусматривается, и

если обмен непрерывный, то выделить начало байта, чтобы синхронизировать

чтение/запись, невозможно. Поэтому обычно на время чтения генератор

приостанавливают и заодно подают сигнал высокого уровня на SS (если этот

вывод задействован), чтобы остановить ведомый и привести его в исходное

состояние.

43.

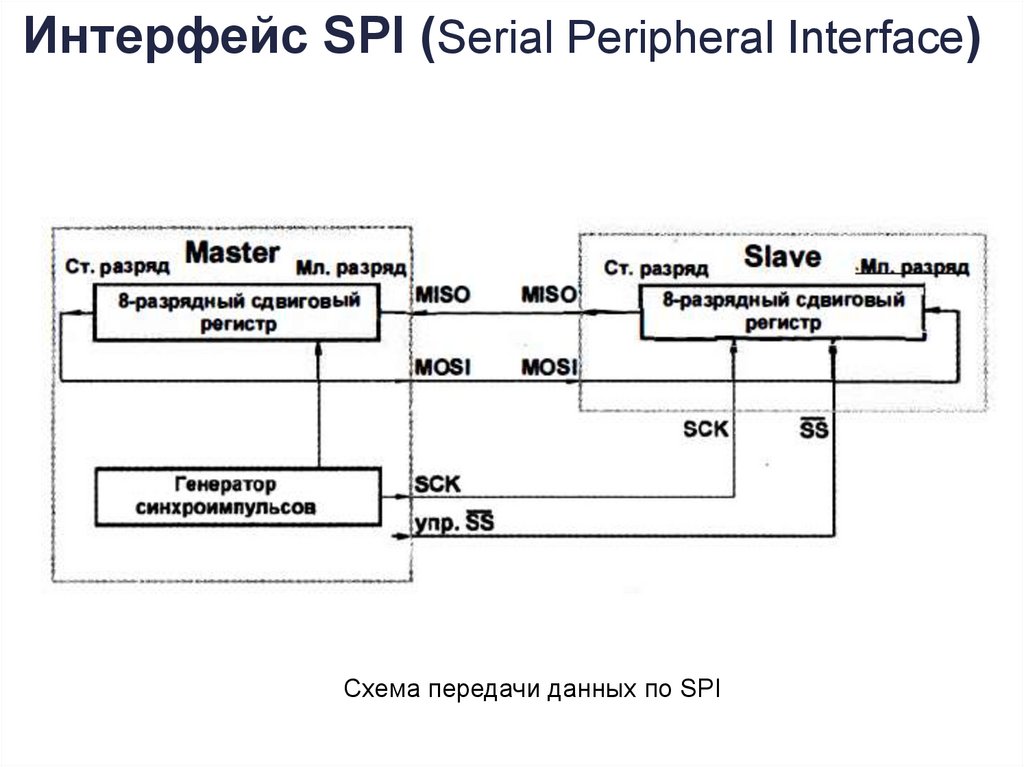

Интерфейс SPI (Serial Peripheral Interface)Схема передачи данных по SPI

44.

Интерфейс ТWI (I2С)Интерфейс I2C, требует двухпроводного соединения, но с

обязательным объединением «земель».

В интерфейсе I2С устройства могут работать в режиме

«ведущий» (Master) или «ведомый» (Slave).

В отличие от большинства других интерфейсов, ведомые

устройства с интерфейсом I2C должны иметь индивидуальный

адрес, присваиваемый производителем.

I2С, как и SPI, как правило, служит для связи между собой

микросхем на одной плате или в пределах одного устройства.

Однако это значительно более медленный интерфейс (типовое

значение скорости обмена- 100 кбит/с), и потому применяется там,

где не требуется скоростной передачи данных.

Существуют устройства (например, датчики температуры

фирмы Dallas Semiconductor, которые способны работать без

питания, получая его от сигнальных линий интерфейса I2С.

45.

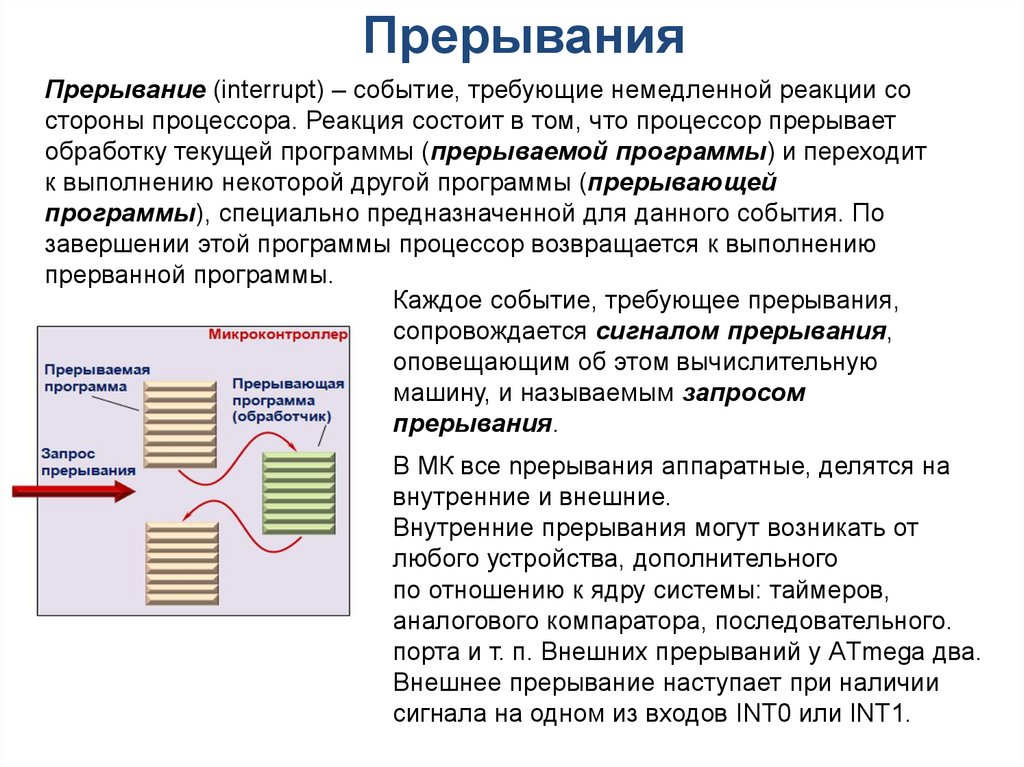

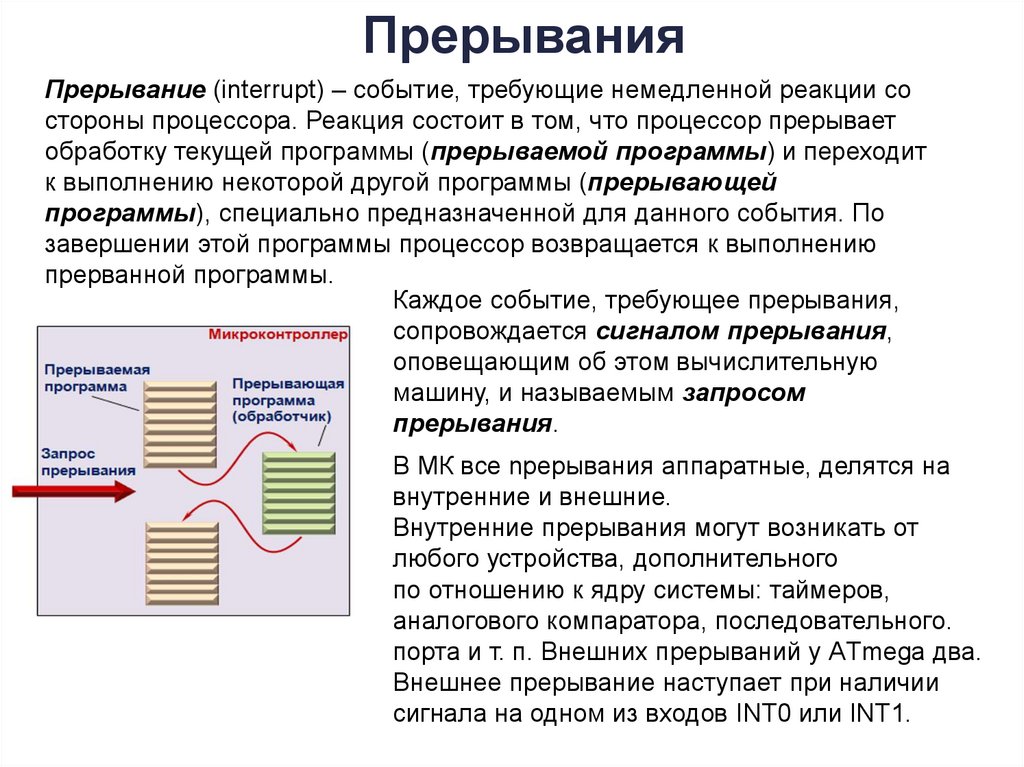

ПрерыванияПрерывание (interrupt) – событие, требующие немедленной реакции со

стороны процессора. Реакция состоит в том, что процессор прерывает

обработку текущей программы (прерываемой программы) и переходит

к выполнению некоторой другой программы (прерывающей

программы), специально предназначенной для данного события. По

завершении этой программы процессор возвращается к выполнению

прерванной программы.

Каждое событие, требующее прерывания,

сопровождается сигналом прерывания,

оповещающим об этом вычислительную

машину, и называемым запросом

прерывания.

В МК все nрерывания аппаратные, делятся на

внутренние и внешние.

Внутренние прерывания могут возникать от

любого устройства, дополнительного

по отношению к ядру системы: таймеров,

аналогового компаратора, последовательного.

порта и т. п. Внешних прерываний у АTmega два.

Внешнее прерывание наступает при наличии

сигнала на одном из входов INT0 или INТ1.

46.

ПрерыванияСостояние программы представляет собой совокупность состояний всех

запоминающих элементов после выполнения последней команды. При

возникновении прерывания микроконтроллер сохраняет в стеке содержимое

счетчика команд и загружает в него адрес соответствующего вектора

прерывания. Последней командой подпрограммы обработки прерывания

должна быть команда, которая осуществляет возврат в основную программу и

восстановление предварительно сохраненного счетчика команд. Во время

выполнения обработчика прерывания некоторая информация может

подвергнуться изменению. Поэтому при переходе к обработчику прерывания

необходимо сохранить элементы, подвергающиеся изменению. Набор таких

элементов представляет собой вектор состояния программы.

Вектор прерывания является вектором начального состояния прерывающей

программы (обработчика) и содержит всю необходимую информацию для

перехода к обработчику, в том числе его начальный адрес. Каждому типу

прерываний соответствует свой вектор прерывания, который инициализирует

выполнение соответствующего обработчика. Обычно векторы прерывания

хранятся в специально выделенных фиксированных ячейках памяти с

короткими адресами, представляющих собой таблицу векторов

прерываний. Для перехода к соответствующей прерывающей программе

процессор должен располагать вектором прерывания и адресом этого вектора.

По этому адресу, как правило, находится команда безусловного перехода к

подпрограмме обработки прерывания.

47.

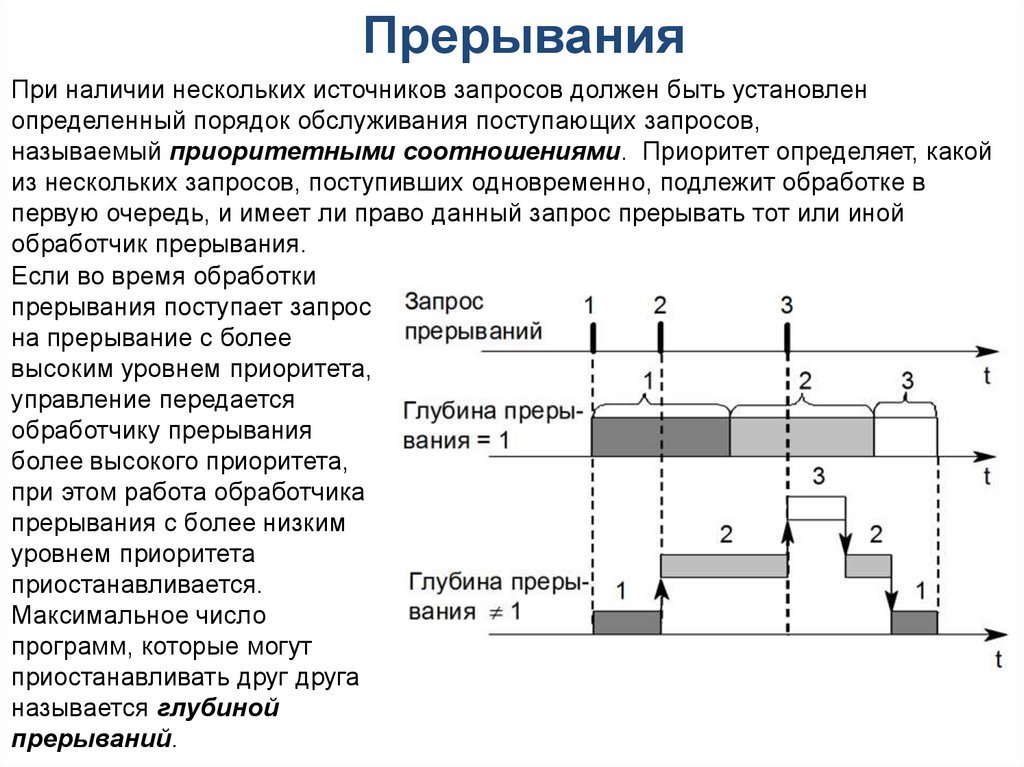

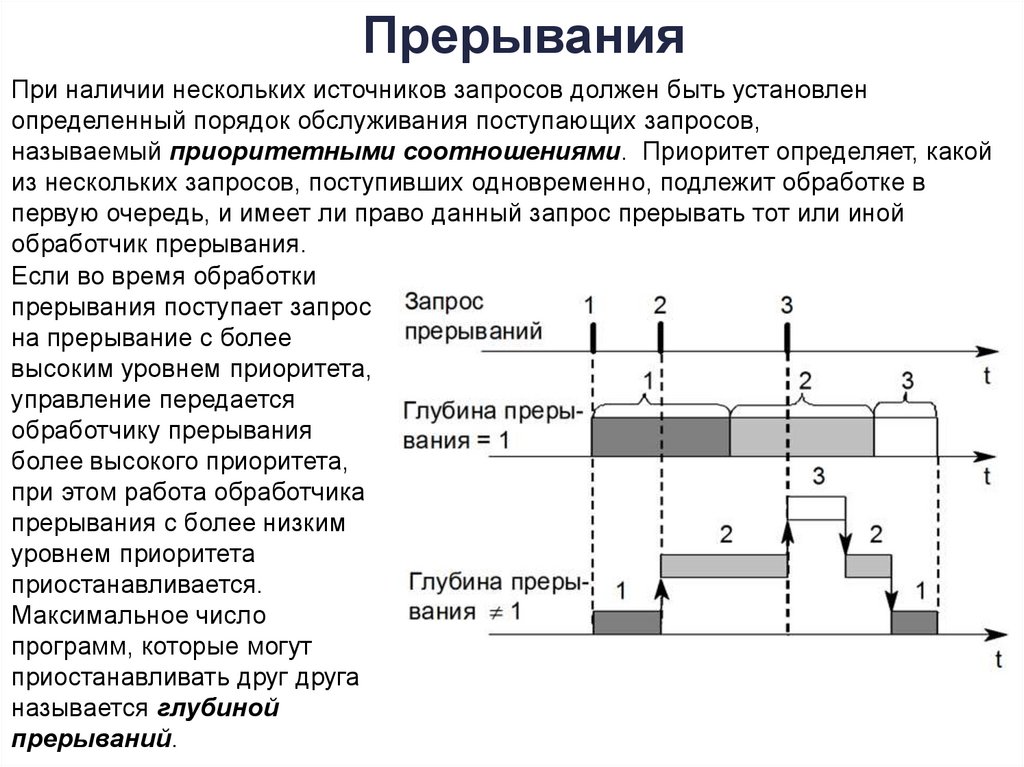

ПрерыванияПри наличии нескольких источников запросов должен быть установлен

определенный порядок обслуживания поступающих запросов,

называемый приоритетными соотношениями. Приоритет определяет, какой

из нескольких запросов, поступивших одновременно, подлежит обработке в

первую очередь, и имеет ли право данный запрос прерывать тот или иной

обработчик прерывания.

Если во время обработки

прерывания поступает запрос

на прерывание с более

высоким уровнем приоритета,

управление передается

обработчику прерывания

более высокого приоритета,

при этом работа обработчика

прерывания с более низким

уровнем приоритета

приостанавливается.

Максимальное число

программ, которые могут

приостанавливать друг друга

называется глубиной

прерываний.

48.

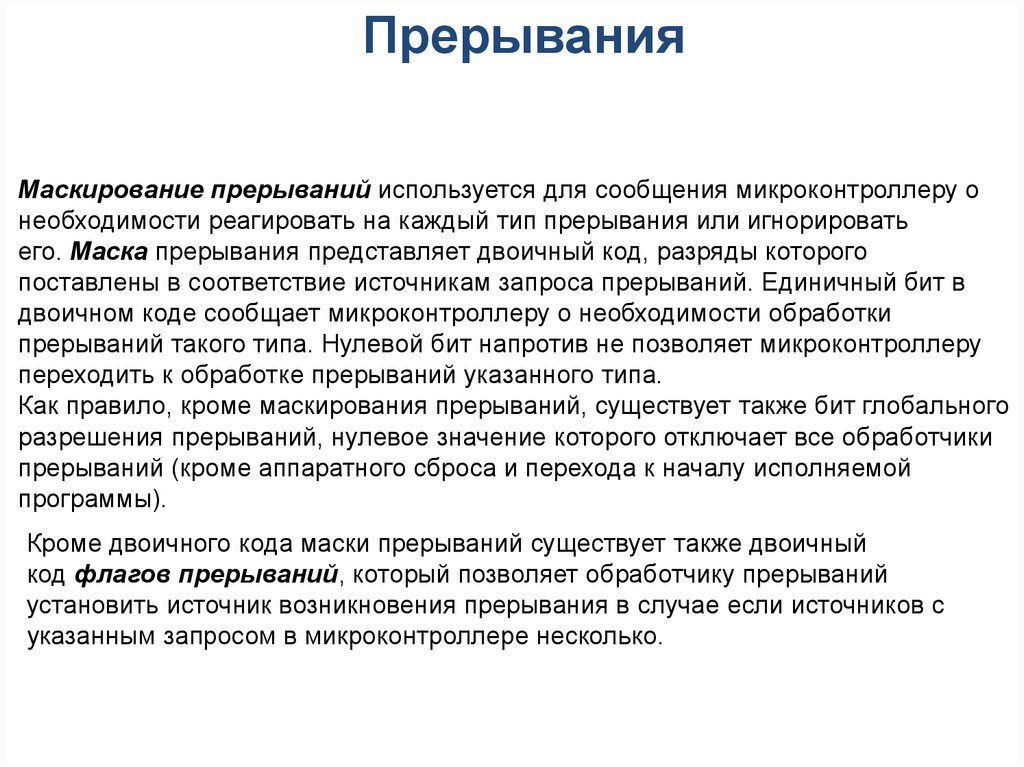

ПрерыванияМаскирование прерываний используется для сообщения микроконтроллеру о

необходимости реагировать на каждый тип прерывания или игнорировать

его. Маска прерывания представляет двоичный код, разряды которого

поставлены в соответствие источникам запроса прерываний. Единичный бит в

двоичном коде сообщает микроконтроллеру о необходимости обработки

прерываний такого типа. Нулевой бит напротив не позволяет микроконтроллеру

переходить к обработке прерываний указанного типа.

Как правило, кроме маскирования прерываний, существует также бит глобального

разрешения прерываний, нулевое значение которого отключает все обработчики

прерываний (кроме аппаратного сброса и перехода к началу исполняемой

программы).

Кроме двоичного кода маски прерываний существует также двоичный

код флагов прерываний, который позволяет обработчику прерываний

установить источник возникновения прерывания в случае если источников с

указанным запросом в микроконтроллере несколько.

49.

ПрерыванияДля надлежащего управления этим процессом флаги прерываний образуют

иерархию.

Во главе данной структуры стоит бит I регистра флагов SREG, который

разрешает (если установлен в логическую единицу) или запрещает (если

установлен в логический нуль) аппаратные прерывания вообще. Как правило,

непосредственно с этим битом (как и вообще с регистром SREG) программисту

дело можно не иметь: для общего разрешения (запрещения) прерываний

предусмотрены специальные команды sei (разрешить) и cli (запретить),

устанавливающие данный бит в нужное состояние. Отметим, что по умолчанию

бит I регистра флагов SREG сброшен, т. е. прерывания при запуске МК

запрещены. Для того чтобы их разрешить, необходимо в процедуре начальной

инициализации, выполняющейся по сбросу МК," разместить команду sei.

Кроме общего флага прерываний, для каждого конкретного прерывания имеется

свой разрешающий/запрещающий бит, расположенный в соответствующем

регистре (например, для таймеров это регистры ТIМSК или ЕТ IМSК, для

внешних прерываний- GIМSК). Для разрешения прерываний указанные биты

необходимо устанавливать в состояние логической единицы, в противном случае

автоматического вызова прерываний не произойдет.

50.

ПрерыванияОбщая схема обработки аппаратных прерываний следующая. При

возникновении любого прерывания флаг I регистра SREG аппаратно

сбрасывается, тем самым запрещая обработку других прерываний. При

нормальном течении событий он автоматически устанавливается опять, когда

обработка прерывания заканчивается (по команде reti).

После сброса флага I контроллер определяет, запрос на обработку

какого именно прерывания произошел, - это делается по флагу конкретного

прерывания, который также автоматически устанавливается при возникновении

прерывания (например, флаги для прерываний таймеров находятся в регистре

TIFR или ETIFR, для внешних прерываний- в регистре GIFR или EFI R и т.п.).

После определения типа прерывания контроллер автоматически

вычисляет адрес соответствующего вектора прерывания (векторы обычно

располагаются по начальным адресам памяти программ). На этом месте должна

располагаться команда jmp, которая содержит адрес (вектор процедурыобработчика.

Перед тем как перейти по вектору прерывания, МК сбрасывает флаг

прерывания и автоматически сохраняет содержимое счетчика команд в стеке.

Заканчиваться процедура-обработчик должна командой выхода из

прерывания reti, восстанавливающей содержимое счетчика команд и снова

устанавливающей общий флаг разрешения прерываний.

51.

Режимы энергосбережения1. IDLE MODE (режим ожидания)- режим, в котором останавливается GPU (а

также устройство управления выборкой команд из памяти). Все периферийные

устройства(таймеры, АЦП, порты) продолжают функционировать. Поэтому

значительной экономии не получается: потребление снижается лишь на 30-50%.

Очевидно, что режим Idle целесообразен, когда общее потребление устройства

лимитирует именно МК, который при этом обязательно должен находиться в

состоянии постоянной готовности. Во всех остальных случаях следует выбирать

режимы «глубокого» энергосбережения, когда собственное потребление МК

снижается до единиц или десятков микроампер.

2.POWER DOWN MODE - режим, общий для всех моделей МК. В нем

останавливаются все узлы МК, за исключением сторожевого таймера, системы

обработки внешних асинхронных прерываний и модуля ·тw1. Соответственно,

выход из данного режима возможен либо по сбросу МК (в том числе и от

сторожевого таймера), либо от прерывания TWI, либо от внешнего прерывания.

Важная особенность Power Down mode - остановка тактового генератора.

3. POWER SAVE MODE - таймер продолжит работу и в этом режиме.

Практически используется при реализации часов реального времени.

4. STANDBY MODE - отличается от Power Down тем, что в этом режиме

продолжает работать тактовый генератор (только при установке внешнего

резонатора). Режим полезен тем, что позволяет выходить из «спящего»

состояния всего за 6 тактов.

52.

Программная модель AVRмикроконтроллеров53.

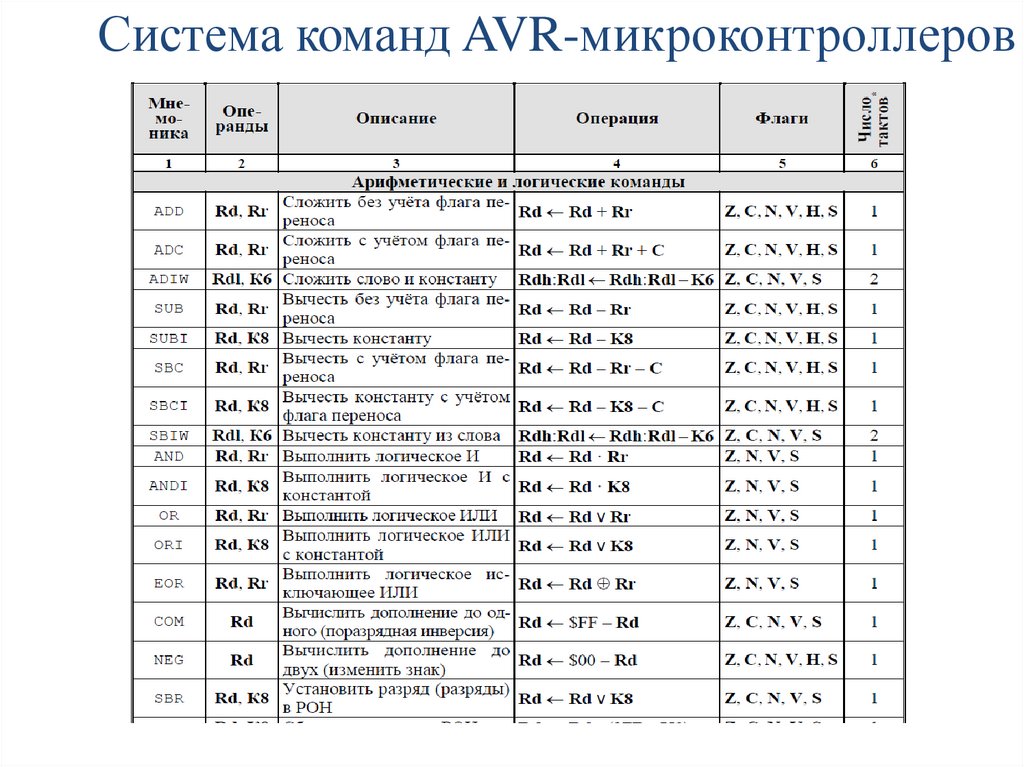

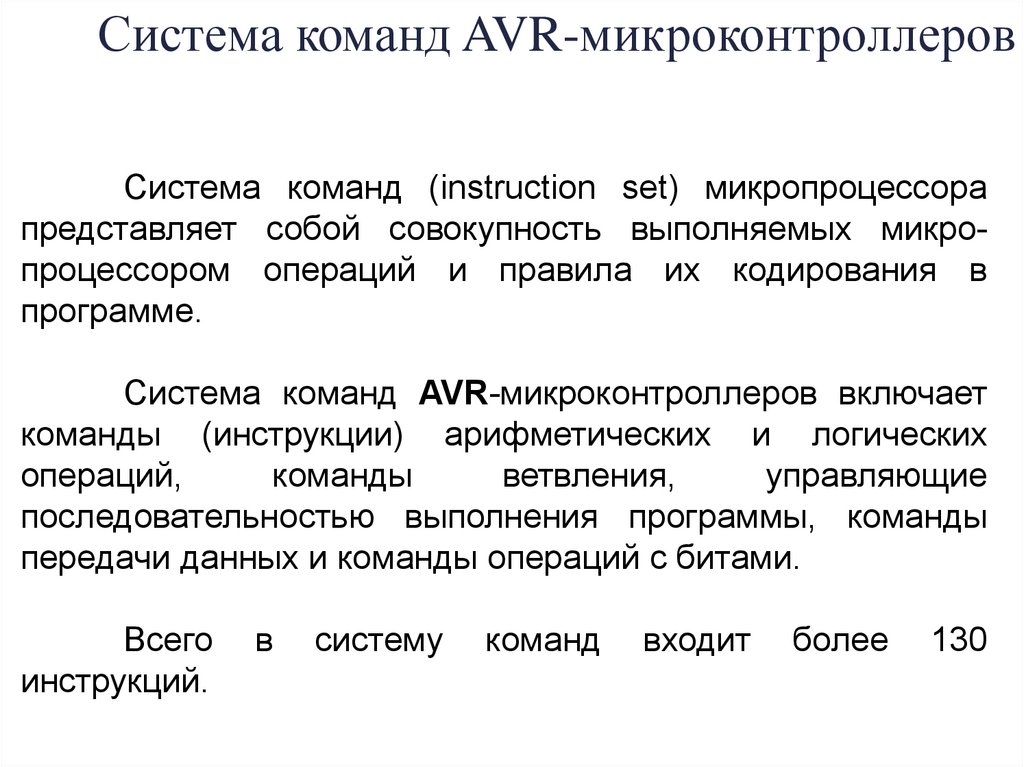

Система команд AVR-микроконтроллеровСистема команд (instruction set) микропроцессора

представляет собой совокупность выполняемых микропроцессором операций и правила их кодирования в

программе.

Система команд AVR-микроконтроллеров включает

команды (инструкции) арифметических и логических

операций,

команды

ветвления,

управляющие

последовательностью выполнения программы, команды

передачи данных и команды операций с битами.

Всего

инструкций.

в

систему

команд

входит

более

130

54.

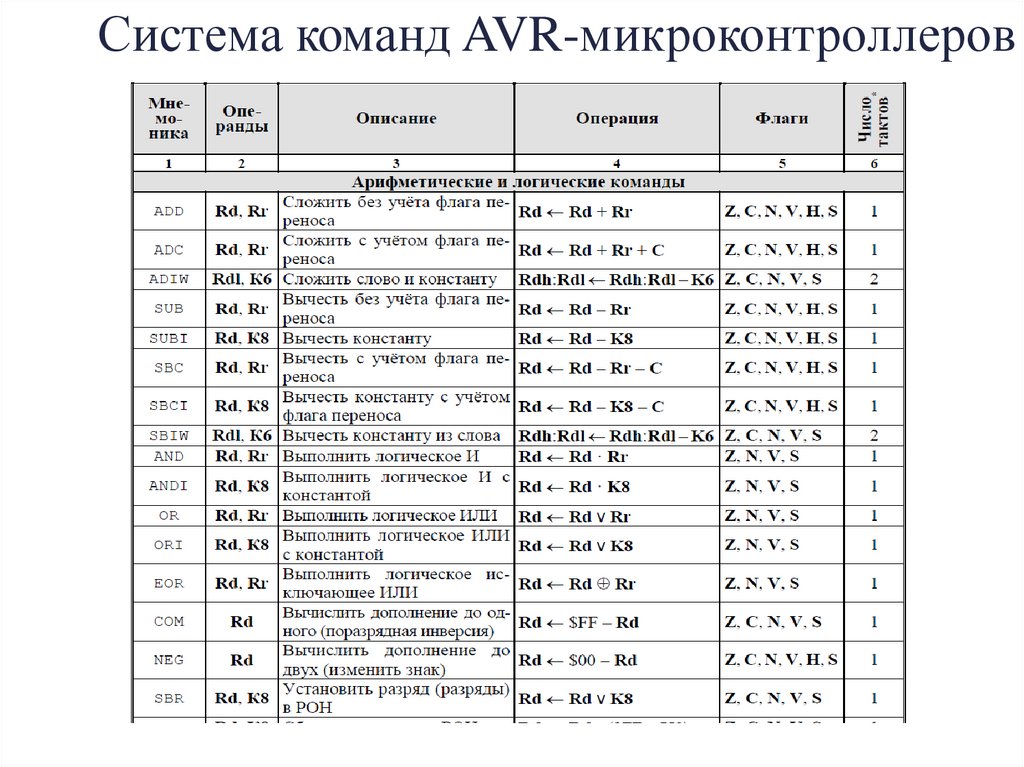

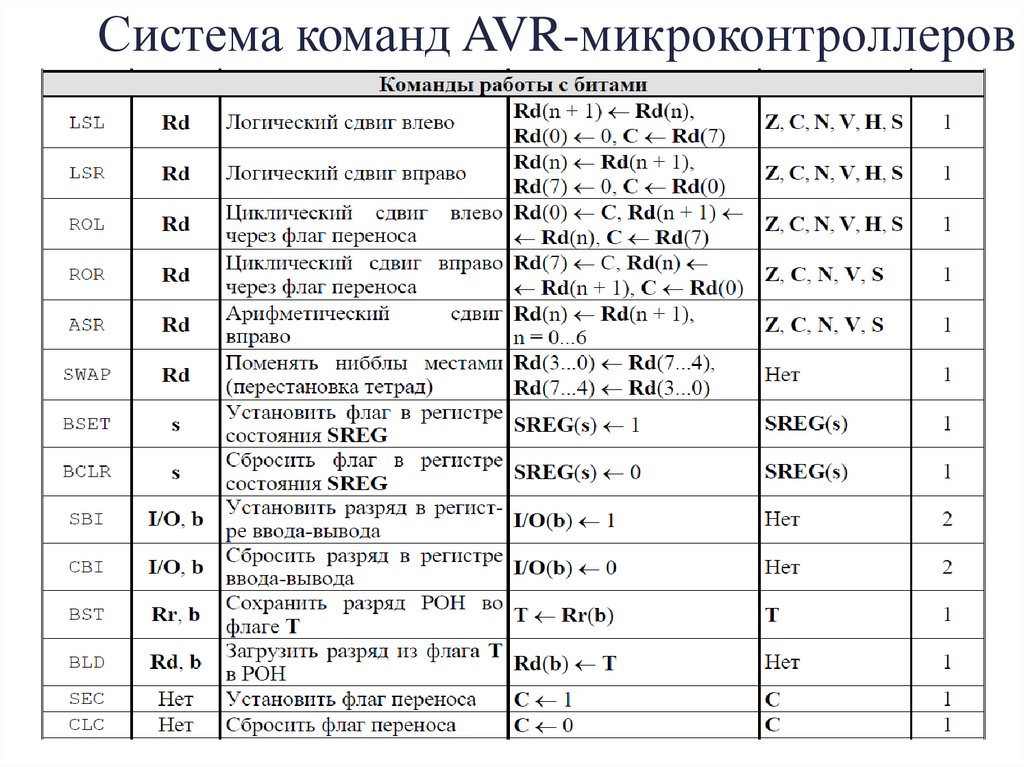

Система команд AVR-микроконтроллеров55.

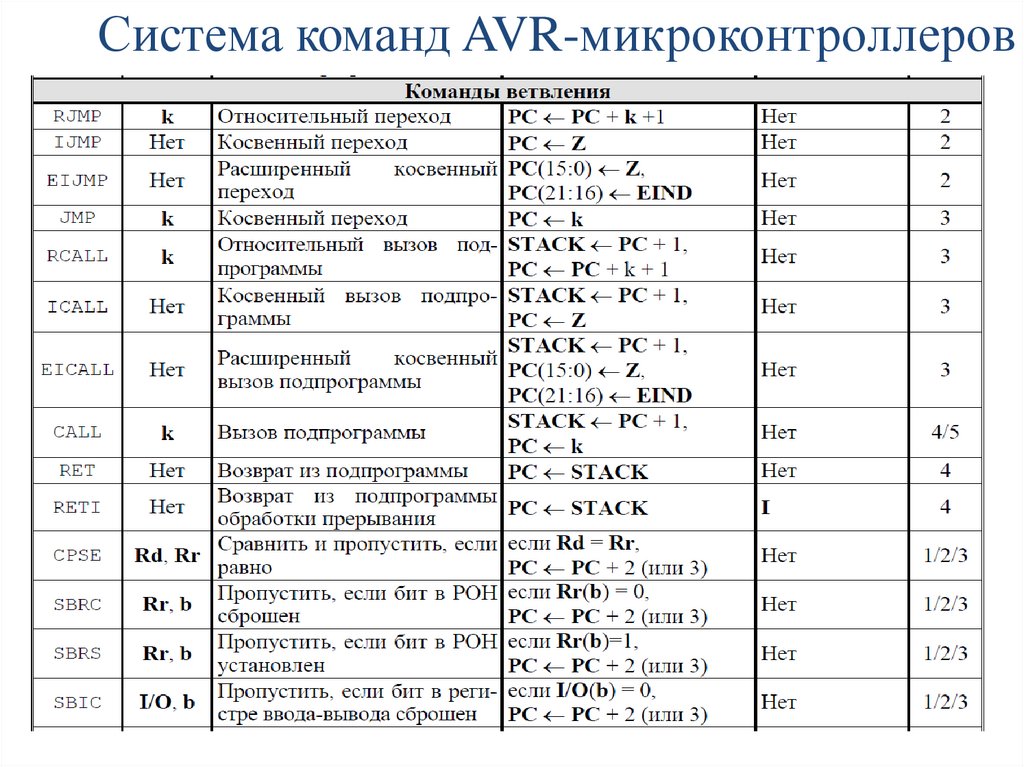

Система команд AVR-микроконтроллеров56.

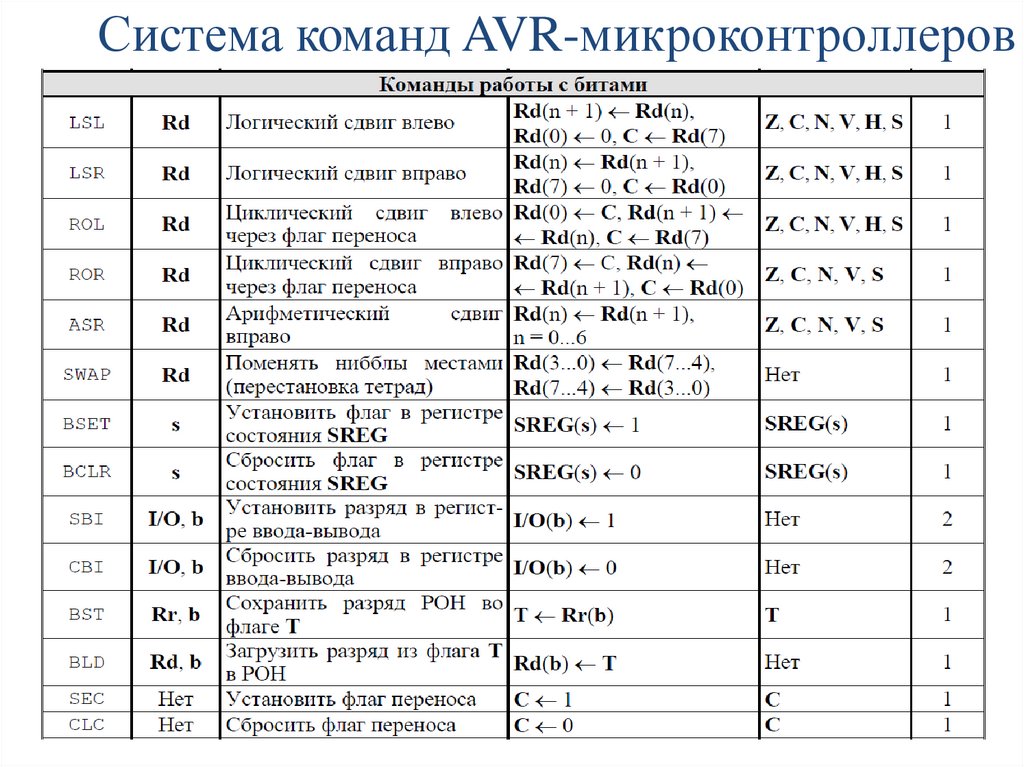

Система команд AVR-микроконтроллеров57.

Система команд AVR-микроконтроллеров58.

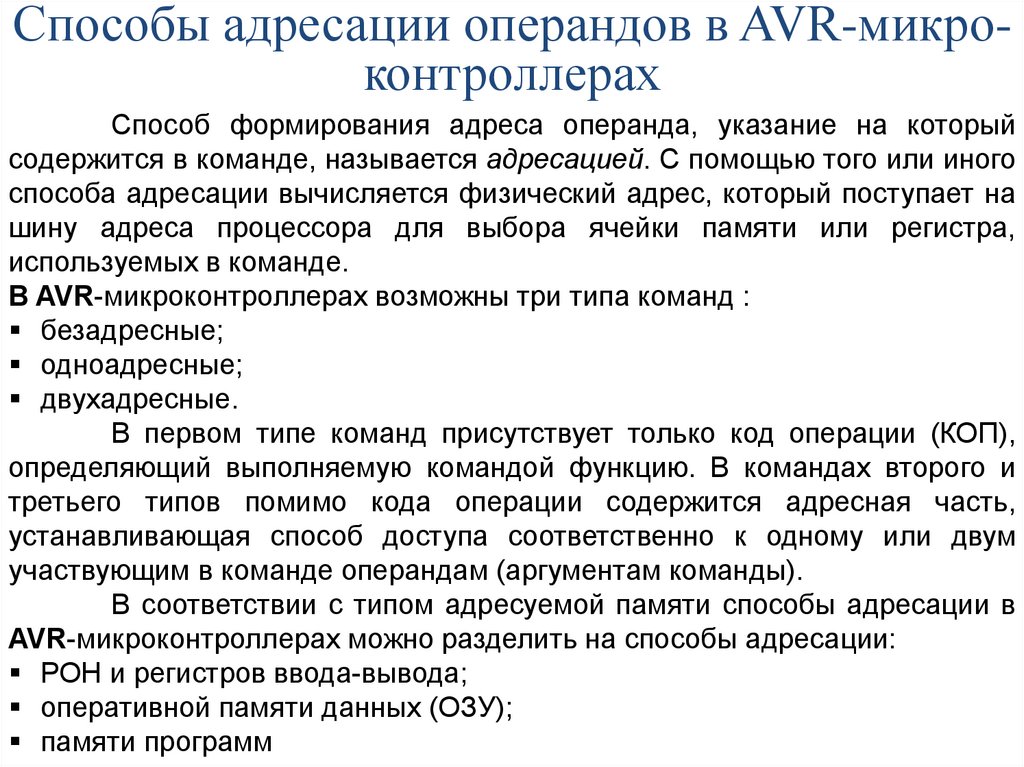

Способы адресации операндов в AVR-микроконтроллерахСпособ формирования адреса операнда, указание на который

содержится в команде, называется адресацией. С помощью того или иного

способа адресации вычисляется физический адрес, который поступает на

шину адреса процессора для выбора ячейки памяти или регистра,

используемых в команде.

В AVR-микроконтроллерах возможны три типа команд :

безадресные;

одноадресные;

двухадресные.

В первом типе команд присутствует только код операции (КОП),

определяющий выполняемую командой функцию. В командах второго и

третьего типов помимо кода операции содержится адресная часть,

устанавливающая способ доступа соответственно к одному или двум

участвующим в команде операндам (аргументам команды).

В соответствии с типом адресуемой памяти способы адресации в

AVR-микроконтроллерах можно разделить на способы адресации:

РОН и регистров ввода-вывода;

оперативной памяти данных (ОЗУ);

памяти программ

59.

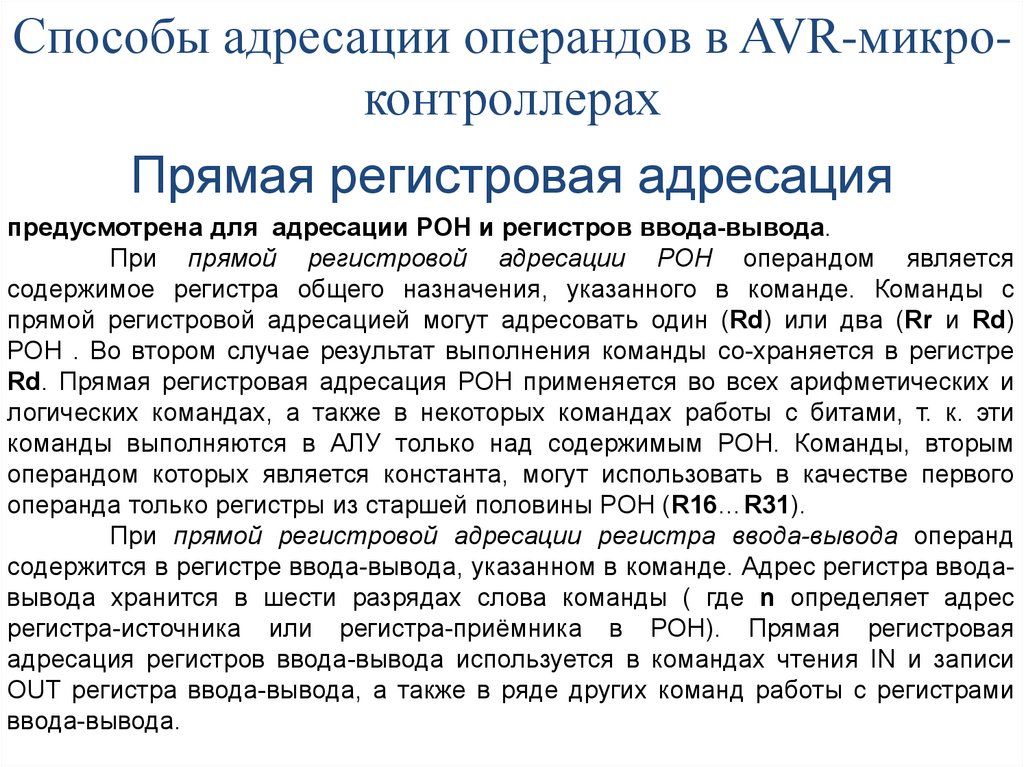

Способы адресации операндов в AVR-микроконтроллерахПрямая регистровая адресация

предусмотрена для адресации РОН и регистров ввода-вывода.

При прямой регистровой адресации РОН операндом является

содержимое регистра общего назначения, указанного в команде. Команды с

прямой регистровой адресацией могут адресовать один (Rd) или два (Rr и Rd)

РОН . Во втором случае результат выполнения команды со-храняется в регистре

Rd. Прямая регистровая адресация РОН применяется во всех арифметических и

логических командах, а также в некоторых командах работы с битами, т. к. эти

команды выполняются в АЛУ только над содержимым РОН. Команды, вторым

операндом которых является константа, могут использовать в качестве первого

операнда только регистры из старшей половины РОН (R16…R31).

При прямой регистровой адресации регистра ввода-вывода операнд

содержится в регистре ввода-вывода, указанном в команде. Адрес регистра вводавывода хранится в шести разрядах слова команды ( где n определяет адрес

регистра-источника или регистра-приёмника в РОН). Прямая регистровая

адресация регистров ввода-вывода используется в командах чтения IN и записи

OUT регистра ввода-вывода, а также в ряде других команд работы с регистрами

ввода-вывода.

60.

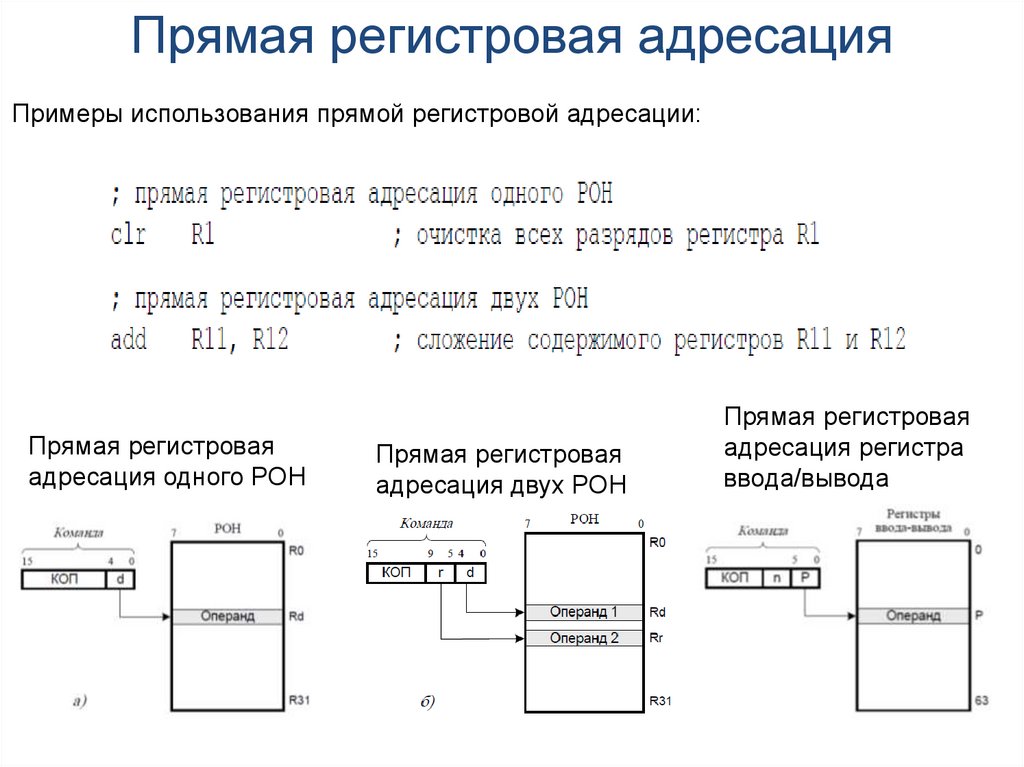

Прямая регистровая адресацияПримеры использования прямой регистровой адресации:

Прямая регистровая

адресация одного РОН

Прямая регистровая

адресация двух РОН

Прямая регистровая

адресация регистра

ввода/вывода

61.

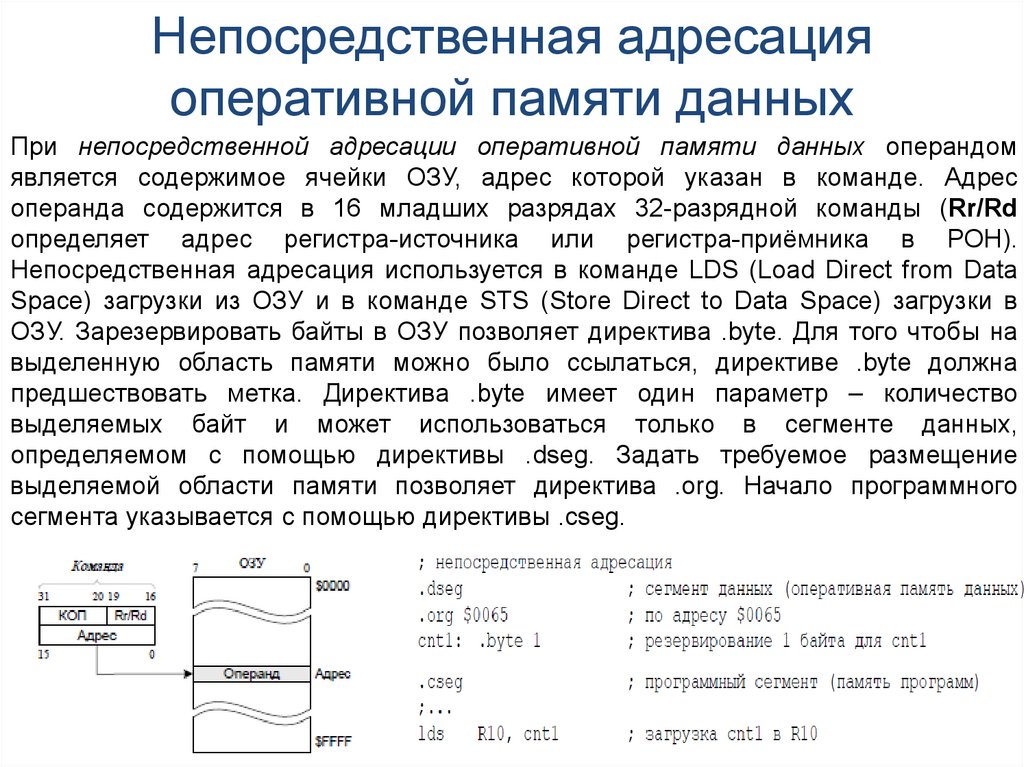

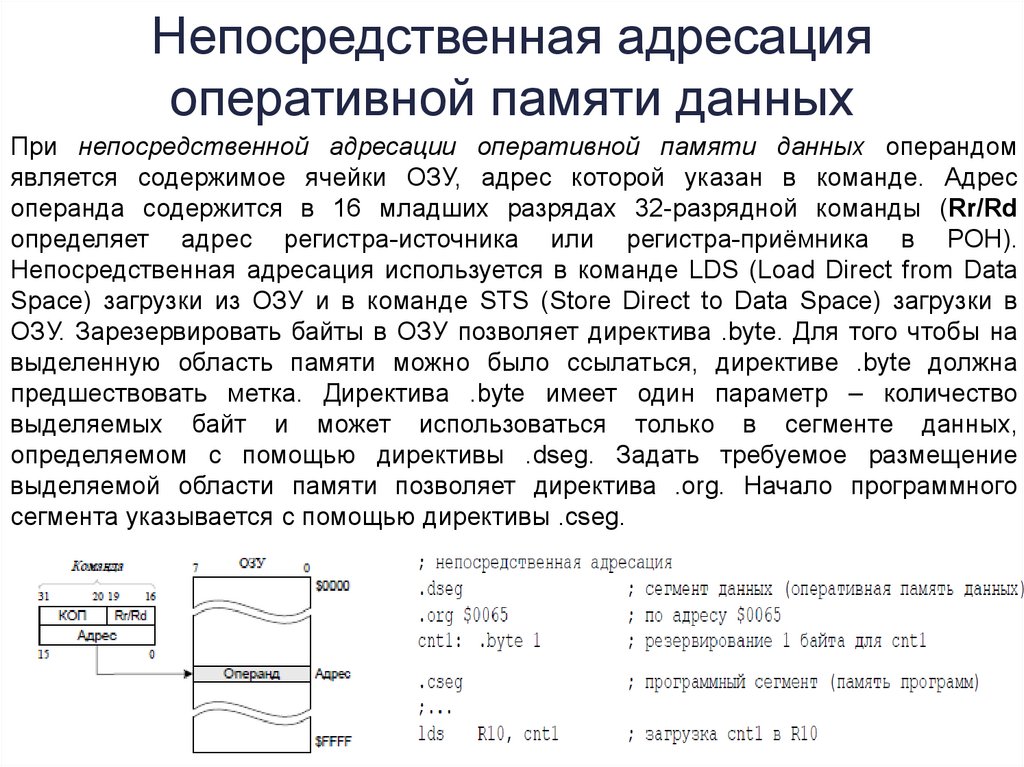

Непосредственная адресацияоперативной памяти данных

При непосредственной адресации оперативной памяти данных операндом

является содержимое ячейки ОЗУ, адрес которой указан в команде. Адрес

операнда содержится в 16 младших разрядах 32-разрядной команды (Rr/Rd

определяет адрес регистра-источника или регистра-приёмника в РОН).

Непосредственная адресация используется в команде LDS (Load Direct from Data

Space) загрузки из ОЗУ и в команде STS (Store Direct to Data Space) загрузки в

ОЗУ. Зарезервировать байты в ОЗУ позволяет директива .byte. Для того чтобы на

выделенную область памяти можно было ссылаться, директиве .byte должна

предшествовать метка. Директива .byte имеет один параметр – количество

выделяемых байт и может использоваться только в сегменте данных,

определяемом с помощью директивы .dseg. Задать требуемое размещение

выделяемой области памяти позволяет директива .org. Начало программного

сегмента указывается с помощью директивы .cseg.

62.

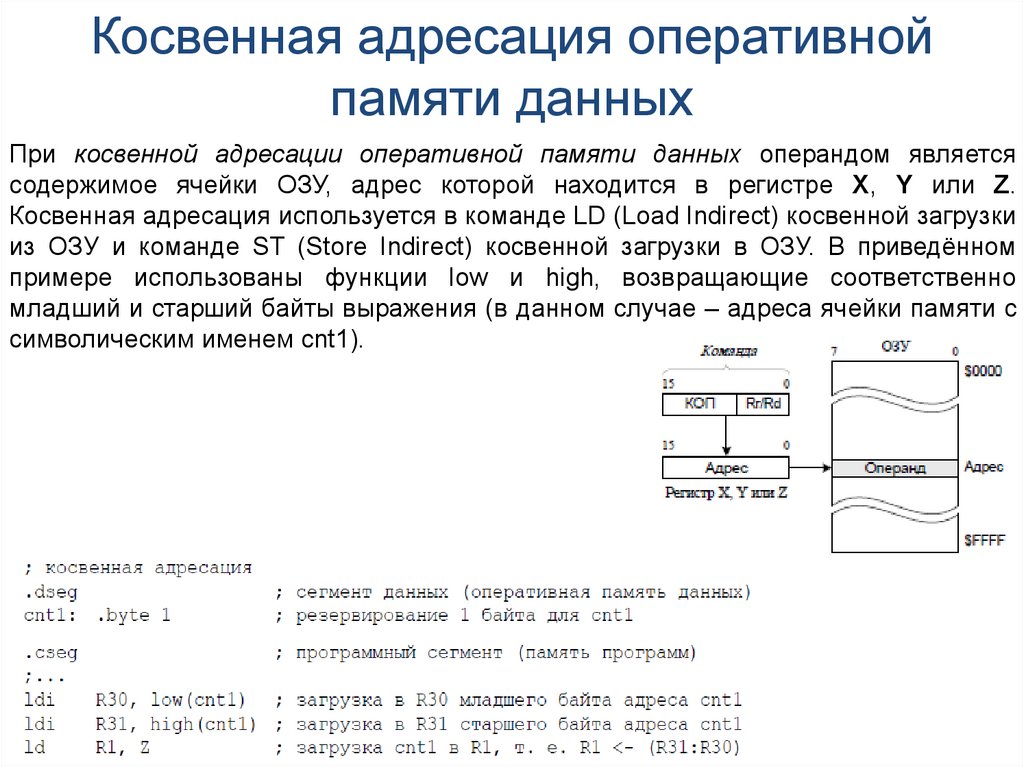

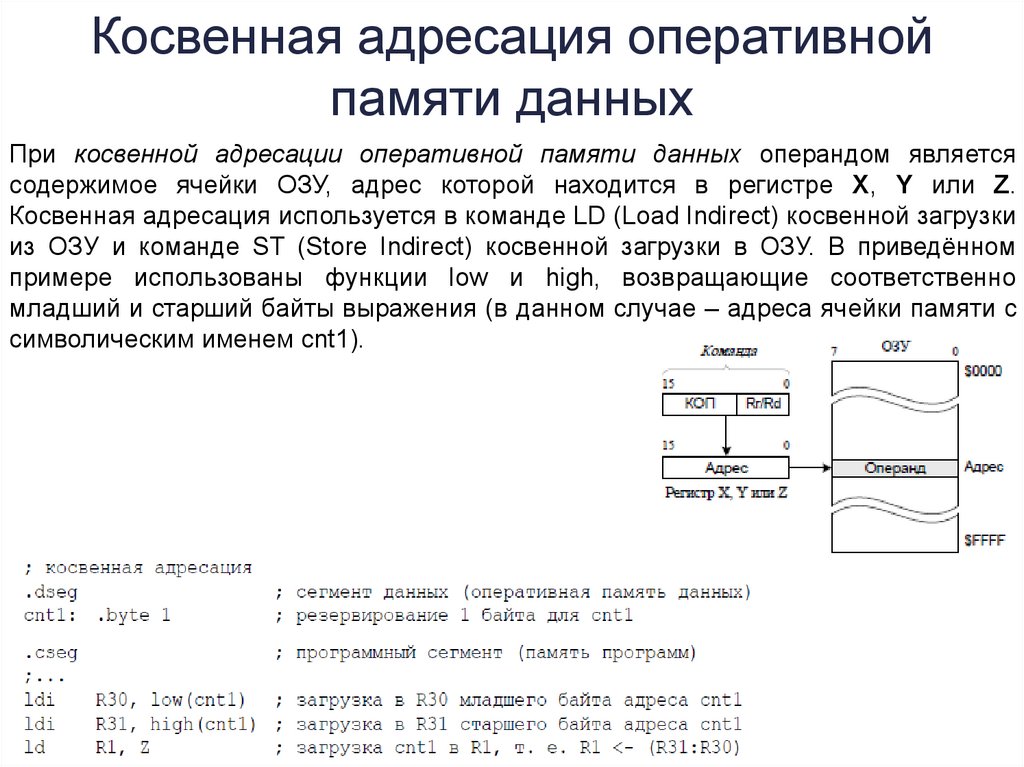

Косвенная адресация оперативнойпамяти данных

При косвенной адресации оперативной памяти данных операндом является

содержимое ячейки ОЗУ, адрес которой находится в регистре X, Y или Z.

Косвенная адресация используется в команде LD (Load Indirect) косвенной загрузки

из ОЗУ и команде ST (Store Indirect) косвенной загрузки в ОЗУ. В приведённом

примере использованы функции low и high, возвращающие соответственно

младший и старший байты выражения (в данном случае – адреса ячейки памяти с

символическим именем cnt1).

63.

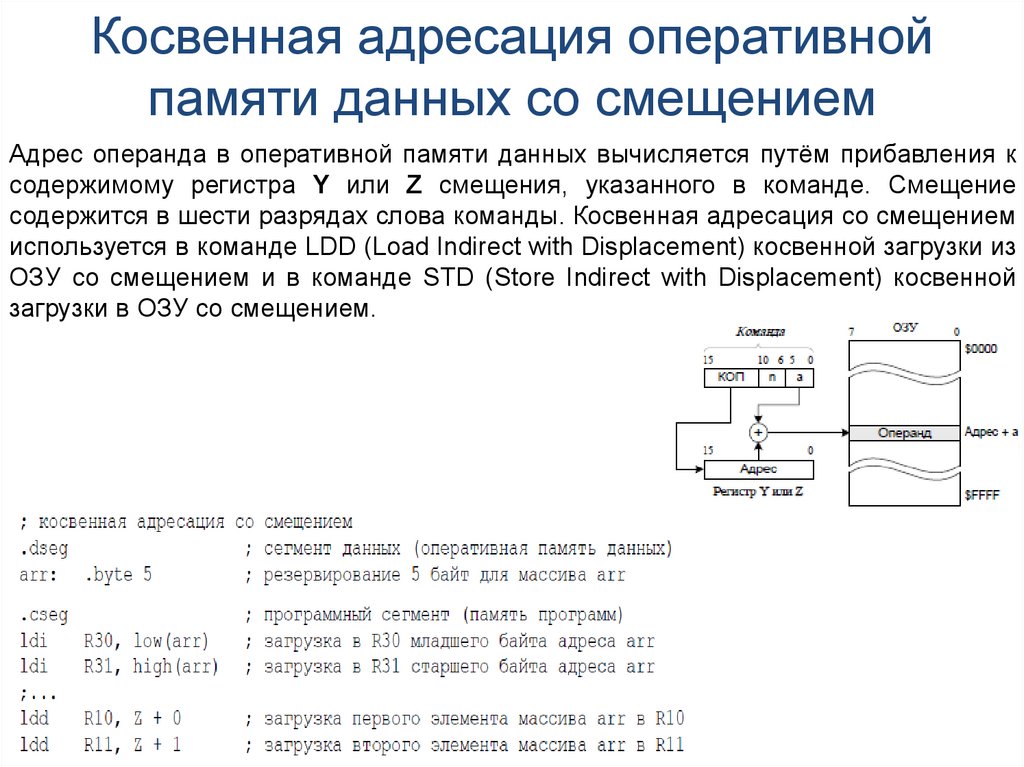

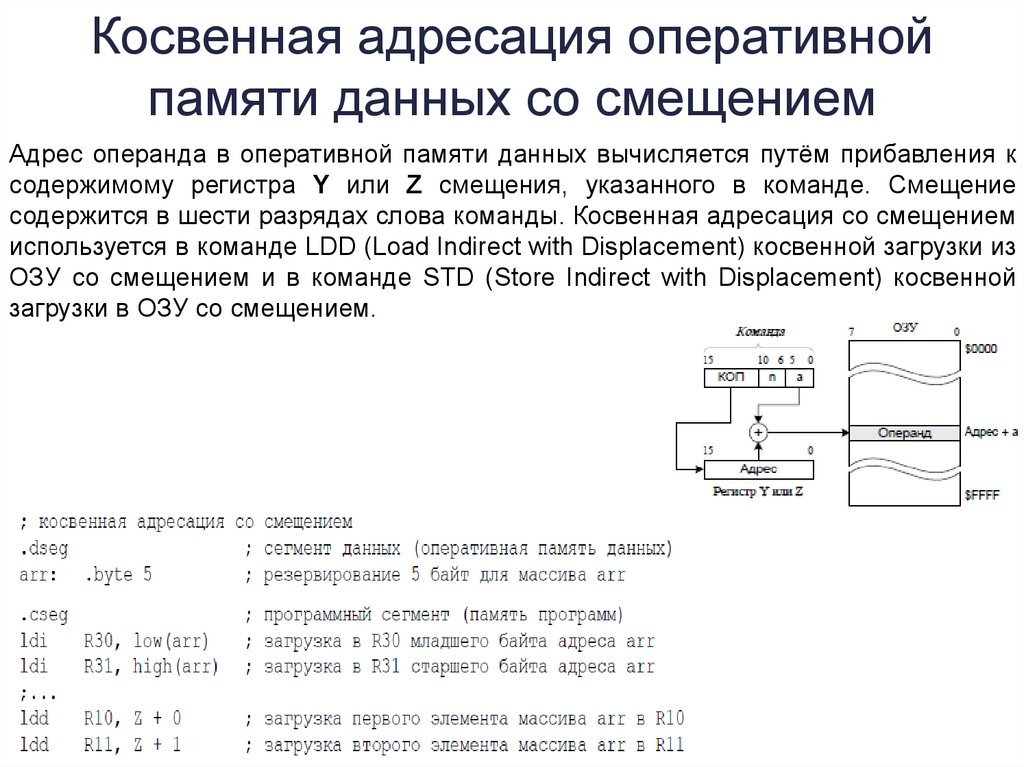

Косвенная адресация оперативнойпамяти данных со смещением

Адрес операнда в оперативной памяти данных вычисляется путём прибавления к

содержимому регистра Y или Z смещения, указанного в команде. Смещение

содержится в шести разрядах слова команды. Косвенная адресация со смещением

используется в команде LDD (Load Indirect with Displacement) косвенной загрузки из

ОЗУ со смещением и в команде STD (Store Indirect with Displacement) косвенной

загрузки в ОЗУ со смещением.

64.

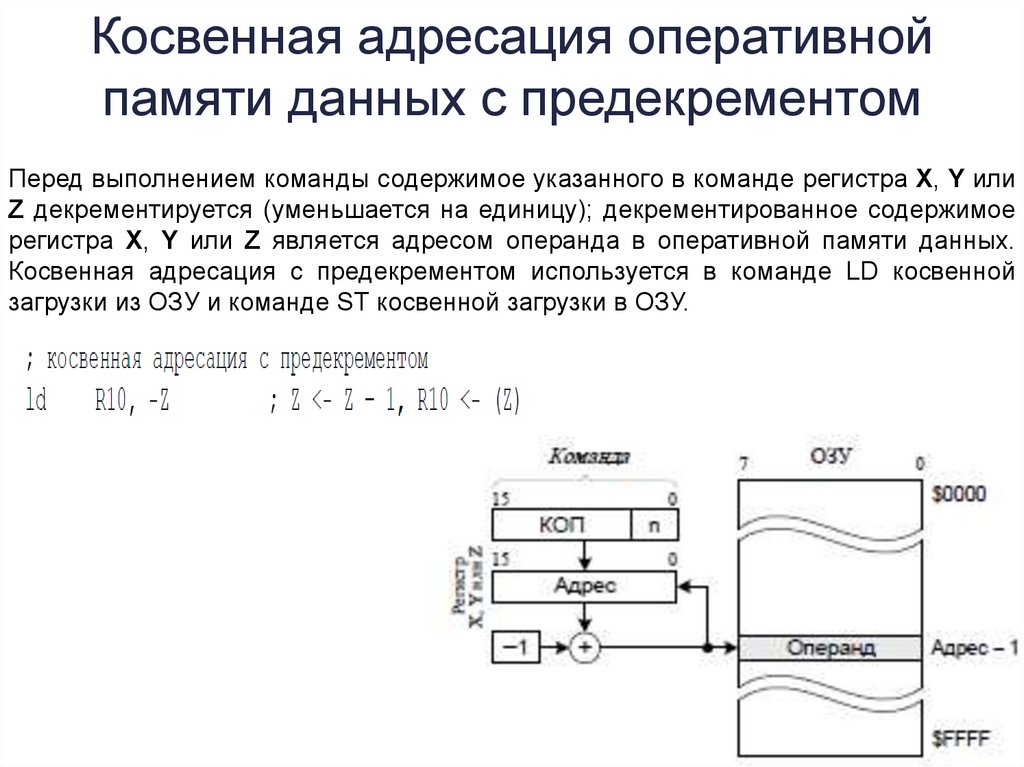

Косвенная адресация оперативнойпамяти данных с предекрементом

Перед выполнением команды содержимое указанного в команде регистра X, Y или

Z декрементируется (уменьшается на единицу); декрементированное содержимое

регистра X, Y или Z является адресом операнда в оперативной памяти данных.

Косвенная адресация с предекрементом используется в команде LD косвенной

загрузки из ОЗУ и команде ST косвенной загрузки в ОЗУ.

65.

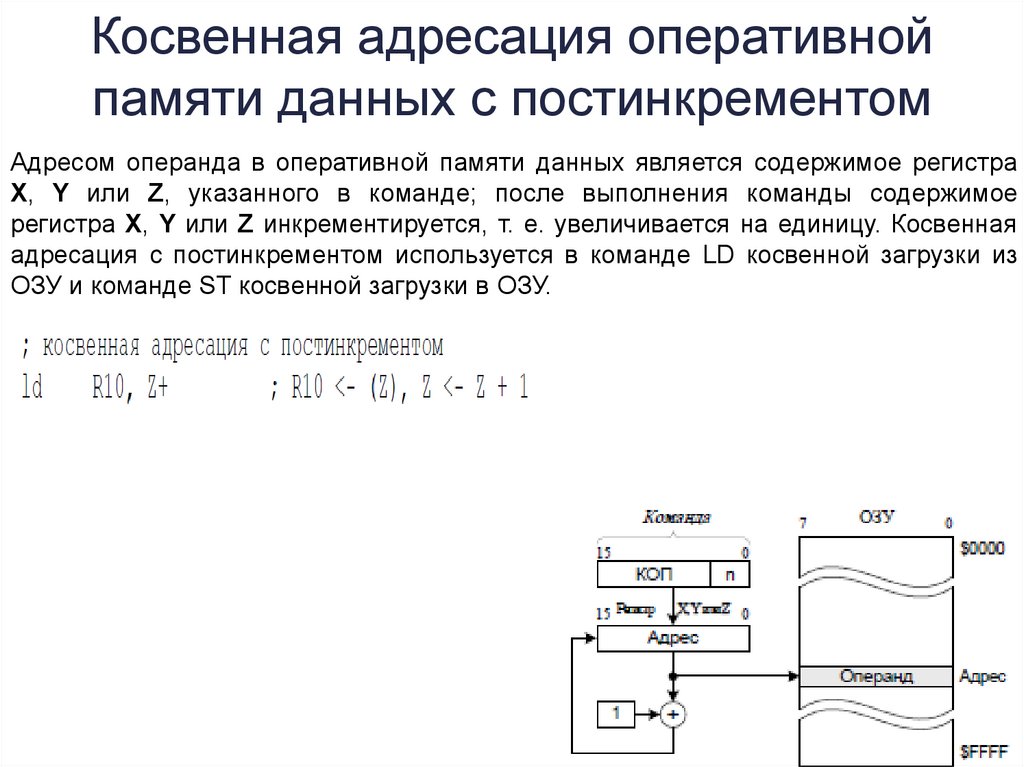

Косвенная адресация оперативнойпамяти данных с постинкрементом

Адресом операнда в оперативной памяти данных является содержимое регистра

X, Y или Z, указанного в команде; после выполнения команды содержимое

регистра X, Y или Z инкрементируется, т. е. увеличивается на единицу. Косвенная

адресация с постинкрементом используется в команде LD косвенной загрузки из

ОЗУ и команде ST косвенной загрузки в ОЗУ.

66.

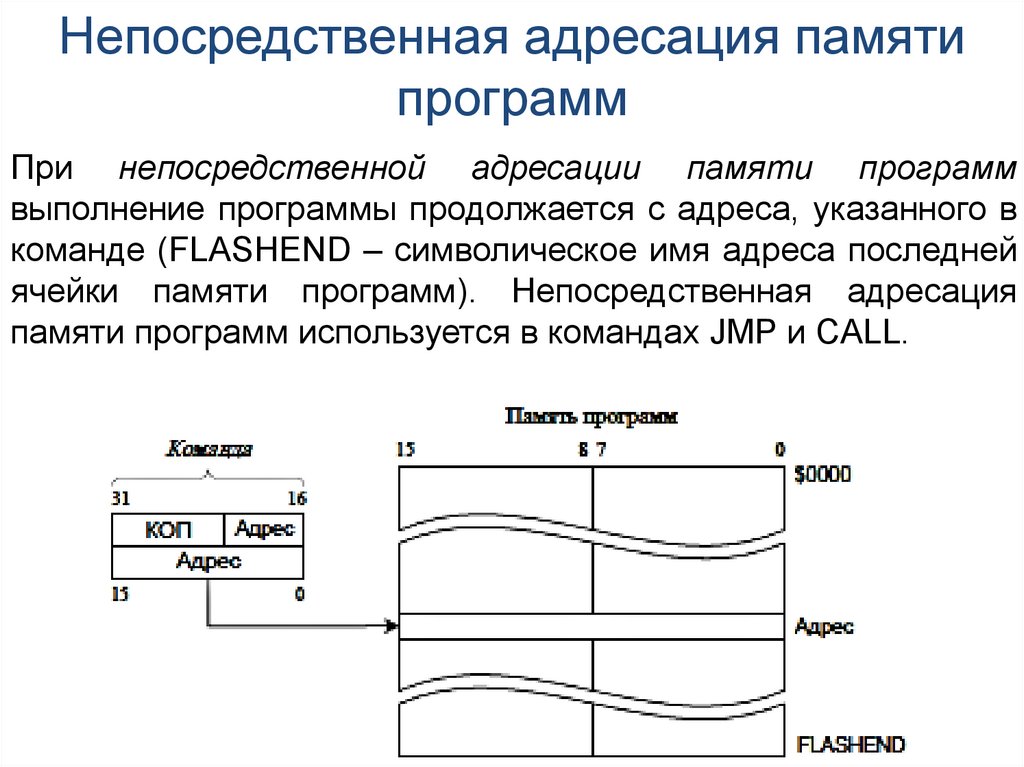

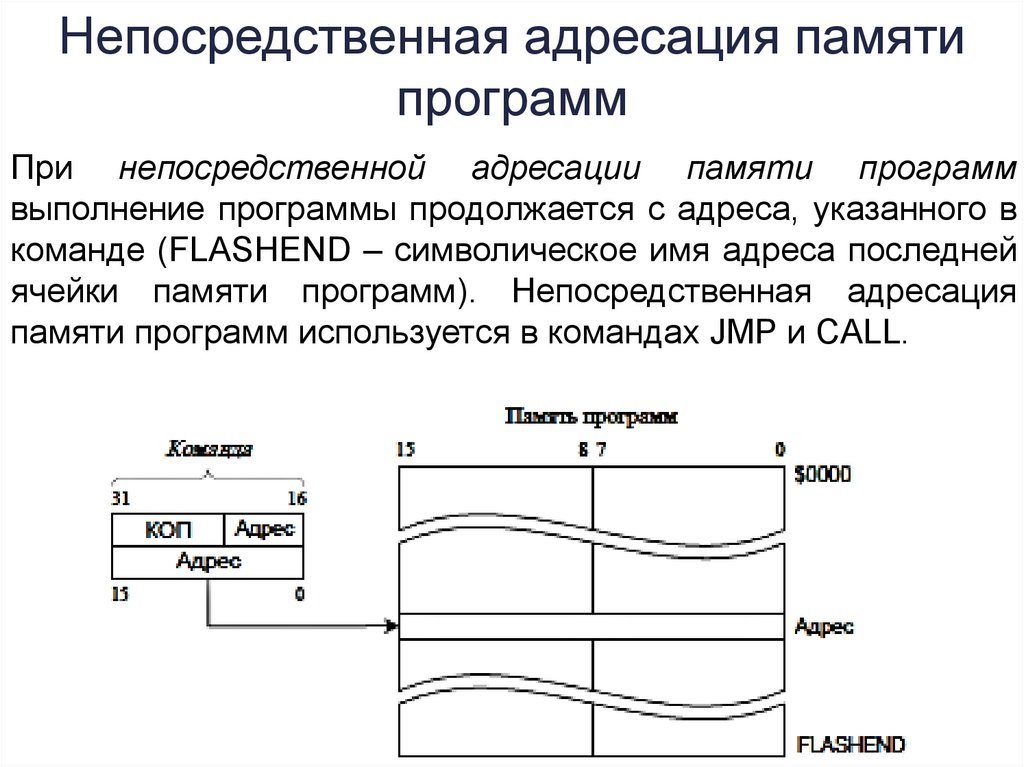

Непосредственная адресация памятипрограмм

При непосредственной адресации памяти программ

выполнение программы продолжается с адреса, указанного в

команде (FLASHEND – символическое имя адреса последней

ячейки памяти программ). Непосредственная адресация

памяти программ используется в командах JMP и CALL.

67.

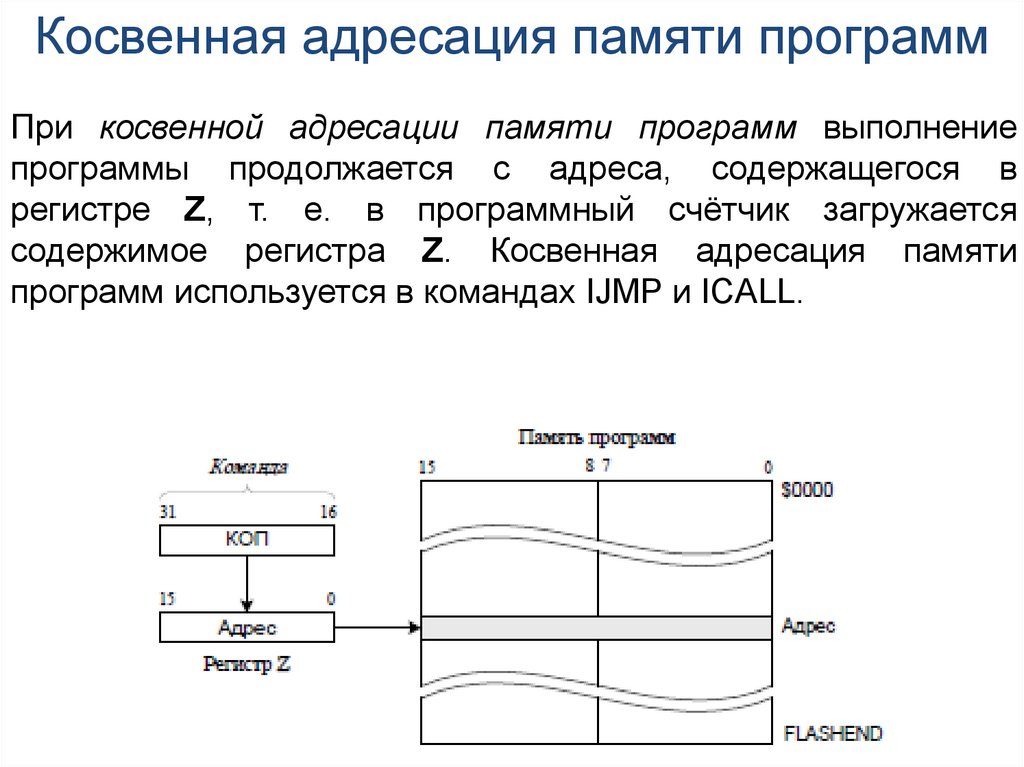

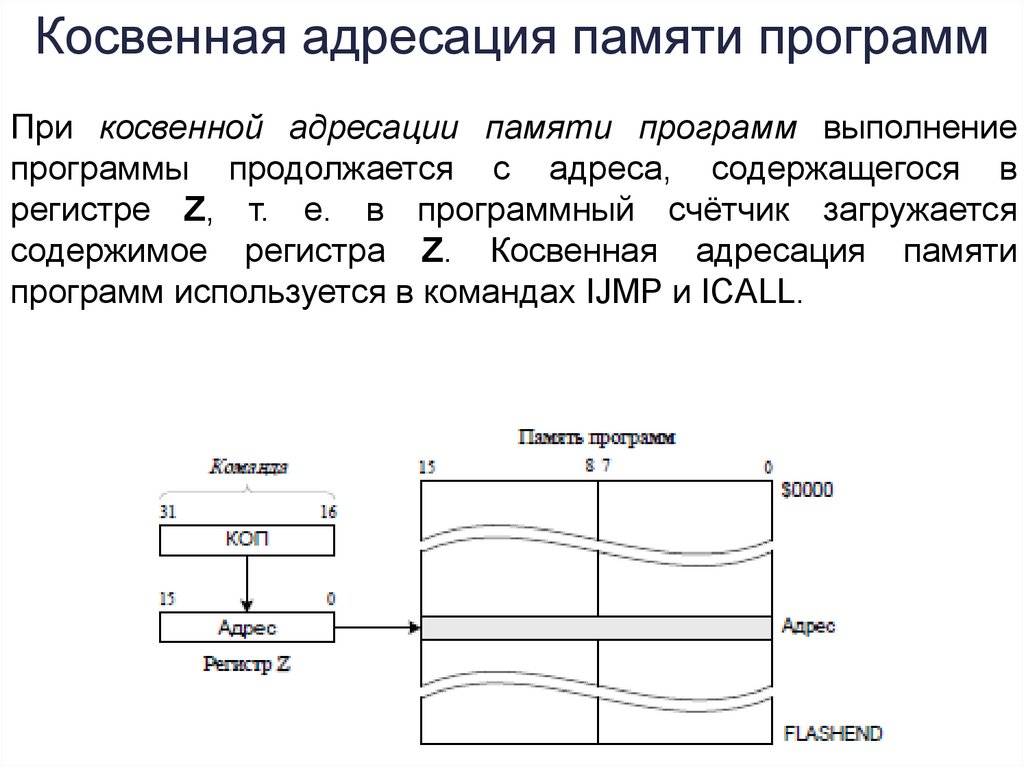

Косвенная адресация памяти программПри косвенной адресации памяти программ выполнение

программы продолжается с адреса, содержащегося в

регистре Z, т. е. в программный счётчик загружается

содержимое регистра Z. Косвенная адресация памяти

программ используется в командах IJMP и ICALL.

68.

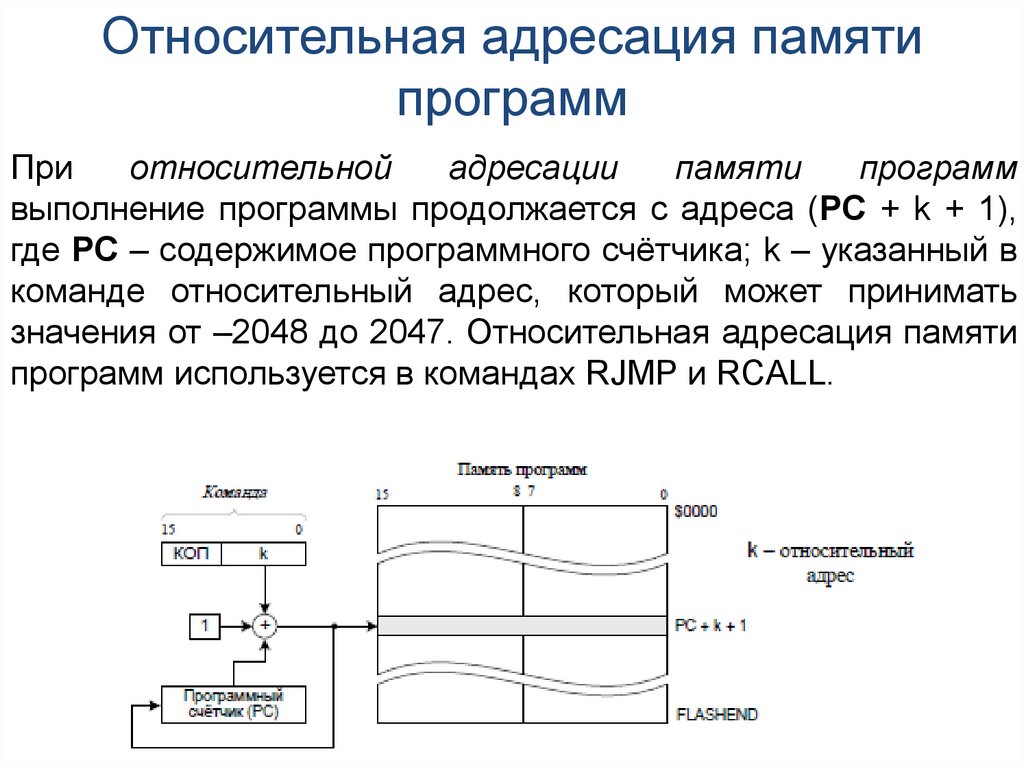

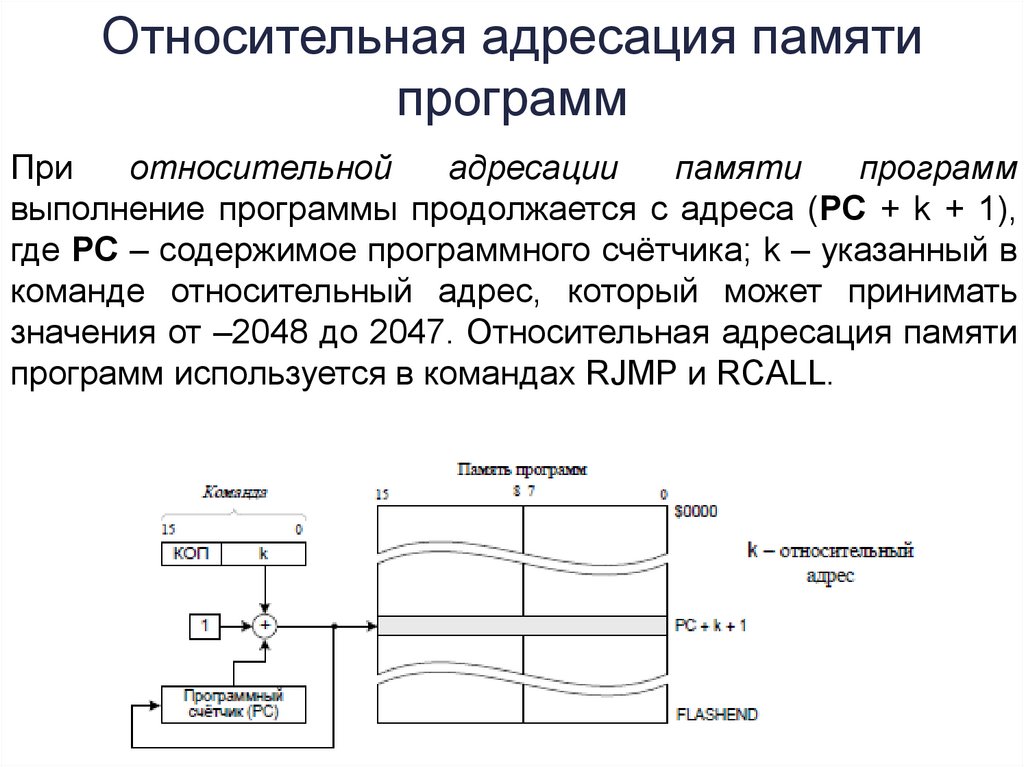

Относительная адресация памятипрограмм

При

относительной

адресации

памяти

программ

выполнение программы продолжается с адреса (PC + k + 1),

где PC – содержимое программного счётчика; k – указанный в

команде относительный адрес, который может принимать

значения от –2048 до 2047. Относительная адресация памяти

программ используется в командах RJMP и RCALL.

69.

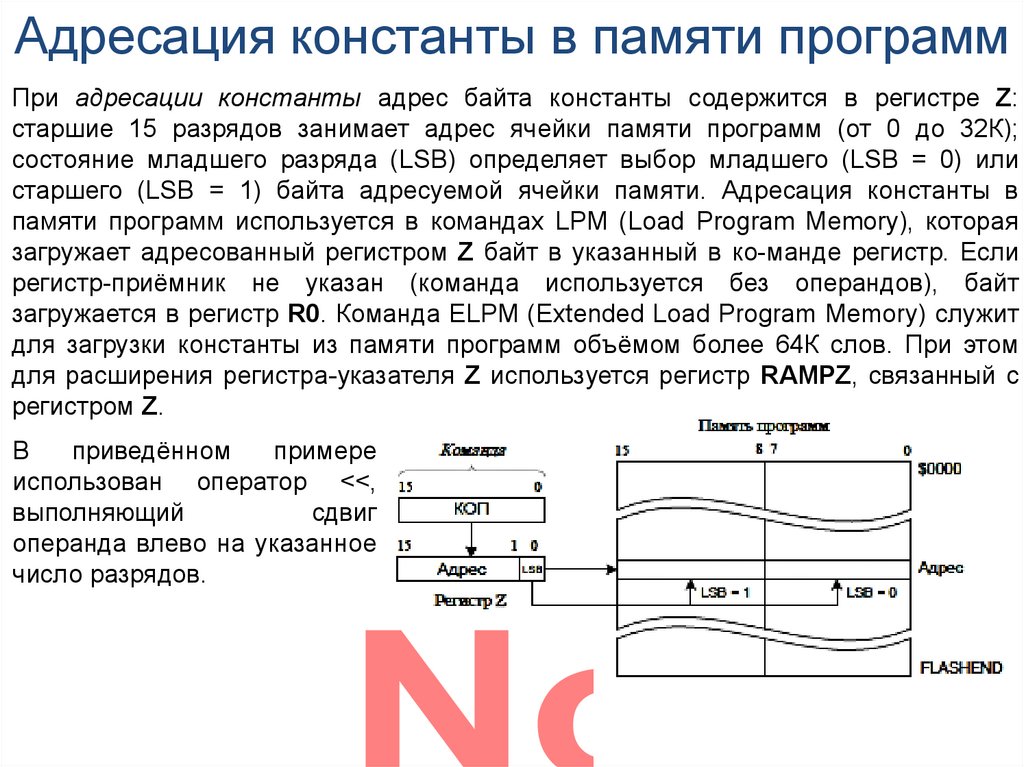

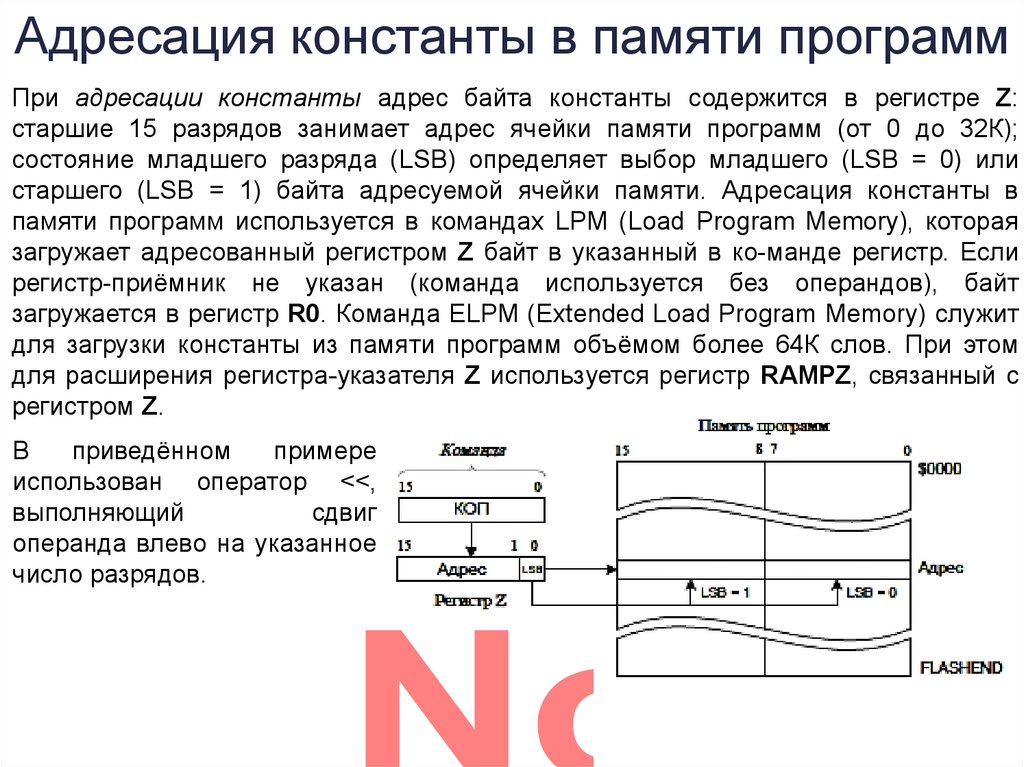

Адресация константы в памяти программПри адресации константы адрес байта константы содержится в регистре Z:

старшие 15 разрядов занимает адрес ячейки памяти программ (от 0 до 32К);

состояние младшего разряда (LSB) определяет выбор младшего (LSB = 0) или

старшего (LSB = 1) байта адресуемой ячейки памяти. Адресация константы в

памяти программ используется в командах LPM (Load Program Memory), которая

загружает адресованный регистром Z байт в указанный в ко-манде регистр. Если

регистр-приёмник не указан (команда используется без операндов), байт

загружается в регистр R0. Команда ELPM (Extended Load Program Memory) служит

для загрузки константы из памяти программ объёмом более 64К слов. При этом

для расширения регистра-указателя Z используется регистр RAMPZ, связанный с

регистром Z.

В

приведённом

примере

использован оператор <<,

выполняющий

сдвиг

операнда влево на указанное

число разрядов.

70.

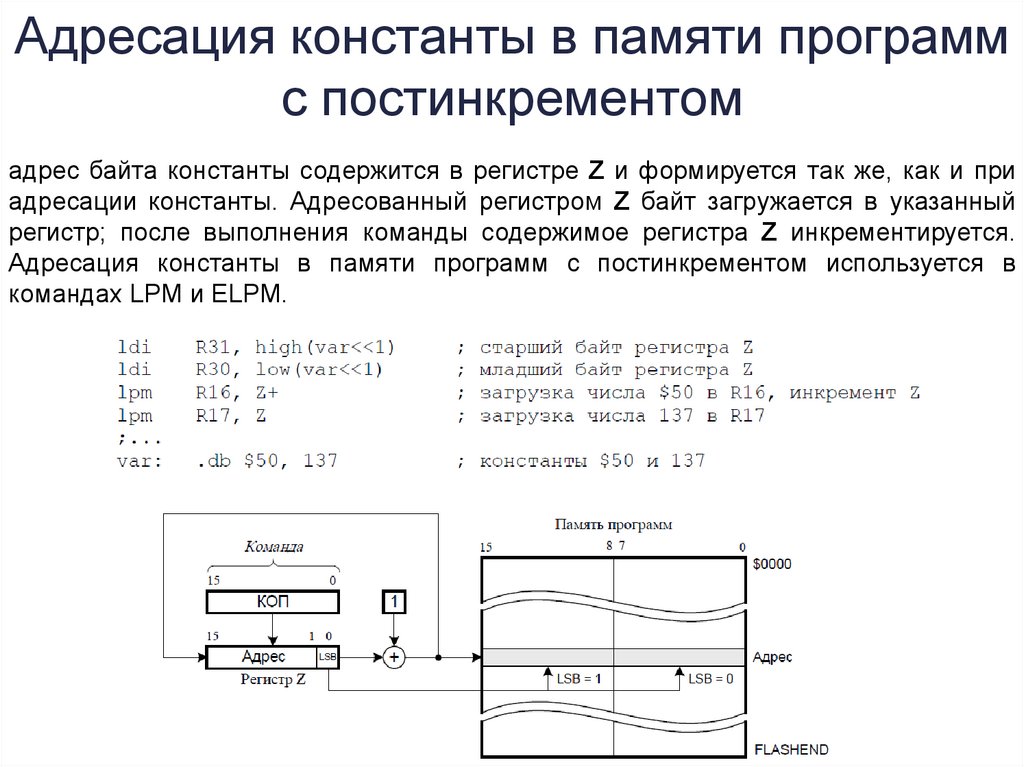

Адресация константы в памяти программс постинкрементом

адрес байта константы содержится в регистре Z и формируется так же, как и при

адресации константы. Адресованный регистром Z байт загружается в указанный

регистр; после выполнения команды содержимое регистра Z инкрементируется.

Адресация константы в памяти программ с постинкрементом используется в

командах LPM и ELPM.

71.

Реализация типовых структуралгоритмов

Ветвления используются для выполнения различных частей

программы (разделения ветвей алгоритма) в зависимости от некоторых

условий.

В циклах одна и та же операция выполняется над содержимым

нескольких последовательно расположенных в памяти ячеек или

элементов данных.

В циклической программе можно выделить блоки:

1. Блок инициализации, в котором производится присвоение начальных

значений переменным, счётчикам, индексам и указателям. Указатели

представляют собой адреса данных в памяти.

2. Блок обработки, в котором выполняются требуемые вычисления, т. е.

одинаковые повторяющиеся действия над различными последовательно

расположенными в памяти данными.

3. Блок управления циклом, в котором изменяются значения счётчиков и

индексов (указателей) перед выполнением следующей повторяющейся

операции, а также производится проверка условия выхода из цикла.

4. Заключительный блок, в котором производится сохранение

полученных результатов.

72.

Команды безусловных переходовКоманды безусловных переходов JMP, RJMP, IJMP и EIJMP

передают управление по указанному в команде адресу памяти программ.

Команда JMP (Jump – переход) позволяет передавать управление

внутри всего объёма памяти программ.

Команда RJMP (Relative Jump – относительный переход)

обеспечива-ет переход в пределах ±2К слов (±4К байт) относительно

текущего содержимо-го программного счётчика.

По команде IJMP (Indirect Jump – косвенный пере-ход)

выполняется косвенный переход по адресу, указанному регистром Z; максимальное смещение составляет 64К слов (128К байт).

Команда EIJMP (Extend-ed Indirect Jump – расширенный

косвенный переход) обеспечивает косвенный переход по всему объёму

памяти программ; для расширения программного счётчика используется

регистр EIND. При выполнении команд безусловных переходов в

программный счётчик загружается адрес ячейки памяти программ, на

которую передаётся управление.

73.

Команды условных переходовКоманды BRхх (Branch if… – перейти, если …) выполняют

переход по результатам проверки разрядов регистра состояния SREG.

Коды условий (C, Z, N, V, S, H) формируются в регистре состояния при

выполнении арифметических, логических команд и команд работы с

битами и представляют собой признаки результата операции. Разряд С

устанавливается, если при выполнении команды был перенос из старшего

разряда результата. Разряд Z устанавливается, если результат

выполнения команды равен нулю. Разряд N устанавливается, если

старший значащий разряд результата равен 1. Разряд V (overflow –

переполнение) устанавливается, если при выполнении команды

произошло переполнение разрядной сетки числа со знаком. Разряд S = N

⊕ V (sign – знак) правильно показывает знак результата при переполнении

разрядной сетки числа со знаком. Разряд H (half carry – полуперенос)

устанавливается, если при выполнении команды был перенос из третьего

разряда результата.

Для организации ветвлений при сравнении операндов команды

BRхх используются совместно с командами CP (Compare) сравнения

содержимого двух РОН, CPC (Compare with Carry) сравнения с учётом

признака переноса и CPI (Compare with Immediate) сравнения с

константой.

74.

Команды условных переходовК командам условных переходов также относится команда CPSE

(Compare and Skip if Equal – сравнить и пропустить, если равно), которая

сравнивает содержимое двух РОН и пропускает следующую за ней

команду, если содержи-мое одинаково.

Команды SBRS, SBRC, SBIS, SBIC (Skip if Bit in Register [I/O

Register] is Set [Cleared] – пропустить, если разряд в регистре общего

назначения [ввода-вывода] установлен [сброшен]) пропускают следующую

команду в случае выполнения соответствующего условия.

75.

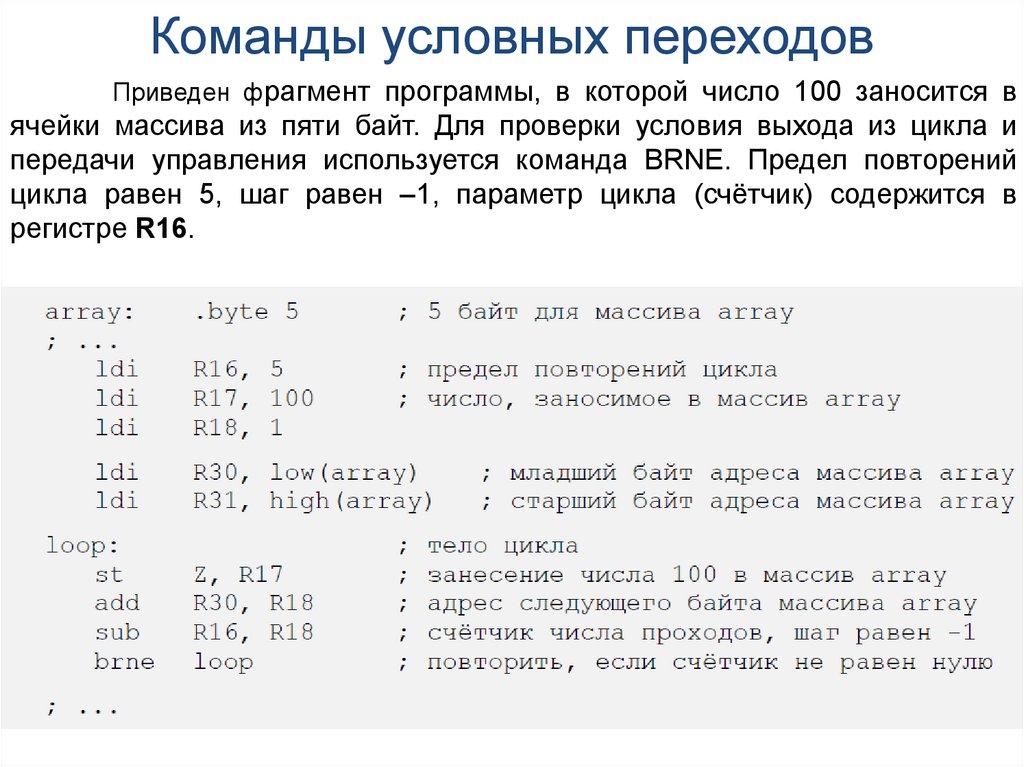

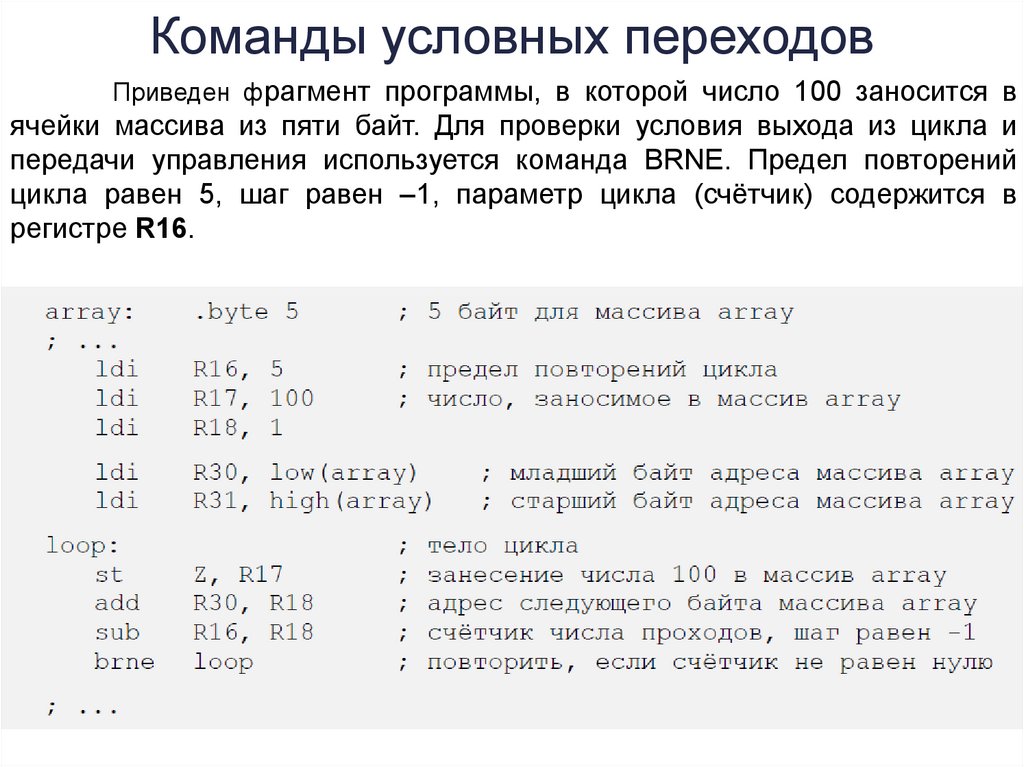

Команды условных переходовПриведен фрагмент программы, в которой число 100 заносится в

ячейки массива из пяти байт. Для проверки условия выхода из цикла и

передачи управления используется команда BRNE. Предел повторений

цикла равен 5, шаг равен –1, параметр цикла (счётчик) содержится в

регистре R16.

76.

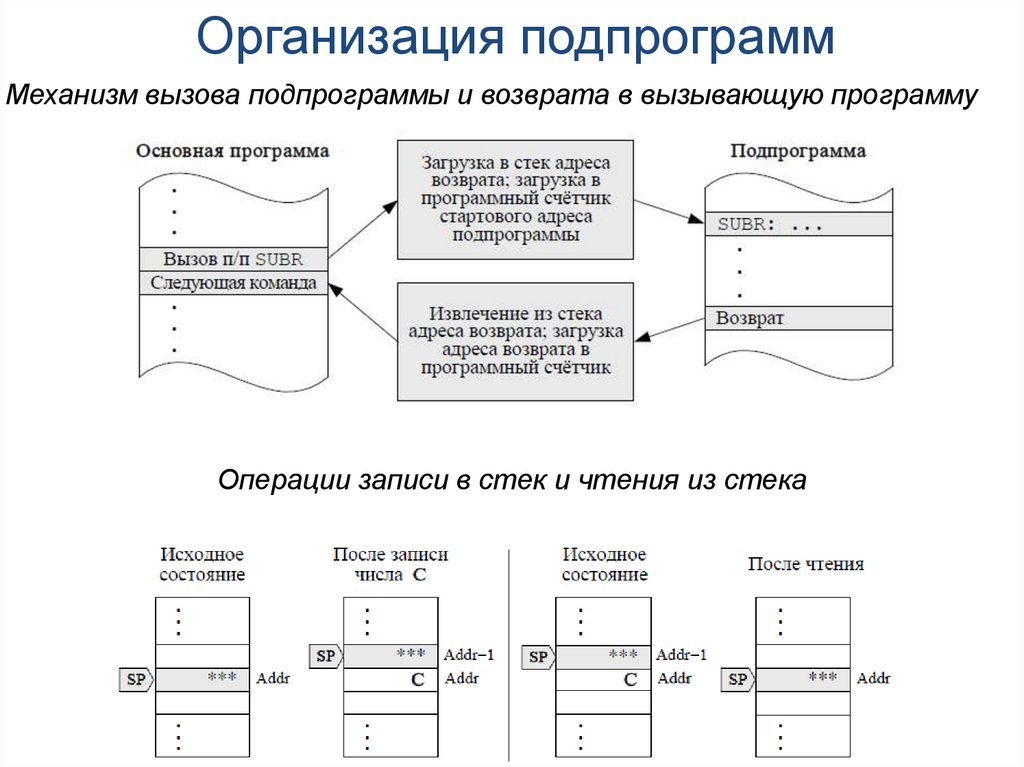

Организация подпрограммПоложение подпрограммы в общей структуре программы определяется по

её имени. Имя подпрограммы на ассемблере, задаваемое символической меткой,

является стартовым адресом исполняемой части подпрограммы.

Вызов подпрограммы подразумевает передачу в неё управления ходом выполнения команд. Передача управления осуществляется путём загрузки в программный счётчик (РС) стартового адреса подпрограммы. Для хранения адресов

возврата из подпрограмм используется стек (stack).

Стек – специальным образом организованная последовательность ячеек

памяти с дисциплиной обслуживания LIFO. При занесении в стек новых данных

предыдущие данные сохраняются («опускаются»). Выгружаются из стека

(«поднимаются») данные в обратном порядке. Программный стек (Software Stack)

организуется в оперативной памяти; глубина определяется размером и степенью

использования памяти.

Адрес очередной свободной ячейки стека содержится в специальном

регистре – указателе стека SP (Stack Pointer). При записи в стек число помещается

в ячейку с адресом, содержащимся в указателе стека, после чего содержимое

указателя стека уменьшается на единицу. При чтении из стека производится

выборка содержимого ячейки по адресу, на единицу большему содержимого

указателя стека.

77.

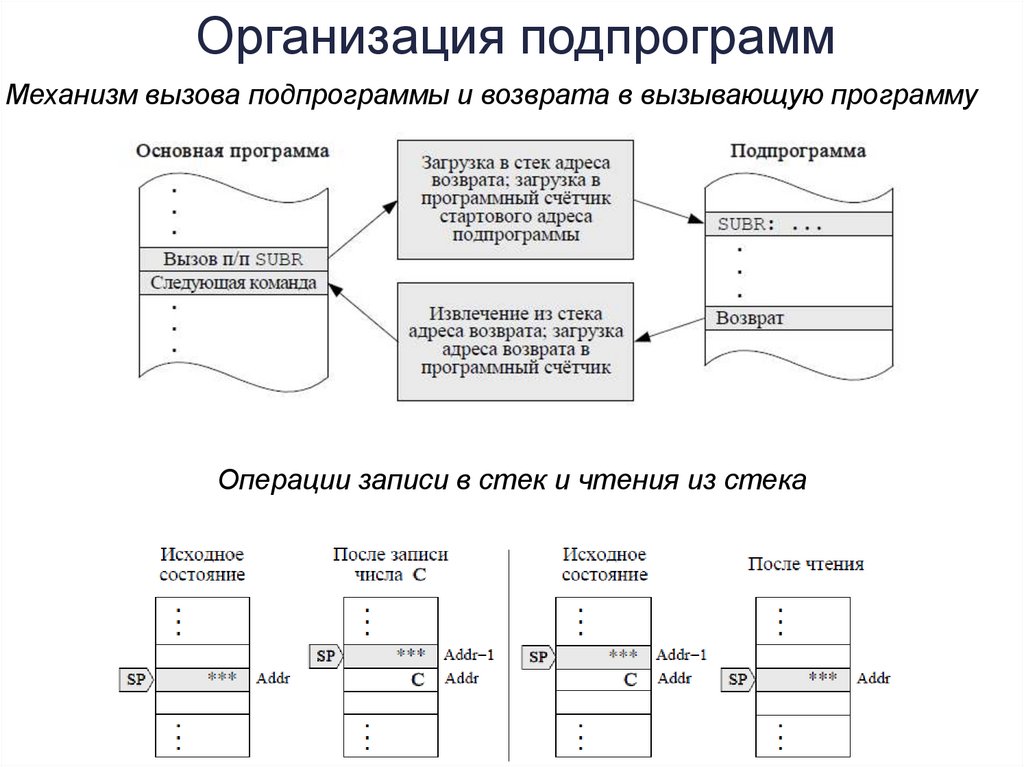

Организация подпрограммМеханизм вызова подпрограммы и возврата в вызывающую программу

Операции записи в стек и чтения из стека

78.

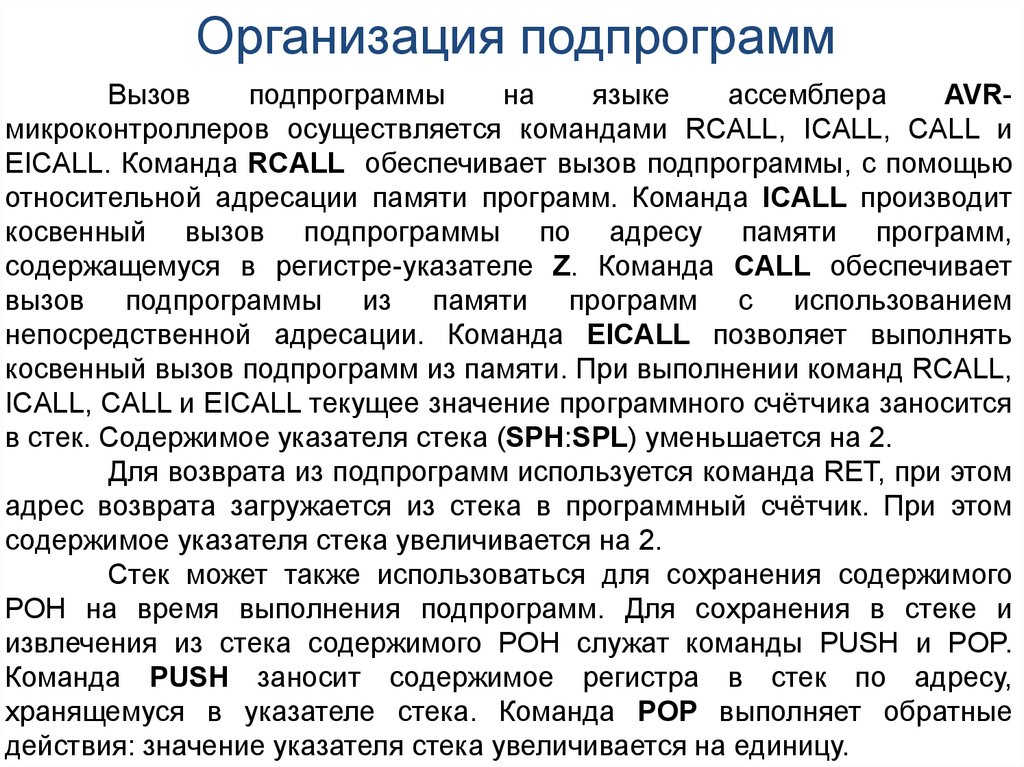

Организация подпрограммВызов

подпрограммы

на

языке

ассемблера

AVRмикроконтроллеров осуществляется командами RCALL, ICALL, CALL и

EICALL. Команда RCALL обеспечивает вызов подпрограммы, с помощью

относительной адресации памяти программ. Команда ICALL производит

косвенный вызов подпрограммы по адресу памяти программ,

содержащемуся в регистре-указателе Z. Команда CALL обеспечивает

вызов подпрограммы из памяти программ с использованием

непосредственной адресации. Команда EICALL позволяет выполнять

косвенный вызов подпрограмм из памяти. При выполнении команд RCALL,

ICALL, CALL и EICALL текущее значение программного счётчика заносится

в стек. Содержимое указателя стека (SPH:SPL) уменьшается на 2.

Для возврата из подпрограмм используется команда RET, при этом

адрес возврата загружается из стека в программный счётчик. При этом

содержимое указателя стека увеличивается на 2.

Стек может также использоваться для сохранения содержимого

РОН на время выполнения подпрограмм. Для сохранения в стеке и

извлечения из стека содержимого РОН служат команды PUSH и POP.

Команда PUSH заносит содержимое регистра в стек по адресу,

хранящемуся в указателе стека. Команда POP выполняет обратные

действия: значение указателя стека увеличивается на единицу.

79.

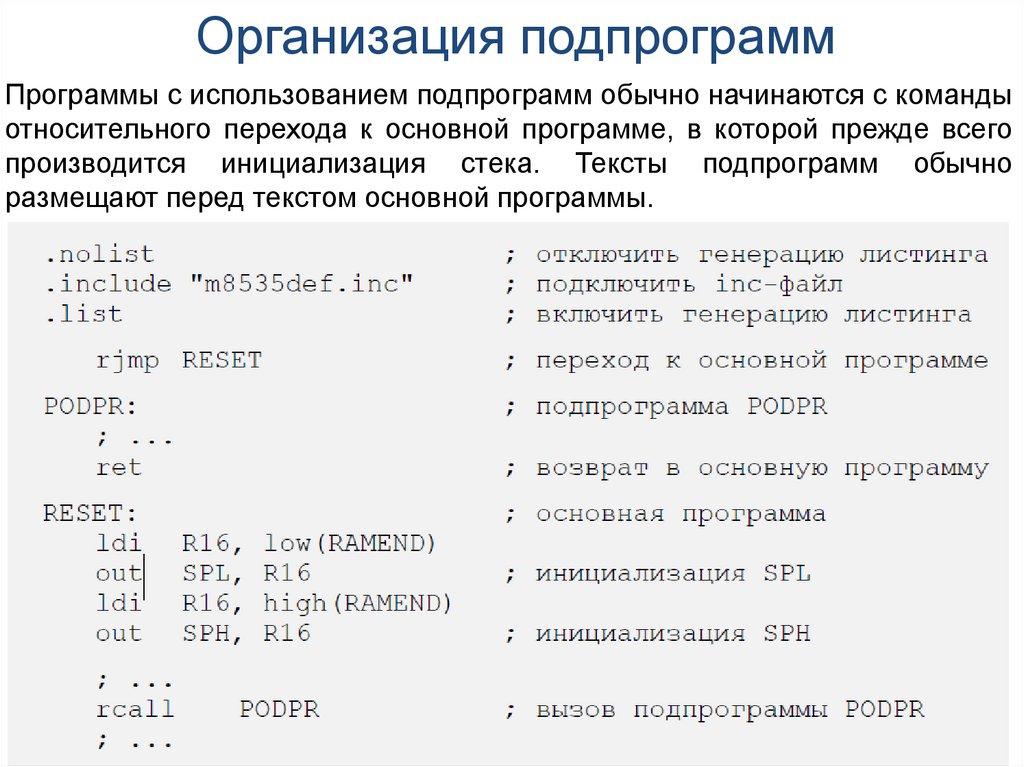

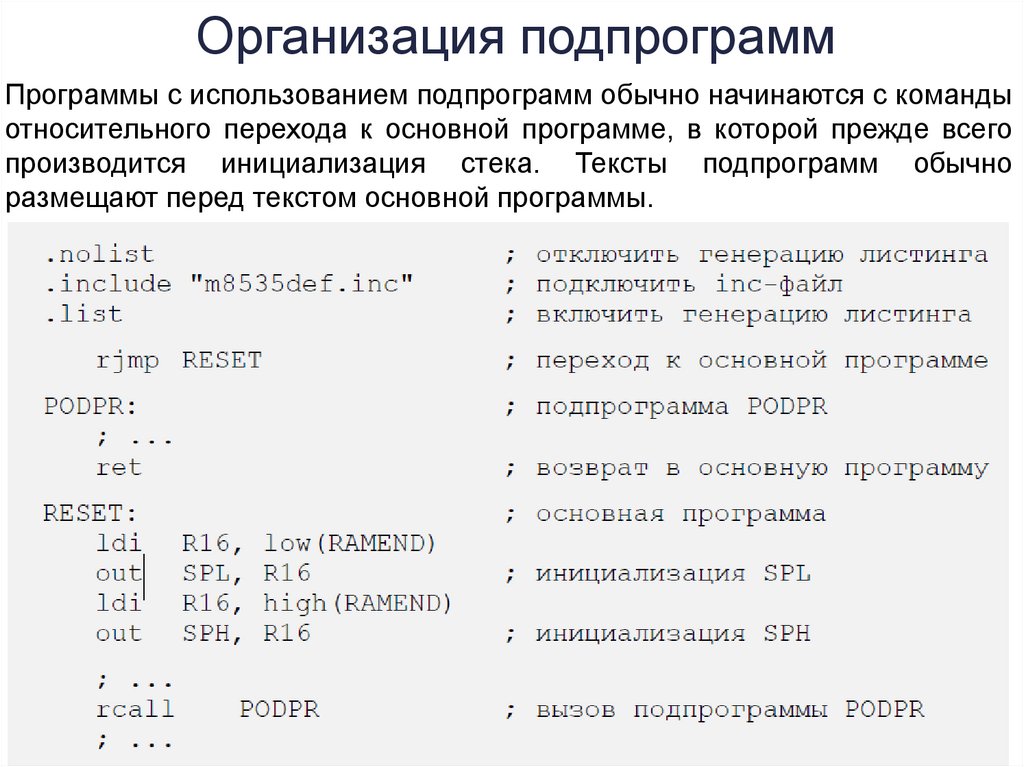

Организация подпрограммПрограммы с использованием подпрограмм обычно начинаются с команды

относительного перехода к основной программе, в которой прежде всего

производится инициализация стека. Тексты подпрограмм обычно

размещают перед текстом основной программы.

80.

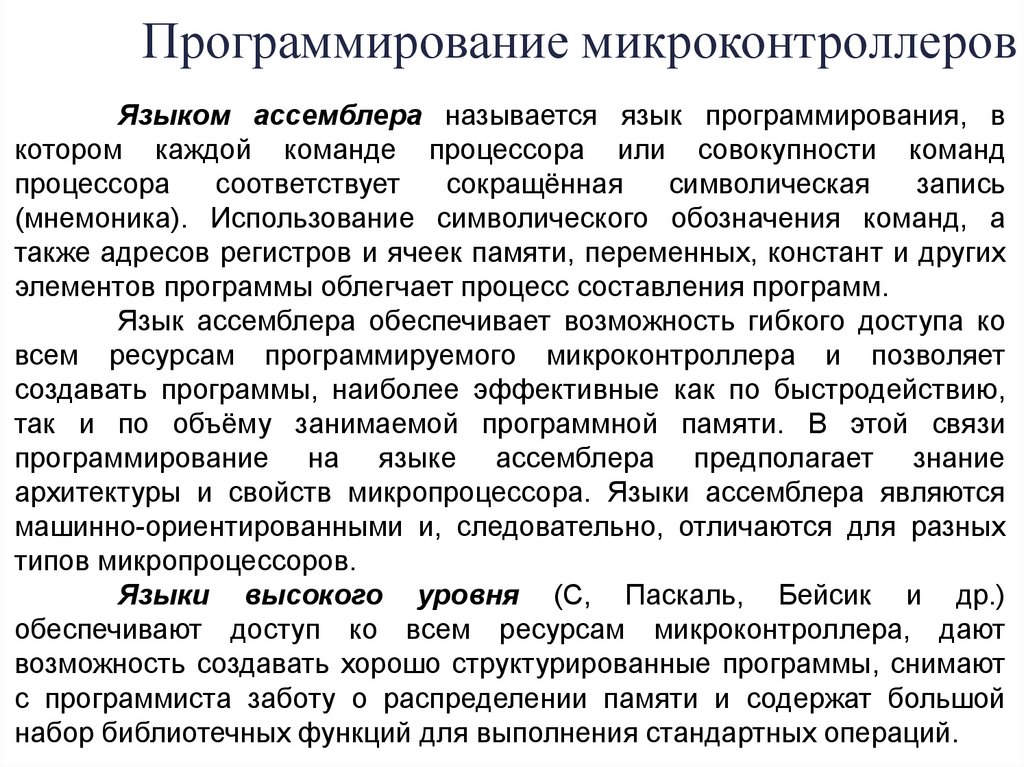

Программирование микроконтроллеровЯзыком ассемблера называется язык программирования, в

котором каждой команде процессора или совокупности команд

процессора

соответствует

сокращённая

символическая

запись

(мнемоника). Использование символического обозначения команд, а

также адресов регистров и ячеек памяти, переменных, констант и других

элементов программы облегчает процесс составления программ.

Язык ассемблера обеспечивает возможность гибкого доступа ко

всем ресурсам программируемого микроконтроллера и позволяет

создавать программы, наиболее эффективные как по быстродействию,

так и по объёму занимаемой программной памяти. В этой связи

программирование на языке ассемблера предполагает знание

архитектуры и свойств микропроцессора. Языки ассемблера являются

машинно-ориентированными и, следовательно, отличаются для разных

типов микропроцессоров.

Языки высокого уровня (С, Паскаль, Бейсик и др.)

обеспечивают доступ ко всем ресурсам микроконтроллера, дают

возможность создавать хорошо структурированные программы, снимают

с программиста заботу о распределении памяти и содержат большой

набор библиотечных функций для выполнения стандартных операций.

81.

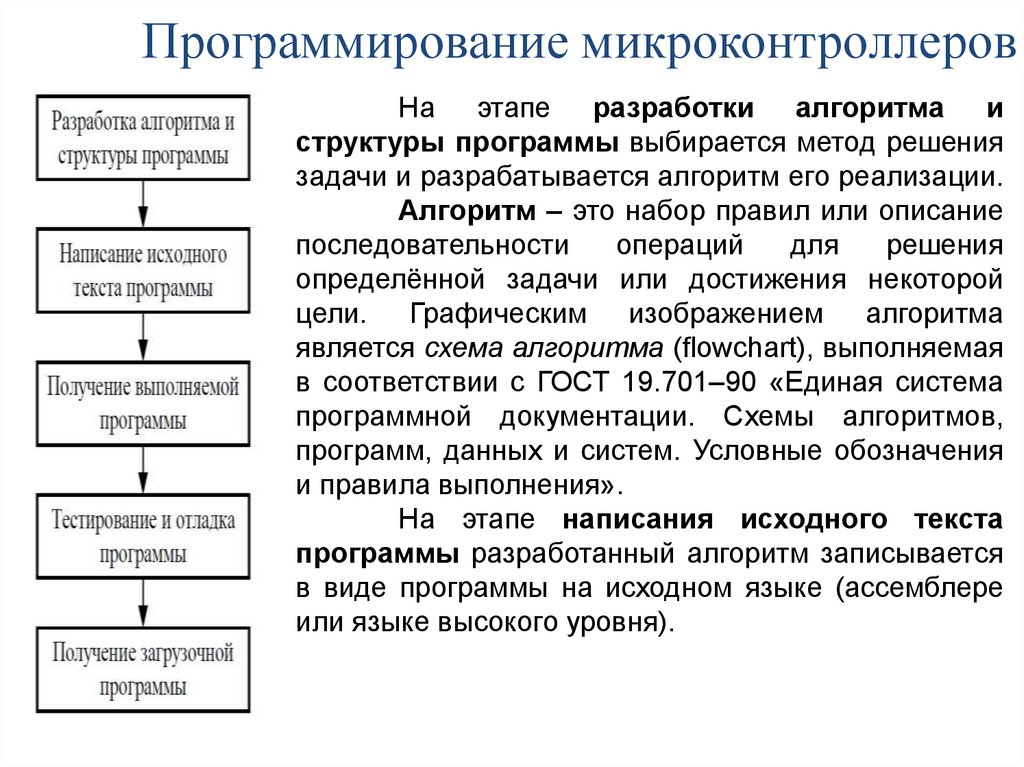

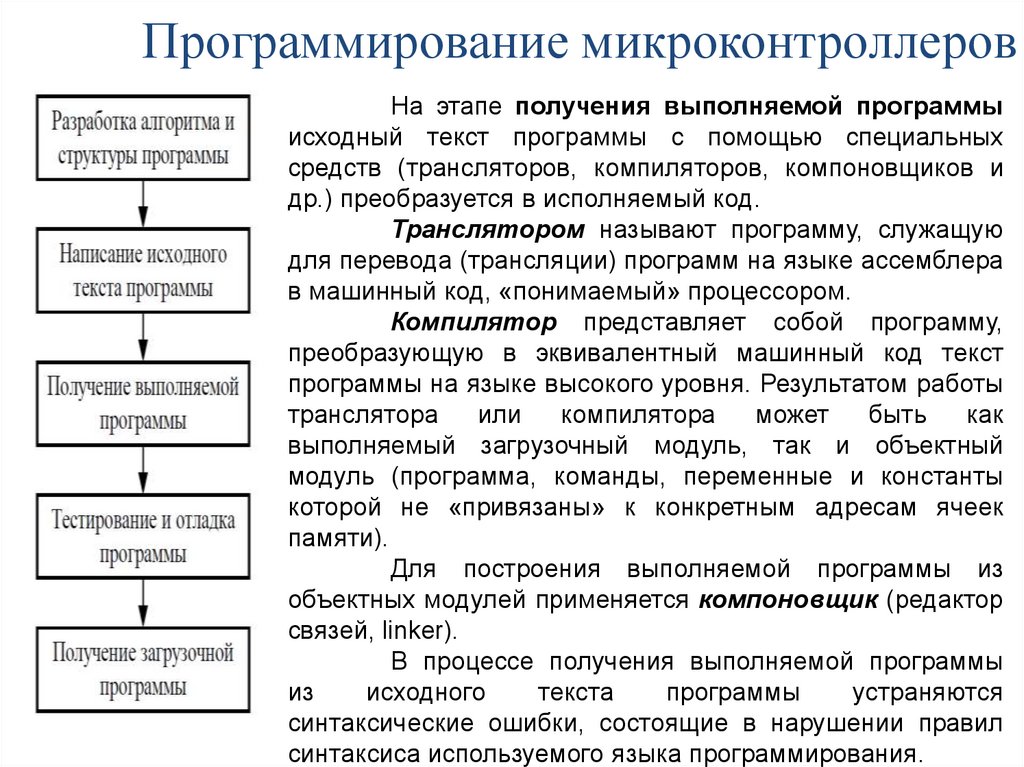

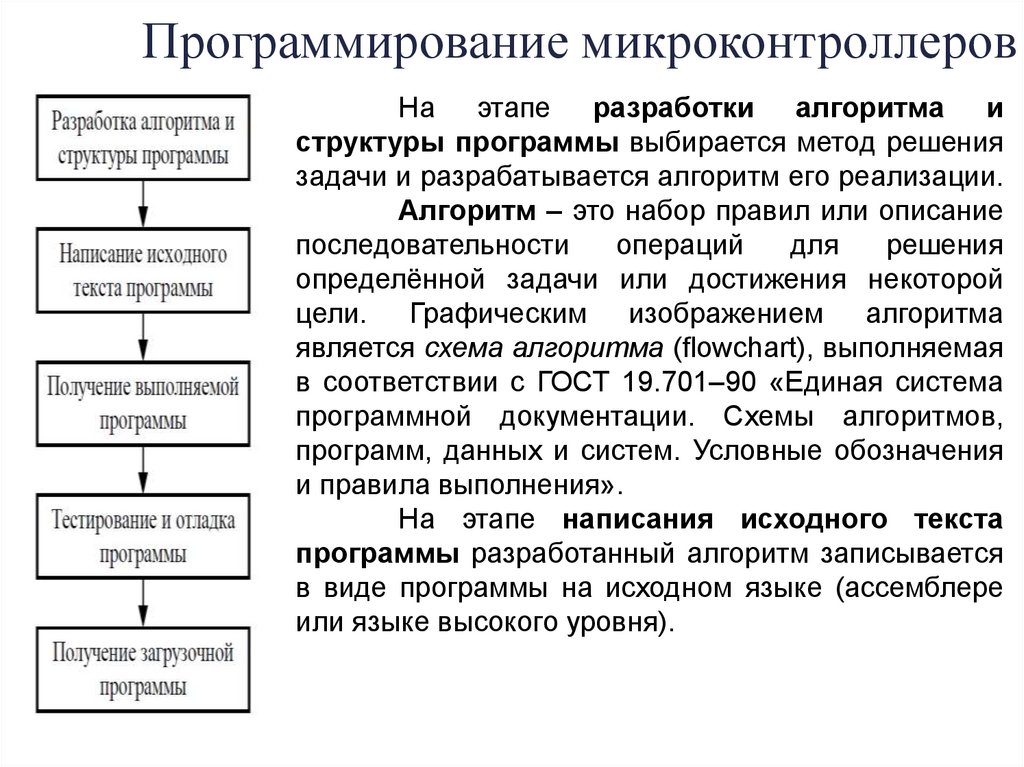

Программирование микроконтроллеровНа этапе разработки алгоритма и

структуры программы выбирается метод решения

задачи и разрабатывается алгоритм его реализации.

Алгоритм – это набор правил или описание

последовательности

операций

для

решения

определённой задачи или достижения некоторой

цели. Графическим изображением алгоритма

является схема алгоритма (flowchart), выполняемая

в соответствии с ГОСТ 19.701–90 «Единая система

программной документации. Схемы алгоритмов,

программ, данных и систем. Условные обозначения

и правила выполнения».

На этапе написания исходного текста

программы разработанный алгоритм записывается

в виде программы на исходном языке (ассемблере

или языке высокого уровня).

82.

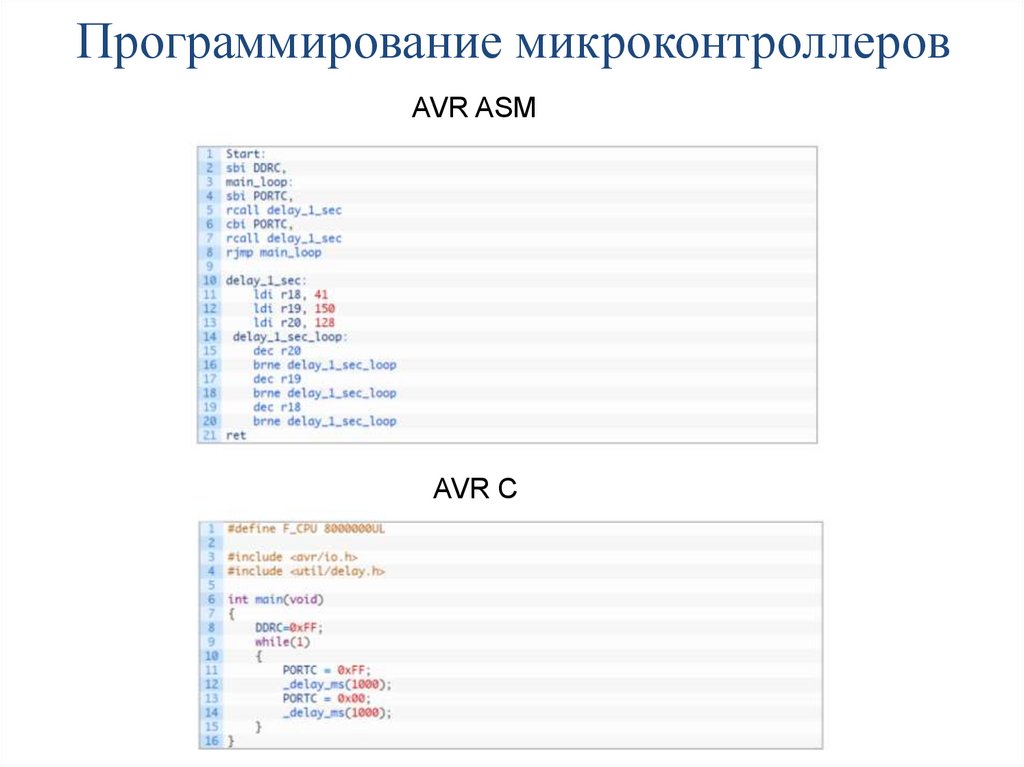

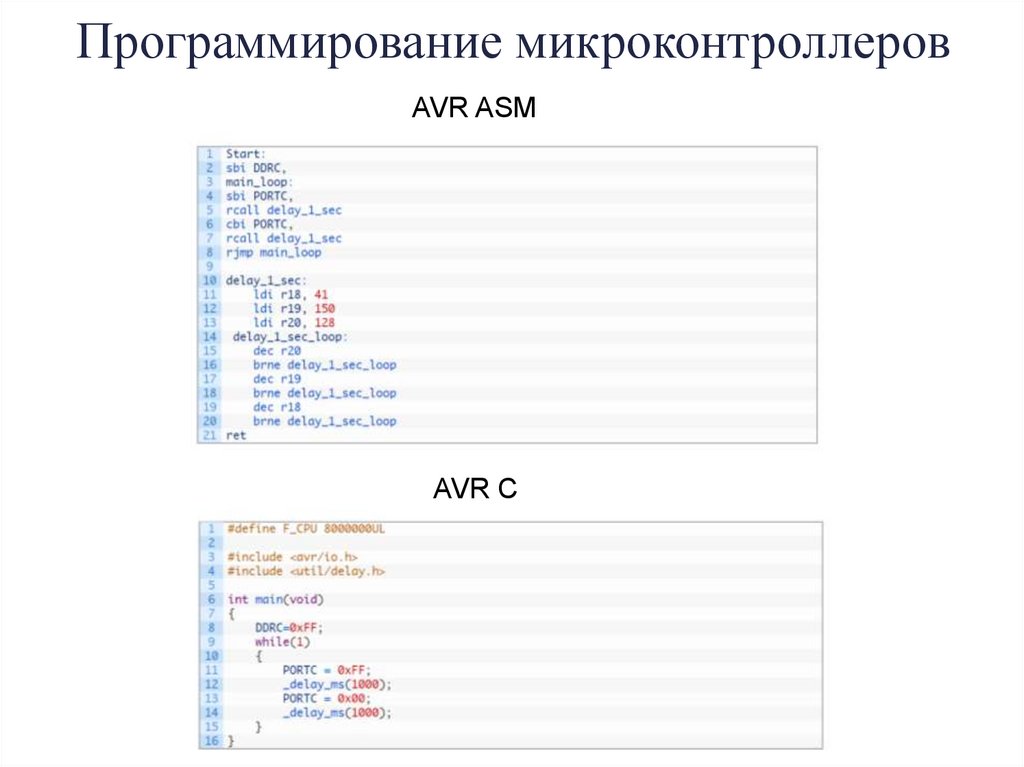

Программирование микроконтроллеровAVR ASM

AVR C

83.

Программирование микроконтроллеровНа этапе получения выполняемой программы

исходный текст программы с помощью специальных

средств (трансляторов, компиляторов, компоновщиков и

др.) преобразуется в исполняемый код.

Транслятором называют программу, служащую

для перевода (трансляции) программ на языке ассемблера

в машинный код, «понимаемый» процессором.

Компилятор представляет собой программу,

преобразующую в эквивалентный машинный код текст

программы на языке высокого уровня. Результатом работы

транслятора

или

компилятора

может

быть

как

выполняемый загрузочный модуль, так и объектный

модуль (программа, команды, переменные и константы

которой не «привязаны» к конкретным адресам ячеек

памяти).

Для построения выполняемой программы из

объектных модулей применяется компоновщик (редактор

связей, linker).

В процессе получения выполняемой программы

из

исходного

текста

программы

устраняются

синтаксические ошибки, состоящие в нарушении правил

синтаксиса используемого языка программирования.

84.

Программирование микроконтроллеровТестирование служит для обнаружения в

программе ошибок.

После тестирования программа должна быть

подвергнута отладке (debug), задачей которой является

локализация ошибки, т. е. нахождение места в программе,

вызывающего ошибку.

На этапе получения загрузочной программы

производится «освобождение» программы от лишних

фрагментов, использовавшихся для тестирования и

отладки. Далее полученная загрузочная программа

заносится в память микроконтроллера.

По

завершении

процесса

разработки

производится документирование, т. е. составление

комплекта документов, необходимых для эксплуатации и

сопровождения программы. Сопровождение программы

(program maintenance) – это процесс внесения изменений,

исправления

оставшихся

ошибок

и

проведения

консультаций по программе, находящейся в эксплуатации.

Виды программных документов регламентированы ГОСТ

19.101–77 «Единая система программной документации.

Виды программ и программных документов».

85.

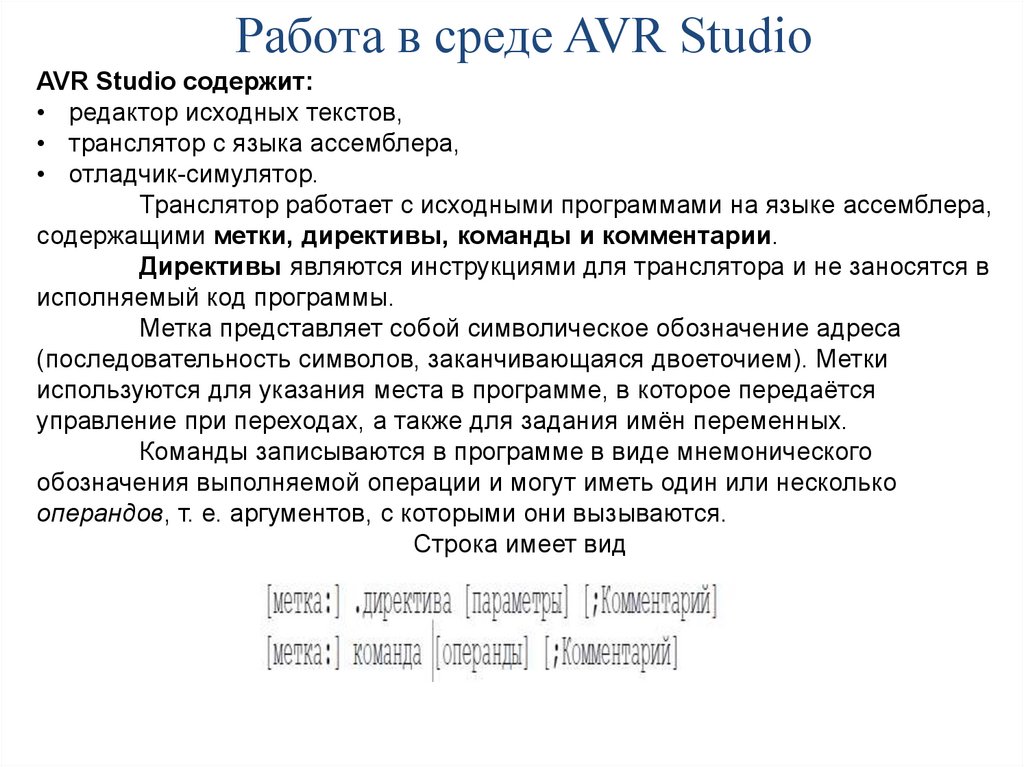

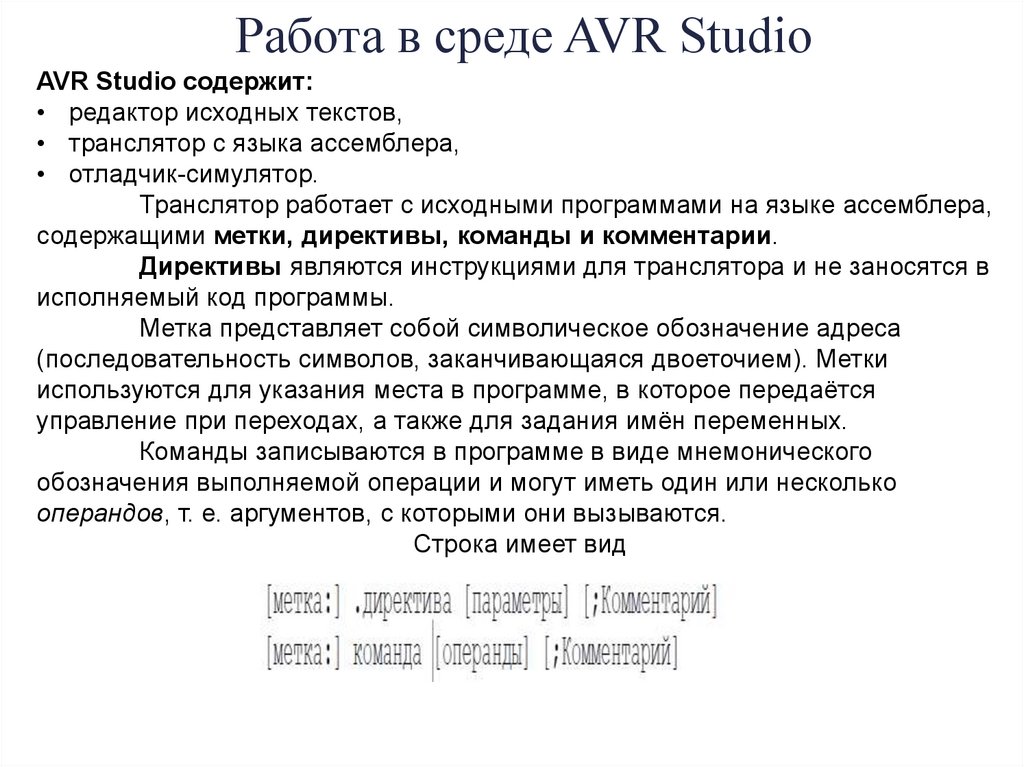

Работа в среде AVR StudioAVR Studio содержит:

• редактор исходных текстов,

• транслятор с языка ассемблера,

• отладчик-симулятор.

Транслятор работает с исходными программами на языке ассемблера,

содержащими метки, директивы, команды и комментарии.

Директивы являются инструкциями для транслятора и не заносятся в

исполняемый код программы.

Метка представляет собой символическое обозначение адреса

(последовательность символов, заканчивающаяся двоеточием). Метки

используются для указания места в программе, в которое передаётся

управление при переходах, а также для задания имён переменных.

Команды записываются в программе в виде мнемонического

обозначения выполняемой операции и могут иметь один или несколько

операндов, т. е. аргументов, с которыми они вызываются.

Строка имеет вид

86.

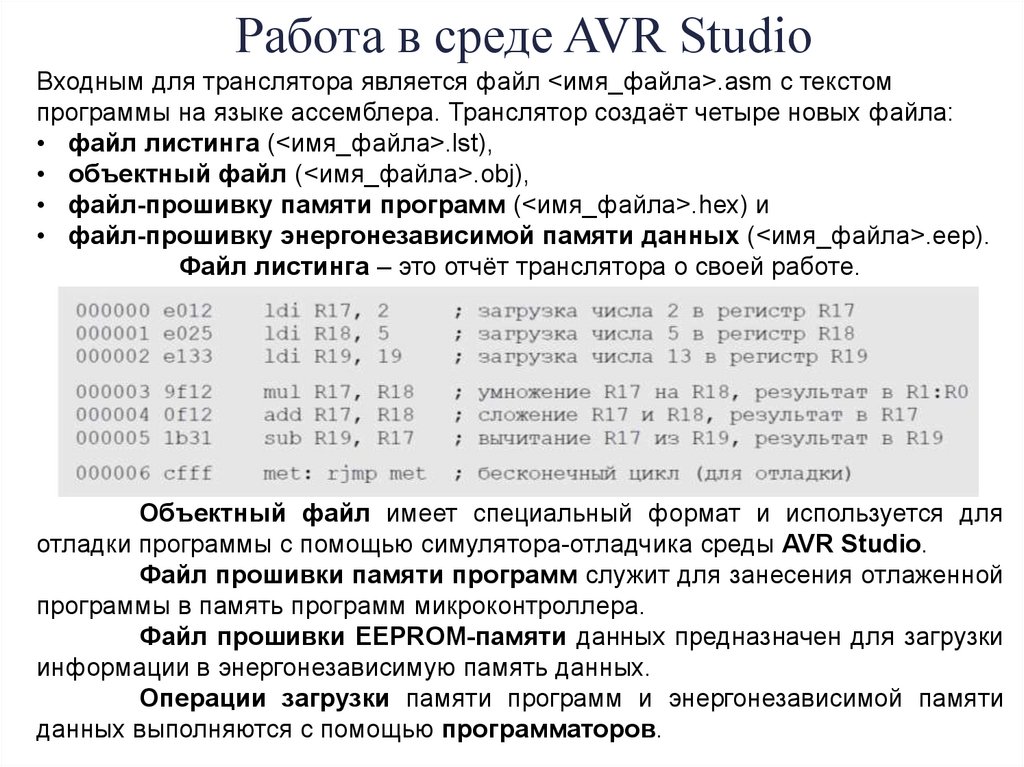

Работа в среде AVR StudioВходным для транслятора является файл <имя_файла>.asm с текстом

программы на языке ассемблера. Транслятор создаёт четыре новых файла:

• файл листинга (<имя_файла>.lst),

• объектный файл (<имя_файла>.obj),

• файл-прошивку памяти программ (<имя_файла>.hex) и

• файл-прошивку энергонезависимой памяти данных (<имя_файла>.eep).

Файл листинга – это отчёт транслятора о своей работе.

Объектный файл имеет специальный формат и используется для

отладки программы с помощью симулятора-отладчика среды AVR Studio.

Файл прошивки памяти программ служит для занесения отлаженной

программы в память программ микроконтроллера.

Файл прошивки EEPROM-памяти данных предназначен для загрузки

информации в энергонезависимую память данных.

Операции загрузки памяти программ и энергонезависимой памяти

данных выполняются с помощью программаторов.

87.

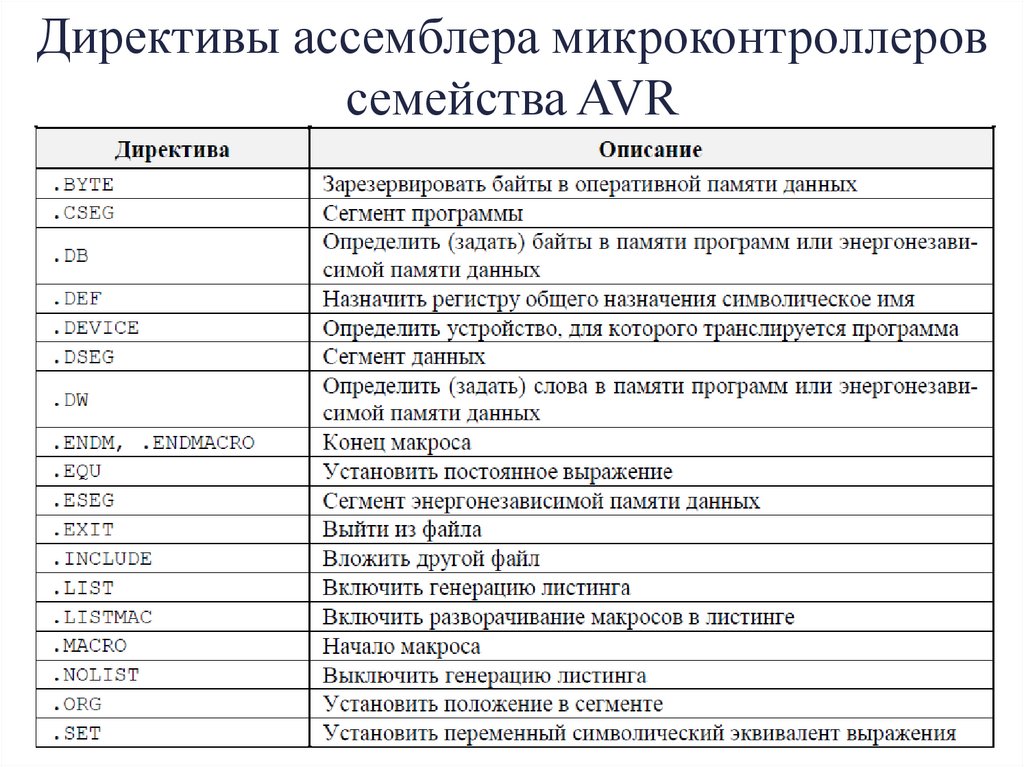

Директивы ассемблера микроконтроллеровсемейства AVR

88.

Описание регистров из области ввода/выводаИмя

регистра

ACSR

UBRR

UCR

USR

UDR

SPCR

SPSR

SPDR

PIND

DDRD

PORTD

PINC

DDRC

PORTC

PINB

DDRB

PORTB

PINA

DDRA

PORTA

EECR

EEDR

EEARL

Адрес

ввода/

вывода

0x08

0x09

0х0А

0x0В

0х0С

0x0D

0х0Е

0x0F

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

0x1А

0x1В

0x1С

0x1D

0x1Е

Адрес

SRAM

Описание

0x28

0x29

0х2А

0x2В

0х2С

0x2D

0х2Е

0x2F

0x30

0x31

0x32

0x33

0x34

0x35

0x36

0x37

0x38

0x39

0х3А

0х3В

0х3С

0x3D

0х3Е

Регистр управления и состояния аналогового компаратора

Регистр скорости передачи данных через UART

Регистр управления приемопередатчиком UART

Регистр состояния приемопередатчика UART

Регистр данных приемопередатчика UART

Регистр управления интерфейсом SPI

Регистр состояния интерфейса SPI

Регистр ввода/вывода данных интерфейса SPI

Выводы порта D

Регистр направления передачи данных порта D

Регистр данных порта D

Выводы порта С

Регистр направления передачи данных порта С

Регистр данных порта С

Выводы порта В

Регистр направления передачи данных порта В

Регистр данных порта В

Выводы порта А

Регистр направления передачи данных порта А

Регистр данных порта А

Регистр управления памяти EEPROM

Регистр данных памяти EEPROM

Регистр адреса памяти EEPROM (младший байт)

89.

Описание регистров из области ввода/выводаEEARH

0x1F

0x3F

Регистр адреса памяти EEPROM (старший байт)

WDTCR

0x21

0x41

Регистр управления сторожевым таймером

ICR1L

0x24

0x44

Регистр захвата таймера/счетчика Т/С1 (младший байт)

ICR1H

0x25

0x45

Регистр захвата таймера/счетчика Т/С1 (младший байт)

OCR1BL

0x28

0x48

Регистр сравнения В таймера Т/С1 (младший байт)

OCR1BH

0x29

0x49

Регистр сравнения В таймера Т/С1 (старший байт)

OCR1AL

0х2А

0х4А

Регистр сравнения А таймера Т/С1 (младший байт)

OCR1AH

0x2В

0x4В

Регистр сравнения А таймера Т/С1 (старший байт)

TCNT1L

0х2С

0х4С

Счетный регистр таймера/счетчика Т/С1 (младший байт)

TCNT1H

0x2D

0x4D

Счетный регистр таймера/счетчика Т/С1 (старший байт)

TCCR1B

0x2Е

0х4Е

Регистр управления В таймера/счетчика Т/С1

TCCR1A

0x2F

0x4F

Регистр управления А таймера/счетчика Т/С1

TCNT0

0x32

0x52

Счетный регистр таймера/счетчика Т/С0

TCCR0

0x33

0x53

Регистр управления таймера/счетчика Т/С0

MCUCR

0x35

0x55

Регистр управления микроконтроллером

TIFR

0x38

0x58

Регистр флагов прерываний от таймеров/счетчиков

TIMSK

0x39

0x59

Регистр маскирования прерываний от таймеров

GIFR

0х3А

0х5А

Общий регистр флагов прерываний

GIMSK

0х3В

0x5В

Общий регистр маскирования прерываний

SPL

0x3D

0x5D

Указатель стека (младший байт)

SPH

0х3Е

0х5Е

Указатель стека (старший байт)

SREG

0x3F

0x5F

Регистр состояния

90.

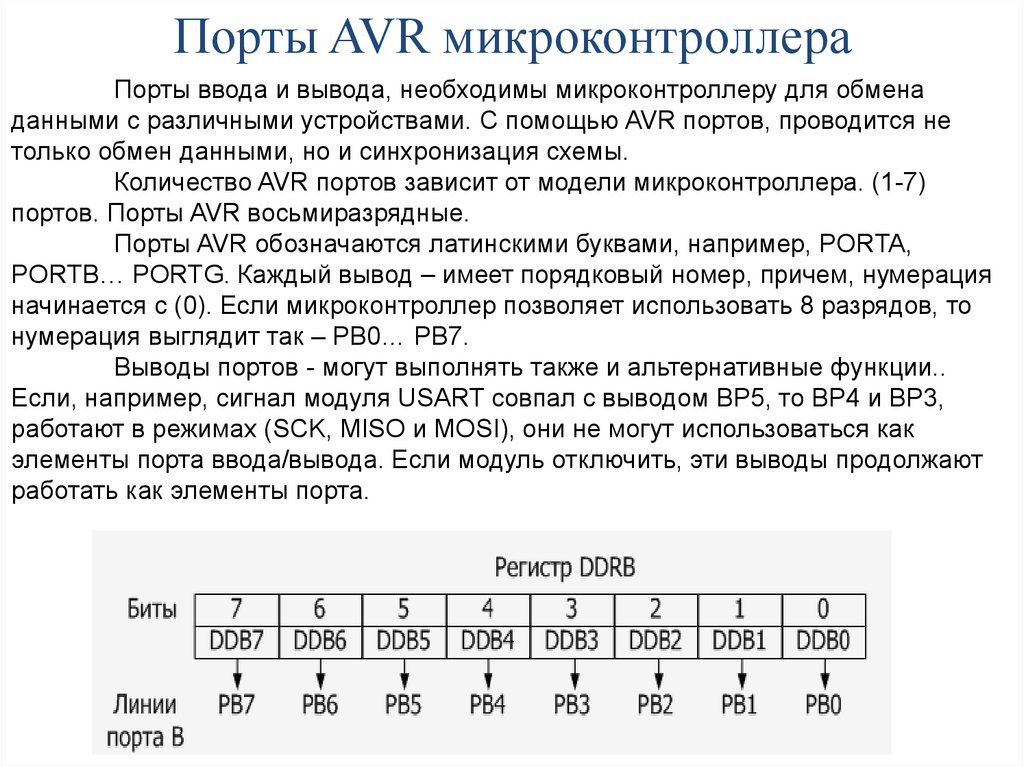

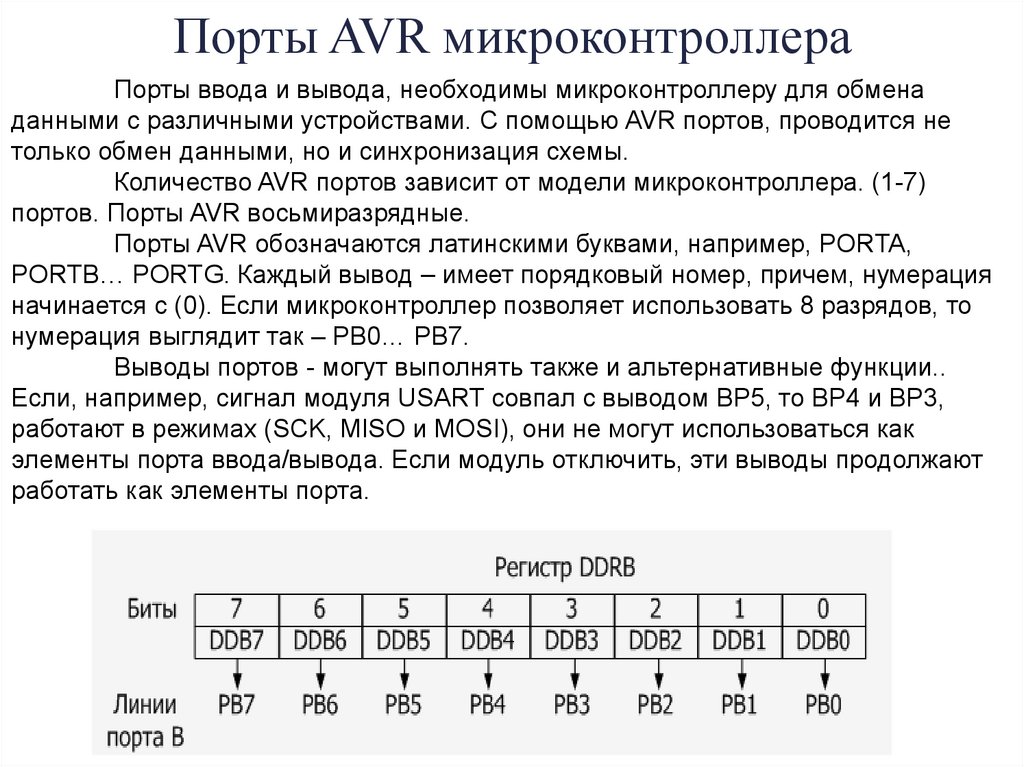

Порты AVR микроконтроллераПорты ввода и вывода, необходимы микроконтроллеру для обмена

данными с различными устройствами. С помощью AVR портов, проводится не

только обмен данными, но и синхронизация схемы.

Количество AVR портов зависит от модели микроконтроллера. (1-7)

портов. Порты AVR восьмиразрядные.

Порты AVR обозначаются латинскими буквами, например, PORTA,

PORTB… PORTG. Каждый вывод – имеет порядковый номер, причем, нумерация

начинается с (0). Если микроконтроллер позволяет использовать 8 разрядов, то

нумерация выглядит так – PB0… PB7.

Выводы портов - могут выполнять также и альтернативные функции..

Если, например, сигнал модуля USART совпал с выводом BP5, то BP4 и BP3,

работают в режимах (SCK, MISO и MOSI), они не могут использоваться как

элементы порта ввода/вывода. Если модуль отключить, эти выводы продолжают

работать как элементы порта.

91.

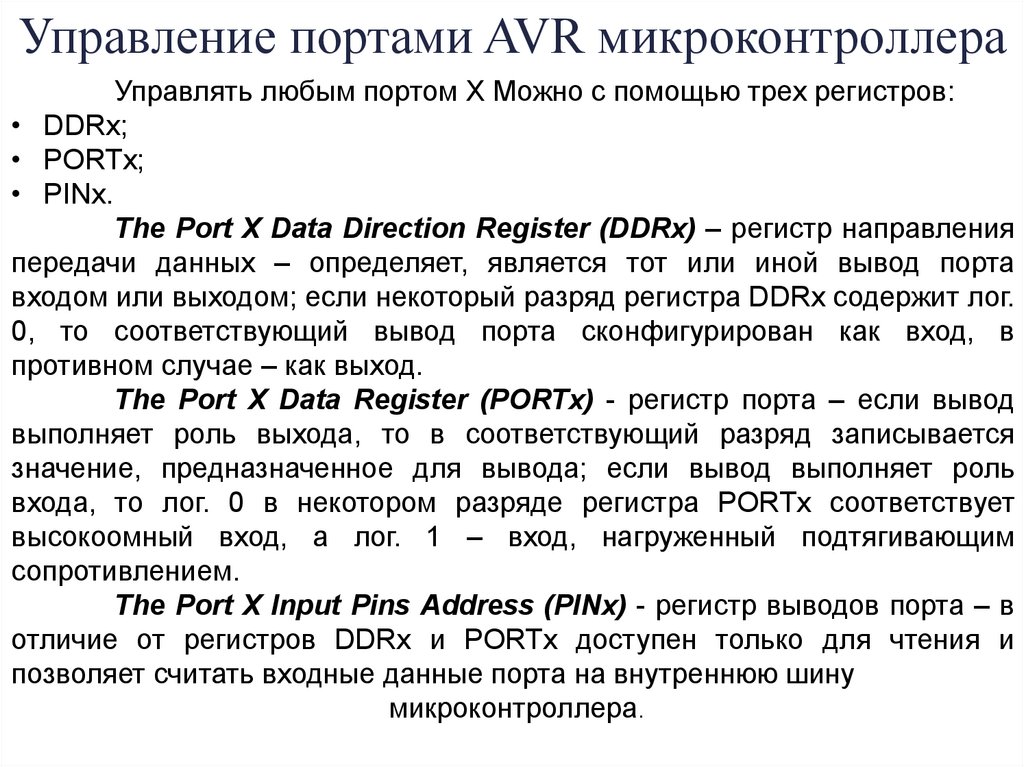

Управление портами AVR микроконтроллераУправлять любым портом X Можно с помощью трех регистров:

• DDRx;

• PORTx;

• PINx.

The Port X Data Direction Register (DDRx) – регистр направления

передачи данных – определяет, является тот или иной вывод порта

входом или выходом; если некоторый разряд регистра DDRx содержит лог.

0, то соответствующий вывод порта сконфигурирован как вход, в

противном случае – как выход.

The Port X Data Register (PORTx) - регистр порта – если вывод

выполняет роль выхода, то в соответствующий разряд записывается

значение, предназначенное для вывода; если вывод выполняет роль

входа, то лог. 0 в некотором разряде регистра PORTx соответствует

высокоомный вход, а лог. 1 – вход, нагруженный подтягивающим

сопротивлением.

The Port X Input Pins Address (PINx) - регистр выводов порта – в

отличие от регистров DDRx и PORTx доступен только для чтения и

позволяет считать входные данные порта на внутреннюю шину

микроконтроллера.

92.

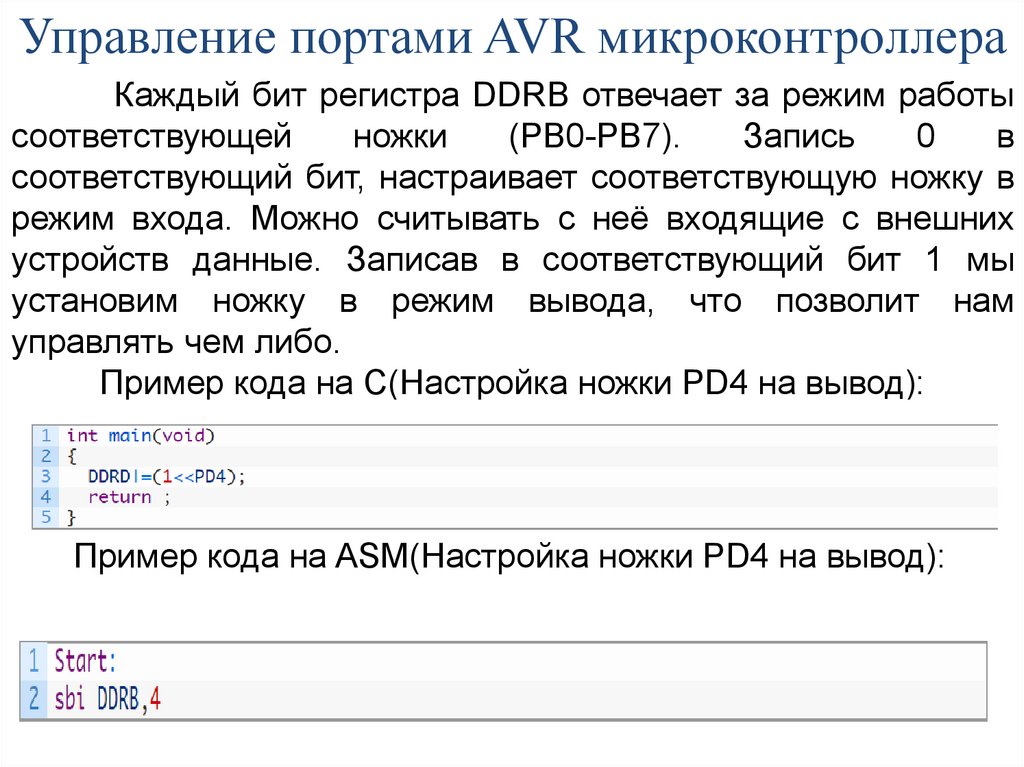

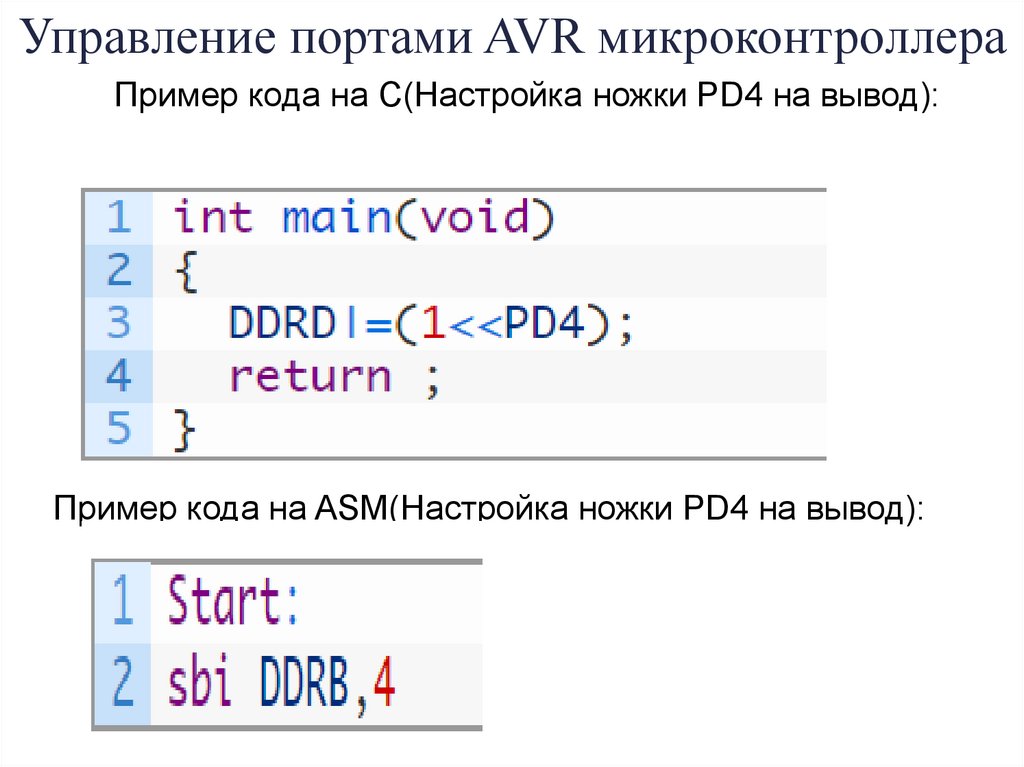

Управление портами AVR микроконтроллераКаждый бит регистра DDRB отвечает за режим работы

соответствующей

ножки

(PB0-PB7).

Запись

0

в

соответствующий бит, настраивает соответствующую ножку в

режим входа. Можно считывать с неё входящие с внешних

устройств данные. Записав в соответствующий бит 1 мы

установим ножку в режим вывода, что позволит нам

управлять чем либо.

Пример кода на C(Настройка ножки PD4 на вывод):

Пример кода на ASM(Настройка ножки PD4 на вывод):

93.

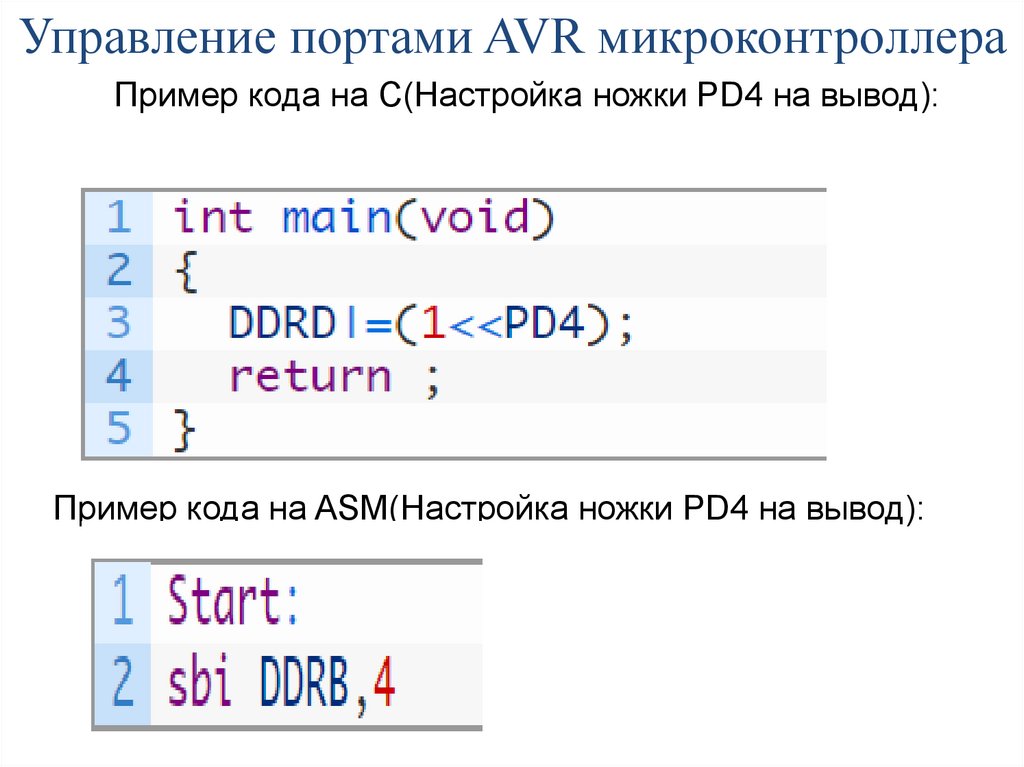

Управление портами AVR микроконтроллераПример кода на C(Настройка ножки PD4 на вывод):

Пример кода на ASM(Настройка ножки PD4 на вывод):

94.

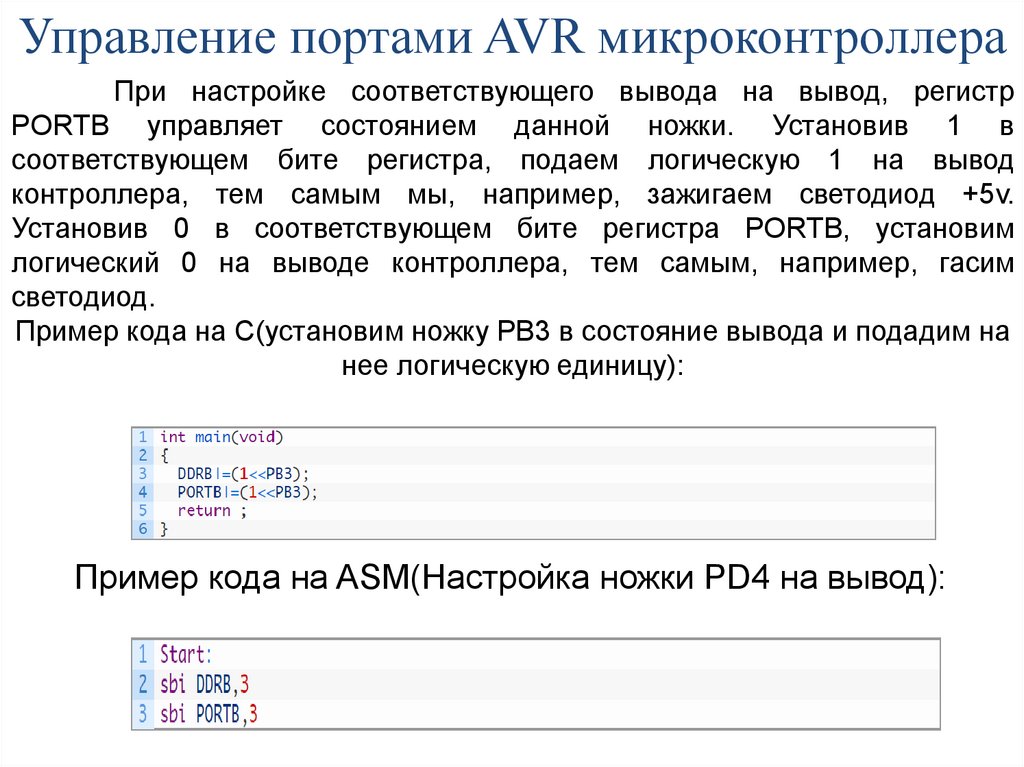

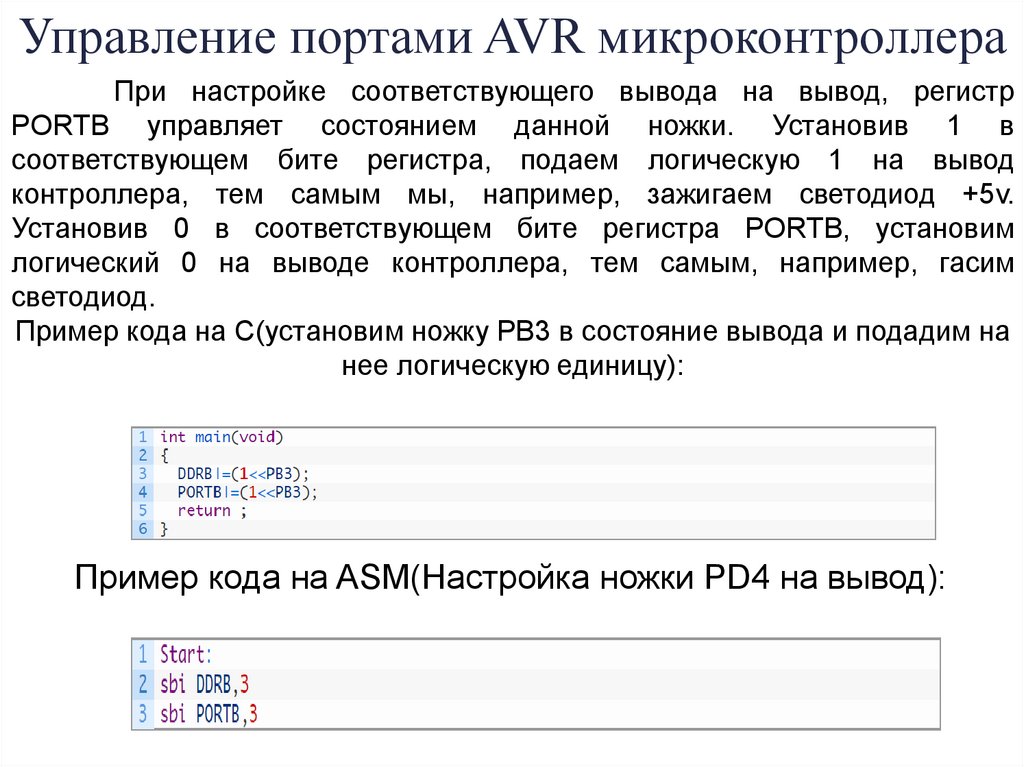

Управление портами AVR микроконтроллераПри настройке соответствующего вывода на вывод, регистр

PORTB управляет состоянием данной ножки. Установив 1 в

соответствующем бите регистра, подаем логическую 1 на вывод

контроллера, тем самым мы, например, зажигаем светодиод +5v.

Установив 0 в соответствующем бите регистра PORTB, установим

логический 0 на выводе контроллера, тем самым, например, гасим

светодиод.

Пример кода на C(установим ножку PB3 в состояние вывода и подадим на

нее логическую единицу):

Пример кода на ASM(Настройка ножки PD4 на вывод):

95.

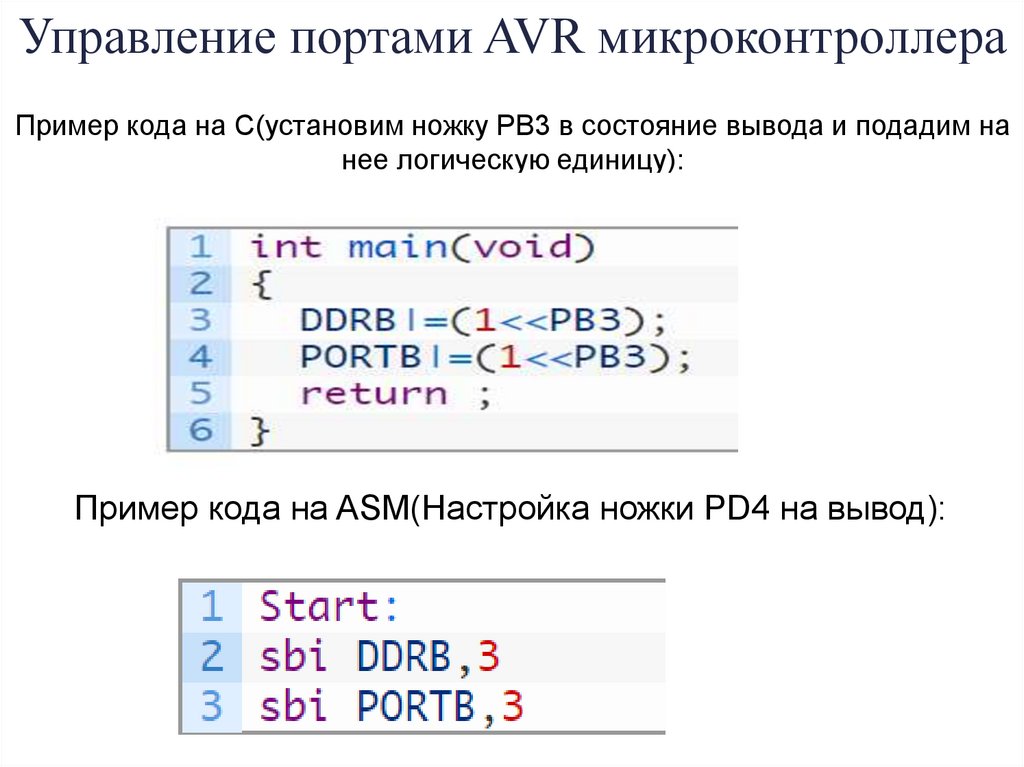

Управление портами AVR микроконтроллераПример кода на C(установим ножку PB3 в состояние вывода и подадим на

нее логическую единицу):

Пример кода на ASM(Настройка ножки PD4 на вывод):

96.

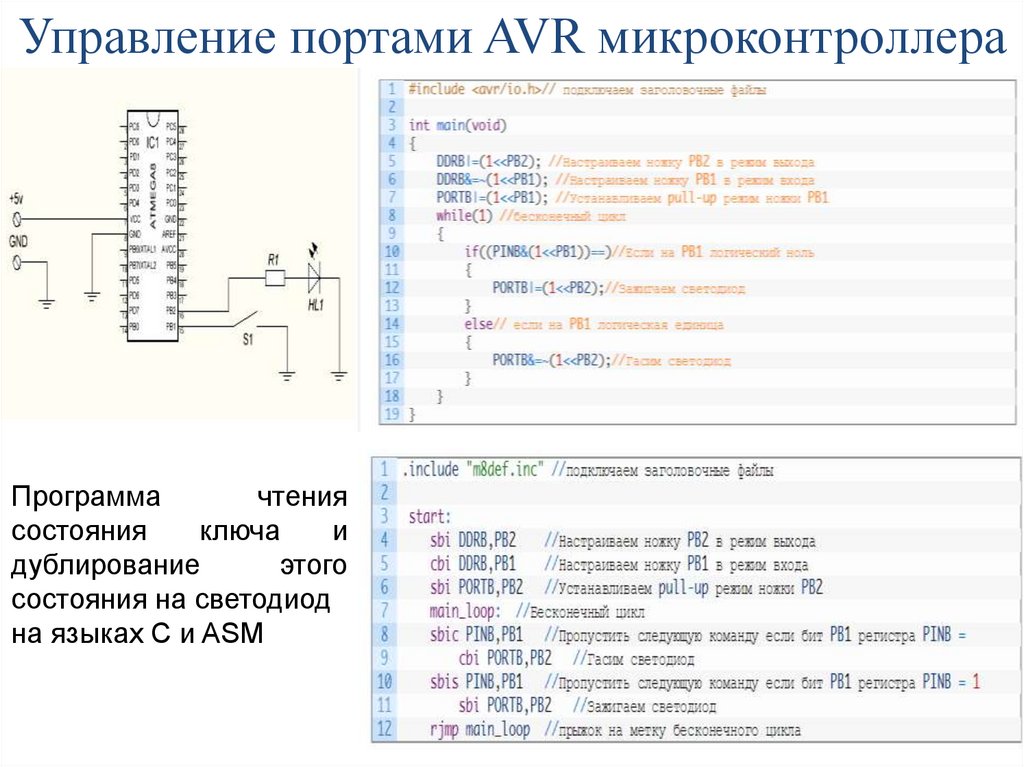

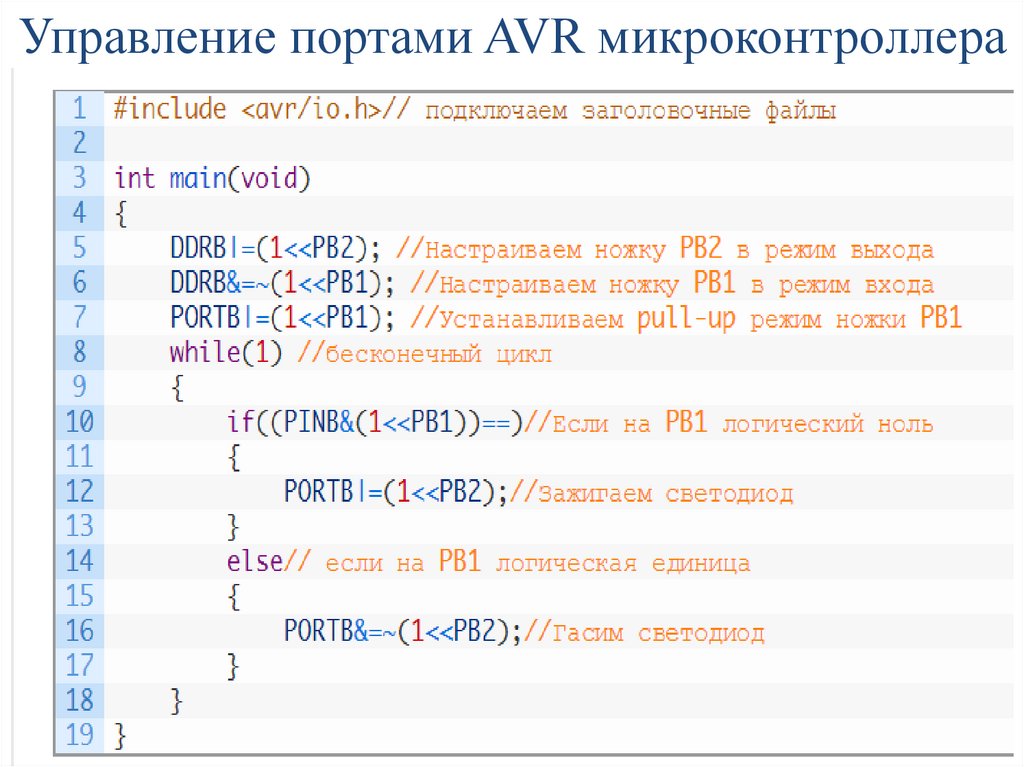

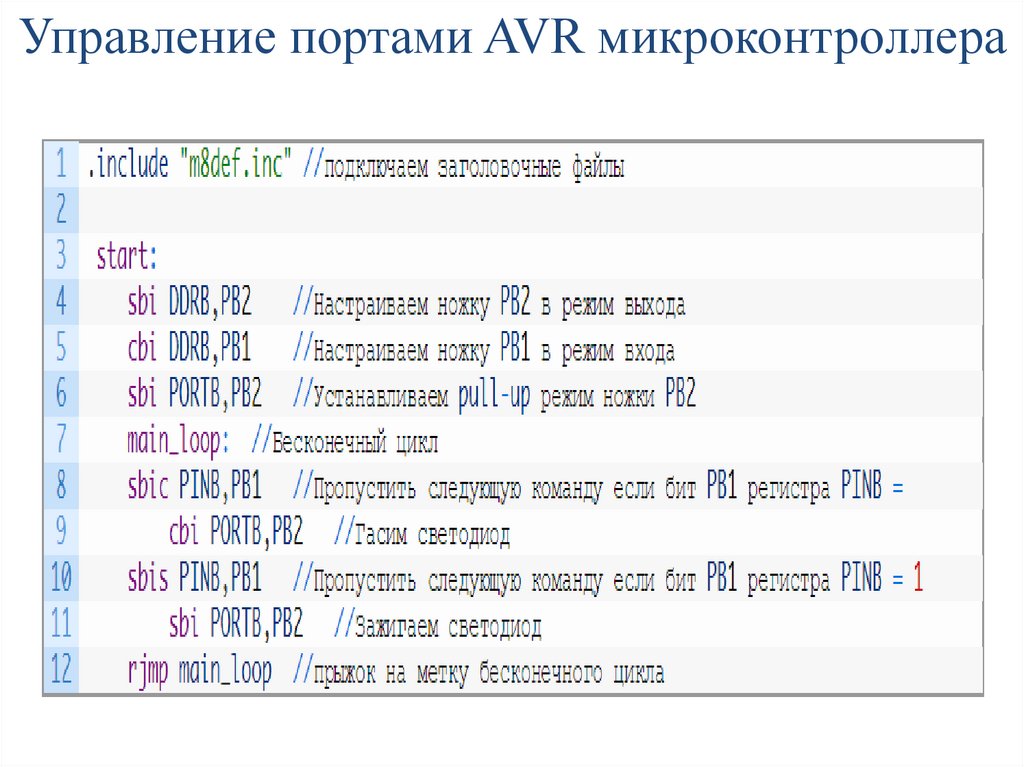

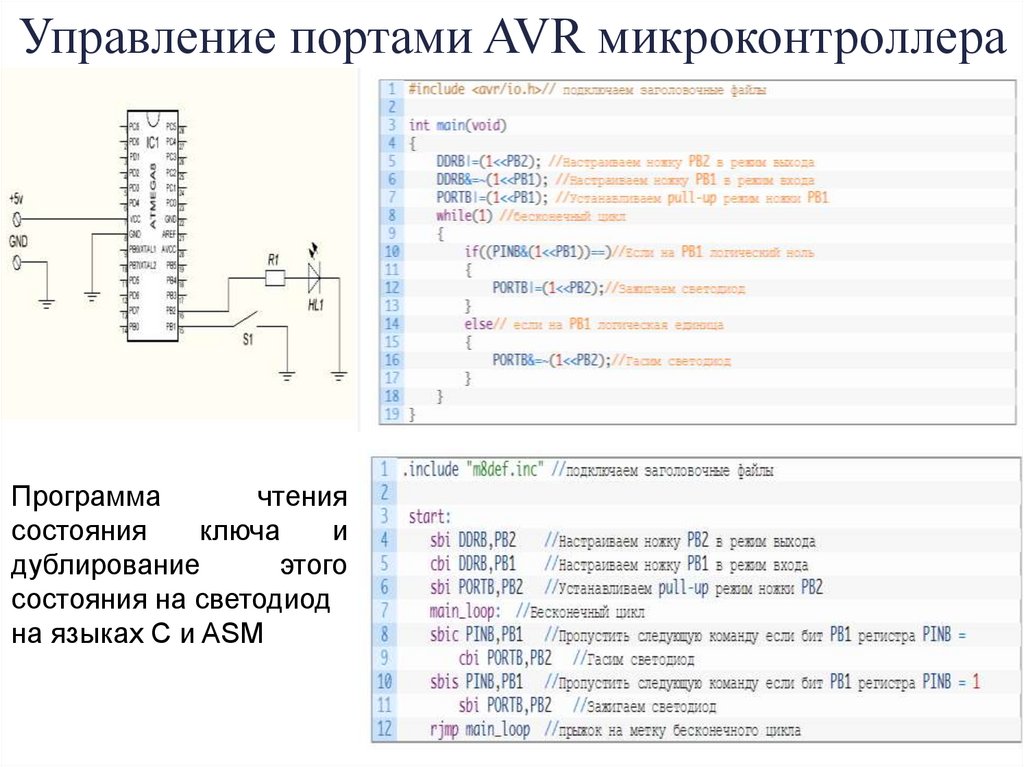

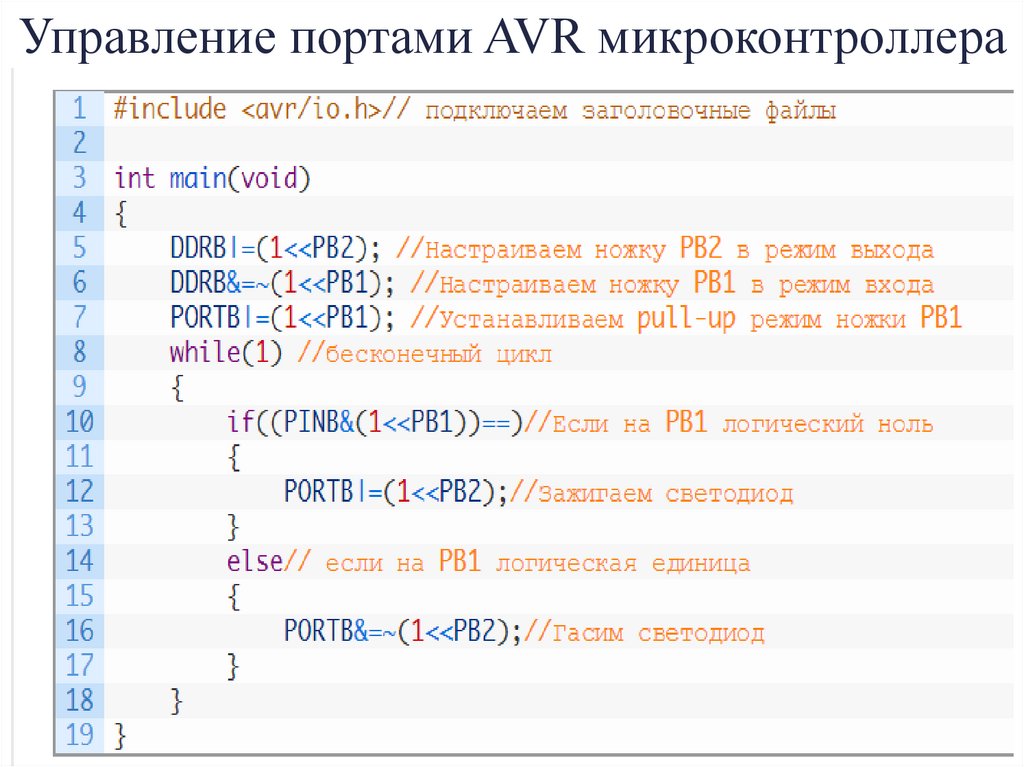

Управление портами AVR микроконтроллераПрограмма

чтения

состояния

ключа

и

дублирование

этого

состояния на светодиод

на языках С и ASM

97.

Управление портами AVR микроконтроллера98.

Управление портами AVR микроконтроллера99.

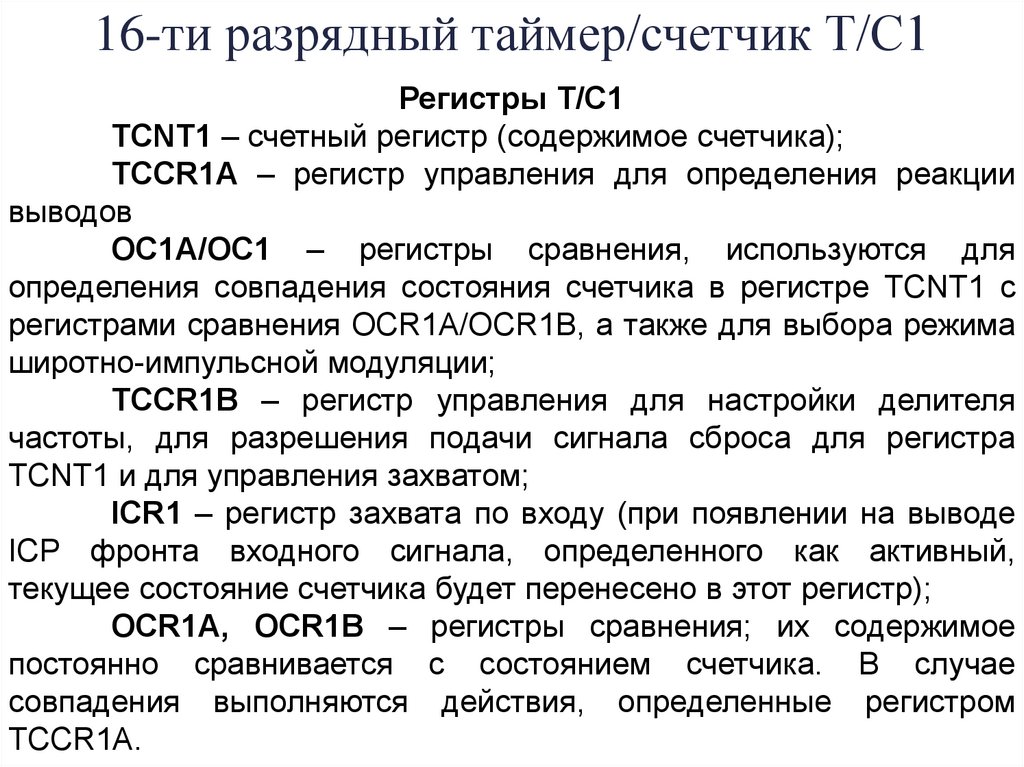

16-ти разрядный таймер/счетчик Т/С1Регистры Т/С1

TCNT1 – счетный регистр (содержимое счетчика);

TCCR1А – регистр управления для определения реакции

выводов

ОС1А/ОС1 – регистры сравнения, используются для

определения совпадения состояния счетчика в регистре TCNT1 с

регистрами сравнения OCR1A/OCR1B, а также для выбора режима

широтно-импульсной модуляции;

TCCR1B – регистр управления для настройки делителя

частоты, для разрешения подачи сигнала сброса для регистра

TCNT1 и для управления захватом;

ICR1 – регистр захвата по входу (при появлении на выводе

ICP фронта входного сигнала, определенного как активный,

текущее состояние счетчика будет перенесено в этот регистр);

OCR1A, OCR1B – регистры сравнения; их содержимое

постоянно сравнивается с состоянием счетчика. В случае

совпадения выполняются действия, определенные регистром

TCCR1A.

100.

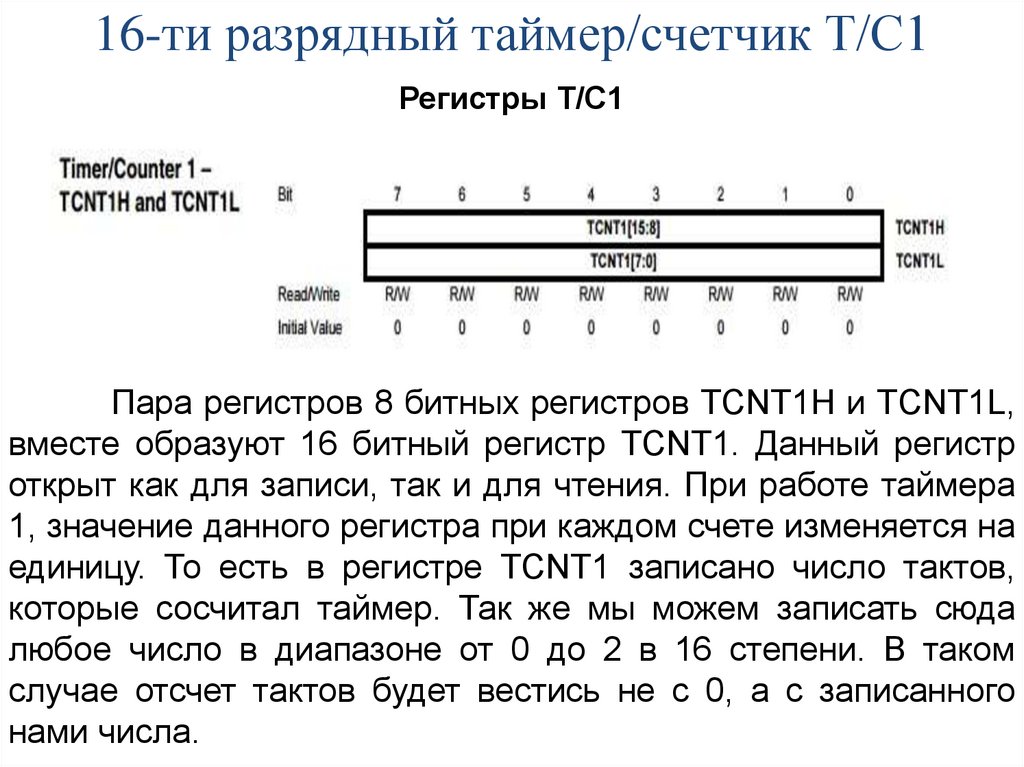

16-ти разрядный таймер/счетчик Т/С1Регистры Т/С1

Пара регистров 8 битных регистров TCNT1H и TCNT1L,

вместе образуют 16 битный регистр TCNT1. Данный регистр

открыт как для записи, так и для чтения. При работе таймера

1, значение данного регистра при каждом счете изменяется на

единицу. То есть в регистре TCNT1 записано число тактов,

которые сосчитал таймер. Так же мы можем записать сюда

любое число в диапазоне от 0 до 2 в 16 степени. В таком

случае отсчет тактов будет вестись не с 0, а с записанного

нами числа.

101.

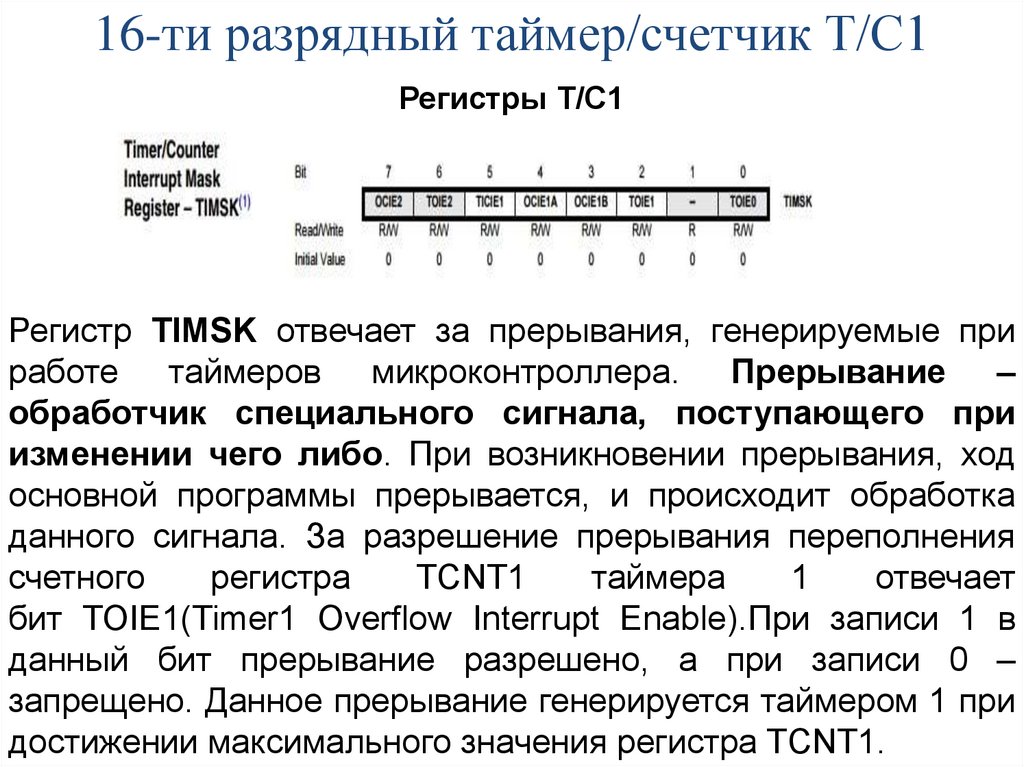

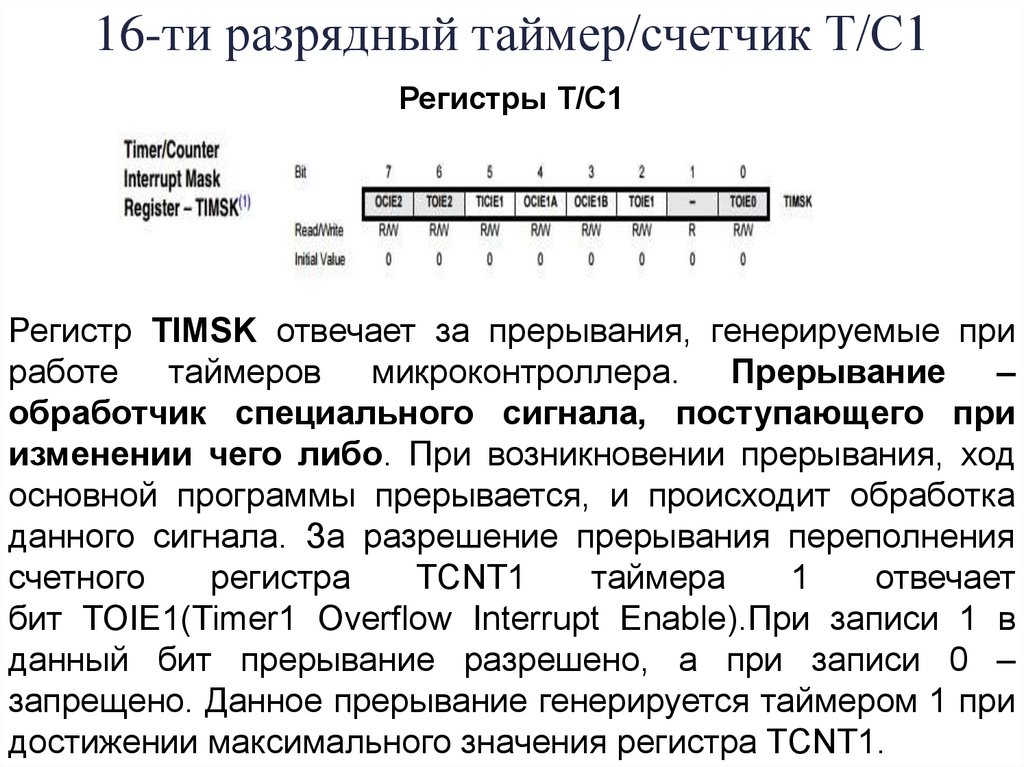

16-ти разрядный таймер/счетчик Т/С1Регистры Т/С1

Регистр TIMSK отвечает за прерывания, генерируемые при

работе таймеров микроконтроллера. Прерывание –

обработчик специального сигнала, поступающего при

изменении чего либо. При возникновении прерывания, ход

основной программы прерывается, и происходит обработка

данного сигнала. За разрешение прерывания переполнения

счетного

регистра

TCNT1

таймера

1

отвечает

бит TOIE1(Timer1 Overflow Interrupt Enable).При записи 1 в

данный бит прерывание разрешено, а при записи 0 –

запрещено. Данное прерывание генерируется таймером 1 при

достижении максимального значения регистра TCNT1.

102.

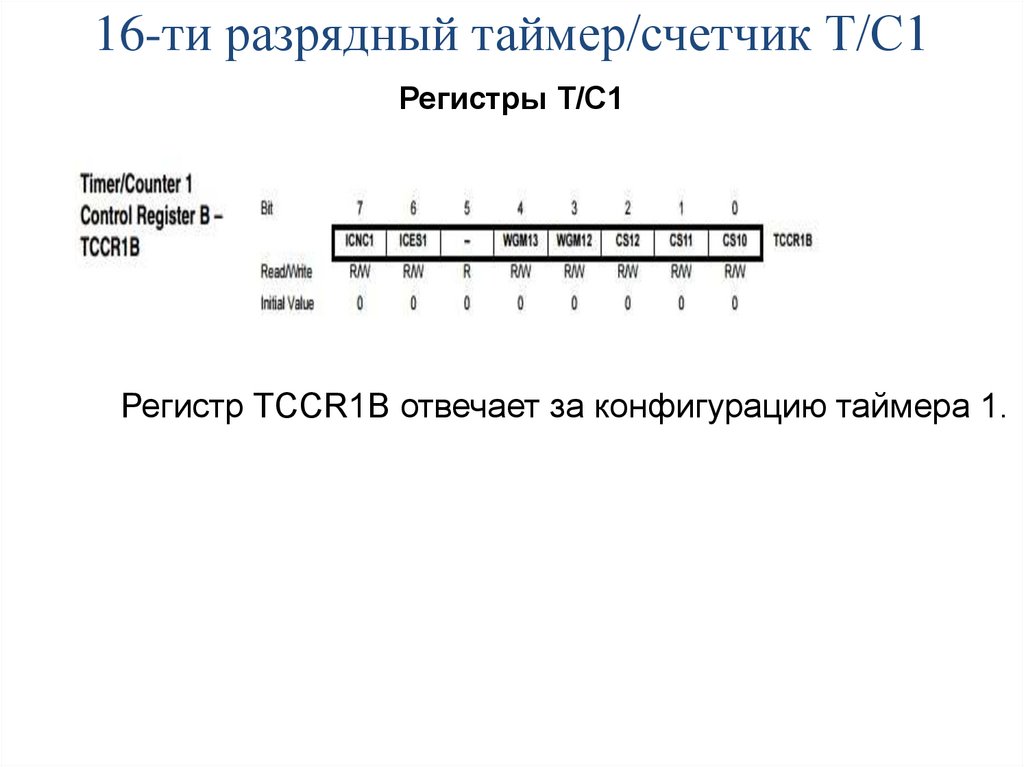

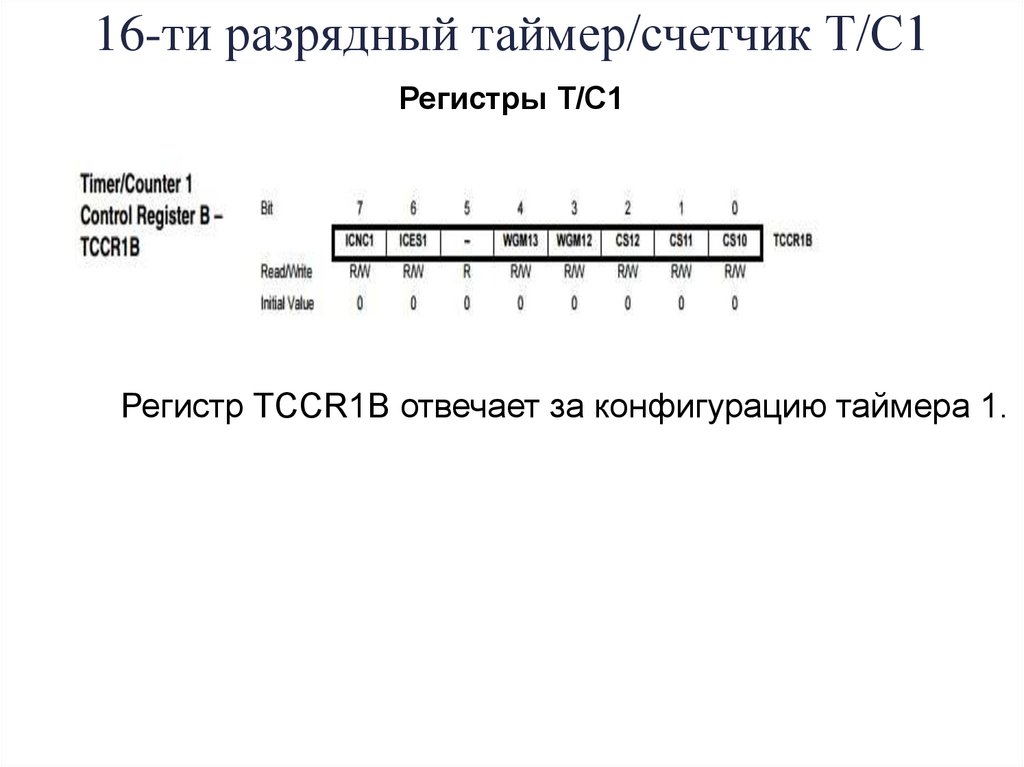

16-ти разрядный таймер/счетчик Т/С1Регистры Т/С1

Регистр TCCR1B отвечает за конфигурацию таймера 1.

103.

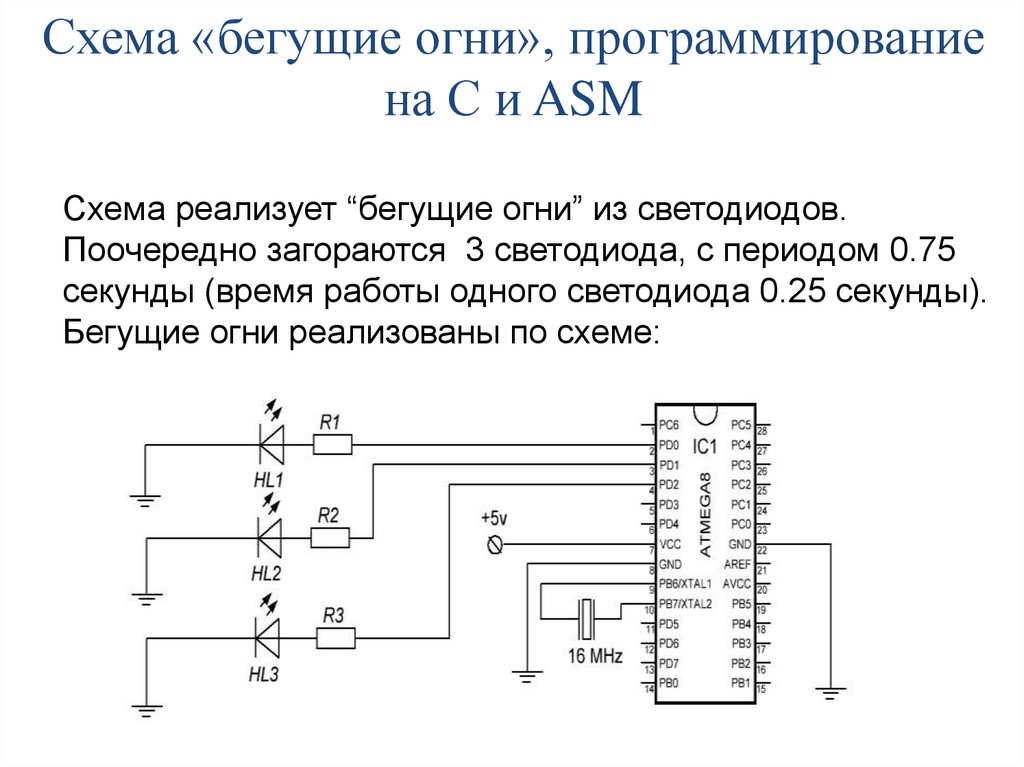

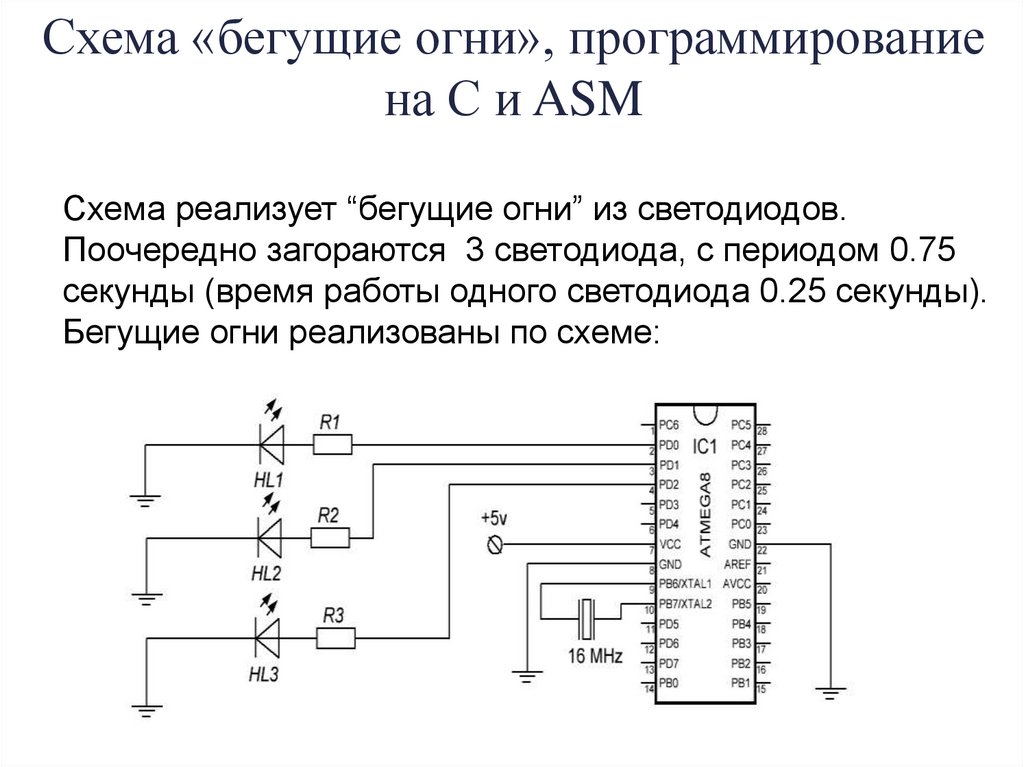

Схема «бегущие огни», программированиена С и ASM

Схема реализует “бегущие огни” из светодиодов.

Поочередно загораются 3 светодиода, с периодом 0.75

секунды (время работы одного светодиода 0.25 секунды).

Бегущие огни реализованы по схеме:

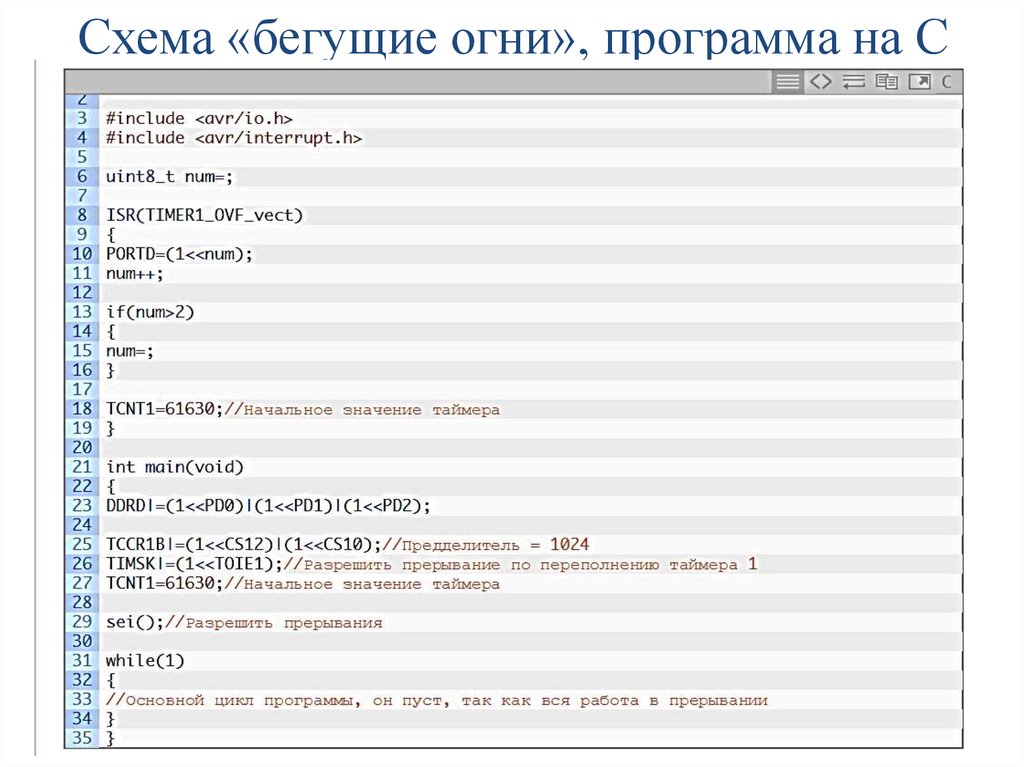

104.

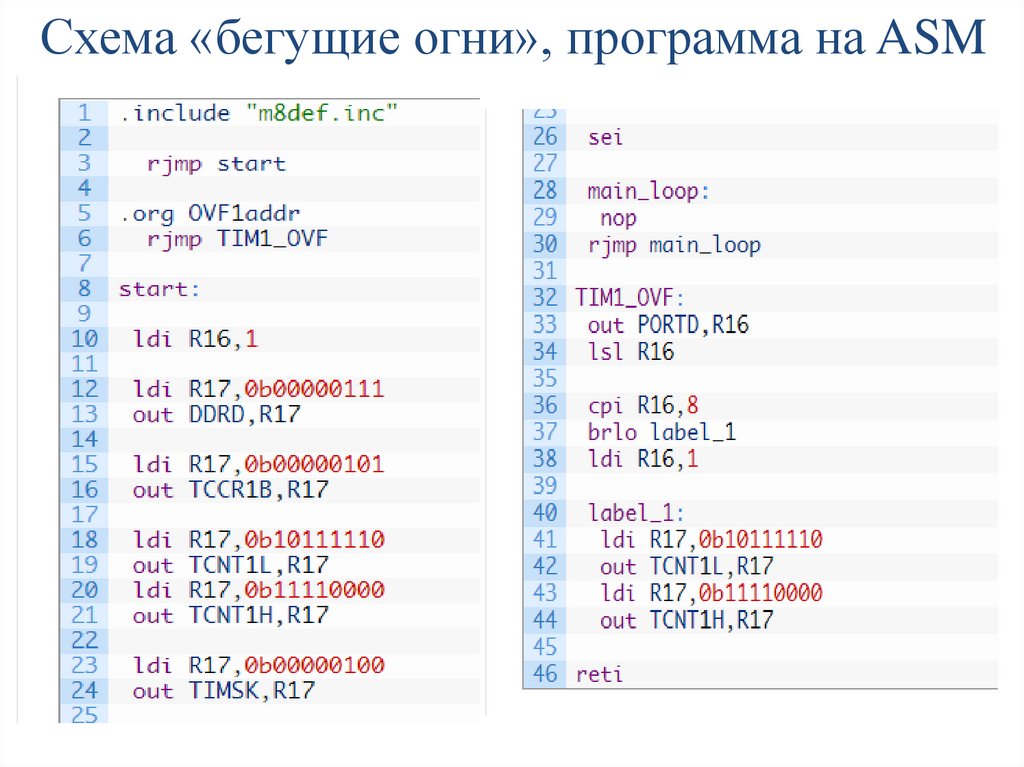

Схема «бегущие огни», программа на С105.

Схема «бегущие огни», программа на ASM106.

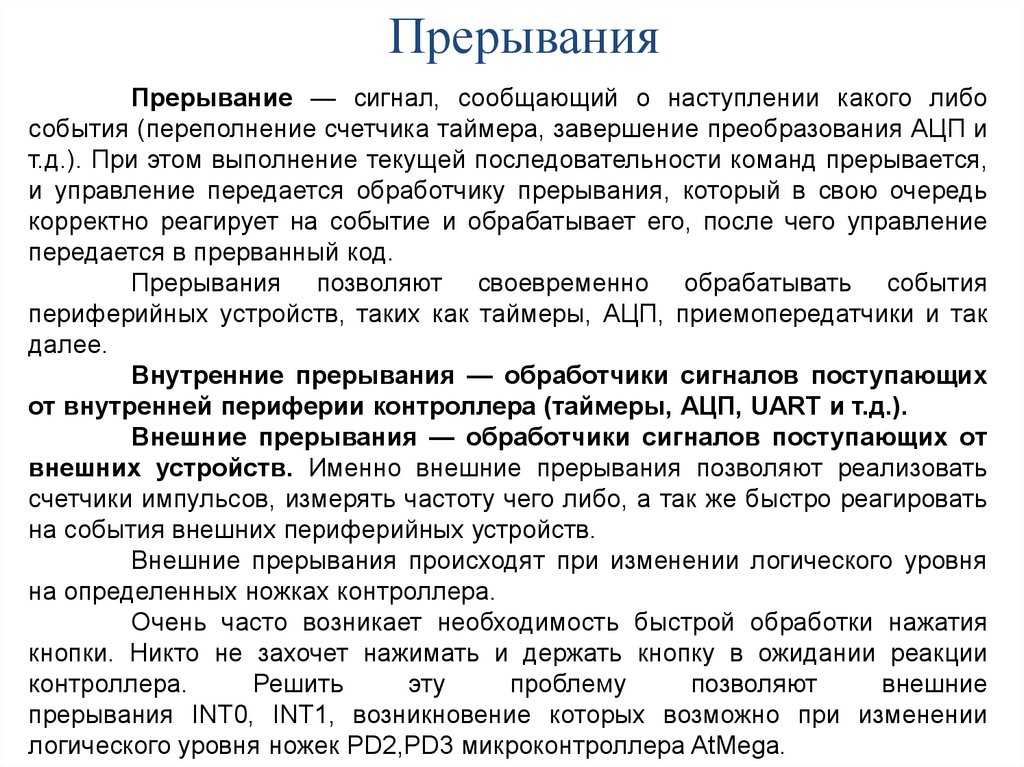

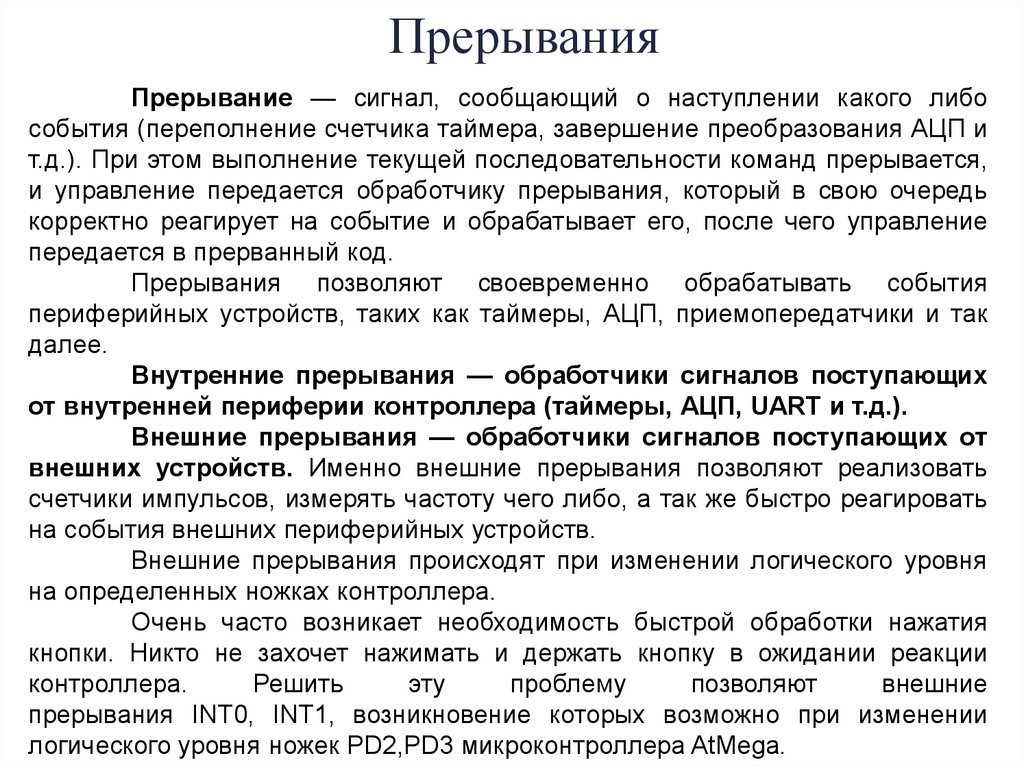

ПрерыванияПрерывание — сигнал, сообщающий о наступлении какого либо

события (переполнение счетчика таймера, завершение преобразования АЦП и

т.д.). При этом выполнение текущей последовательности команд прерывается,

и управление передается обработчику прерывания, который в свою очередь

корректно реагирует на событие и обрабатывает его, после чего управление

передается в прерванный код.

Прерывания позволяют своевременно обрабатывать события

периферийных устройств, таких как таймеры, АЦП, приемопередатчики и так

далее.

Внутренние прерывания — обработчики сигналов поступающих

от внутренней периферии контроллера (таймеры, АЦП, UART и т.д.).

Внешние прерывания — обработчики сигналов поступающих от

внешних устройств. Именно внешние прерывания позволяют реализовать

счетчики импульсов, измерять частоту чего либо, а так же быстро реагировать

на события внешних периферийных устройств.

Внешние прерывания происходят при изменении логического уровня

на определенных ножках контроллера.

Очень часто возникает необходимость быстрой обработки нажатия

кнопки. Никто не захочет нажимать и держать кнопку в ожидании реакции

контроллера.

Решить

эту

проблему

позволяют

внешние

прерывания INT0, INT1, возникновение которых возможно при изменении

логического уровня ножек PD2,PD3 микроконтроллера AtMega.

107.

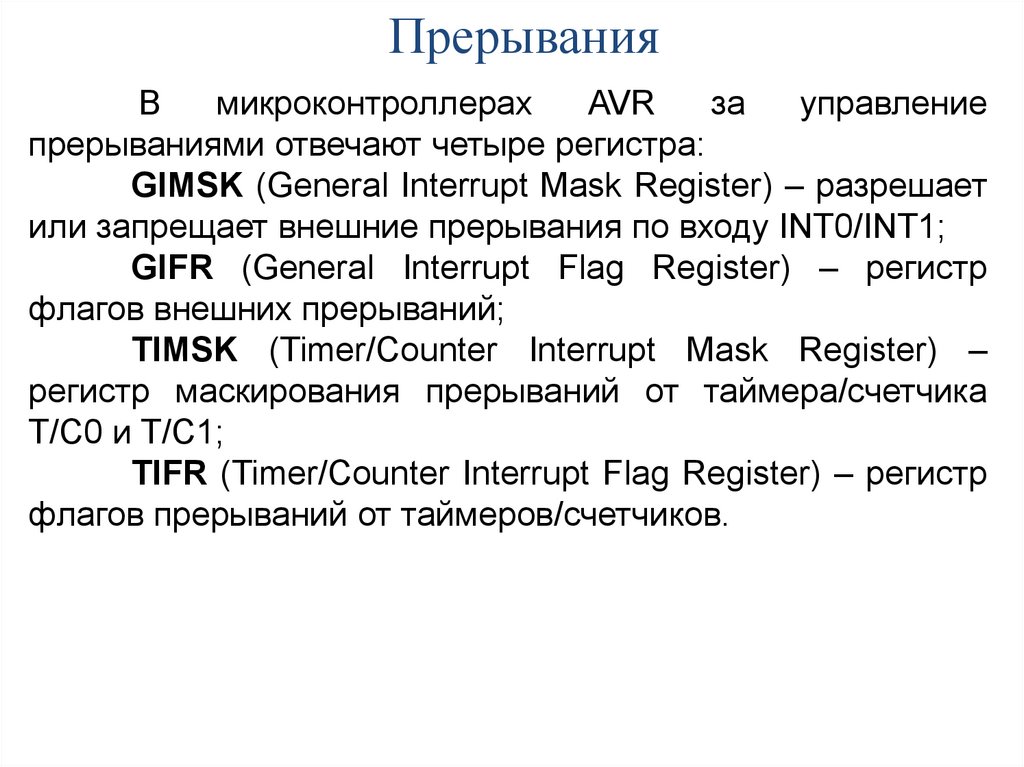

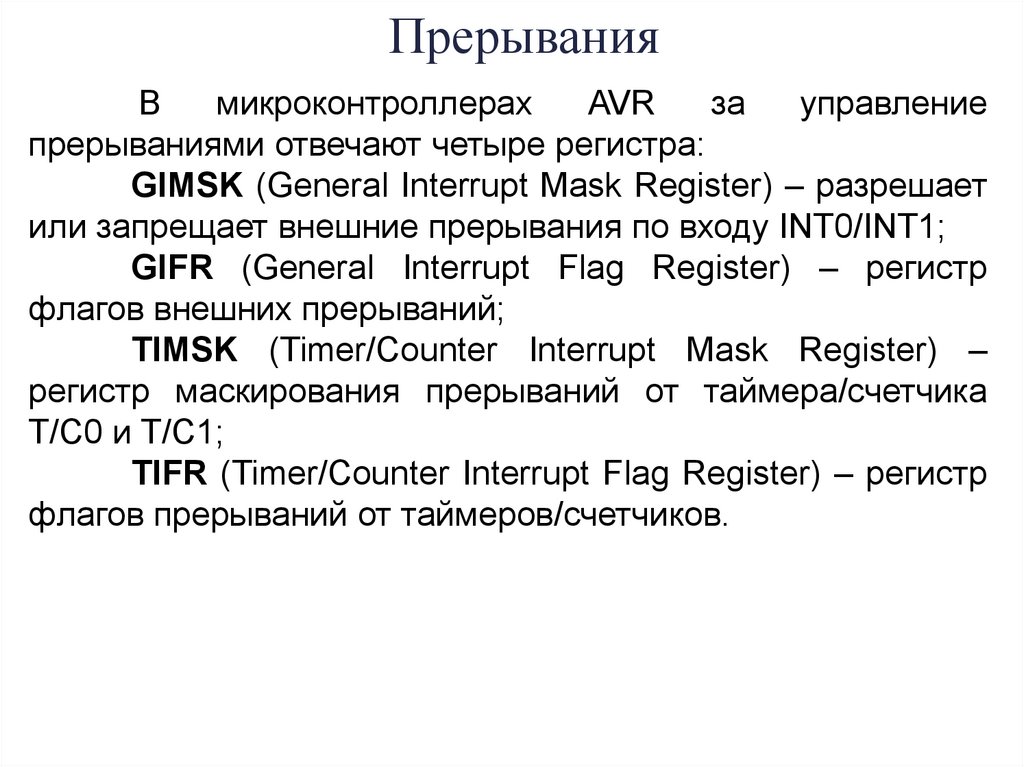

ПрерыванияВ

микроконтроллерах

AVR

за

управление

прерываниями отвечают четыре регистра:

GIMSK (General Interrupt Mask Register) – разрешает

или запрещает внешние прерывания по входу INT0/INT1;

GIFR (General Interrupt Flag Register) – регистр

флагов внешних прерываний;

TIMSK (Timer/Counter Interrupt Mask Register) –

регистр маскирования прерываний от таймера/счетчика

Т/С0 и Т/С1;

TIFR (Timer/Counter Interrupt Flag Register) – регистр

флагов прерываний от таймеров/счетчиков.

108.

ПрерыванияРегистр GIMSK используется для разрешения внешних прерываний.

7

6

5

4

3

2

1

0

INT1

INT0

–

–

–

–

–

–

Состояние внешнего прерывания определяется по регистру GIFR .

7

6

5

4

3

2

1

0

INTF1

INTF0 –

–

–

–

–

–

Регистр

TIMSK

используется

таймеров/счетчиков.

7

для

6

разрешения

5

прерываний

от

2

1

0

TOIE0

–

4 3

TOIE1 OCIE1A OCIE1B – TICIE1 –

Состояние прерываний, имеющих отношение

определяется по регистру TIFR. 7

6

5

к

таймерам/счетчикам

4

3

2

1

ICF1

–

TOV0 –

TOV1 OCF1A OCF1B –

0

Когда разряд TOIE1 и разряд I в регистре состояния SREG установлены в лог.

1, то разрешено прерывание при переполнении Т/С1. В случае переполнения в

регистре TIFR устанавливается флаг TOV1.

Если разряд OCIE1A и разряд I в регистре состояния SREG установлены в лог.

1, то разрешено прерывание при совпадении содержимого регистра сравнения

А с текущим состоянием Т/С1. В случае совпадения, в регистре TIFR

устанавливается флаг OCF1 А.

109.

Векторы прерыванийАдрес в

Источник

памяти

прерывания

Описание

программ

0x0000

RESET

Сигнал сброса

0x0001

INT0

Внешний запрос на прерывание по входу INT0

0x0002

INT1

Внешний запрос на прерывание по входу INT1

0x0003

Т/С1

Захват по таймеру/счетчику Т/С1

0x0004

Т/С1

Совпадение с регистром сравнения А таймера Т/С1

0x0005

Т/С1

Совпадение с регистром сравнения В таймера Т/С1

0x0006

Т/С1

Переполнение таймера/счетчика Т/С1

0x0007

Т/С0

Переполнение таймера/счетчика Т/С0

0x0008

SPI

Завершение передачи данных по интерфейсу SPI

0x0009

UART

Прием байта приемопередатчиком UART завершен

0х000А

UART

Регистр данных приемопередатчика UART пуст

0x000В

UART

Передача данных приемопередатчиком UART завершена

0х000С

ANA_COMP

Прерывание от аналогового компаратора

110.

Векторы прерыванийАдрес в

Источник

памяти

прерывания

Описание

программ

0x0000

RESET

Сигнал сброса

0x0001

INT0

Внешний запрос на прерывание по входу INT0

0x0002

INT1

Внешний запрос на прерывание по входу INT1

0x0003

Т/С1

Захват по таймеру/счетчику Т/С1

0x0004

Т/С1

Совпадение с регистром сравнения А таймера Т/С1

0x0005

Т/С1

Совпадение с регистром сравнения В таймера Т/С1

0x0006

Т/С1

Переполнение таймера/счетчика Т/С1

0x0007

Т/С0

Переполнение таймера/счетчика Т/С0

0x0008

SPI

Завершение передачи данных по интерфейсу SPI

0x0009

UART

Прием байта приемопередатчиком UART завершен

0х000А

UART

Регистр данных приемопередатчика UART пуст

0x000В

UART

Передача данных приемопередатчиком UART завершена

0х000С

ANA_COMP

Прерывание от аналогового компаратора

111.

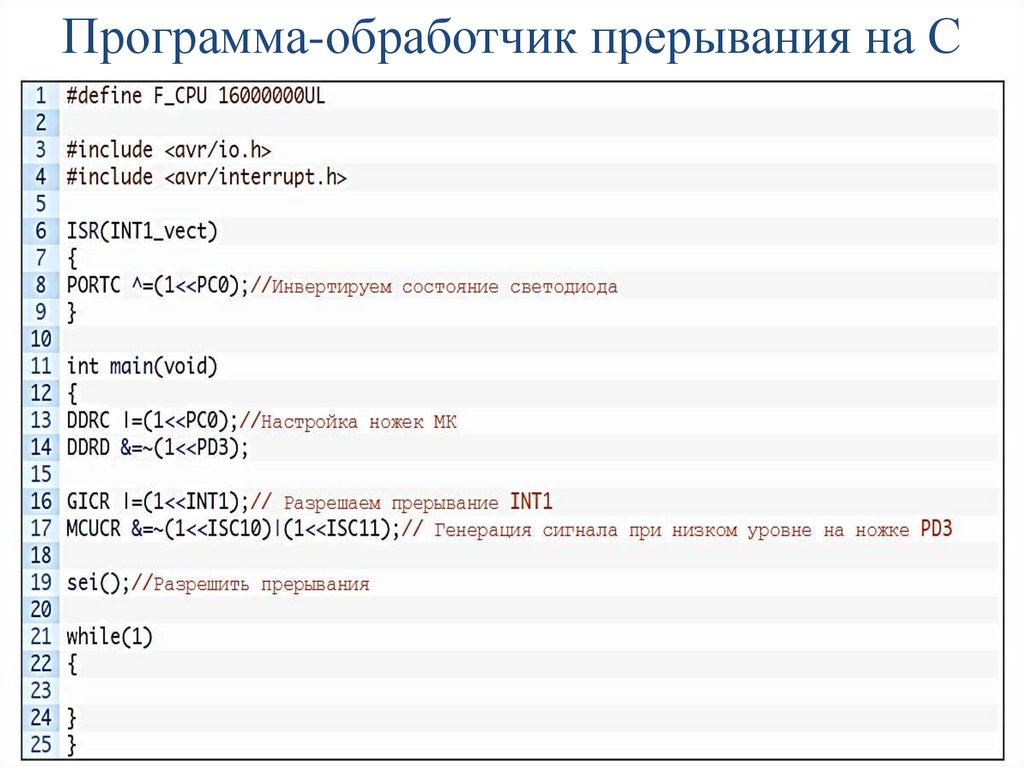

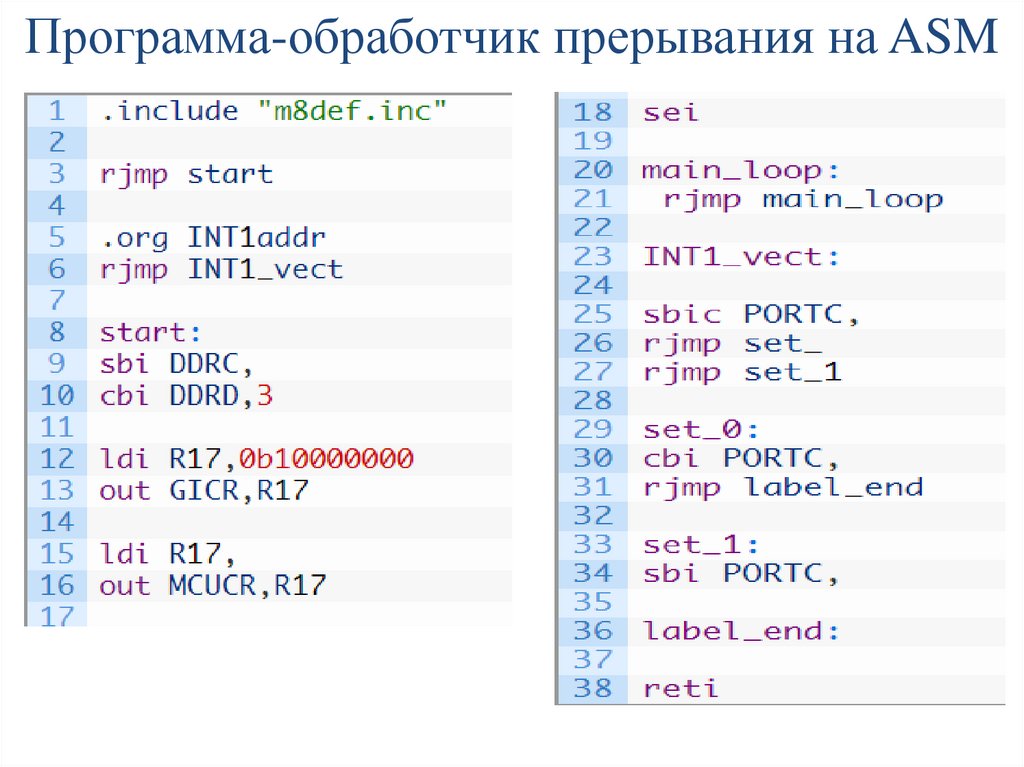

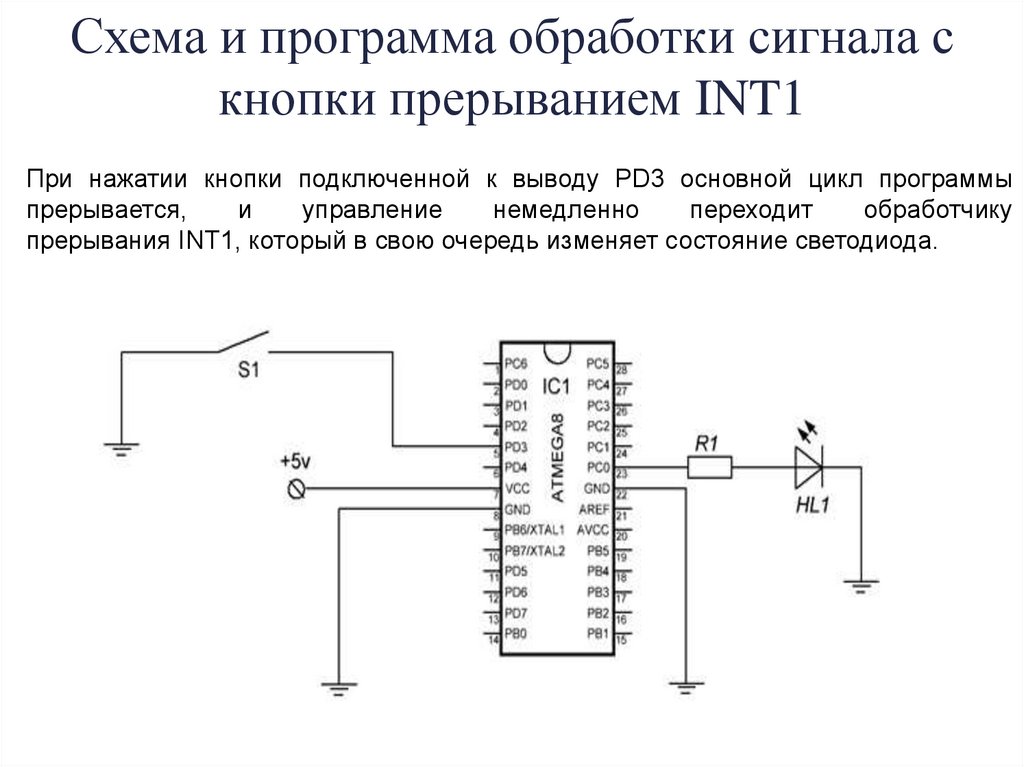

Схема и программа обработки сигнала скнопки прерыванием INT1

При нажатии кнопки подключенной к выводу PD3 основной цикл программы

прерывается,

и

управление

немедленно

переходит

обработчику

прерывания INT1, который в свою очередь изменяет состояние светодиода.

112.

Программа-обработчик прерывания на С113.

Программа-обработчик прерывания на ASM114.

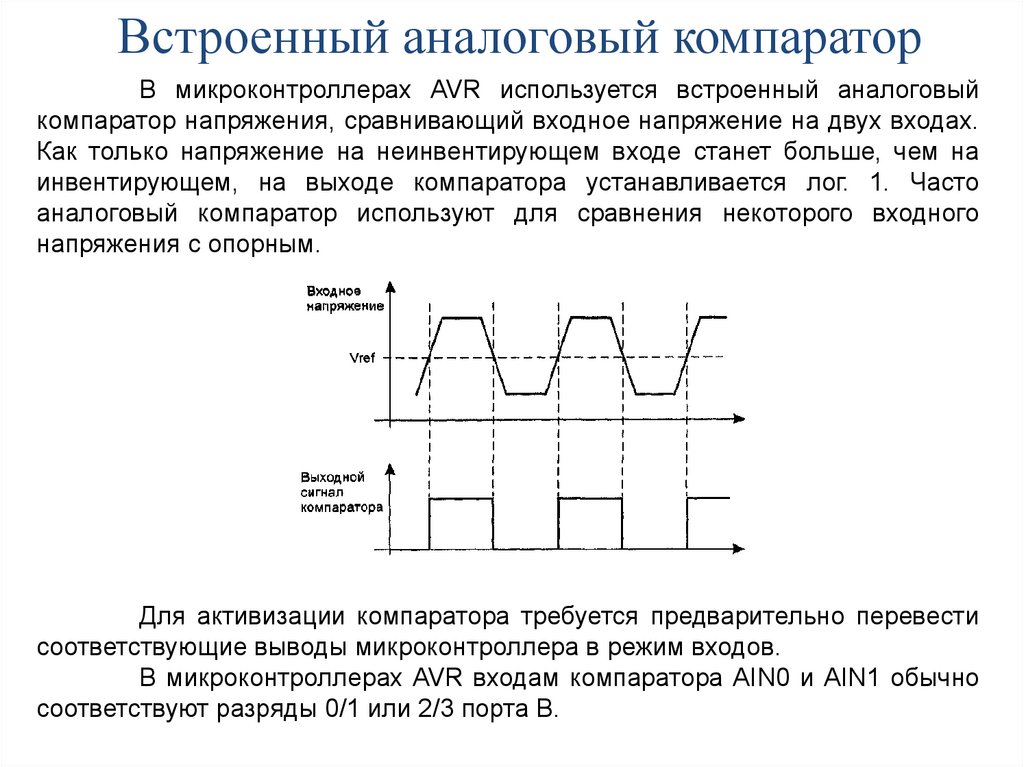

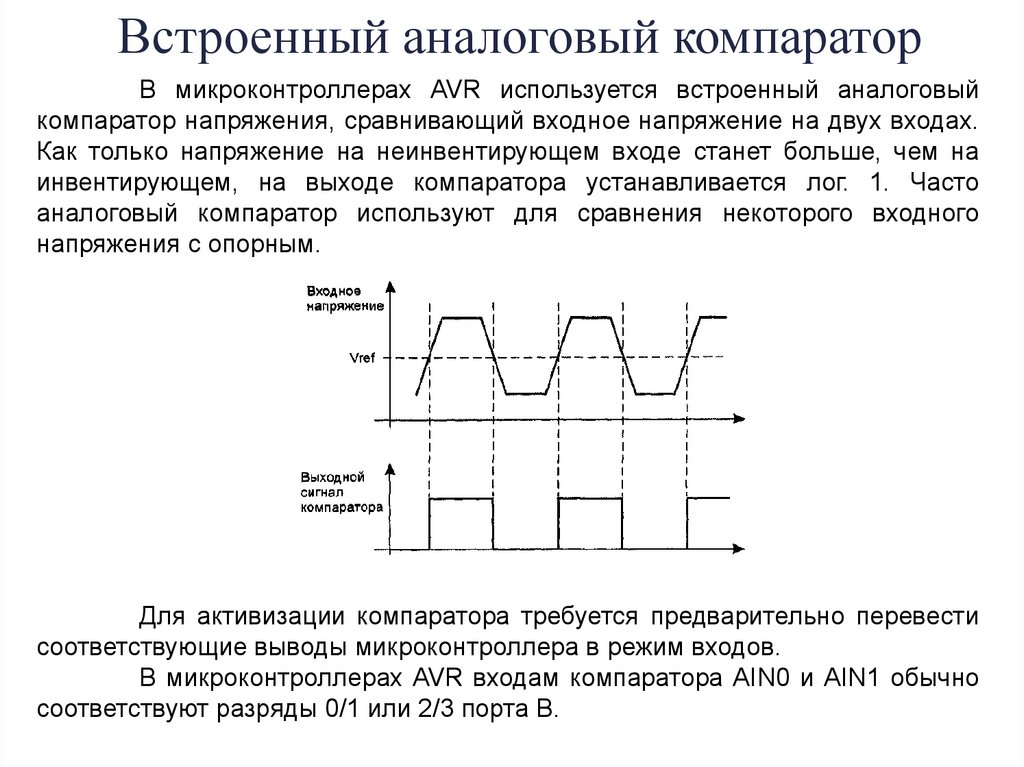

Встроенный аналоговый компараторВ микроконтроллерах AVR используется встроенный аналоговый

компаратор напряжения, сравнивающий входное напряжение на двух входах.

Как только напряжение на неинвентирующем входе станет больше, чем на

инвентирующем, на выходе компаратора устанавливается лог. 1. Часто

аналоговый компаратор используют для сравнения некоторого входного

напряжения с опорным.

Для активизации компаратора требуется предварительно перевести

соответствующие выводы микроконтроллера в режим входов.

В микроконтроллерах AVR входам компаратора AIN0 и AIN1 обычно

соответствуют разряды 0/1 или 2/3 порта В.

115.

Встроенный аналоговый компараторВ микроконтроллерах AVR для управления работой аналогового

компаратора используется регистр ACSR

7

6

5

4

3

2

1

0

ACD

–

ACO

ACI

ACIE

ACIC

ACIS1

ACIS0

Назначение разрядов регистра ACSR:

ACD – если установлен в лог. 1, питание аналогового компаратора отключено;

АСО – напрямую связан с выходом аналогового компаратора;

ACI – флаг прерываний от аналогового компаратора – устанавливается в лог.

1, когда наступает событие, определенное разрядами ACIS1 и ACIS0;

ACIE – разряд разрешения прерывания от аналогового компаратора;

ACIC – разряд разрешения захвата на входе аналогового компаратора; для

того чтобы можно было вызвать прерывание по захвату, оно должно быть

разрешено разрядом TICIE1 в регистре TIMSK;

ACIS1, ACIS0 – устанавливают вид события на выходе аналогового

компаратора, которое должно вызвать прерывание его работы.

ACIS1 AC1S0

0

0

0

1

1

0

1

1

Вид прерывания аналогового компаратора

Прерывание при изменении состояния выхода (разряда АСО)

Не используется

Прерывание по ниспадающему фронту на выходе аналогового

компаратора (напряжение на AIN1 больше, чем на AIN0)

Прерывание по нарастающему фронту на выходе аналогового

компаратора (напряжение на AIN0 больше, чем на AIN1)

116.

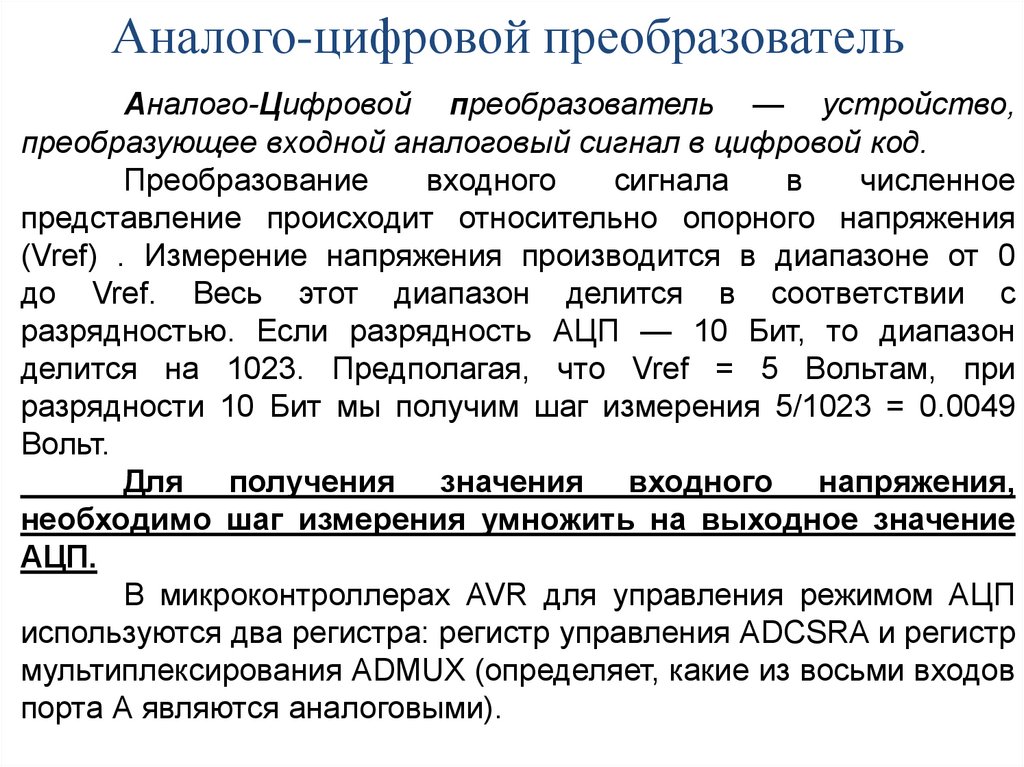

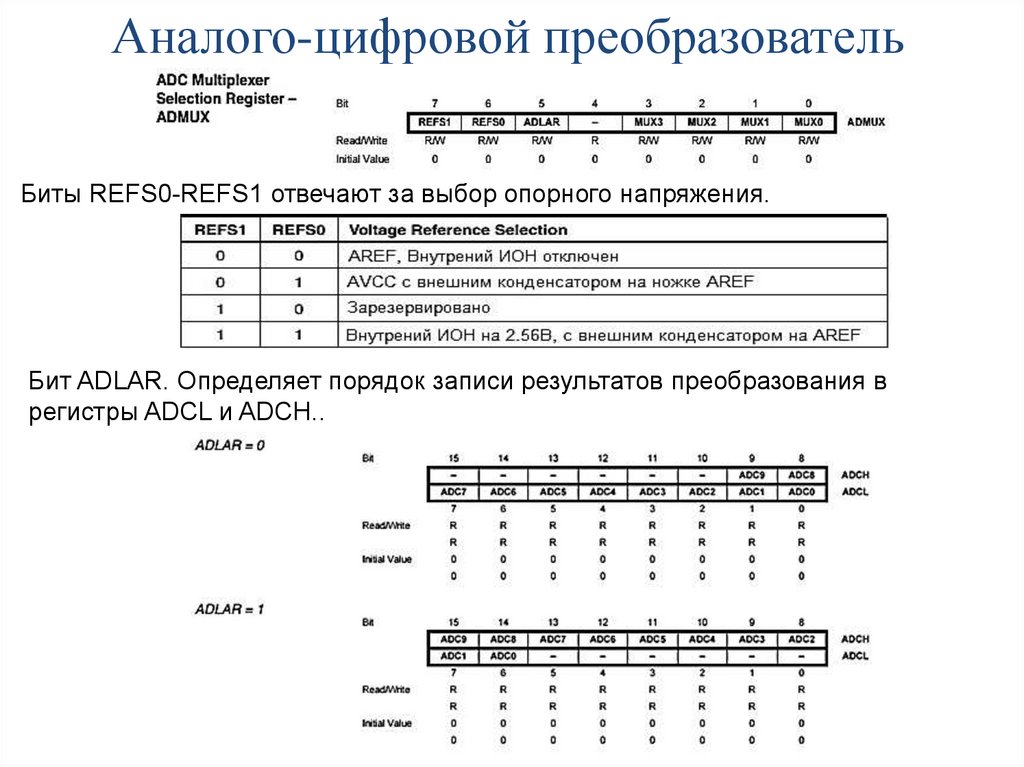

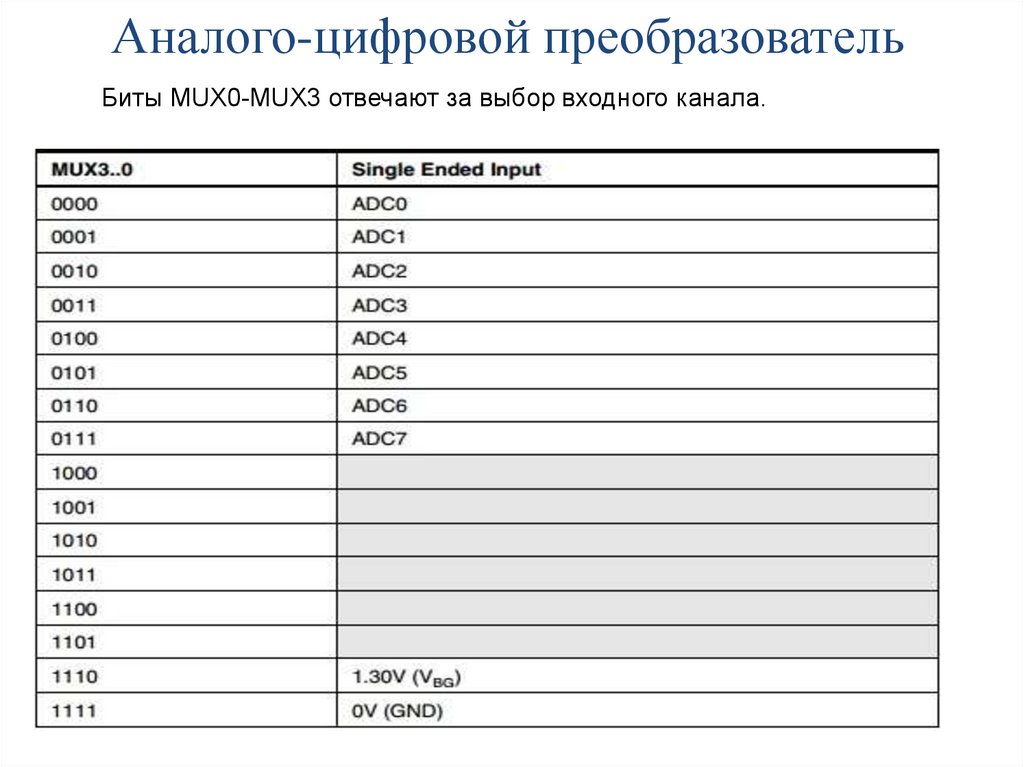

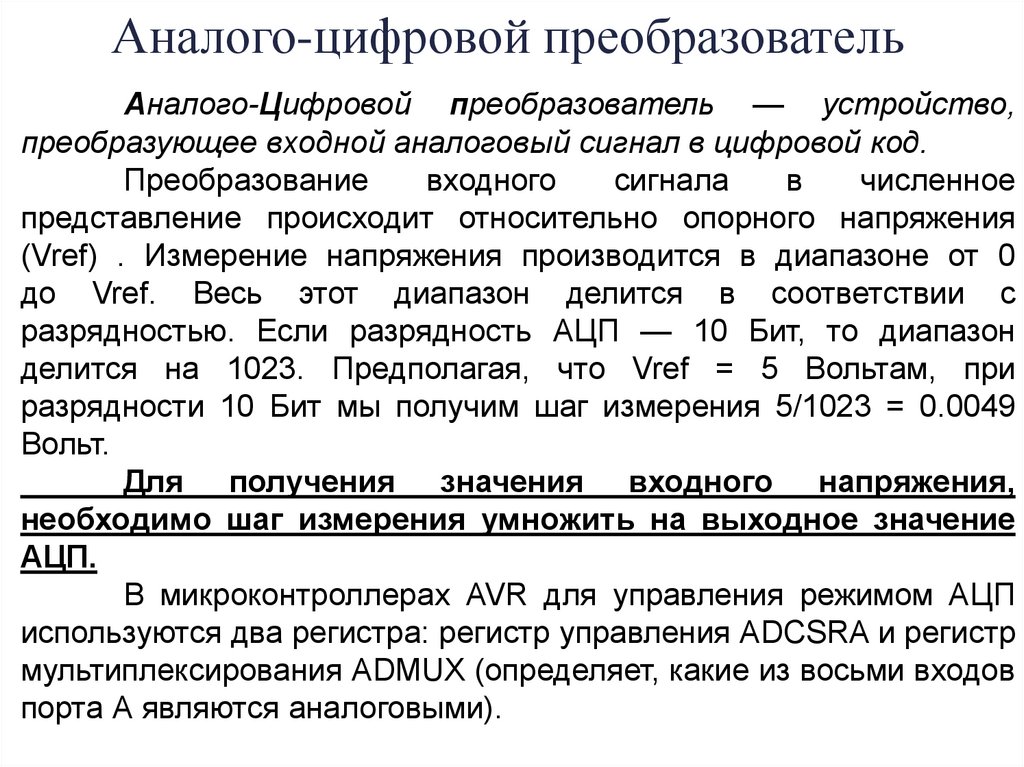

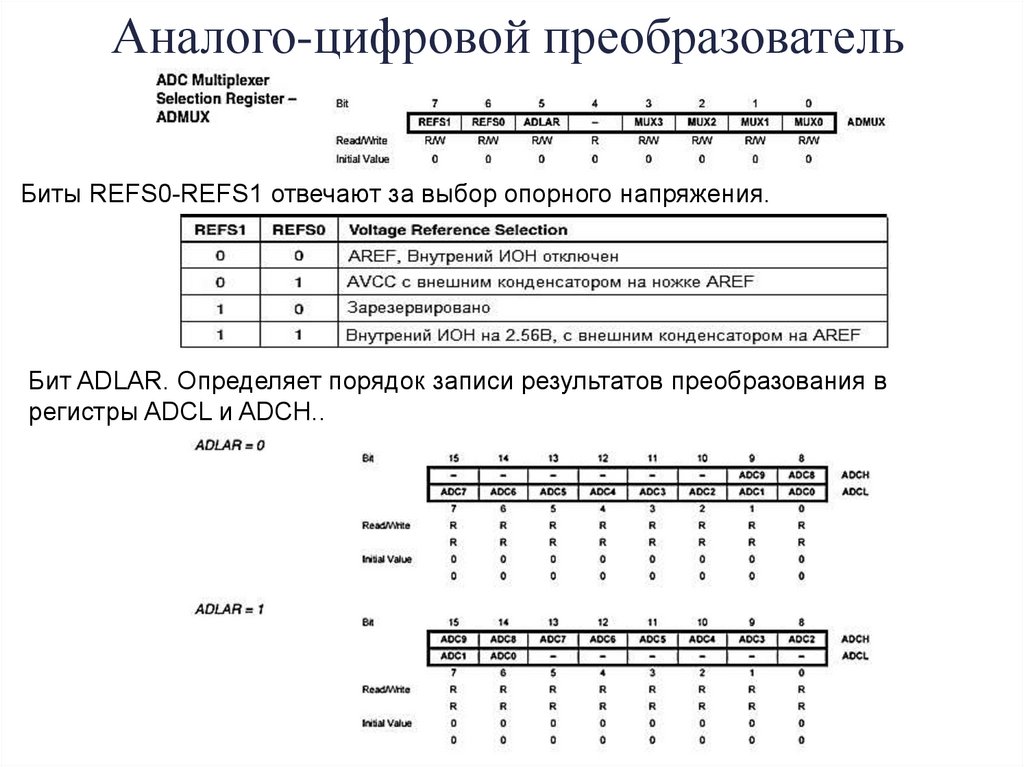

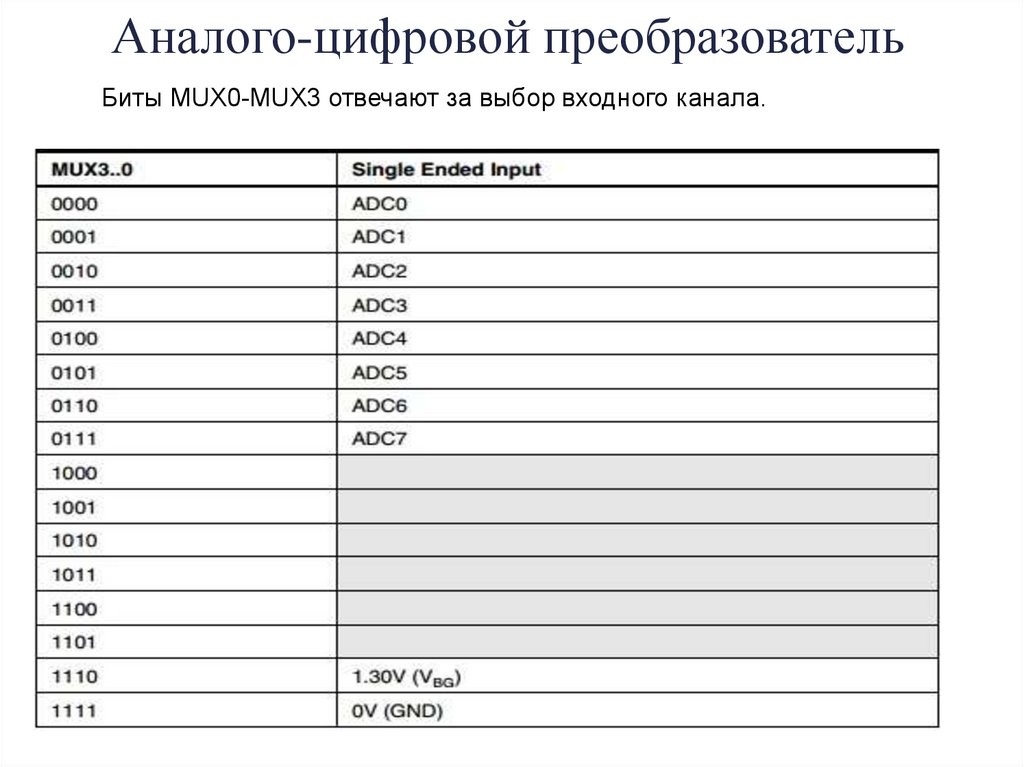

Аналого-цифровой преобразовательАналого-Цифровой преобразователь — устройство,

преобразующее входной аналоговый сигнал в цифровой код.

Преобразование

входного

сигнала

в

численное

представление происходит относительно опорного напряжения

(Vref) . Измерение напряжения производится в диапазоне от 0

до Vref. Весь этот диапазон делится в соответствии с

разрядностью. Если разрядность АЦП — 10 Бит, то диапазон