Похожие презентации:

Historia rozwoju systemów komputerowych

1.

1. Historia rozwoju systemów komputerowychKomputer

Rok

uruchomienia

Pochodzeni

e

Dziesiętny

/Binarny

Elektroniczny

Programowalny

Test

Turinga

Zuse Z3

1941

Niemcy

binarny

Nie

dziurkowana taśma

Tak

Atanasof-Berry

Computer

1941

USA

binarny

Tak

nie

Nie

Colossus

1944

UK

binarny

Tak

częściowo przez zmianę

okablowania

Nie

Harvard Mark I

1944

USA

dziesiętny

Nie

dziurkowane karty

Tak

ENIAC

1944

USA

dziesiętny

Tak

częściowo przez zmianę

okablowania

Tak

ENIAC v2

1948

USA

dziesiętny

Tak

poprzez tablice funkcyjne

Tak

pierwsze komputery były konstruowane w oparciu o mechaniczne przekaźniki, albo lampy elektronowe. Nie

wszystkie z nich były programowalne lub w pełni programowalne. „Programowanie”, w niektórych przypadkach,

wiązało się z mechanicznym połączeniem specjalnymi kablami poszczególnych modułów komputera.

1

2.

Procesor (ang. processor) lub CPU (ang. Central Processing Unit) –centralne (główne) urządzenie sekwencyjne cyfrowe potrafiące pobierać

dane z pamięci, interpretować je i wykonywać jako rozkazy.

Procesor wykonuje ciąg prostych operacji (rozkazów) wybranych ze zbioru

operacji podstawowych określonych zazwyczaj przez producenta procesora

jako lista rozkazów procesora.

Pamięć komputerowa to różnego rodzaju urządzenia i bloki

funkcjonalne komputera, służące do przechowywania danych i

programów (systemu operacyjnego oraz aplikacji).

Urządzenie wejścia-wyjścia, urządzenie we/wy, urządzenie I/O (ang.

input/output device) służy do komunikacji komputera z użytkownikiem,

komputerem lub innym urządzeniem.

•urządzenia wejścia to np.: klawiatura, mysz komputerowa, skaner, oraz

czytniki nośników danych

•urządzenia wyjścia to np.: monitor, drukarka, głośniki, słuchawki

•urządzenia wejścia i wyjścia to np.: karta sieciowa, modem, ekran dotykowy,

dysk twardy, Bluetooth, USB oraz wszelkie inne nagrywalne stacje nośników

danych

2

3.

Warstwy systemu komputerowegoSystem komputerowy– układ współdziałania sprzętu komputerowego oraz oprogramowania

Struktura systemu komputerowego składa się z pięciu zasadniczych warstw tj. :

warstwa sprzętowa,

system operacyjny,

programy narzędziowe,

programy użytkowe

i użytkownicy.

Warstwa Sprzętowa – zapewnia podstawowe możliwości obliczeniowe (procesor, pamięć, urządzenia wejścia/wyjścia)

– podstawowe zasoby systemu komputerowego.

System operacyjny – kontroluje i koordynuje użycie zasobów sprzętowych poprzez różne programy użytkowe dla różnych użytkowników.

Programy narzędziowe – wspomagają zarządzanie zasobami sprzętowymi poprzez dogodne interfejsy użytkowe oraz usprawniają,

modyfikują oprogramowanie systemowe, zazwyczaj pisane przez niezależnych programistów którzy mają na celu usprawnienia wykonywania

programów w bardziej wygodny i wydajny sposób, a przy tym często eliminują błędy czy też niedociągnięcia oprogramowania systemowego.

Programy użytkowe – określają sposoby, w jakie zostają użyte zasoby systemowe do rozwiązywania problemów obliczeniowych zadanych

przez użytkownika (kompilatory, systemy baz danych, gry, oprogramowanie biurowe), tworzone przez programistów.

Użytkownicy – ludzie, maszyny, inne komputery, mają bezpośredni kontakt z oprogramowaniem użytkowym

3

4.

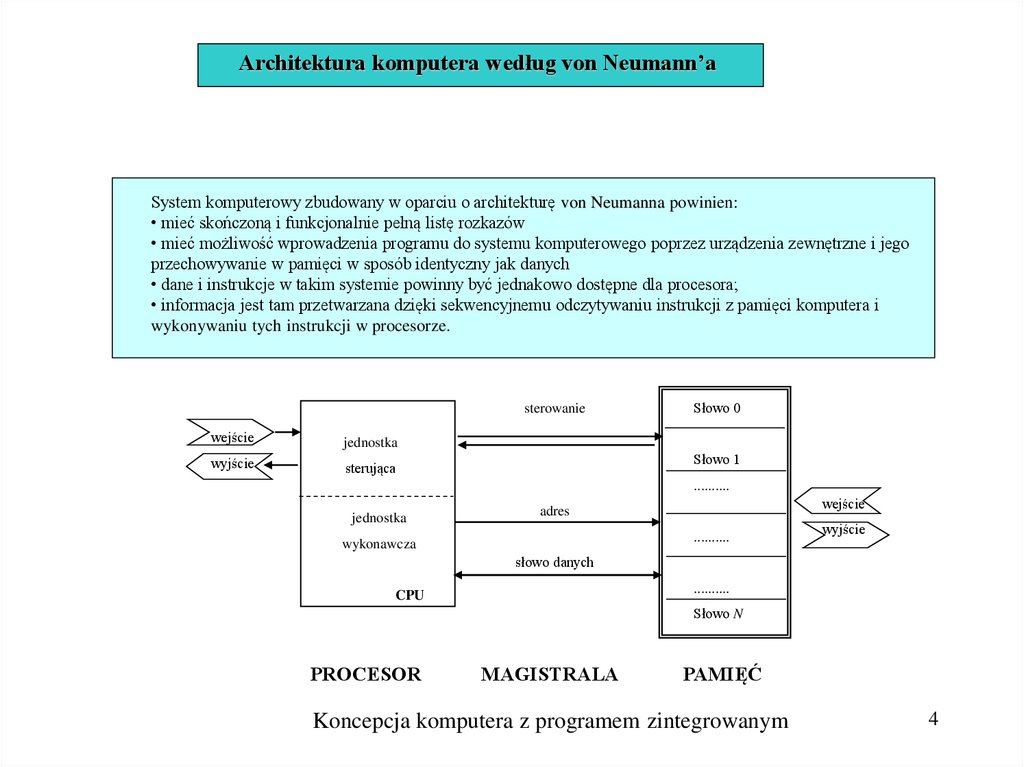

Architektura komputera według von Neumann’aSystem komputerowy zbudowany w oparciu o architekturę von Neumanna powinien:

• mieć skończoną i funkcjonalnie pełną listę rozkazów

• mieć możliwość wprowadzenia programu do systemu komputerowego poprzez urządzenia zewnętrzne i jego

przechowywanie w pamięci w sposób identyczny jak danych

• dane i instrukcje w takim systemie powinny być jednakowo dostępne dla procesora;

• informacja jest tam przetwarzana dzięki sekwencyjnemu odczytywaniu instrukcji z pamięci komputera i

wykonywaniu tych instrukcji w procesorze.

sterowanie

wejście

jednostka

wyjście

sterująca

Słowo 0

Słowo 1

..........

jednostka

wejście

adres

..........

wykonawcza

wyjście

słowo danych

..........

CPU

Słowo N

PROCESOR

MAGISTRALA

PAMIĘĆ

Koncepcja komputera z programem zintegrowanym

4

5.

Typy architektury komputerówArchitektura systemu komputerowego to sposób połączenia i organizacji jego poszczególnych

elementów. Definiuje ona zatem budowę komputera bardziej na poziomie funkcjonalnym niż

technologicznym. Ważne są tu takie elementy jak: sposób współpracy jednostki arytmetycznologicznej z urządzeniami zewnętrznymi, format danych, sposób organizacji i adresowania pamięci,

budowa słowa rozkazowego, sposób kontroli wszystkich elementów systemu.

Koncepcja komputera według von Neumanna

Komputer taki składa się z:

• Jednostki arytmetyczno-logicznej (ALU), która wykonuje operacje arytmetyczne i logiczne na liczbach binarnych.

• Pamięci głównej, w której przechowywane są dane i rozkazy.

• Jednostki sterującej, która interpretuje i wykonuje rozkazy.

• Urządzeń wejścia-wyjścia, sterowanych przez jednostkę sterującą, poprzez które są wprowadzane i wyprowadzane dane

5

6.

Architektura komputera według von Neumann’aCPU – Centralna Jednostka Przetwarzająca

MEM – pamięć

PAO – pamięć operacyjna

ROM – pamięć do odczytu (EEPROM- przechowuje

oprogramowanie obsługujące urządzenia wejścia-wyjścia

dołączone do mikrokomputera, tzw. BIOS)

I/O - Układy wejścia-wyjścia

DB – (Data Bus) magistrala danych

AB – (Address Bus) magistrala adresowa

CB – (Control Bus) magistrala sterująca

Zadania:

Procesor

-

przetwarzanie danych, których źródłem jest pamięć

Pamięć

-

informacja przechowywana w komórkach o jednakowym rozmiarze ,

każda komórka zawiera jednostkę informacji zwaną słowem,

sposób przechowywania danych jak i tez instrukcji jest identyczny,

struktura (kod) słowa nie pozwala na odróżnienie instrukcji od danych,

komórki tworzą zbiór uporządkowany (unikatowy wskaźnik lokacji),

zawartość komórki może zmienić procesor

6

7.

Architektura komputera według von Neumann’aPamięć (główna, operacyjna, pierwotna) jest adresowana podczas wykonywania pojedynczego rozkazu i jest

pamięcią o dostępie swobodnym (random access)

Program jest sekwencją rozkazów.

Układ wytwarzający adres kolejnego rozkazu podczas wykonywania poprzedniego rozkazu nosi nazwę

Licznika Rozkazów (Program Counter)

Alternatywna koncepcja komputera z programem

zintegrowanym (Harwardzka )

Jednostka sterująca

sterowanie

rozkazy

Jednostka wykonawcza

PAMIĘĆ

ROZKAZÓW

adres

dane

PAMIĘĆ

DANYCH

wejście

wyjście

PROCESOR

Podstawowa architektura komputerów zerowej generacji i początkowa komputerów pierwszej generacji.

7

8.

2. Klasyfikacja systemów komputerowychprzeznaczenie systemu:

•ogólnego przeznaczenia (konfiguracja tak dobrana, aby komputer mógł służyć wielu celom),

•specjalizowane (przeznaczone do wykonywania określonego zdania lub klasy zdań)

tryb przetwarzania informacji:

•systemy jednoprogramowe – jednozadaniowe (jednocześnie jest wykonywany tylko jeden program,

wykonanie kolejnego programu jest możliwe po całkowitym zakończeniu programu poprzedniego),

•systemy wieloprogramowe – wielozadaniowe (wiele programów może być wykonywanych pozornie

jednocześnie, wykonywanie wielu programów następuje na przemian),

•systemy wielodostępne – wieloużytkownikowe (możliwe jest korzystanie z systemu jednocześnie przez

wielu użytkowników).

gabaryty komputera:

•systemy osadzone (ang. embedded) – komputery sterujące wbudowywane w inne urządzenia,

•komputery osobiste (biurowe, domowe, używane w jednym miejscu – stacjonarne),

•komputery przenośne (ang. laptop, notebook),

•komputery kieszonkowe (ang. palmtop),

•systemy serwerowe - wykorzystywane głównie poprzez sieć.

długości słowa procesora komputera:

•8-bitowe,

•16-bitowe,

•32-bitowe,

•64-bitowe.

8

9.

3. Składniki systemu komputerowegoKomputer PC ogólnego przeznaczenia składa się z jednej bądź kilku jednostek centralnych i urządzeń I/O,

połączonych wspólną magistralą umożliwiającą współpracę ze wspólną pamięcią.

Każde urządzenie wchodzące w skład systemu komputerowego (dysk twardy, karta grafiki, drukarka itd.) ma

zdefiniowany standard połączenia z jednostką centralną.

Sterowniki mają zapewnić uporządkowany dostęp do wspólnej pamięci danych i innych zasobów.

Na architekturę komputera składają się:

•Jednostka centralna (CPU), czyli przynajmniej jeden procesor.

•Magistrala systemowa, poprzez którą komunikują się

poszczególne elementy systemu.

•Wspólna pamięć, która służy do przechowywania

danych i kodu programu.

•Urządzenia wejścia-wyjścia, poprzez które możliwa

jest komunikacja ludzi z komputerem.

9

10.

W sytuacjach, kiedy jakiekolwiek dane zapisywane są przy użyciu wielu (przynajmniej dwóch)bajtów, nie istnieje jeden unikalny sposób uporządkowania tych bajtów w pamięci lub w czasie

transmisji przez dowolne medium i musi być użyta jedna z wielu konwencji ustalająca kolejność

bajtów

Forma zapisu danych

Big endian - najbardziej znaczący bajt umieszczony jest jako pierwszy.

Procesory, które używają formy big endian, to między innymi SPARC, Motorola 68000, PowerPC 970,

IBM System/360, Siemens SIMATIC S7.

Jest ona analogiczna do używanego na co dzień sposobu zapisu liczb.

Little endian - mniej znaczący bajt (zwany też dolnym bajtem, z ang. low-order byte) umieszczony jest

jako pierwszy.

Procesory, które używają formy little endian, to między innymi wszystkie z rodziny x86, DEC VAX.

Jest ona odwrotna do używanego na co dzień sposobu zapisu liczb.

Procesor zapisujący 32-bitowe wartości w pamięci, przykładowo 4A3B2C1D pod adresem 100, umieszcza dane, zajmując adresy od 100 do 103 w

następującej kolejności:

adres

100

101

102

103

bajty

4A

3B

2C

1D

adres

100

101

102

103

bajty

1D

2C

3B

4A

10

11.

ZESTAWIENIE BINARNYCH KODÓW POZYCYJNYCHKod

NKB

ZM

U1

U2

bias=3

0000

0

0

0

0

-3

Kod

Reprezentacja

Konstrukcja kodu

0001

1

1

1

1

-2

NKB

bn-1...b1b0

bn-12n-1+...+b121+b020

0010

2

2

2

2

-1

ZM

bzbn-2...b1b0

(-1)bz kod NKB

0011

3

3

3

3

0

U1

bn-1bn-2...b1b0

bn-1(-2n-1-1) + kod NKB

0100

4

4

4

4

1

U2

bn-1bn-2...b1b0

bn-1(-2n-1) + kod NKB

0101

5

5

5

5

1

bias

bn-1...b1b0

0110

6

6

6

6

3

0111

7

7

7

7

4

1000

8

0

-7

-8

5

1001

9

-1

-6

-7

6

Kod

Reprezentacja

zakres

1010

10

-2

-5

-6

7

NKB

bn-1...b1b0

0 ... 2n-1

1011

11

-3

-4

-5

8

ZM

bzbn-2...b1b0

-2n-1+1 ... 2n-1-1

1100

12

-4

-3

-4

9

U1

bn-1bn-2...b1b0

-2n-1+1 ... 2n-1-1

1101

13

-5

-2

-3

10

U2

bn-1bn-2...b1b0

-2n-1 ... 2n-1-1

1110

14

-6

-1

-2

11

bias

bn-1...b1b0

-bias ... 2n-1-bias

1111

15

-7

0

-1

12

x

kod NKB (bn-1...b0) - bias

11

12.

Operacje logiczneOperacje na bitach

Przy operacjach na bitach stosuje się specjalne słowo bitowe

nazywane maską. Maska posiada odpowiednio ustawione lub

wyzerowane bity na odpowiednich miejscach.

Zerowanie bitu

11011111

AND 11110111

z = x AND y

z = x OR y

z = x XOR y

x

y

z

x

y

z

x

y

z

0

0

0

0

0

0

0

0

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

1

1

0

1

1

1

1

1

1

1

1

1

0

maska

11010111

Ustawianie bitu

11011111

OR 00100000

11111111

Zmiana stanu bitu na przeciwny

maska

11001111

XOR 00001000

maska

11000111

12

13.

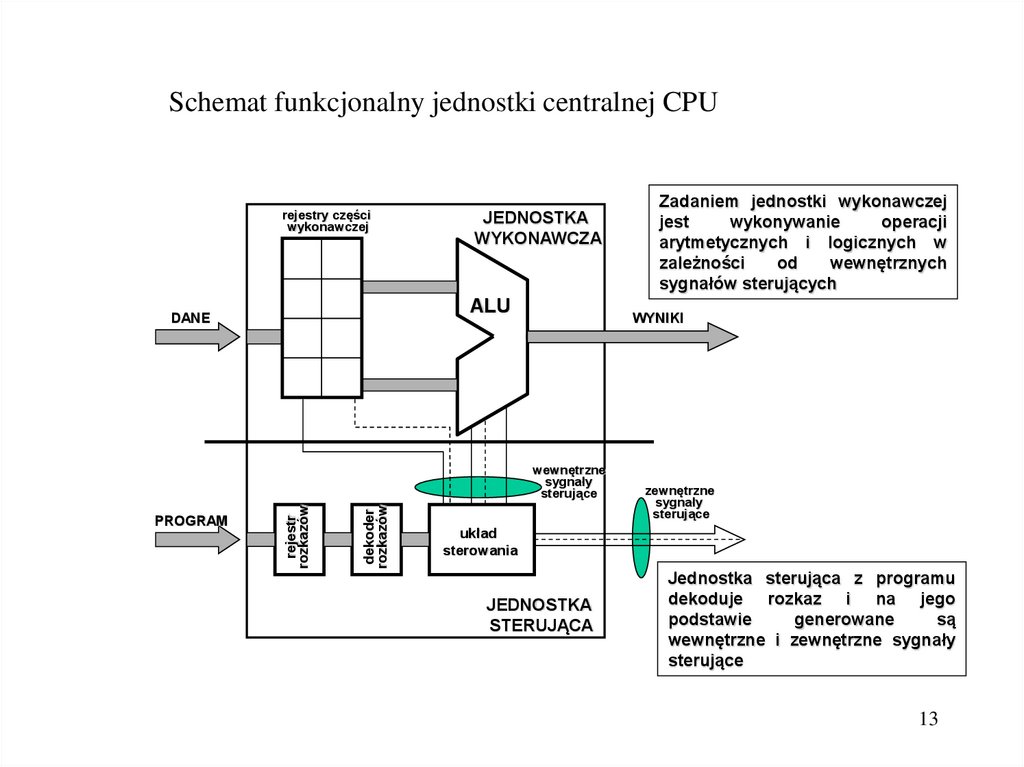

Schemat funkcjonalny jednostki centralnej CPUrejestry części

wykonawczej

JEDNOSTKA

WYKONAWCZA

ALU

DANE

WYNIKI

dekoder

rozkazów

rejestr

rozkazów

wewnętrzne

sygnały

sterujące

PROGRAM

Zadaniem jednostki wykonawczej

jest

wykonywanie

operacji

arytmetycznych i logicznych w

zależności

od

wewnętrznych

sygnałów sterujących

zewnętrzne

sygnały

sterujące

układ

sterowania

JEDNOSTKA

STERUJĄCA

Jednostka sterująca z programu

dekoduje rozkaz i na jego

podstawie

generowane

są

wewnętrzne i zewnętrzne sygnały

sterujące

13

14.

4. Procesor – informacje ogólneProcesor (CPU – ang. Central Processing Unit) interpretuje instrukcje programu i zgodnie z nim przetwarza dane.

Procesor wykonuje sekwencyjnie instrukcje przechowywane w pamięci.

Instrukcja nie jest wykonywana w jednym kroku. Jej wykonanie jest rozbite na wiele etapów.

Można wyróżnić pięć głównych etapów wykonywania instrukcji. Są to:

•Pobranie rozkazu – odczyt rozkazu z pamięci (rozkaz operacji pobrany do rejestru rozkazów (ang. Instruction Register IR).

Każde polecenie jest wartością liczbową interpretowaną jako polecenie.

Adres aktualnie wykonywanej instrukcji jest umieszczony w specjalnym rejestrze rozkazów PC (ang. Program Counter).

•Zdekodowanie rozkazu – po odczytaniu instrukcji z pamięci, procesor interpretuje polecenie (ang. Decoder).

W trakcie tego procesu instrukcja jest rozbijana na poszczególne części o odmiennym znaczeniu.

•Generacja adresów operandów – na tym etapie obliczane są bezpośrednie adresy danych, na których operuje instrukcja.

Dane te muszą być ściągnięte do rejestrów procesora ( ang. general purpose registers).

•Wykonanie rozkazu – jest to wykonanie polecenia (ang. Execution Unit EU).

Wykorzystywane mogą być różne moduły procesora:

całkowitoliczbowa jednostka arytmetyczno-logiczna (ALU), jednostka zmiennopozycyjna (FPU).

Dane na tym etapie są pobierane z rejestrów, a wyniki umieszczane w rejestrach.

Nie jest możliwe wykonywanie operacji arytmetyczno-logicznych bezpośrednio w pamięci RAM.

•Zapis do pamięci – jest to faza końcowa. Na tym etapie wyniki mogą zostać odesłane do pamięci operacyjnej RAM.

Mi

F

D

(R)

cykl pamięci

E

W

Mj

F

- pobranie kodu

D

- dekodowanie

R

- odczyt argumentu

E

- wytworzenie wyniku

W

- zapamiętanie wyniku

Mi,j - stan komputera

14

15.

REJESTRY OGÓLNEGO STOSOWANIARejestry ogólnego stosowania

Układy pamięciowe przeznaczone do przechowywania informacji oraz spełniające

spełniające funkcje specjalne.

Rejestry 16-to bitowe podzielone na dwie 8-bitowe części: dolną (L) i górną (H).

– AX - (akumulator) rejestr przeznaczony do przechowywania jednego z z

argumentów wykonywanej operacji oraz miejsce wyniku operacji

–

BX - rejestr bazowy wykorzystywany do operacji związanych z pamięcią

operacyjną lub do adresowania pamięci. Domyślnie rejestr BX, wraz z

rejestrem segmentowym DS, jest używany jako wskaźnik pamięci

–

CX - rejestr wykorzystywany głównie jako licznik odliczający powtarzające

się fragmenty programów bądź pojedynczych rozkazów

–

DX - rejestr najczęściej wykorzystywany głównie jako wskaźnik adresów w

rozkazach IN i OUT

15

8 7

0

AX

AH

AL

Akumulator

BX

BH

BL

Rejestr bazowy

CX

CH

CL

Rejestr zliczający

DX

DH

DL

Rejestr danych

15

16.

REJESTRYREJESTRY

dostępne programowo

niedostępne programowo

(na przykładzie procesora 8086/8088)

15

0

FLAGS

15

7

0

Rejestr

znaczników

(flagowy

AX

AH

AL

Akumulator

BX

BH

BL

Rejestr bazowy

CX

CH

CL

Rejestr zliczający

DX

DH

DL

Rejestr danych

DI

Rejestr indeksowy

źródła

Rejestr indeksowy

przeznaczenia

BP

Wskaźnik bazy

SP

Wskaźnik stosu

SI

OF DF IF

Rejestry

ogólnego

stosowania

Rejestry

wskaźnikowe

i indeksowe

TF SF ZF

AF

PF

CF

Znaczniki stanu

OF - flaga nadmiaru (przepełnienia)

SF - flaga znaku

ZF - flaga zera

CF - flaga przeniesienia

PF - flaga parzystości

AF - flaga przeniesienia pomocniczego

Znaczniki kontrolne

IF - flaga zezwolenia na przerwanie

TF - flaga pracy krokowej

DF - flaga kierunku

Wskaźnik

rozkazów

IP

CS

Rejestr kodu

DS

Rejestr danych

ES

Rejestr dodatkowy

SS

Rejestr stosu

Rejestry

segmentowe

16

17.

REJESTRY SEGMENTOWERejestr CS wskazuje początek 64KB (216 ) bloku pamięci zawierającej kod

rozkazu lub na segment kodu, w którym rezyduje następny do wykonania

rozkaz. (CS:IP)

Rejestr DS wskazuje początek 64KB bloku pamięci zawierający dane

(argumenty) (DS:DI);(DS:SI),(DS,BX)

Rejestr ES wskazuje początek 64KB bloku pamięci zwanego dodatkowym.

Jest on używany jest w operacjach łańcuchowych (wykorzystując pary

rejestrów ES:DI) lub w operacjach na blokach np. kopiowanie,

porównywanie, przeszukiwanie, czyszczenie.

Rejestr SS wskazuje początek 64KB bloku pamięci zwanego segmentem

stosu.

blok pamięci

CS

Rejestr kodu

DS

Rejestr danych

ES

Rejestr dodatkowy

SS

Rejestr stosu

CS:IP

17

18.

REJESTRY INDEKSOWE I WSKAŹNIKOWESI - rejestr indeksowy źródła danych wykorzystywany jest głównie

jako wskaźnik przesunięcia w bloku pamięci operacyjnej

DI - rejestr indeksowy miejsca przeznaczenia danych wykorzystywany

jest głównie jako wskaźnik przesunięcia w bloku pamięci operacyjnej

rejestr SI adresuje przesunięcie źródła (wyniku) danych w połączeniu z

rejestrem segmentowym DS.

rejestr DI adresuje przesunięcie przeznaczenia danych w połączeniu z

rejestrem segmentowym ES

-

BP (wskaźnik bazy) - rejestr ten dotyczy obszaru segmentu stosu.

Używany jest jako wskaźnik przesunięcia pamięci wspólnie z rejestrem

segmentowym SS (SS:BP)

SP (wskaźnik stosu) - rejestr ten podaje bieżące położenie wierzchołka

stosu.

18

19.

STOSPamięć operacyjna

Stos jest liniową strukturą danych, w której dane

dokładane są na wierzch stosu i z wierzchołka stosu są

pobierane (bufor typu LIFO, Last In, First Out; ostatni na

wejściu, pierwszy na wyjściu).

Elementy stosu poniżej wierzchołka stosu można

wyłącznie obejrzeć, aby je ściągnąć, trzeba najpierw po

kolei ściągnąć to, co jest nad nimi.

Stos jest używany są przez procesor:

- do chwilowego zapamiętywania stanu rejestrów

procesora,

- do przechowywania zmiennych lokalnych,

- a także w programowaniu wysokopoziomowym.

SP

BP

Adresacja stosu

•SS – rejestr segmentowy, wskazujący na początek stosu, czyli krańcową wartość, jaką może przyjąć ESP (SS:BP)

•ESP (SP dla procesorów 16-bitowych) – rejestr wskazujący na element znajdujący się na szczycie stosu.

Operacje na stosie

push

umieszczenie wartości na szczycie stosu. Odpowiada on przesunięciu rejestru ESP o o ilość bajtów zależną od rozmiaru rejestru, którego

wartość przenosimy na stos

pop

zdjęcie wartości ze stosu. Odpowiada on zapisaniu ilości bajtów zależnej od rozmiaru rejestru, do którego przenosimy wartość

19

20.

Operacje logiczneOperacje logiczne w odróżnieniu do operacji arytmetycznych operują na pojedynczych bitach.

Logika cyfrowa opiera się na algebrze Boole’a

Symbol Algebry

Boole'a

Symbol

bitowy

PRAWDA

1

FAŁSZ

0

Funkcje dwóch zmiennych - suma, iloczyn, negacja (funkcja jednej zmiennej) nie

wyczerpują

listy

wszystkich

możliwych

funkcji

dwóch

zmiennych.

Zakładając, że mamy zmienne x0 i x1 funkcje te można zapisać:

gdzie kolejne funkcje:

Prawa Algebry Boole’a

1. przemienność A*B = B*A, A+B = B+A,

2. łączność (A*B)*C = A*(B*C), (A+B)+ C = A+(B+C),

3. rozdzielczość A*(B+C) = A*B+A*C,

(A+B)*(A+C) = A+B*C,

4. tożsamość A*0 = 0, A+0 = A,

A*1 = A , A+1 = A,

A*A = A, A+A = A,

5. komplementarność , ,

oraz dwa tzw. prawa de Morgana:

A B A B

f0- funkcja stała,

f1- funkcja NOR,

f2- funkcja implikacji (zakazu),

f3- negacja x0,

f4- funkcja implikacji (zakazu),

f5- negacja x1,

f6- funkcja sumy wyłączającej,

sumy modulo 2 lub funkcja

EXOR,

f7- funkcja NAND,

f8- funkcja iloczynu,

f9- funkcja równoważności,

f10- funkcja tożsama ze zmienną,

f11- funkcja implikacji,

f12- funkcja tożsama ze zmienną,

f13- funkcja implikacji,

f14- funkcja sumy,

f15- funkcja stała.

20

21.

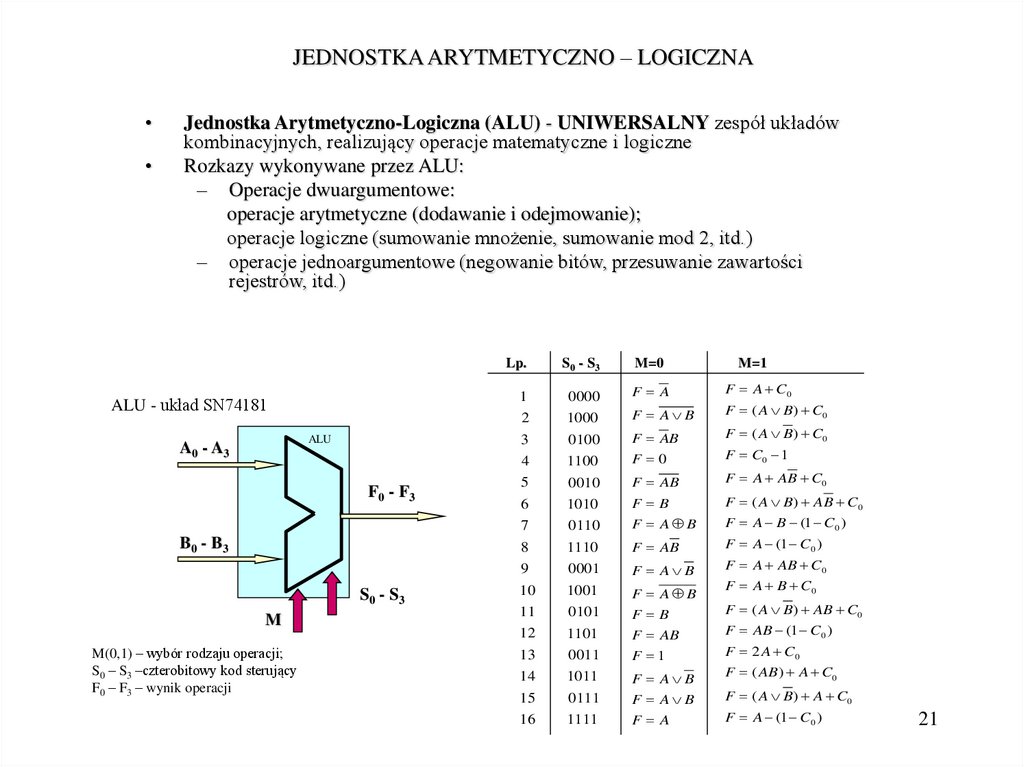

JEDNOSTKA ARYTMETYCZNO – LOGICZNAJednostka Arytmetyczno-Logiczna (ALU) - UNIWERSALNY zespół układów

kombinacyjnych, realizujący operacje matematyczne i logiczne

Rozkazy wykonywane przez ALU:

– Operacje dwuargumentowe:

operacje arytmetyczne (dodawanie i odejmowanie);

operacje logiczne (sumowanie mnożenie, sumowanie mod 2, itd.)

– operacje jednoargumentowe (negowanie bitów, przesuwanie zawartości

rejestrów, itd.)

ALU - układ SN74181

ALU

A0 - A3

F0 - F3

B0 - B3

S0 - S3

M

M(0,1) – wybór rodzaju operacji;

S0 – S3 –czterobitowy kod sterujący

F0 – F3 – wynik operacji

Lp.

S0 - S3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

0000

1000

0100

1100

0010

1010

0110

1110

0001

1001

0101

1101

0011

1011

0111

1111

M=0

M=1

F A

F A C0

F A B

F ( A B ) C0

F AB

F 0

F ( A B ) C0

F AB

F B

F A B

F A A B C0

F AB

F A (1 C0 )

F A B

F A AB C0

F A B

F B

F AB

F 1

F A B

F A B

F A

F C0 1

F ( A B ) A B C0

F A B (1 C0 )

F A B C0

F ( A B ) AB C0

F AB (1 C0 )

F 2 A C0

F ( AB) A C0

F ( A B ) A C0

F A (1 C0 )

21

22.

Adresowanie pamięci operacyjnejProcesory

16-bitowe

Do zaadresowania 1 MB pamięci operacyjnej (o gradacji 8 bitów (1 bajt))

wymagane jest 20 linii adresowych – 220

220 -linie adresowe

Rejestr segmentowy wskazuje na ciągły obszar

pamięci o wielkości 64 kB

216

Każdy indywidualny adres pamięci zawiera komórkę o gradacji 8-bitów

Przyrost wartości o 1 w rejestrze segmentowym zwiększa o 16 adres fizyczny

22

23.

Procesory16-bitowe

Adresowanie pamięci operacyjnej

W heksadecymalnym systemie zapisu :

segment*10

+ offset

(adres logiczny)*10 + (adres logiczny)

0002h *10h

=

00020h

+0003h

-----------00023h

adres fizyczny

Dla procesorów 16-bitowych adres fizyczny komórki pamięci operacyjnej był realizowany poprzez

dwa adresy logiczne (rejestrów 16-bitowych)

23

24.

Adresowanie pamięci operacyjnejProcesory

16-bitowe

Dostęp do pamięci operacyjnej dla kodów rozkazu, danych źródłowych, danych docelowych jak i

obszaru przechowującego dane tymczasowe ( stos) realizowany jest poprzez następujące konfiguracje

rejestrów:

Code Segment

CS:IP

Data Segment

DS:SI

Extra Segment

ES:DI

Stack Segment

SS:BP

24

25.

Adresowanie pamięci operacyjnejAdresowanie 3 D

Adresowanie wybranej komórki pamięci następuje w dwóch fazach:

-

w fazie pierwszej, wraz z opadającym sygnałem RAS (Row Address Strobe), na szynie adresowej wystawiany jest

adres wiersza,

-

w fazie drugiej – przy opadającym zboczu sygnału CAS (Column Address Strobe) – adres kolumny.

W ten sposób za pomocą 10 linii adresowych A[0:9] oraz linii RAS i CAS uzyskuje się 20 bitowy adres zdolny zaadresować

obszar 1 MEG komórek (1 MEG = 1024 x 1024)

25

26.

Adresowanie pamięci operacyjnejTypy adresacji

Typ adresacji jest to sposób określenia miejsca przechowywania argumentów rozkazu

Kod rozkazu zawiera:

rodzaj wykonywanego rozkazu czyli tzw. kod operacji

(w pierwszym bajcie rozkazu)

opcjonalnie operandy i/lub adresy operandów wykonywanych

operacji

WYBRANE TRYBY ADRESOWANIA

Adresowanie natychmiastowe

argument rozkazu zawarty jest w

kodzie rozkazu

MOV AX,1234

MOV BYTE PTR[ABBA],1234

Adresowanie bezpośrednie

kod rozkazu zawiera adres komórki

pamięci,w której przechowywany

jest argument

MOV BL,[ABBA]

MOV [ABBA],BL

26

27.

Adresowanie pamięci operacyjnejTypy adresacji

Adresowanie rejestrowe

w kodzie rozkazu określony

jest rejestr, w którym

przechowywany jest argument

MOV AX,BX

Adresowanie pośrednie (lub

rejestrowe pośrednie)

Umożliwia modyfikację położenia

argumentu w pamięci w trakcie

wykonywania Programu, lub inaczej

adres argumentu może zostać

wyliczony przez program

MOV [BX],AL

Adresowanie indeksowe z

przemieszczeniem

adres argumentu w pamięci

obliczany jest jako suma zawartości

rejestru określonego w kodzie i

wartości umieszczonej w kodzie

rozkazu zwanej przemieszczeniem

MOV [BX+4],AL

27

28.

Pojęcia podstawoweStan komputera:

superpozycja stanu procesora i pamięci

Stan procesora:

informacja zawarta w rejestrach (pamięć wewnętrzna)

Zmiana stanu komputera: wykonanie rozkazu przez CPU

Rozkaz:

jest funkcją, która przeprowadza stan wejściowy w stan wyjściowy

Pamięć:

jest dziedziną i zbiorem wartości każdego rozkazu

Architektura komputera:

zbiór rozkazów i pamięć

Maszyna właściwa

lub mikromaszyna

(host machine):

interpreter kodów rozkazów (procesor)

Maszyna wirtualna:

przetwarzanie sekwencji poleceń (instrukcji) na bezpośrednio

wykonywane rozkazy zakodowane w pamięci (komputer z

oprogramowaniem)

Proces:

stan wejściowy + sekwencja rozkazów (w chwili wykonania rozkazu

jest znany adres lub sposób wyznaczenia adresu kolejnego rozkazu)

Cykl procesora:

czas potrzebny na zmianę stanu procesora

Cykl pamięci

(cykl rozkazowy):

czas potrzebny na zmianę stanu pamięci

28

29.

Cykle wykonania rozkazucykle procesora

Mi

F

D

(R)

E

W

Mj

cykl pamięci

Pobranie kodu z pamięci F,

F

- pobranie kodu

Dekodowanie D, - wytworzenie sygnałów sterujących,

wytworzenie adresu argumentu,

D

- dekodowanie

R

- odczyt argumentu

Odczyt argumentów z pamięci, R

E

- wytworzenie wyniku

Wytworzenie wyniku, E,

W

- zapamiętanie wyniku

Zapamiętanie wyniku w pamięci lub rejestrze procesora, W

Mi,j - stan komputera

W każdym etapie wykonania rozkazu występują:

- identyfikacja (adresowanie danych)

- wybór (adresowanie) jednostek wykonawczych

29

30.

Szybkość przetwarzaniaN

t p Tc I i Ci

tp

czas wykonania programu bez przerwań

Tc

czas cyklu procesora

Ii

liczba wykonań instrukcji i-tego typu

Ci

średnia liczba cykli potrzebnych na

wykonanie instrukcji

i 1

Schemat przetwarzania

Fi

Di

Ei

Wi

Fi 1

Di 1

Ei 1

Wi 1

Fi 2

t

Di 2

przetwarzanie

sekwencyjne

Fi

Di

Ei

Wi 3

Fi 1

Di 1

Ei 1

Ei 2

Wi 2

Fi 2

Di 2

Di 1

Ei 1

Wi 1

Wi

Fi 4

Fi 3

Di 4

Wi 1

Ei 2

Di 3

Ei 4

Fi 5

Di 5

Wi 2

Ei 3

Fi 6

Wi 3

t

przetwarzanie

30

potokowe

31.

Poziomy maszynowe i ich powiązaniaPoziom maszynowy:

L5

L4

L3

L2

język makropoleceń

język algorytmiczny

język asemblerowy

translator języka makropoleceń

opis działania komputera poprzez

realizacje rozkazów na umownych

poziomach abstrakcji

translator języka algorytmicznego

translator języka asemblerowego

funkcje systemu operacyjnego

system operacyjny

Maszyna

wirtualna

interpreter kodu maszynowego

L1

struktura logiczna

interpreter mikroprogramu

L0

przetwornik sygnałów

Maszyna

rzeczywista

Warstwy poziomu maszynowego:

L0 – przetwornik sygnałów (hardware)

L1 – struktura logiczna z generatorem mikrorozkazów (firmware)

L2 – system operacyjny (operating system)

L3 – język asemblerowy (assembly language)

L4 – język algorytmiczny (high-level language)

L5 – język makropoleceń (application program)

31

32.

Pojęcia podstawowe – poziom maszynowyKod maszynowy – język rozumiany przez procesor, notowany w postaci dwójkowej, obecnie opisywany

symbolicznie za pomocą mnemoników, identyfikuje maszynę rzeczywistą

System operacyjny – poziom hybrydowy, udostępnienie listy rozkazów procesora, standardowe usługi systemu

Asembler – język programowania niskiego poziomu, wykorzystujący instrukcje procesora. Program napisany w

asemblerze jest tłumaczony na (binarny) kod maszynowy, najniższy poziom języka symbolicznego – udostępnienie

elementarnych działań procesora, operacje na pamięci oraz systemu operacyjnego

Język algorytmiczny – język wysokiego poziomu (C++, Fortran, Pascal)

Kompilacja – tłumaczenie algorytmu na sekwencję rozkazów procesora i wytworzenie obrazu struktur danych

algorytmu w pamięci

Interpretacja – osobne tłumaczenie każdego polecenia na sekwencje rozkazów procesora w chwili użycia

Maszyna wirtualna - oprogramowanie rozbudowujące system komputerowy o nowe właściwości funkcjonalne,

nieudostępniane przez sam sprzęt

Program źródłowy - tekst programu wyrażonego w język programowania, nadający się do czytania przez człowieka

i przeznaczony do tłumaczenia przez translator.

Program wynikowy - efekt pracy kompilatora, półprodukt tłumaczenia w postaci nadającej się do dalszego

tłumaczenia przez asembler lub do konsolidacji.

Program wykonywalny - plik utworzony z plików wynikowych (przetłumaczonych przez kompilator) i modułów

bibliotecznych wskutek połączenia ich przez program łączący. Plik wykonywalny zawiera globalnie ujednolicone

adresy i jest zdatny do ładowania i wykonania przez procesor

.txt

program źródłowy

.obj

.exe

kompilator

program wynikowy

konsolidator

procesor

inne moduły

procesor

program wykonywalny

kod maszynowy

procesor

32

История

История