Похожие презентации:

Программируемая логическая интегральная схема

1.

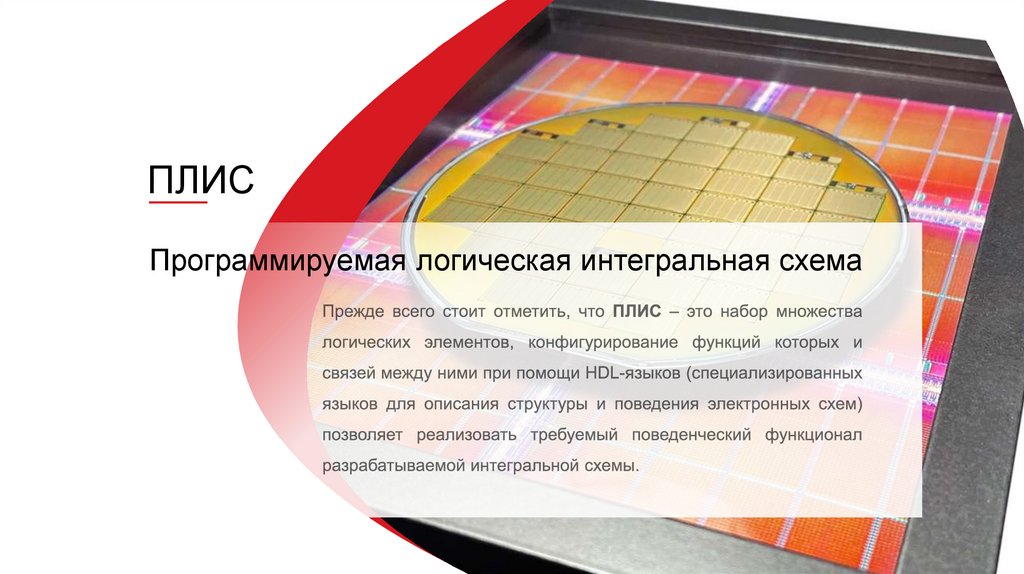

ПЛИСПрограммируемая логическая интегральная схема

2.

РАЗДЕЛ 1ПРОЦЕССОР

ПЛИС

КРИСТАЛЛ

ПЛИС

2

vs

3.

ЛОГИКАПЛИС vs

ПРОЦЕССОР

4.

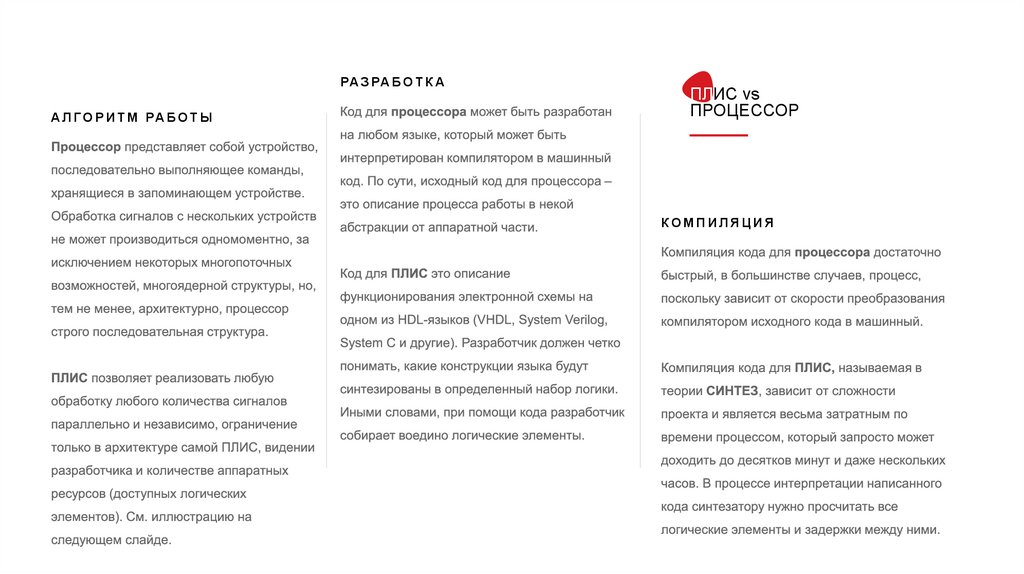

РА З РА Б О Т К АА Л Г О Р И Т М РА Б О Т Ы

ПЛИС vs

ПРОЦЕССОР

КОМПИЛЯЦИЯ

5.

ИНСТРУКЦИЯИНСТРУКЦИЯ

ИНСТРУКЦИЯ

ИНСТРУКЦИЯ

ИНСТРУКЦИЯ

CPU/

DSP

ИНСТРУКЦИЯ

ПЛИС

ОСОБЕННОСТИ

ПРИМЕНЕНИЯ

CPU/

DSP

ПЛИС

ТЕПЛОВЫДЕЛЕНИЕ

ГИБКОСТЬ ДЛЯ

РА З Л И Ч Н Ы Х

ПРИМЕНЕНИЙ

ПРОИЗВОДИТЕЛЬНОСТЬ

КРАТКИЙ ИТОГ СРАВНЕНИЯ

С РА В Н Е Н И Е А Л Г О Р И Т М О В

РА Б О Т Ы

ИНСТРУКЦИЯ

6.

Дальнейшие отличия процессора отПЛИС будут рассмотрены в

предметном формате на следующих

слайдах.

6

7.

КРИСТАЛЛПЛИС

Д А Л Е Е РАС С М О Т Р И М К А Ж Д У Ю С Т Р У К Т У Р У П О Д Р О Б Н Е Е

8.

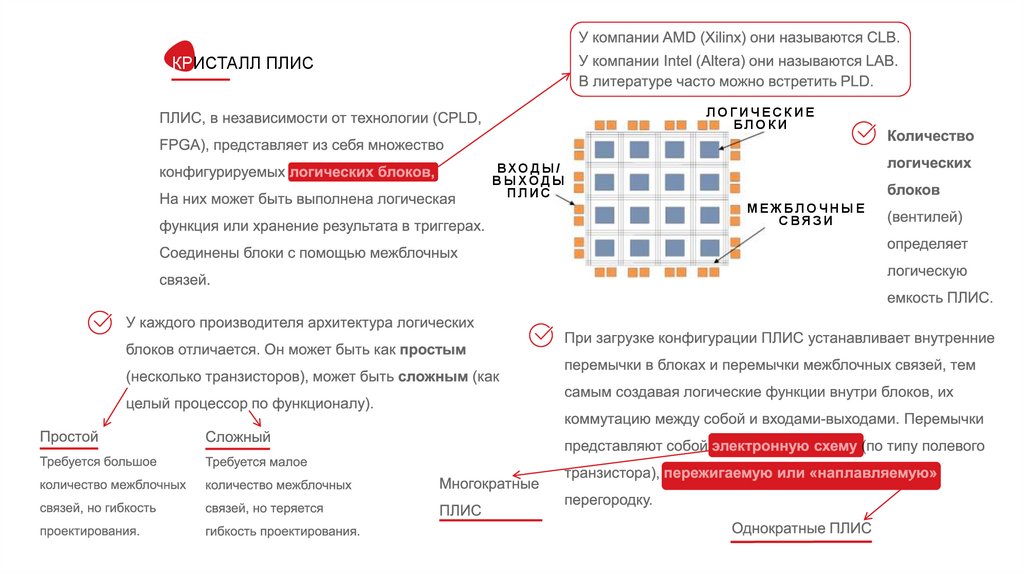

КРИСТАЛЛ ПЛИСЛОГИЧЕСКИЕ

БЛОКИ

ВХОД Ы /

ВЫХОДЫ

ПЛИС

МЕЖБЛОЧНЫЕ

СВЯЗИ

9.

ВХОД ЫЛ О Г.

БЛОК

(PLA)

ВХОД Ы

ВЕНТИЛИ «ИЛИ»

ПРЕДОХРАНИТЕЛИ

(ВЕНТИЛИ «И»)

Л О Г.

БЛОК

( PA L )

ВЕНТИЛИ «ИЛИ»

ПРЕДОХРАНИТЕЛИ

(ВЕНТИЛИ «И»)

ВЫХОДЫ

ВЫХОДЫ

КРИСТАЛЛ ПЛИС

С Т Р У К Т У Р Ы PA L , P L A , S P L D , G A L

10.

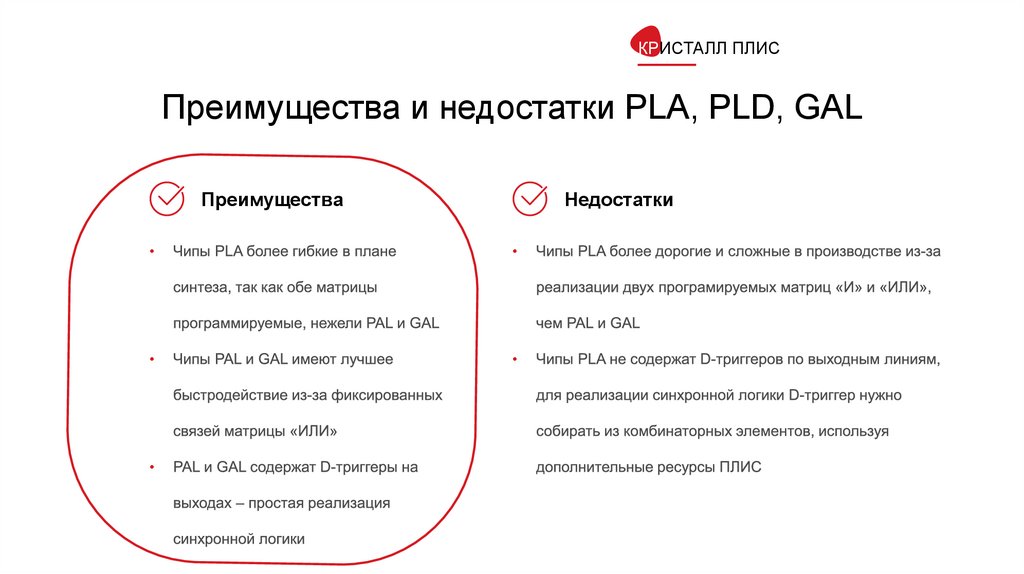

КРИСТАЛЛ ПЛИСПреимущества и недостатки PLA, PLD, GAL

Преимущества

Недостатки

11.

Л О Г.БЛОК

ИНТЕРКОННЕКТ

Л О Г.

БЛОК

Л О Г.

БЛОК

ВХОД Ы / В Ы ХОД Ы П Л И С

ВХОД Ы / В Ы ХОД Ы П Л И С

Л О Г.

БЛОК

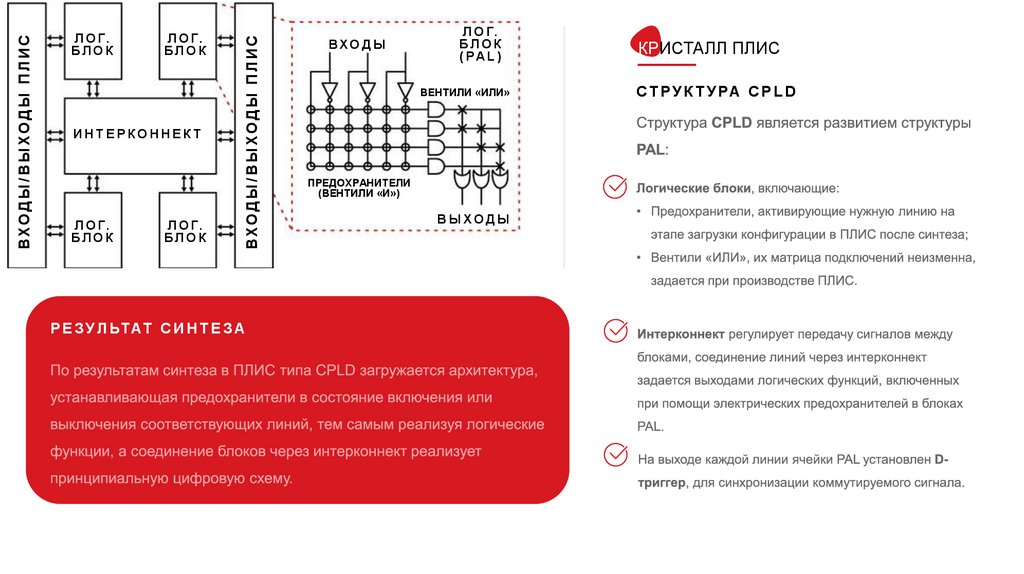

Р Е З У Л ЬТАТ С И Н Т Е З А

ВХОД Ы

Л О Г.

БЛОК

( PA L )

ВЕНТИЛИ «ИЛИ»

ПРЕДОХРАНИТЕЛИ

(ВЕНТИЛИ «И»)

ВЫХОДЫ

КРИСТАЛЛ ПЛИС

С Т Р У К Т У РА C P L D

12.

КРИСТАЛЛ ПЛИСПреимущества и недостатки CPLD

Преимущества

Недостатки

13.

ВХ/ВЫХ

ПЛИС

ПЛИС

ЛО Г.

БЛО К

ВХ/

ВЫХ

ПЛИС

ВХ/

ВЫХ

ПЛИС

ЛО Г.

БЛО К

О П Е Р АН Д Ы

ВХ/

ВЫХ

D

ЛО Г.

БЛО К

( CLB)

RESET

ИНТ ЕРКО ННЕКТ ( SB)

ЛО Г.

БЛОК

ВХ/

ВЫХ

ВХ/

ВЫХ

ПЛИС

ЛО Г.

БЛОК

ВХ/

ВЫХ

ПЛИС

MUX

CLK

ЛО Г.

БЛОК

ВХ/

ВЫХ

КРИСТАЛЛ ПЛИС

LUT

ПЛИС

ПЛИС

ПРИМЕР LUT

a

b

&

a

b

c

y

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

1

1

1

0

1

1

1

c

y

1

0

1

1

1

0

000

001

010

011

100

101

1

1

110

111

MUX

y

ab c

С Т Р У К Т У РА F P G A

14.

КРИСТАЛЛ ПЛИСПреимущества и недостатки FPGA

Преимущества

Недостатки

15.

КРИСТАЛЛ ПЛИСFPGA vs CPLD

Подача питания

Снятие питания

Временной

анализ

Потребление

энергии

Доступные

ресурсы

Работа в

нагруженном

режиме

CPLD

FPGA

16.

ARMCortex A9

L1 Cache

GPIO

JTAG

SD

ARM

Cort ex A9

L1 Cache

I2C

L2 Cache

WDT

Timer

QSPI/

NAND

DDR/SD

RAM

из

FPG A

UART

SPI

CAN

Ethernet

USB

в

FPG A

FPG A

Config

КРИСТАЛЛ ПЛИС

ВХОДЫ/ВЫХОДЫ

ПРОЦЕССОРА

ВХОДЫ/ВЫХОДЫ

ПРОЦЕССОРА

DMA

УД О Б С Т В О :

С Т Р У К Т У РА S o C

FPGA

ВХОДЫ/ВЫХОДЫ ПЛИС

Р Е З У Л ЬТАТ С И Н Т Е З А

В Р Е М Я РА З РА Б О Т К И :

17.

КРИСТАЛЛ ПЛИСПреимущества и недостатки SoC

Преимущества

Недостатки

18.

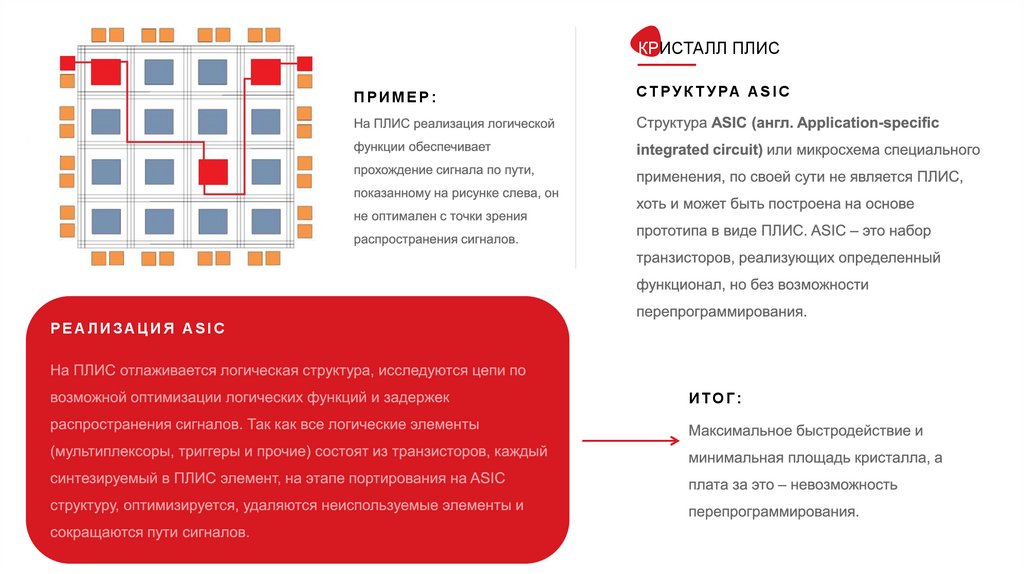

КРИСТАЛЛ ПЛИСПРИМЕР:

С Т Р У К Т У РА A S I C

РЕАЛИЗ АЦИЯ ASI C

ИТОГ:

19.

КРИСТАЛЛ ПЛИСПреимущества и недостатки ASIC

Преимущества

Недостатки

20.

КРИСТАЛЛ ПЛИСFPGA

CPLD

ПРИМЕНЕНИЕ

SoC

ПРОЦЕССОР

21.

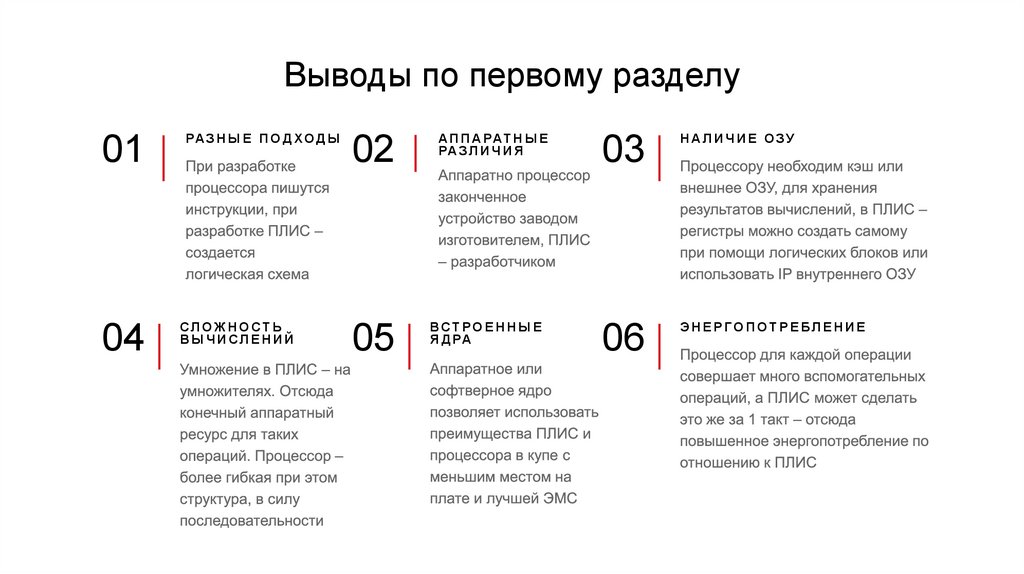

Выводы по первому разделу01

РА З Н Ы Е П О Д Х О Д Ы

04

СЛОЖНОСТЬ

ВЫЧИСЛЕНИЙ

02

А П П А РАТ Н Ы Е

РА З Л И Ч И Я

05

ВСТ РО Е Н НЫ Е

Я Д РА

03

НАЛИЧИЕ ОЗУ

06

ЭНЕРГОПОТРЕБЛЕНИЕ

22.

РАЗДЕЛ 2ИНТЕРФЕЙСЫ

ПЛИС

22

23.

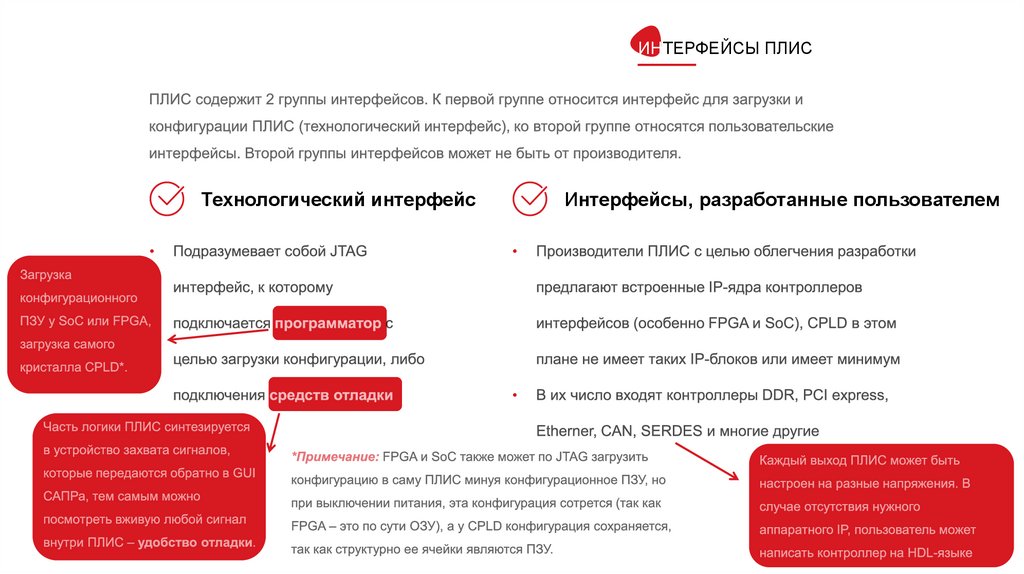

ИНТЕРФЕЙСЫ ПЛИСТехнологический интерфейс

Интерфейсы, разработанные пользователем

24.

ИНТЕРФЕЙСЫ ПЛИСТехнологический интерфейс

25.

ИНТЕРФЕЙСЫ ПЛИСИнтерфейсы, разработанные пользователем

IP Eternet контроллера

Пример интерфейсного ядра

26.

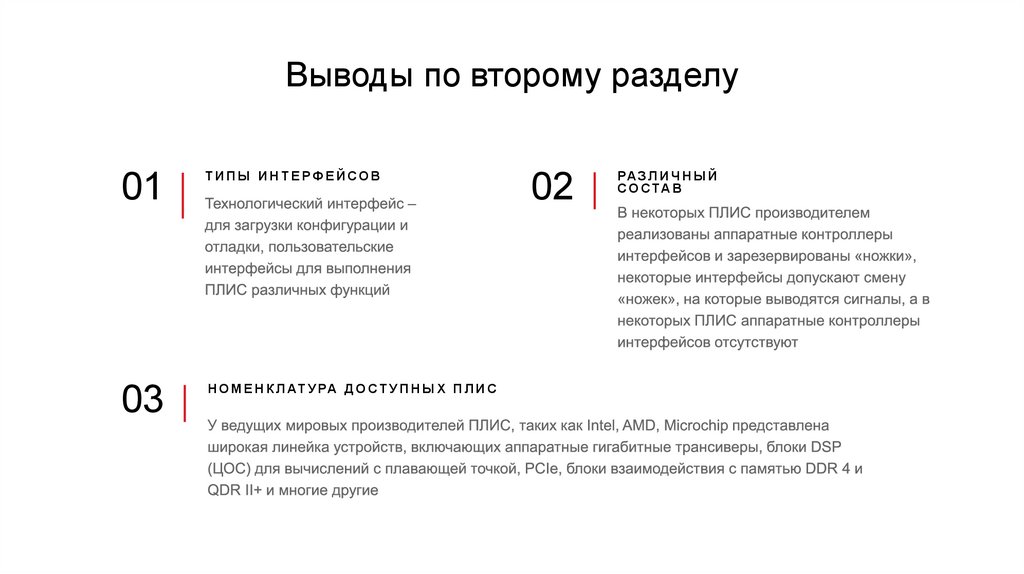

Выводы по второму разделу01

ТИПЫ ИНТЕРФЕЙСОВ

03

Н О М Е Н К Л АТ У РА Д О С Т У П Н Ы Х П Л И С

02

РА З Л И Ч Н Ы Й

С О С ТАВ

27.

РАЗДЕЛ 3ПРОЕКТИРОВАНИЕ

ПЛИС

27

28.

Уровниразработки

ПЛИС

ПРОЕКТИРОВАНИЕ ПЛИС

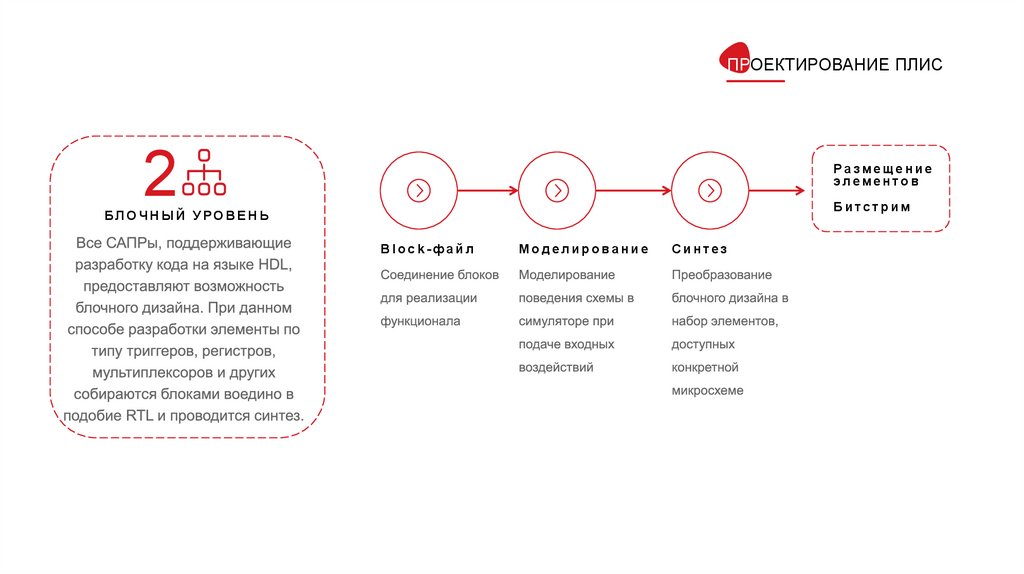

2

БЛОЧНЫЙ

1

НИЗКИЙ

3

ВЫСОКИЙ

29.

ПРОЕКТИРОВАНИЕ ПЛИССреды разработки

1

Размещение

элементов

Битстрим

НИЗКИЙ УРОВЕНЬ

HDL-описание

Моделирование

Синтез

30.

ПРОЕКТИРОВАНИЕ ПЛИС2

Размещение

элементов

Битстрим

БЛОЧНЫЙ УРОВЕНЬ

Block-файл

Моделирование

Синтез

31.

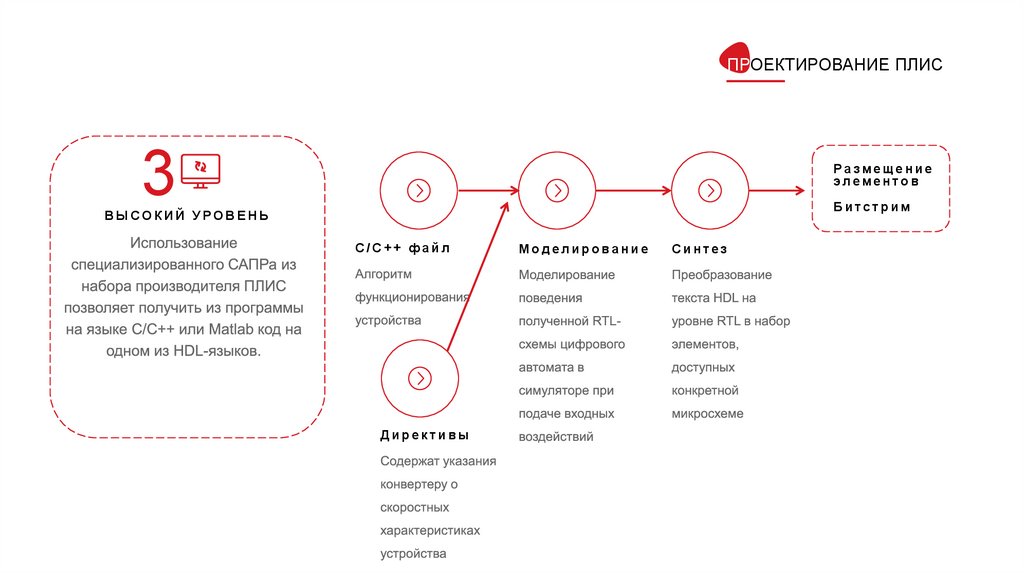

ПРОЕКТИРОВАНИЕ ПЛИС3

Размещение

элементов

Битстрим

ВЫСОКИЙ УРОВЕНЬ

С/С++ файл

Директивы

Моделирование

Синтез

32.

Языки разработкиVerilog

VHDL

System

verilog

ПРОЕКТИРОВАНИЕ ПЛИС

System C

C/C++

Схемотехническое

моделирование

Логическое

моделирование

RTL-описание

Тестирование

Функциональная

верификация

Поведенческое

моделирование

Программное

проектирование

Архитектурноалгоритмическое

проектирование

Аппаратные языки

Программные языки

33.

Важнаяособенность

ПРОЕКТИРОВАНИЕ ПЛИС

34.

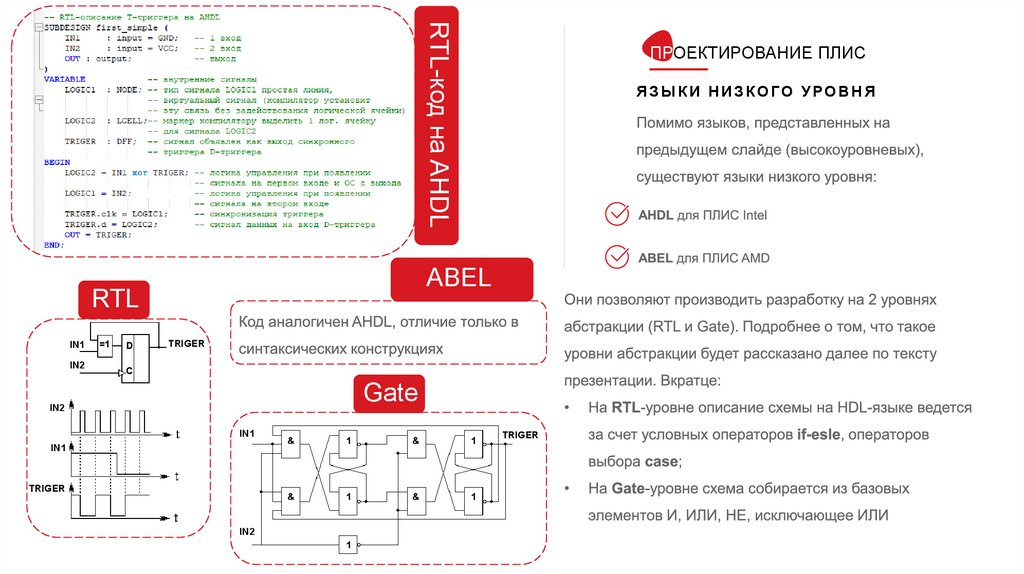

RTL-код на AHDLIN2

=1

D

ЯЗЫКИ НИЗКОГО УРОВНЯ

ABEL

RTL

IN1

ПРОЕКТИРОВАНИЕ ПЛИС

TRIGER

C

Gate

IN2

IN1

IN1

TRIGER

&

1

&

1

&

1

&

1

IN2

1

TRIGER

35.

ПРОЕКТИРОВАНИЕ ПЛИСПреимущества и недостатки низкоуровневых

AHDL и ABEL

Преимущества

Недостатки

36.

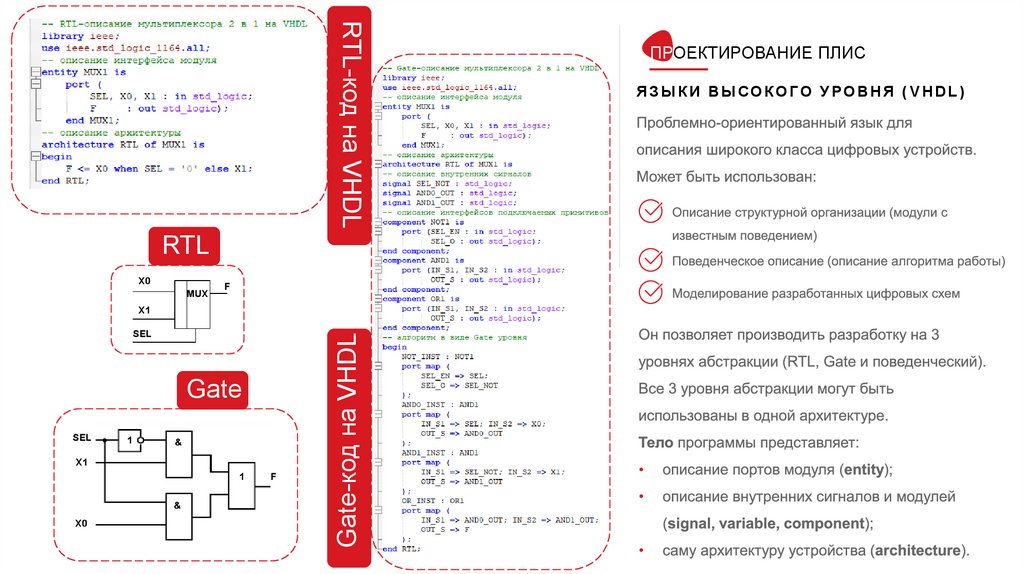

RTL-код на VHDLПРОЕКТИРОВАНИЕ ПЛИС

ЯЗЫКИ ВЫСОКОГО УРОВНЯ ( VHDL)

RTL

X0

MUX

ABEL

F

SEL

Gate

SEL

1

&

X1

1

&

X0

F

Gate-код на VHDL

X1

37.

ПРОЕКТИРОВАНИЕ ПЛИСПреимущества и недостатки VHDL

Преимущества

Недостатки

38.

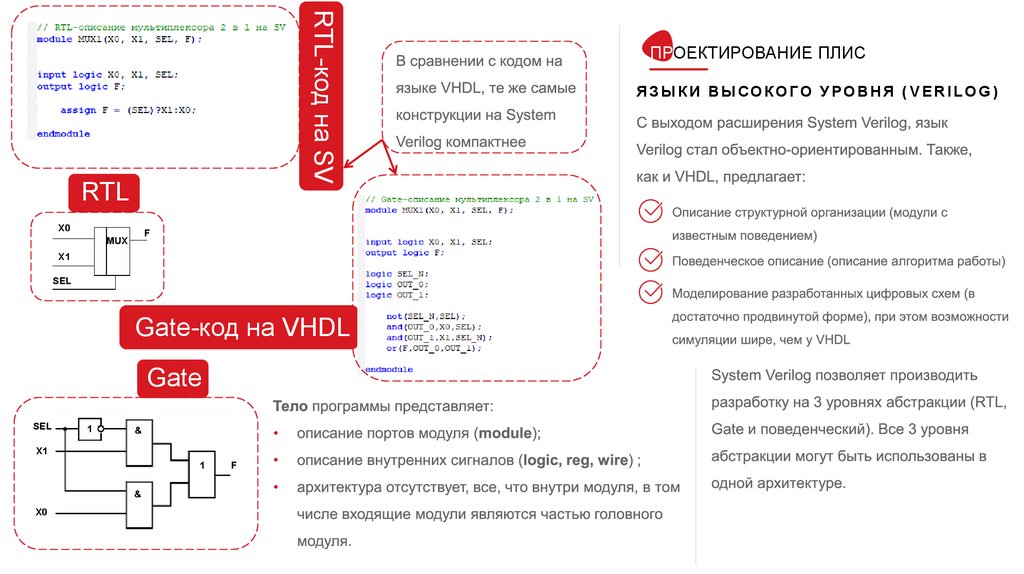

RTL-код на SVRTL

X0

ПРОЕКТИРОВАНИЕ ПЛИС

ЯЗЫКИ ВЫСОКОГО УРОВНЯ ( VERI LOG)

F

MUX

X1

ABEL

SEL

Gate-код на VHDL

Gate

SEL

1

&

X1

1

&

X0

F

39.

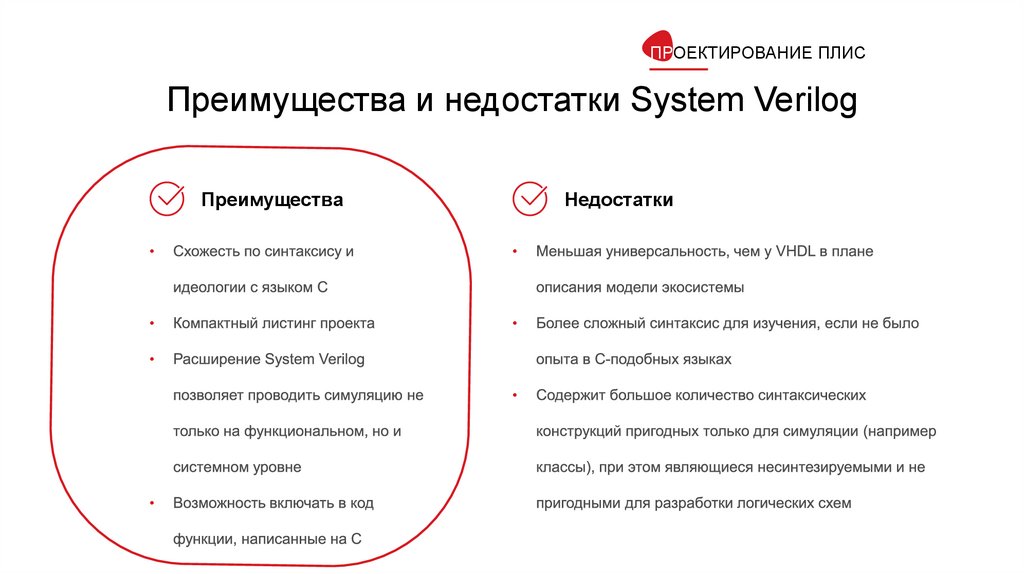

ПРОЕКТИРОВАНИЕ ПЛИСПреимущества и недостатки System Verilog

Преимущества

Недостатки

40.

ПРОЕКТИРОВАНИЕ ПЛИСAHDL, ABEL

VHDL или

SYSTEM VERILOG

ПРИМЕНЕНИЕ

VHDL

S ys t e m Ve r i l o g

41.

ПРОЕКТИРОВАНИЕ ПЛИСОписание

внутренних

сигналов

Описание

подключаемых

модулей

Список

чувствительности

SV

VHDL

Сравнение концепций VHDL и SV

Описание

внешних портов

42.

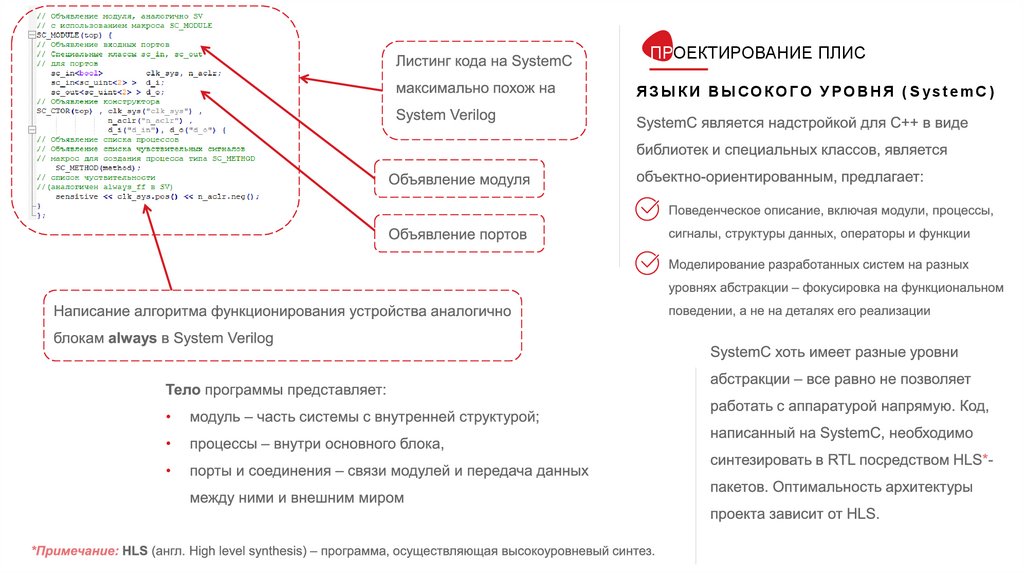

ПРОЕКТИРОВАНИЕ ПЛИСЯ ЗЫ КИ ВЫ СО КО ГО У РО ВНЯ ( S ys t e m C )

ABEL

43.

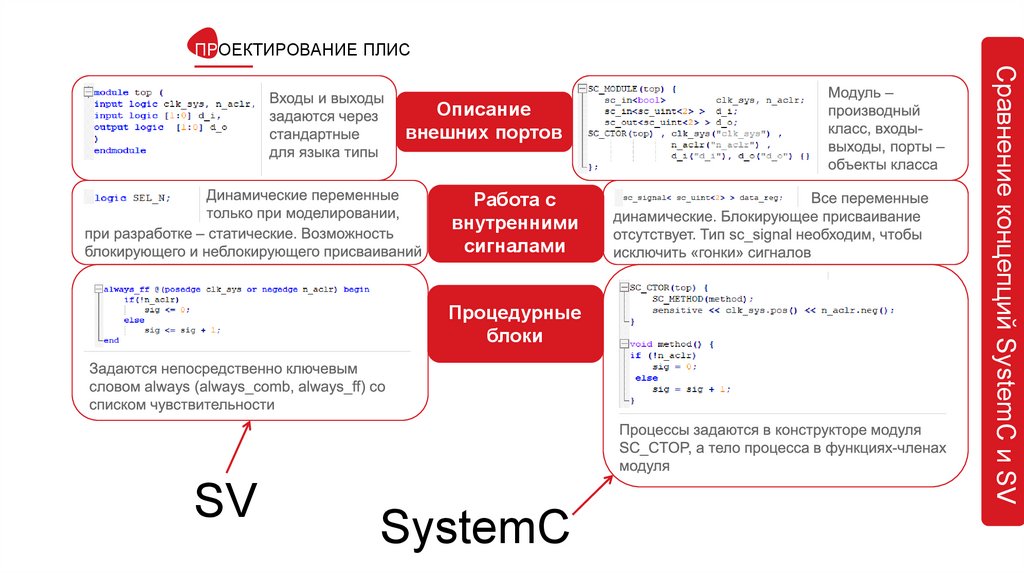

ПРОЕКТИРОВАНИЕ ПЛИСРабота с

внутренними

сигналами

Процедурные

блоки

SV

SystemC

Сравнение концепций SystemC и SV

Описание

внешних портов

44.

ПРОЕКТИРОВАНИЕ ПЛИСПреимущества и недостатки SystemС

Недостатки

Преимущества

45.

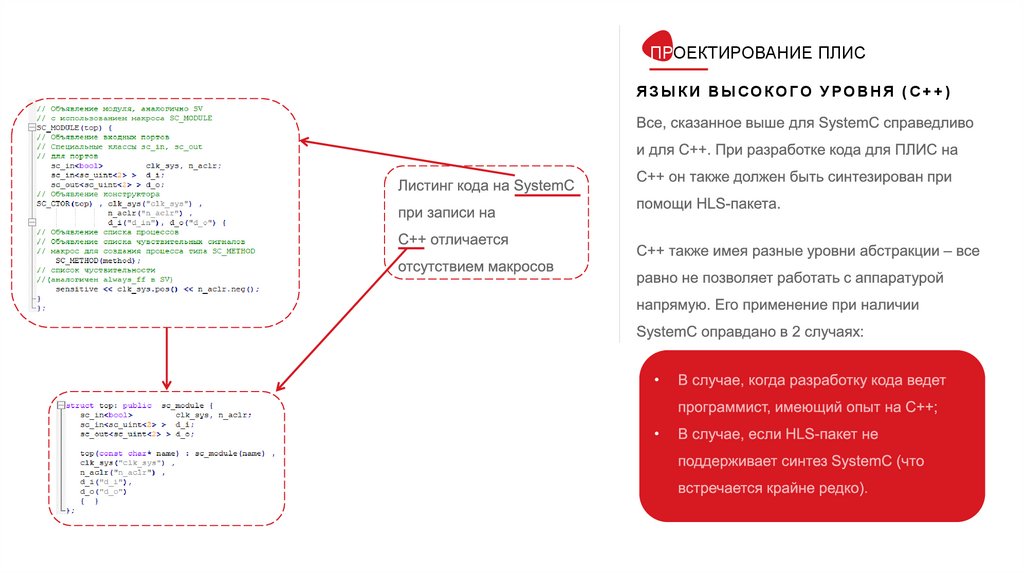

ПРОЕКТИРОВАНИЕ ПЛИСЯЗЫКИ ВЫСОКОГО УРОВНЯ ( C++)

46.

ПРОЕКТИРОВАНИЕ ПЛИСС++/SystemC

ПРИМЕНЕНИЕ

VHDL или

SYSTEM VERILOG

47.

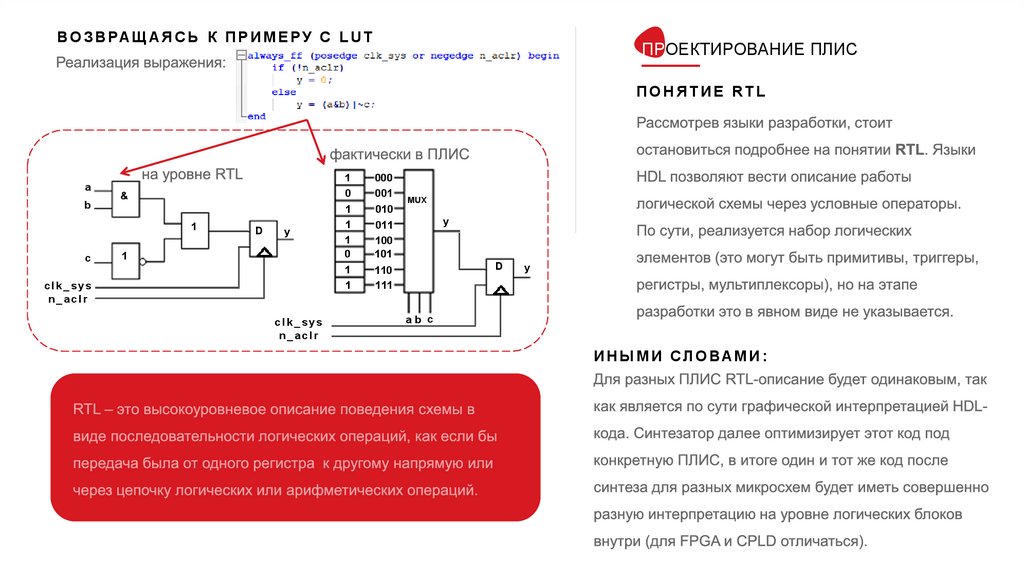

В О З В РА Щ А Я С Ь К П Р И М Е Р У С L U TПРОЕКТИРОВАНИЕ ПЛИС

ПОНЯТИЕ RTL

a

b

&

1

c

D

y

1

clk_sys

n_aclr

clk_sys

n_aclr

1

0

1

1

1

0

000

001

010

011

100

101

1

1

110

111

MUX

y

D

y

ab c

И Н Ы М И С Л О ВА М И :

48.

ПРОЕКТИРОВАНИЕ ПЛИСП О Н Я Т И Е G AT E

a

b

&

1

c

D

y

1

clk_sys

n_aclr

clk_sys

n_aclr

1

0

1

1

1

0

000

001

010

011

100

101

1

1

110

111

MUX

y

D

ab c

y

49.

ПРОЕКТИРОВАНИЕ ПЛИСПОНЯТИЕ

ПОВЕДЕНЧЕСКОГО УРОВНЯ

ПОНЯТИЕ БЛОЧНОГО

УРОВНЯ

50.

Все рассмотренные языки описанияаппаратуры и уровни разработки дают

степень свободы разработчику, а также

возможность сочетать несколько

подходов в рамках 1 проекта.

51.

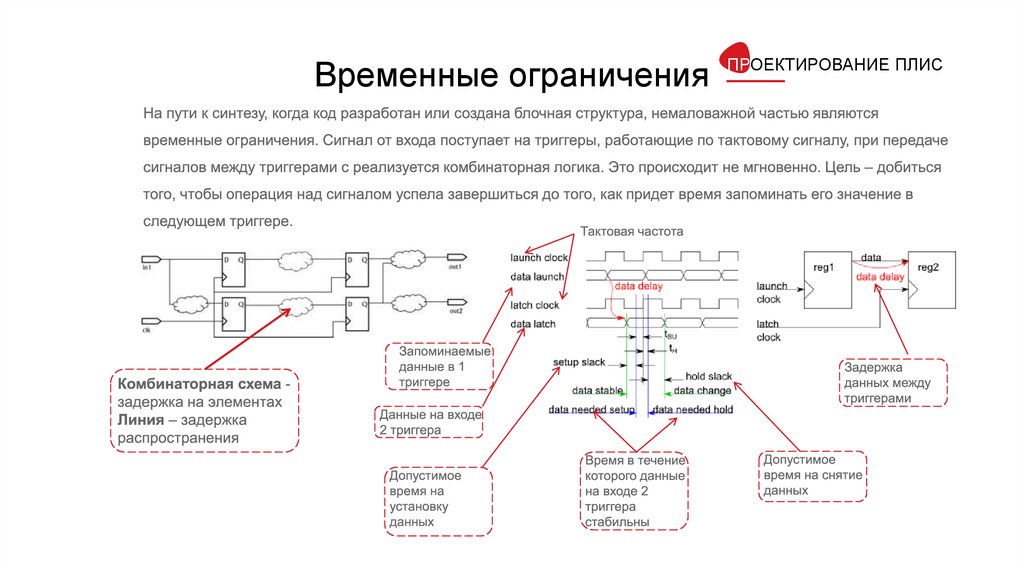

Временные ограниченияПРОЕКТИРОВАНИЕ ПЛИС

52.

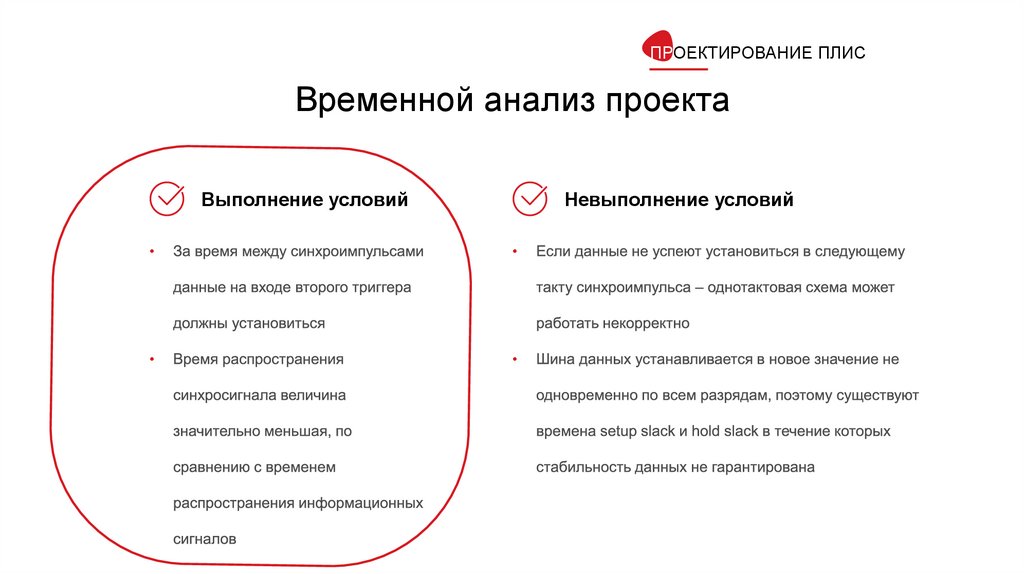

ПРОЕКТИРОВАНИЕ ПЛИСВременной анализ проекта

Выполнение условий

Невыполнение условий

53.

ПРОЕКТИРОВАНИЕ ПЛИСУчет

временных

соотношений

Ф А Й Л О Г РА Н И Ч Е Н И Й

У К АЗ Ы ВАЮ Т С Я Ч АС Т О Т Ы П Р О Е К ТА

ИСКЛЮЧЕНИЯ

53

54.

ПРОЕКТИРОВАНИЕ ПЛИСФайл

временных

ограничений

О П И С АН И Е ТАК Т О В О Г О С И Г Н А Л А

ПУТЬ БОЛЕЕ 1 ПЕРИОДА

ТАК Т О В О Г О С И Г Н А Л А

ПУТЬ НЕ ТРЕБУЮЩИЙ АНАЛИЗ А

55.

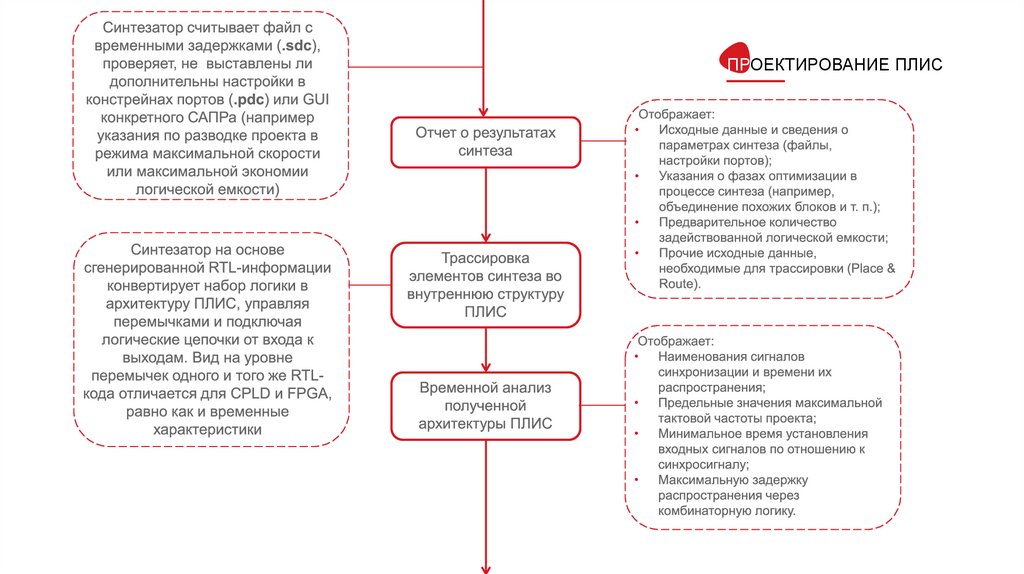

Синтез проектаПРОЕКТИРОВАНИЕ ПЛИС

56.

ПРОЕКТИРОВАНИЕ ПЛИС57.

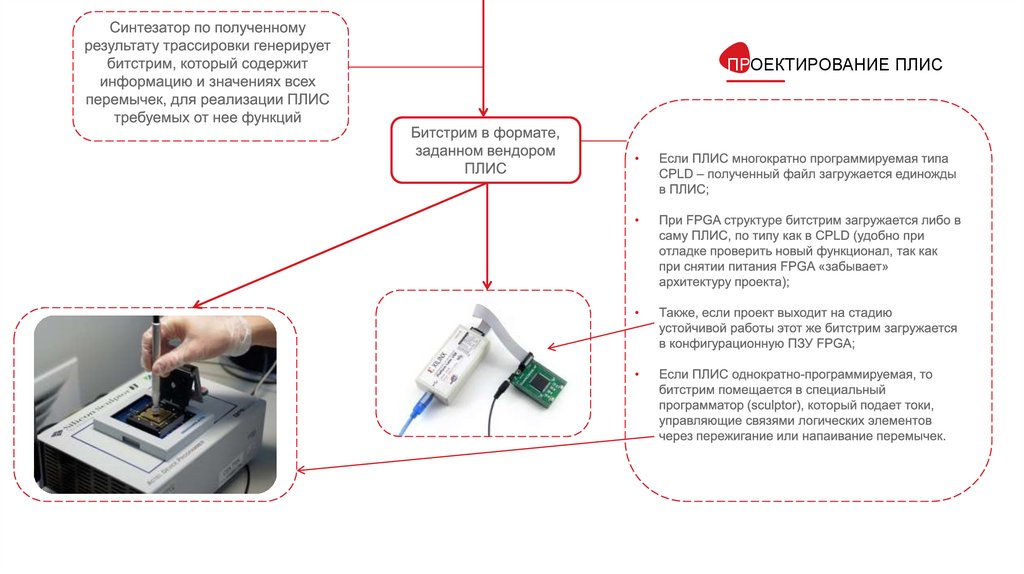

ПРОЕКТИРОВАНИЕ ПЛИС58.

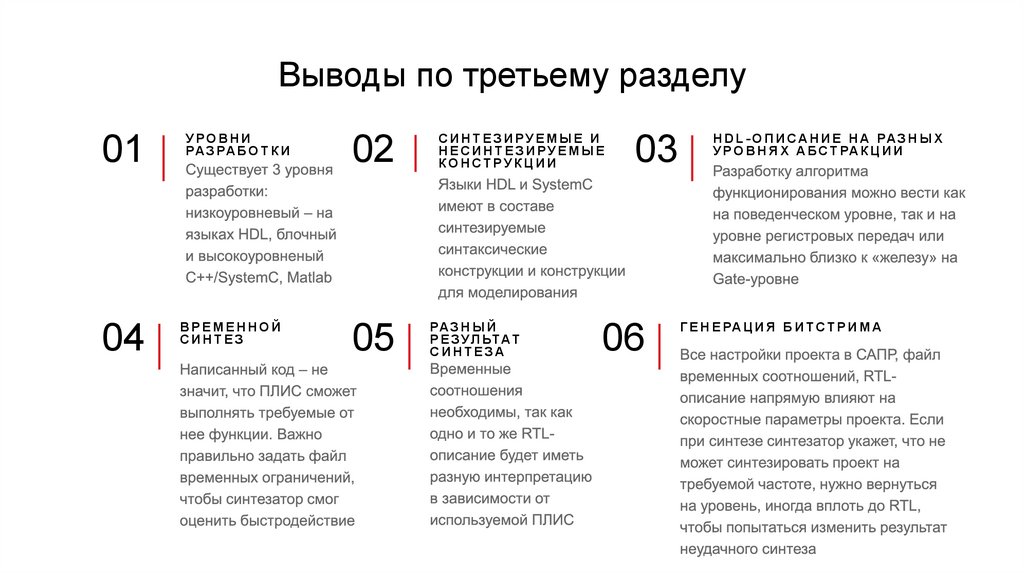

Выводы по третьему разделу01

УРОВНИ

РА З РА Б О Т К И

04

ВРЕМЕННОЙ

СИНТЕЗ

02

СИНТЕЗИРУЕМЫЕ И

НЕСИНТЕЗИРУЕМЫЕ

КОНСТРУКЦИИ

05

РА З Н Ы Й

Р Е З У Л ЬТ АТ

СИНТЕЗА

03

06

H D L - О П И С А Н И Е Н А РА З Н Ы Х

У Р О В Н Я Х А Б С Т РА К Ц И И

Г Е Н Е РА Ц И Я Б И Т С Т Р И М А

59.

ВМЕСТОЗАКЛЮЧЕНИЯ

ПРИМЕНЕНИЕ

ПЛИС

РА З РА Б О Т К А

ПЛИС

Информатика

Информатика