Похожие презентации:

Информатика и базы данных. Типы структур ВМ и ВС (тема №1)

1. Информатика и базы данных

Москин Николай ДмитриевичИнститут математики и информационных

технологий, ПетрГУ

1

2. Список литературы

Симонович С. В. Информатика. Базовый курс. Учебник длявузов. 3-е изд. СПб.: Питер, 2020.

Гусева Е. Н., Ефимова И. Ю., Коробков Р. И., Коробкова К.

В., Мовчан И. Н., Савельева Л. А. Информатика. Учебное

пособие. 4-е изд. М.: ФЛИНТА, 2016

(http://biblioclub.ru/index.php?page=book&id=83542).

Колокольникова А. И. Информатика : учебное пособие. 2-е

изд. Москва; Берлин: Директ-Медиа, 2020. – URL:

https://biblioclub.ru/index.php?page=book&id=596690.

Прохорова О. В. Информатика. Учебник. Самара, 2013.

(http://biblioclub.ru/index.php?page=book_red&id=256147).

2

3. Список литературы

Степанов А. Н. Информатика. Учебник для вузов. 6-е изд.СПб.: Питер, 2010.

Тушко Т. А., Пестунова Т. М. Информатика. Учебное

пособие. – Красноярск: Сиб. федер. ун-т, 2017. – URL:

http://biblioclub.ru/index.php?page=book_red&id=497738.

Платонов Ю. М., Уткин Ю. Г., Иванов М. И. Информатика.

Учебное пособие. М.: Альтаир-МГАВТ, 2014. – URL:

http://biblioclub.ru/index.php?page=book_red&id= 429784.

Питухин Е. А., Зятева О. А. Основы информатики. Курс

лекций. Петрозаводск: Изд-во ПетрГУ, 2012. – URL:

http://elibrary.karelia.ru/docs/pituhin/osn_inf/total.pdf.

3

4. § 1 Типы структур ВМ и ВС

Слово «информатика» происходит от французскогослова «informatique», которое образовано из двух

слов: information – информация и automatique –

автоматика (англ. computer science).

Информатика – это комплексная техническая наука,

которая изучает и систематизирует приемы создания,

хранения, представления, обработки и передачи

данных средствами вычислительной техники, а также

принципы функционирования этих средств и методы

управления ими.

4

5. Вычислительная машина и вычислительная система

Вычислительная машина (ВМ) - это совокупностьтехнических средств, создающая возможность

проведения обработки информации (данных) и

получение результата в необходимой форме. Под

техническими средствами понимают все оборудование, предназначенное для автоматизированной

обработки данных. Как правило, в состав ВМ входит

и системное программное обеспечение.

Вычислительная система (ВС) - это одна или

несколько вычислительных машин, периферийное

оборудование и программное обеспечение, которые

выполняют обработку данных.

5

6. Архитектура вычислительной машины

Впервые термин «архитектура вычислительноймашины» (computer architecture) был употреблен

фирмой IBM при разработке машин семейства IBM

360 для описания тех средств, которыми может

пользоваться программист, составляя программу на

уровне машинных команд.

Подобную трактовку называют «узкой», так как

охватывает она лишь часть вопросов, описывающих

функциональные возможности: перечень и формат

команд, формы представления данных, механизмы

ввода/вывода, способы адресации памяти и т. п.

6

7. Архитектура вычислительной машины

В государственном стандарте 15971-90 подархитектурой вычислительной машины понимается

концептуальная структура ВМ, определяющая

проведение обработки информации и включающая

методы преобразования информации в данные и

принципы взаимодействия технических средств и

программного обеспечения.

Международный стандарт ISO/IEC 2382/1-93 дает

такое же определение, используя следующую

формулировку: это логическая структура и

функциональные характеристики ВМ, включая

взаимосвязи между ее аппаратными и программными

компонентами.

7

8. Уровни детализации вычислительной машины

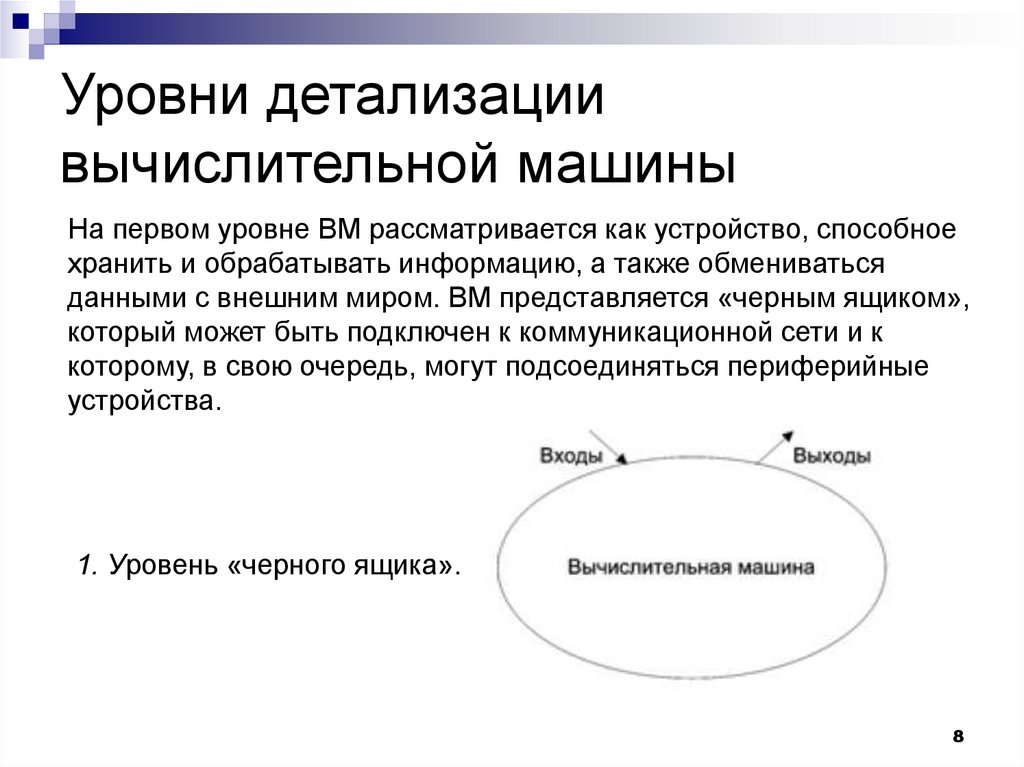

На первом уровне ВМ рассматривается как устройство, способноехранить и обрабатывать информацию, а также обмениваться

данными с внешним миром. ВМ представляется «черным ящиком»,

который может быть подключен к коммуникационной сети и к

которому, в свою очередь, могут подсоединяться периферийные

устройства.

1. Уровень «черного ящика».

8

9. Уровень общей архитектуры

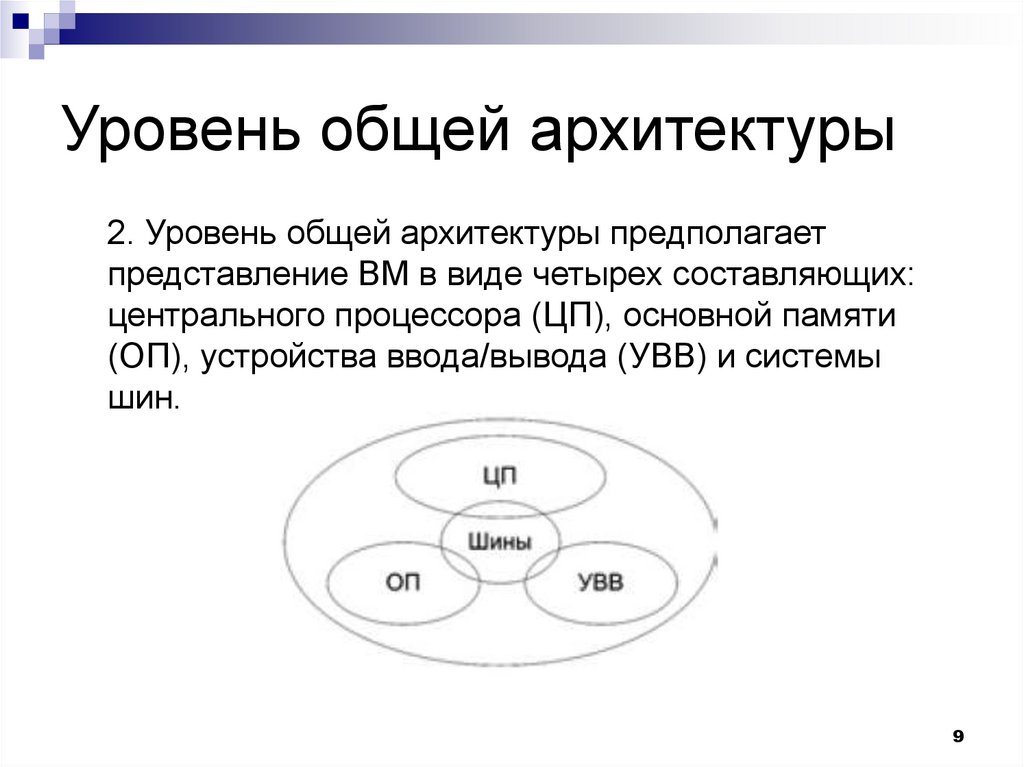

2. Уровень общей архитектуры предполагаетпредставление ВМ в виде четырех составляющих:

центрального процессора (ЦП), основной памяти

(ОП), устройства ввода/вывода (УВВ) и системы

шин.

9

10. Уровень архитектуры центрального процессора

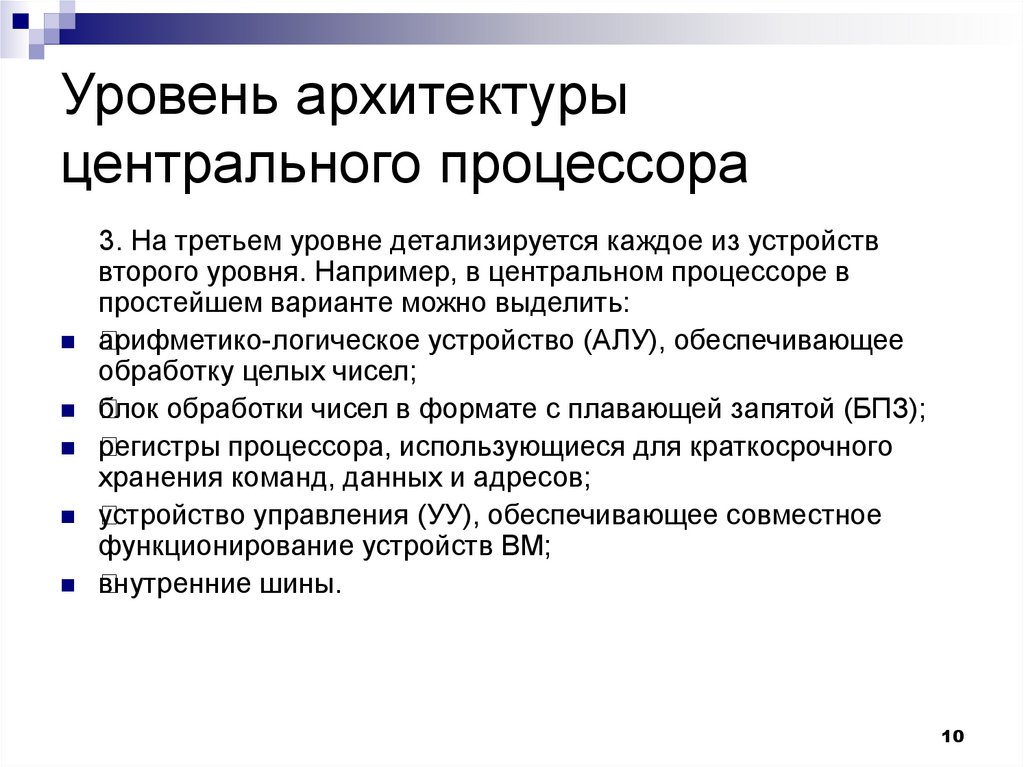

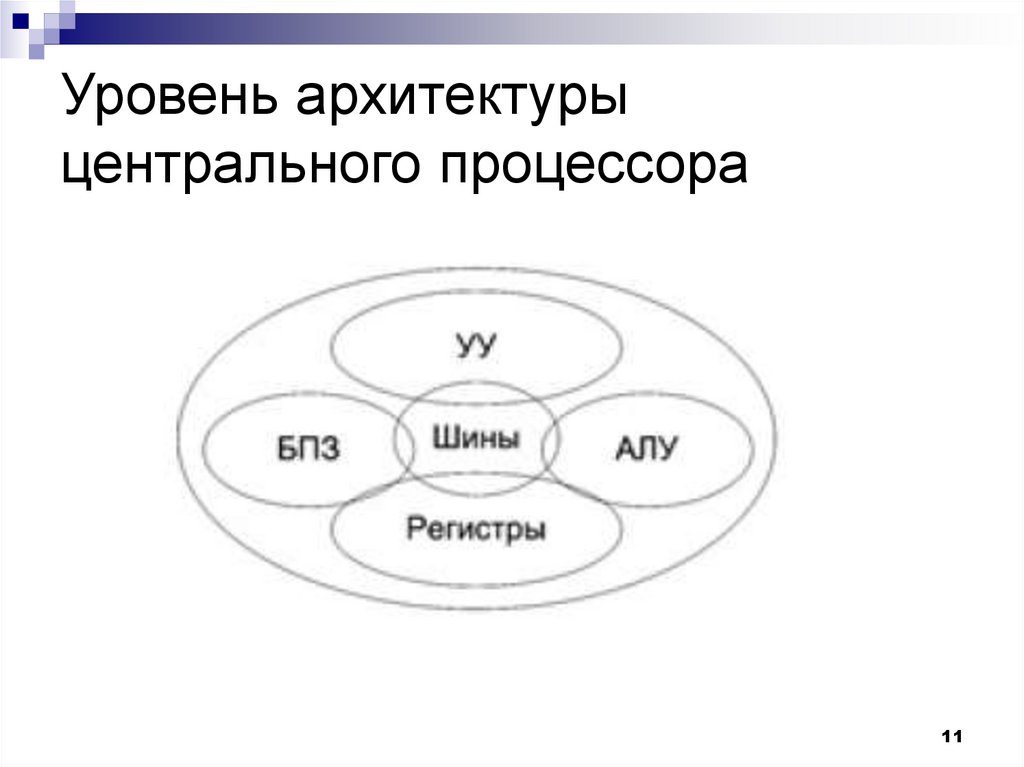

3. На третьем уровне детализируется каждое из устройстввторого уровня. Например, в центральном процессоре в

простейшем варианте можно выделить:

арифметико-логическое устройство (АЛУ), обеспечивающее

обработку целых чисел;

блок обработки чисел в формате с плавающей запятой (БПЗ);

регистры процессора, использующиеся для краткосрочного

хранения команд, данных и адресов;

устройство управления (УУ), обеспечивающее совместное

функционирование устройств ВМ;

внутренние шины.

10

11. Уровень архитектуры центрального процессора

1112. Уровень архитектуры устройства управления

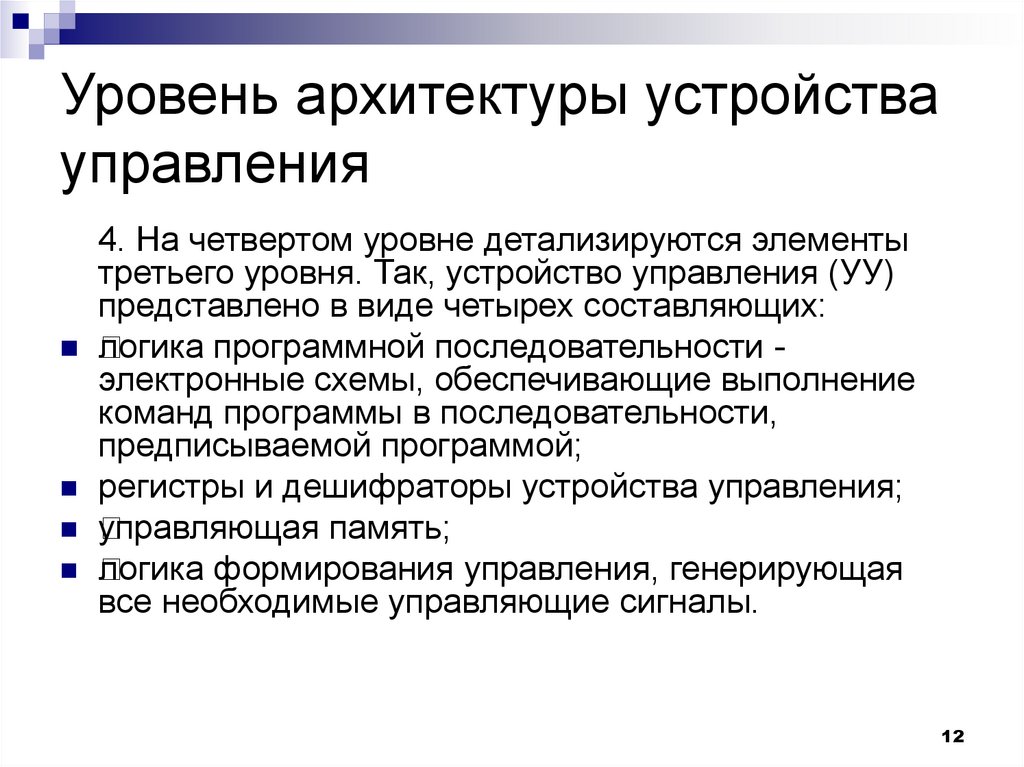

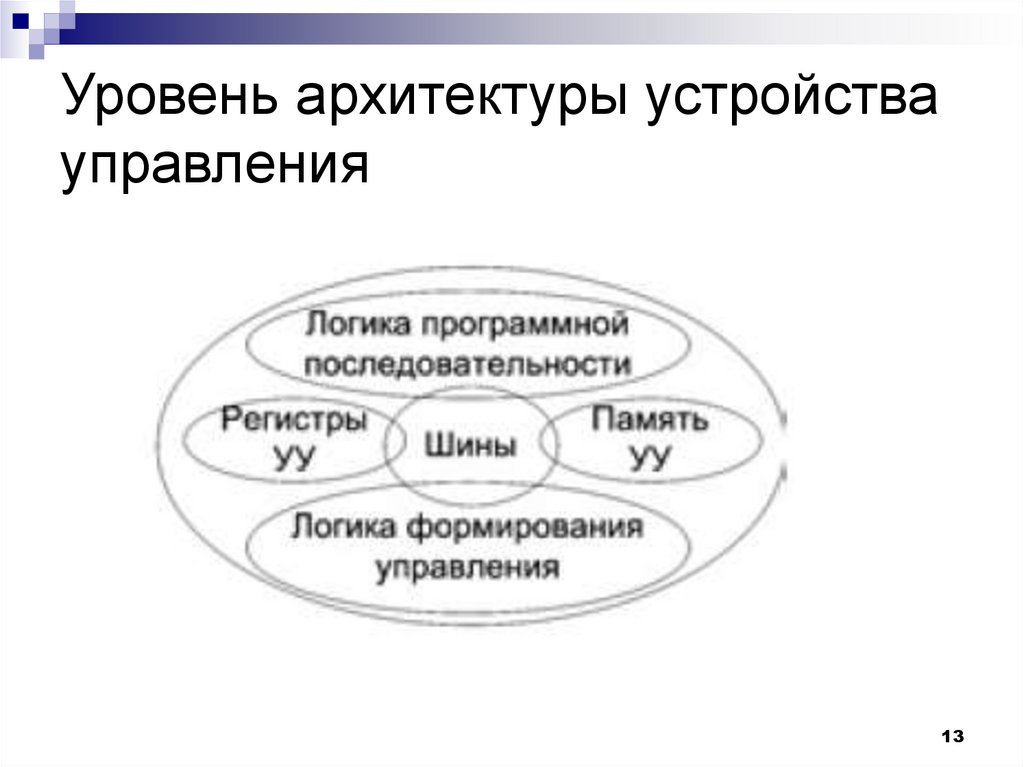

4. На четвертом уровне детализируются элементытретьего уровня. Так, устройство управления (УУ)

представлено в виде четырех составляющих:

логика программной последовательности электронные схемы, обеспечивающие выполнение

команд программы в последовательности,

предписываемой программой;

регистры и дешифраторы устройства управления;

управляющая память;

логика формирования управления, генерирующая

все необходимые управляющие сигналы.

12

13. Уровень архитектуры устройства управления

1314. Типы структур ВМ и ВС

Достоинства и недостатки архитектуры вычислительных машин и систем изначально зависят от способасоединения компонентов. При самом общем подходе

можно говорить о 2-х основных типах структур

вычислительных машин и 2-х типах структур

вычислительных систем.

В настоящее время примерно одинаковое распространение получили два способа построения ВМ:

а) ВМ с непосредственными связями.

б) Структура ВМ на базе общей шины.

14

15. ВМ с непосредственными связями

Типичным представителем первого способа можетслужить классическая фон-неймановская ВМ.

В ней между взаимодействующими устройствами

(процессор, память, устройство ввода/вывода) имеются

непосредственные связи. Особенности связей (число

линий в шинах, пропускная способность и т. п.)

определяются видом информации, характером и

интенсивностью обмена.

15

16. Фон-неймановская ВМ

ВМ, где определенным образом закодированные командыпрограммы хранятся в памяти, известна под названием

вычислительной машины с хранимой в памяти

программой. Идея принадлежит создателям вычислителя

ENIAC (Electronic Numerical Integrator and Computer)

Эккерту, Мочли и фон Нейману.

Относительно авторства существует несколько версий, но

поскольку в законченном виде идея впервые была

изложена в 1945 году в статье фон Неймана, именно его

фамилия фигурирует в обозначении архитектуры

подобных машин, составляющих подавляющую часть

современного парка ВМ и ВС.

16

17. 4 принципа фон Неймана

Сущность фон-неймановской концепциивычислительной машины можно свести к

четырем принципам:

1) Двоичное кодирование;

2) Программное управление;

3) Однородность памяти;

4) Адресуемость памяти.

17

18. 1. Двоичное кодирование

Вся информация (и данные, и команды), кодируетсядвоичными цифрами 0 и 1. В формате числа обычно

выделяют поле знака и поле значащих разрядов. В

формате команды можно выделить два поля: поле кода

операции (КОП) и поле адресов (адресную часть - АЧ).

В командах преобразования данных АЧ содержит адреса

объектов обработки (операндов) и результата; в командах

изменения порядка вычислений - адрес следующей

команды программы; в командах ввода/вывода - номер

устройства ввода/вывода.

18

19. 2. Программное управление

Все вычисления, предусмотренные алгоритмомрешения задачи, представлены в виде программы,

состоящей из последовательности управляющих слов команд. Каждая команда предписывает некоторую

операцию из набора операций, реализуемых

вычислительной машиной.

Команды программы хранятся в последовательности

смежных ячеек памяти ВМ и выполняются в

естественном порядке, т. е. в порядке их

расположения в программе. При необходимости, с

помощью специальных команд, естественный порядок

выполнения может быть изменен.

19

20. 3. Однородность памяти

Команды и данные хранятся в одной и той же памяти ивнешне неразличимы. Это позволяет производить над

командами те же операции, что и над числами, и,

соответственно, открывает ряд возможностей. Так,

циклически изменяя адресную часть команды, можно

обеспечить обращение к последовательности смежных

элементов массива данных (модификация команд).

Более полезно бывает, когда команды одной программы

могут быть получены как результат исполнения другой

программы. Эта возможность лежит в основе трансляции перевода текста программы с языка высокого уровня на

машинный язык).

20

21. 4. Адресуемость памяти

Структурно основная память состоит изпронумерованных ячеек, причем процессору в

произвольный момент доступна любая ячейка.

Двоичные коды команд и данных разделяются на

единицы информации, называемые словами, и

хранятся в ячейках памяти, а для доступа к ним

используются номера соответствующих ячеек —

адреса.

21

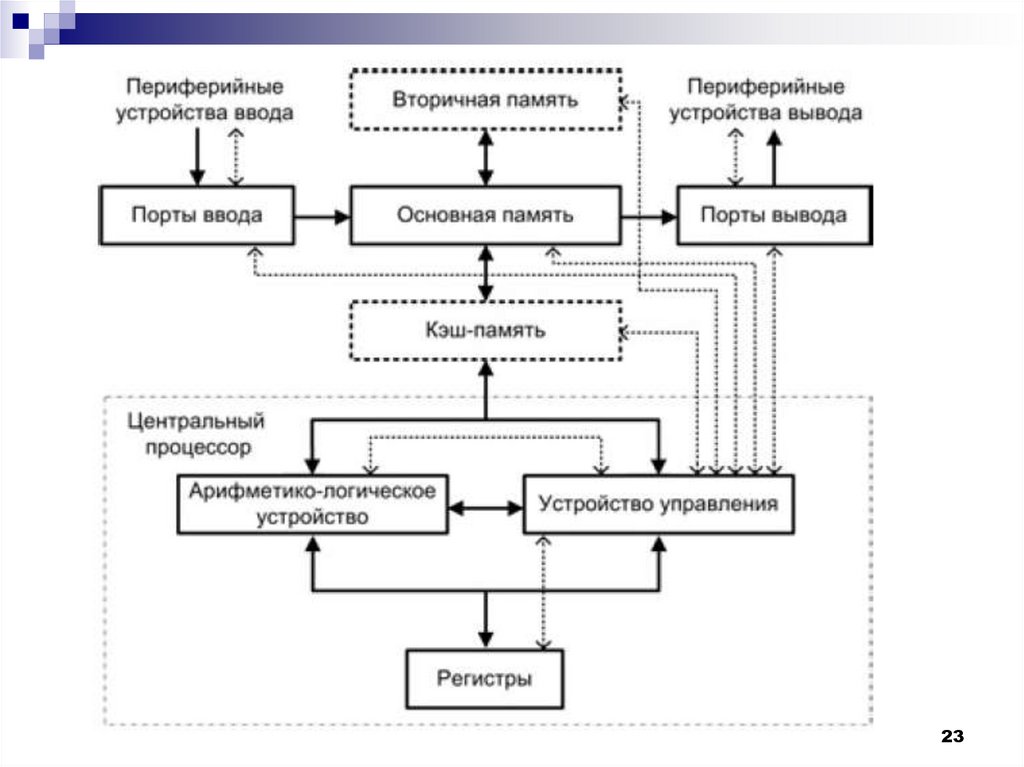

22. Структура фон-неймановской вычислительной машины

В статье фон Неймана определены основныеустройства ВМ, с помощью которых должны быть

реализованы вышеперечисленные принципы.

Большинство современных ВМ по своей структуре

отвечают принципу программного управления.

Типичная фон-неймановская ВМ содержит: память,

устройство управления, арифметико-логическое

устройство и устройство ввода/вывода (см. рисунок)

22

23.

2324. Устройство ввода/вывода

Информация поступает из подсоединенных к ВМпериферийных устройств (ПУ) ввода. Результаты

вычислений выводятся на периферийные устройства

вывода. Связь и взаимодействие ВМ и ПУ

обеспечивают порты ввода и порты вывода.

Термином порт обозначают аппаратуру сопряжения

периферийного устройства с ВМ и управления им.

Совокупность портов ввода и вывода называют

устройством ввода/вывода (УВВ) или модулем

ввода/вывода вычислительной машины (МВВ).

24

25. Основная память

Введенная информация сначала запоминается в основнойпамяти, а затем переносится во вторичную память, для

длительного хранения. Чтобы программа могла

выполняться, команды и данные должны располагаться в

основной памяти (ОП), организованной таким образом,

что каждое двоичное слово хранится в отдельной ячейке,

идентифицируемой адресом, причем соседние ячейки

памяти имеют следующие по порядку адреса.

Показанные на рисунке кэш-память и вторичная память в

состав типичной фон-неймановской ВМ не входят

(являются ее расширением).

25

26. ОЗУ и ПЗУ

Доступ к любым ячейкам основной памяти можетпроизводиться в произвольном порядке. Такой вид памяти

известен как память с произвольным доступом.

ОП современных ВМ в основном состоит из

полупроводниковых оперативных запоминающих

устройств (ОЗУ), обеспечивающих считывание и запись

информации. Для ОЗУ характерна энергозависимость хранимая информация теряется при отключении

электропитания. Если необходимо, чтобы часть основной

памяти была энергонезависимой, в состав ОП включают

постоянные запоминающие устройства (ПЗУ), также

обеспечивающие произвольный доступ. Хранящаяся в

ПЗУ информация может только считываться.

26

27. Кэш-память

Неотъемлемой частью современных ВМ стала кэшпамять (от английского слова cache - убежище,тайник), - память небольшой емкости, но высокого

быстродействия. В нее из основной памяти

копируются наиболее часто используемые команды и

данные.

При обращении со стороны процессора информация

берется не из основной памяти, а из

соответствующей копии, находящейся в более

быстродействующей кэш-памяти.

27

28. Кэш-память

Когда ЦП пытается прочитать слово из основнойпамяти, сначала осуществляется поиск копии этого

слова в КП. Если такая копия существует, обращение к

ОП не производится, а в ЦП передается слово,

извлеченное из кэш-памяти. Данную ситуацию принято

называть успешным обращением или попаданием (hit).

При отсутствии слова в кэш-памяти, то есть при

неуспешном обращении (промахе - miss), блок данных,

содержащий это слово, сначала пересылается из ОП в

кэш-память, а затем уже из КП затребованное слово

передается в ЦП.

28

29. Кэш-память

2930. Кэш-память

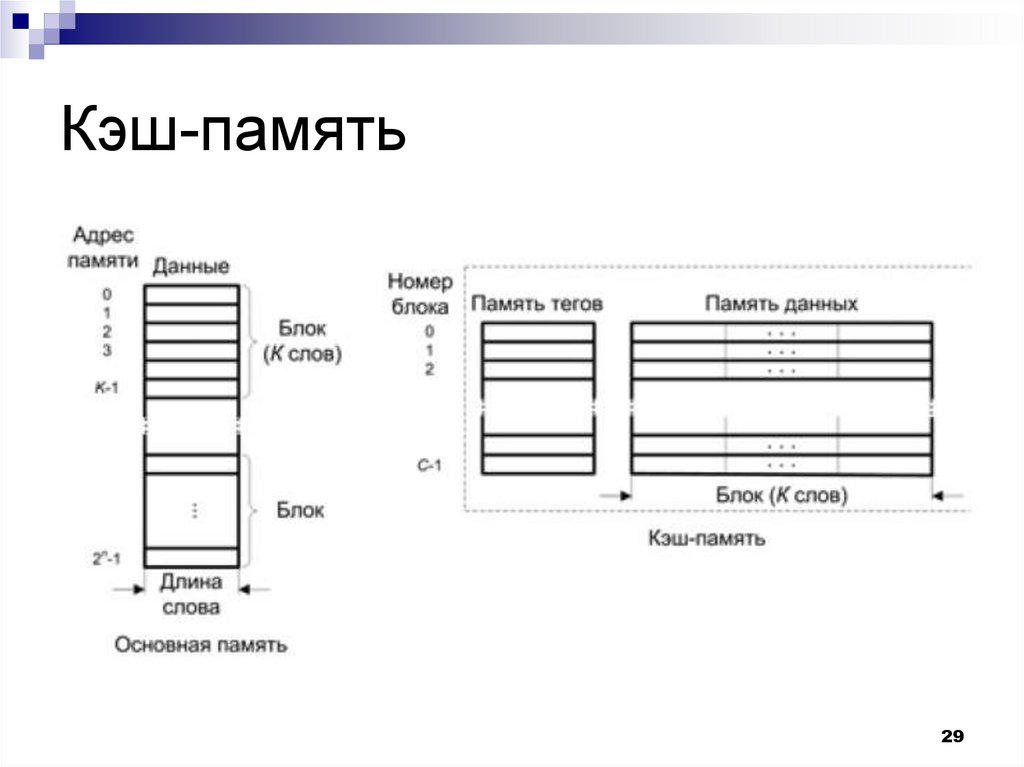

ОП при взаимодействии с кэш-памятью рассматривается как состоящее из M блоков фиксированнойдлины по K слов в каждом. Кэш-память также условно

разбивается на C блоков аналогичного размера, причем

С << M. При обращении к какой-либо ячейке ОП блок,

содержащий данную ячейку, копируется в какой-то из

блоков кэш-памяти, и все последующие обраще-ния к

блоку переадресовываются на его копию в КП.

Каждую копию необходимо снабдить так называемым

тегом (признаком), указывающим на то, копия какого

блока ОП в настоящий момент хранится в данном

блоке КП.

30

31. Регистры ЦП

Четвертый вид памяти - это регистры центральногопроцессора. Каждый регистр можно рассматривать как

одну ячейку памяти, обращение к которой занимает

значительно меньше времени даже по сравнению с

быстродействующей кэш-памятью.

Число регистров в ВМ обычно невелико, и они

образуют небольшую память, иногда называемую

сверхоперативной памятью или регистровым файлом.

В них обычно помещают часто используемые

константы или промежуточные результаты вычислений,

что позволяет сократить число обращений к медленным

видам памяти.

31

32. Устройство управления

Устройство управления (УУ) - важнейшая частьвычислительной машины, организующая

автоматическое выполнение программ (путем

реализации функций управления) и обеспечивающая

функционирование ВМ как единой системы.

Пересылка информации между любыми элементами

ВМ инициируется своим сигналом управления (СУ).

Основной функцией УУ является формирование

управляющих сигналов, отвечающих за извлечение

команд из памяти в порядке, определяемом

программой, и последующее исполнение этих команд.

Кроме того, УУ формирует СУ для синхронизации и

координации внутренних и внешних устройств ВМ.

32

33. Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ)обеспечивает арифметическую и логическую обработку

двух входных переменных (операндов), в итоге которой

формируется выходная переменная (результат). Функции

АЛУ обычно сводятся к простым арифметическим и

логическим операциям, а также операциям сдвига.

Помимо результата операции, АЛУ формирует ряд

признаков результата (флагов), характеризующих

полученный результат и события, произошедшие в ходе

его получения (равенство нулю, знак, четность, перенос,

переполнение и т. д.). Флаги могут анализироваться в УУ с

целью принятия решения о дальнейшем порядке

следования команд программы.

33

34. Структура ВМ на базе общей шины

Все устройства подключены к магистральной общейшине, служащей единственным трактом для потоков

команд, данных и сигналов управления. Наличие

общей шины существенно упрощает реализацию ВМ,

позволяет легко менять состав и конфигурацию

машины.

Недостаток архитектуры: в каждый момент передавать

информацию по шине может только одно устройство.

Основную нагрузку на шину создают обмены между

процессором и памятью, связанные с извлечением из

памяти команд и данных и записью в память

результатов вычислений.

34

35. Структура ВМ на базе общей шины

3536. Структура ВМ на базе общей шины

Более распространена архитектура с иерархиейшин, где помимо магистральной шины имеется еще

несколько дополнительных шин. Они могут

обеспечивать непосредственную связь между

устройствами с наиболее интенсивным обменом,

например процессором и кэш-памятью.

Другой вариант использования дополнительных шин

- объединение однотипных устройств ввода/вывода с

последующим выходом с дополнительной шины на

магистральную. Все эти меры позволяют снизить

нагрузку на общую шину и более эффективно

расходовать ее пропускную способность.

36

37. Структуры вычислительных систем

Понятие «вычислительная система» предполагаетналичие множества процессоров или законченных

вычислительных машин, при объединении которых

используется один из двух подходов:

1) Вычислительные системы с общей памятью

2) Распределенная система

37

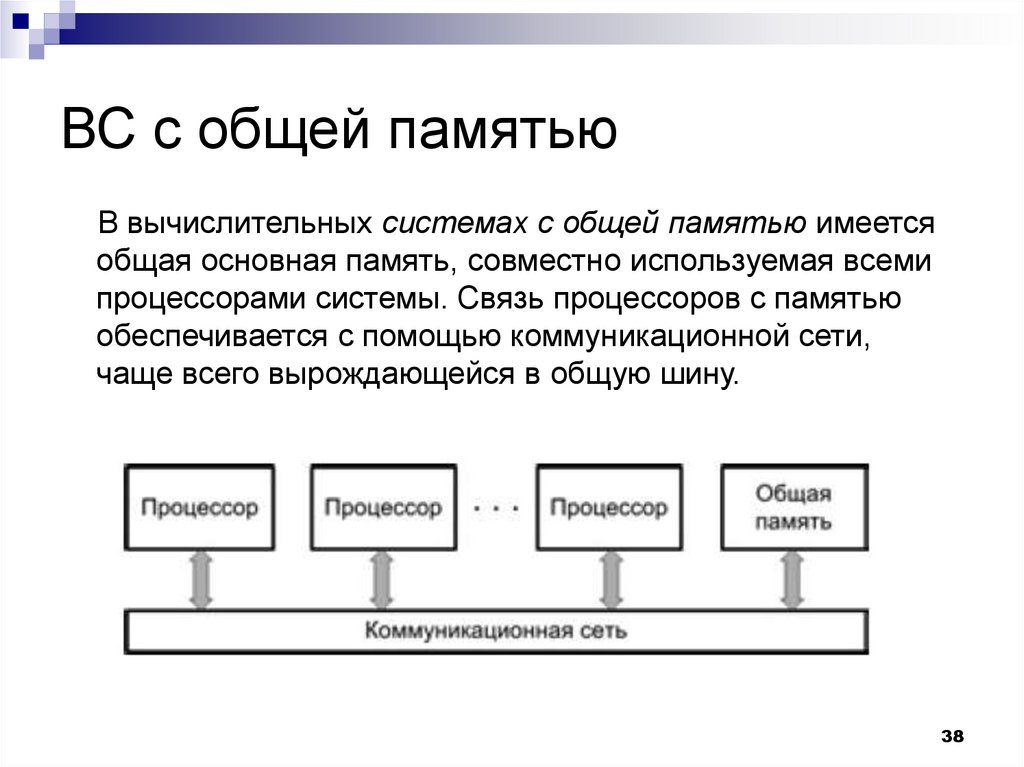

38. ВС с общей памятью

В вычислительных системах с общей памятью имеетсяобщая основная память, совместно используемая всеми

процессорами системы. Связь процессоров с памятью

обеспечивается с помощью коммуникационной сети,

чаще всего вырождающейся в общую шину.

38

39. ВС с общей памятью

Таким образом, структура ВС с общей памятьюаналогична рассмотренной выше архитектуре с

общей шиной, в силу чего ей свойственны те же

недостатки.

Применительно к вычислительным системам

данная схема имеет дополнительное достоинство:

обмен информацией между процессорами не

связан с дополнительными операциями и

обеспечивается за счет доступа к общим областям

памяти.

39

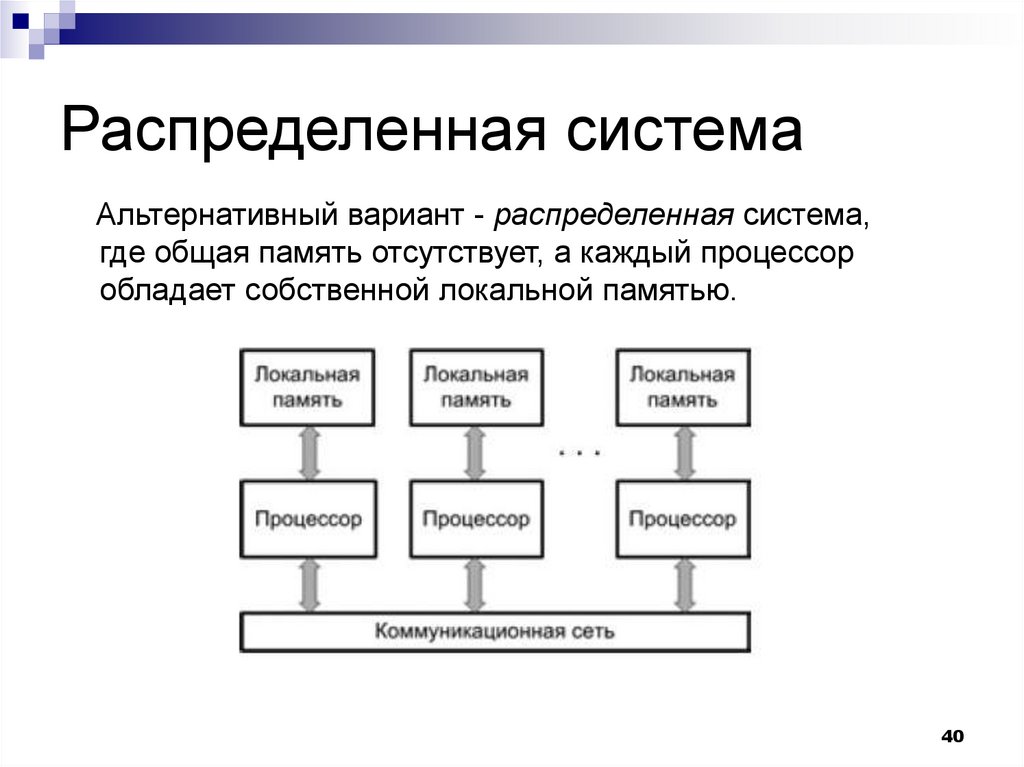

40. Распределенная система

Альтернативный вариант - распределенная система,где общая память отсутствует, а каждый процессор

обладает собственной локальной памятью.

40

41. Распределенная система

Часто такие системы объединяют отдельные ВМ.Обмен информацией между составляющими

системы обеспечивается с помощью

коммуникационной сети посредством обмена

сообщениями.

Подобное построение ВС снимает ограничения,

свойственные для общей шины, но приводит к

дополнительным издержкам на пересылку

сообщений между процессорами или машинами.

41

42. Перспективы совершенствования архитектуры ВМ и ВС

Эволюцию архитектур определяют самые различныефакторы, главные из которых показаны на рисунке.

На современном уровне вычислительной техники

подавляющее большинство устройств ВМ и ВС

реализуется на базе полупроводниковых технологий в

виде сверхбольших интегральных микросхем (СБИС).

Пока основные успехи связаны с уменьшением

размеров элементарных транзисторов и плотности их

размещения на кристалле.

42

43. Перспективы совершенствования архитектуры ВМ и ВС

4344. Закон Мура

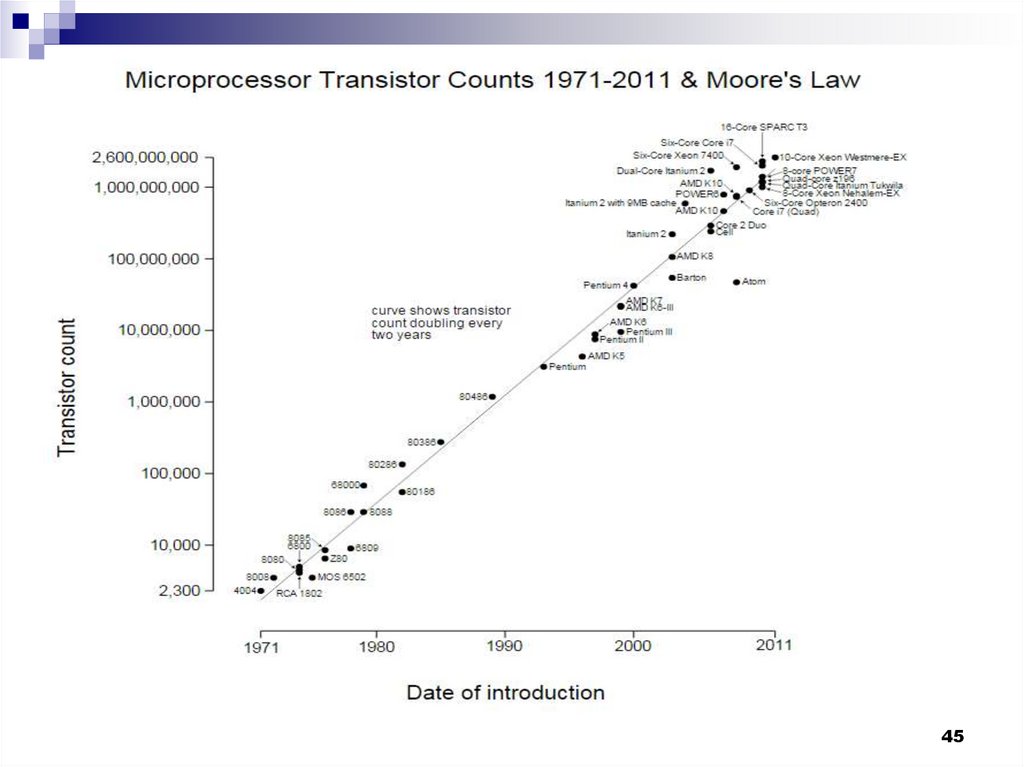

Тенденции эволюции СБИС хорошо описываютсяэмпирическим законом Мура. В 1965 году Мур заметил,

что число транзисторов, которое удается разместить на

кристалле микросхемы, удваивается каждые 12

месяцев. Он предсказал, что эта тенденция сохранится

в 70-е годы, а начиная с 80-х темп роста начнет

спадать.

В 1995 году Мур уточнил свое предсказание, сделав

прогноз, что удвоение числа транзисторов далее будет

происходить каждые 24 месяца.

44

45.

4546. Закон Мура

Современные технологии производствасверхбольших интегральных микросхем позволяют

разместить на одном кристалле логические схемы

всех компонентов процессора.

В настоящее время процессоры всех

вычислительных машин реализуются в виде одной

или нескольких СБИС. Более того, во многих

многопроцессорных ВС используются СБИС, где на

одном кристалле располагаются сразу несколько

процессоров (обычно не очень сложных).

46

47. Емкость и быстродействие памяти

Для СБИС памяти также подтверждаетсясправедливость закона Мура: в целом число

запоминающих элементов на кристалле будет

возрастать в два раза каждые полтора года.

С быстродействием СБИС памяти дело обстоит хуже.

Общая тенденция: на двукратное уменьшение

длительности цикла динамического ЗУ уходит

примерно 15 лет. В плане снижения стоимости СБИС

памяти перспективы весьма обнадеживающие. В

течение длительного времени стоимость в пересчете

на один бит снижается примерно на 25–40 % в год.

47

Информатика

Информатика