Похожие презентации:

Назначение и структура процессора

1. Назначение и структура процессора

2.

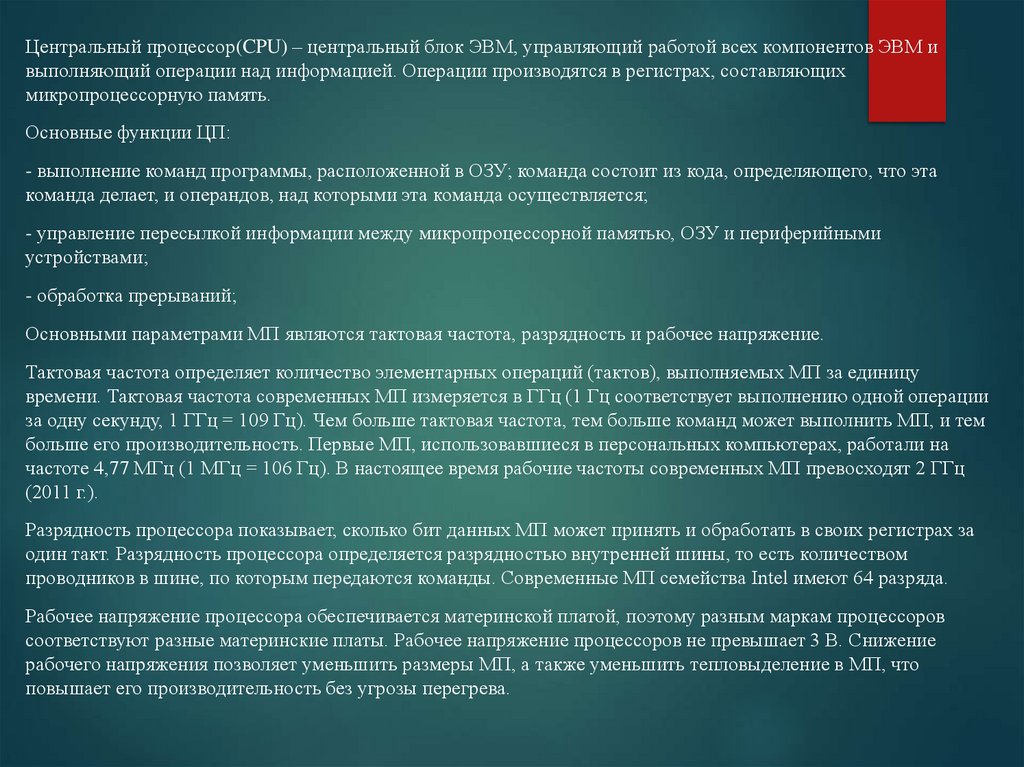

Центральный процессор(CPU) – центральный блок ЭВМ, управляющий работой всех компонентов ЭВМ ивыполняющий операции над информацией. Операции производятся в регистрах, составляющих

микропроцессорную память.

Основные функции ЦП:

- выполнение команд программы, расположенной в ОЗУ; команда состоит из кода, определяющего, что эта

команда делает, и операндов, над которыми эта команда осуществляется;

- управление пересылкой информации между микропроцессорной памятью, ОЗУ и периферийными

устройствами;

- обработка прерываний;

Основными параметрами МП являются тактовая частота, разрядность и рабочее напряжение.

Тактовая частота определяет количество элементарных операций (тактов), выполняемых МП за единицу

времени. Тактовая частота современных МП измеряется в ГГц (1 Гц соответствует выполнению одной операции

за одну секунду, 1 ГГц = 109 Гц). Чем больше тактовая частота, тем больше команд может выполнить МП, и тем

больше его производительность. Первые МП, использовавшиеся в персональных компьютерах, работали на

частоте 4,77 МГц (1 МГц = 106 Гц). В настоящее время рабочие частоты современных МП превосходят 2 ГГц

(2011 г.).

Разрядность процессора показывает, сколько бит данных МП может принять и обработать в своих регистрах за

один такт. Разрядность процессора определяется разрядностью внутренней шины, то есть количеством

проводников в шине, по которым передаются команды. Современные МП семейства Intel имеют 64 разряда.

Рабочее напряжение процессора обеспечивается материнской платой, поэтому разным маркам процессоров

соответствуют разные материнские платы. Рабочее напряжение процессоров не превышает 3 В. Снижение

рабочего напряжения позволяет уменьшить размеры МП, а также уменьшить тепловыделение в МП, что

повышает его производительность без угрозы перегрева.

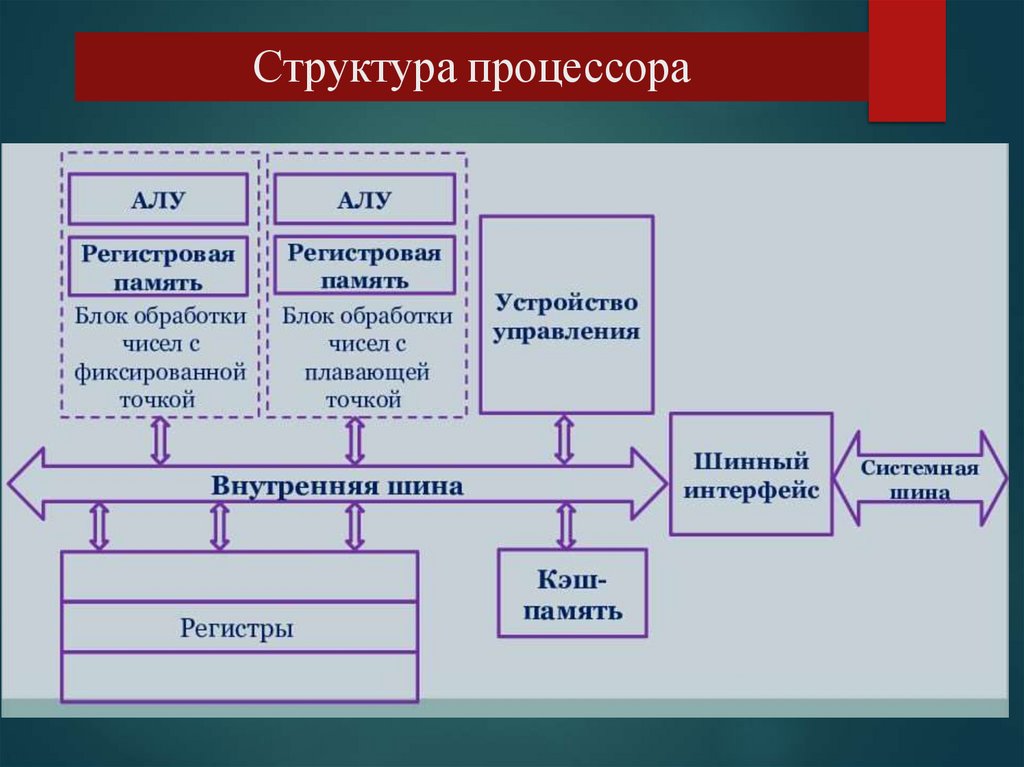

3. Структура процессора

4. Структура процессора

АЛУ – арифметико-логическое устройство - выполняет все арифметические (сложение, вычитание, умножение,деление) и логические (конъюнкция, дизъюнкция и др.) операции над целыми двоичными числами и символьной

информацией.

ДБ – другие блоки (математический сопроцессор, модуль предсказания ветвлений);

ИМП – интерфейс микропроцессора - предназначен для связи и согласования МП с системной шиной ЭВМ.

Принятые команды и данные временно помещаются в кэш-память второго уровня. Размер кэш-памяти второго

уровня – 256-2048 Кбайт.

УС – устройство синхронизации - определяет дискретные интервалы времени – такты работы МП между

выборками очередной команды. Частота, с которой осуществляется выборка команд, называется тактовой

частотой.

УУ – устройство управления - выполняет команды, поступающие в МП в следующей последовательности:

1) выборка из регистра-счетчика адреса ячейки ОЗУ, где хранится очередная команда программы;

2) выборка из ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд;

3) расшифровка кода команды дешифратором команды (ДК);

4) формирование полных адресов операндов;

5) выборка операндов из ОЗУ или МПП и выполнение заданной команды обработки этих операндов;

6) запись результатов команды в память;

7) формирование адреса следующей команды программы.

5.

Устройство управления (УУ) управляет работой АЛУ путем выработки последовательности микрокоманд,необходимых для выполнения той или иной операции (+, -, /, * и т.д.).

Порядок выполнения микрокоманд определен микропрограммой реализации операции, но может изменяться в

зависимости от признаков операции, вырабатываемых в АЛУ (P1,...,Pm) и подаваемых на вход УУ.

Микропрограммы могут иметь как линейную структуру, так и быть разветвленными.

Технические реализации УУ даже простейших процессоров разнообразны. Однако в самом общем случае их

различают по способу хранения микропрограмм.

По этому критерию УУ подразделяются на:

- УУ с жесткой (схемной) логикой

- УУ с хранимой в специальной памяти микропрограммой.

Если микропроцессорная память доступна программисту, то УУ являются микропрограммируемыми и позволяют

изменить систему команд процессора.

Если микропрограммная память не доступна, то процессор имеет неизменную систему команд, как и в случае УУ с

жесткой логикой.

УУ современных процессоров во многих случаях комбинированные.

Выполнением простых команд управляет быстродействующее УУ на жесткой логике, а выполнением сложных

команд – более медленное УУ с микропрограммной памятью.

УУ, построенные на жесткой логике, исторически появились первыми.

Основным преимуществом таких УУ является их быстродействие.

Системы команд таких процессоров всегда фиксированные и не могут быть изменены пользователем. Подобные УУ

иногда называют специализированными. Специализированные УУ формируют неизменные последовательности

сигналов управления (СУ).

6.

Основные регистры можно разделить на 4 группы:1.Регистры общего назначения: AX, BX, CX, DX. Можно работать с регистром целиком

или отдельно с каждой его половинкой: регистром старшего (high) байта – AH, BH, и

регистром младшего (low) байта – AL, BL, CL, DL.

2. Сегментные регистры -используются для хранения начальных адресов полей памяти

(сегментов), отведенных в программах для хранения команд кода (регистр CS), данных

(DS), стека (SS), дополнительной области памяти данных при обмене между сегментами

(ES).

3. Регистры смещений IP, SP, ВР, SI, DI предназначены для хранения относительных

адресов ячеек памяти внутри сегментов (смещений относительно начала сегментов).

4. Регистр флагов - FL содержит одноразрядные флаги, управляющие выполнением

программы в ЭВМ. Флаги принимают значения 0 или 1. Значения флагов

устанавливаются независимо друг от друга. Всего в регистре 9 флагов: 6 – статусные,

отражающие результаты операций (флаги переноса, нуля, переполнения и др.); 3 –

управляющие, определяющие режим выполнения программы (флаги пошагового

выполнения программы, прерываний и направления обработки данных).

7.

Дешифратор команд(ДК) - анализирует команды в целях выделенияоперандов и адресов, по которым размещаются результаты. Затем следует

сообщение другому независимому устройству о том, что необходимо

сделать для выполнения инструкции.

Кэш L1 – кэш-память первого уровня – в ней временно хранятся команды,

поступающие в УУ, освобождая шину для выполнения других операций.

Размер кэш-памяти первого уровня 8-32 Кбайт.

Кэш L2 – кэш-память второго уровня - также находится внутри процессора.

Информация, хранящаяся в ней, используется реже, чем информация,

хранящаяся в кэш-памяти первого уровня, но зато по объёму памяти он

больше.

МПП – микропроцессорная память - включает 14 основных двухбайтовых

запоминающих регистров и множество (до 256) дополнительных регистров.

Регистры – это быстродействующие ячейки памяти различного размера.

8. АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

9.

АЛУ – одна из основных функциональных частей процессора, осуществляющая непосредственноепреобразование информации.

Все операции, выполняемые в АЛУ, можно разделить на следующие группы:

операции двоичной арифметики для чисел с фиксированной точкой;

операции двоичной (шестнадцатеричной) арифметики для чисел с плавающей точкой;

операции десятичной арифметики над числами, представленными в двоично-десятичном коде;

операции адресной арифметики (при модификации адресов команд);

операции специальной арифметики (нормализация, сдвиг);

логические операции;

операции над алфавитно-цифровыми полями.

Для выполнения перечисленных операций в АЛУ включают следующие функциональные узлы:

сумматор (для выполнения суммирования и других действий над кодами операндов);

регистры (для хранения кодов операндов на время выполнения действия над ними);

сдвигатели (для сдвига кода на один или несколько разрядов вправо или влево);

преобразователи (для преобразования прямого кода числа в обратный или дополнительный);

комбинационные схемы (для реализации логических операций, мультиплексирования данных, управляемой

передачи информации, формирования признаков результата).

Регистры и в некоторых случаях сумматоры имеют цепи управления приемом, выдачей и сбросом кодов

операндов. Логические операции, операции сдвига и преобразования кодов могут выполняться не только

специальными устройствами, но и с помощью дополнительных связей регистров и сумматора.

10.

Обобщенная структурная схема АЛУ включает:- блок регистров для приема и размещения операндов и результатов;

- операционный блок, в котором осуществляется преобразование операндов в

соответствии с реализуемыми алгоритмами;

- схемы контроля, обеспечивающие

диагностирование ошибок;

непрерывный

оперативный

контроль

и

- блок управления (БУ), в котором после приема кода операции (КОП) из центрального

устройства управления формируются управляющие сигналы (УС), координирующие

взаимодействие всех узлов АЛУ между собой и с другими блоками процессора.

Блок регистров связан с РОН центрального процессора и кэш-памятью данных.

Иногда АЛУ не содержит своего БР, в этом случае операционный блок

непосредственно работает с регистрами общего назначения процессора. Для

оперативного управления выполнением операции в ОБ на разных этапах анализируется

преобразуемая информация и формируются сигналы признаков (флаги), которые

используются в БУ для выработки и посылки в процессор сигнала признака результата

(ПРез).

Для оценки АЛУ используются следующие характеристики: множество выполняемых

операций, разрядность, время выполнения операций, надежностные и энергетические

характеристики.

11. Структура АЛУ

12. Сумматоры АЛУ

Сумматоры АЛУ делятся:по

типу использования для суммирования базовых элементов (комбинационные и

накапливающие);

по способу осуществления операции суммирования (последовательные и параллельные).

Сумматоры последовательного действия выполняются, как правило, на комбинационных

элементах; на сегодняшний день устройства такого типа почти не применяются. В АЛУ

современных ЭВМ средней и высокой производительности применяются сумматоры

параллельного действия, выполняемые на накапливающих или комбинационных

элементах.

В качестве накапливающих элементов могут служить обычные T-триггеры. Перед

суммированием триггеры сумматора устанавливаются в нулевое состояние сигналом

сброс. Затем на счетные входы триггеров подается первое слагаемое и запоминается. В

следующем такте на входы триггеров подается второе слагаемое.

Триггеры тех разрядов, в которых второе слагаемое равно 1, меняют свое состояние на

противоположное. В тех разрядах, в которых триггеры перешли из единичного состояния в

нулевое, возникают сигналы переносов, последовательно передаваемые в старшие разряды

сумматора. Арифметические операции сумматора выполняются с учетом знаков операндов.

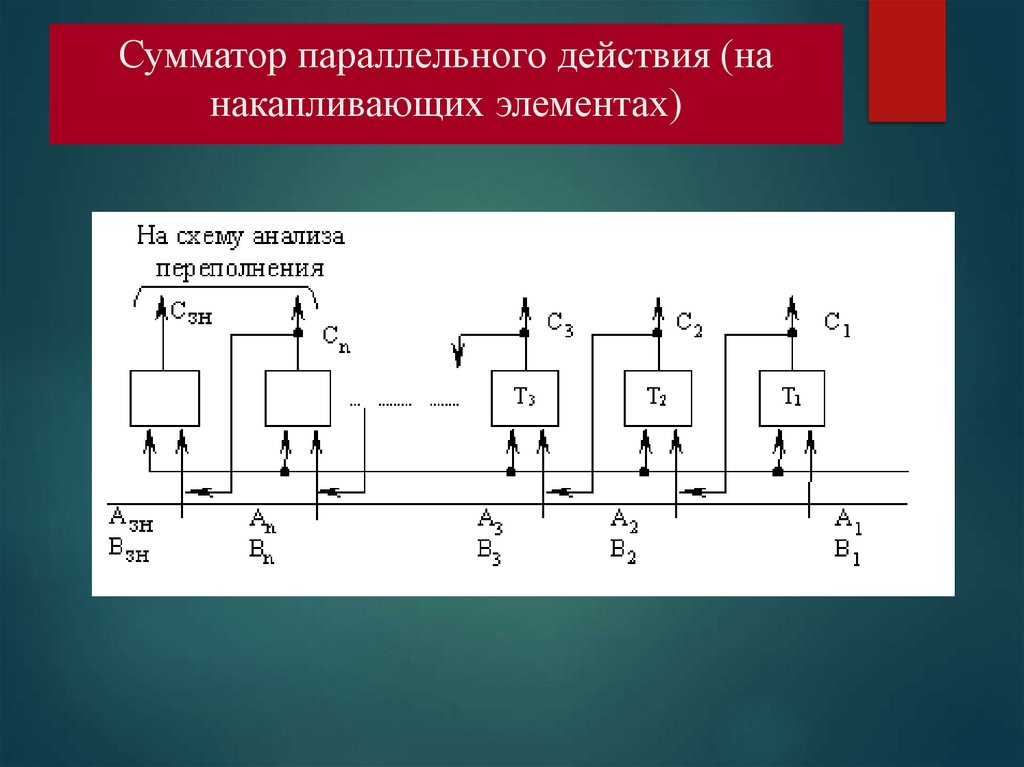

13. Сумматор параллельного действия (на накапливающих элементах)

14. КЛАССИФИКАЦИЯ АЛУ

По способу представления чисел:для чисел с фиксированной точкой;

для чисел с плавающей точкой;

для десятичных чисел.

По способу действия над операндами:

последовательные;

В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во

времени над их отдельными разрядами. Такие АЛУ, как правило, используют конвейерный метод обработки, при котором

совмещаются во времени фазы выполнения операции для различных разрядов операндов.

параллельные.

В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над

всеми разрядами операндов.

По выполняемым функциям АЛУ подразделяются на:

многофункциональные;

В многофункциональных АЛУ все возможные операции для всех форм представления чисел выполняются одними и теми же

схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

функциональные (блочные).

В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными и алфавитно-цифровыми полями,

операции умножения выполняются в отдельных блоках. Такой подход позволяет увеличить скорость работы АЛУ за счет

использования быстродействующих блоков, а также за счет организации параллельной работы этих блоков. Однако в этом случае

значительно увеличиваются затраты на оборудование.

15.

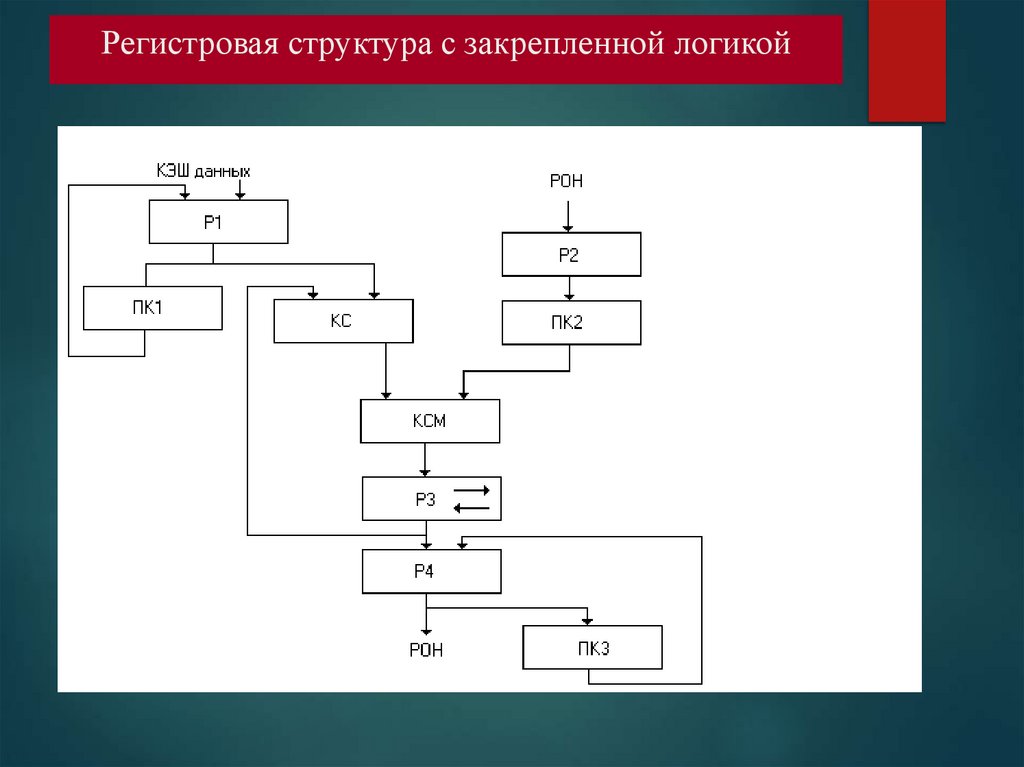

По структурной организации АЛУимеющие:

регистровую

подразделяются на устройства,

структуру с непосредственными связями и закрепленной

логикой;

магистральную структуру с сосредоточенной памятью и логикой.

В АЛУ с регистровой структурой за каждым из регистров закреплена своя

логическая схема, используемая для выполнения микрооперации.

Пример:

С регистром Рг1 непосредственно связан преобразователь кода ПК1. С

регистром Рг3 объединен КСМ по схеме накапливания сумматора, а с КСМ, в

свою очередь, связаны ПК2 и комбинационная схема КС для

мультиплексирования входных данных. На регистре Рг3 выполняются

микрооперации сдвига вправо или влево и сброс. Регистр Рг4 выполняет

микрооперации сдвига и непосредственно связан с ПК3. Таким образом, в

АЛУ с такой структурой функции хранения и преобразования информации

выполняются одним и тем же операционным блоком.

16. Регистровая структура с закрепленной логикой

17.

В АЛУ с магистральной структурой регистры выделены в отдельный блок, а схемыдля преобразования информации выделены также в отдельный операционный блок

(ОБ), который связан с блоками регистров по входам и выходам. Блок регистров (БР)

осуществляет функции приема, хранения и выдачи операндов и результатов, а ОБ

выполняет весь набор микроопераций над словами, хранимыми в блоке регистров. В

АЛУ с такой структурой блок регистров может быть реализован или как СОЗУ, или

как совокупность отдельных регистров с индивидуальными схемами управления.

Структура же ОБ имеет следующие модификации:

последовательное соединение операционных узлов;

параллельное соединение операционных узлов.

Пример АЛУ с магистральной структурой с последовательным соединением узлов

ОБ.

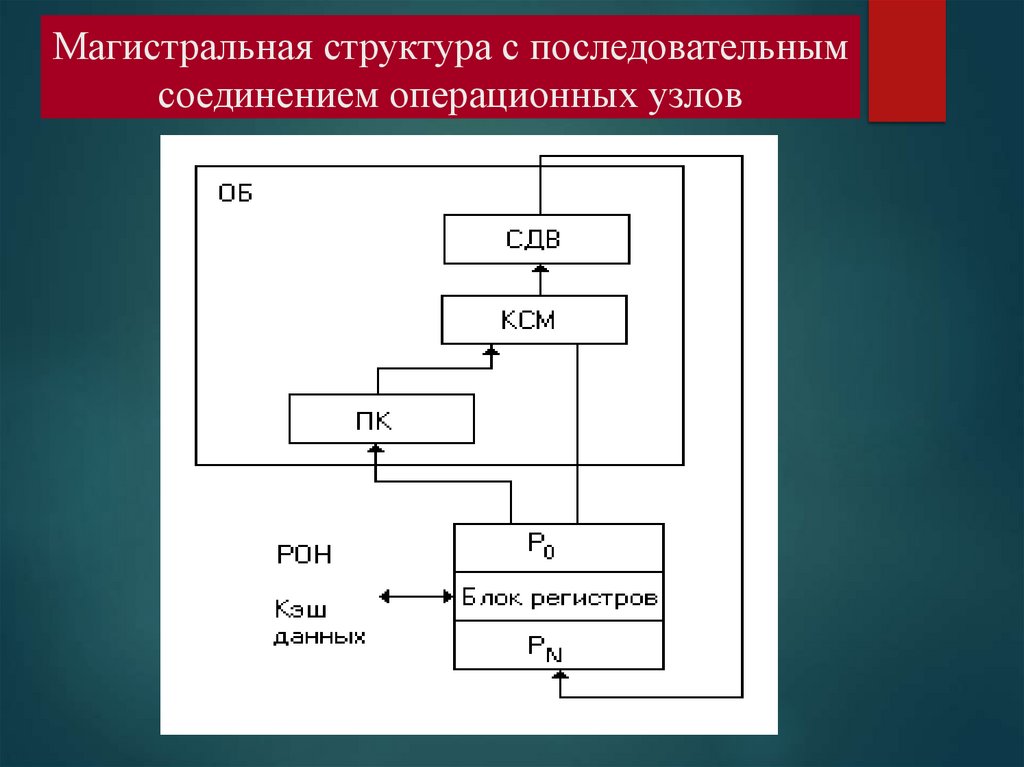

В этом АЛУ преобразователь кода ПК, комбинационный сумматор КСМ и

сдвигатель СДВ соединены последовательно, причем ПК и КСМ по входам связаны

с выходными шинами блока регистров, а выход СДВ – с входной шиной блока

регистров. Такая организация операционного блока дает возможность выполнять с

высокой скоростью последовательности микроопераций, обеспечивающие

выполнение одного слова.

18. Магистральная структура с последовательным соединением операционных узлов

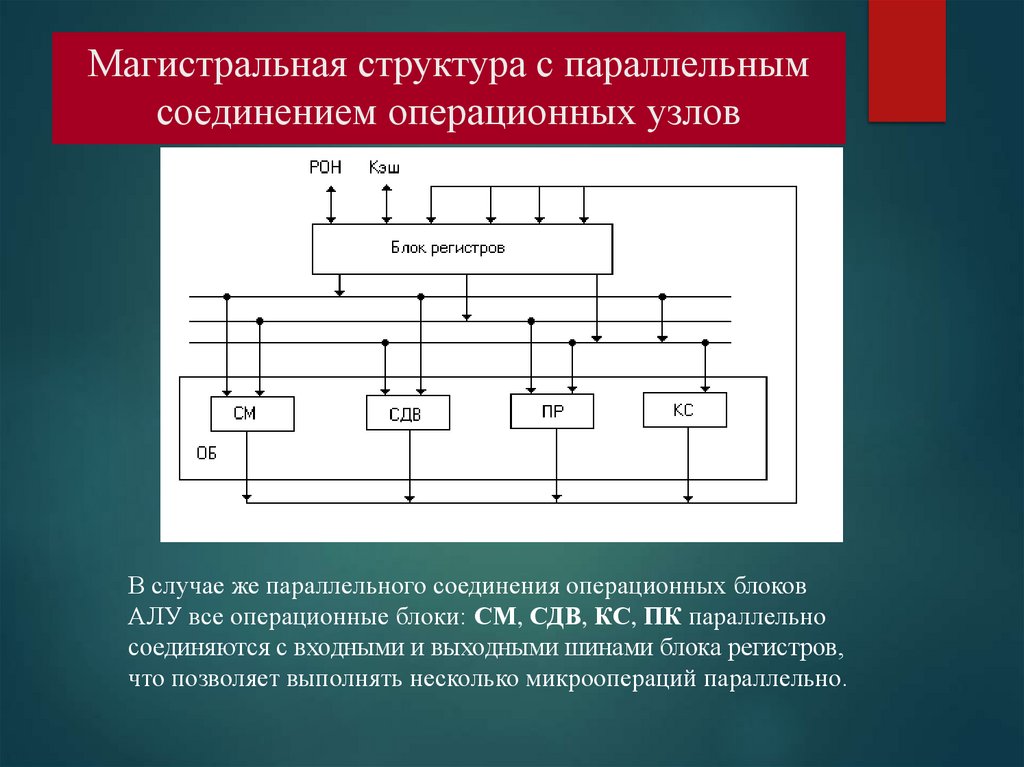

19. Магистральная структура с параллельным соединением операционных узлов

В случае же параллельного соединения операционных блоковАЛУ все операционные блоки: СМ, СДВ, КС, ПК параллельно

соединяются с входными и выходными шинами блока регистров,

что позволяет выполнять несколько микроопераций параллельно.

20. МЕТОДЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ АЛУ

21.

Одним из таких методов является реализация принципа локального параллелизма.Суть этого принципа – в распараллеливании во времени алгоритма выполняемой

отдельно команды на ряд независимых этапов и их реализации на различных

операционных блоках АЛУ.

Второй хорошо известный метод – конвейерная обработка. Операционный блок

разделяется на несколько частей – уровней конвейера. На каждой ступени

выполняется определенная стадия операции (например, считывание операндов,

сравнение порядков чисел, сложение мантисс чисел и так далее). Совмещение стадий

выполнения нескольких операций на различных ступенях конвейера приводит к тому,

что реализация следующей операции начинается до окончания предыдущей. Это

значительно увеличивает быстродействие операционного блока.

Другой способ сокращения длительности выполнения многотактных операций –

использование эффективных алгоритмов. При использовании таких алгоритмов

сочетается использование быстродействующих блоков, одновременно анализа

нескольких разрядов операндов и реализация конвейерного метода обработки.

Наиболее новый способ увеличения быстродействия всех блоков процессора ЭВМ –

введение векторных операций – операций над упорядоченными массивами данных

(в суперЭВМ векторные операции появились давно, в связи с чем в составе

процессоров появилась специализация устройств по типам операндов – скалярные и

векторные).

22.

Например, в современных процессорах появилисьрегистровая память и средства обработки двух

типов: векторные и скалярные.

К векторным средствам обработки относятся:

один или несколько арифметических конвейеров

для обработки элементов векторов;

векторные

регистры для хранения векторной

информации.

Векторные средства обработки данных позволяют

увеличить производительность ЭВМ в несколько

раз.

23. Системы команд процессора

24.

Система команд - это набор допустимых для данногопроцессора управляющих кодов и способов

адресации данных. Система команд жестко связана с

конкретным типом процессора, поскольку

определяется аппаратной структурой блока

дешифрации команд, и обычно не обладает

переносимостью на другие типы процессоров.

25. Типовая структура формата команды:

1. КОП - код операции - двоичный код,однозначно указывающий процессору на

выполнение конкретных действий (пересылка,

сложение и т.п.), и определяющий при этом форму

задания адресов операндов; 1 или 2 байта;

2. АЧ - адресная часть - двоичное число, которое

может представлять собой адрес (адреса)

операндов, значение операнда, адрес следующей

команды (адрес перехода, передачи управления).

От 1 до 4 байт.

26.

По характеру выполняемых операций различаютследующие основные группы команд:

арифметические операции над числами с

фиксированной или плавающей точкой;

команды двоично-десятичной арифметики;

логические (поразрядные) операции;

пересылка операндов;

операции ввода-вывода;

передача управления;

управление работой центрального процессора.

27. Представление команды

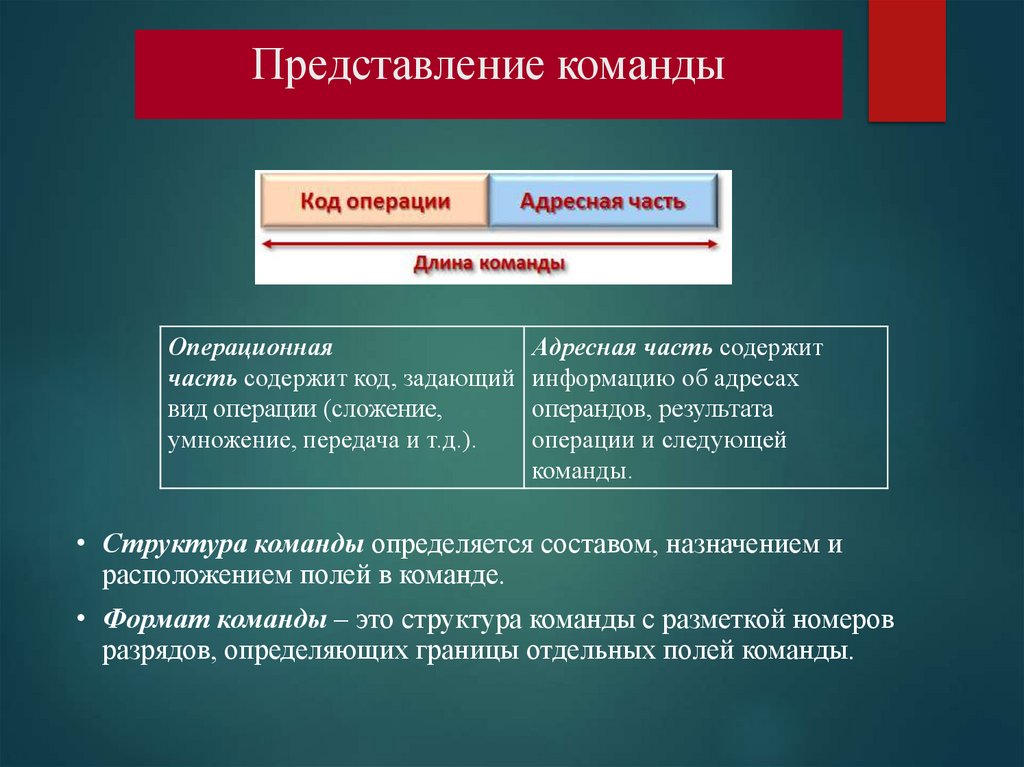

ОперационнаяАдресная часть содержит

часть содержит код, задающий информацию об адресах

вид операции (сложение,

операндов, результата

умножение, передача и т.д.).

операции и следующей

команды.

• Структура команды определяется составом, назначением и

расположением полей в команде.

• Формат команды – это структура команды с разметкой номеров

разрядов, определяющих границы отдельных полей команды.

28.

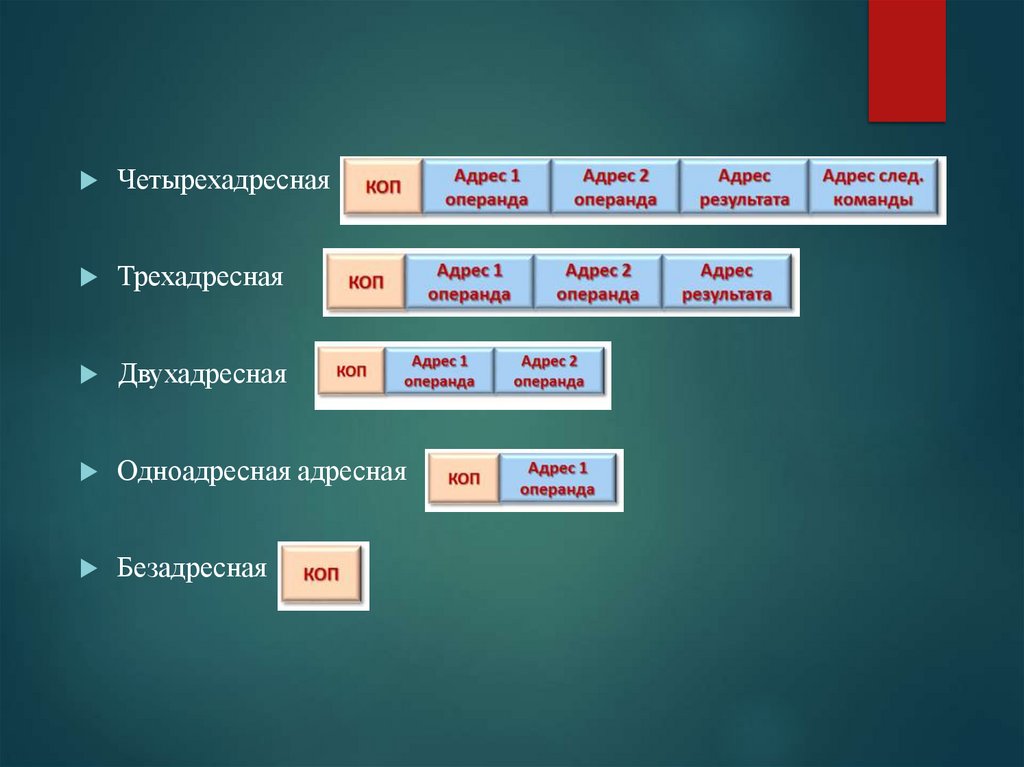

ЧетырехадреснаяТрехадресная

Двухадресная

Одноадресная адресная

Безадресная

29.

Одноадресная - подразумеваемые адреса имеют результат операции и одиниз операндов. При этом один из операндов и результат операции

размещаются в одном фиксированном регистре. Выделенный для этой цели

внутренний регистр процессора получил название аккумулятор.

Двухадресная - используется в ВМ, построенных так, что результат

операции будет всегда помещаться в фиксированный регистр процессора.

Трехадресная - используется в ВМ, построенных так, что после выполнения

команды по адресу K (команда занимает L ячеек памяти) выполняется

команда по адресу K+L. Такой порядок выборки команд называется

естественным.

Четырехадресная - полная информация о выполняемой операции. Порядок

выборки команд называется принудительным. Он использовался в первых

моделях ВМ, имеющих небольшое число команд и очень незначительный

объем ОП, поскольку длина такой команды зависит от разрядности адресов

операндов и результата.

Безадресная - фиксирует адреса обоих операндов и результата операции,

например при работе со стековой памятью.

30.

Прерывание — сигнал, сообщающий процессору о наступлениикакого-либо события.

При этом выполнение текущей последовательности команд

приостанавливается и управление передаётся обработчику

прерывания, который реагирует на событие и обслуживает его, после

чего возвращает управление в прерванный код. На основе

прерываний организуется одновременная работа с несколькими

периферийными устройствами, позволяет ПК приостановить

текущие действия и переключиться на что-то еще в ответ на

прерывание.

31. Классификация прерываний

32.

В зависимости от источника возникновения сигналаa) асинхронные (внешние, аппаратные) — события, которые

исходят от внешних источников (например, периферийных

устройств).

Могут произойти в любой момент: сигнал от таймера,

сетевой карты или дискового накопителя, нажатие клавиш

клавиатуры, движение мыши и др. Факт возникновения в

системе такого прерывания трактуется как запрос на

прерывание.

33.

b) синхронные (внутренние, особого случая) — события всамом процессоре как результат нарушения каких-то условий

при исполнении машинного кода (деление на ноль,

переполнение, обращение к недопустимым адресам или

недопустимый код операции)

34.

c) программные (частный случай внутреннегопрерывания) — инициируются исполнением специальной

инструкции в коде программы. Программные прерывания в

основном используются для обращения к функциям

встроенного программного обеспечения, драйверов и

операционной системы.

35.

В зависимости от возможности запрета внешние прерыванияделятся на:

маскируемые — прерывания, которые можно запрещать

установкой соответствующих битов в регистре маскирования

прерываний

(в x86-процессорах — сбросом флага IF в регистре флагов);

немаскируемые — обрабатываются всегда, независимо от

запретов на другие прерывания.

Например, такое прерывание может быть вызвано сбоем в

микросхеме памяти.

36.

Вектор прерывания — закреплённый за устройствомномер, который идентифицирует соответствующий

обработчик прерываний.

Вектор прерывания занимает двойное слово (4 байта) и

содержит адрес программы обработки данного прерывания

в формате «сегмент : смещение».

37.

Имеется 256 векторов прерываний, которые нумеруются с 0 поFF. Всякий раз, когда происходит прерывание, текущие значение

CS, IP и регистра флагов вталкиваются в стек и управление

передается по адресу заданному в соответствующем векторе

прерывания. Программа обработки прерывания завершает свою

работу и содержимое CS, IP и регистра флагов выталкиваются из

стека, продолжая работу прерванной программы.

38.

Последовательность действий при обработке прерыванийПри любом прерывании происходит следующее:

1. Возникновение прерывания. Например, в процессе работы

приложения была нажата какая-то клавиша.

2. Обращение к таблице векторов прерываний. Пусть

возникшее прерывание имеет номер 9, тогда процессор,

предварительно запомнив место возникновения прерывания,

обращается к девятой строке таблицы и извлекает оттуда адрес

обработчика девятого прерывания.

3. Обработка прерывания.

4. Возвращение из прерывания. Окончив свою работу,

обработчик прерывания сообщает об этом процессору, который в

ответ на неё возвращается к тому, чем он занимался до

возникновения прерывания, т.е. к выполнению запущенного

приложения.

39. Приоритеты прерываний

40.

До окончания обработки прерывания обычноустанавливается запрет на обработку этого типа прерывания,

чтобы процессор не входил в цикл обработки одного

прерывания. Приоритезация означает, что все источники

прерываний делятся на классы и каждому классу назначается

свой уровень приоритета запроса на прерывание.

41.

Относительное обслуживание прерываний означает, чтоесли во время обработки прерывания поступает более

приоритетное прерывание, то это прерывание будет

обработано только после завершения текущей процедуры

обработки прерывания.

42.

Абсолютное обслуживание прерываний означает, чтоесли во время обработки прерывания поступает более

приоритетное прерывание, то текущая процедура обработки

прерывания вытесняется, и процессор начинает выполнять

обработку вновь поступившего более приоритетного

прерывания. После завершения этой процедуры процессор

возвращается к выполнению вытесненной процедуры

обработки прерывания.

43. Функционирование компьютера при обработке прерывания

При поступлении запроса прерывания компьютер выполняет следующую последовательностьдействий:

1) определение наиболее приоритетного незамаскированного запроса на прерывание (если

одновременно поступило несколько запросов);

2) определение типа (номера) выбранного запроса;

3) сохранение текущего состояния счетчика команд и регистра флагов;

4) определение адреса обработчика прерывания по типу прерывания и передача управления

первой команде этого обработчика;

5) выполнение программы - обработчика прерывания;

6) восстановление сохраненных значений счетчика команд и регистра флагов прерванной

программы;

7) продолжение выполнения прерванной программы.

Этапы 1-4 выполняются аппаратными средствами ЭВМ автоматически при появлении

запроса прерывания. Этап 6 также выполняется аппаратно по команде возврата из

обработчика прерывания.

Электроника

Электроника