Похожие презентации:

Статическая память. Применение и принцип работы (лекция № 11)

1.

Статическая память.Применение и принцип

работы.

Базовая система ввода/вывода

(BIOS)

2.

Статическая память SRAMSRAM (Static Random Access Memory)

способна хранить информацию в статическом

режиме при наличии питающего напряжения

сколь угодно долго при отсутствии обращений.

Ячейки SRAM реализуются на триггерах –

элементах с двумя устойчивыми состояниями.

По сравнению с динамической памятью эти

ячейки сложнее и занимают больше места на

кристалле, однако они проще в управлении и не

требуют регенерации.

3.

Быстродействие и потребление энергиистатической памятью определяется технологией

изготовления и схемотехникой ее ячеек.

Самая экономичная КМОП память (CMOS

Memory) имеет время доступа более 100 нс,

но зато пригодна для длительного хранения

информации при питании от маломощной

батареи, что и применяется в памяти

конфигурации PC.

Самая быстрая статическая память имеет

время доступа в несколько наносекунд. Это

позволяет ей работать на частоте системной

шины ЦПУ, не требуя от него тактов ожидания.

4.

Типовой объем памяти микросхем SRAMдостигает 1 Мбит. Относительно высокая

удельная стоимость хранения информации и

энергопотребление при низкой плотности

упаковки не позволяют использовать SRAM в

качестве основной памяти компьютеров.

В PC микросхемы SRAM используют в

основном для построения внешнего (L2) кэша

основной памяти.

Существуют следующие разновидности

статической памяти – Async SRAM, Sync Burst

SRAM и Pipelined Burst SRAM.

5.

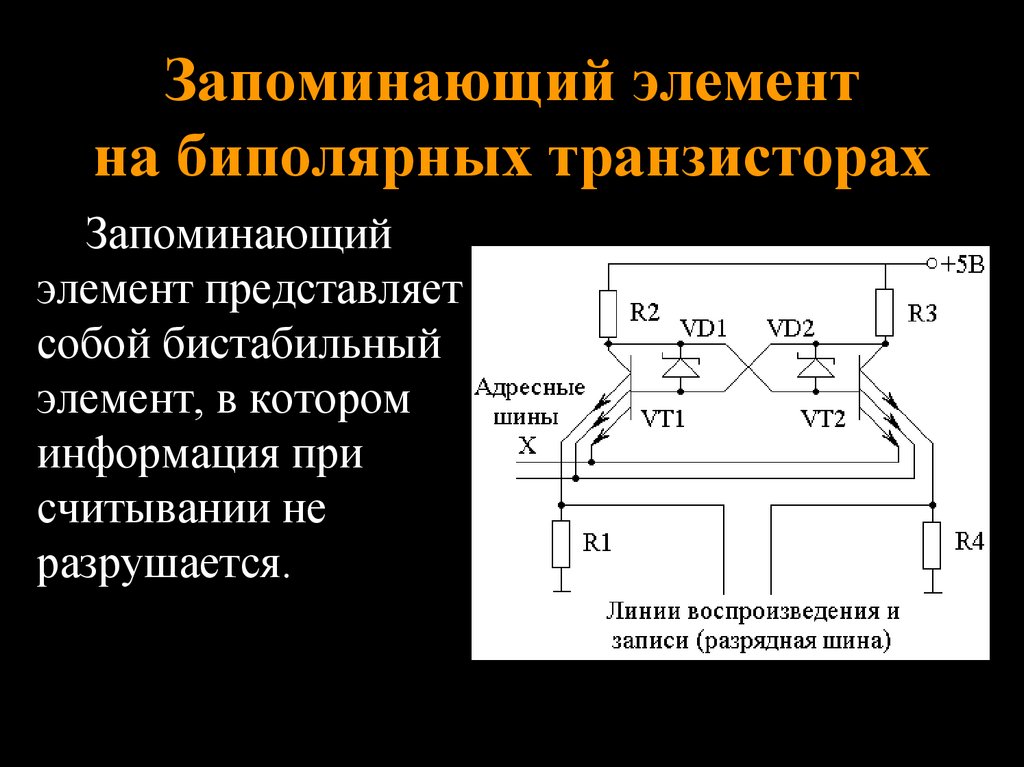

Запоминающий элементна биполярных транзисторах

Запоминающий

элемент представляет

собой бистабильный

элемент, в котором

информация при

считывании не

разрушается.

6.

Запоминающий элементна биполярных транзисторах

Разрядная шина предназначена для считывания состояния

триггера и для записи в него новой информации.

Если на одну или обе адресные шины подано низкое

напряжение (уровень ‘0’), то триггер будет находиться в

устойчивом состоянии и ток открытого транзистора будет

замыкаться на землю через эмиттеры, подключенные к адресным

шинам.

Если напряжение на адресных шинах повысить до уровня лог.

‘1’, то эмиттеры, подключенные к разрядной шине, управляют

током транзисторов. Если транзистор VT1 открыт, то ток пойдет

через левый резистор (R1). В это время транзистор VT2 закрыт и,

таким образом, через резистор R4 ток не протекает. Это означает,

что напряжение на резисторе R1 будет больше, чем напряжение на

резисторе R2.

Из изложенного следует, что состояние триггера можно

определить, измеряя напряжение на резисторах R1 и R2. Это

7.

Запоминающий элементна биполярных транзисторах

Используя линии разряда, можно также

записывать информацию в ячейку.

Предположим, что на адресных шинах

уровень лог. ‘1’, и напряжение на R1

установлено выше, чем на R4. Тогда

транзистор VT2 откроется и закроет

транзистор VT1.

Таким образом, одни и те же разрядные

шины используют для считывания

состояния триггера и для установки

заданного значения в выбранную ячейку.

8.

Запоминающий элементна МДП-транзисторах

ЗЭ на основе МДП-структур представляет собой

простейший RS-триггер. На их базе создают ЗУ

большой и сверхбольшой емкости.

Основной их недостаток - потребление тока в

режиме хранения, так как один из транзисторов

триггера всегда находится в открытом состоянии.

Для уменьшения потребляемой мощности

необходимо увеличить сопротивление нагрузки, но

это приводит к снижению быстродействия. Поэтому

используют схемы на КМДП - транзисторах, где ток

потребляется только в момент переключения.

9.

Async SRAM – это обычная (стандартная)асинхронная статическая память (Standard или

Asynchronous SRAM). Под термином SRAM по

умолчанию подразумевается этот тип, когда он

не указан.

Микросхемы Async SRAM имеют простейший

асинхронный интерфейс, включающий шину

адреса, шину данных и сигналы управления

CS#, ОЕ# и WE#. Микросхема выбирается

низким уровнем сигнала CS# (Chip select),

низкий уровень сигнала ОЕ# (Output Enable)

открывает выходные буферы для считывания

данных, WE# (Write Enable) низким уровнем

разрешает запись.

10.

Временные диаграммычтения и записи памяти SRAM

При записи управление выходными буферами

может производиться как сигналом ОЕ# (цикл 1),

так и сигналом WE# (цикл 2).

11.

Sync Burst SRAM – это синхронная статическаяпамять. Она оптимизирована для выполнения

пакетных (burst) операций обмена кэш-памяти.

В ней имеется внутренний двухбитный счетчик

адреса.

В дополнение к сигналам асинхронной памяти

(адрес, данные, CS#, OE# и WE#), эта память

использует сигнал CLC (Clock) для синхронизации с системной шиной и сигналы управления

пакетным циклом ADSP#, CADS# и ADV#.

12.

Сигналы CADS# (Cache ADdress Strobe) иADSP# (ADdress Status of Processor), которыми

процессор или кэш-контроллер отмечает фазу

адреса очередного цикла, являются стробами

записи начального адреса цикла во внутренний

регистр адреса.

Любой из этих сигналов инициирует цикл

обращения, одиночный (single) или пакетный

(burst), а сигнал ADV# (ADVance) используется

для перехода к следующему адресу пакетного

цикла.

13.

Все сигналы, кроме ОЕ#, синхронизируются поположительному перепаду сигнала CLK.

Поэтому значение входных сигналов должно

установиться до перепада и удерживаться после

него еще некоторое время. Выходные данные

при считывании будут также действительны во

время этого перепада.

Двухбитный счетчик адреса не позволяет

перейти границу четырехэлементного пакетного

цикла. Порядок счета адресов внутри пакетного

цикла соответствует специфическому порядку

чередования (interleaved), принятому в ЦПУ i486

и старше.

14.

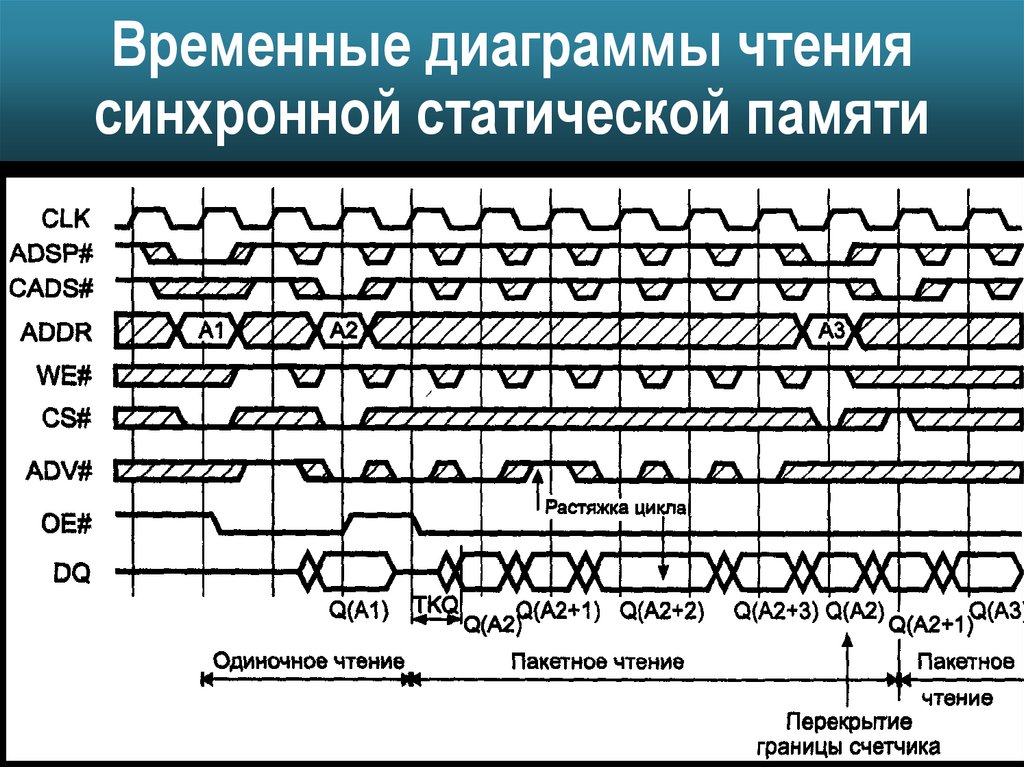

Временные диаграммы чтениясинхронной статической памяти

15.

РВ SRAM (Pipelined Burst SRAM) – конвейерноеусовершенствование синхронной памяти (слово

«синхронная» из названия для краткости изъято).

Конвейер – дополнительный внутренний

регистр данных, который, требуя дополнительного такта в первой пересылке цикла, позволяет

остальные данные получать без тактов ожидания даже на частотах выше 75 МГц.

Задержка данных относительно синхронизирующего перепада у современных микросхем РВ

SRAM составляет 4,5-8 нс.

16.

Но этот параметр не является временемдоступа в чистом виде из-за двух-трех тактов в

первой передаче, а отражает появление

действительных данных относительно

очередного перепада сигнала синхронизации.

Интерфейс РВ SRAM аналогичен интерфейсу

Sync Burst SRAM.

Кэш-память делится на две части – Data RAM

и Tag RAM. В первой располагаются данные, а

во второй микросхеме содержится информация

о нахождении этих данных в кэш-памяти.

17.

Микросхемы асинхронной памяти обычноисполняются в DIP-корпусах с 8-битной организацией, которые вставляются в специальные

«кроватки» системной платы. При установке

микросхем с 28 выводами в «кроватку» с 32

контактами свободными оставляют контакты 1,

2, 31 и 32. Банк собирается из 4 штук для

процессоров 486, 8 штук – для Pentium.

Микросхемы синхронной памяти обычно имеют

разрядность 16 или 32 бит (18 или 36 – с паритетом), один банк для Pentium собирается из

четырех или двух микросхем.

18.

DIP-32DIP-28

Микросхемы асинхронной памяти

в DIP-корпусах

19.

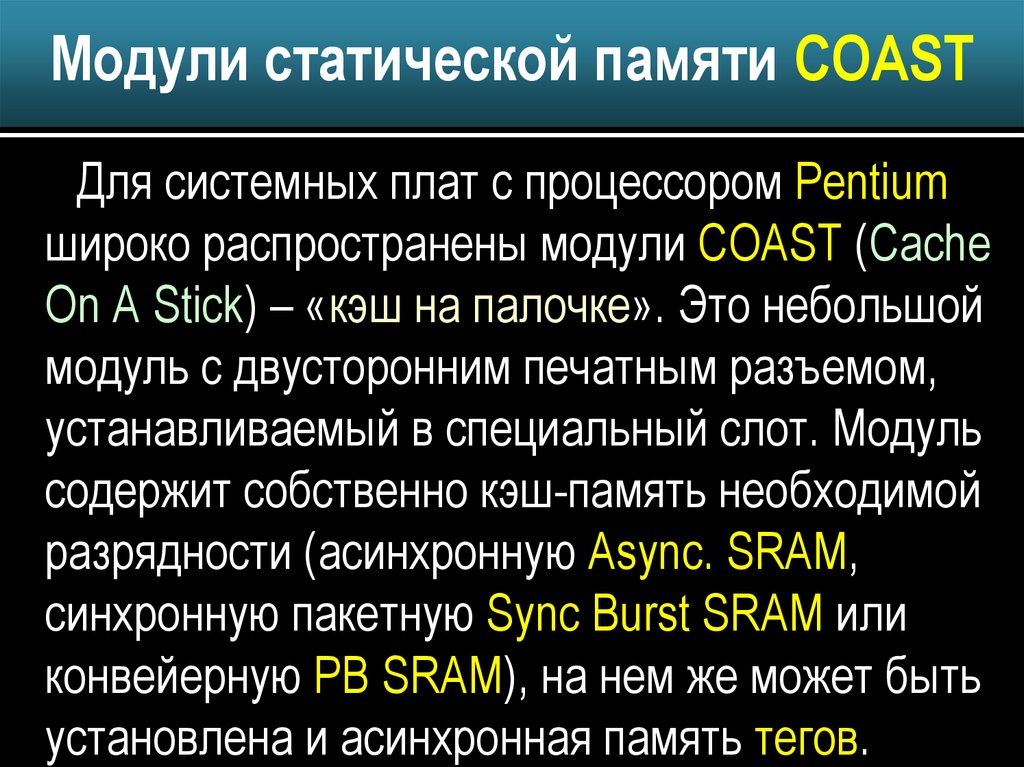

Модули статической памяти COASTДля системных плат с процессором Pentium

широко распространены модули COAST (Cache

On A Stick) – «кэш на палочке». Это небольшой

модуль с двусторонним печатным разъемом,

устанавливаемый в специальный слот. Модуль

содержит собственно кэш-память необходимой

разрядности (асинхронную Async. SRAM,

синхронную пакетную Sync Burst SRAM или

конвейерную РВ SRAM), на нем же может быть

установлена и асинхронная память тегов.

20.

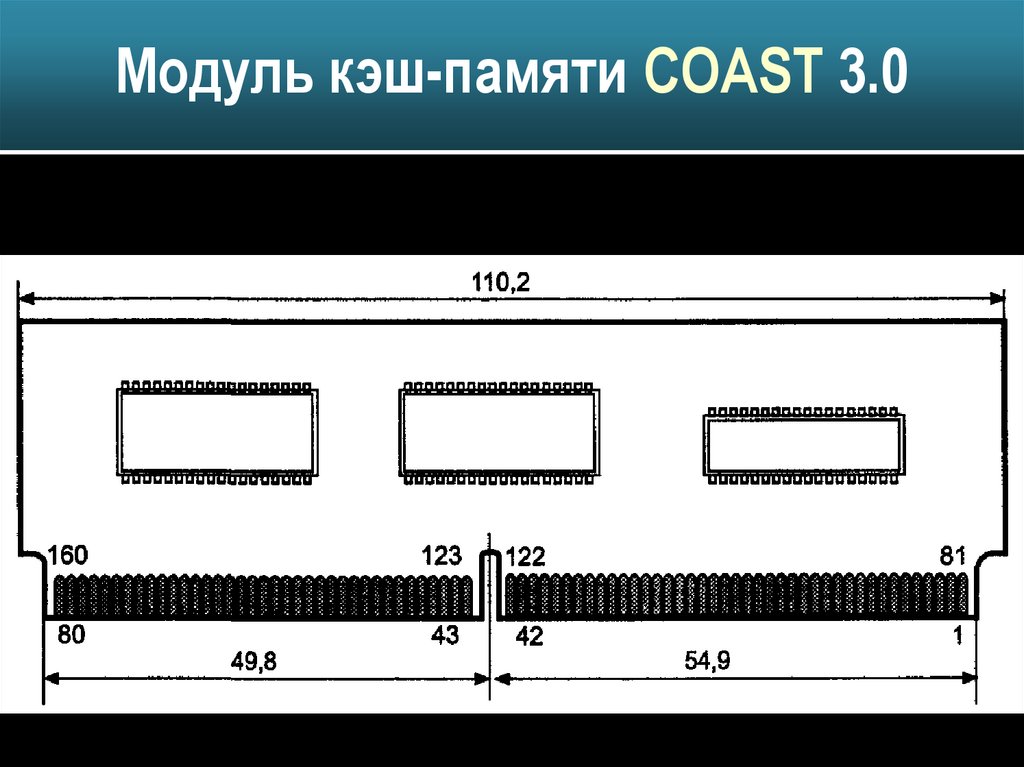

Модуль кэш-памяти COAST 3.021.

Энергонезависимая памятьОна хранит записанные данные при отсутствии

питающего напряжения, в отличие от статической и динамической памяти.

Существует несколько типов энергонезависимой

памяти: ROM, PROM, EPROM, EEPROM, Flash

Memory. Они отличаются своими свойствами,

способом построения запоминающих ячеек и

сферам применения. Запись информации в

такую память, или программирование,

существенно сложнее и требует больших затрат

времени и энергии, чем считывание.

22.

Основной режим работы такой памяти –считывание данных. После программирования

она допускает только считывание. Отсюда ее

общее название – ROM (Read Only Memory) или

ПЗУ (постоянное запоминающее устройство).

По виду программирования различают:

Микросхемы, программируемые при

изготовлении (масочные ПЗУ) – ROM.

Микросхемы, программируемые однократно

после изготовления перед установкой в РС

(прожигаемые ПЗУ, программируемые на

программаторах) – PROM (Programmable ROM),

ППЗУ (программируемые ПЗУ).

23.

Микросхемы, стираемые и программируемыемногократно РПЗУ (репрограммируемые ПЗУ),

EPROM (Erasable PROM – стираемые ПЗУ).

В энергонезависимую память записывают нули

в предварительно стертые (чистые) ячейки.

По способу стирания различают:

• микросхемы, стираемые ультрафиолетовым

облучением, EPROM (Erasable PROM –

стираемые микросхемы) или UV-EPROM

(Ultra-Violet EPROM, УФРПЗУ);

• электрически стираемые микросхемы

EEPROM (Electrical Erasable PROM, ЭСПЗУ), в

том числе и флэш-память.

24.

Масочная памятьТакую память можно представить в виде

матрицы, в которой уже при изготовления в

нужных местах прожигают "0" и "1". Матрица

представляет собой кремниевый кристалл

(микросхему).

Подобный процесс экономически оправдывает

себя при изготовлении сотен тысяч микросхем с

одинаковой информацией.

Если необходимо изменить хотя бы один

единственный бит, придется переделать маску,

а это обойдется недешево. Поэтому такой тип

памяти ROM сейчас не используется.

25.

Память PROMВ нее после изготовления можно записать

любые данные. При изготовлении они

прописываются двоичными единицами. При

программировании "пустой" PROM в нее

записываются нули. Этот процесс выполняется

с помощью специального программирующего

устройства, которое подает более высокое

напряжение (не 5 В, а 12 В) по различным

адресам в пределах адресного пространства,

отведенного для микросхемы. Микросхемы

PROM часто называются ОТР (One Time

Programmable – программируемые один раз).

26.

Память EPROMДанные в памяти EPROM можно стирать. Она

имеет прозрачное кварцевое окно прямо над

кристаллом – матрицей.

Окно пропускает ультрафиолетовые лучи

(УФЛ), которые стирают информацию на

микросхеме EPROM за счет хим. реакции. При

этом двоичные 0 в микросхеме становятся 1.

Длина волны УФЛ должна быть равна примерно

2,537 ангстрема, а их интенсивность – довольно

высокой (12 000 мВт/см2). Источник УФЛ должен

располагаться в нe дальше 2-3 см, а время

экспозиции составлять от 5 до 15 мин.

27.

Память EPROM и программаторКварцевое окно на EPROM после программирования заклеивается липкой лентой, чтобы УФЛ

обычном комнатном освещении не стерли

данные в памяти.

28.

Память EEPROM, или Flash ROMЭлектрически стираемую программируемую

постоянную память – или Flash ROM – можно

перепрограммировать, не снимая с системной

платы и не открывая системного блока, без

специального оборудования.

Для этого достаточно загрузить программу

модификации, взятую с Web-сервера

изготовителя BIOS системной платы, а затем

запустить программу модификации.

29.

Новая память PSiRAMНедавно созданный прототип модуля псевдостатической оперативной памяти PSiRAM обеспечивает отклик в течение 1,3 нс, продолжительность цикла обращения 1 нс и пропускную способность 2 Гбит/с на каждом информационном

выводе.

Литера i в названии памяти обозначает электрический ток, потому что ее трехтранзисторные

ячейки реагируют на изменение протекающего

тока, а не напряжения.

30.

Протототип сконструирован в варианте 32мегабитного модуля в конфигурации 2 Мб х 16бит. Напряжение питания составляет 1,2 В, но

возможна работа и при 0,8 В. В этом случае

память работает на частоте 400 МГц и

рассеивает всего 0,125 ватт тепловой мощности.

Модуль PSiRAM был изготовлен по 90-нанометровому техпроцессу, размер ячеек памяти составил 0,59 квадратных микрон. Из-за использования КМОП-логики новая память хорошо подходит для проектирования одночиповых (SoC)

устройств. Производство PSiRAM начнётся в

2006 г.

31.

BIOSBIOS (Basic Input/Output System) – Базовая система

ввода/вывода. Физически BIOS – это набор микросхем

ROM, расположенных на материнской плате. Емкость

CMOS (Сcomplementary Metal-Oxide Semiconductor –

дополнительный (добавочный) металл-оксидный

полупроводник) обычно 1-2 Мбит. Это энергонезависимая

память для хранения информации о конфигурации

компьютера. BIOS хранится в EEPROM (Erasable

Programmable Read Only Memory. Микросхема постоянной

памяти, содержимое которой стирается с помощью

ультрафиолета. Устаревший тип памяти.), EPROM или во

Flash ROM, а в микросхеме CMOS BIOS сохраняет

аппаратную конфигурацию компьютера.

32.

BIOS• BIOS компании AWARD имеет собственную систему конфигурирования,

позволяющую тонко настраивать различные аппаратные параметры

работы компьютера. Настроенная пользователем конфигурация хранится

в специальной энергозависимой памяти типа CMOS, содержимое

которой постоянно поддерживается питанием от системного

аккумулятора.

• Также кроме аппаратных настроек компонентов материнской платы в

CMOS памяти хранятся пароли доступа к программе Setup BIOS и

пароль пользователя. Запуск программы CMOS Setup происходит по

нажатию клавиши Del во время прохождения теста POST(Power Qn Self

Test -тестирование компьютера после включения питания)при загрузке

ПК, либо автоматически после замены пользователем аккумулятора или

возникновении какой-либо ошибки.

• Итак, программа БИОС хранится в EEPROM, EPROM или во Flash ROM,

а в микросхеме CMOS БИОС сохраняет аппаратную конфигурацию

компьютера.

33.

BIOS• После запуска программы CMOS Setup

появляется ее главное меню. Перемещение по

пунктам меню осуществляется с помощью

курсорных клавиш, выбор нужной системы

конфигурации - клавишей Enter. Также, в

случае нечеткого или монохромного монитора

можно настроить цветовую гамму программы

клавишами Shift+F2. Выход с сохранением

внесенных изменений - клавиша F10, выход

без сохранения - клавиша Esc.

Электроника

Электроника