Похожие презентации:

Schem_lc_08

1. Лекция №8 Функциональные узлы комбинационного типа. Дешифраторы. Шифраторы. Приоритетные шифраторы. Указатели старшей единицы

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИСТЕТ

Схемотехника ЭВМ

Лекция №8

Функциональные узлы комбинационного типа.

Дешифраторы. Шифраторы. Приоритетные

шифраторы. Указатели старшей единицы

Мальчуков Андрей Николаевич

Томск – 2014

2. Функциональные узлы комбинационного типа

•Кузлам

комбинационного

типа

относятся

мультиплексоры, демультиплексоры, дешифраторы,

шифраторы, приоритетные шифраторы, сумматоры,

АЛУ, компараторы (сравнители кодов), матричные

умножители, схемы контроля (паритет, код Хэмминга),

преобразователи кода и т.д.

2

3. Дешифраторы

• Дешифраторы относятся к преобразователям кодов(кодирующим устройствам). Кодирующим устройством

называют

логический

узел,

преобразующий

многоразрядный входной код в выходной код,

построенный по иному закону.

• Двоичным дешифратором или декодером (от англ. слова

decoder) чаще всего называют кодирующее устройство,

преобразующее двоичный код в код «1 из N».

• Из всех m выходов дешифратора активный уровень

имеется только на одном, а именно на том, номер

которого равен поданному на вход двоичному числу. На

всех остальных выходах дешифратора уровни

напряжения неактивные.

3

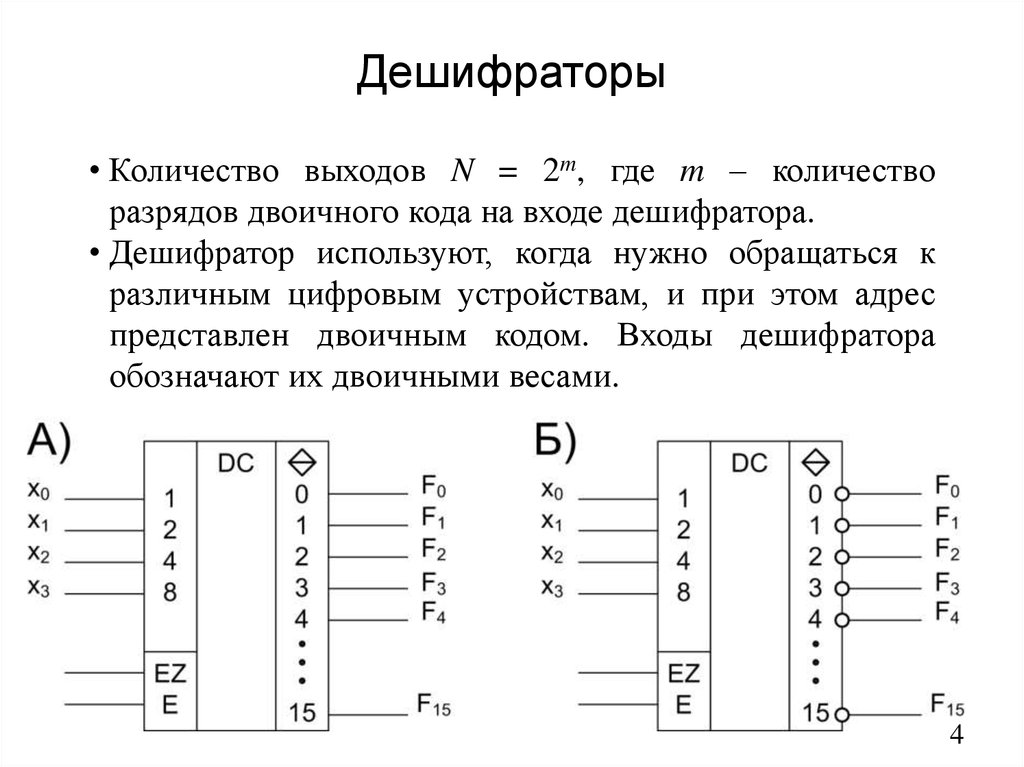

4. Дешифраторы

• Количество выходов N = 2m, где m – количестворазрядов двоичного кода на входе дешифратора.

• Дешифратор используют, когда нужно обращаться к

различным цифровым устройствам, и при этом адрес

представлен двоичным кодом. Входы дешифратора

обозначают их двоичными весами.

4

5. Таблица функционирования DC 3-8

ВХОДЫ4 2 1 E

X X X X

X X X 0

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 1

1 0 0 1

1 0 1 1

1 1 0 1

1 1 1 1

EZ

0

1

1

1

1

1

1

1

1

1

0

Z

0

1

0

0

0

0

0

0

0

1

Z

0

0

1

0

0

0

0

0

0

ВЫХОДЫ

2 3 4 5

Z Z Z Z

0 0 0 0

0 0 0 0

0 0 0 0

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

0 0 0 0

0 0 0 0

6

Z

0

0

0

0

0

0

0

1

0

7

Z

0

0

0

0

0

0

0

0

1

5

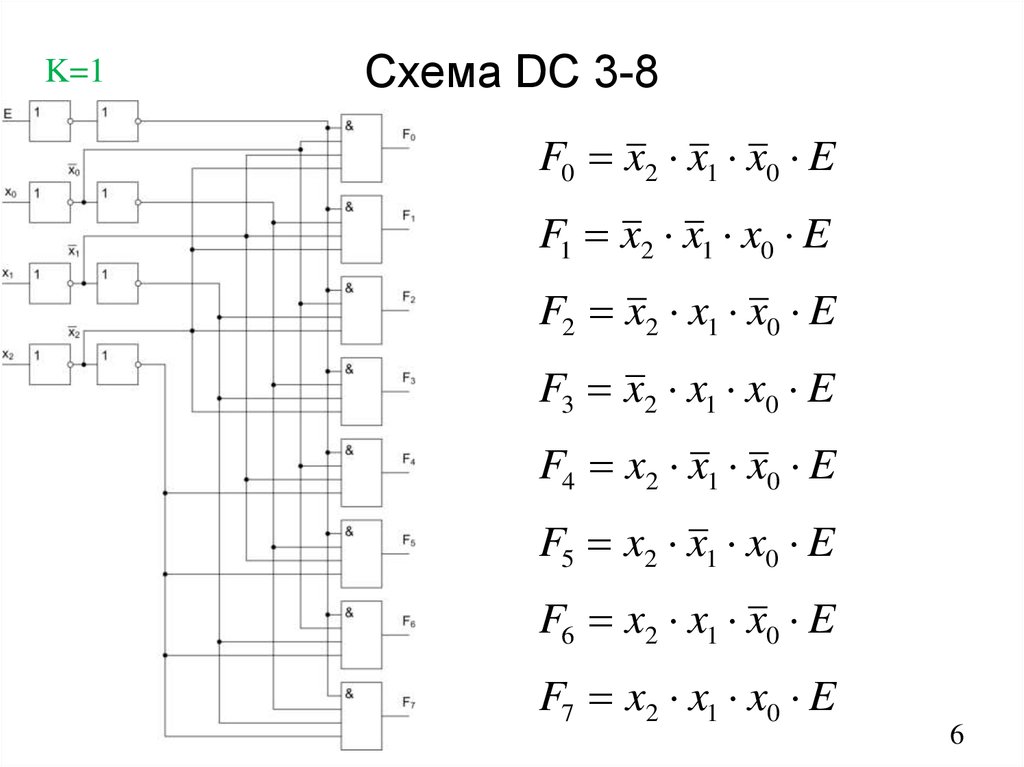

6. Схема DC 3-8

K=1Схема DC 3-8

F0 x2 x1 x0 E

F1 x2 x1 x0 E

F2 x2 x1 x0 E

F3 x2 x1 x0 E

F4 x2 x1 x0 E

F5 x2 x1 x0 E

F6 x2 x1 x0 E

F7 x2 x1 x0 E

6

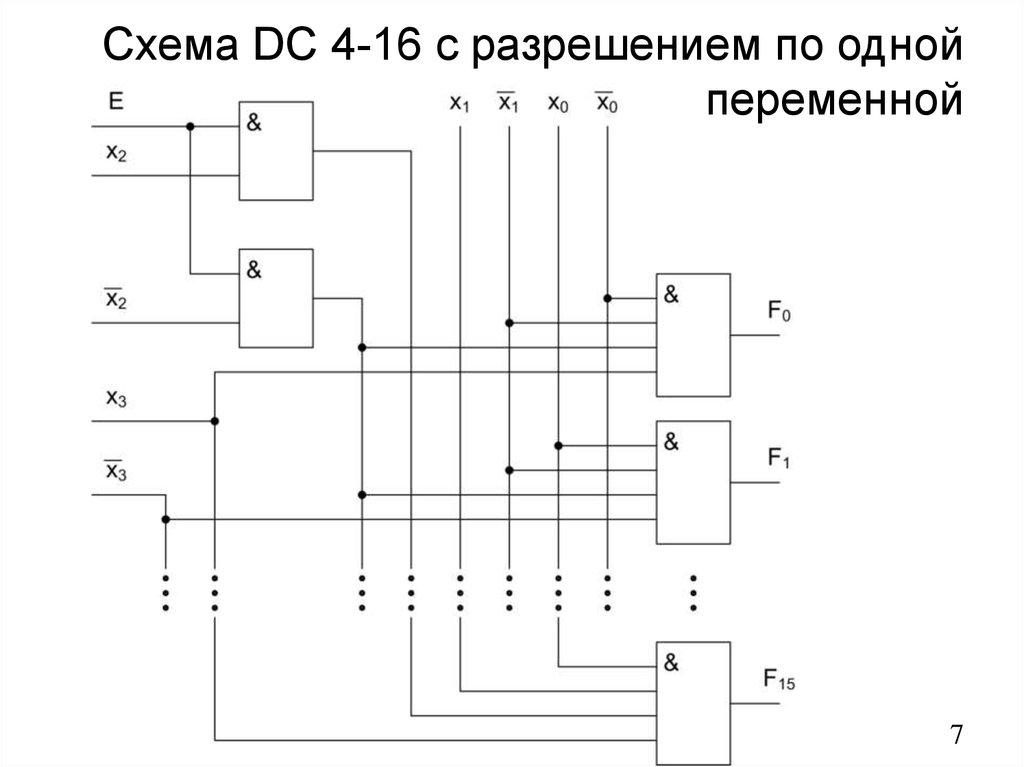

7. Схема DC 4-16 с разрешением по одной переменной

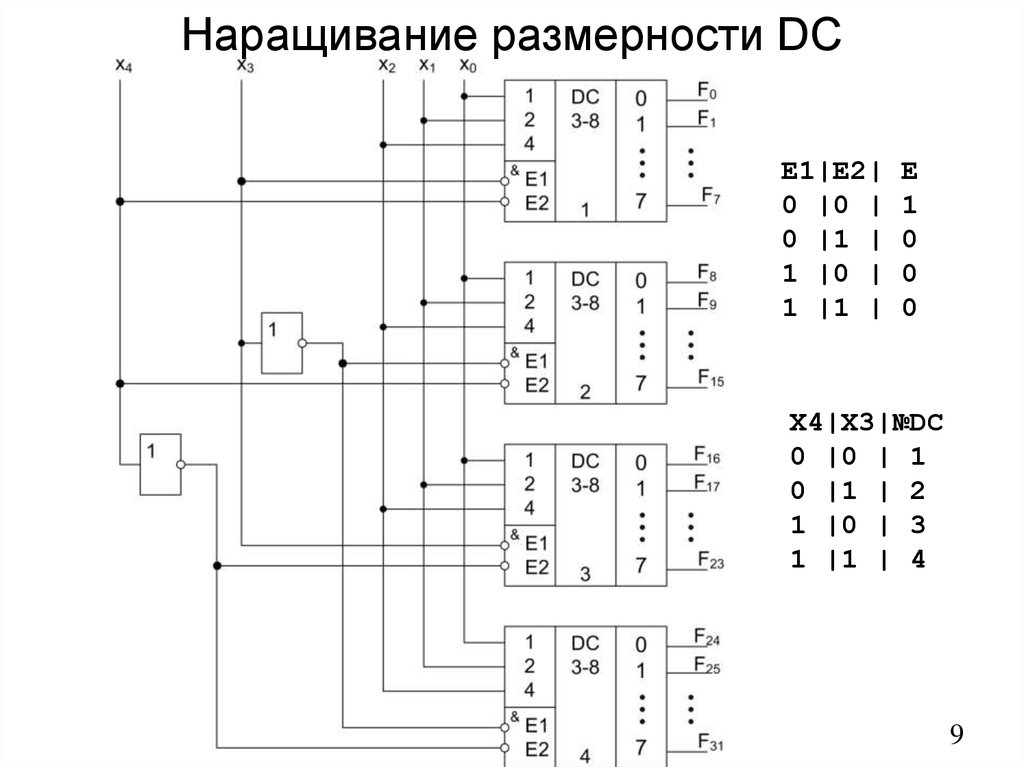

78. Наращивание размерности DC: каскады

X4|X3|№DC0 |0 | 1

0 |1 | 2

1 |0 | 3

1 |1 | 4

8

9. Наращивание размерности DC

E1|E2|0 |0 |

0 |1 |

1 |0 |

1 |1 |

E

1

0

0

0

X4|X3|№DC

0 |0 | 1

0 |1 | 2

1 |0 | 3

1 |1 | 4

9

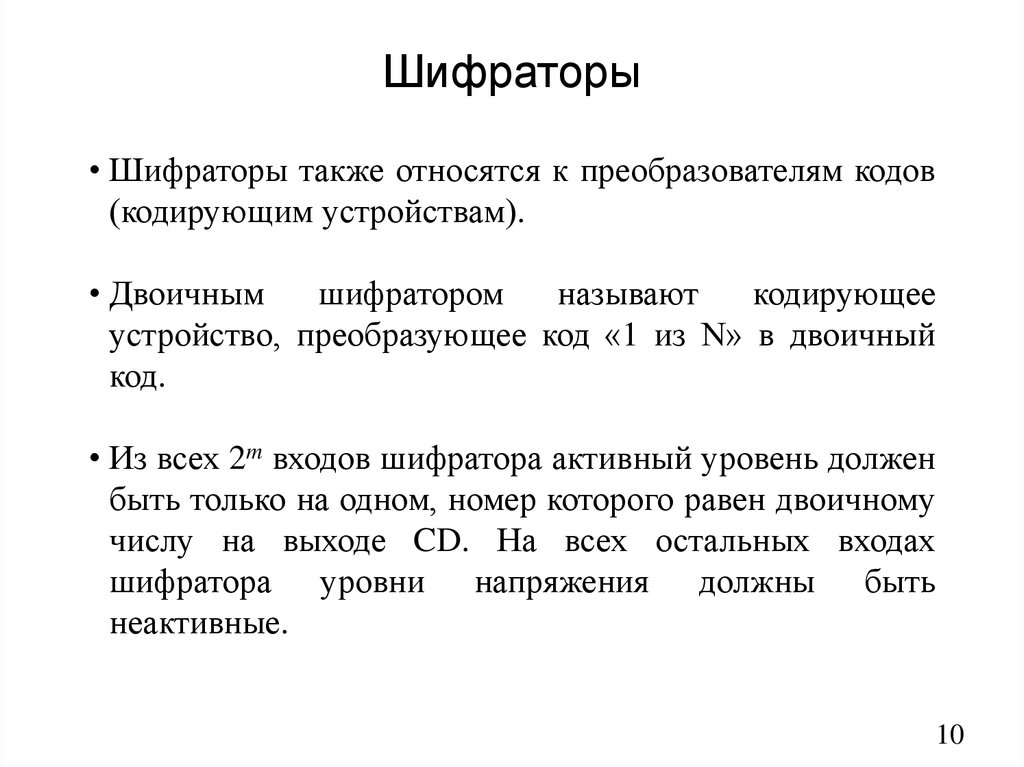

10. Шифраторы

• Шифраторы также относятся к преобразователям кодов(кодирующим устройствам).

• Двоичным

шифратором

называют

кодирующее

устройство, преобразующее код «1 из N» в двоичный

код.

• Из всех 2m входов шифратора активный уровень должен

быть только на одном, номер которого равен двоичному

числу на выходе CD. На всех остальных входах

шифратора уровни напряжения должны быть

неактивные.

10

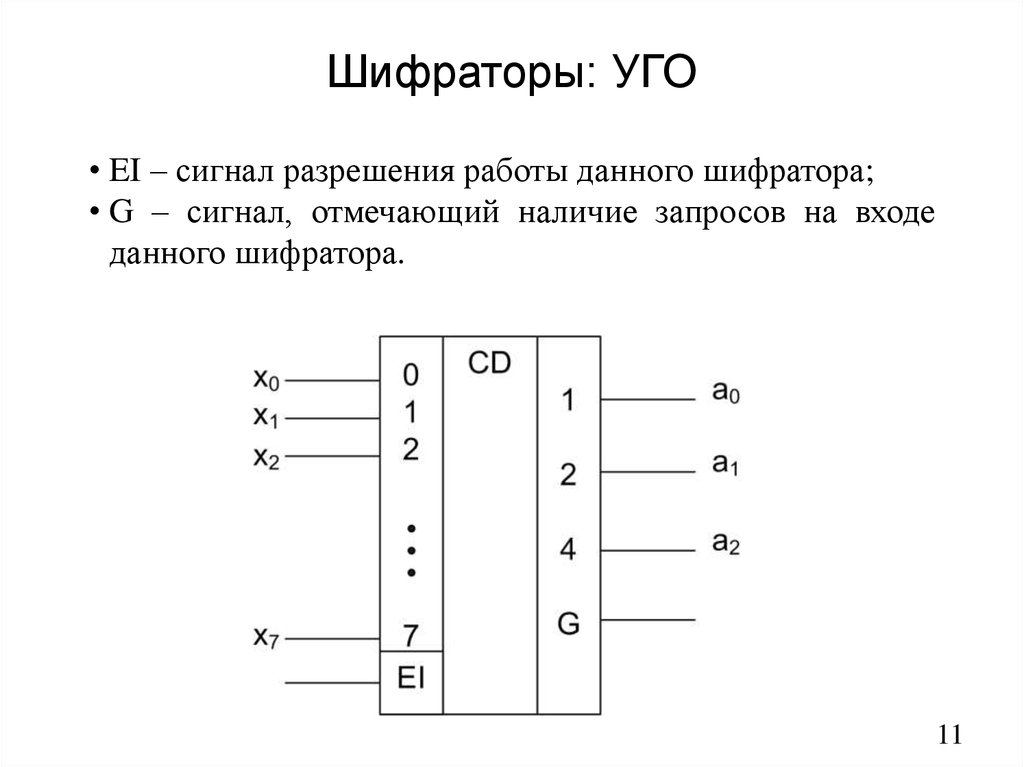

11. Шифраторы: УГО

• EI – сигнал разрешения работы данного шифратора;• G – сигнал, отмечающий наличие запросов на входе

данного шифратора.

11

12. Шифраторы: таблица функционирования

EI1

1

1

1

1

1

1

1

1

0

Входы

X7 X6 X5 X4 X3

1 0 0 0 0

0 1 0 0 0

0 0 1 0 0

0 0 0 1 0

0 0 0 0 1

0 0 0 0 0

0 0 0 0 0

0 0 0 0 0

0 0 0 0 0

Х Х Х Х Х

Выходы

X2 X1 X0 а2 а1 а0 G

0 0 0 1 1 1 1

0 0 0 1 1 0 1

0 0 0 1 0 1 1

0 0 0 1 0 0 1

0 0 0 0 1 1 1

1 0 0 0 1 0 1

0 1 0 0 0 1 1

0 0 1 0 0 0 1

0 0 0 0 0 0 0

Х Х Х 0 0 0 0

• При наличии на входе двух 1 – на выходе либо нули,

либо дизъюнкция разных состояний в зависимости от

реализации CD.

12

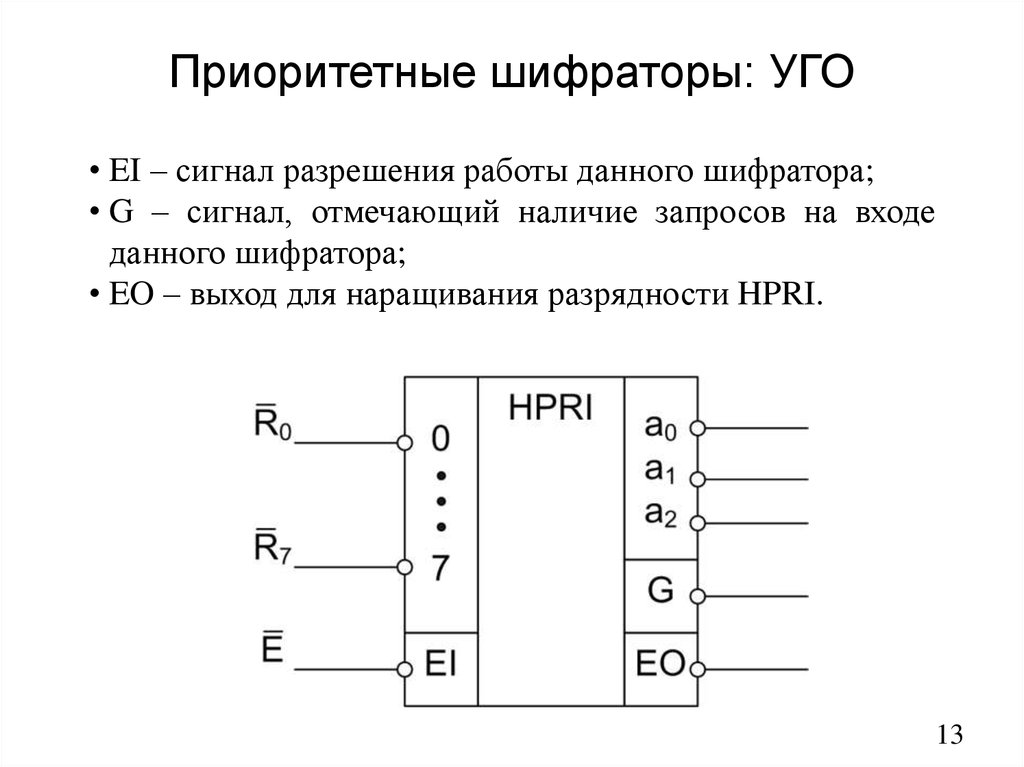

13. Приоритетные шифраторы: УГО

• EI – сигнал разрешения работы данного шифратора;• G – сигнал, отмечающий наличие запросов на входе

данного шифратора;

• EO – выход для наращивания разрядности HPRI.

13

14. Приоритетные шифраторы: таблица функционирования

ВходыEI R7 R6 R5 R4 R3

1 1 X X X X

1 0 1 X X X

1 0 0 1 X X

1 0 0 0 1 X

1 0 0 0 0 1

1 0 0 0 0 0

1 0 0 0 0 0

1 0 0 0 0 0

1 0 0 0 0 0

0 Х Х Х Х Х

Выходы

R2 R1 R0 а2 а1 а0 G

X X X 1 1 1 1

X X X 1 1 0 1

X X X 1 0 1 1

X X X 1 0 0 1

X X X 0 1 1 1

1 X X 0 1 0 1

0 1 X 0 0 1 1

0 0 1 0 0 0 1

0 0 0 0 0 0 0

Х Х Х 0 0 0 0

EO

0

0

0

0

0

0

0

0

1

0

14

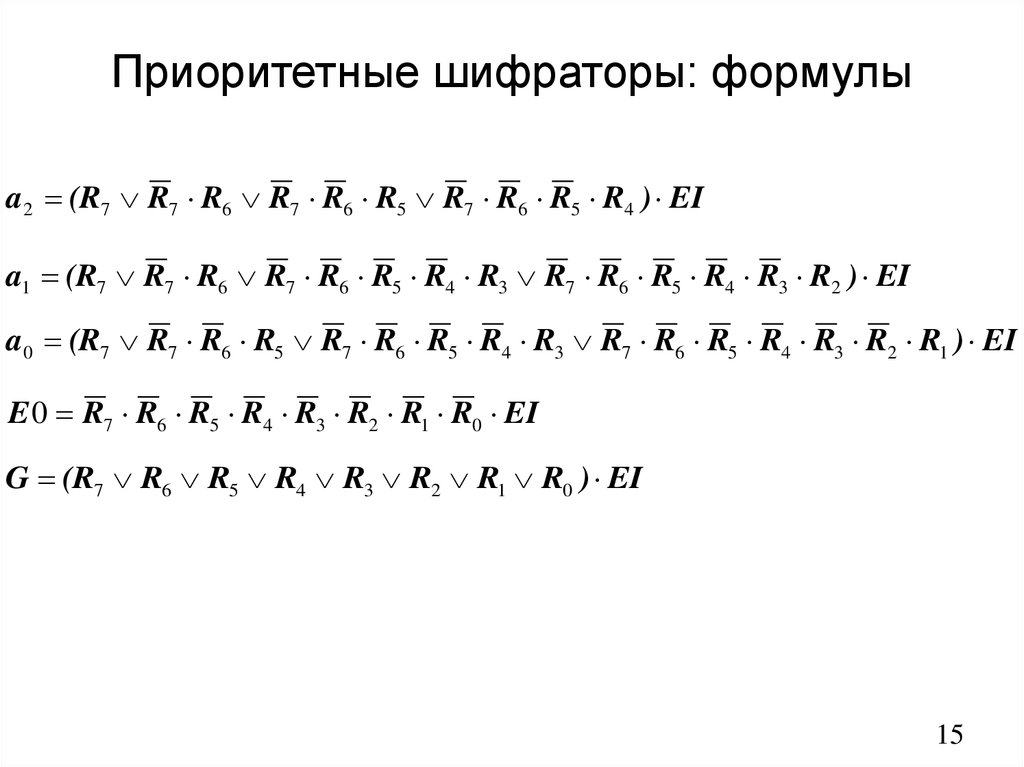

15. Приоритетные шифраторы: формулы

a 2 (R7 R7 R6 R7 R6 R5 R7 R6 R5 R4 ) EIa1 (R7 R7 R6 R7 R6 R5 R4 R3 R7 R6 R5 R4 R3 R2 ) EI

a0 (R7 R7 R6 R5 R7 R6 R5 R4 R3 R7 R6 R5 R4 R3 R2 R1 ) EI

E 0 R7 R6 R5 R4 R3 R2 R1 R0 EI

G (R7 R6 R5 R4 R3 R2 R1 R0 ) EI

15

16. Указатели старшей единицы

• Указатели старшей единицы решают ту же задачу, что иприоритетные шифраторы, но вырабатывают результат

в виде кода «1 из N».

• Число входов в этом случае равно числу выходов

схемы.

• Указатели старшей единицы могут быть реализованы

подключением двоичного дешифратора к выходу

шифратора приоритета.

16

17. Указатели старшей единицы: схема

1718. УСЕ: таблица функционирования

EI1

1

1

1

1

1

1

1

1

0

Входы

X7 X6 X5 X4 X3

1 X X X X

0 1 X X X

0 0 1 X X

0 0 0 1 X

0 0 0 0 1

0 0 0 0 0

0 0 0 0 0

0 0 0 0 0

0 0 0 0 0

Х Х Х Х Х

Выходы

X2 X1 X0 F7 F6 F5 F4 F3 F2

X X X 1 0 0 0 0 0

X X X 0 1 0 0 0 0

X X X 0 0 1 0 0 0

X X X 0 0 0 1 0 0

X X X 0 0 0 0 1 0

1 X X 0 0 0 0 0 1

0 1 X 0 0 0 0 0 0

0 0 1 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0

Х Х Х 0 0 0 0 0 0

F1

0

0

0

0

0

0

1

0

0

0

F0

0

0

0

0

0

0

0

1

0

0

18

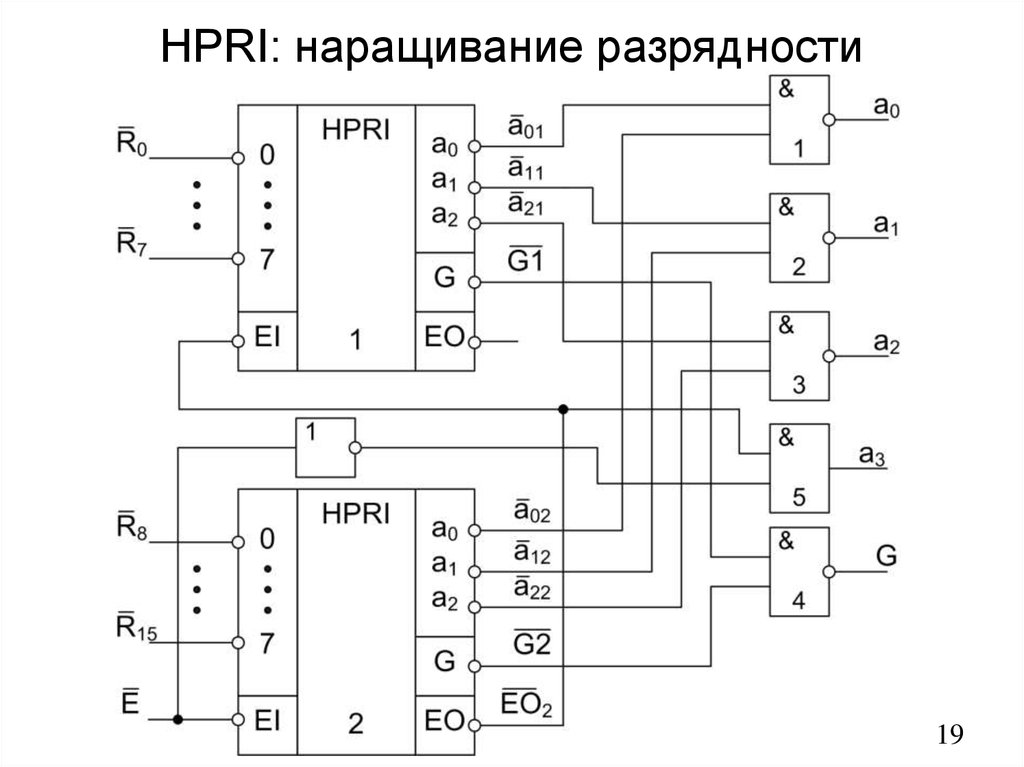

19. HPRI: наращивание разрядности

1920. Лекция №8 Функциональные узлы комбинационного типа. Дешифраторы. Шифраторы. Приоритетные шифраторы. Указатели старшей единицы

НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИСТЕТ

Схемотехника ЭВМ

Лекция №8

Функциональные узлы комбинационного типа.

Дешифраторы. Шифраторы. Приоритетные

шифраторы. Указатели старшей единицы

Мальчуков Андрей Николаевич

Томск – 2014

Электроника

Электроника