Похожие презентации:

Design For Test

1. Design For Test

Professor: Sci.D., ProfessorVazgen Melikyan

1

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

2. Course Overview

IntroductionApproximately 2 lectures

Scan Testing

Built-in Self Testing

Approximately 4 lectures

Approximately 5 lectures

Boundary Scan Testing

Approximately 5 lectures

2

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

3. Built-in Self Testing

3Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

4. Built-in Self-test

Built-in self-test lets blocks test themselvesGeneration of pseudo-random inputs to combinational

logic

Combination of outputs into a syndrome

With high probability, block is fault-free if it produces

the expected syndrome

4

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

5. Economics: BIST Costs

Chip area overhead for:Test controller

Hardware pattern generator

Hardware response compacter

Testing of BIST hardware

Pin overhead: at least 1 pin needed to activate BIST operation

Performance overhead: extra path delays due to BIST

Yield loss: due to increased chip area or more chips in system

because of BIST

Reliability reduction: due to increased area

Increased BIST hardware complexity: happens when BIST

hardware is made testable

5

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

6. BIST Benefits

Faults testedSingle combinational / sequential stuck-at faults

Delay faults

Single stuck-at faults in BIST hardware

BIST benefits

Reduced testing and maintenance cost

Lower test generation cost

Reduced storage / maintenance of test patterns

Simpler and less expensive ATE

Can test many units in parallel

Shorter test application times

Can test at functional system speed.

6

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

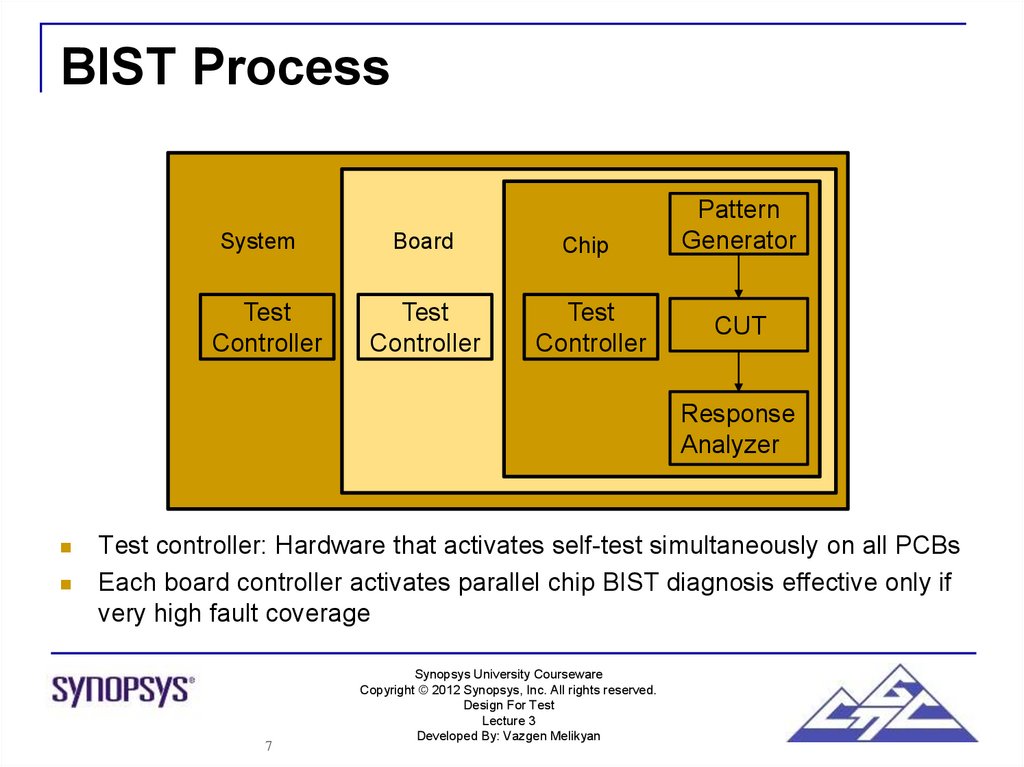

7. BIST Process

SystemBoard

Chip

Test

Controller

Test

Controller

Test

Controller

Pattern

Generator

CUT

Response

Analyzer

Test controller: Hardware that activates self-test simultaneously on all PCBs

Each board controller activates parallel chip BIST diagnosis effective only if

very high fault coverage

7

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

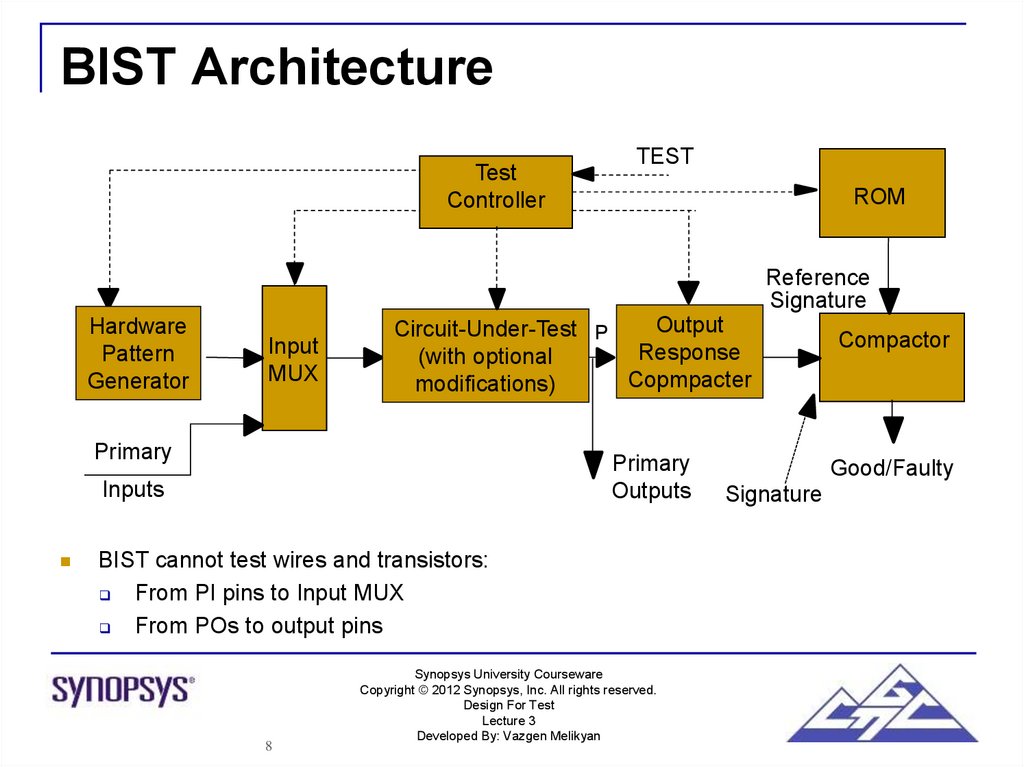

8. BIST Architecture

TestController

TEST

ROM

Reference

Signature

Hardware

Pattern

Generator

Input

MUX

Output

Circuit-Under-Test P

Response

(with optional

Copmpacter

modifications)

Primary

Primary

Outputs

Inputs

BIST cannot test wires and transistors:

From PI pins to Input MUX

From POs to output pins

8

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

Compactor

Good/Faulty

Signature

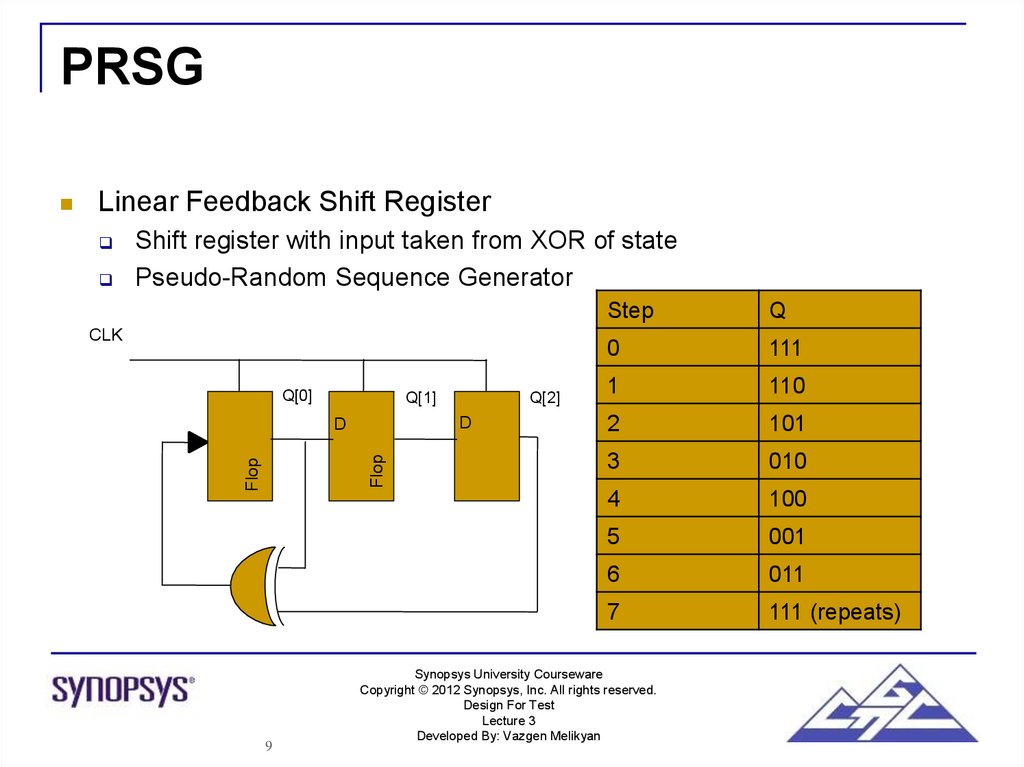

9. PRSG

Linear Feedback Shift RegisterShift register with input taken from XOR of state

Pseudo-Random Sequence Generator

CLK

Q[0]

Flop

D

Flop

9

Q[2]

Q[1]

D

D

Flop

Step

Q

0

111

1

110

2

101

3

010

4

100

5

001

6

011

7

111 (repeats)

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

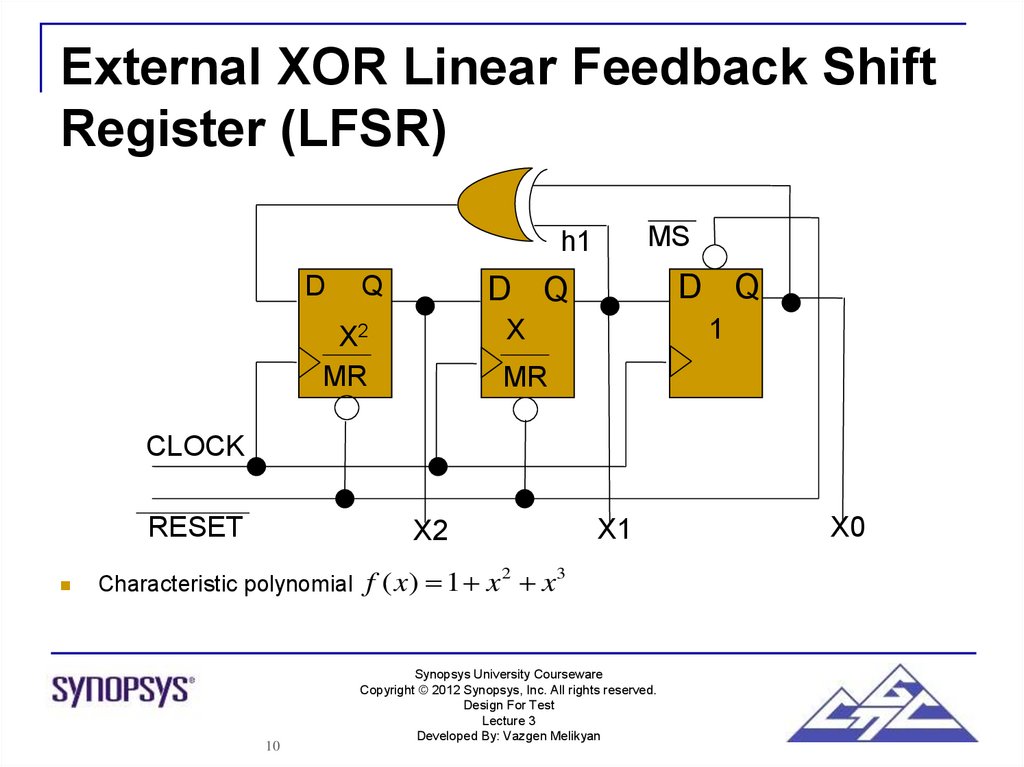

10. External XOR Linear Feedback Shift Register (LFSR)

MSh1

D

Q

X2

MR

D Q

D Q

X

1

MR

CLOCK

RESET

X1

X2

Characteristic polynomial f ( x) 1 x x

2

10

3

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

X0

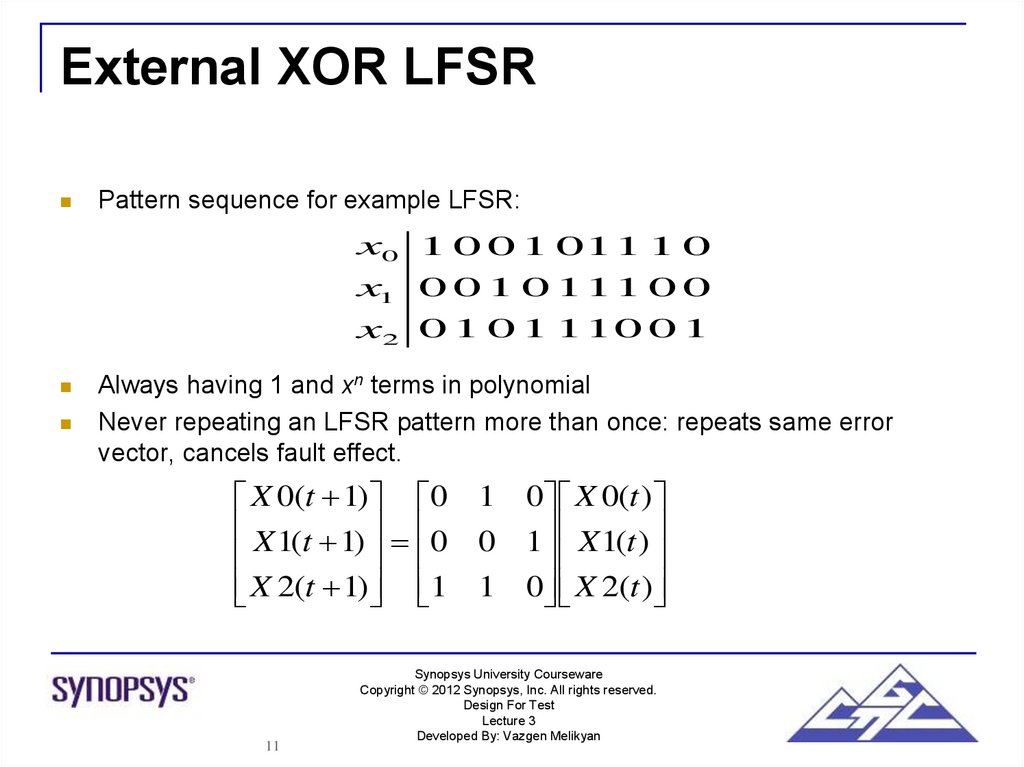

11. External XOR LFSR

Pattern sequence for example LFSR:x0 1 0 0 1 01 1 1 0

x1 0 0 1 0 1 1 1 0 0

x2 0 1 0 1 1 1 0 0 1

Always having 1 and xn terms in polynomial

Never repeating an LFSR pattern more than once: repeats same error

vector, cancels fault effect.

X 0(t 1) 0

X 1(t 1) 0

X 2(t 1) 1

11

1

0

1

0 X 0(t )

1 X 1(t )

0 X 2(t )

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

12. Response Compaction

Severe amounts of data in CUT response toLFSR patterns, for example:

Generation of 5 million random patterns

CUT has 200 outputs

Leads to 5 million x 200 = 1 billion bits response

Uneconomical to store and check all of these

responses on chip

Responses must be compacted

12

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

13. Definitions

Aliasing: due to information loss, signatures of good and some badmachines match

Compaction: drastical reduction of number of bits in original circuit

response – loss of information

Compression: reduction of number of bits in original circuit response

– no information loss – fully invertible (can get back original

response)

Signature analysis: compaction of good machine response into good

machine signature. Actual signature generated during testing, and

compared with good machine signature

13

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

14. LFSR for Response Compaction

Usage of cyclic redundancy check code (CRCC) generator (LFSR)for response compacter

Treating data bits from circuit POs to be compacted as a decreasing

order coefficient polynomial

CRCC divides the PO polynomial by its characteristic polynomial

Leaves remainder of division in LFSR

Must initialize LFSR to seed value (usually 0) before testing

After testing – comparison of signature in LFSR to known good

machine signature

Critical: Must compute good machine signature

14

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

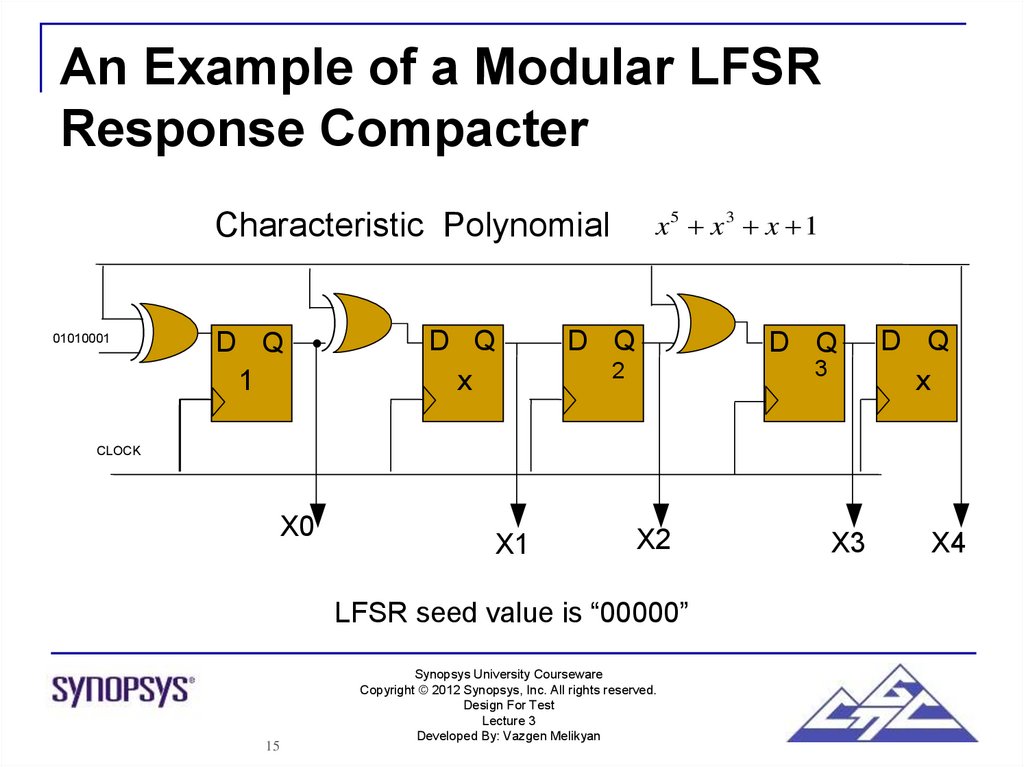

15. An Example of a Modular LFSR Response Compacter

x5 x3 x 1Characteristic Polynomial

01010001

D Q

1

D Q

x

D Q

D Q

2

3

D Q

x

CLOCK

X0

X1

X2

LFSR seed value is “00000”

15

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

X3

X4

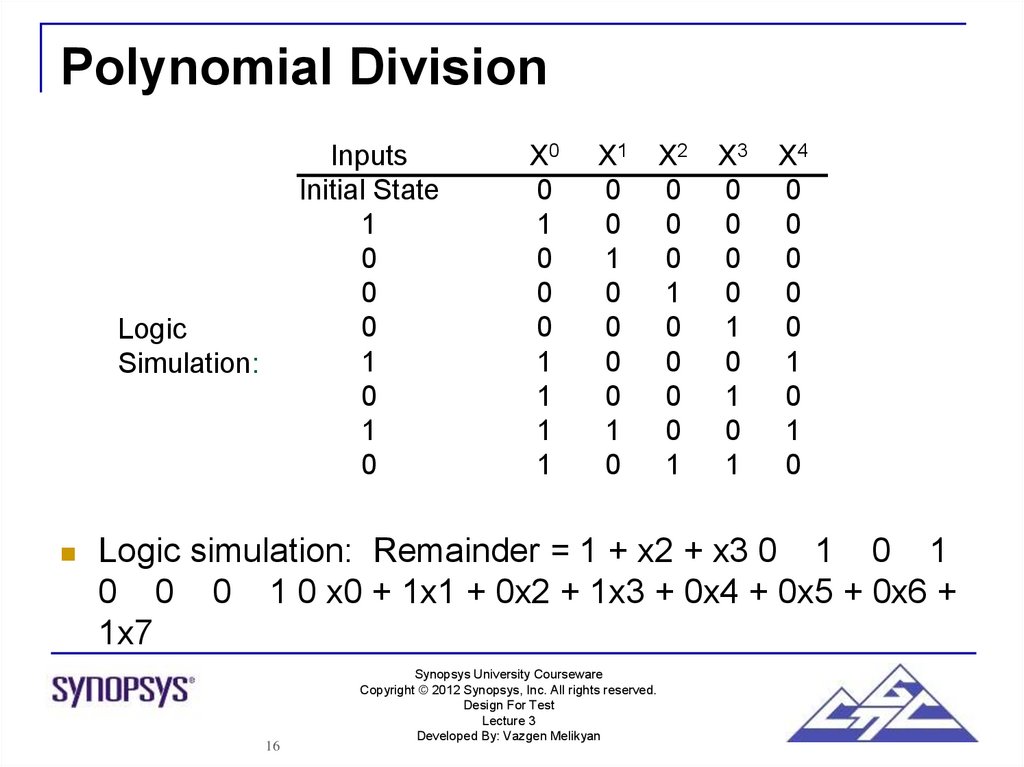

16. Polynomial Division

InputsInitial State

1

0

0

0

1

0

1

0

Logic

Simulation:

X0

0

1

0

0

0

1

1

1

1

X1

0

0

1

0

0

0

0

1

0

X2

0

0

0

1

0

0

0

0

1

X3

0

0

0

0

1

0

1

0

1

X4

0

0

0

0

0

1

0

1

0

Logic simulation: Remainder = 1 + x2 + x3 0 1 0 1

0 0 0 1 0 x0 + 1x1 + 0x2 + 1x3 + 0x4 + 0x5 + 0x6 +

1x7

16

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

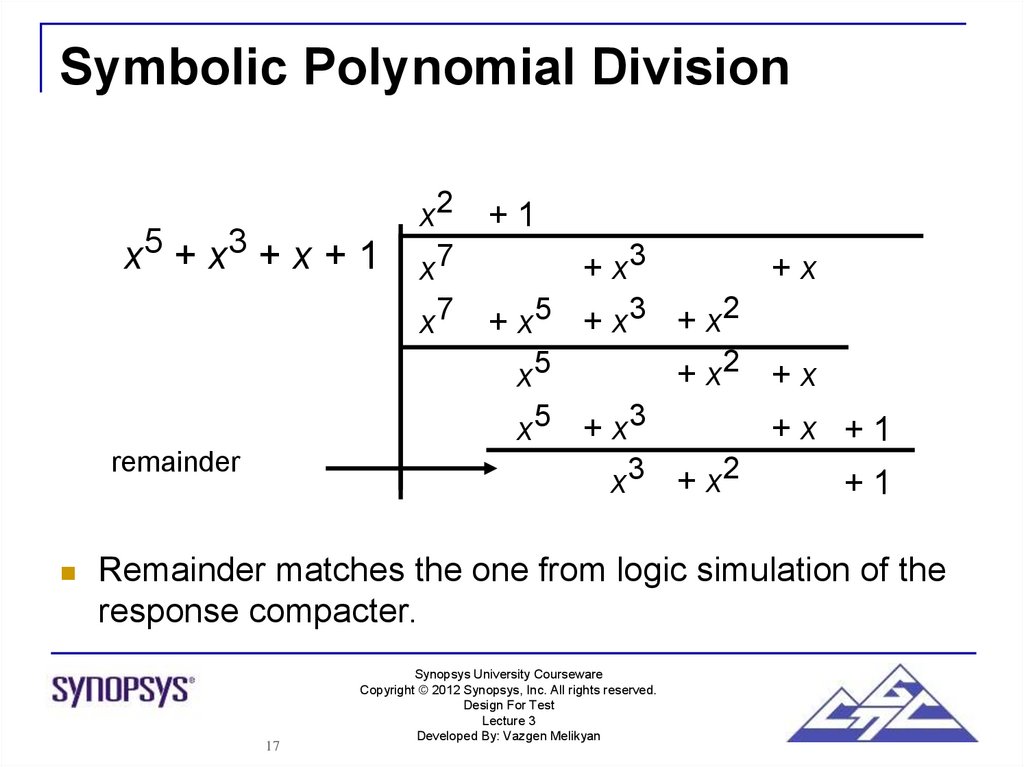

17. Symbolic Polynomial Division

x2x5 + x3 + x + 1 x7

x7

+1

+ x3

+x

+ x5 + x3 + x2

+ x2 + x

x5

x5 + x3

remainder

x3 + x2

+x +1

+1

Remainder matches the one from logic simulation of the

response compacter.

17

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

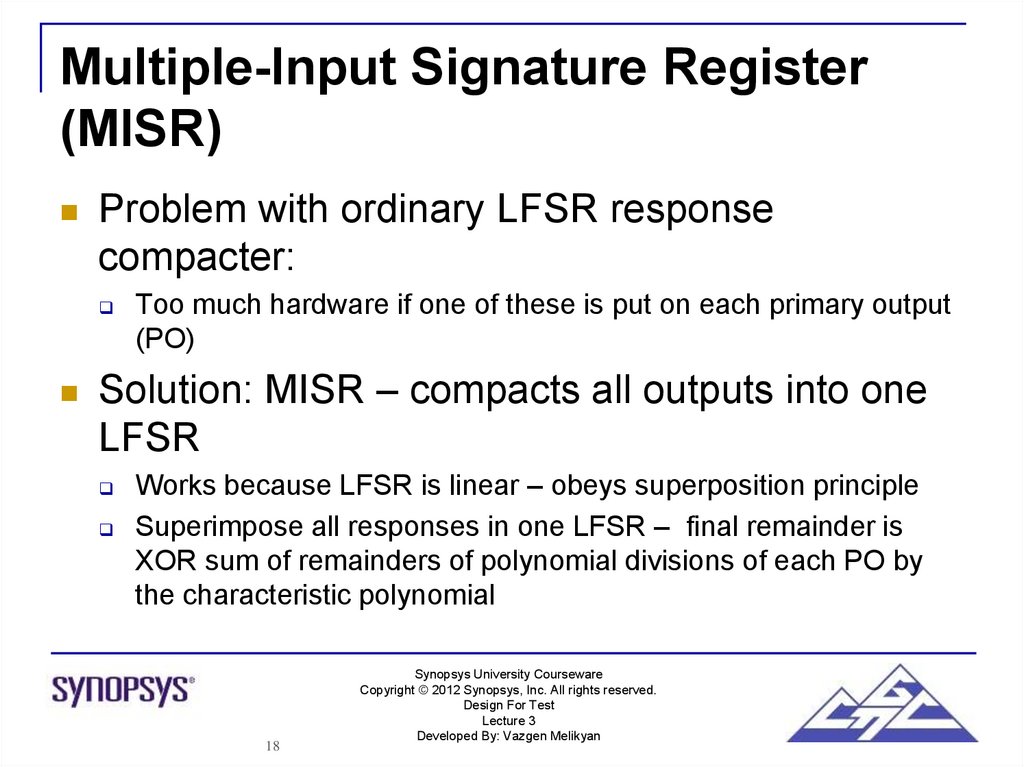

18. Multiple-Input Signature Register (MISR)

Problem with ordinary LFSR responsecompacter:

Too much hardware if one of these is put on each primary output

(PO)

Solution: MISR – compacts all outputs into one

LFSR

Works because LFSR is linear – obeys superposition principle

Superimpose all responses in one LFSR – final remainder is

XOR sum of remainders of polynomial divisions of each PO by

the characteristic polynomial

18

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

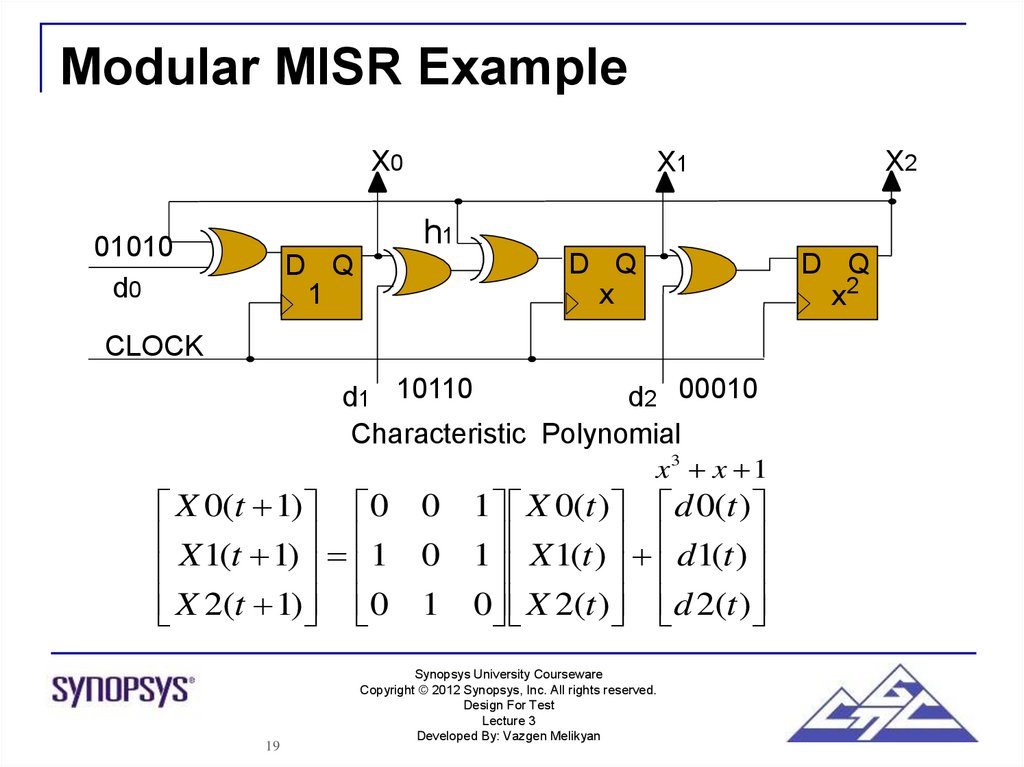

19. Modular MISR Example

X0X2

X1

h1

01010

d0

D Q

1

D Q

x

D Q

x2

CLOCK

d1 10110

d2 00010

Characteristic Polynomial

x3 x 1

X 0(t 1) 0 0 1 X 0(t ) d 0(t )

X 1(t 1) 1 0 1 X 1(t ) d1(t )

X 2(t 1) 0 1 0 X 2(t ) d 2(t )

19

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

20. Aliasing Theorem

Theorem: Assuming that each PO dij hasprobability pj of being in error, where the pj

probabilities are independent, and that all

outputs dij are independent, in a k-bit MISR,

Pal = 1/(2k), regardless of the initial

condition.

20

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

21. Circuit Initialization

Full-scan BIST – shift in scan chain seed beforestarting BIST

Partial-scan BIST – critical to initialize all FFs

before BIST starts

Otherwise X’s are clocked into MISR and signature is not unique

and not repeatable

Discovering initialization problems by:

Modeling all BIST hardware

Setting all FFs to X’s

Running logic simulation of CUT with BIST hardware

21

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

22. Circuit Initialization (2)

If MISR finishes with BIST cycle with X’s in signature,DFT initialization hardware must be added

Adding MS (master set) or MR (master reset) lines on

flip-flops and exciting them before BIST starts

Otherwise:

All cycles of FF’s are broken

A partial BIST synchronizing sequence is applied to initialize all FF’s

The MISR is turned on to compact the response.

22

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

23. Test Point Insertion

BIST does not detect all faults:Test patterns are not rich enough to test all faults

Modification of a circuit after synthesis to

improve signal controllability

Observability addition – routing internal signal

to extra FF in MISR or XOR into existing FF

in MISR

23

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

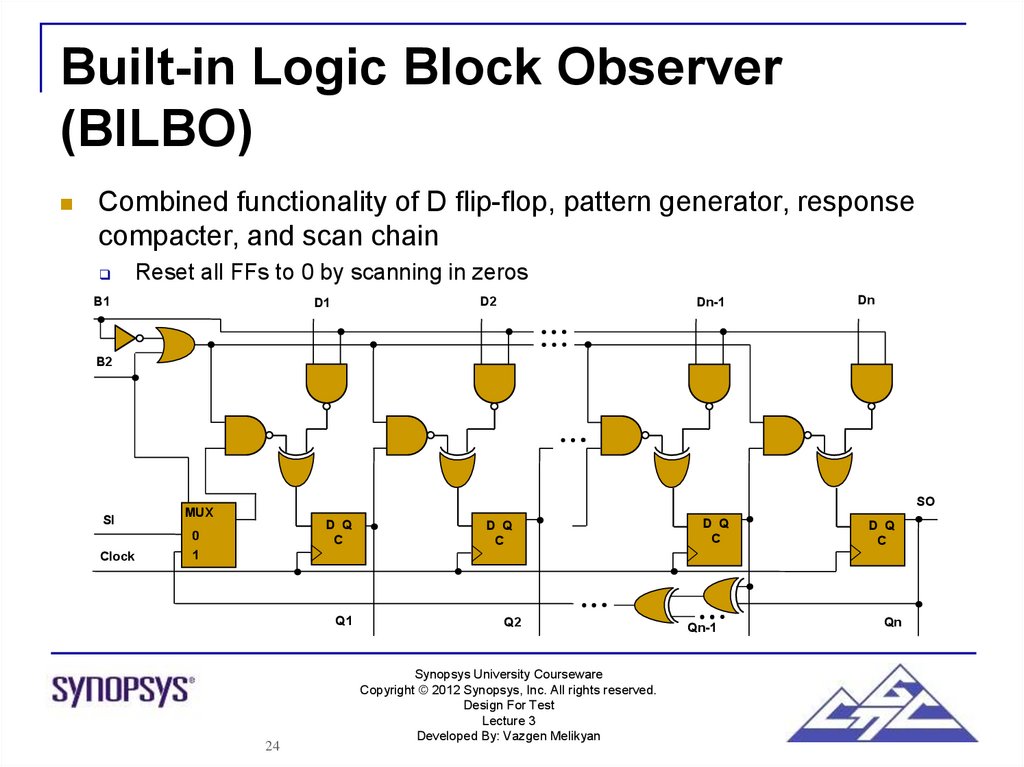

24. Built-in Logic Block Observer (BILBO)

Combined functionality of D flip-flop, pattern generator, responsecompacter, and scan chain

Reset all FFs to 0 by scanning in zeros

B1

D2

D1

Dn-1

Dn

B2

SI

Clock

SO

MUX

0

1

24

D Q

C

D Q

C

Q1

Q2

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

D Q

C

Qn-1

D Q

C

Qn

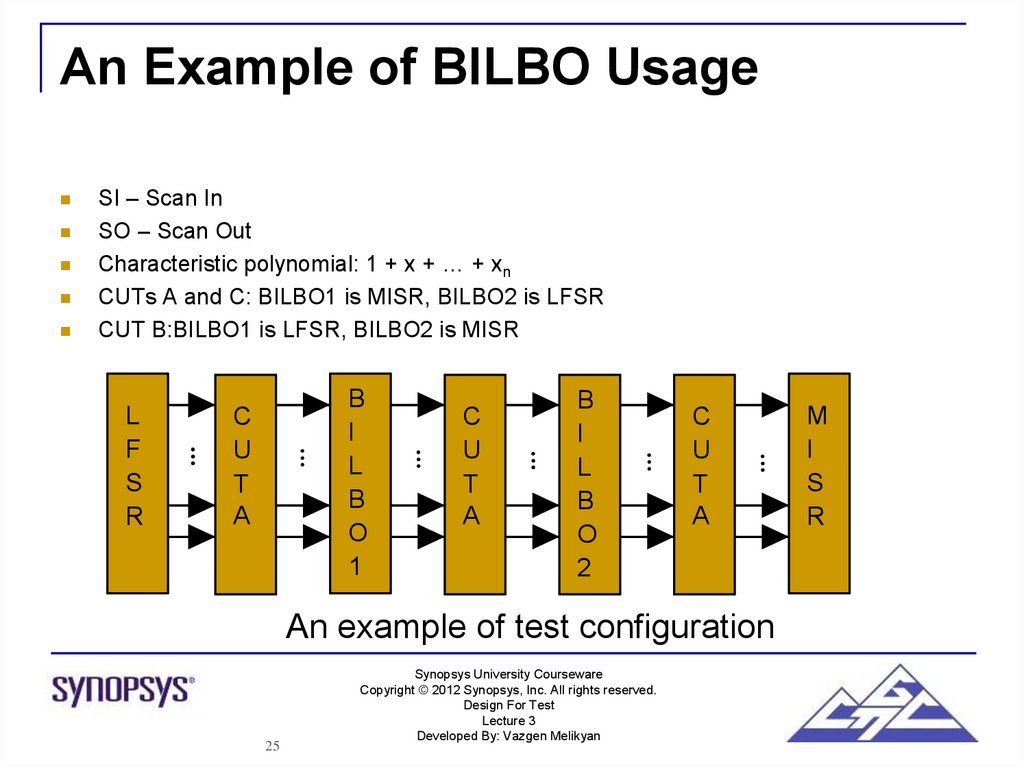

25. An Example of BILBO Usage

SI – Scan InSO – Scan Out

Characteristic polynomial: 1 + x + … + xn

CUTs A and C: BILBO1 is MISR, BILBO2 is LFSR

CUT B:BILBO1 is LFSR, BILBO2 is MISR

L

F

S

R

B

I

L

B

O

1

C

U

T

A

C

U

T

A

B

I

L

B

O

2

C

U

T

A

An example of test configuration

25

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

M

I

S

R

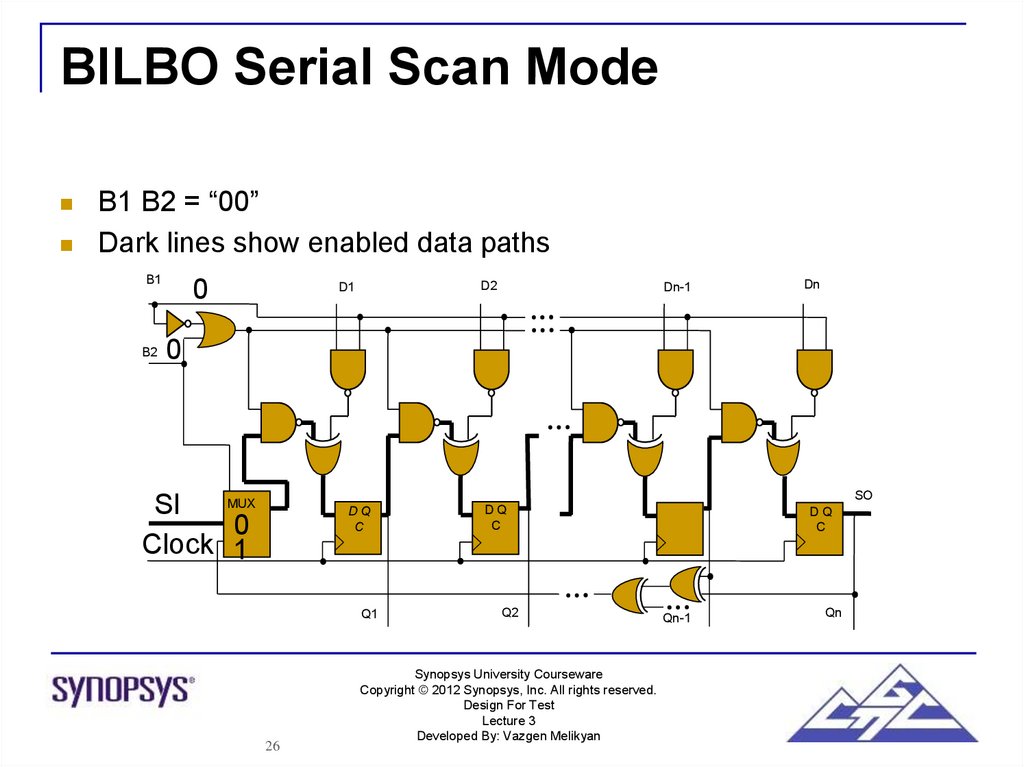

26. BILBO Serial Scan Mode

B1 B2 = “00”Dark lines show enabled data paths

B1

B2

0

D1

D2

Dn-1

Dn

DQ

C

DQ

C

DQ

C

0

SO

MUX

SI

0

Clock 1

DQ

C

Q1

26

Q2

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

Qn-1

Qn

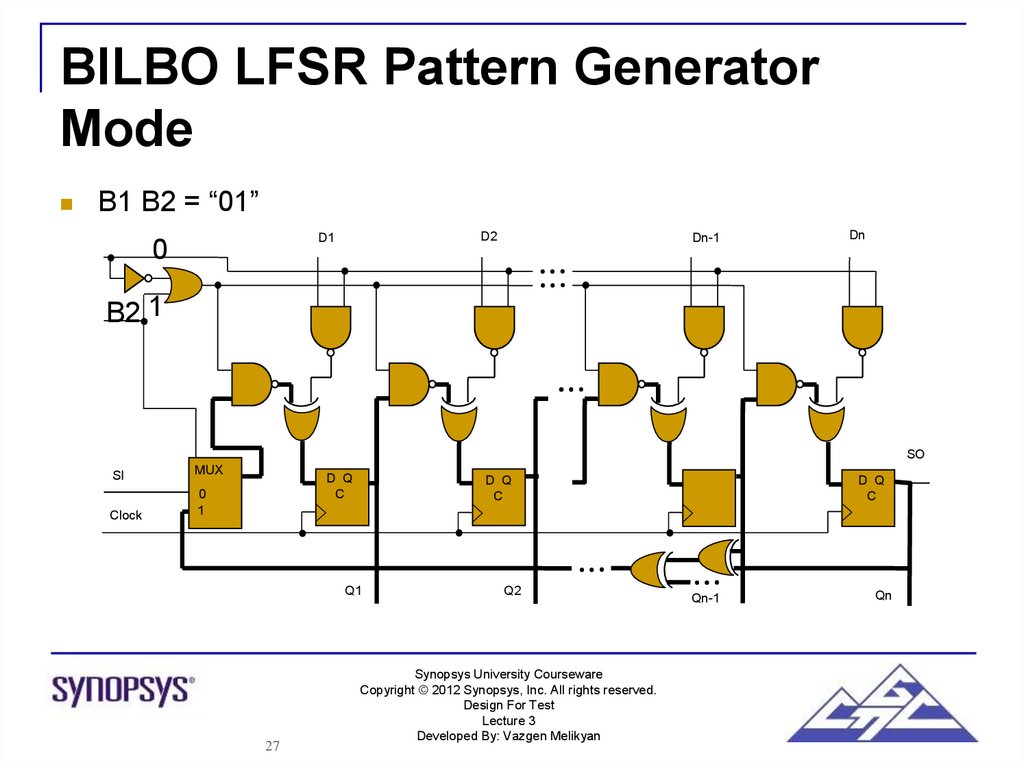

27. BILBO LFSR Pattern Generator Mode

B1 B2 = “01”D2

D1

0

Dn-1

Dn

B2 1

SO

SI

MUX

Clock

0

1

D Q

C

D Q

C

Q1

27

Q2

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

DQ

C

D Q

C

Qn-1

Qn

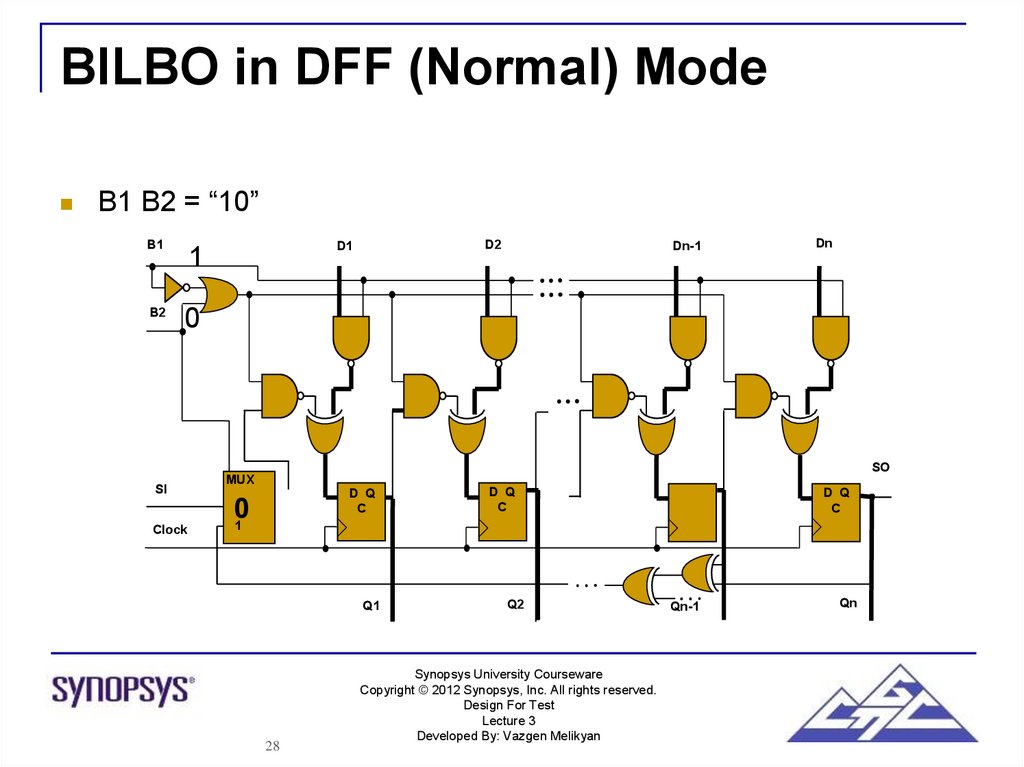

28. BILBO in DFF (Normal) Mode

B1 B2 = “10”B1

B2

D2

D1

1

Dn-1

Dn

0

SO

SI

Clock

MUX

0

1

28

D Q

C

D Q

C

D Q

C

D Q

C

Q1

Q2

Qn-1

Qn

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

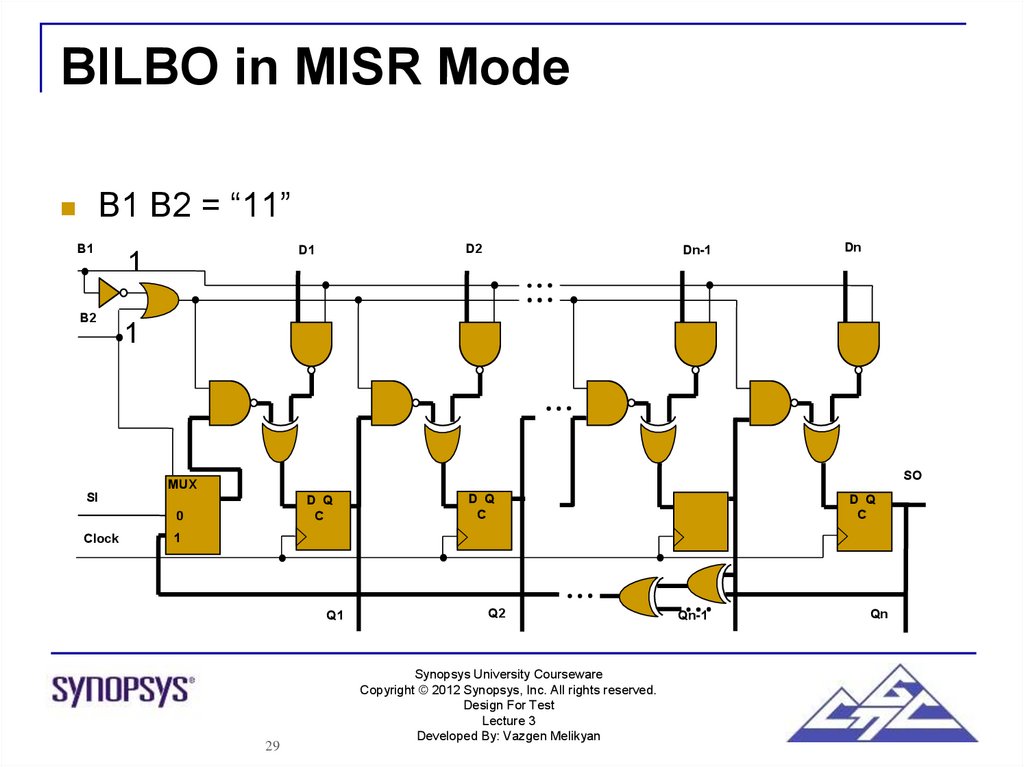

29. BILBO in MISR Mode

B1 B2 = “11”B1

B2

D2

D1

1

Dn-1

Dn

1

SO

MUX

SI

D Q

C

0

Clock

D Q

C

D Q

C

D Q

C

1

Q1

29

Q2

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

Qn-1

Qn

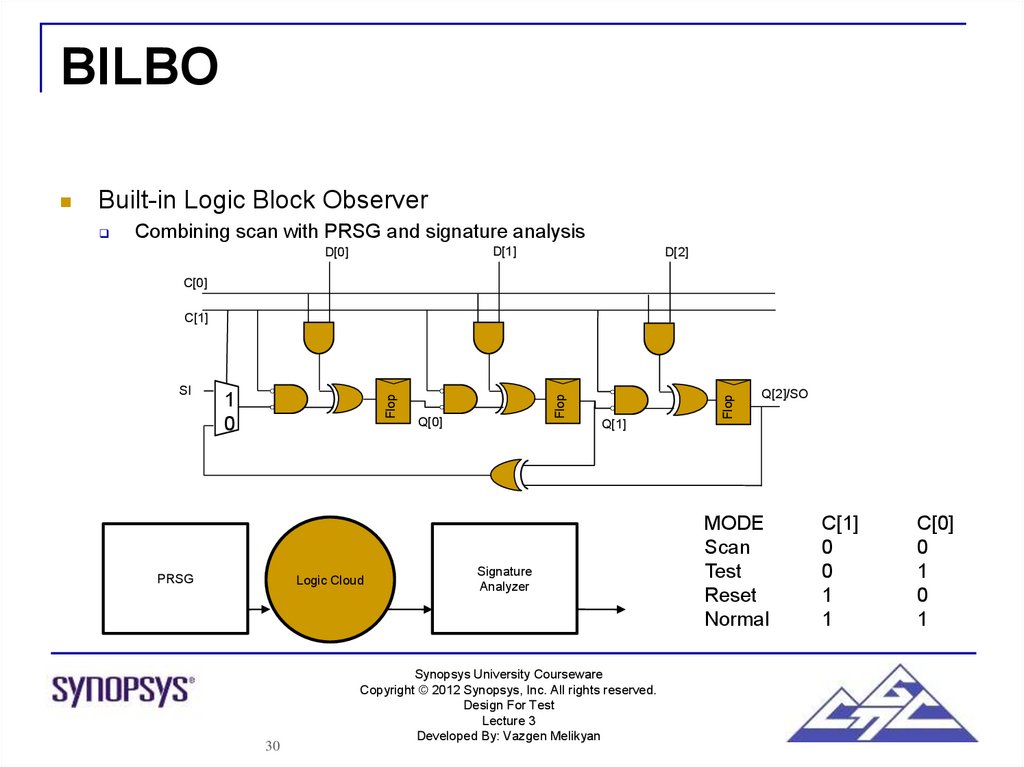

30. BILBO

Built-in Logic Block ObserverCombining scan with PRSG and signature analysis

D[1]

D[0]

D[2]

C[0]

SI

1

0

PRSG

Logic Cloud

30

Q[0]

Q[1]

Signature

Analyzer

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

Flop

C[1]

Flop

Flop

Q[2]/SO

MODE

Scan

Test

Reset

Normal

C[1]

0

0

1

1

C[0]

0

1

0

1

31. Summary

LFSR pattern generator and MISR response compacterBIST benefits:

Preferred BIST methods

At-speed testing for delay & stuck-at faults

Drastic ATE cost reduction

Field test capability

Faster diagnosis during system test

Less effort to design testing process

Shorter test application times

Ability to support testing in different levels(wafer, after packaging, in the board,

after integrating board in the system and during operation)

BIST has overheads: test controller, extra delay, Input MUX, pattern

generator, response compacter, DFT to initialize circuit and test the

test hardware

31

Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

32.

32Synopsys University Courseware

Copyright © 2012 Synopsys, Inc. All rights reserved.

Design For Test

Lecture 3

Developed By: Vazgen Melikyan

Английский язык

Английский язык