Похожие презентации:

Типы шин. Принцип обмена информацией между функциональными узлами

1.

Типы шин.Принцип обмена

информацией между

функциональными узлами

2.

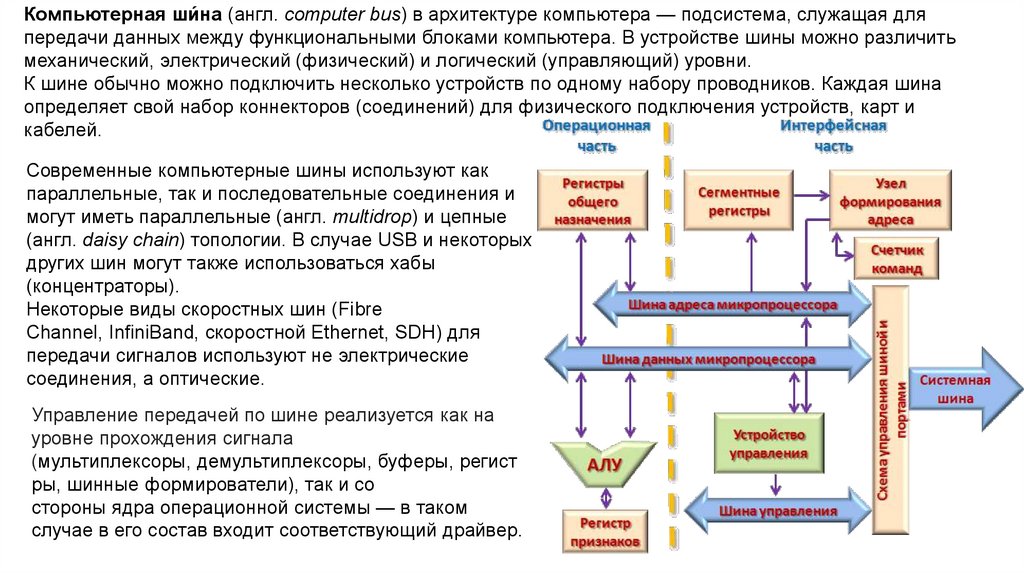

Компьютерная ши́на (англ. computer bus) в архитектуре компьютера — подсистема, служащая дляпередачи данных между функциональными блоками компьютера. В устройстве шины можно различить

механический, электрический (физический) и логический (управляющий) уровни.

К шине обычно можно подключить несколько устройств по одному набору проводников. Каждая шина

определяет свой набор коннекторов (соединений) для физического подключения устройств, карт и

кабелей.

Современные компьютерные шины используют как

параллельные, так и последовательные соединения и

могут иметь параллельные (англ. multidrop) и цепные

(англ. daisy chain) топологии. В случае USB и некоторых

других шин могут также использоваться хабы

(концентраторы).

Некоторые виды скоростных шин (Fibre

Channel, InfiniBand, скоростной Ethernet, SDH) для

передачи сигналов используют не электрические

соединения, а оптические.

Управление передачей по шине реализуется как на

уровне прохождения сигнала

(мультиплексоры, демультиплексоры, буферы, регист

ры, шинные формирователи), так и со

стороны ядра операционной системы — в таком

случае в его состав входит соответствующий драйвер.

3.

Используемые в настоящее время шины отличаются по разрядности, способу передачисигнала (последовательные или параллельные), пропускной способности, количеству и типу

поддерживаемых устройств, а также протоколу работы

Шины могут быть синхронными (осуществляющими передачу данных только по тактовым

импульсам) и асинхронными(осуществляющими передачу данных в произвольные моменты

времени), а также использовать различные схемы арбитража (то есть способа совместного

использования шины несколькими устройствами).

Если обмен информацией ведется между периферийным устройством и контроллером, то

соединяющая их линия передачи данных называется интерфейсом передачи данных , или просто

интерфейсом . Среди применяемых в современных и перспективных ПК интерфейсов можно отметить

EIDE, SCSI, SSA и Fibre Channel, USB, FireWire (IEEE 1394) и DeviceBay.

Среди интерфейсов передачи данных особняком стоят порты ввода/вывода, использующиеся для

подключения низкоскоростных периферийных устройств: последовательный порт (COM),

параллельный порт (LPT), игровой порт/MIDI порт и инфракрасный порт (IrDA) .

Все современные компьютеры располагают комбинированными системными шинами, например, ISA

(Industry Standart Architecture - стандартная промышленная архитектура) и PCI или EISA ( Extanded

Industry Standart Architecture ) и PCI ( Peripheral Component Interconnect ). Одна из шин называется

первичной системной (EISA, ISA), а другая (PCI) вторичной системной.

4.

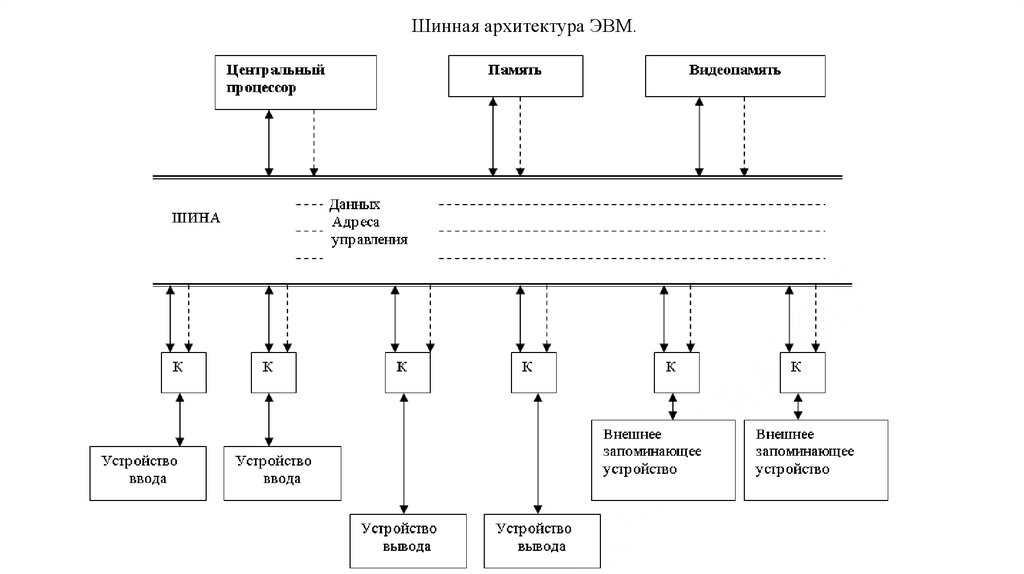

Шинная архитектура ЭВМ.5.

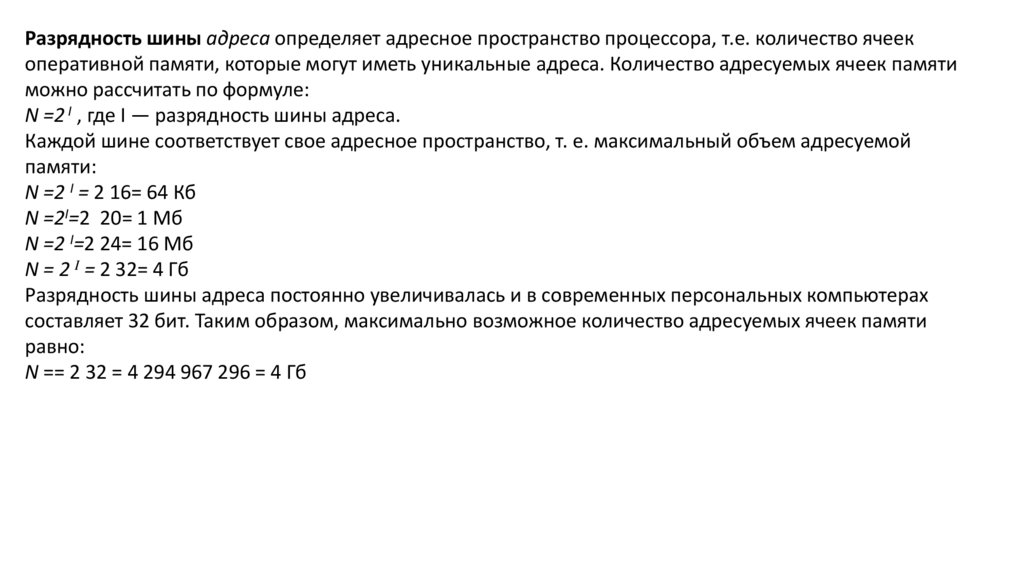

Разрядность шины адреса определяет адресное пространство процессора, т.е. количество ячеекоперативной памяти, которые могут иметь уникальные адреса. Количество адресуемых ячеек памяти

можно рассчитать по формуле:

N =2 I , где I — разрядность шины адреса.

Каждой шине соответствует свое адресное пространство, т. е. максимальный объем адресуемой

памяти:

N =2 I = 2 16= 64 Кб

N =2I=2 20= 1 Мб

N =2 I=2 24= 16 Мб

N = 2 I = 2 32= 4 Гб

Разрядность шины адреса постоянно увеличивалась и в современных персональных компьютерах

составляет 32 бит. Таким образом, максимально возможное количество адресуемых ячеек памяти

равно:

N == 2 32 = 4 294 967 296 = 4 Гб

6.

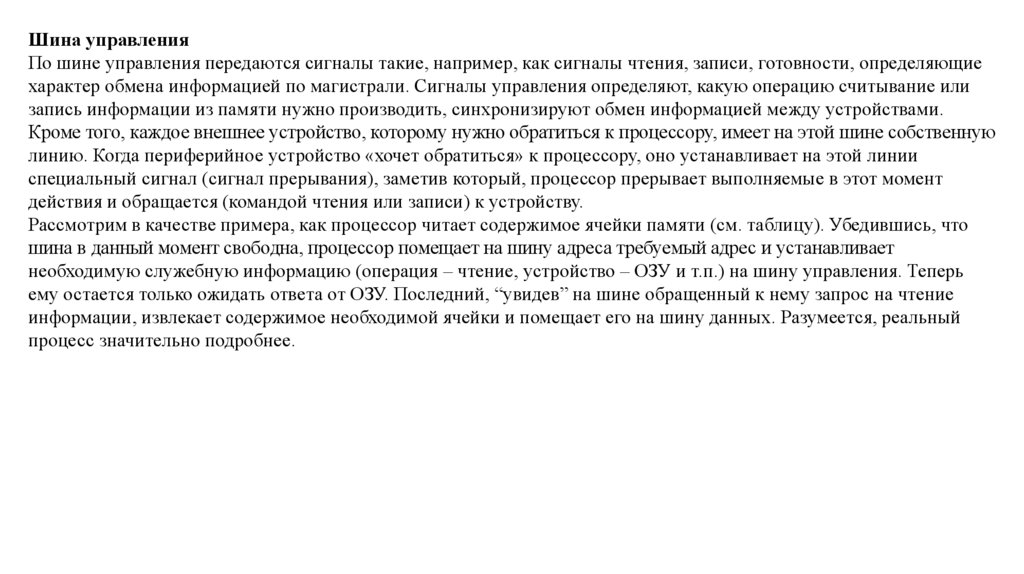

Шина управленияПо шине управления передаются сигналы такие, например, как сигналы чтения, записи, готовности, определяющие

характер обмена информацией по магистрали. Сигналы управления определяют, какую операцию считывание или

запись информации из памяти нужно производить, синхронизируют обмен информацией между устройствами.

Кроме того, каждое внешнее устройство, которому нужно обратиться к процессору, имеет на этой шине собственную

линию. Когда периферийное устройство «хочет обратиться» к процессору, оно устанавливает на этой линии

специальный сигнал (сигнал прерывания), заметив который, процессор прерывает выполняемые в этот момент

действия и обращается (командой чтения или записи) к устройству.

Рассмотрим в качестве примера, как процессор читает содержимое ячейки памяти (см. таблицу). Убедившись, что

шина в данный момент свободна, процессор помещает на шину адреса требуемый адрес и устанавливает

необходимую служебную информацию (операция – чтение, устройство – ОЗУ и т.п.) на шину управления. Теперь

ему остается только ожидать ответа от ОЗУ. Последний, “увидев” на шине обращенный к нему запрос на чтение

информации, извлекает содержимое необходимой ячейки и помещает его на шину данных. Разумеется, реальный

процесс значительно подробнее.

7.

8.

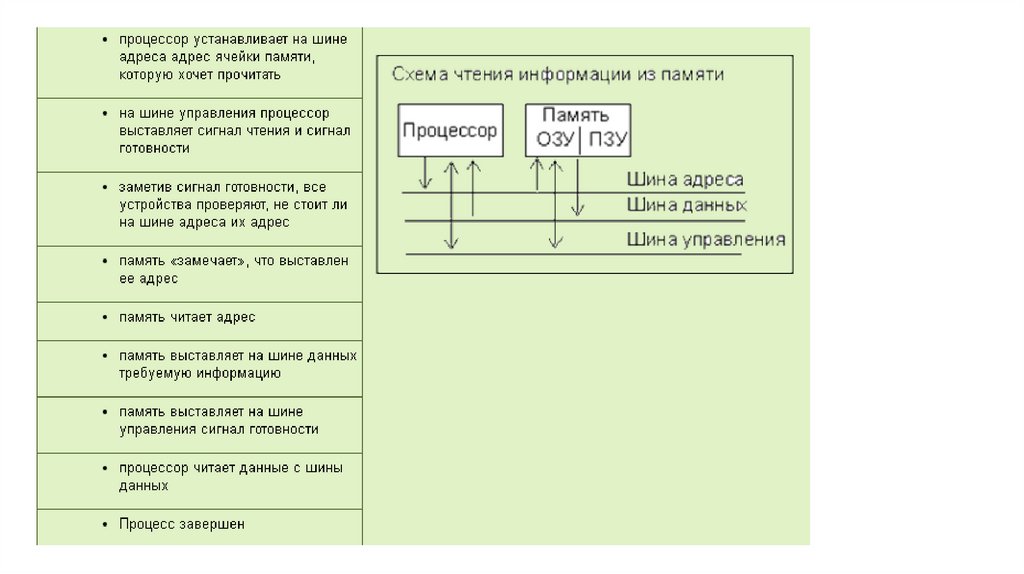

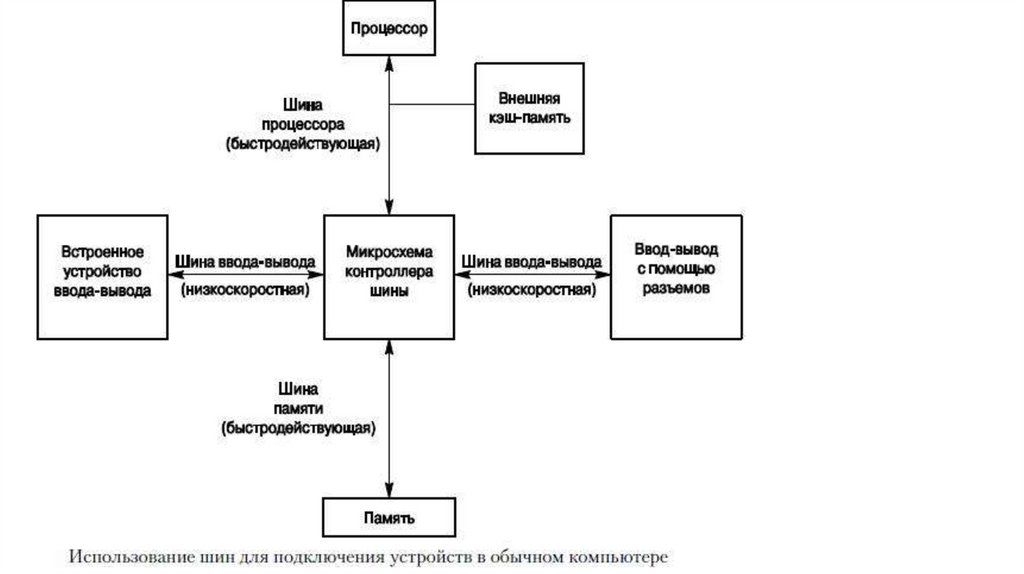

Система шин ЭВМВ вычислительной системе, состоящей из множества подсистем,

необходим механизм для их взаимодействия. Эти подсистемы

должны быстро и эффективно обмениваться данными с

помощью центральной шины или системы нескольких шин.

9.

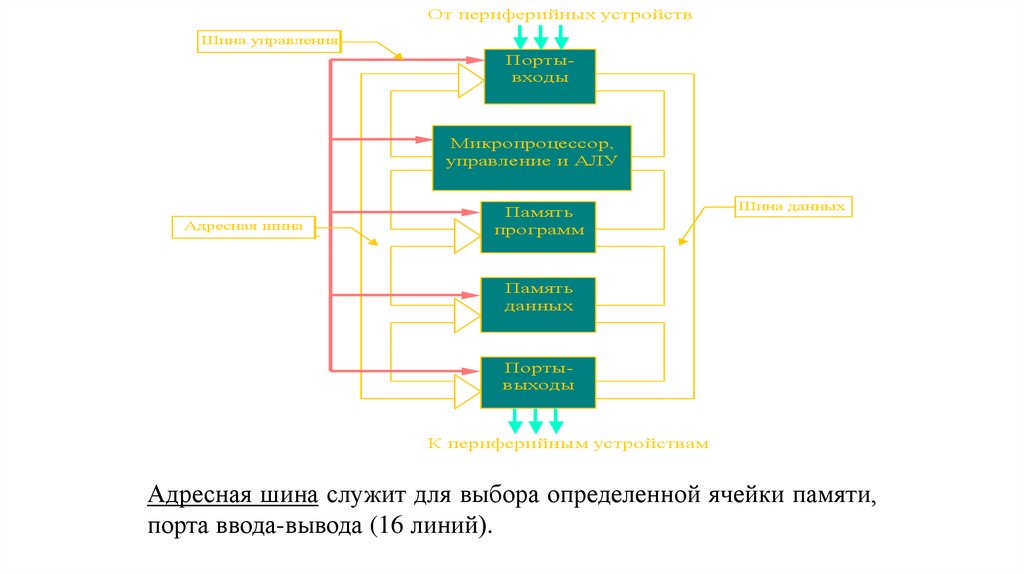

От периферийных устройствШина управления

Портывходы

Микропроцессор,

управление и АЛУ

Адресная шина

Память

программ

Шина данных

Память

данных

Портывыходы

К периферийным устройствам

Адресная шина служит для выбора определенной ячейки памяти,

порта ввода-вывода (16 линий).

10.

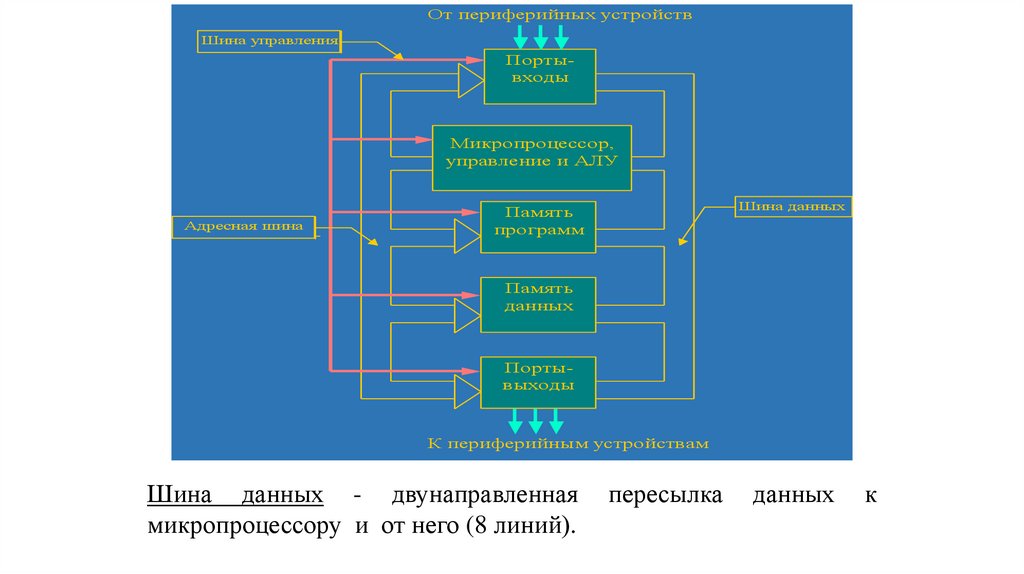

От периферийных устройствШина управления

Портывходы

Микропроцессор,

управление и АЛУ

Адресная шина

Шина данных

Память

программ

Память

данных

Портывыходы

К периферийным устройствам

Шина данных - двунаправленная

микропроцессору и от него (8 линий).

пересылка

данных

к

11.

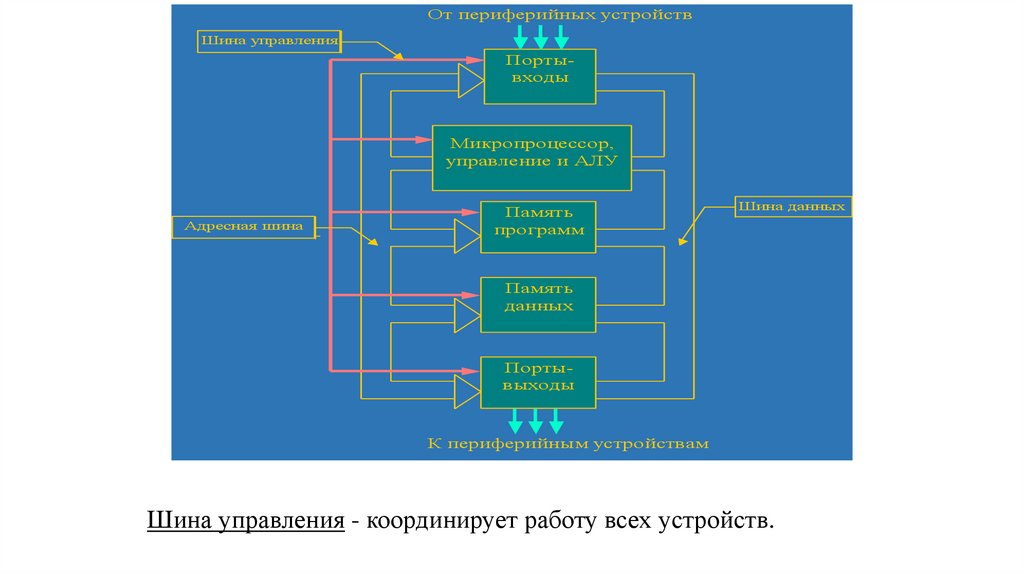

От периферийных устройствШина управления

Портывходы

Микропроцессор,

управление и АЛУ

Адресная шина

Память

программ

Шина данных

Память

данных

Портывыходы

К периферийным устройствам

Шина управления - координирует работу всех устройств.

12.

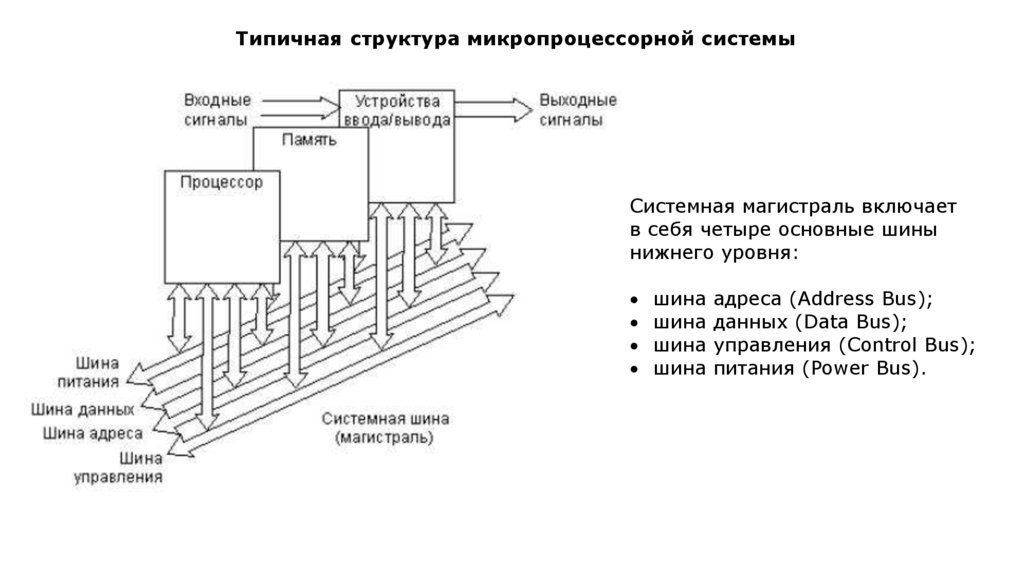

Типичная структура микропроцессорной системыСистемная магистраль включает

в себя четыре основные шины

нижнего уровня:

шина адреса (Address Bus);

шина данных (Data Bus);

шина управления (Control Bus);

шина питания (Power Bus).

13.

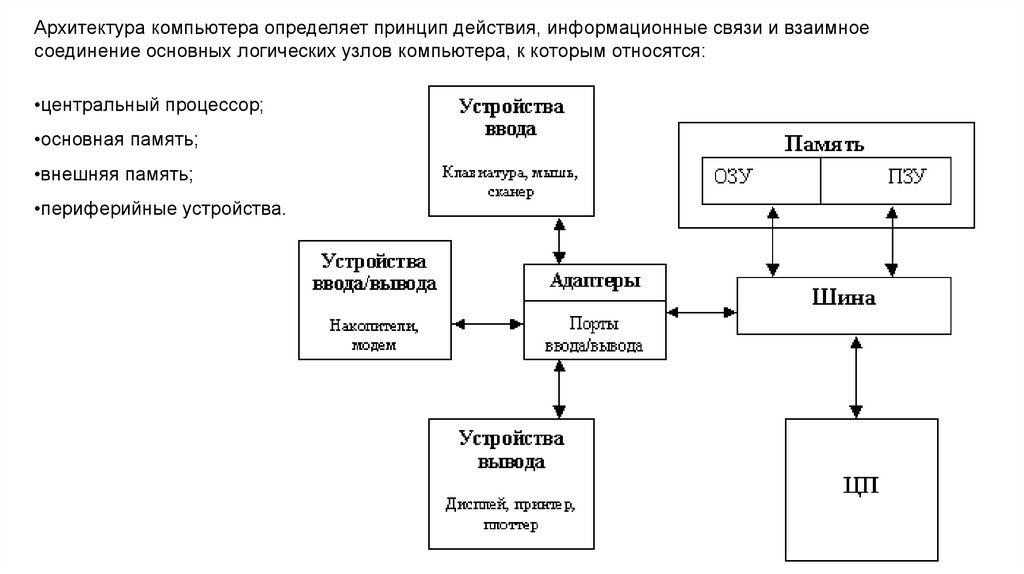

Архитектура компьютера определяет принцип действия, информационные связи и взаимноесоединение основных логических узлов компьютера, к которым относятся:

•центральный процессор;

•основная память;

•внешняя память;

•периферийные устройства.

14.

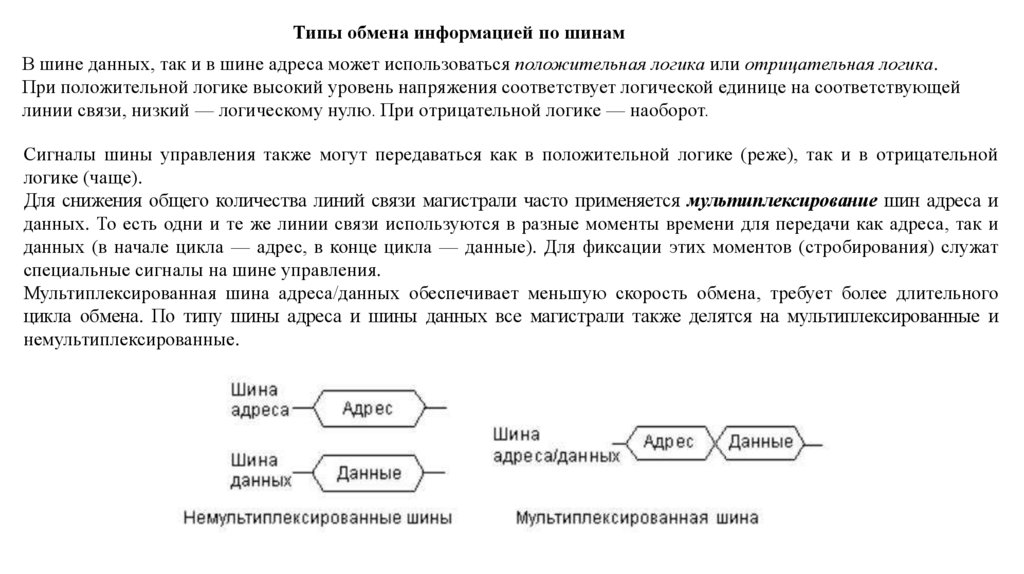

Типы обмена информацией по шинамВ шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика.

При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей

линии связи, низкий — логическому нулю. При отрицательной логике — наоборот.

Сигналы шины управления также могут передаваться как в положительной логике (реже), так и в отрицательной

логике (чаще).

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и

данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и

данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат

специальные сигналы на шине управления.

Мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного

цикла обмена. По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и

немультиплексированные.

15.

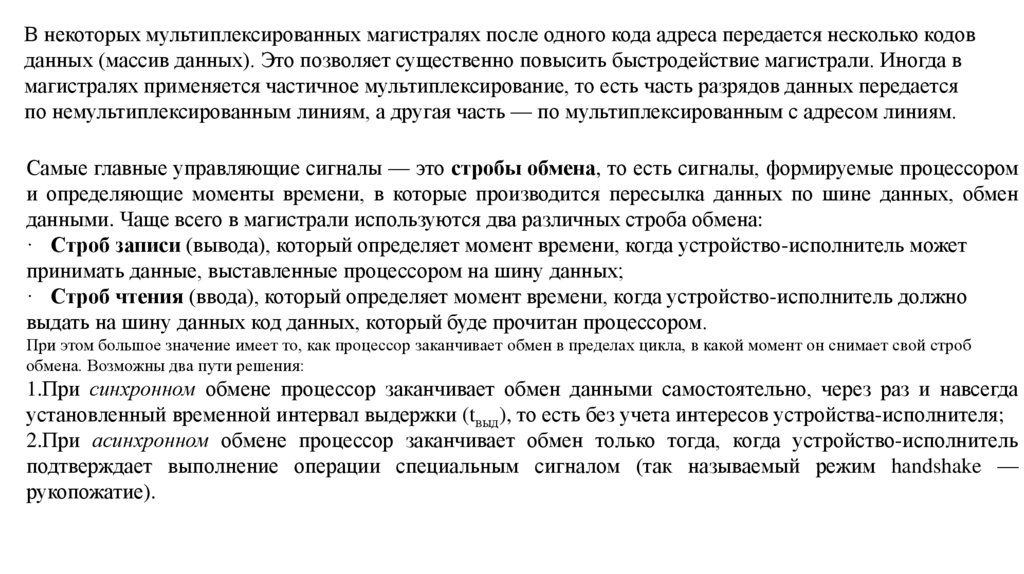

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодовданных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в

магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается

по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором

и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен

данными. Чаще всего в магистрали используются два различных строба обмена:

· Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может

принимать данные, выставленные процессором на шину данных;

· Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно

выдать на шину данных код данных, который буде прочитан процессором.

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб

обмена. Возможны два пути решения:

1.При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда

установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

2.При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель

подтверждает выполнение операции специальным сигналом (так называемый режим handshake —

рукопожатие).

16.

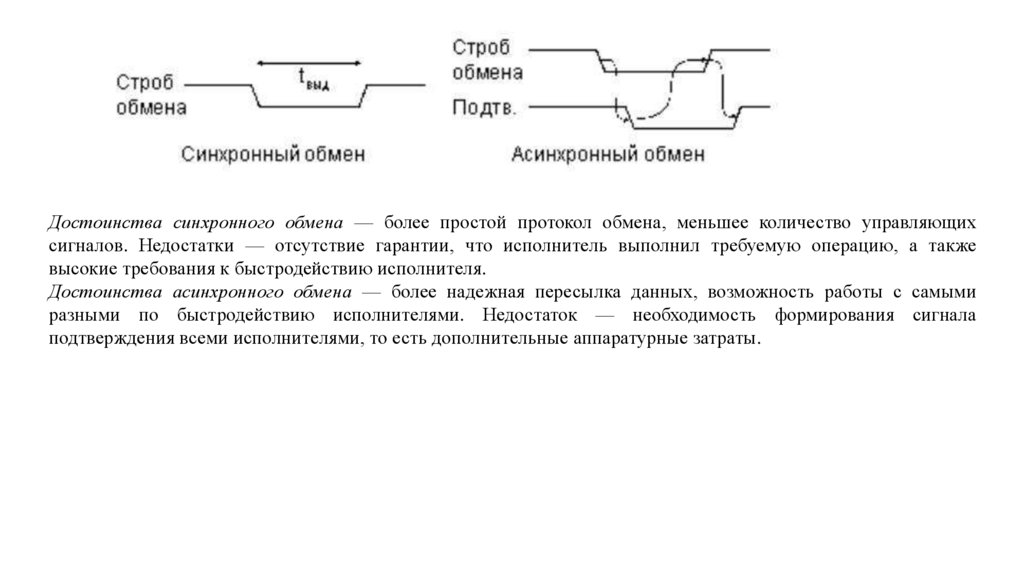

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющихсигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также

высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми

разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала

подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

17.

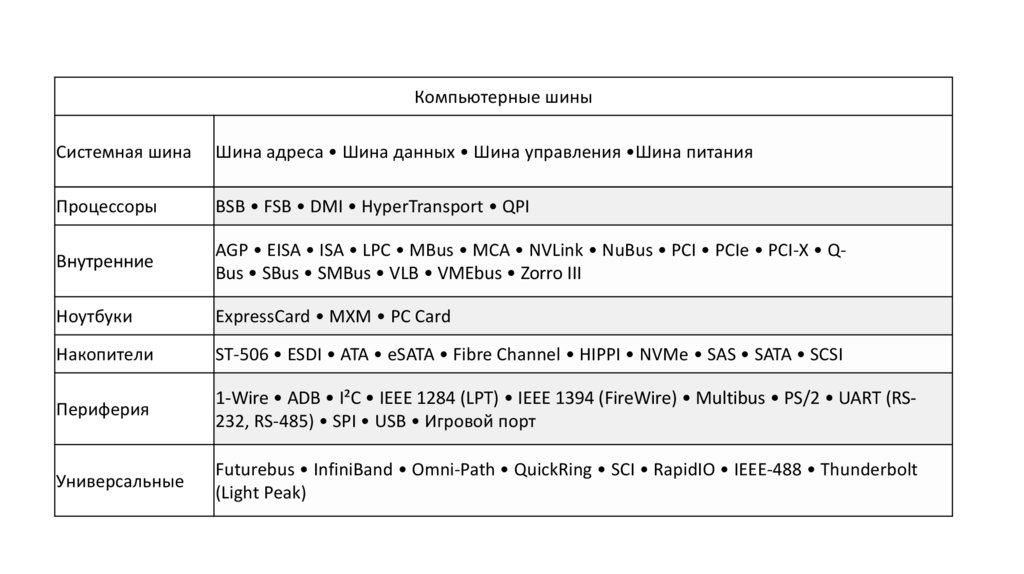

Компьютерные шиныСистемная шина

Шина адреса • Шина данных • Шина управления •Шина питания

Процессоры

BSB • FSB • DMI • HyperTransport • QPI

Внутренние

AGP • EISA • ISA • LPC • MBus • MCA • NVLink • NuBus • PCI • PCIe • PCI-X • QBus • SBus • SMBus • VLB • VMEbus • Zorro III

Ноутбуки

ExpressCard • MXM • PC Card

Накопители

ST-506 • ESDI • ATA • eSATA • Fibre Channel • HIPPI • NVMe • SAS • SATA • SCSI

Периферия

1-Wire • ADB • I²C • IEEE 1284 (LPT) • IEEE 1394 (FireWire) • Multibus • PS/2 • UART (RS232, RS-485) • SPI • USB • Игровой порт

Универсальные

Futurebus • InfiniBand • Omni-Path • QuickRing • SCI • RapidIO • IEEE-488 • Thunderbolt

(Light Peak)

18.

19.

20.

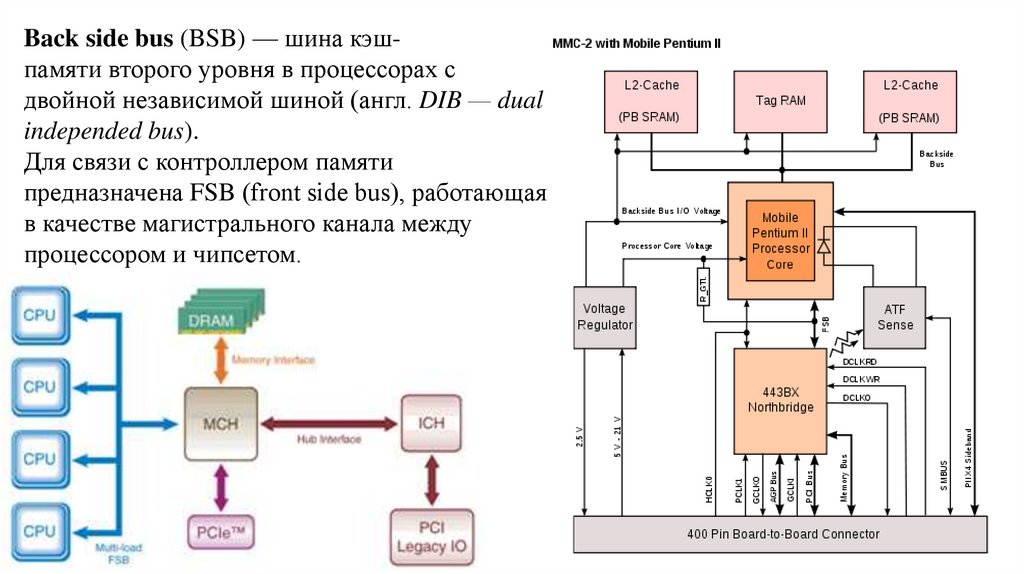

Back side bus (BSB) — шина кэшпамяти второго уровня в процессорах сдвойной независимой шиной (англ. DIB — dual

independed bus).

Для связи с контроллером памяти

предназначена FSB (front side bus), работающая

в качестве магистрального канала между

процессором и чипсетом.

21.

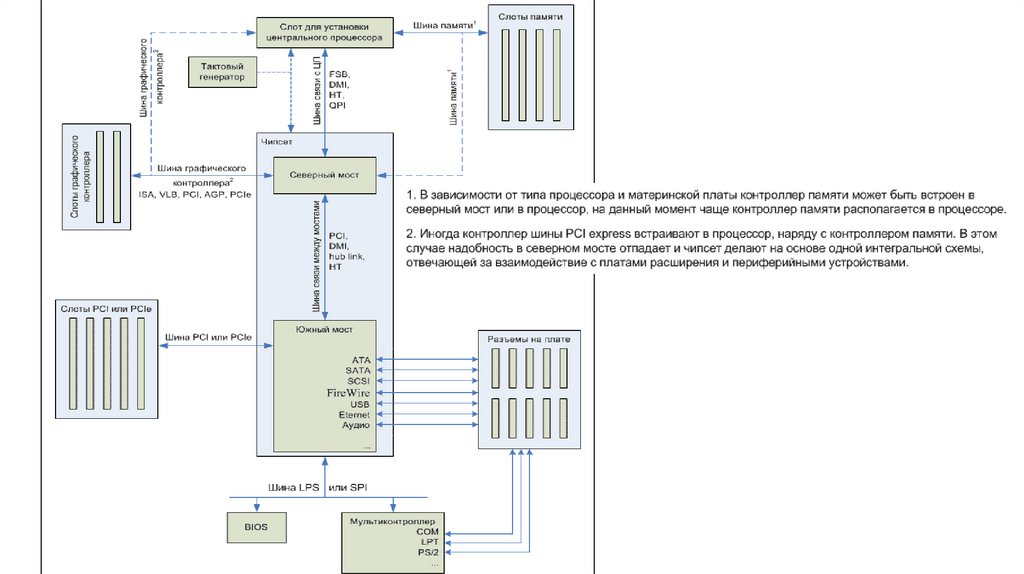

Front Side Bus (FSB, системная шина) — шина, обеспечивающая соединение между x86- и x64-совместимымцентральным процессором и внутренними устройствами.

Как правило, современный персональный компьютер на базе x86- и x64-совместимого микропроцессора устроен

следующим образом: микропроцессор через FSB подключается к системному контроллеру, который обычно

называют «северным мостом», (англ. Northbridge). Системный контроллер имеет в своём составе контроллер ОЗУ (в

некоторых современных персональных компьютерах контроллер ОЗУ встроен в микропроцессор), а также

контроллеры шин, к которым подключаются периферийные устройства. Получил распространение подход, при

котором к северному мосту подключаются наиболее производительные периферийные устройства, например,

видеокарты с шиной PCI Express 16x, а менее производительные устройства (микросхема BIOS'а, устройства с

шиной PCI) подключаются к т. н. «южному мосту» (англ. Southbridge), который соединяется с северным мостом

специальной шиной. Набор из «южного» и «северного» мостов называют набором системной логики, но чаще

применяется калька с английского языка «чипсет» (англ. chipset).

Таким образом, FSB работает в качестве магистрального канала между процессором и чипсетом.

Некоторые компьютеры имеют внешнюю кэш-память, подключенную через «заднюю» шину (англ. back side bus),

которая быстрее, чем FSB, но работает только со специфичными устройствами.

Каждая из вторичных шин работает на своей частоте (которая может быть как выше, так и ниже частоты FSB).

Иногда частота вторичной шины является производной от частоты FSB, иногда задаётся независимо.

22.

Частоты, на которых работают центральный процессор и FSB, имеют общую опорную частоту, и вконечном счете определяются, исходя из их коэффициентов умножения (частота устройства =

опорная частота * коэффициент умножения).

Современные процессоры имеют встроенный контроллер памяти, поэтому в них очень слабая

зависимость производительности процессора от FSB.

Существуют системы, преимущественно старые, где FSB и периферийные шины ISA, PCI, AGP

имеют общую опорную частоту, и попытка изменения частоты FSB не посредством её коэффициента

умножения, а посредством изменения опорной частоты приведет к изменению частот периферийных

шин, и даже внешних интерфейсов, таких, как Parallel ATA. На других системах, преимущественно

новых, частоты периферийных шин не зависят от частоты FSB.

В системах с высокой интеграцией контроллеры памяти и периферийных шин могут быть встроены

в процессор, и сама FSB в таких процессорах отсутствует принципиально. К таким системам можно

отнести персональную платформу Intel LGA1156.

23.

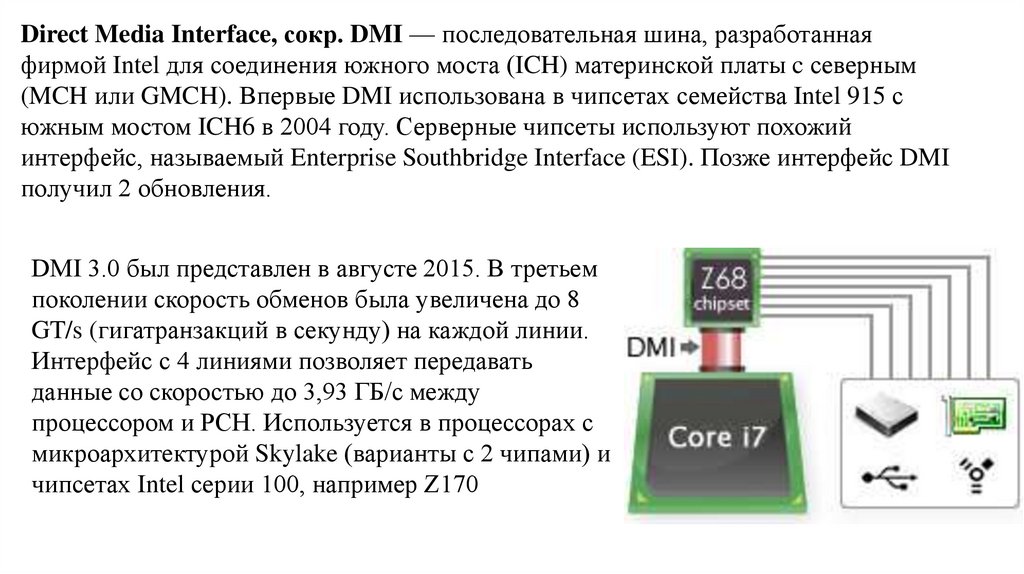

Direct Media Interface, сокр. DMI — последовательная шина, разработаннаяфирмой Intel для соединения южного моста (ICH) материнской платы c северным

(MCH или GMCH). Впервые DMI использована в чипсетах семейства Intel 915 с

южным мостом ICH6 в 2004 году. Серверные чипсеты используют похожий

интерфейс, называемый Enterprise Southbridge Interface (ESI). Позже интерфейс DMI

получил 2 обновления.

DMI 3.0 был представлен в августе 2015. В третьем

поколении скорость обменов была увеличена до 8

GT/s (гигатранзакций в секунду) на каждой линии.

Интерфейс с 4 линиями позволяет передавать

данные со скоростью до 3,93 ГБ/с между

процессором и PCH. Используется в процессорах с

микроархитектурой Skylake (варианты с 2 чипами) и

чипсетах Intel серии 100, например Z170

24.

HyperTransport (ранее известная как Lightning Data Transport (LDT)) —двунаправленная последовательно-параллельная компьютерная шина с высокой

пропускной способностью и малыми задержками. Для разработки и продвижения

данной шины был образован консорциум HyperTransport Technology.

HyperTransport работает на частотах от 200 МГц до 3,2 ГГц (у шины PCI — 33 и 66 МГц). Кроме того, она

использует DDR, что означает, что данные посылаются как по фронту, так и по срезу сигнала синхронизации, что

позволяет осуществлять до 5200 миллионов посылок в секунду при частоте сигнала синхронизации 2,6 ГГц; частота

сигнала синхронизации настраивается автоматически.

HyperTransport поддерживает автоматическое определение ширины шины от 2 до 32 бит. Полноразмерная

полноскоростная 32-битная шина в двунаправленном режиме способна обеспечить пропускную способность до 51

600 Мбайт/с = 2 (DDR) × 2 × 32/8 (байт) × 3200 (МГц) (максимум в одном направлении — 25 600 Мбайт/с), являясь,

таким образом, самой быстрой шиной среди себе подобных. Шина может быть использована как в подсистемах с

высокими требованиями к пропускной способности (оперативная память и ЦПУ), так и в подсистемах с низкими

требованиями (периферийные устройства). Данная технология также способна обеспечить низкие задержки для

других применений в других подсистемах.

25.

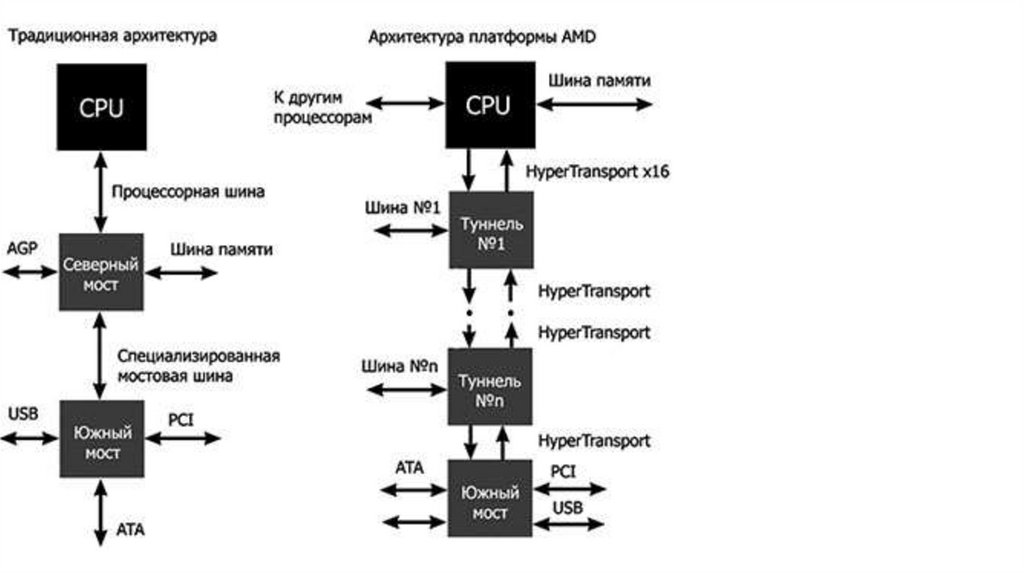

Шина HyperTransport основана на передаче пакетов. Каждый пакет состоит из 32разрядных слов, вне зависимости от физической ширины шины (количестваинформационных линий). Первое слово в пакете — всегда управляющее слово. Если

пакет содержит адрес, то последние 8 бит управляющего слова сцеплены со

следующим 32-битным словом, в результате образуя 40-битный адрес. Шина

поддерживает 64-разрядную адресацию — в этом случае пакет начинается со

специального 32-разрядного управляющего слова, указывающего на 64-разрядную

адресацию, и содержащего разряды адреса с 40 по 63 (разряды адреса нумеруются

начиная с 0). Остальные 32-битные слова пакета содержат непосредственно

передаваемые данные. Данные всегда передаются 32-битными словами, вне

зависимости от их реальной длины (например, в ответ на запрос на чтение одного

байта по шине будет передан пакет, содержащий 32 бита данных и флагом-признаком

того, что значимыми из этих 32 бит являются только 8).

26.

27.

Пакеты HyperTransport передаются по шине последовательно. Увеличение пропускной способности влечёт за собойувеличение ширины шины. HyperTransport может использоваться для передачи служебных сообщений системы, для

передачи прерываний, для конфигурирования устройств, подключённых к шине, и для передачи данных.

Операция записи на шине бывает двух видов — posted и non-posted. Posted-операция записи заключается в передаче

единственного пакета, содержащего адрес, по которому необходимо произвести запись, и данные. Эта операция

обычно используется для обмена данными с высокоскоростными устройствами, например, для DMA-передачи.

Non-posted операция записи состоит из посылки двух пакетов: устройство, инициирующее операцию записи,

посылает устройству-адресату пакет, содержащий адрес и данные. Устройство-адресат, получив такой пакет,

проводит операцию записи и отсылает устройству-инициатору пакет, содержащий информацию о том, успешно ли

произведена запись. Таким образом, posted-запись позволяет получить максимальную скорость передачи данных

(нет затрат на пересылку пакета-подтверждения), а non-posted-запись позволяет обеспечить надёжную передачу

данных (приход пакета-подтверждения гарантирует, что данные дошли до адресата).

Шина HyperTransport поддерживает технологии энергосбережения, а именно ACPI. Это значит, что при изменении

состояния процессора (C-state) на энергосберегающее изменяется также и состояние устройств (D-state). Например,

при отключении процессора жёсткие диски также отключаются.

Электрический интерфейс HyperTransport/LDT — низковольтные дифференциальные сигналы с напряжением 1,2 В.

28.

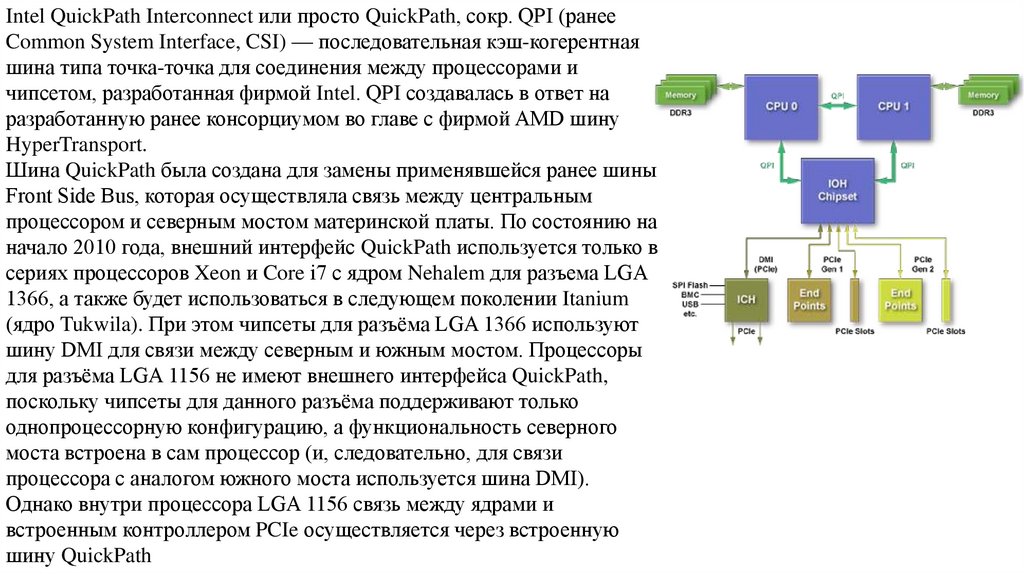

Intel QuickPath Interconnect или просто QuickPath, сокр. QPI (ранееCommon System Interface, CSI) — последовательная кэш-когерентная

шина типа точка-точка для соединения между процессорами и

чипсетом, разработанная фирмой Intel. QPI создавалась в ответ на

разработанную ранее консорциумом во главе с фирмой AMD шину

HyperTransport.

Шина QuickPath была создана для замены применявшейся ранее шины

Front Side Bus, которая осуществляла связь между центральным

процессором и северным мостом материнской платы. По состоянию на

начало 2010 года, внешний интерфейс QuickPath используется только в

сериях процессоров Xeon и Core i7 с ядром Nehalem для разъема LGA

1366, а также будет использоваться в следующем поколении Itanium

(ядро Tukwila). При этом чипсеты для разъёма LGA 1366 используют

шину DMI для связи между северным и южным мостом. Процессоры

для разъёма LGA 1156 не имеют внешнего интерфейса QuickPath,

поскольку чипсеты для данного разъёма поддерживают только

однопроцессорную конфигурацию, а функциональность северного

моста встроена в сам процессор (и, следовательно, для связи

процессора с аналогом южного моста используется шина DMI).

Однако внутри процессора LGA 1156 связь между ядрами и

встроенным контроллером PCIe осуществляется через встроенную

шину QuickPath

29.

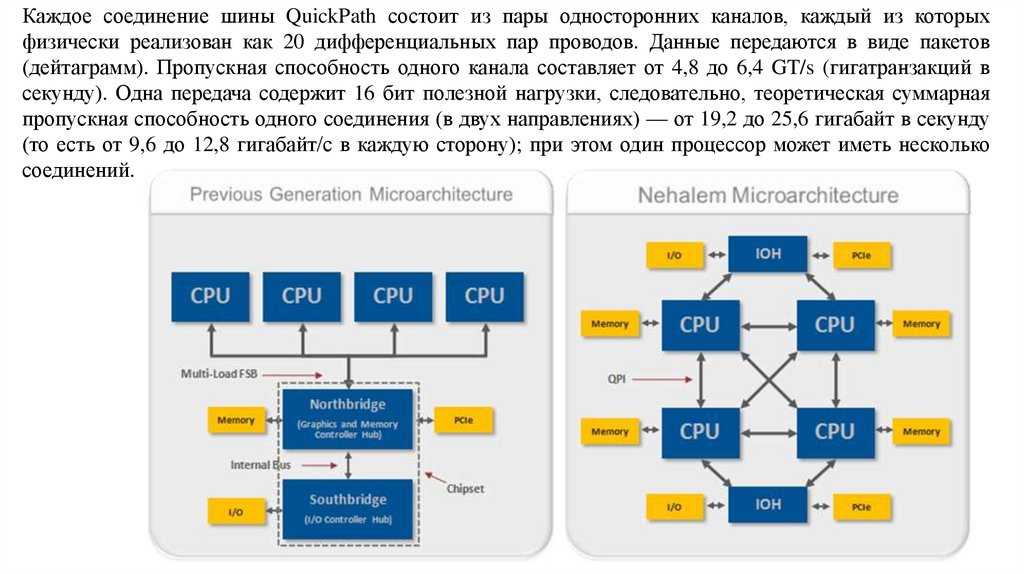

Каждое соединение шины QuickPath состоит из пары односторонних каналов, каждый из которыхфизически реализован как 20 дифференциальных пар проводов. Данные передаются в виде пакетов

(дейтаграмм). Пропускная способность одного канала составляет от 4,8 до 6,4 GT/s (гигатранзакций в

секунду). Одна передача содержит 16 бит полезной нагрузки, следовательно, теоретическая суммарная

пропускная способность одного соединения (в двух направлениях) — от 19,2 до 25,6 гигабайт в секунду

(то есть от 9,6 до 12,8 гигабайт/с в каждую сторону); при этом один процессор может иметь несколько

соединений.

30.

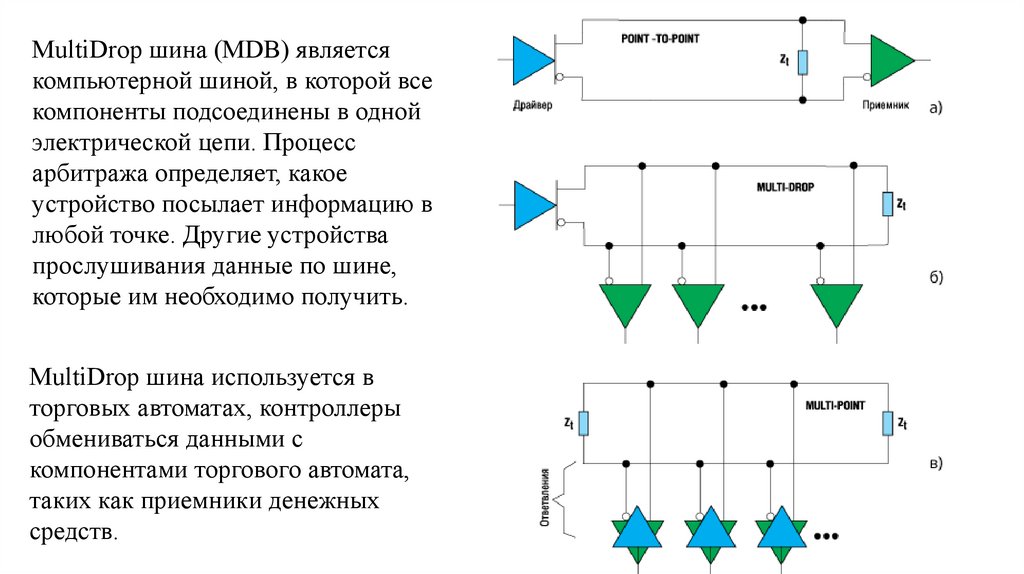

MultiDrop шина (MDB) являетсякомпьютерной шиной, в которой все

компоненты подсоединены в одной

электрической цепи. Процесс

арбитража определяет, какое

устройство посылает информацию в

любой точке. Другие устройства

прослушивания данные по шине,

которые им необходимо получить.

MultiDrop шина используется в

торговых автоматах, контроллеры

обмениваться данными с

компонентами торгового автомата,

таких как приемники денежных

средств.

31.

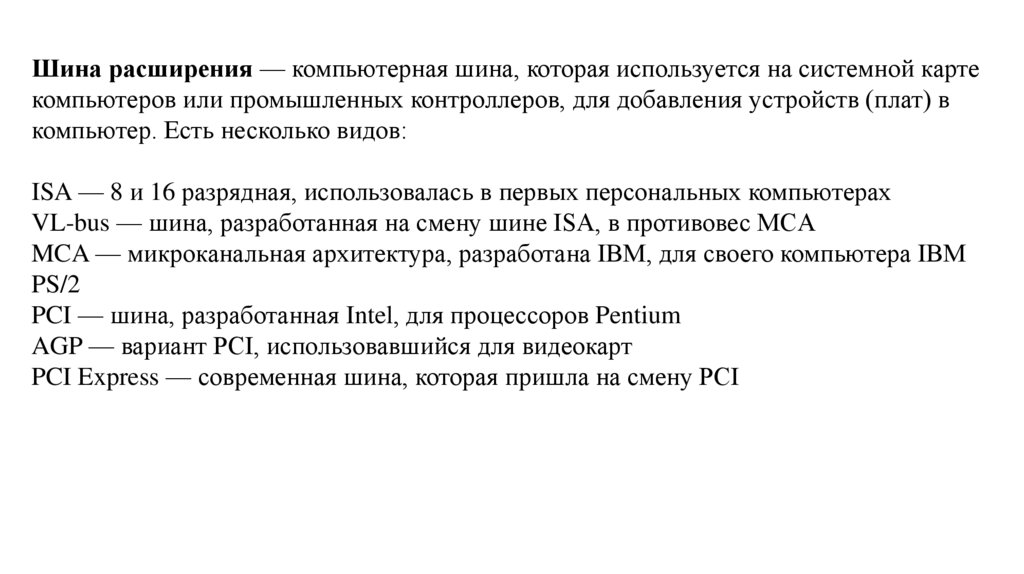

Шина расширения — компьютерная шина, которая используется на системной картекомпьютеров или промышленных контроллеров, для добавления устройств (плат) в

компьютер. Есть несколько видов:

ISA — 8 и 16 разрядная, использовалась в первых персональных компьютерах

VL-bus — шина, разработанная на смену шине ISA, в противовес MCA

MCA — микроканальная архитектура, разработана IBM, для своего компьютера IBM

PS/2

PCI — шина, разработанная Intel, для процессоров Pentium

AGP — вариант PCI, использовавшийся для видеокарт

PCI Express — современная шина, которая пришла на смену PCI

32.

33.

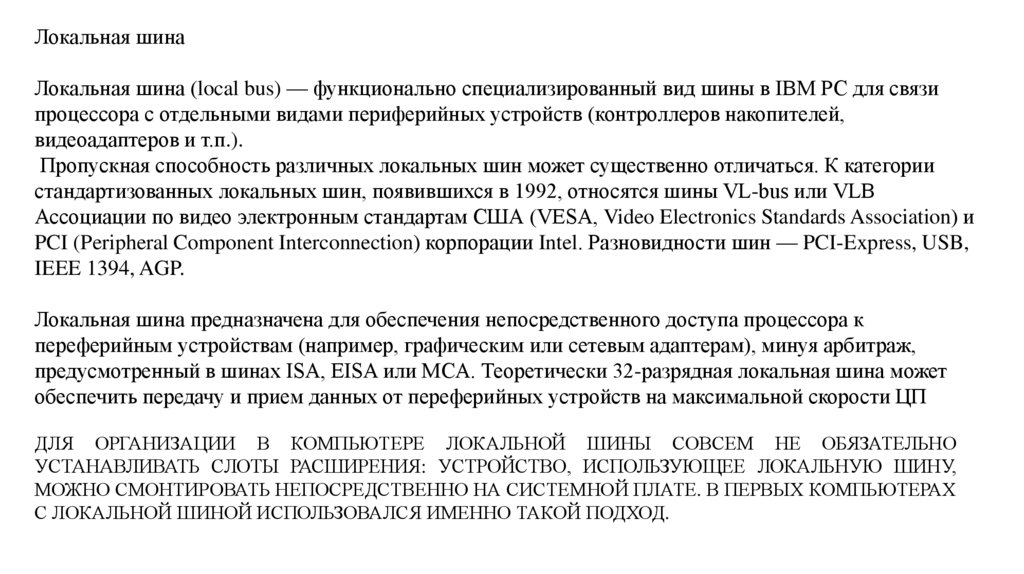

Локальная шинаЛокальная шина (local bus) — функционально специализированный вид шины в IBM PC для связи

процессора с отдельными видами периферийных устройств (контроллеров накопителей,

видеоадаптеров и т.п.).

Пропускная способность различных локальных шин может существенно отличаться. К категории

стандартизованных локальных шин, появившихся в 1992, относятся шины VL-bus или VLB

Ассоциации по видео электронным стандартам США (VESA, Video Electronics Standards Association) и

PCI (Peripheral Component Interconnection) корпорации Intel. Разновидности шин — PCI-Express, USB,

IEEE 1394, AGP.

Локальная шина предназначена для обеспечения непосредственного доступа процессора к

переферийным устройствам (например, графическим или сетевым адаптерам), минуя арбитраж,

предусмотренный в шинах ISA, EISA или MCA. Теоретически 32-разрядная локальная шина может

обеспечить передачу и прием данных от переферийных устройств на максимальной скорости ЦП

ДЛЯ ОРГАНИЗАЦИИ В КОМПЬЮТЕРЕ ЛОКАЛЬНОЙ ШИНЫ СОВСЕМ НЕ ОБЯЗАТЕЛЬНО

УСТАНАВЛИВАТЬ СЛОТЫ РАСШИРЕНИЯ: УСТРОЙСТВО, ИСПОЛЬЗУЮЩЕЕ ЛОКАЛЬНУЮ ШИНУ,

МОЖНО СМОНТИРОВАТЬ НЕПОСРЕДСТВЕННО НА СИСТЕМНОЙ ПЛАТЕ. В ПЕРВЫХ КОМПЬЮТЕРАХ

С ЛОКАЛЬНОЙ ШИНОЙ ИСПОЛЬЗОВАЛСЯ ИМЕННО ТАКОЙ ПОДХОД.

34.

35.

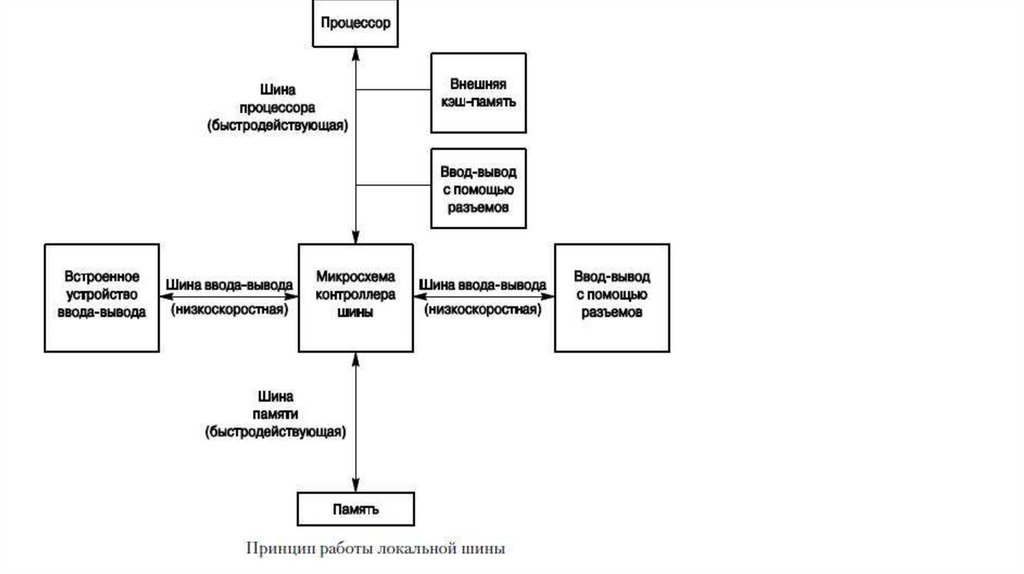

Шина PCIВ начале 1992 года Intel организовала группу разработчиков, перед которой была поставлена та же задача, что и перед

группой VESA: разработать новую шину, в которой были бы устранены все недостатки шин ISA и EISA.

В июне 1992 года была выпущена спецификация шины PCI версии 1.0, которая с тех пор претерпела несколько

изменений.

36.

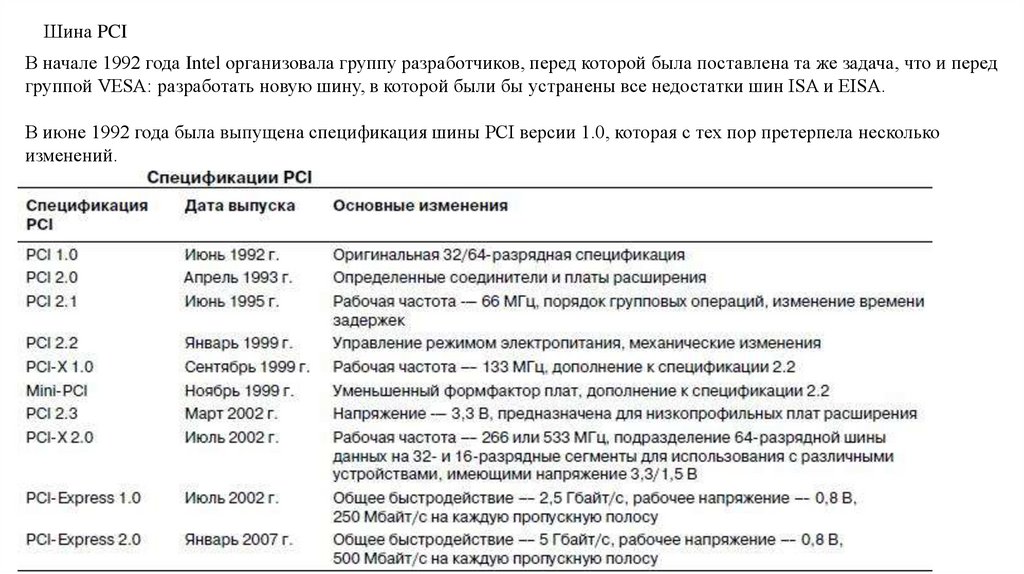

Создатели PCI отказалисьот

традиционной

концепции, введя еще одну

шину между процессором и

обычной шиной вводавывода. Вместо того чтобы

подключить

ее

непосредственно к шине

процессора,

весьма

чувствительной к подобным

вмешательствам (что было

характерно для VL-Bus),

они разработали новый

комплект

микросхем

контроллеров

для

расширения шины.

37.

Шина PCI добавляет к традиционной конфигурации шин еще один уровень. При этом обычная шинаввода-вывода не используется, а создается фактически еще одна высокоскоростная системная шина с

разрядностью, равной разрядности данных процессора. Компьютеры с шиной PCI появились в

середине 1993 года, и вскоре она стала неотъемлемой частью компьютеров высокого класса.

Тактовая частота стандартной шины PCI — 33 МГц, а разрядность соответствует разрядности данных

процессора. Для 32-разрядного процессора пропускная способность составляет 132 Мбайт/с:

33,33 МГц × 4 байт (32 бит) = 133 Мбайт/с.

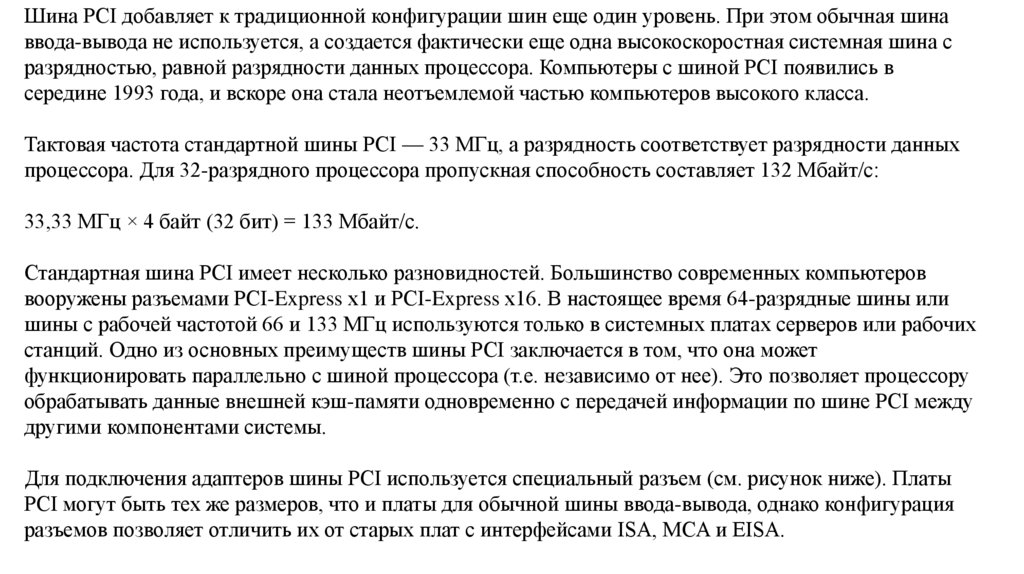

Стандартная шина PCI имеет несколько разновидностей. Большинство современных компьютеров

вооружены разъемами PCI-Express x1 и PCI-Express x16. В настоящее время 64-разрядные шины или

шины с рабочей частотой 66 и 133 МГц используются только в системных платах серверов или рабочих

станций. Одно из основных преимуществ шины PCI заключается в том, что она может

функционировать параллельно с шиной процессора (т.е. независимо от нее). Это позволяет процессору

обрабатывать данные внешней кэш-памяти одновременно с передачей информации по шине PCI между

другими компонентами системы.

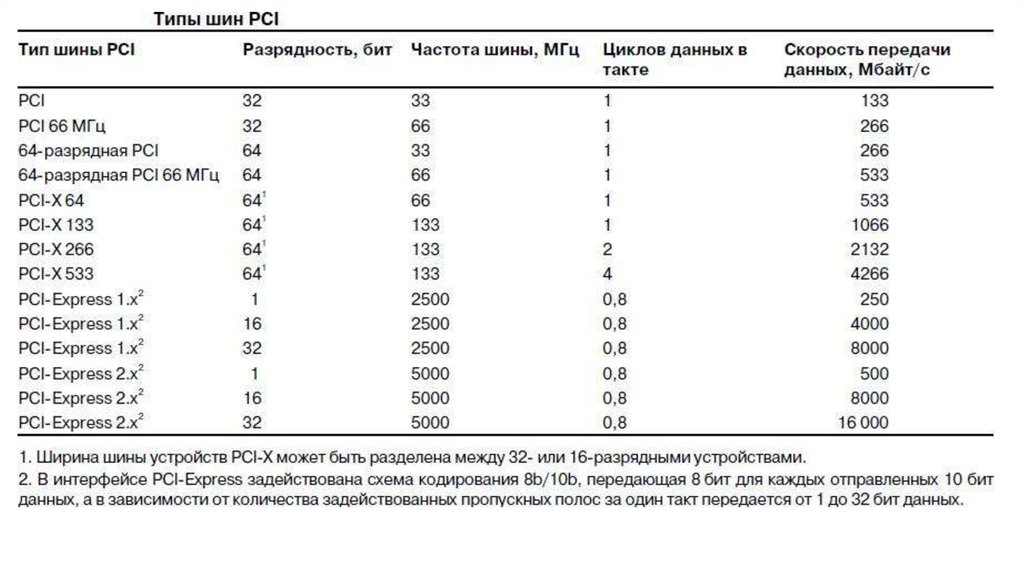

Для подключения адаптеров шины PCI используется специальный разъем (см. рисунок ниже). Платы

PCI могут быть тех же размеров, что и платы для обычной шины ввода-вывода, однако конфигурация

разъемов позволяет отличить их от старых плат с интерфейсами ISA, MCA и EISA.

38.

39.

40.

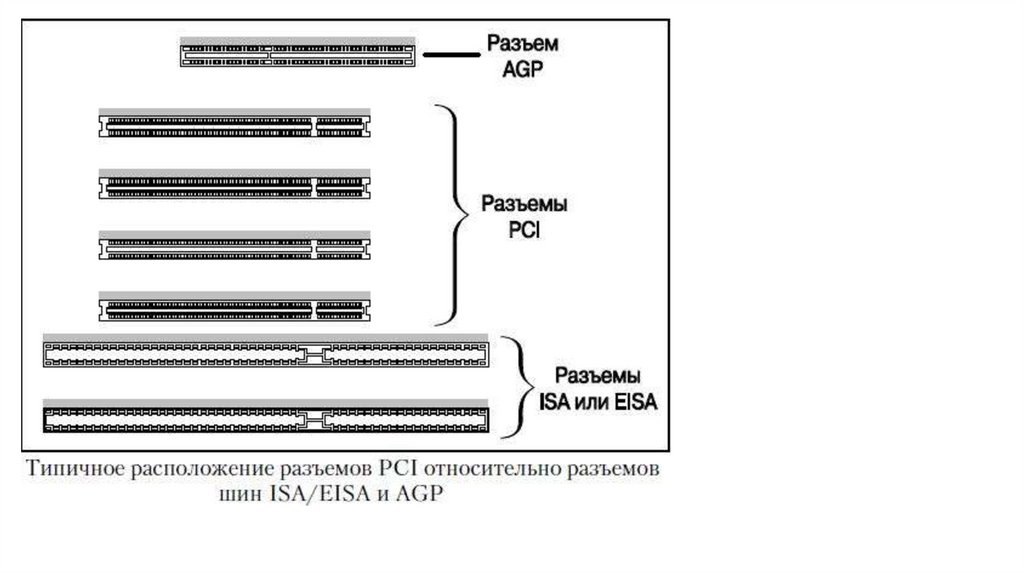

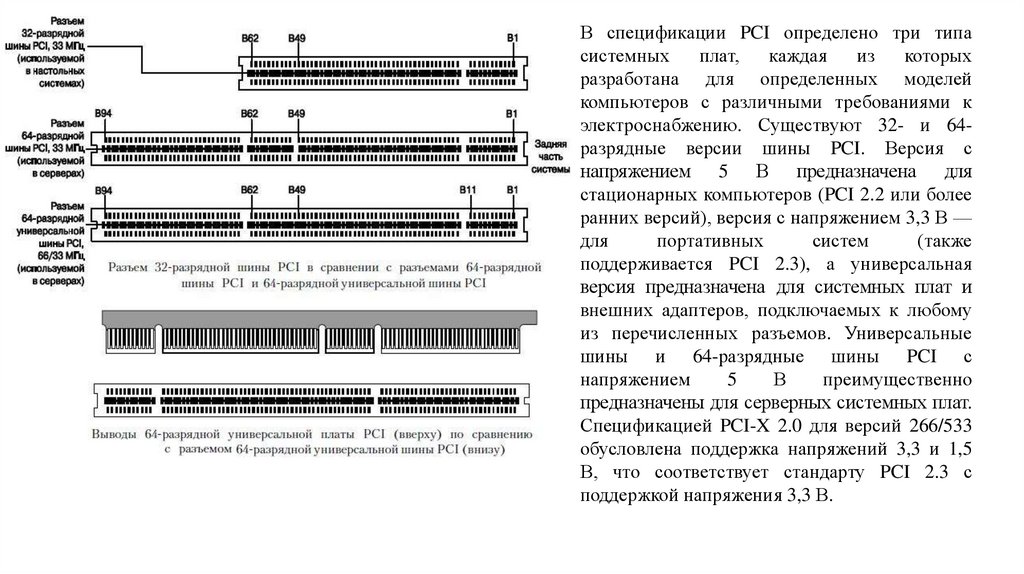

В спецификации PCI определено три типасистемных

плат,

каждая

из

которых

разработана для определенных моделей

компьютеров с различными требованиями к

электроснабжению. Существуют 32- и 64разрядные версии шины PCI. Версия с

напряжением 5 В предназначена для

стационарных компьютеров (PCI 2.2 или более

ранних версий), версия с напряжением 3,3 В —

для

портативных

систем

(также

поддерживается PCI 2.3), а универсальная

версия предназначена для системных плат и

внешних адаптеров, подключаемых к любому

из перечисленных разъемов. Универсальные

шины и 64-разрядные шины PCI с

напряжением

5

В

преимущественно

предназначены для серверных системных плат.

Спецификацией PCI-X 2.0 для версий 266/533

обусловлена поддержка напряжений 3,3 и 1,5

В, что соответствует стандарту PCI 2.3 с

поддержкой напряжения 3,3 В.

41.

Обратите внимание, что универсальная плата PCI может устанавливаться в разъем,предназначенный для любой платы с фиксированным напряжением питания. Если напряжение,

подаваемое на те или иные контакты, может быть разным, то оно обозначается +В I/O. На эти

контакты подается опорное напряжение, определяющее уровни выходных логических сигналов.

Другим важным свойством платы PCI является то, что она удовлетворяет спецификации Plug and

Play компании Intel. Это означает, что PCI не имеет перемычек и переключателей и может

настраиваться с помощью специальной программы настройки. Системы с Plug and Play способны

самостоятельно настраивать адаптеры, а в тех компьютерах, в которых отсутствует система Plug

and Play, но есть разъемы PCI, настройку адаптеров нужно выполнять вручную с помощью

программы настройки BIOS. С конца 1995 года в большинстве компьютеров устанавливается

система BIOS, удовлетворяющая спецификации Plug and Play и обеспечивающая автоматическую

настройку.

42.

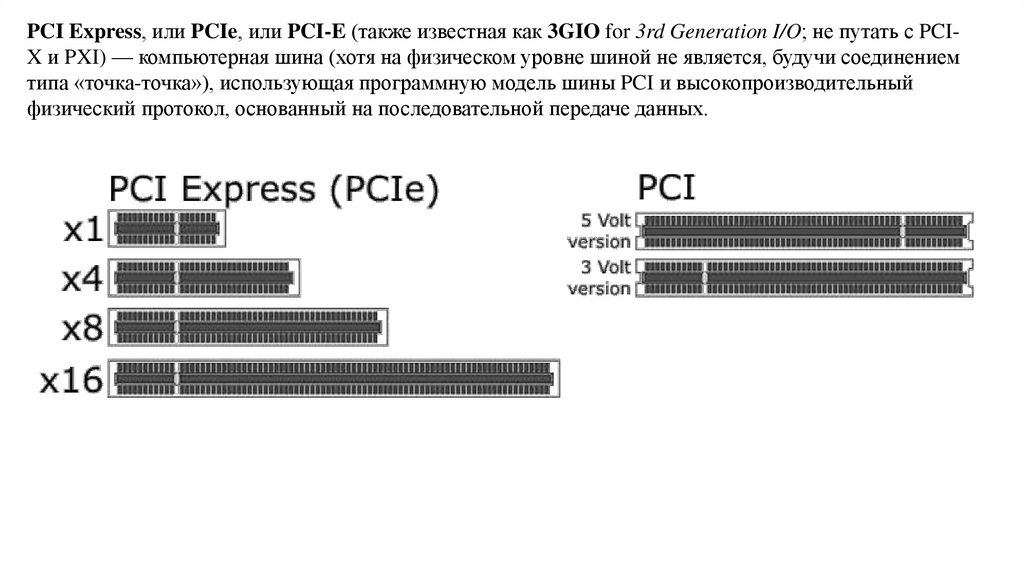

PCI Express, или PCIe, или PCI-E (также известная как 3GIO for 3rd Generation I/O; не путать с PCIX и PXI) — компьютерная шина (хотя на физическом уровне шиной не является, будучи соединениемтипа «точка-точка»), использующая программную модель шины PCI и высокопроизводительный

физический протокол, основанный на последовательной передаче данных.

43.

В течение 2001 года специалисты группы компаний, получившей название Arapahoe Work Group(изначально находившейся под управлением Intel), работали над проектом спецификации новой

быстродействующей шины, имеющей кодовое название 3GIO (Third-Generation I/O — шина ввода-вывода

третьего поколения). В августе 2001 года специальная группа PCI-SIG (PCI Special-Interest Group)

приняла решение об использовании, управлении и поддержке спецификации архитектуры 3GIO в

качестве шины PCI будущего поколения. Работа над черновой версией 3GIO 1.0 была завершена в апреле

2002 года, после чего была передана в группу PCISIG, где и получила новое название — PCI-Express. В

июле того же года была одобрена специ фикация PCI-Express 1.0. Впоследствии эта спецификация

обновлялась в апреле 2005 года (версия 1.1) и в январе 2007 года (версия 2.0).

Как следует из первоначального кодового названия (3GIO), новая спецификация шины разрабатывалась в

целях расширения и последующей замены существующих шин ISA/AT (первое поколение) и PCI (второе

поколение), используемых в персональных компьютерах. Архитектура шины каждого из предыдущих

поколений разрабатывалась с учетом 10- или 15-летнего срока службы. Спецификация PCI Express,

принятая и одобренная специальной группой PCI-SIG, станет, как предполагается, доминирующей

архитектурой шины ПК, созданной для поддержки увеличивающейся пропускной способности

компьютера, в течение следующих 10–15 лет.

44.

Основные особенности PCI Express таковы:совместимость с существующей шиной PCI и программными драйверами различных устройств;

физическое соединение, осуществляемое с помощью медных, оптических или других физических

носителей и обеспечивающее поддержку будущих схем кодирования;

максимальная пропускная способность каждого вывода, позволяющая создавать шины малых

формфакторов, снижать их себестоимость, упрощать конструкцию плат, а также сокращать количество

проблем, связанных с целостностью сигнала;

встроенная схема синхронизации, позволяющая быстрее изменять частоту (быстродействие) шины,

чем при согласованной синхронизации;

ширина полосы частот (пропускная способность), увеличиваемая при повышении частоты и

разрядности (ширины) шины;

малое время ожидания, наиболее подходящее для приложений, требующих изохронной (зависящей от

времени) доставки данных, что происходит, например, при обработке потоковых видеоданных;

возможность “горячей” коммутации и “горячей” замены (т.е. без выключения электропитания);

возможности управления режимом питания.

45.

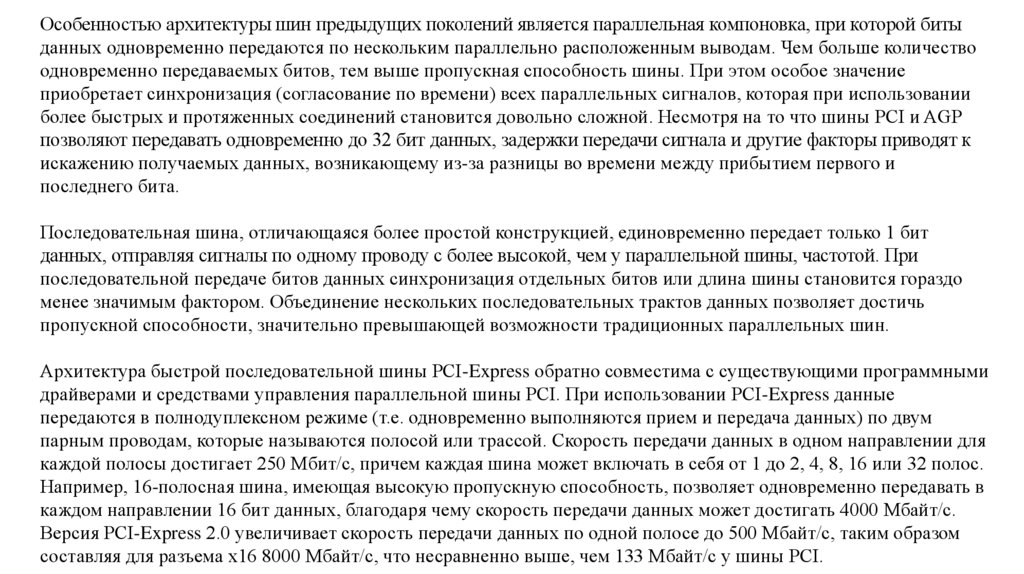

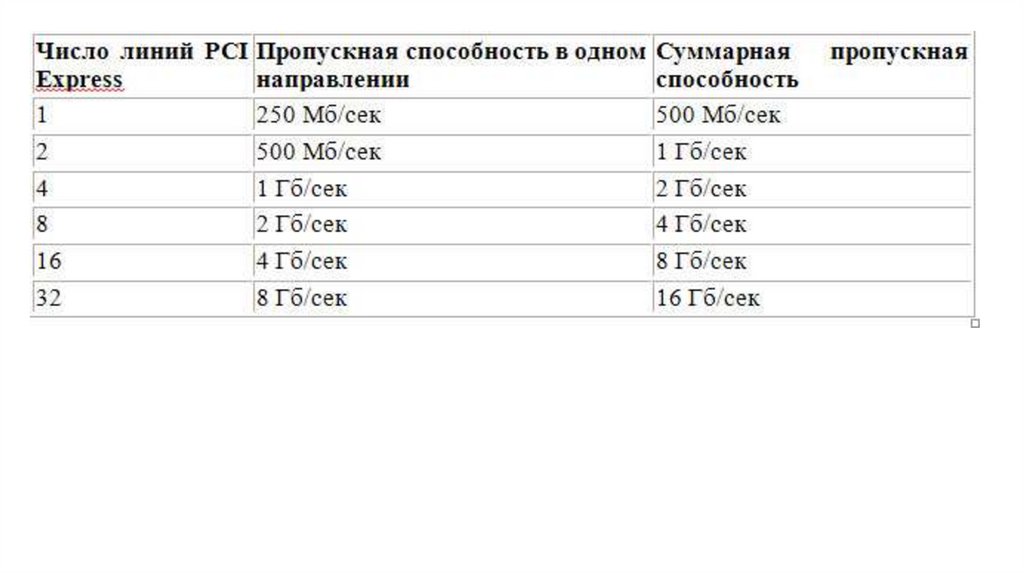

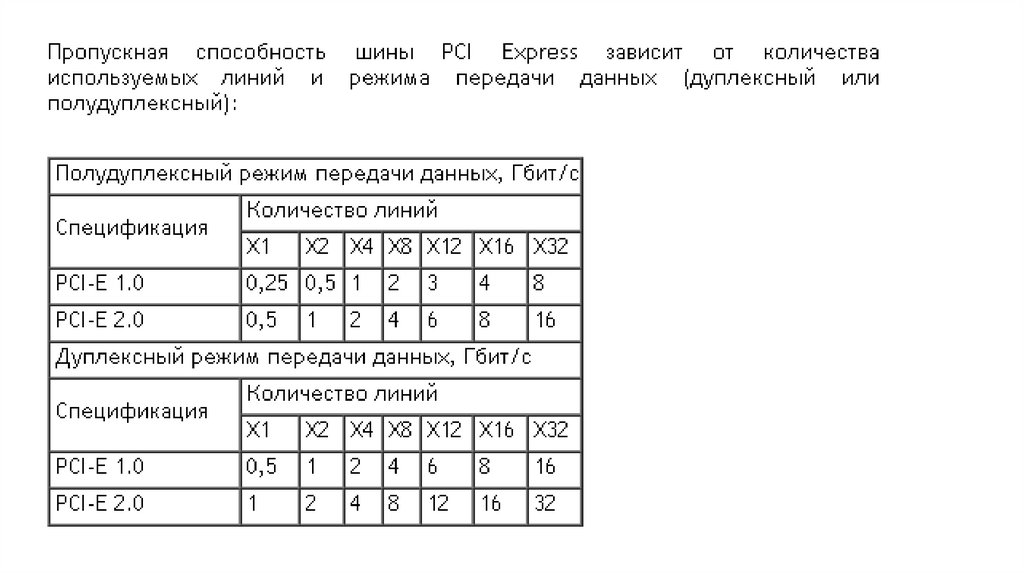

Особенностью архитектуры шин предыдущих поколений является параллельная компоновка, при которой битыданных одновременно передаются по нескольким параллельно расположенным выводам. Чем больше количество

одновременно передаваемых битов, тем выше пропускная способность шины. При этом особое значение

приобретает синхронизация (согласование по времени) всех параллельных сигналов, которая при использовании

более быстрых и протяженных соединений становится довольно сложной. Несмотря на то что шины PCI и AGP

позволяют передавать одновременно до 32 бит данных, задержки передачи сигнала и другие факторы приводят к

искажению получаемых данных, возникающему из-за разницы во времени между прибытием первого и

последнего бита.

Последовательная шина, отличающаяся более простой конструкцией, единовременно передает только 1 бит

данных, отправляя сигналы по одному проводу с более высокой, чем у параллельной шины, частотой. При

последовательной передаче битов данных синхронизация отдельных битов или длина шины становится гораздо

менее значимым фактором. Объединение нескольких последовательных трактов данных позволяет достичь

пропускной способности, значительно превышающей возможности традиционных параллельных шин.

Архитектура быстрой последовательной шины PCI-Express обратно совместима с существующими программными

драйверами и средствами управления параллельной шины PCI. При использовании PCI-Express данные

передаются в полнодуплексном режиме (т.е. одновременно выполняются прием и передача данных) по двум

парным проводам, которые называются полосой или трассой. Скорость передачи данных в одном направлении для

каждой полосы достигает 250 Мбит/с, причем каждая шина может включать в себя от 1 до 2, 4, 8, 16 или 32 полос.

Например, 16-полосная шина, имеющая высокую пропускную способность, позволяет одновременно передавать в

каждом направлении 16 бит данных, благодаря чему скорость передачи данных может достигать 4000 Мбайт/с.

Версия PCI-Express 2.0 увеличивает скорость передачи данных по одной полосе до 500 Мбайт/с, таким образом

составляя для разъема x16 8000 Мбайт/с, что несравненно выше, чем 133 Мбайт/с у шины PCI.

46.

47.

48.

49.

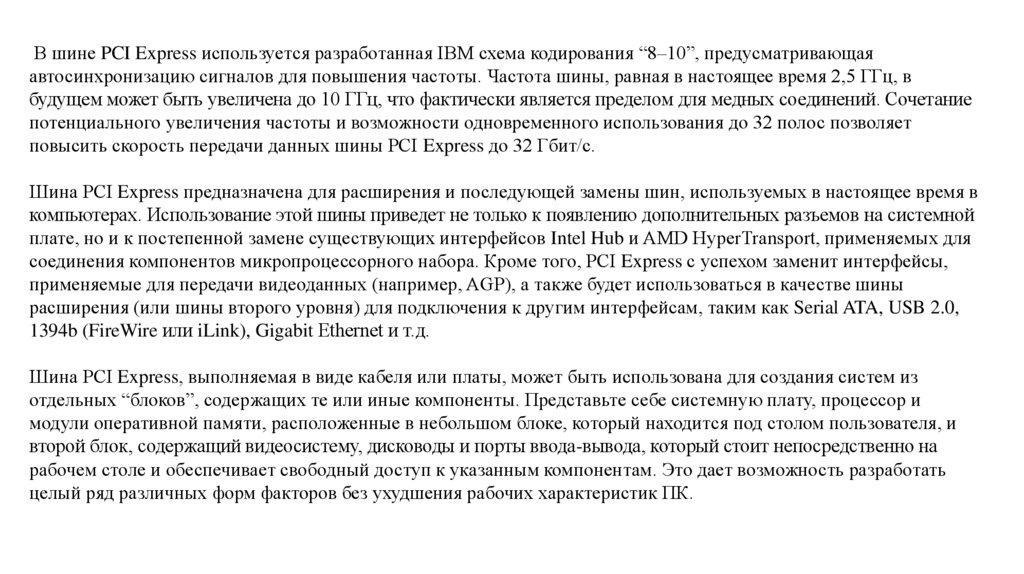

В шине PCI Express используется разработанная IBM схема кодирования “8–10”, предусматривающаяавтосинхронизацию сигналов для повышения частоты. Частота шины, равная в настоящее время 2,5 ГГц, в

будущем может быть увеличена до 10 ГГц, что фактически является пределом для медных соединений. Сочетание

потенциального увеличения частоты и возможности одновременного использования до 32 полос позволяет

повысить скорость передачи данных шины PCI Express до 32 Гбит/с.

Шина PCI Express предназначена для расширения и последующей замены шин, используемых в настоящее время в

компьютерах. Использование этой шины приведет не только к появлению дополнительных разъемов на системной

плате, но и к постепенной замене существующих интерфейсов Intel Hub и AMD HyperTransport, применяемых для

соединения компонентов микропроцессорного набора. Кроме того, PCI Express с успехом заменит интерфейсы,

применяемые для передачи видеоданных (например, AGP), а также будет использоваться в качестве шины

расширения (или шины второго уровня) для подключения к другим интерфейсам, таким как Serial ATA, USB 2.0,

1394b (FireWire или iLink), Gigabit Ethernet и т.д.

Шина PCI Express, выполняемая в виде кабеля или платы, может быть использована для создания систем из

отдельных “блоков”, содержащих те или иные компоненты. Представьте себе системную плату, процессор и

модули оперативной памяти, расположенные в небольшом блоке, который находится под столом пользователя, и

второй блок, содержащий видеосистему, дисководы и порты ввода-вывода, который стоит непосредственно на

рабочем столе и обеспечивает свободный доступ к указанным компонентам. Это дает возможность разработать

целый ряд различных форм факторов без ухудшения рабочих характеристик ПК.

50.

PCI-Express пока не заменила полностью шину PCI и всеостальные интерфейсы, и вряд ли это возможно в ближайшем

будущем. Разработчики систем продолжают использовать в своих

решениях шины PCI, AGP и некоторые другие, причем будут

делать это еще не один год. Как и в свое время с комбинацией

PCI и ISA/AT-Bus, разные поколения шин будут некоторое время

соседствовать друг с другом. Постепенно количество разъемов

PCI будет уменьшаться, а количество разъемов PCI-Express —

увеличиваться. В конечном итоге основной шиной для

подключения устройств окажется PCI-Express, придя на смену

шине PCI, которая выполняла данную роль на протяжении

довольно длительного времени. В настоящее время системные

платы содержат равное количество разъемов PCI и PCI-Express.

Хотя потребуется некоторое время на то, чтобы PCI-Express

заменила PCI, разъем PCI-Express x16 уже повсеместно вытеснил

разъем AGP 8x.

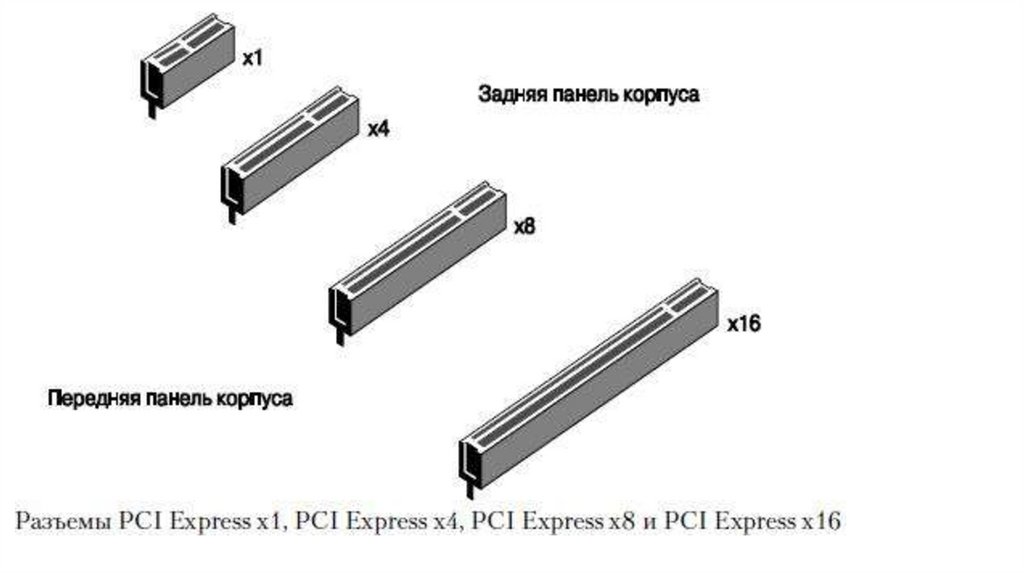

Современные системные платы содержат несколько разъемов

PCI, а также разъемы PCI-Express x1 и PCI-Express x16;

системные платы для рабочих станций и серверов содержат

шины PCI-Express, PCI-X и PCI. Для обеспечения совместимости

новых решений PCI-Express с существующей инфраструктурой

PCI разработаны спецификации Express Bridge 1.0 и Mini PCIExpress Card.

51.

52.

53.

Гибкие удлинители и переходники для шин PCI Express x16,x8,x4,x1, PCI32, PCI64, PCI-X, AGP.FPCIEXP1, FPCIEXP4, FPCIEXP8,

FPCIEXP16, FPCIEXP16R Удлинители для шин PCI Express X1,

X4, X8 и X16 с гибким кабелем.

Минимальная длина кабеля 2,5 см,

стандартная длина кабеля при заказе

7,62 см, можно заказать длину кабеля

до 38 см, также можно

заказать разъемы F-M, M-M,

CX(TX/RX crossed). Кабель

экранированный.

FPCIEXP16R доступен в

двухвариантах – с разъемом M

54.

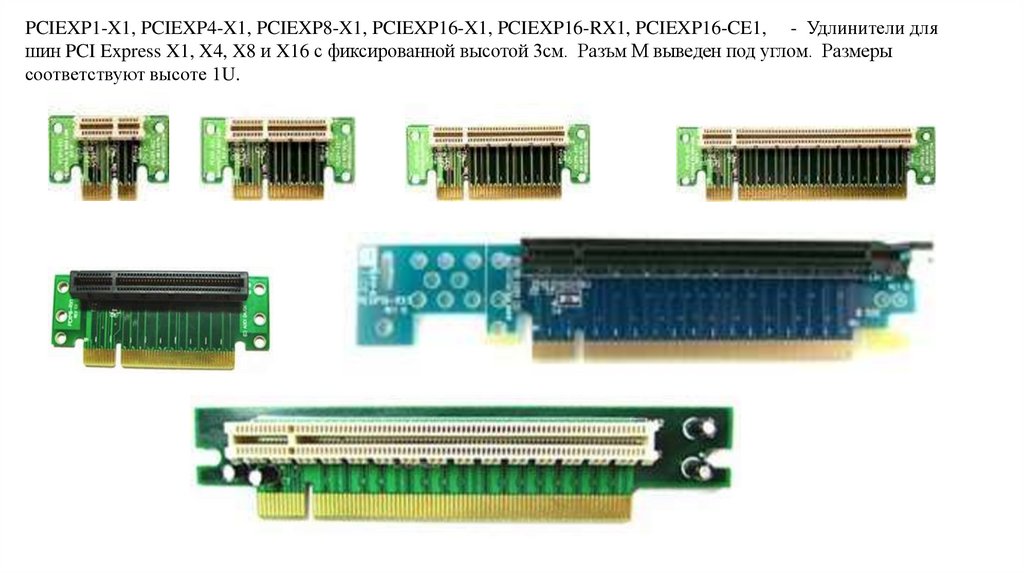

PCIEXP1-X1, PCIEXP4-X1, PCIEXP8-X1, PCIEXP16-X1, PCIEXP16-RX1, PCIEXP16-CE1, - Удлинители дляшин PCI Express X1, X4, X8 и X16 с фиксированной высотой 3см. Разъм М выведен под углом. Размеры

соответствуют высоте 1U.

55.

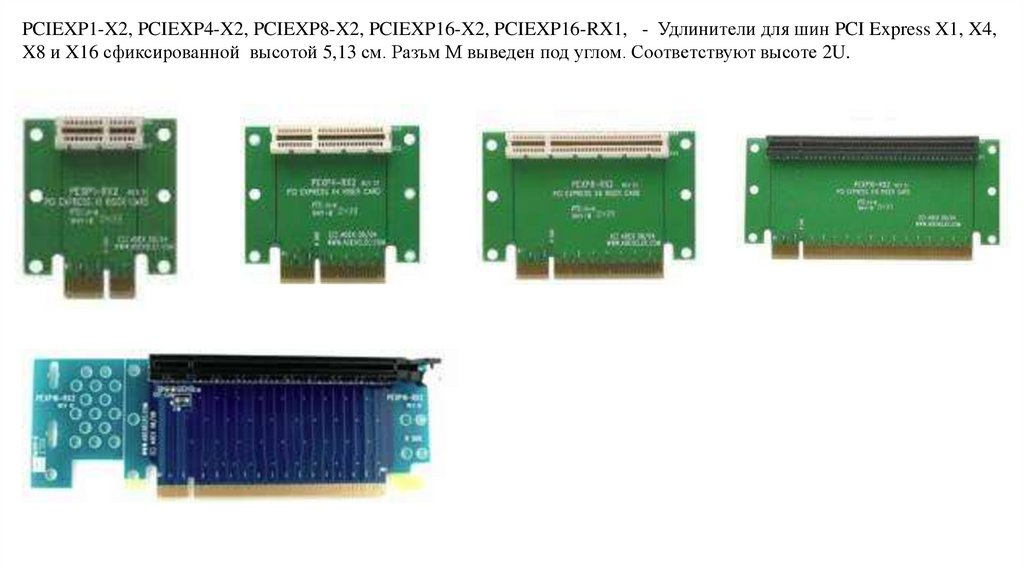

PCIEXP1-X2, PCIEXP4-X2, PCIEXP8-X2, PCIEXP16-X2, PCIEXP16-RX1, - Удлинители для шин PCI Express X1, X4,X8 и X16 сфиксированной высотой 5,13 см. Разъм М выведен под углом. Соответствуют высоте 2U.

56.

PCIEXP1-X3, PCIEXP4-X3, PCIEXP8-X3 и PCIEXP16-X3 - Удлинителидля шин PCI Express X1, X4, X8 и X16 сфиксированнойвысотой 7,16 см. Разъм М выведен под углом. Соответствуют высоте 3U.

57.

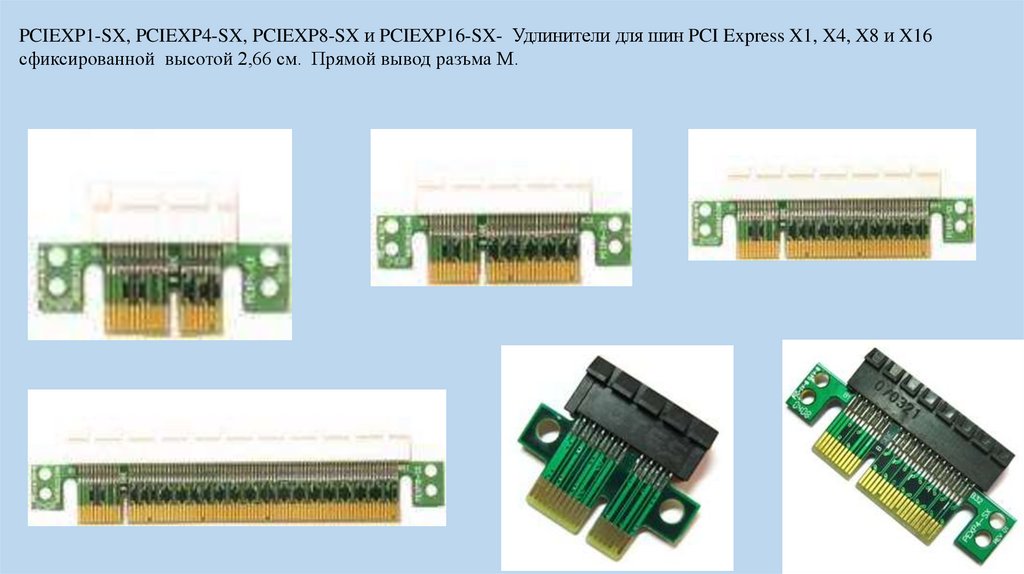

PCIEXP1-SX, PCIEXP4-SX, PCIEXP8-SX и PCIEXP16-SX- Удлинители для шин PCI Express X1, X4, X8 и X16сфиксированной высотой 2,66 см. Прямой вывод разъма М.

58.

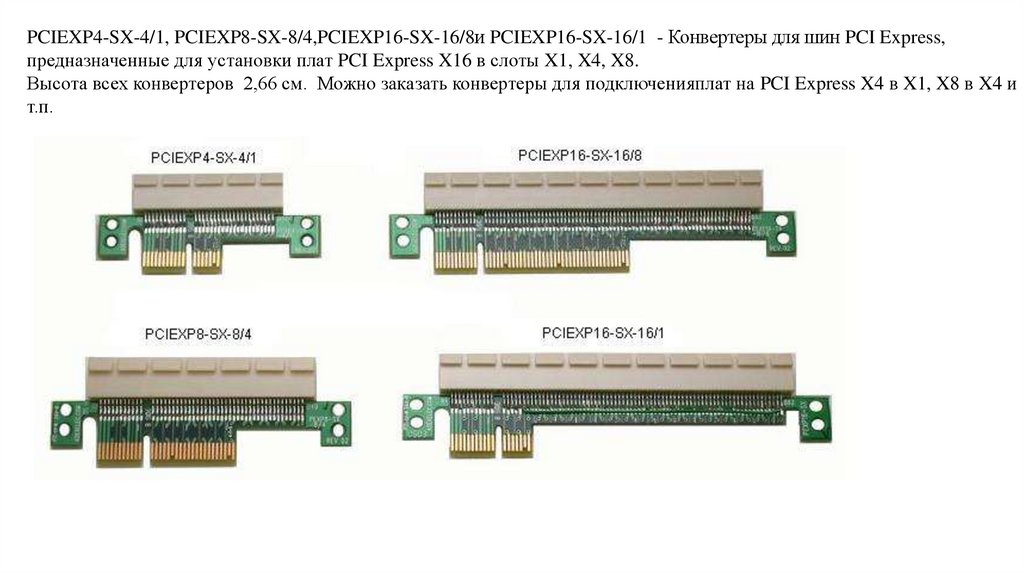

PCIEXP4-SX-4/1, PCIEXP8-SX-8/4,PCIEXP16-SX-16/8и PCIEXP16-SX-16/1 - Конвертеры для шин PCI Express,предназначенные для установки плат PCI Express X16 в слоты X1, X4, X8.

Высота всех конвертеров 2,66 см. Можно заказать конвертеры для подключенияплат на PCI Express X4 в X1, X8 в X4 и

т.п.

59.

PCIEXP16-SL057Гибкий удлинитель для PCI-Express 16x.

60.

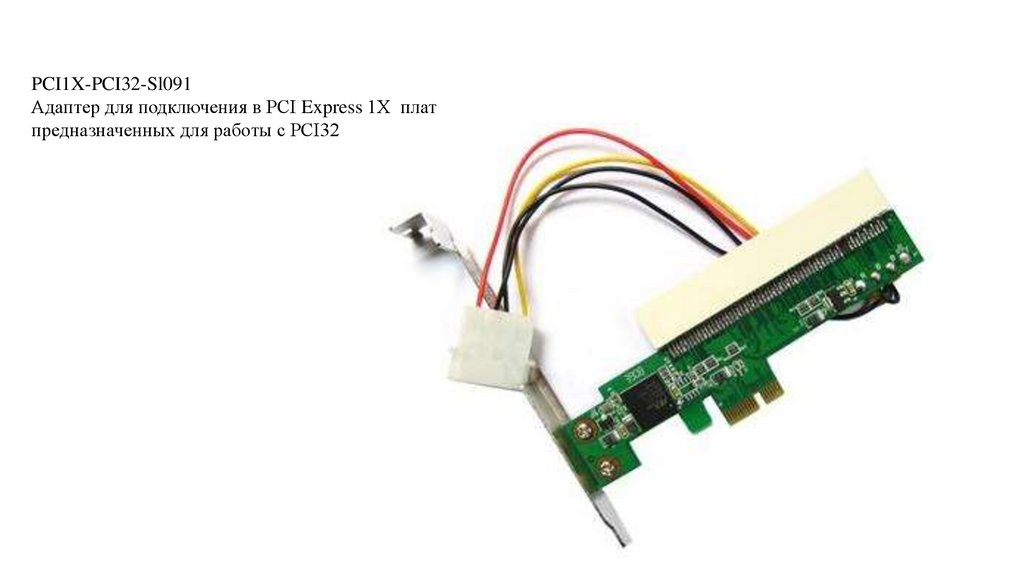

PCI1X-PCI32-Sl091Адаптер для подключения в PCI Express 1X плат

предназначенных для работы с PCI32

61.

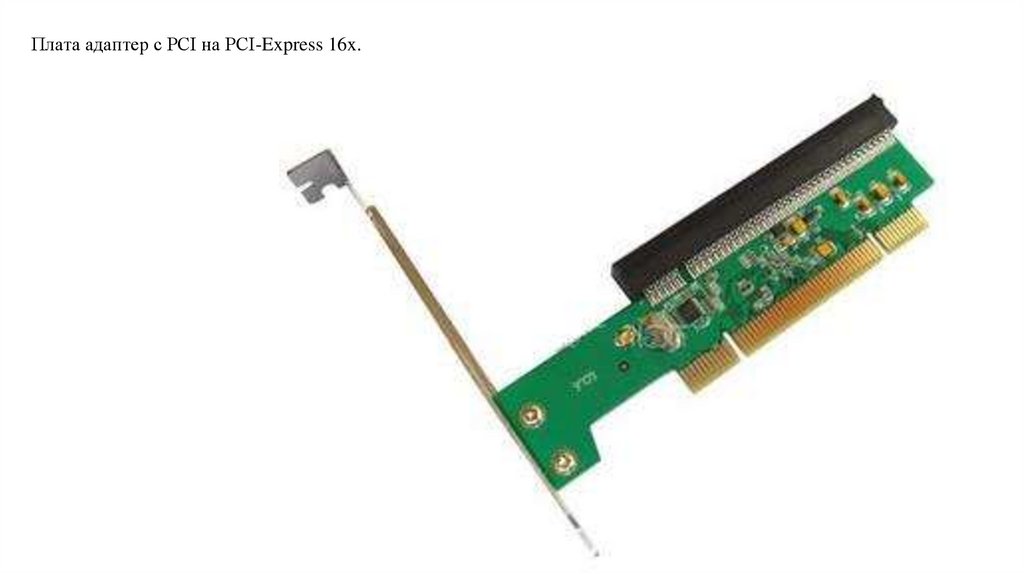

Плата адаптер с PCI на PCI-Express 16x.62.

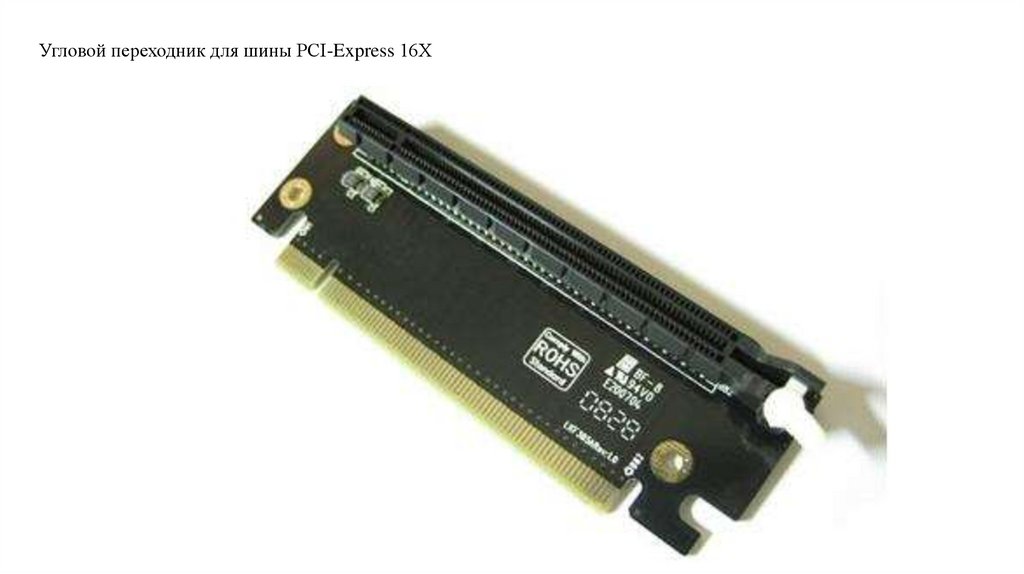

Угловой переходник для шины PCI-Express 16Х63.

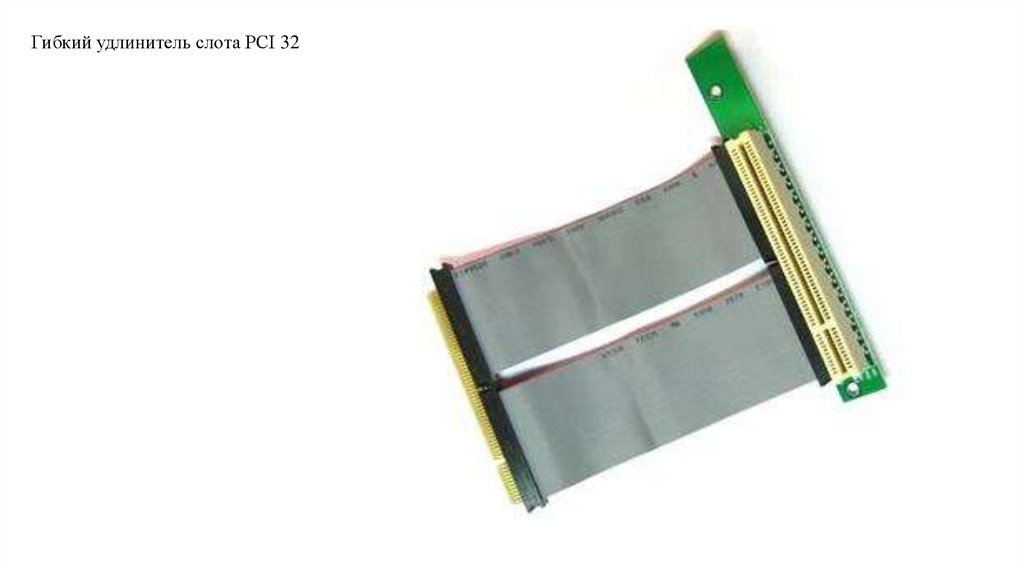

Гибкий удлинитель слота PCI 3264.

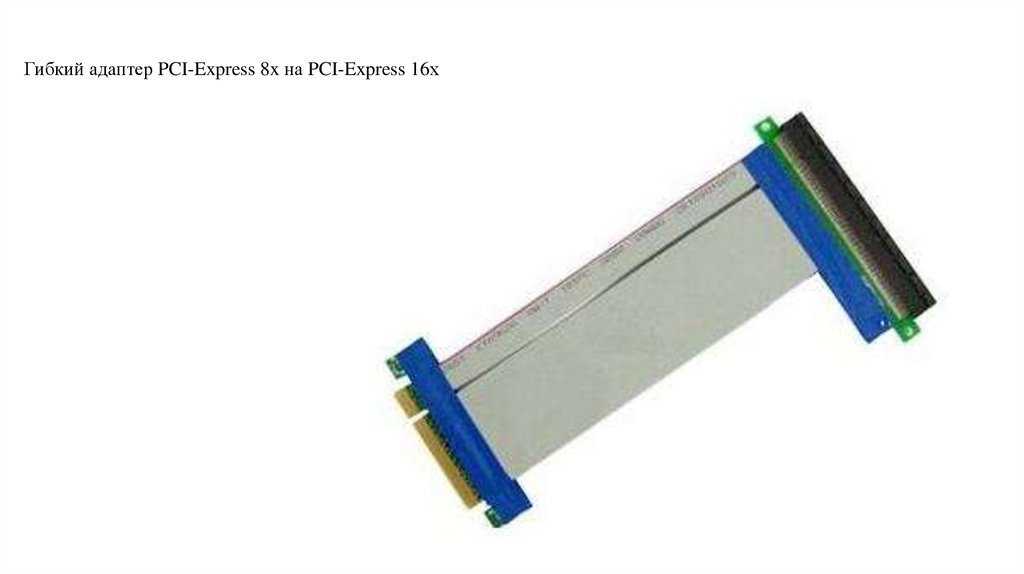

Гибкий адаптер PCI-Express 8x на PCI-Express 16х65.

Райзер карта расширитель двух слотов PCI66.

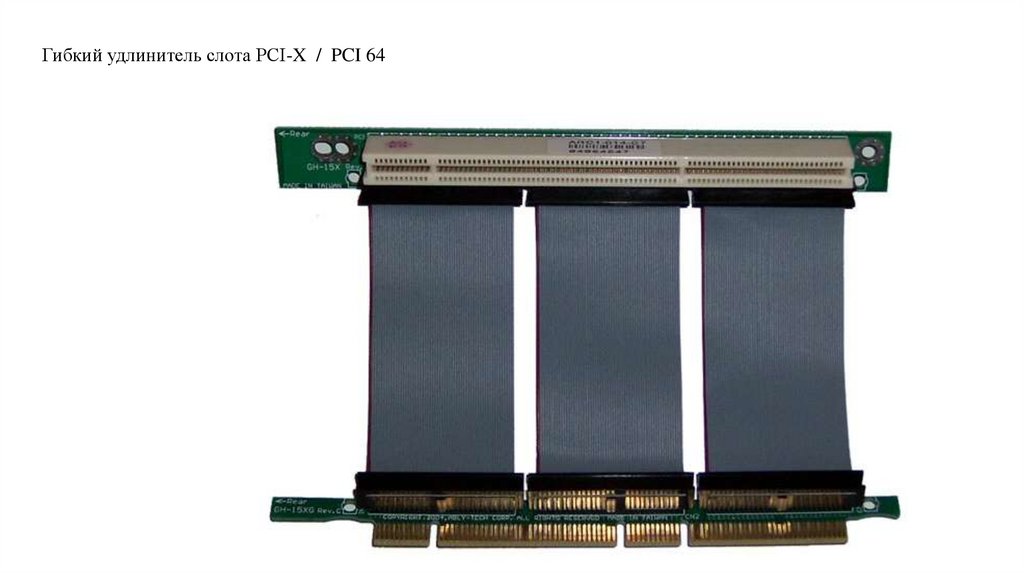

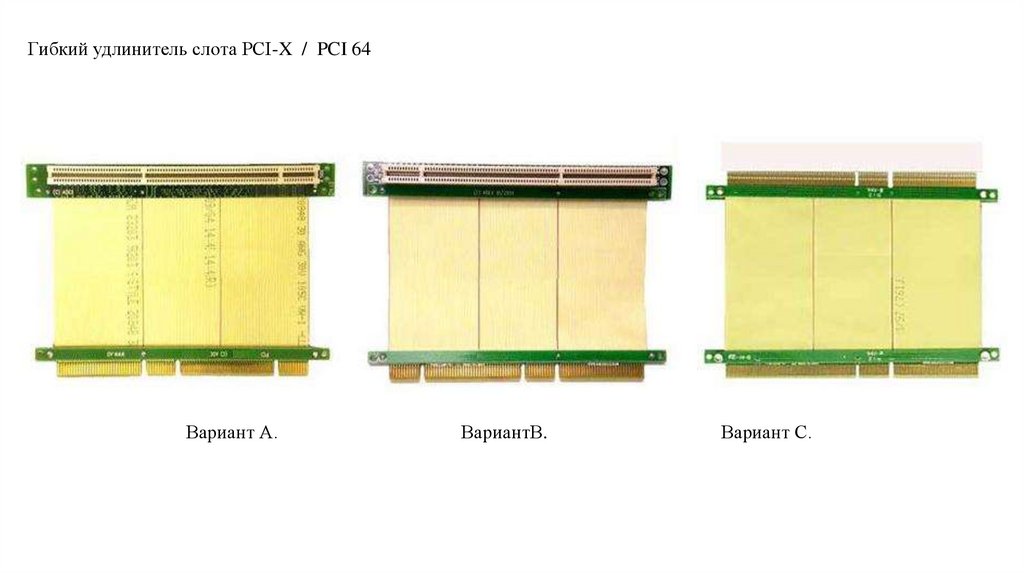

Гибкий удлинитель слота PCI-X / PCI 6467.

Гибкий удлинитель слота PCI-X / PCI 64Вариант А.

ВариантB.

Вариант С.

68.

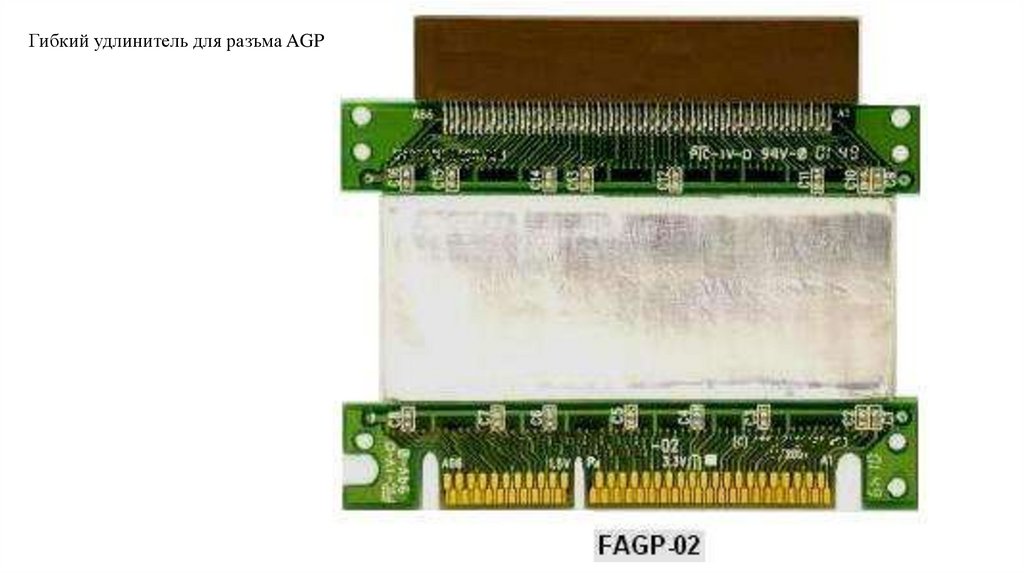

Гибкий удлинитель для разъма AGP69.

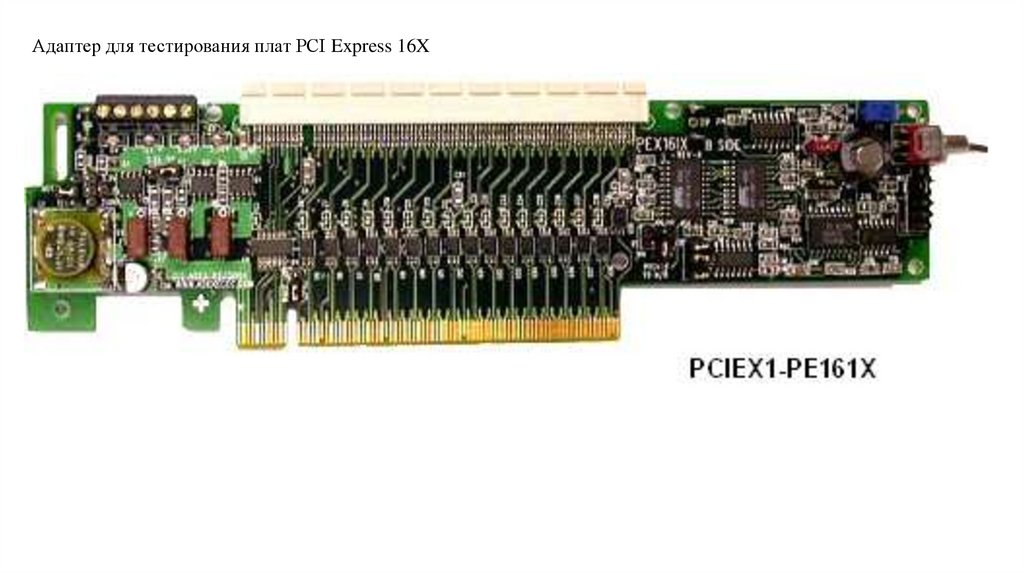

Адаптер для тестирования плат PCI Express 16X70.

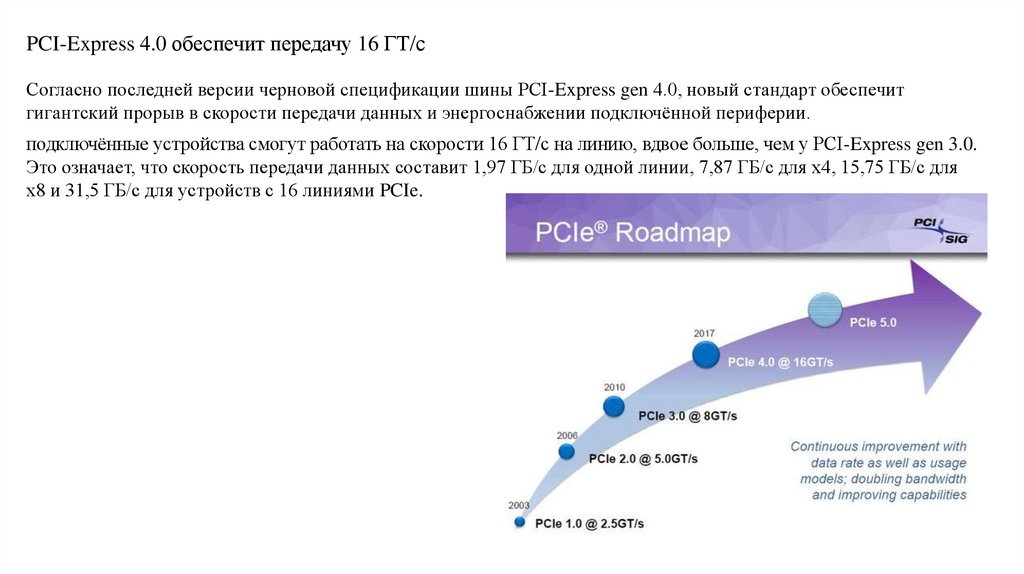

PCI-Express 4.0 обеспечит передачу 16 ГТ/сСогласно последней версии черновой спецификации шины PCI-Express gen 4.0, новый стандарт обеспечит

гигантский прорыв в скорости передачи данных и энергоснабжении подключённой периферии.

подключённые устройства смогут работать на скорости 16 ГТ/с на линию, вдвое больше, чем у PCI-Express gen 3.0.

Это означает, что скорость передачи данных составит 1,97 ГБ/с для одной линии, 7,87 ГБ/с для x4, 15,75 ГБ/с для

x8 и 31,5 ГБ/с для устройств с 16 линиями PCIe.

Электроника

Электроника