Похожие презентации:

Принцип побудови основних функціональних вузлів

1.

Факультет військової підготовкиКафедра ВТП

Предмет: “УСТРІЙ ТА БОЙОВЕ

ЗАСТОСУВАННЯ КЗА 86Ж6”

Тема 2. Типові елементи і вузли апаратури

Заняття 1. Принцип побудови основних

функціональних вузлів

Навчальна мета:

1. Вивчити схемну побудову типових елементів

заміни.

2. Навчити користуватися технічною документацією.

Доцент кафедри ВТП, полковник Казанцев О. Ю.

1

2.

Навчальні питання:1. Призначення, склад, принцип роботи регістрів.

2. Призначення, склад, принцип роботи.

Лічильники, суматори, шифратори, дешифратори,

аналоговий (ТЕЗ АНШ-118).

Інформаційно-методичне забезпечення:

1.

2.

3.

4.

Лекція.

Робочий зошит студента.

Презентація УБЗ 2.1.

Устрій та бойове застосування КЗА 86Ж6.

Частина І. К., - 2001.- 206 с.

2

3.

1. Призначення, склад, принципроботи регістрів (ТЕЗ ЛУШ-0-011)

ТЕЗ-ЛУШ-0-011

(регістр)

призначений

для

записування,

тимчасового зберігання та видачі

інформації.

В ТЕЗі 16 синхронних тригерів

типу DV.

Входи D1-D16 – інформаційні

входи тригерів, 1÷16 – парафазні

виходи відповідних тригерів.

Входи

синхронізації

тригерів

об'єднані та підключені до контакту

роз`єднання

«СИНХРОНИЗАЦИЯ»

(С).

50

R

15

C

61

11

5

12

6

10

7

46

17

21

18

22

16

23

29

55

30

56

60

28

68

59

65

64

42

53

54

41

49

43

VA

V1

D1

V2

D2

V3

D3

V4

D4

V5

D5

V6

D6

V7

D7

V8

D8

VB

V9

D9

D1

0

V10

D11

D1

V11

2

D1

3D

V12

14

D1

5D

16

RG

0-011

4

1 3

9

2 8

14

3 13

20

4 19

25

5 24

27

6 26

32

7 31

34

8 33

69

9 70

66

10 67

62

11 63

57

12 58

51

13 52

47

14 48

44

15 45

39

16 40

3

4.

50R

15

C

61

Для керування синхронізацією

служать

входи

«ГРУППОВОЕ

РАЗРЕШЕНИЕ»

(Va,Vb)

і

«РАЗРЕШЕНИЕ» (V1-V8, V9-V12).

11

5

12

6

10

7

46

17

21

18

22

16

23

29

55

30

56

60

28

68

59

65

64

42

53

54

41

49

43

VA

V1

D1

V2

D2

V3

D3

V4

D4

V5

D5

V6

D6

V7

D7

V8

D8

VB

V9

D9

D1

0

V10

D11

D1

V11

2

D1

3D

V12

14

D1

5D

16

RG

0-011

4

1 3

9

2 8

14

3 13

20

4 19

25

5 24

27

6 26

32

7 31

34

8 33

69

9 70

66

10 67

62

11 63

57

12 58

51

13 52

47

14 48

44

15 45

39

16 40

4

5.

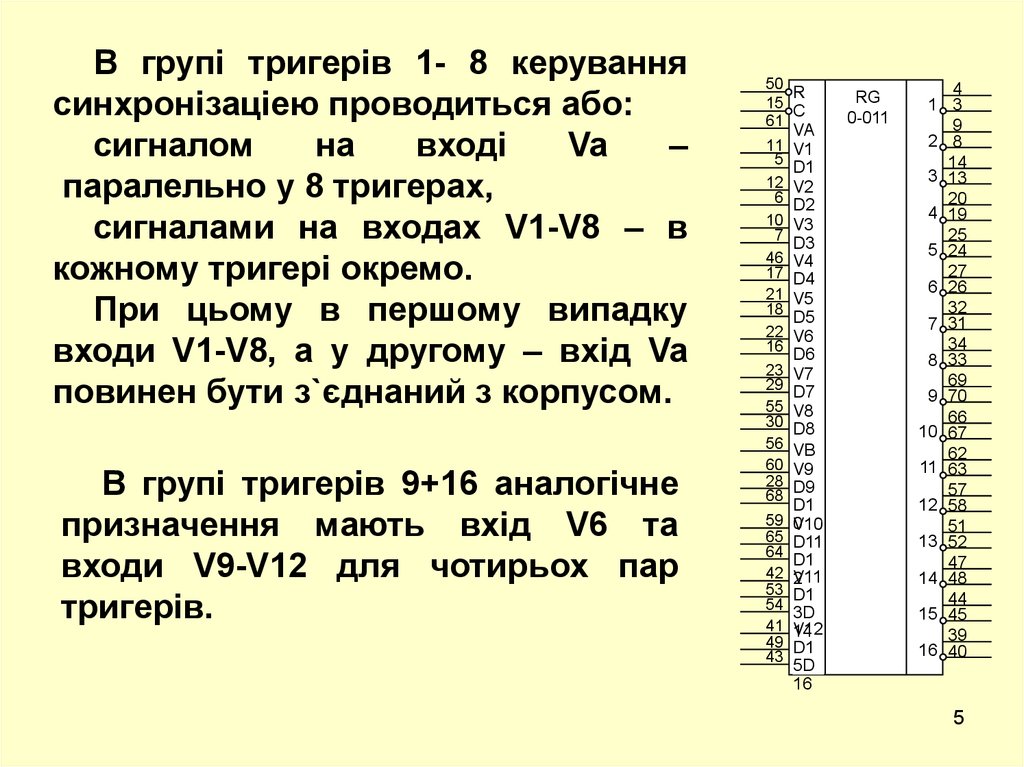

В групі тригерів 1- 8 керуваннясинхронізаціею проводиться або:

сигналом

на

вході

Va

–

паралельно у 8 тригерах,

сигналами на входах V1-V8 – в

кожному тригері окремо.

При цьому в першому випадку

входи V1-V8, а у другому – вхід Va

повинен бути з`єднаний з корпусом.

В групі тригерів 9+16 аналогічне

призначення мають вхід V6 та

входи V9-V12 для чотирьох пар

тригерів.

50

R

15

C

61

11

5

12

6

10

7

46

17

21

18

22

16

23

29

55

30

56

60

28

68

59

65

64

42

53

54

41

49

43

VA

V1

D1

V2

D2

V3

D3

V4

D4

V5

D5

V6

D6

V7

D7

V8

D8

VB

V9

D9

D1

0

V10

D11

D1

V11

2

D1

3D

V12

14

D1

5D

16

RG

0-011

4

1 3

9

2 8

14

3 13

20

4 19

25

5 24

27

6 26

32

7 31

34

8 33

69

9 70

66

10 67

62

11 63

57

12 58

51

13 52

47

14 48

44

15 45

39

16 40

5

6.

50R

15

C

61

Скидання регістру в нульове

положення здіснюється асинхронно

сигналом логічного нуля на вході

«УСТАНОВКА В НУЛЬ» (R), який

надходить одночасно на всі 16

тригерів.

11

5

12

6

10

7

46

17

21

18

22

16

23

29

55

30

56

60

28

68

59

65

64

42

53

54

41

49

43

VA

V1

D1

V2

D2

V3

D3

V4

D4

V5

D5

V6

D6

V7

D7

V8

D8

VB

V9

D9

D1

0

V10

D11

D1

V11

2

D1

3D

V12

14

D1

5D

16

RG

0-011

4

1 3

9

2 8

14

3 13

20

4 19

25

5 24

27

6 26

32

7 31

34

8 33

69

9 70

66

10 67

62

11 63

57

12 58

51

13 52

47

14 48

44

15 45

39

16 40

6

7.

tnR

C

Va

tn+1

V1 D1

Qn+1

0

X

X

0

X

0

1

1

1

1

1

1

1

1

0

0

0

0

0

1

0

Qn

Qn

0

1

1

0

0

1

1

Представлена таблиця істинності

DV

тригера

при

керуванні

синхронізацією сигналом на входи

Vа (паралельно у 8 тригерах)

50

R

15

C

61

11

5

12

6

10

7

46

17

21

18

22

16

23

29

55

30

56

60

28

68

59

65

64

42

53

54

41

49

43

VA

V1

D1

V2

D2

V3

D3

V4

D4

V5

D5

V6

D6

V7

D7

V8

D8

VB

V9

D9

D1

0

V10

D11

D1

V11

2

D1

3D

V12

14

D1

5D

16

RG

0-011

4

1 3

9

2 8

14

3 13

20

4 19

25

5 24

27

6 26

32

7 31

34

8 33

69

9 70

66

10 67

62

11 63

57

12 58

51

13 52

47

14 48

44

15 45

39

16 40

7

8.

Входи50

R

0

1

1

133ЛА6

У43

Б2

1

1

133ЛА6

У26

Б10

1

6

0

3

1

9

133ЛА6

У43

Б2

1

4

133ЛА6

У25

В10

Гн 12

8

0

tn

R

1

6

1

1

133ЛА6

У27

А8

1

0

1

3 12

133ЛА6

У28

Е8

Гн 5

15

c

59

VA

11

V1

0

5

D1

1

1

1

133ЛА6

У44

Е6

&

12

133ЛА3

13 У30

Б6

&

2

133ЛА3

1 У23

В2

9 &

10 133ЛА4

11 У19

Б3

&

1

133ЛА3

2 У2

Б5

1

11 9

133ЛА6

У45

Е10

6

8

0

3

D1

Qn+1

8

0

1 1

1

0

0

Qn

1 1

1

0

1

Qn

1 1

0

0

0

0

1 1

0

0

1

1

Гн 14

4 &

5 133ЛА4

3 У34

В8

1

8

3

V1

0 X X 0 X

11

0

Va

Гн 4

Гн 1

1

9

133ЛА6

У44

Е6

C

tn+1

0

6

1

&

10

133ЛА3

9 У2

Б5

&

5

133ЛА3

4 У2

Б5

8

6

0

1

3&

2

4

1

133ЛР1

У10

Б9

1&

9

10

1

133ЛР1

У10

Б9

Виходи

6

3

1вих

8

4

1вих

1

0

8

9.

Вхо50

R

1

1д

и133ЛА6

У43

Б2

1

9

133ЛА6

У43

Б2

6

Гн 12

8

tn

Va

V1

D1

Qn+1

0 X 0

1 1 0

X

1

X

0

0

Qn

1 1 0

1 1 0

1 1 0

1

0

0

1

0

1

Qn

0

1

R

1

1

133ЛА6

У26

Б10

1

4

133ЛА6

У25

В10

3

6

1

1

133ЛА6

У27

А8

1

3 12

133ЛА6

У28

Е8

Гн 5

15

S

61

VA

11

V1

5

D1

1

1

133ЛА6

У44

Е6

&

13

133ЛА3

12 У30

Б6

&

1

133ЛА3

2 У1

А5

9 &

10 133ЛА4

11 У19

Б3

&

1

133ЛА3

2 У2

Б5

1

11 9

133ЛА6

У45

Е10

6

8

8

11

Гн 14

3

8

3

4 &

5 133ЛА4

3 У18

А3

6

&

10

133ЛА3

9 У2

Б5

&

5

133ЛА3

4 У2

Б5

8

6

C

Гн 4

Гн 1

1

9

133ЛА6

У44

Е6

tn+1

3&

2

4

1

133ЛР1

У10

Б9

1&

9

10

1

133ЛР1

У10

Б9

Виход

6

3и

1вих

8

Представлена

таблиця істинності DV

тригера при керуванні

синхронізаціею

сигналом на вході V1

(індивидуально одним

тригером).

4

1вих

9

10.

2. Призначення, склад, принцип роботи.Лічильник (ТЕЗ-ЛУШ-0-022), суматор

(ТЕЗ ЛУШ-0-009), шифратор (ТЕЗ ЛУШ-1-016),

дешифратор ( ТЕЗ ЛУШ-0-008 ), аналоговий

(ТЕЗ АНШ-118)

10

11.

51R1

16

26

29

13

25

30

34

22

C 0-022

+1

0

-1

1

зап

2

D0

3

D1

D2

P

D3

PC

15

5

4

12

6

52

55

45

11

C

+1

-1

P

зап

D0

D1

D2

D3

65

R2

70

57

60

C

+1

-1

61

62

&

P

69

14

20

66

48

зап

D0

D1

D2

D3

63

56

59

C

+1

-1

64

67

68

&

P

?

7

30

43

46

39

зап

D0

D1

D2

D3

СТ

0

1

2

3

24

21

3

33

8

28

31

23

19

17

P 27

PC 58

0

1

2

3

44

54

40

41

P 10

PC 16

0

1

2

3

47

53

42

9

P 32

PC 49

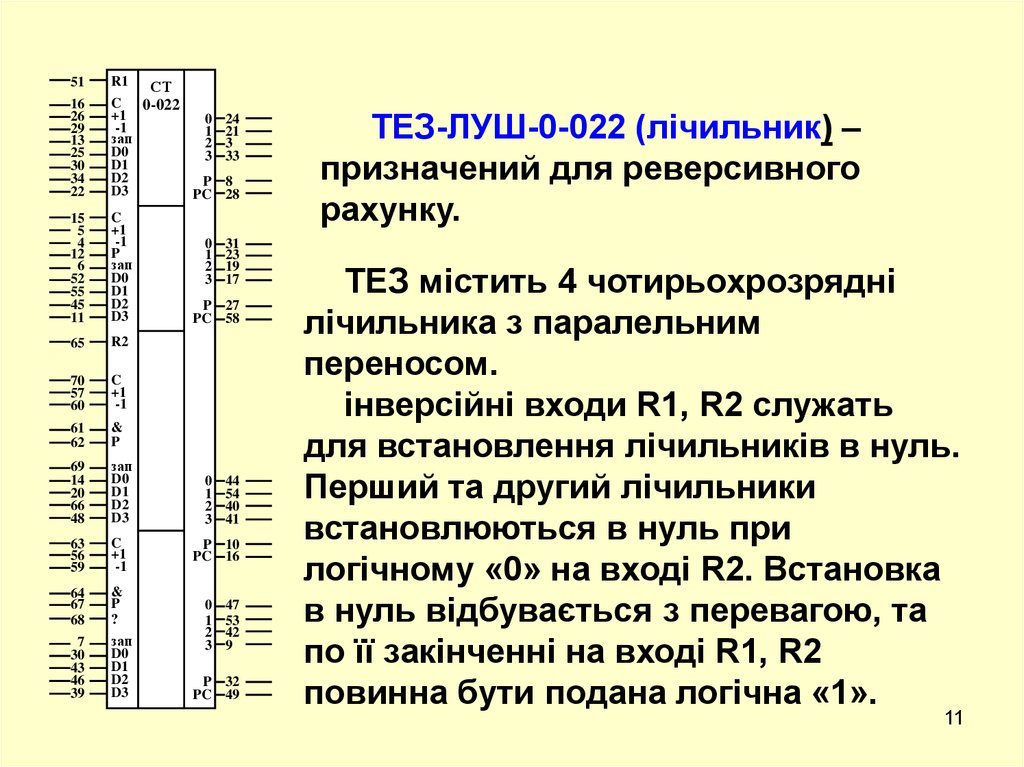

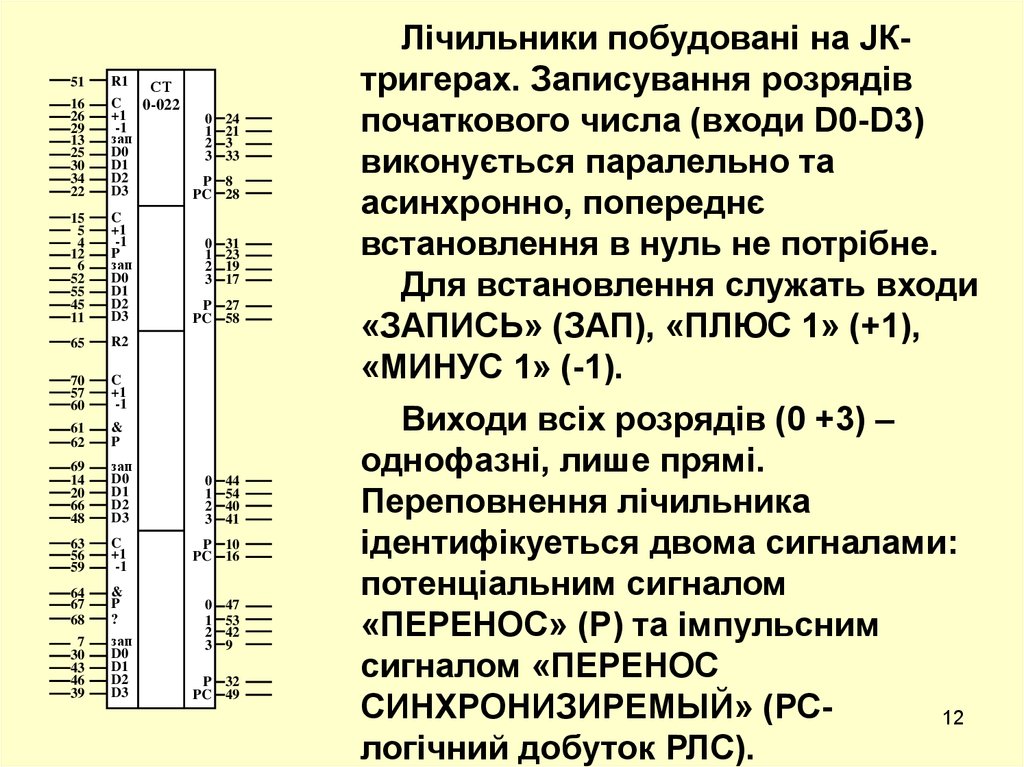

ТЕЗ-ЛУШ-0-022 (лічильник) –

призначений для реверсивного

рахунку.

ТЕЗ містить 4 чотирьохрозрядні

лічильника з паралельним

переносом.

інверсійні входи R1, R2 служать

для встановлення лічильників в нуль.

Перший та другий лічильники

встановлюються в нуль при

логічному «0» на вході R2. Встановка

в нуль відбувається з перевагою, та

по її закінченні на вході R1, R2

повинна бути подана логічна «1».

11

12.

51R1

16

26

29

13

25

30

34

22

C 0-022

+1

0

-1

1

зап

2

D0

3

D1

D2

P

D3

PC

15

5

4

12

6

52

55

45

11

C

+1

-1

P

зап

D0

D1

D2

D3

65

R2

70

57

60

C

+1

-1

61

62

&

P

69

14

20

66

48

зап

D0

D1

D2

D3

63

56

59

C

+1

-1

64

67

68

&

P

?

7

30

43

46

39

зап

D0

D1

D2

D3

СТ

0

1

2

3

24

21

3

33

8

28

31

23

19

17

P 27

PC 58

0

1

2

3

44

54

40

41

P 10

PC 16

0

1

2

3

47

53

42

9

P 32

PC 49

Лічильники побудовані на JКтригерах. Записування розрядів

початкового числа (входи D0-D3)

виконується паралельно та

асинхронно, попереднє

встановлення в нуль не потрібне.

Для встановлення служать входи

«ЗАПИСЬ» (ЗАП), «ПЛЮС 1» (+1),

«МИНУС 1» (-1).

Виходи всіх розрядів (0 +3) –

однофазні, лише прямі.

Переповнення лічильника

ідентифікуеться двома сигналами:

потенціальним сигналом

«ПЕРЕНОС» (Р) та імпульсним

сигналом «ПЕРЕНОС

СИНХРОНИЗИРЕМЫЙ» (РС12

логічний добуток РЛС).

13.

51R1

16

26

29

13

25

30

34

22

C

+1

-1

зап

D0

D1

D2

D3

15

5

4

12

6

52

55

45

11

C

+1

-1

P

зап

D0

D1

D2

D3

65

R2

70

57

60

C

+1

-1

61

62

&

P

69

14

20

66

48

зап

D0

D1

D2

D3

63

56

59

C

+1

-1

64

67

68

&

P

?

7

30

43

46

39

зап

D0

D1

D2

D3

СТ

0-022

0

1

2

3

24

21

3

33

P 8

PC 28

0

1

2

3

31

23

19

17

P 27

PC 58

0

1

2

3

44

54

40

41

P 10

PC 16

0

1

2

3

47

53

42

9

З лічильників ТЕЗа-ЛУШ-0-022

шляхом безпосереднього їх

з`єднання можна побудувати

багатотетрадні лічильники

розрядністю до 16. Для цієї цілі

передбачені входи «ПЕРЕНОС» (Р0

до другого, третього та четвертого

личильників.

Побудову багатотетрадного

лічильника необхідно виконувати

слідуючим чином. Розташувати

лічильники ТЕЗа-ЛУШ-0-022 згідно

старшинства тетрад в порядку

зростання числа виходів «Р».

P 32

PC 49

13

14.

51R1

16

26

29

13

25

30

34

22

C

+1

-1

зап

D0

D1

D2

D3

15

5

4

12

6

52

55

45

11

C

+1

-1

P

зап

D0

D1

D2

D3

65

R2

70

57

60

C

+1

-1

61

62

&

P

69

14

20

66

48

зап

D0

D1

D2

D3

63

56

59

C

+1

-1

64

67

68

&

P

?

7

30

43

46

39

зап

D0

D1

D2

D3

СТ

0-022

0

1

2

3

24

21

3

33

P 8

PC 28

0

1

2

3

31

23

19

17

P 27

PC 58

0

1

2

3

44

54

40

41

P 10

PC 16

0

1

2

3

47

53

42

9

P 32

PC 49

Підключити до входів Р кожної

тетради виходи Р попередніх

тетрад. Використати в якості

молодшої тетради перший

лічильник, який немає виходів Р.

Об`єднати однойменні входи С, Р,

ЗАП, +1, -1.

У лічильника будь-якої

розрядності невикористані входи Р

повинні бути з`єднані до Иоп.

При побудові лічильників

великої розрядності необхідні

додаткові мікросхеми для

складання переносів у п`яту і т.д.

тетради, та необхідно враховувати

відповідне збільшення часу.

14

15.

SM 10-009

62

R

47

53

A0

Б0

0

26

46

50

А1

Б1

1

27

51

52

А2

Б2

2

8

42

41

А3

Б3

3

17

68

60

А4

Б4

4

33

56

67

А5

Б5

5

34

64

58

А6

Б6

6

20

63

59

А7

Б7

7

31

ИЛИ

И

+

V1

9

48

65

49

54

V2

66

70

16

19

22

21

13

10

4

15

6

14

25

11

5

23

3

32

7

Р1

Р2

Р3

Р4

Р5

Р6

Р7

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

P1

P2

55

28

K1

K2

K3

K4

K5

K6

61

40

39

69

24

44

K7

12

18

30

29

K8

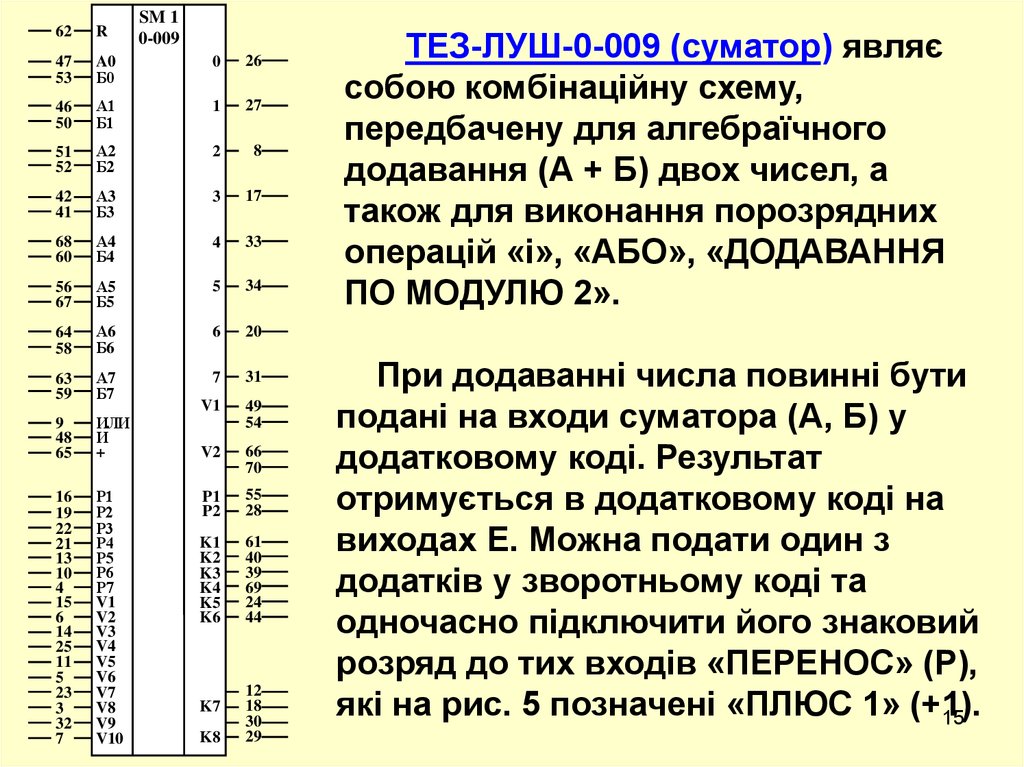

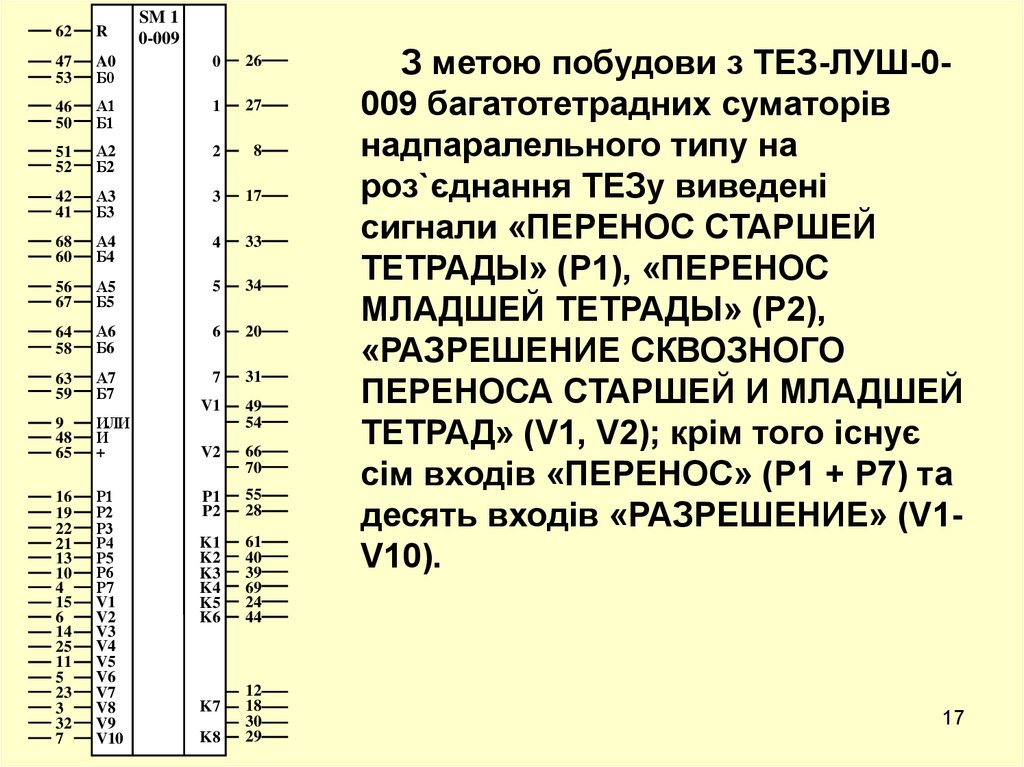

ТЕЗ-ЛУШ-0-009 (суматор) являє

собою комбінаційну схему,

передбачену для алгебраїчного

додавання (А + Б) двох чисел, а

також для виконання порозрядних

операцій «і», «АБО», «ДОДАВАННЯ

ПО МОДУЛЮ 2».

При додаванні числа повинні бути

подані на входи суматора (А, Б) у

додатковому коді. Результат

отримується в додатковому коді на

виходах Е. Можна подати один з

додатків у зворотньому коді та

одночасно підключити його знаковий

розряд до тих входів «ПЕРЕНОС» (Р),

які на рис. 5 позначені «ПЛЮС 1» (+1).

15

16.

SM 10-009

62

R

47

53

A0

Б0

0

26

46

50

А1

Б1

1

27

51

52

А2

Б2

2

8

42

41

А3

Б3

3

17

68

60

А4

Б4

4

33

56

67

А5

Б5

5

34

64

58

А6

Б6

6

20

63

59

А7

Б7

7

31

ИЛИ

И

+

V1

9

48

65

49

54

V2

66

70

16

19

22

21

13

10

4

15

6

14

25

11

5

23

3

32

7

Р1

Р2

Р3

Р4

Р5

Р6

Р7

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

P1

P2

55

28

K1

K2

K3

K4

K5

K6

61

40

39

69

24

44

K7

12

18

30

29

K8

Дія А-Б реалізується як

складання А + (-Б). Якщо виходити

з додаткових кодів чисел А, Б

(наприклад, числа зчитуються з

пам`яті у додатковому коді), то

зручно зробити слідуючим чином:

проінвертувати додатковий вхід

віднімаємого Б і подати на входи Б,

а до виходів +1 підвести сигнал

логічна «1».

Для керування служать входи

«РАЗРЕШЕНИЕ И» (И),

«РАЗРЕШЕНИЕ ИЛИ» (ИЛИ),

«РАЗРЕШЕНИЕ СЛОЖЕНИЯ ПО

МОДУЛЮ 2» (+), «УСТАНОВКА В

НУЛЬ» (R).

16

17.

SM 10-009

62

R

47

53

A0

Б0

0

26

46

50

А1

Б1

1

27

51

52

А2

Б2

2

8

42

41

А3

Б3

3

17

68

60

А4

Б4

4

33

56

67

А5

Б5

5

34

64

58

А6

Б6

6

20

63

59

А7

Б7

7

31

ИЛИ

И

+

V1

9

48

65

49

54

V2

66

70

16

19

22

21

13

10

4

15

6

14

25

11

5

23

3

32

7

Р1

Р2

Р3

Р4

Р5

Р6

Р7

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

P1

P2

55

28

K1

K2

K3

K4

K5

K6

61

40

39

69

24

44

K7

12

18

30

29

K8

З метою побудови з ТЕЗ-ЛУШ-0009 багатотетрадних суматорів

надпаралельного типу на

роз`єднання ТЕЗу виведені

сигнали «ПЕРЕНОС СТАРШЕЙ

ТЕТРАДЫ» (Р1), «ПЕРЕНОС

МЛАДШЕЙ ТЕТРАДЫ» (Р2),

«РАЗРЕШЕНИЕ СКВОЗНОГО

ПЕРЕНОСА СТАРШЕЙ И МЛАДШЕЙ

ТЕТРАД» (V1, V2); крім того існує

сім входів «ПЕРЕНОС» (Р1 + Р7) та

десять входів «РАЗРЕШЕНИЕ» (V1V10).

17

18.

6934

70

33

31

32

68

67

25

24

30

26

52

59

55

18

50

14

15

51

7

13

8

44

5

42

6

41

3

40

4

39

48

49

45

46

10

47

54

19

56

20

57

21

29

64

62

Uоп

0

CD

1

2 1-016

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

12

43

1

11

9

2

22

16

3

58

17

4

65

60

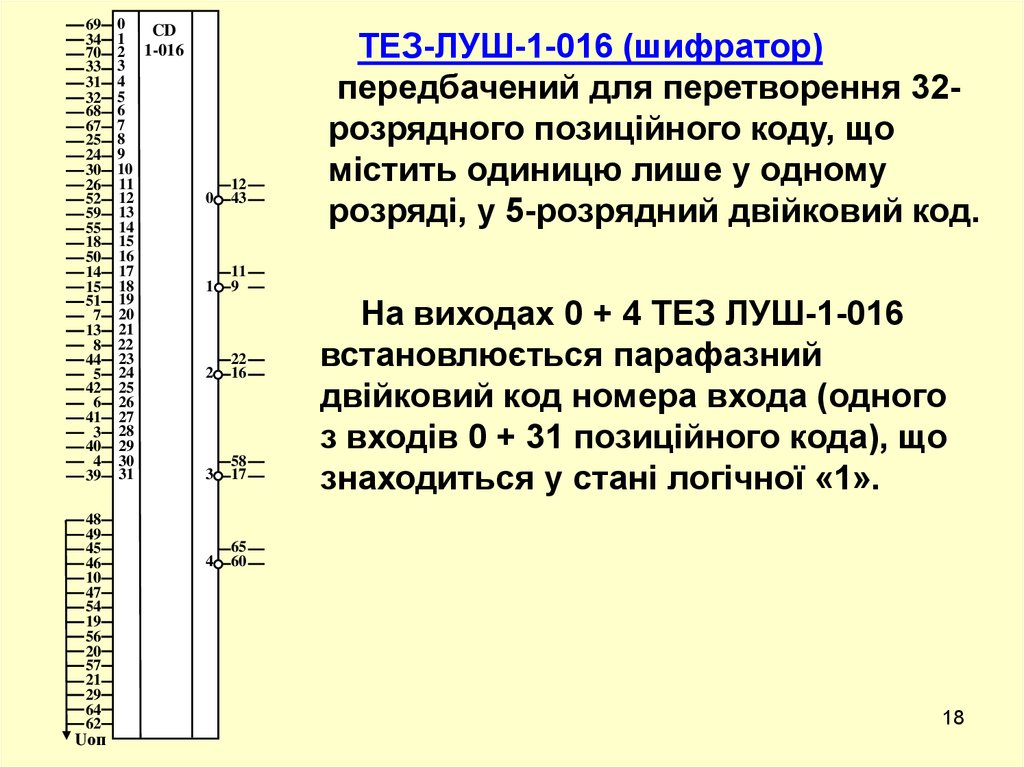

ТЕЗ-ЛУШ-1-016 (шифратор)

передбачений для перетворення 32розрядного позиційного коду, що

містить одиницю лише у одному

розряді, у 5-розрядний двійковий код.

На виходах 0 + 4 ТЕЗ ЛУШ-1-016

встановлюється парафазний

двійковий код номера входа (одного

з входів 0 + 31 позиційного кода), що

знаходиться у стані логічної «1».

18

19.

6934

70

33

31

32

68

67

25

24

30

26

52

59

55

18

50

14

15

51

7

13

8

44

5

42

6

41

3

40

4

39

48

49

45

46

10

47

54

19

56

20

57

21

29

64

62

Uоп

0

CD

1

2 1-016

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

12

43

1

11

9

2

22

16

3

58

17

4

65

60

Безпосередні входи

позиційного коду повинні бути

підключені до корпусу.

З 2, 3, 4 ТЕЗів ЛУШ-1-016

можна побудувати відповідно

64, 96 та 128 розрядний

шифратор.

ТЕЗ ЛУШ-0-016 приміняється у

пристроях: РМ, УСДК, УСС

19

20.

615

63

51

7

14

68

53

10

25

62

54

5

27

61

43

11

26

57

42

12

67

58

44

16

52

65

45

17

29

21

30

4

3

2

1

V

DC

0-008

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

3

4

8

9

13

14

18

19

20

22

23

28

31

32

34

33

70

69

65

64

60

59

56

55

50

49

48

47

46

41

39

40

ТЕЗ ЛУШ-0-008 (дешифратор)

передбачено для перетворення

двійкового

N-розрядного

парафазного коду в 2N-розрядний

код, що містить одиницю лише в

одному розряді.

20

21.

615

63

51

7

14

68

53

10

25

62

54

5

27

61

43

11

26

57

42

12

67

58

44

16

52

65

45

17

29

21

30

4

3

2

1

V

DC

0-008

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

3

4

8

9

13

14

18

19

20

22

23

28

31

32

34

33

70

69

65

64

60

59

56

55

50

49

48

47

46

41

39

40

В залежності від схеми включення,

ТЕЗ ЛУШ-0-008 може бути

використаний у слідуючих режимах:

• 4 дешифратора на 3 входа,

• 2 дешифратора на 4 входа,

• 1 дешифратор на 5 входів.

Кожний дешифратор має керуючий

вхід V. Якщо сигнал на вході V –

логічний «0», виконується

дешифрування. Якщо ж сигнал на

вході V – логічна «1», то на

відповідних виходах виникають

сигнали логічного «0» незалежно від

вхідного коду.

ТЕЗ ЛУШ-0-008 в КЗА 86Ж6

приміняється в слідуючих пристроях;

21

РМ, СВ, УИ, УОИ, УСДК.

22.

5 А25

61

15 C

54 R

3

39

6

56

7

43

40

45

42

58

E01

8

E02

63

-50 B

34

70

Иоп

55

69

68

A/B B1 33

44

118

47

11

B2 46

48

B3 12

49

B4 52

57

B5 59

B6

60

62

64

B7 65

67

B8 66

ТЕЗ-АНШ-118 (перетворювач

напруга – код) призначений для

перетворення напруги у

пропорційний йому позиційний

код, в якому номер розряду, що

містить одиницю, пропорційний

до числа, яке відображається.

Цей код на виходах ТЕЗа

запам'ятовується тригерами, які

встановлюються в нуль при

подачі на вхід «УСТАНОВКА В

НУЛЬ» (R) сигналу логічної «1»

та приймають інформацію при

подачі на вхід

«СИНХРОНИЗАЦИЯ» (С) сигналу

22

логічного «0».

23.

5 А25

61

15 C

54 R

3

39

6

56

7

43

40

45

42

58

E01

8

E02

63

-50 B

34

70

Иоп

55

69

A/B B1 33

44

118

47

11

B2 46

48

B3 12

49

B4 52

57

B5 59

B6

60

62

64

B7 65

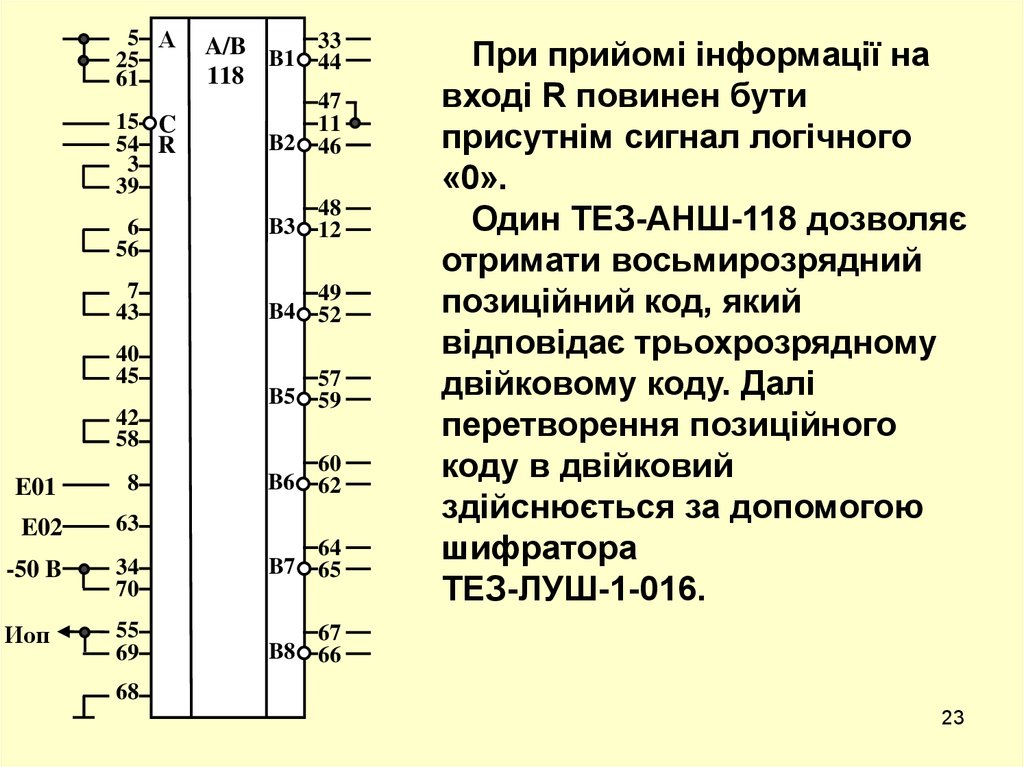

При прийомі інформації на

вході R повинен бути

присутнім сигнал логічного

«0».

Один ТЕЗ-АНШ-118 дозволяє

отримати восьмирозрядний

позиційний код, який

відповідає трьохрозрядному

двійковому коду. Далі

перетворення позиційного

коду в двійковий

здійснюється за допомогою

шифратора

ТЕЗ-ЛУШ-1-016.

67

B8 66

68

23

24.

5 А25

61

15 C

54 R

3

39

6

56

7

43

40

45

42

58

E01

8

E02

63

-50 B

34

70

Иоп

55

69

A/B B1 33

44

118

47

11

B2 46

48

B3 12

49

B4 52

57

B5 59

B6

60

62

64

B7 65

В залежності від величин

еталонних напруг Ео1 та Ео2

можна побудувати

перетворювач напруг на різні

вхідні напруги в межах від -1,6В

до -8В. При цьому різниця

напруг Ео1 та Ео2 визначає

максимальну величину зміни

перетворюємої вхідної напруги,

а величина Ео2 – початковий

вхідний рівень, при перевищенні

якого виконується

перетворення.

67

B8 66

68

24

25.

5 А25

61

15 C

54 R

3

39

6

56

7

43

40

45

42

58

E01

8

E02

63

-50 B

34

70

Иоп

55

69

A/B B1 33

44

118

47

11

B2 46

48

B3 12

49

B4 52

57

B5 59

B6

Для отримання 16-ти, 32-х

розрядного позиційного коду

використовуються відповідно 2

або 4 ТЕЗ-АНШ-118.

Діапазон напруг, що

перетворюються, не залежить

від кількості розрядів та

визначається величинами Ео1

та Ео2.

60

62

64

B7 65

67

B8 66

68

25

26.

5 А25

61

15 C

54 R

3

39

6

56

7

43

40

45

42

58

E01

8

E02

63

-50 B

34

70

Иоп

55

69

A/B B1 33

44

118

47

11

B2 46

48

B3 12

49

B4 52

57

B5 59

B6

60

62

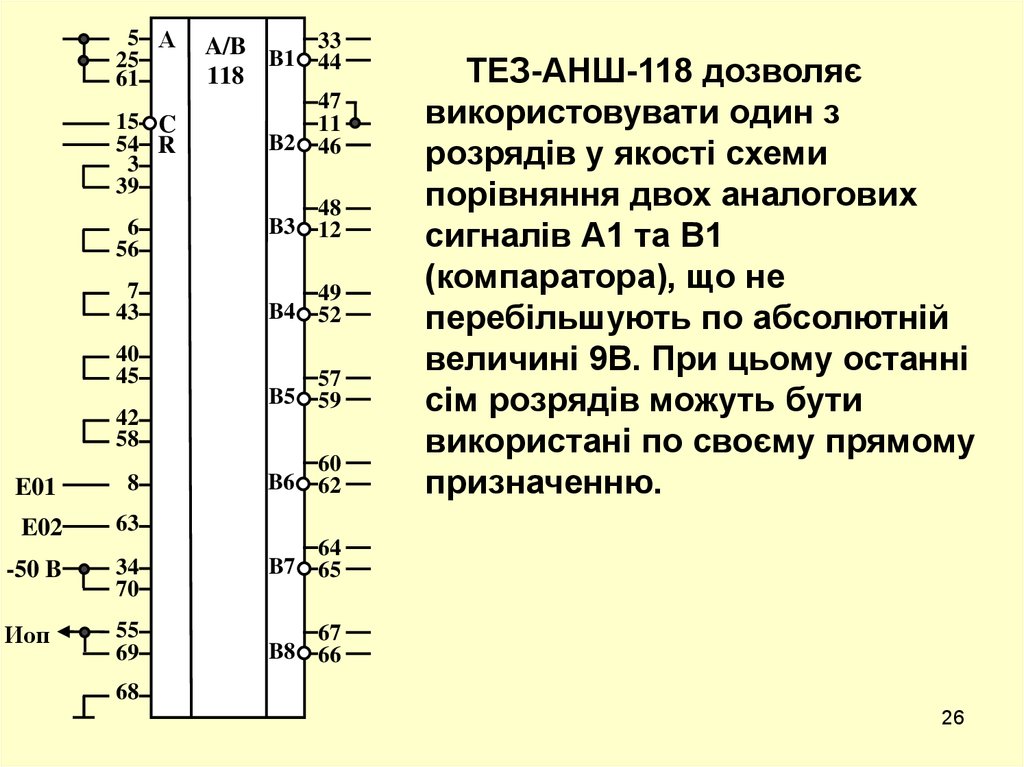

ТЕЗ-АНШ-118 дозволяє

використовувати один з

розрядів у якості схеми

порівняння двох аналогових

сигналів А1 та В1

(компаратора), що не

перебільшують по абсолютній

величині 9В. При цьому останні

сім розрядів можуть бути

використані по своєму прямому

призначенню.

64

B7 65

67

B8 66

68

26

27.

Навчальна мета:Вивчити схемну побудову типових

елементів заміни.

Завдання на самопідготовку:

Вивчати матеріал заняття

27

Военное дело

Военное дело