Похожие презентации:

Обратный порядок байт

1. Информатика

Лекция 82. Обратный порядок байт

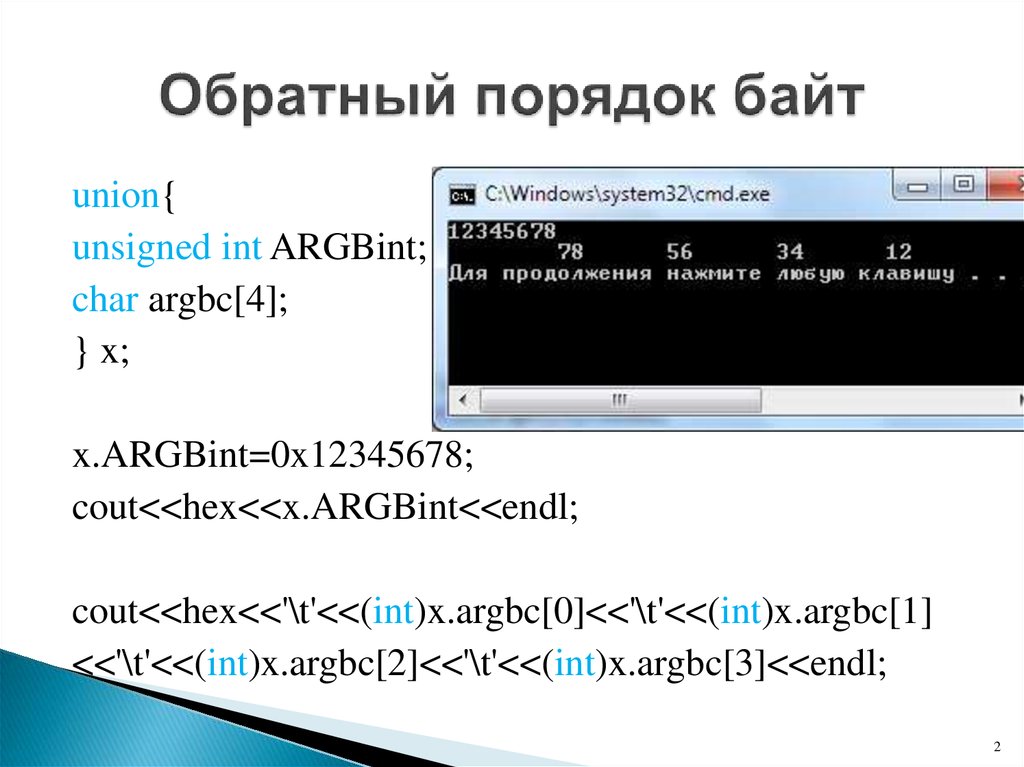

union{unsigned int ARGBint;

char argbc[4];

} x;

x.ARGBint=0x12345678;

cout<<hex<<x.ARGBint<<endl;

cout<<hex<<'\t'<<(int)x.argbc[0]<<'\t'<<(int)x.argbc[1]

<<'\t'<<(int)x.argbc[2]<<'\t'<<(int)x.argbc[3]<<endl;

2

3.

34. Intel 80386

Первым был Intel 80386, он появился в 1986 году имог работать на частоте до 40 МГц.

Этот процессор относится к третьему поколению

Использовался техпроцесс 1500 нм.

4

5. 80486

Четвертое поколение.Процессор работал на частоте 50 МГц и мог

выполнять 40 миллионов команд в секунду.

Процессор имел 8 кб кэша первого уровня

Для изготовления использовался техпроцесс 1000

нм.

5

6. Р5 и Р6

P5 или Pentium. Эти процессоры появились в 1993году, здесь был увеличен кэш до 32 кб, частота до

60 МГц, а техпроцесс уменьшен до 800 нм.

В шестом поколении P6 размер кэша составлял 32

кб, а частота достигла 450 МГц. Тех процесс был

уменьшен до 180 нм.

6

7. Itanium

(произносится: Айтэниум) —микропроцессор с архитектурой IA-64,

разработанный совместно компаниями Intel и

Hewlett-Packard.

Впервые был представлен 29 мая 2001 года.

Производство Itanium прекращено в июле 2002 года

одновременно с выходом Itanium 2.

В ноябре 2007 года Intel переименовала серию

процессоров Itanium 2 обратно в Itanium.

7

8. Архитектура NetBurst

Использовалось 16 кб кэша первого уровня накаждое ядро, и до 2 Мб кэша второго уровня.

Частота выросла до 3 ГГц, а техпроцесс остался на

том же уровне — 180 нм.

Появились 64 битные процессоры, которые

поддерживали адресацию большего количества

памяти. Также было внесено множество

расширений команд.

Добавлена технология Hyper-Threading, которая

позволяла создавать два потока из одного ядра, что

повышало производительность.

8

9. Архитектура Intel Core

Одной из причин разработки этой архитектурыбыла невозможность увеличения частоты в

NetBurst, а также ее очень большое

тепловыделение.

Эта архитектура была рассчитана на разработку

многоядерных процессоров, размер кэша первого

уровня был увеличен до 64 Кб.

Частота осталась на уровне 3 ГГц, но зато была

сильно снижена потребляемая мощность, а также

техпроцесс, до 60 нм.

Не поддерживали Hyper-Threading

9

10. Первое поколение — Nehalem

Появилась в 2007 году.Здесь используется 45 нм тех процесс и была

добавлена поддержка технологии Hyper-Therading.

Процессоры Nehalem имеют размер L1 кэша 64 Кб,

4 Мб L2 кэша и 12 Мб кєша L3.

Кэш доступен для всех ядер процессора.

Появилась возможность встраивать графический

ускоритель в процессор.

10

11. Стратегия «тик-так» Intel

Стратегия «тик-так» разделяет два процесса.За «тик» транзисторы становятся меньше.

Изменения микроархитектуры есть, но они

незначительны.

«Так» означает создание новой микроархитектуры,

то есть большие, иногда фундаментальные

изменения в целях достижения больших приростов

производительности.

11

12. Второе поколение — Sandy Bridge

Sandy Bridge появилась в 2011 году для заменыNehalem.

Используется техпроцесс 32 нм, используется 64

Кб кэша первого уровня, 256 Кб кэша второго

уровня и 8 Мб кэша третьего уровня.

Также теперь все устройства выпускаются со

встроенным графическим ускорителем.

Была увеличена максимальная частота, а также

общая производительность.

12

13. Третье поколение — Ivy Bridge

Процессоры Ivy Bridge работают быстрее чем SandyBridge.

Для изготовления используется техпроцесс 22 нм.

Потребляют на 50% меньше энергии чем

предыдущие модели, а также дают повышение на

25-60% производительности.

13

14. Четвертое поколение — Haswell

Поколение процессора Intel Haswell былоразработано в 2012 году.

Использовался тот же техпроцесс — 22 нм, изменен

дизайн кэша, улучшены механизмы

энергопотребления и немного производительность.

Основное преимущество Haswell в том, что она

может использоваться в портативных устройствах

из-за очень низкого энергопотребления.

14

15. Пятое поколение — Broadwell

Улучшенная версия архитектуры Haswell, котораяиспользует техпроцесс 14 нм.

В архитектуру было внесено несколько улучшений,

которые позволили повысить производительность в

среднем на 5%.

15

16. Шестое поколение — Skylake

Skylake вышла в 2015 году. Это одно из самыхзначительных обновлений архитектуры Core.

Для установки процессора на материнскую плату

используется сокет LGA 1151.

Поддерживается память DDR4, но сохранилась

поддержка DDR3.

По традиции была увеличенная

производительность, а также снижено

энергопотребление.

16

17. Седьмое поколение — Kaby Lake

Kaby Lake вышло в 2017 году, первые процессорыпоявились в середине января.

Сохранен техпроцесс 14 нм, а также тот же

сокет LGA 1151.

Поддерживаются планки памяти DDR3L SDRAM и

DDR4 SDRAM, шины PCI Express 3.0, USB 3.1.

Немного увеличена частота, а также уменьшена

плотность расположения транзисторов.

Максимальная частота 4,2 ГГц.

17

18. Intel отказывается от стратегии «тик-так»

1819. Восьмое поколение — Coffee Lake

Coffee Lake вышло в 3 квартале 2017 году.Сохранен техпроцесс 14 нм, а также тот же сокет LGA

1151.

Поддерживаются планки памяти DDR3L SDRAM и

DDR4 SDRAM, шины PCI Express 3.0, USB 3.1.

Основным отличием архитектуры станет увеличение

до шести количества ядер процессора в настольных

(Coffee Lake-S) и мобильных (Coffee Lake-H) вариантах

процессора..

Ожидается, что производительность процессоров

Coffee Lake увеличится на 15 процентов по сравнению

с процессорами Kaby Lake

19

20. Архитектура x86

Регистры данных — служат для храненияпромежуточных вычислений.

AX (англ. Accumulator), CX (англ. Count Register), DX

(англ. Data Register), BX (англ. Base Register), SP

(англ. Stack Pointer), BP (англ. Base Pointer), SI

(англ. Source Index), DI (англ. Destination Index),

R8W — R15W — 16-битные

AH, AL, CH, CL, DH, DL, BH, BL, SPL, BPL, SIL, DIL,

R8B — R15B — 8-битные (половинки 16-битных

регистров)

20

21. Архитектура x86

Регистры данных — служат для храненияпромежуточных вычислений.

RAX, RCX, RDX, RBX, RSP, RBP, RSI, RDI, R8 —

R15 — 64-битные

EAX, ECX, EDX, EBX, ESP, EBP, ESI, EDI, R8D —

R15D — 32-битные (extended AX)

21

22. Сегментные регистры

Все сегментные регистры - 16-разрядные.CS (англ. Code Segment), DS (англ. Data Segment), SS (англ. Stack

Segment), ES (англ. Extra Segment), FS, GS

В реальном режиме работы процессора сегментные регистры

содержат адрес начала 64Kb сегмента, смещенный вправо на 4

бита.

В защищенном режиме работы процессора сегментные регистры

содержат селектор сегмента памяти, выделенного ОС.

CS — указатель на кодовый сегмент. Связка CS:IP указывает на

адрес в памяти следующей команды.

В 64-разрядном режиме сегментные регистры CS, DS, ES и SS в

формировании линейного (непрерывного) адреса не участвуют,

поскольку сегментация в этом режиме не поддерживаются.

22

23. Instruction Pointer

IP (англ. Instruction Pointer) — регистр,указывающий на смещение (адрес) инструкций в

сегменте кода (1234:0100h сегмент/смещение).

IP — 16-битный (младшая часть EIP)

EIP — 32-битный аналог (младшая часть RIP)

RIP — 64-битный аналог

23

24. Флаговый регистр

В микропроцессорах Intel имеет название FLAGS иявляется 16-разрядным.

Расширенные регистры EFLAGS и RFLAGS,

являются 32-битными и 64-битными

соответственно.

Расширенные регистры сохраняют обратную

совместимость.

Пока используется по 21 бит включительно.

24

25. Векторизация

(в параллельных вычислениях) —вид распараллеливания программы, при котором

однопоточные приложения, выполняющие одну

операцию в каждый момент времени,

модифицируются для выполнения нескольких

однотипных операций одновременно.

Скалярные операции, обрабатывающие по паре

операндов заменяются на операции над массивами

(векторами), обрабатывающие несколько элементов

вектора в каждый момент времени.

25

26. Intel AVX

Новый набор инструкций для x86-процессоров IntelAVX был представлен публике ещё в марте 2008

года.

Поддержка набора инструкций AVX добавлена в

новые версии компиляторов и ассемблеров.

Входит в МАSM в Visual Studio 2010

26

27. AVX-512

Расширяет AVX до векторов длиной 512 бит.Расширение AVX-512 вводит 32 векторных

регистра (ZMM), каждый по 512 бит.

Регистры AVX (YMM0-YMM15) отображаются на

младшие части регистров AVX-512 (ZMM0ZMM15).

27

Электроника

Электроника