Похожие презентации:

Ассемблер Atmel AVR. Занятие №1: Архитектура AVR, схемотехника ЭВМ

1. Ассемблер Atmel AVR

Занятие №1: Архитектура AVR,схемотехника ЭВМ.

2. Уровни абстракции

ApplicatinsKernel

Assembler

Firmware

Hardware

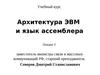

3. Принстонская архитектура

Устройстваввода/вывода

Процессор

Общая

Общая шина

шина данных

данных ии команд

команд

Память

Данные

Команды

4. Гарвардская архитектура

ШинаШина команд

команд

Память

команд

Процессор

Память

данных

Шина

Шина данных

данных

Устройства

ввода/вывода

5. Архитектуры CISC и RISC

CISCRISC

Машинные

инструкции

Машинные

инструкции

Преобразование

микрокода

Обработка

инструкций

Микроинструкции

Обработка

микроинструкций

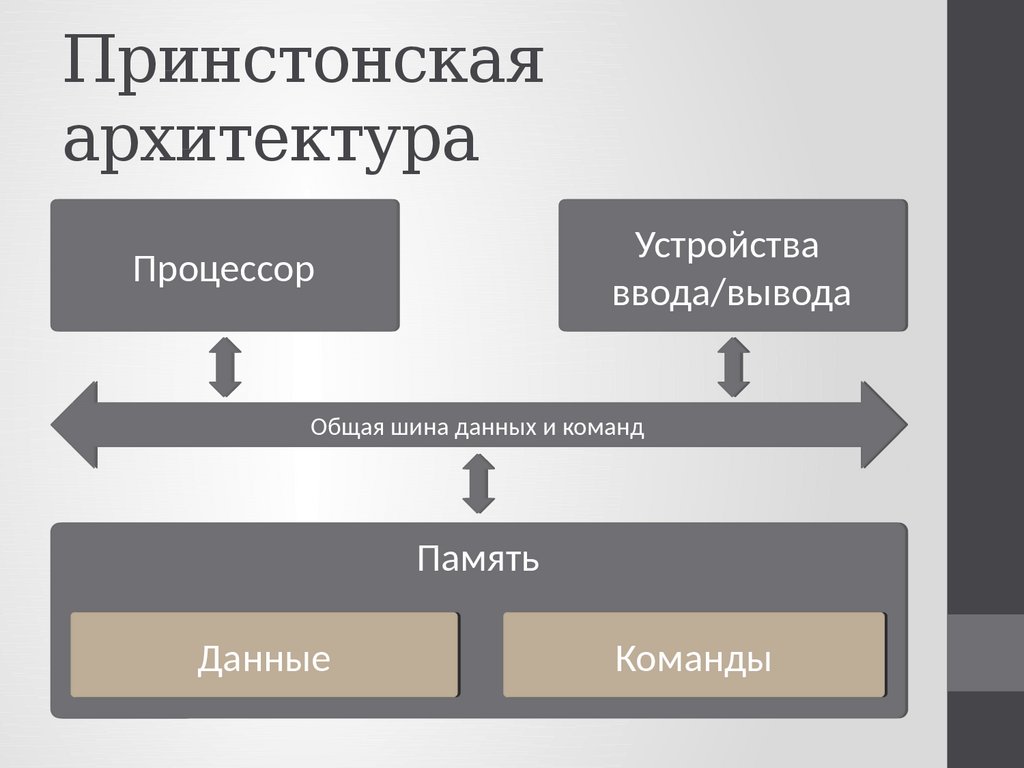

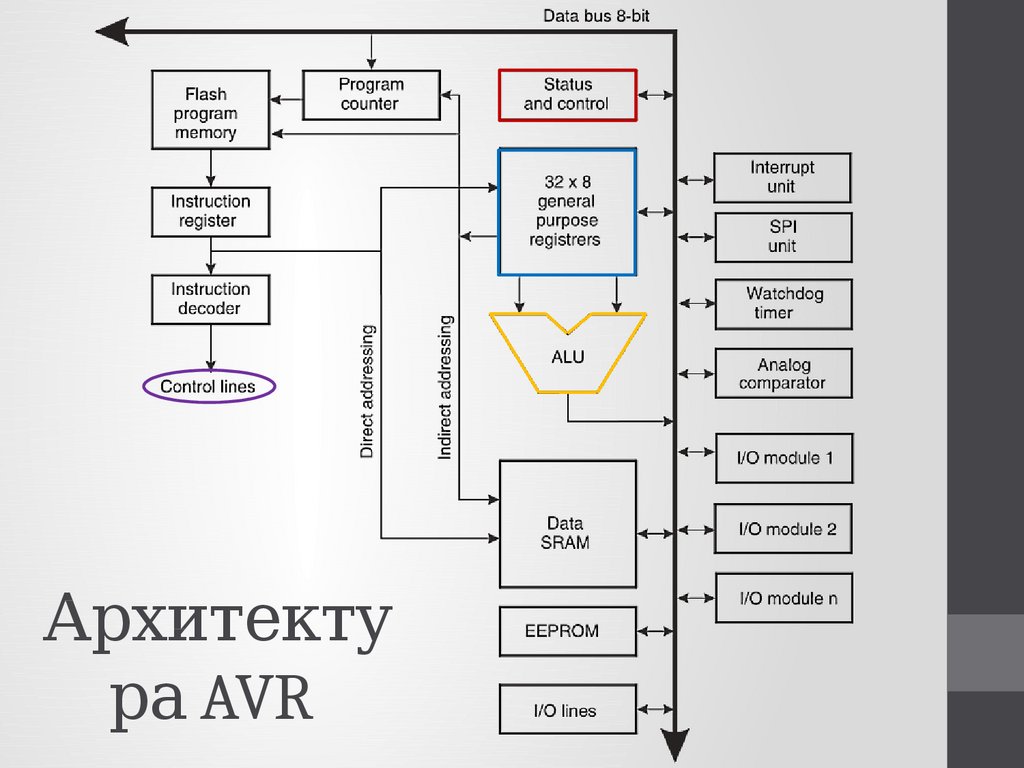

6. Архитектура AVR

Архитектура AVR

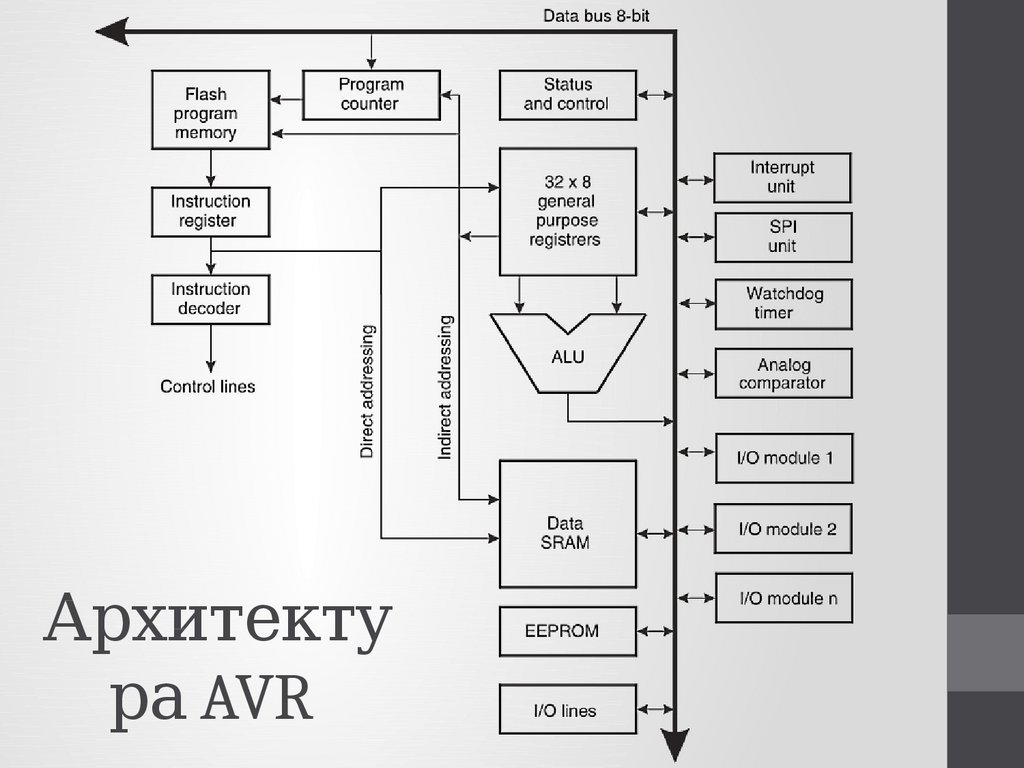

7. Транзистор – всему голова

База

Эмитте

р

Коллекто

р

Транзистор – это кнопка, которая нажимается не

пальцем, а подачей напряжения на Базу, после чего ток

начинает протекать между Коллектором и Эмиттером.

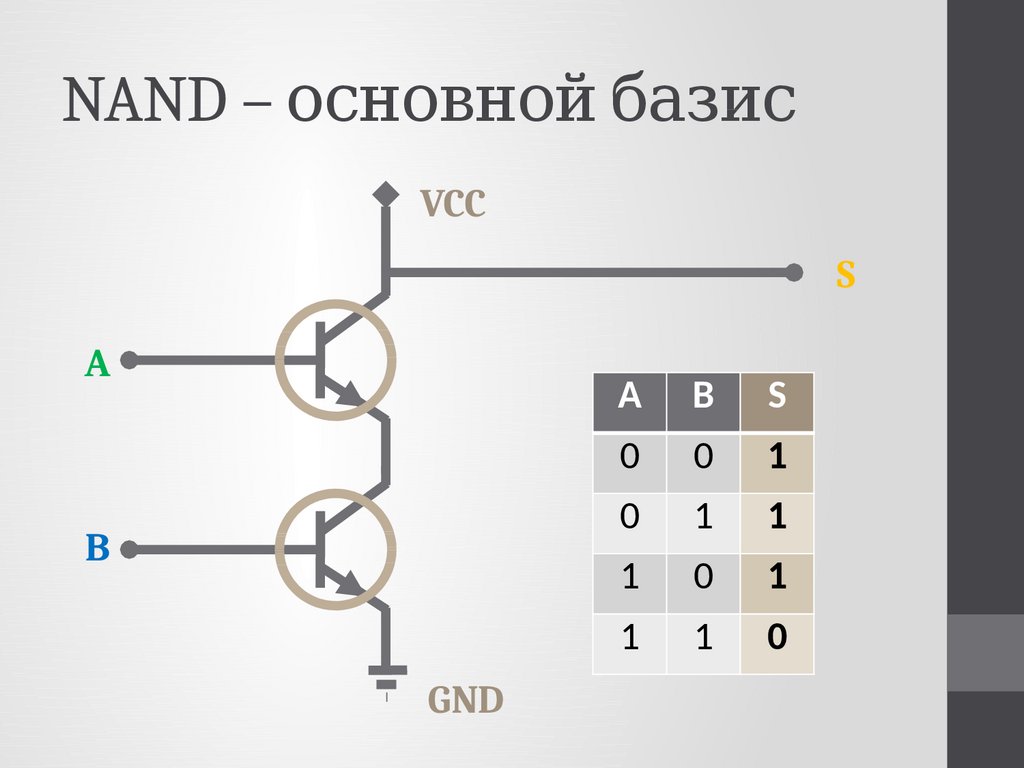

8. NAND – основной базис

VCCS

A

B

GND

A

B

S

0

0

1

0

1

1

1

0

1

1

1

0

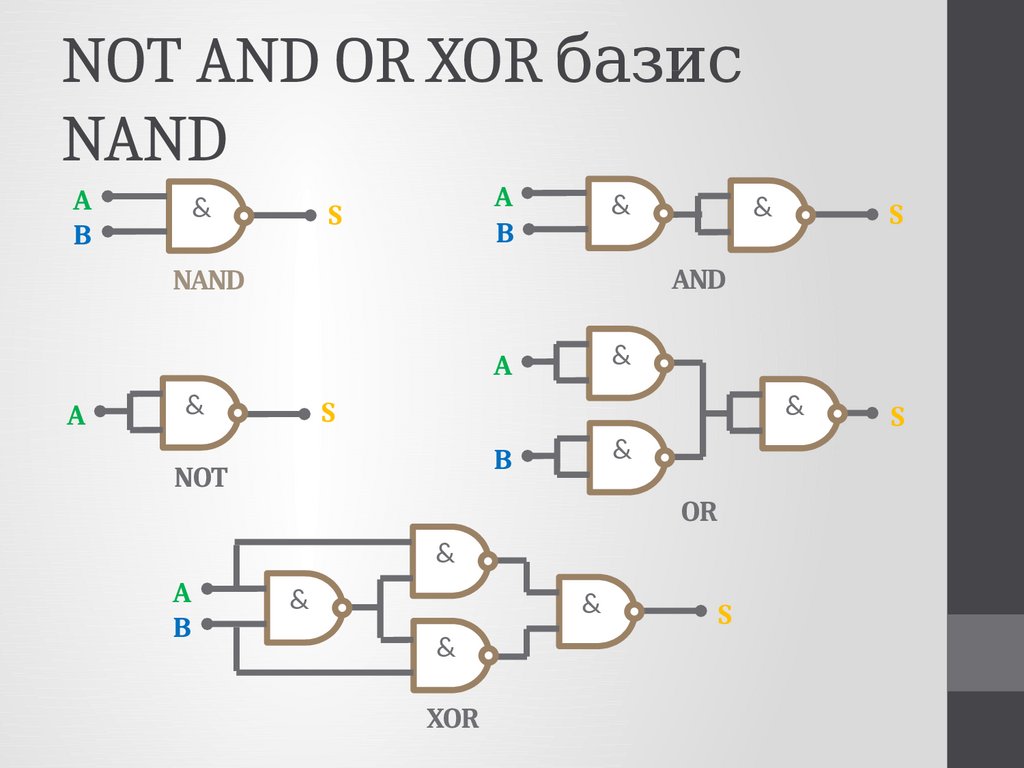

9. NOT AND OR XOR базис NAND

AB

&

A

B

S

&

&

A

&

&

S

&

B

NOT

OR

&

A

B

S

AND

NAND

A

&

&

&

&

XOR

S

S

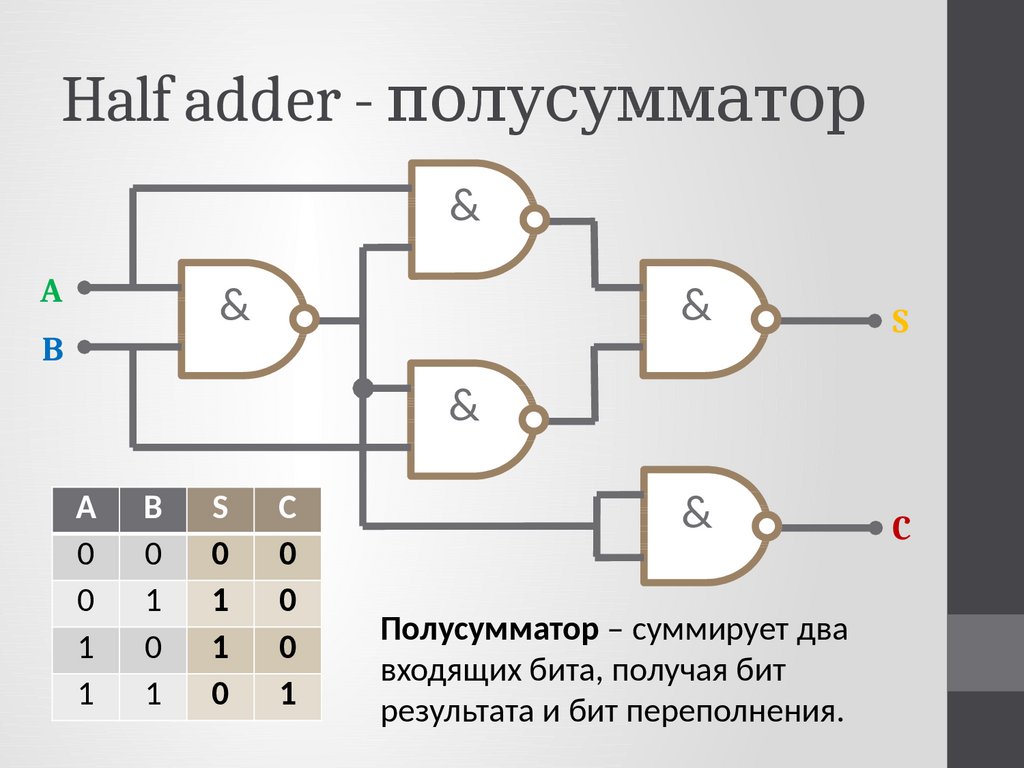

10. Half adder - полусумматор

&A

&

B

&

S

&

C

&

A

0

0

1

1

B

0

1

0

1

S

0

1

1

0

C

0

0

0

1

Полусумматор – суммирует два

входящих бита, получая бит

результата и бит переполнения.

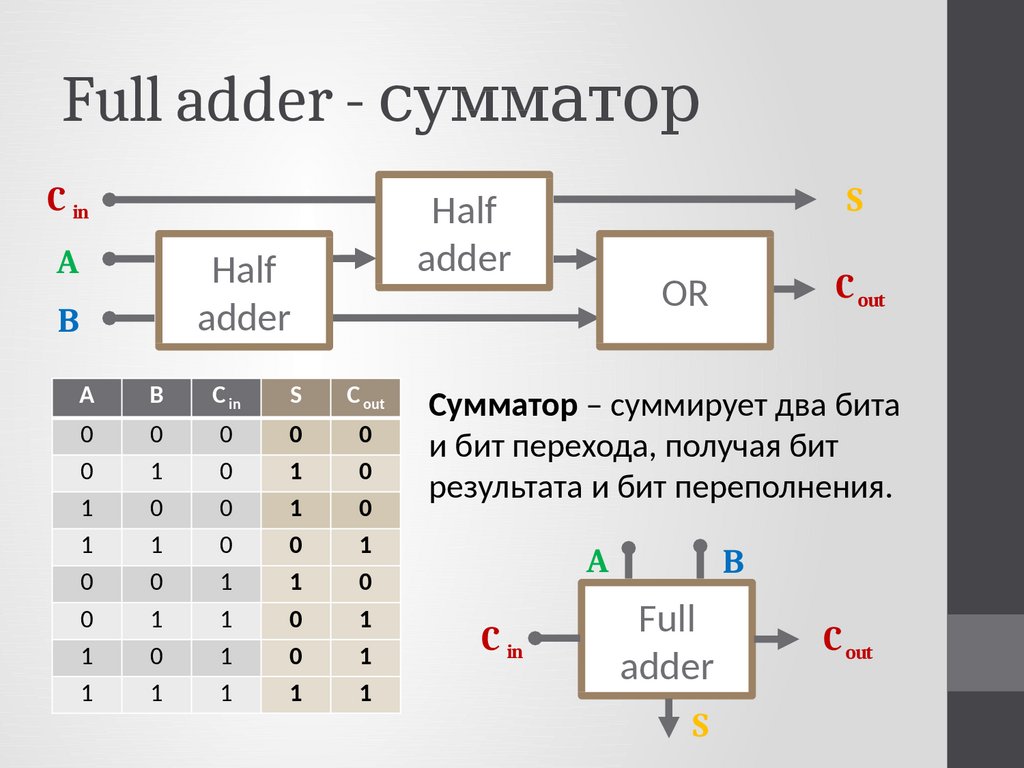

11. Full adder - сумматор

C inA

Half

adder

B

S

Half

S

adder

A

B

С in

S

C out

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

0

1

1

1

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

C out

OR

Сумматор – суммирует два бита

и бит перехода, получая бит

результата и бит переполнения.

A

C in

B

Full

adder

S

C out

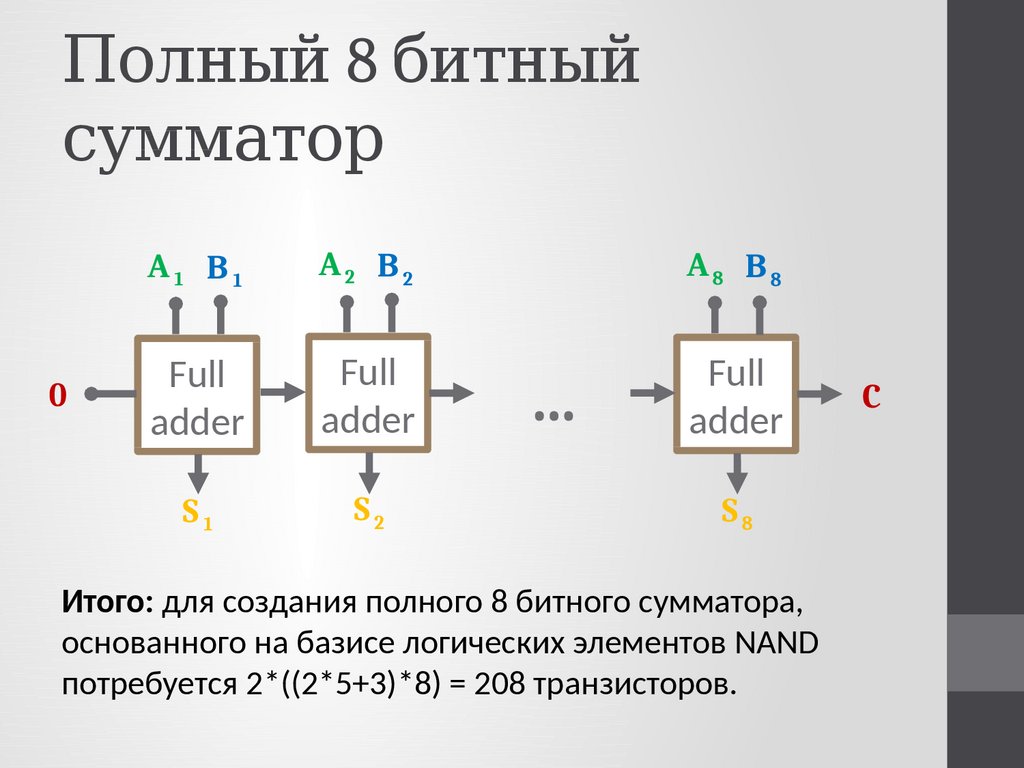

12. Полный 8 битный сумматор

0A1 B1

A2 B2

A8 B8

Full

adder

Full

adder

Full

adder

S1

S2

…

S8

Итого: для создания полного 8 битного сумматора,

основанного на базисе логических элементов NAND

потребуется 2*((2*5+3)*8) = 208 транзисторов.

C

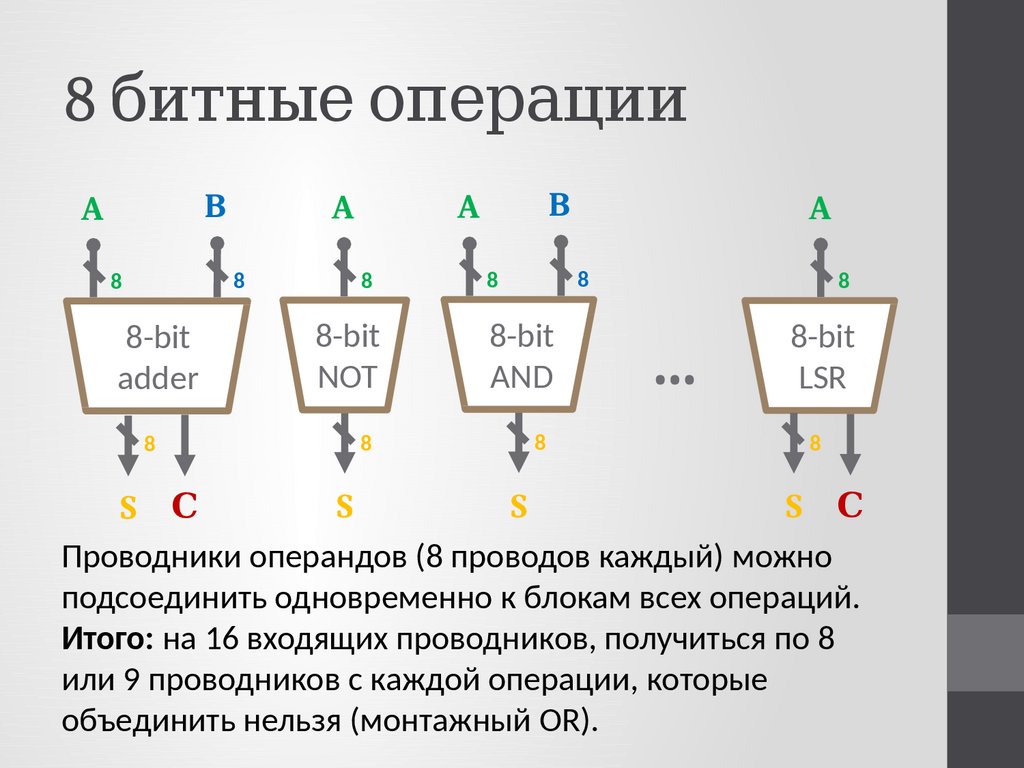

13. 8 битные операции

BA

8

8

8-bit

adder

8

B

A

A

8

8-bit

NOT

8

A

8

8

8-bit

AND

8

8

…

8-bit

LSR

8

S

S

S С

S С

Проводники операндов (8 проводов каждый) можно

подсоединить одновременно к блокам всех операций.

Итого: на 16 входящих проводников, получиться по 8

или 9 проводников с каждой операции, которые

объединить нельзя (монтажный OR).

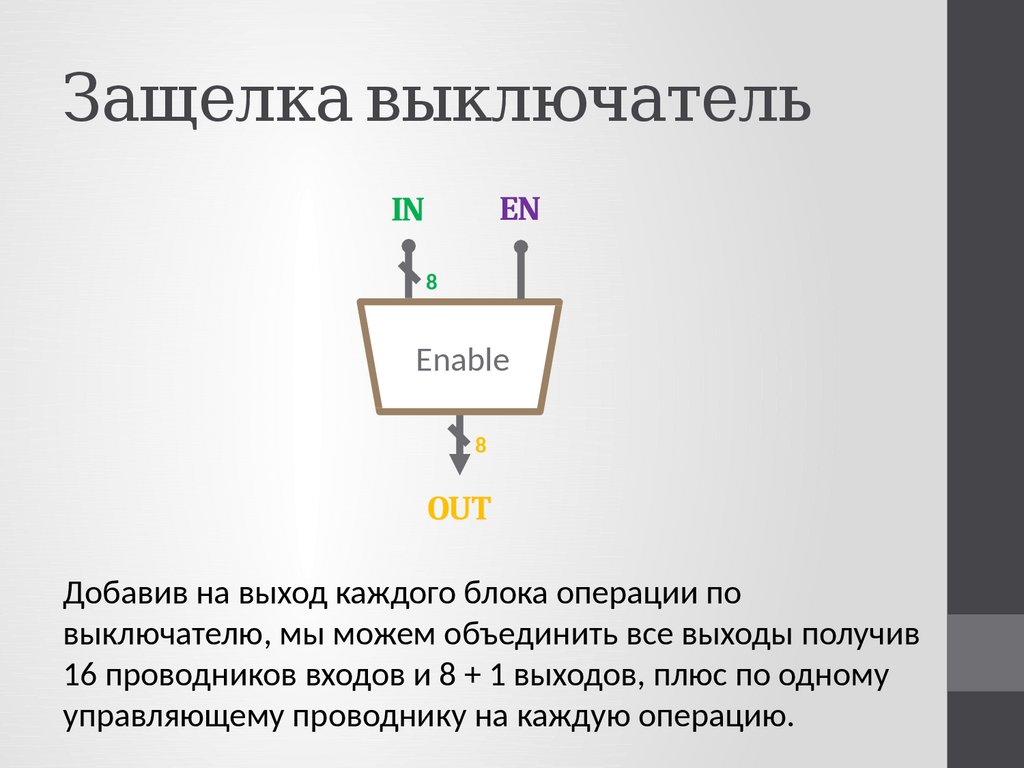

14. Защелка выключатель

ENIN

8

Enable

8

OUT

Добавив на выход каждого блока операции по

выключателю, мы можем объединить все выходы получив

16 проводников входов и 8 + 1 выходов, плюс по одному

управляющему проводнику на каждую операцию.

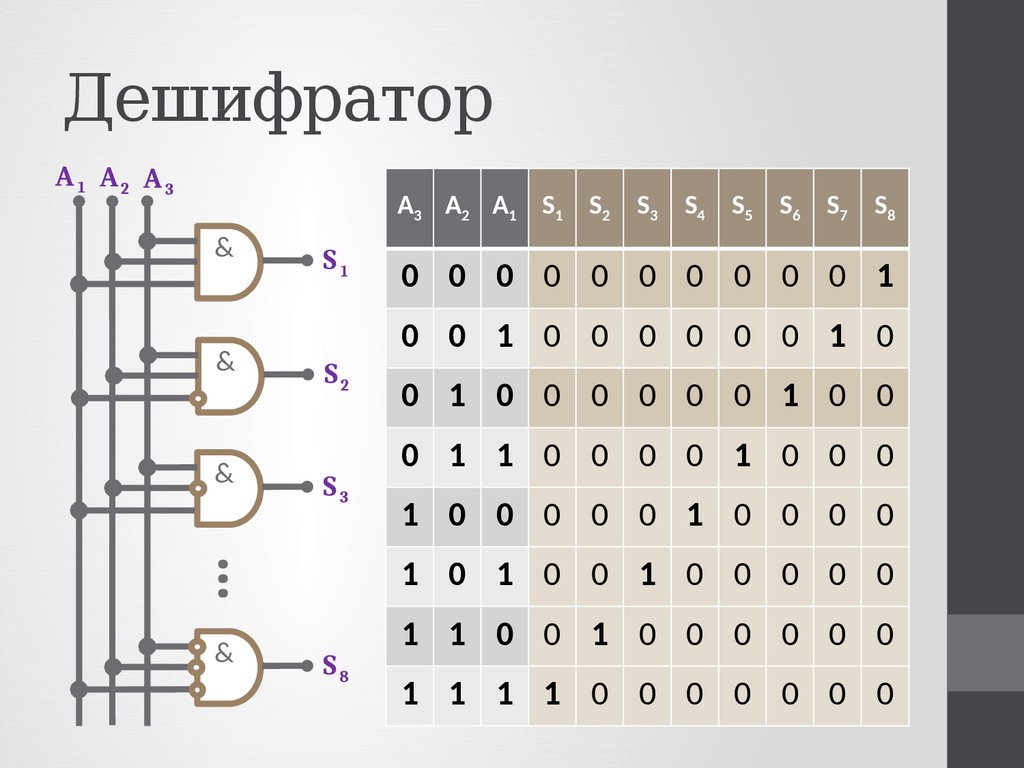

15. Дешифратор

A1 A2 A3A3 A2 A1 S 1 S 2 S 3 S 4 S 5 S 6 S 7 S 8

&

&

&

S1

0 0 1 0 0 0 0 0 0 1 0

S2

S3

…

&

0 0 0 0 0 0 0 0 0 0 1

0 1 0 0 0 0 0 0 1 0 0

0 1 1 0 0 0 0 1 0 0 0

1 0 0 0 0 0 1 0 0 0 0

1 0 1 0 0 1 0 0 0 0 0

S8

1 1 0 0 1 0 0 0 0 0 0

1 1 1 1 0 0 0 0 0 0 0

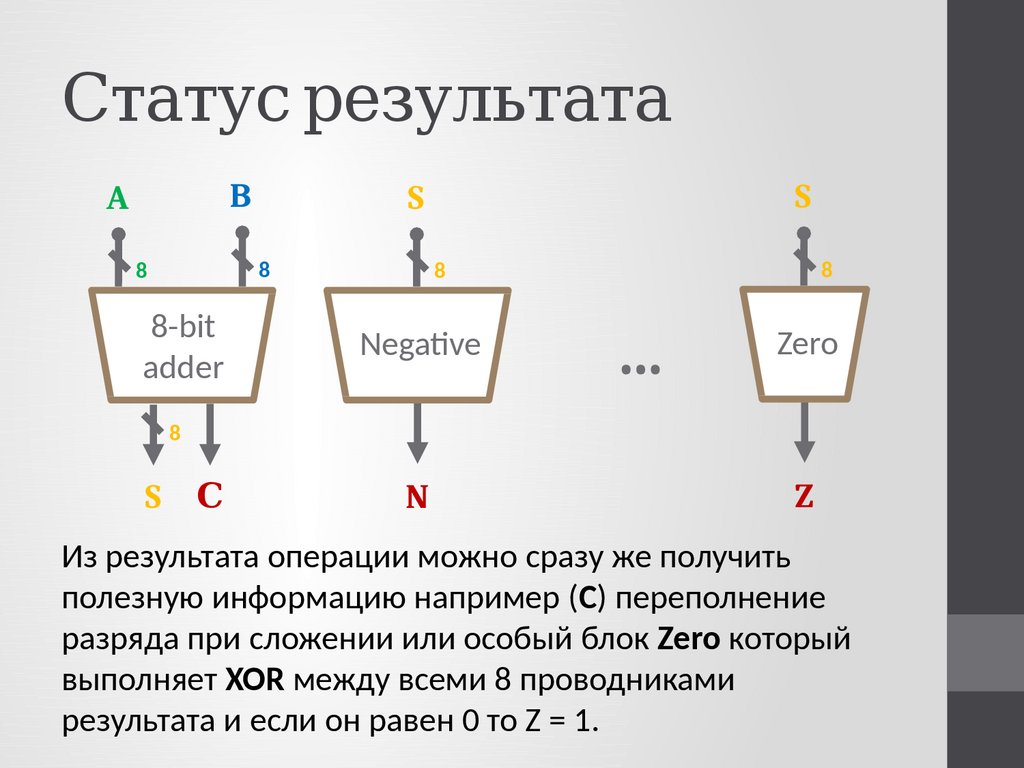

16. Статус результата

BA

8

8

8-bit

adder

S

S

8

8

Negatve

…

Zeri

8

S

С

N

Z

Из результата операции можно сразу же получить

полезную информацию например (C) переполнение

разряда при сложении или особый блок Zero который

выполняет XOR между всеми 8 проводниками

результата и если он равен 0 то Z = 1.

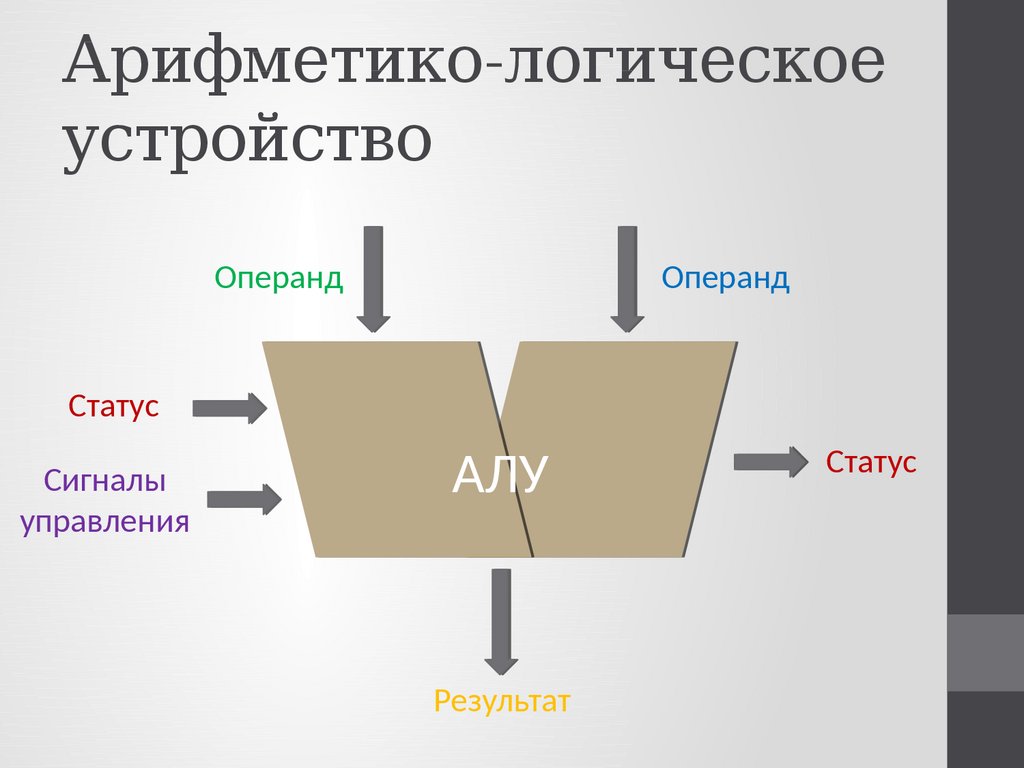

17. Арифметико-логическое устройство

ОперандОперанд

Статус

Сигналы

управления

АЛУ

Результат

Статус

18. Архитектура AVR

Архитектура AVR

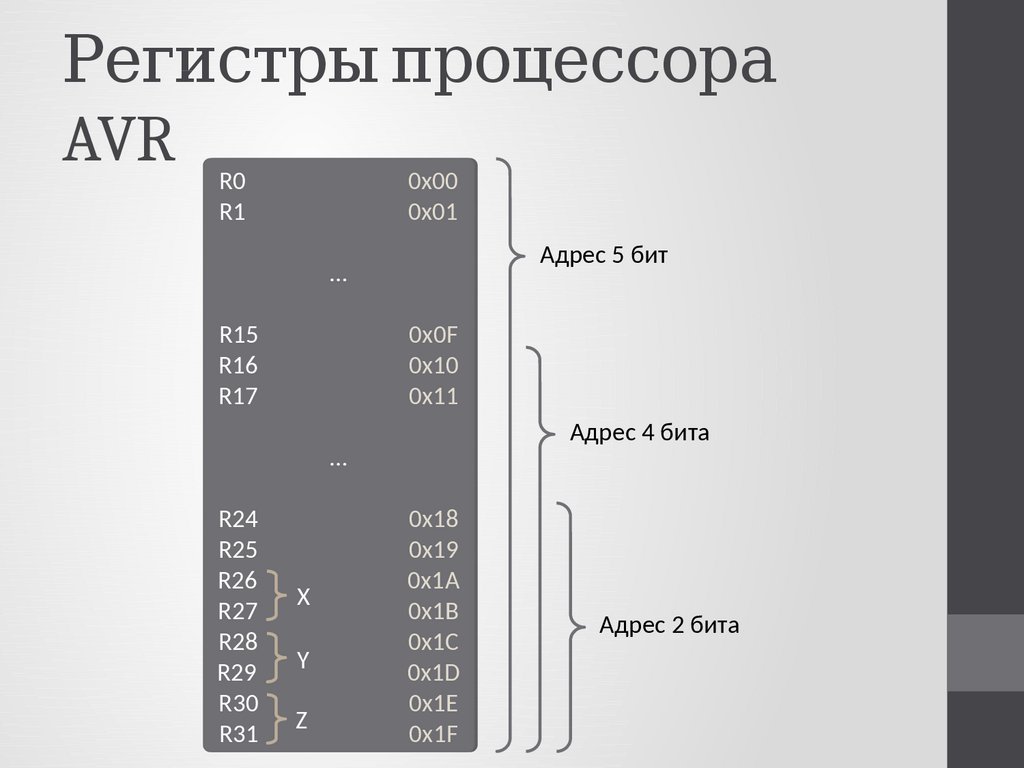

19. Регистры процессора AVR

R0R0

R1

R1

0x00

0x00

0x01

0x01

Адрес 5 бит

…

…

R15

R15

R16

R16

R17

R17

0x0F

0x0F

0x10

0x10

0x11

0x11

Адрес 4 бита

…

…

R24

R24

R25

R25

R26

R26

R27

R27

R28

R28

R29

R29

R30

R30

R31

R31

X

Y

Z

0x18

0x18

0x19

0x19

0x1A

0x1A

0x1B

0x1B

0x1C

0x1C

0x1D

0x1D

0x1E

0x1E

0x1F

0x1F

Адрес 2 бита

20. Память AVR

FlashFlash 16-bits

16-bits

SRAM

SRAM 8-bits

8-bits

EEPROM

EEPROM 8-bits

8-bits

0x0000

0x0000

0x0000

0x0000 РОН

РОН 0x001F

0x001F

0x0000

0x0000

0x0020

0x0020 I/O

I/O 0x005F

0x005F

0x0060

0x0060

Внутренняя

Внутренняя SRAM

SRAM

Память

Память программ

программ

RAMEND

RAMEND

Память

Память EEPROM

EEPROM

RAMEND+1

RAMEND+1

Внешняя

Внешняя SRAM

SRAM

FLASHEND

FLASHEND –– 0xFFFF

0xFFFF

0xFFFF

0xFFFF

EEPROMEND

EEPROMEND –– 0xFFFF

0xFFFF

21. NOP – Ничего не делать

Синтаксис: NOP0000

Размер: 2 байта

0000

0000

0000

Операнды: –

Счетчик: PC += 1

I

T

H

–

–

–

S

–

V

–

Такты: 1

N

Z

–

–

C

–

Определение: Операция выполняется вхолостую, ничего

не происходит.

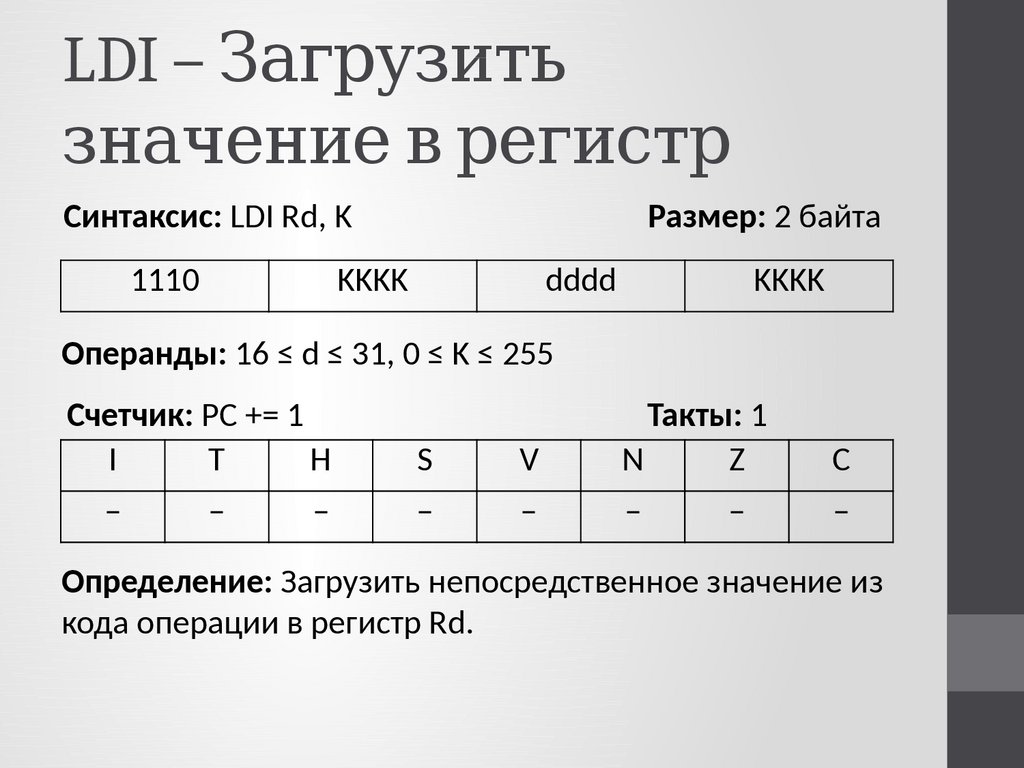

22. LDI – Загрузить значение в регистр

Синтаксис: LDI Rd, K1110

Размер: 2 байта

KKKK

dddd

KKKK

Операнды: 16 ≤ d ≤ 31, 0 ≤ K ≤ 255

Счетчик: PC += 1

I

T

H

–

–

–

S

–

V

–

Такты: 1

N

Z

–

–

C

–

Определение: Загрузить непосредственное значение из

кода операции в регистр Rd.

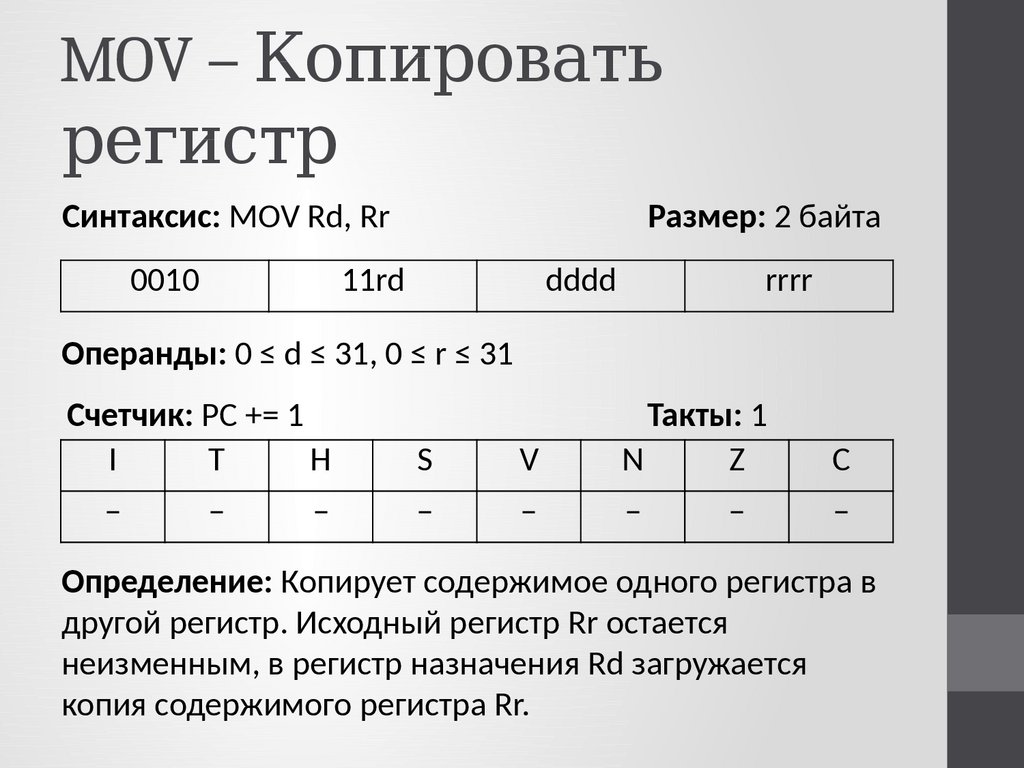

23. MOV – Копировать регистр

Синтаксис: MOV Rd, Rr0010

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

T

H

–

–

–

S

–

V

–

Такты: 1

N

Z

–

–

C

–

Определение: Копирует содержимое одного регистра в

другой регистр. Исходный регистр Rr остается

неизменным, в регистр назначения Rd загружается

копия содержимого регистра Rr.

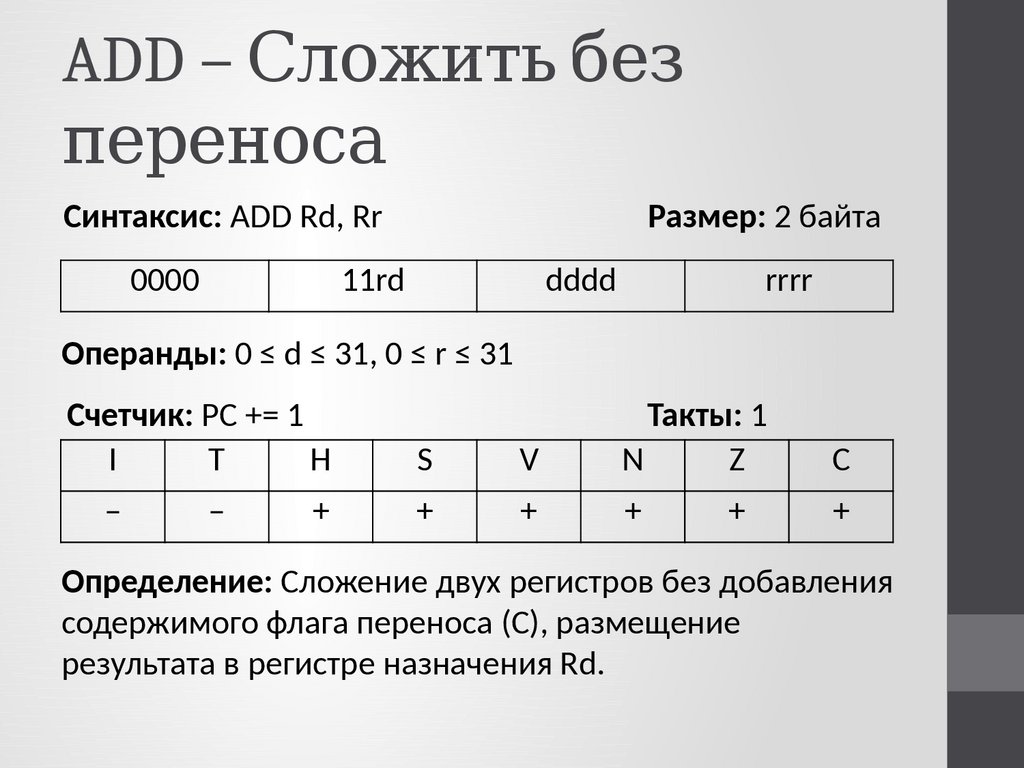

24. ADD – Сложить без переноса

Синтаксис: ADD Rd, Rr0000

Размер: 2 байта

11rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

T

H

–

–

+

S

+

V

+

Такты: 1

N

Z

+

+

C

+

Определение: Сложение двух регистров без добавления

содержимого флага переноса (С), размещение

результата в регистре назначения Rd.

25. AVR Studio 4

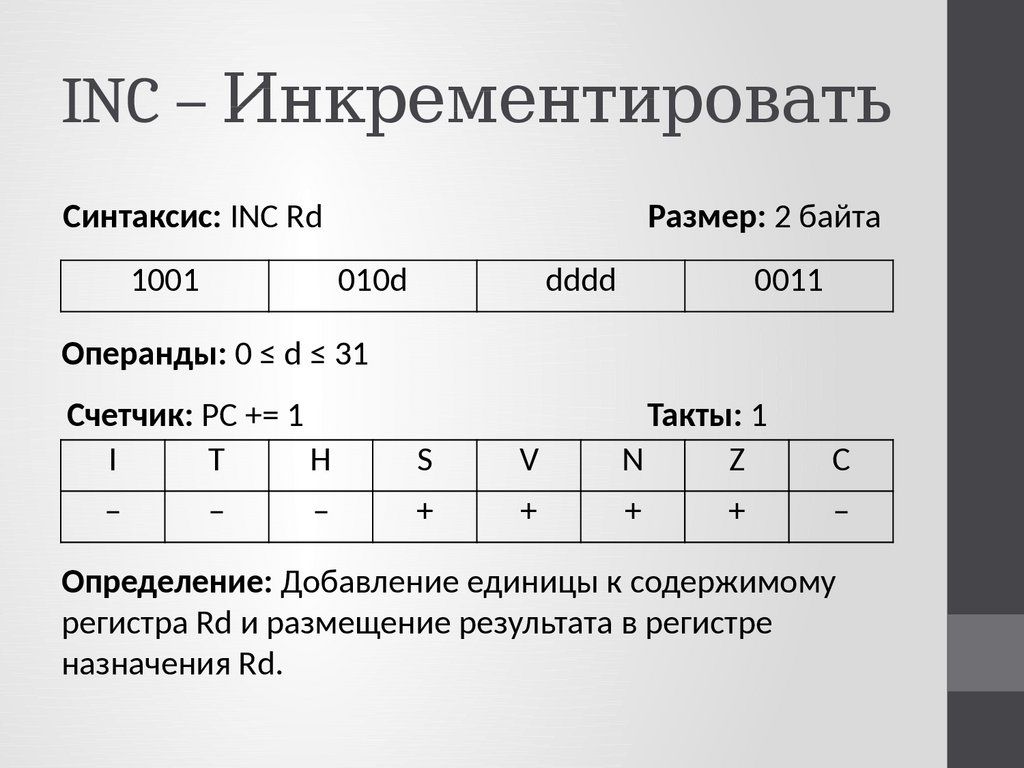

http://www.atmel.cim/ru/ru/tiils/STUDIOARCHIVE.aspx26. INC – Инкрементировать

Синтаксис: INC Rd1001

Размер: 2 байта

010d

dddd

0011

Операнды: 0 ≤ d ≤ 31

Счетчик: PC += 1

I

T

H

–

–

–

S

+

V

+

Такты: 1

N

Z

+

+

C

–

Определение: Добавление единицы к содержимому

регистра Rd и размещение результата в регистре

назначения Rd.

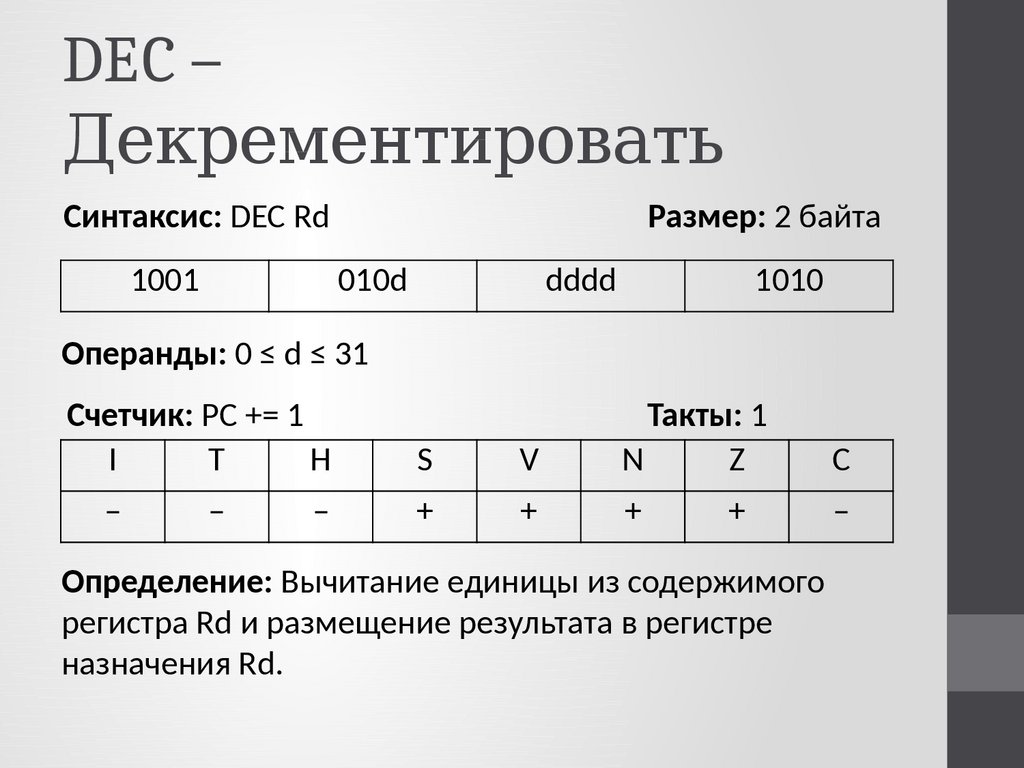

27. DEC – Декрементировать

Синтаксис: DEC Rd1001

Размер: 2 байта

010d

dddd

1010

Операнды: 0 ≤ d ≤ 31

Счетчик: PC += 1

I

T

H

–

–

–

S

+

V

+

Такты: 1

N

Z

+

+

Определение: Вычитание единицы из содержимого

регистра Rd и размещение результата в регистре

назначения Rd.

C

–

28. SUB – Вычесть без переноса

Синтаксис: SUB Rd, Rr0001

Размер: 2 байта

10rd

dddd

rrrr

Операнды: 0 ≤ d ≤ 31, 0 ≤ r ≤ 31

Счетчик: PC += 1

I

T

H

–

–

+

S

+

V

+

Такты: 1

N

Z

+

+

C

+

Определение: Вычитание содержимого регистраисточника Rr из содержимого регистра Rd, размещение

результата в регистре назначения Rd.

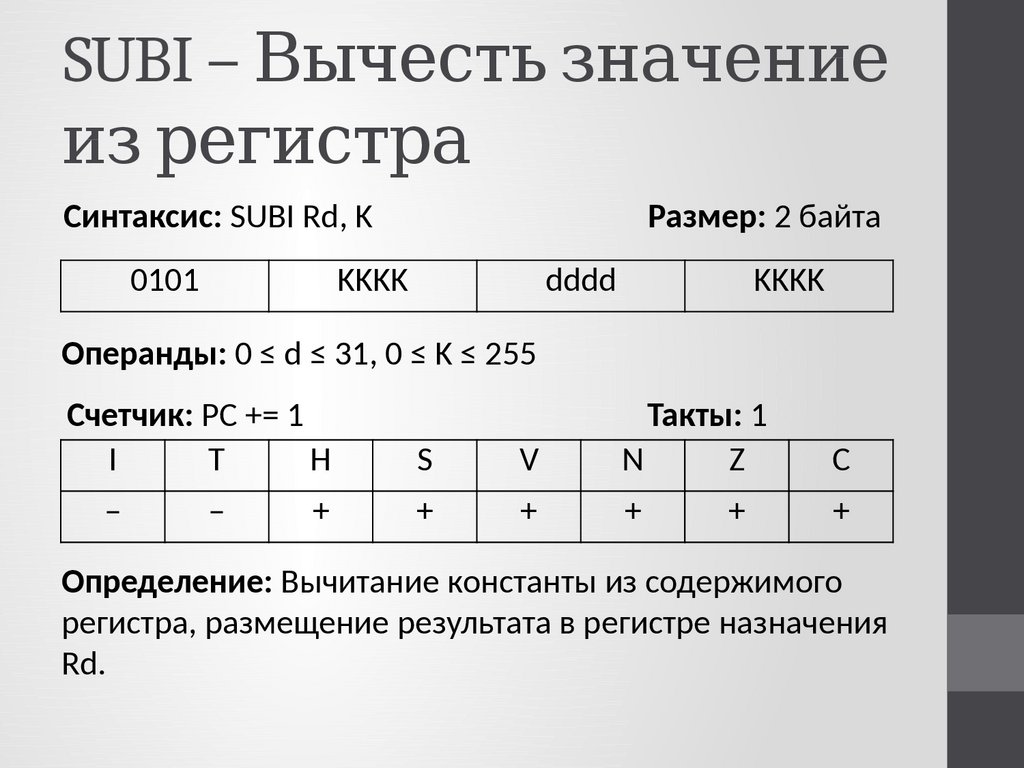

29. SUBI – Вычесть значение из регистра

Синтаксис: SUBI Rd, K0101

Размер: 2 байта

KKKK

dddd

KKKK

Операнды: 0 ≤ d ≤ 31, 0 ≤ K ≤ 255

Счетчик: PC += 1

I

T

H

–

–

+

S

+

V

+

Такты: 1

N

Z

+

+

C

+

Определение: Вычитание константы из содержимого

регистра, размещение результата в регистре назначения

Rd.

Программирование

Программирование