Похожие презентации:

Особенности, регистры, подключение UART

1. UART

ПЛАН•Особенности UART

•Регистры UART

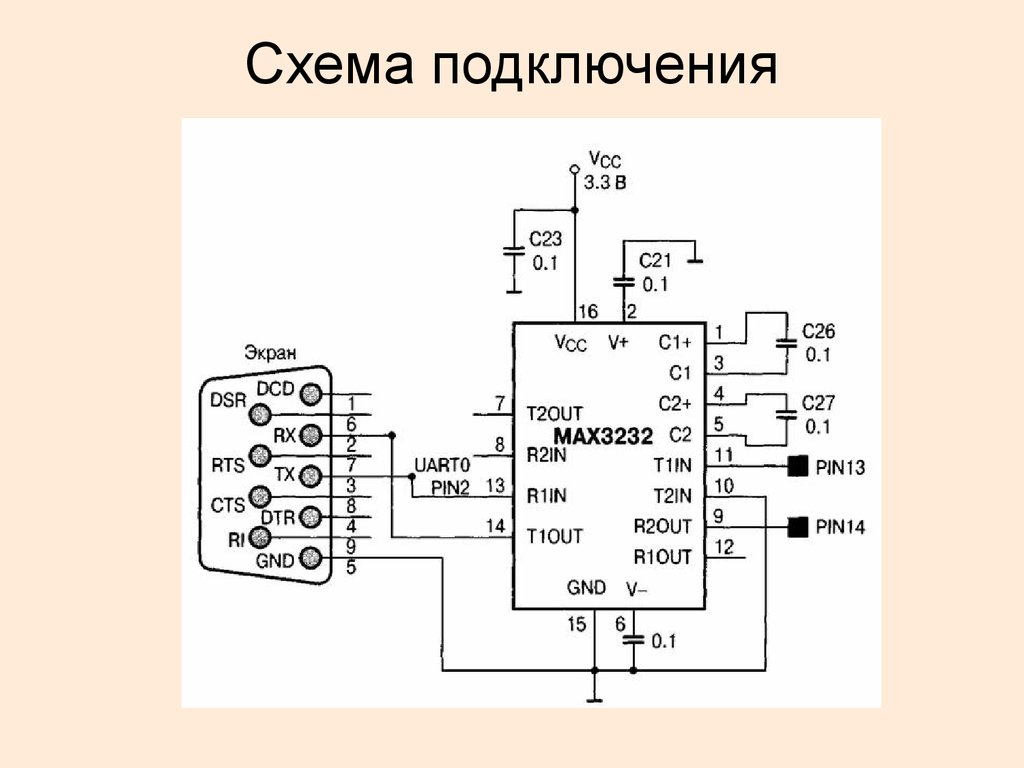

•Подключение UART

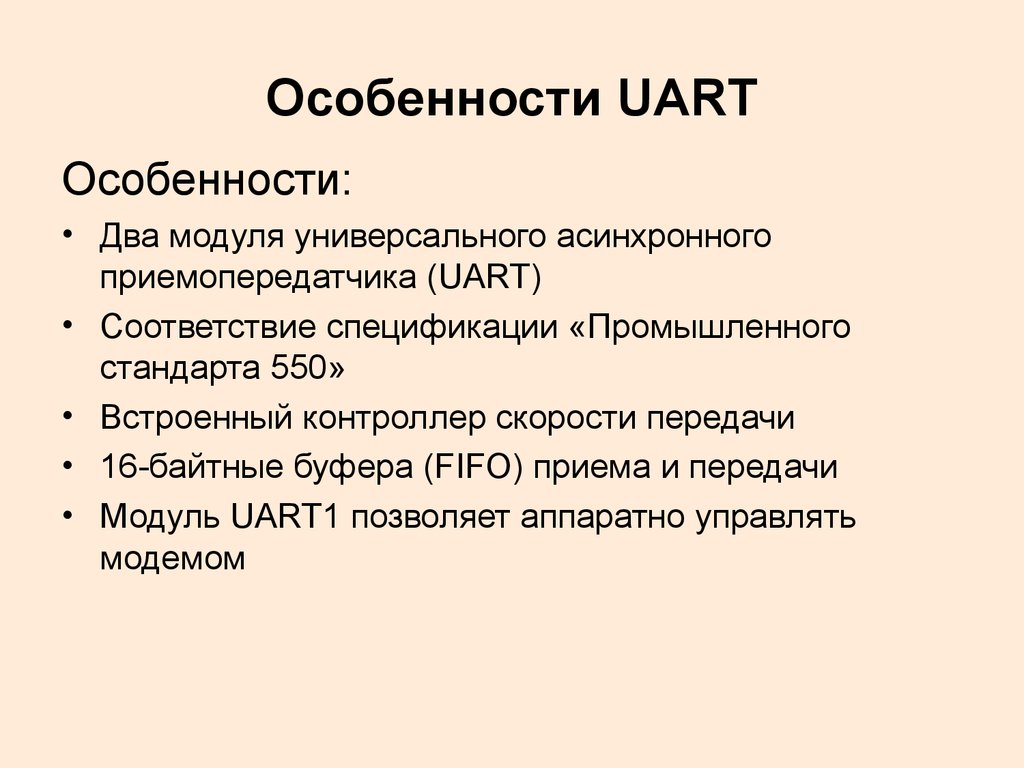

2. Особенности UART

Особенности:• Два модуля универсального асинхронного

приемопередатчика (UART)

• Соответствие спецификации «Промышленного

стандарта 550»

• Встроенный контроллер скорости передачи

• 16-байтные буфера (FIFO) приема и передачи

• Модуль UART1 позволяет аппаратно управлять

модемом

3.

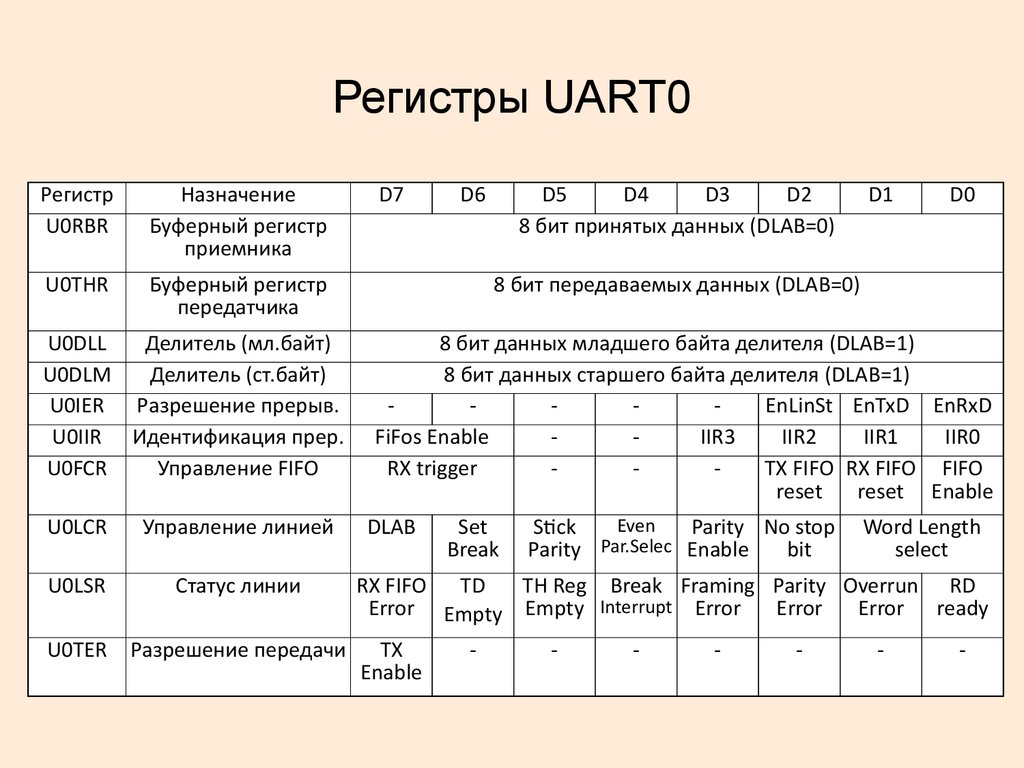

Регистры UART0Регистр

U0RBR

Назначение

Буферный регистр

приемника

U0THR

Буферный регистр

передатчика

U0DLL

Делитель (мл.байт)

U0DLM

Делитель (ст.байт)

U0IER Разрешение прерыв.

U0IIR Идентификация прер.

U0FCR

Управление FIFO

U0LCR

Управление линией

U0LSR

Статус линии

U0TER

Разрешение передачи

D7

D6

D5

D4

D3

D2

8 бит принятых данных (DLAB=0)

D1

D0

8 бит передаваемых данных (DLAB=0)

8 бит данных младшего байта делителя (DLAB=1)

8 бит данных старшего байта делителя (DLAB=1)

EnLinSt EnTxD EnRxD

FiFos Enable

IIR3

IIR2

IIR1

IIR0

RX trigger

TX FIFO RX FIFO FIFO

reset

reset Enable

DLAB

Set

Break

Even

Stick

Parity No stop

Parity Par.Selec Enable

bit

Word Length

select

RX FIFO TD

TH Reg Break Framing Parity Overrun RD

Error Empty Empty Interrupt Error

Error

Error ready

TX

Enable

-

-

-

-

-

-

-

4. Буферный регистр приемника U0RBR

Содержит верхний байт UART0 Rx FIFO. Доступен только для чтения и толькопри DLAB = 0 (Старший бит U0LCR ). Биты Ошибки четности (Parity Error),

Ошибки кадра (Frame Error) и Прерывания сброса (Break Interrupt) регистра

Статуса Линии U0LSR относятся к верхнему значению регистра FIFO.

Буферный регистр передатчика U0THR

Содержит верхний байт UART0 Tx FIFO. Доступен только для записи и только

при DLAB = 0 (Старший бит U0LCR ). После записи в него данные

помещаются в вершину UART Tx FIFO, если есть место, при этом

выставляется флаг (TH Reg Empty) регистра U0LSR (Статуса линии) и

генерируется прерывание, если разрешено.

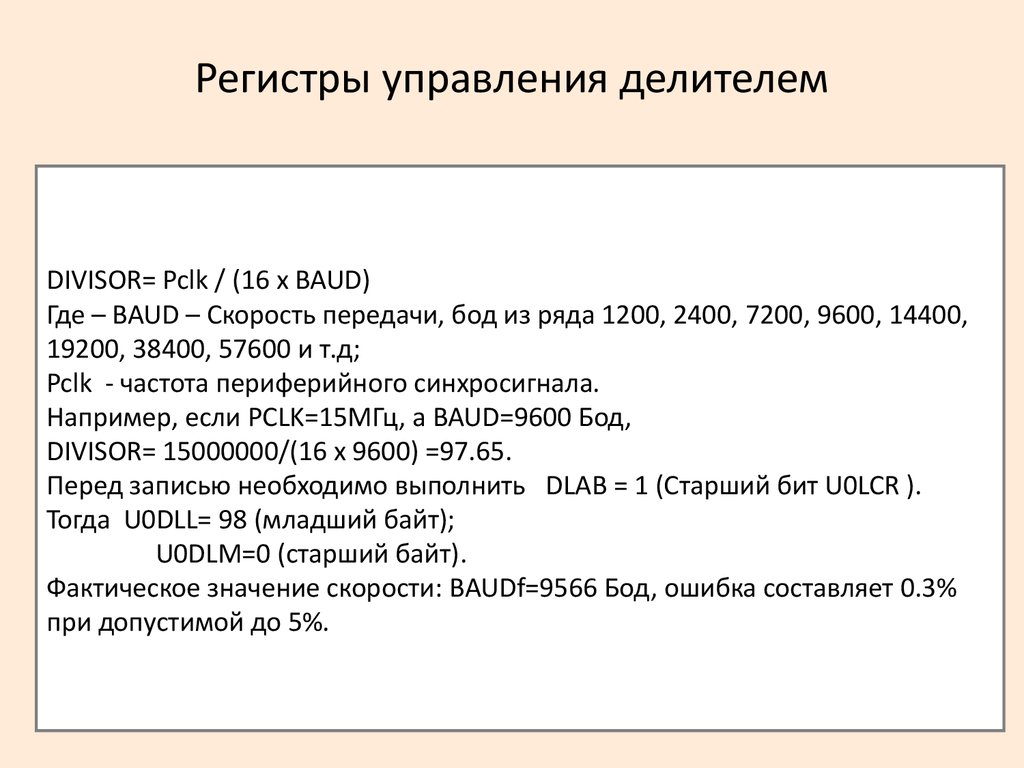

5. Регистры управления делителем

DIVISOR= Pclk / (16 x BAUD)Где – BAUD – Скорость передачи, бод из ряда 1200, 2400, 7200, 9600, 14400,

19200, 38400, 57600 и т.д;

Pclk - частота периферийного синхросигнала.

Например, если PCLK=15МГц, а BAUD=9600 Бод,

DIVISOR= 15000000/(16 x 9600) =97.65.

Перед записью необходимо выполнить DLAB = 1 (Старший бит U0LCR ).

Тогда U0DLL= 98 (младший байт);

U0DLM=0 (старший байт).

Фактическое значение скорости: BAUDf=9566 Бод, ошибка составляет 0.3%

при допустимой до 5%.

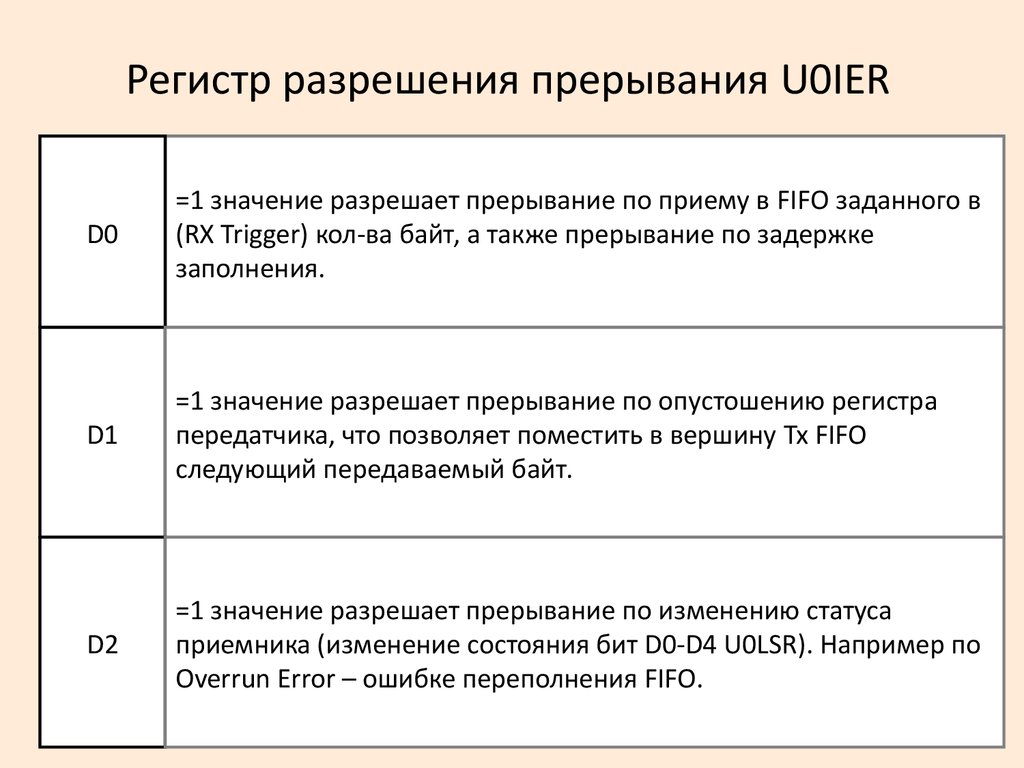

6. Регистр разрешения прерывания U0IER

D0=1 значение разрешает прерывание по приему в FIFO заданного в

(RX Trigger) кол-ва байт, а также прерывание по задержке

заполнения.

D1

=1 значение разрешает прерывание по опустошению регистра

передатчика, что позволяет поместить в вершину Tx FIFO

следующий передаваемый байт.

D2

=1 значение разрешает прерывание по изменению статуса

приемника (изменение состояния бит D0-D4 U0LSR). Например по

Overrun Error – ошибке переполнения FIFO.

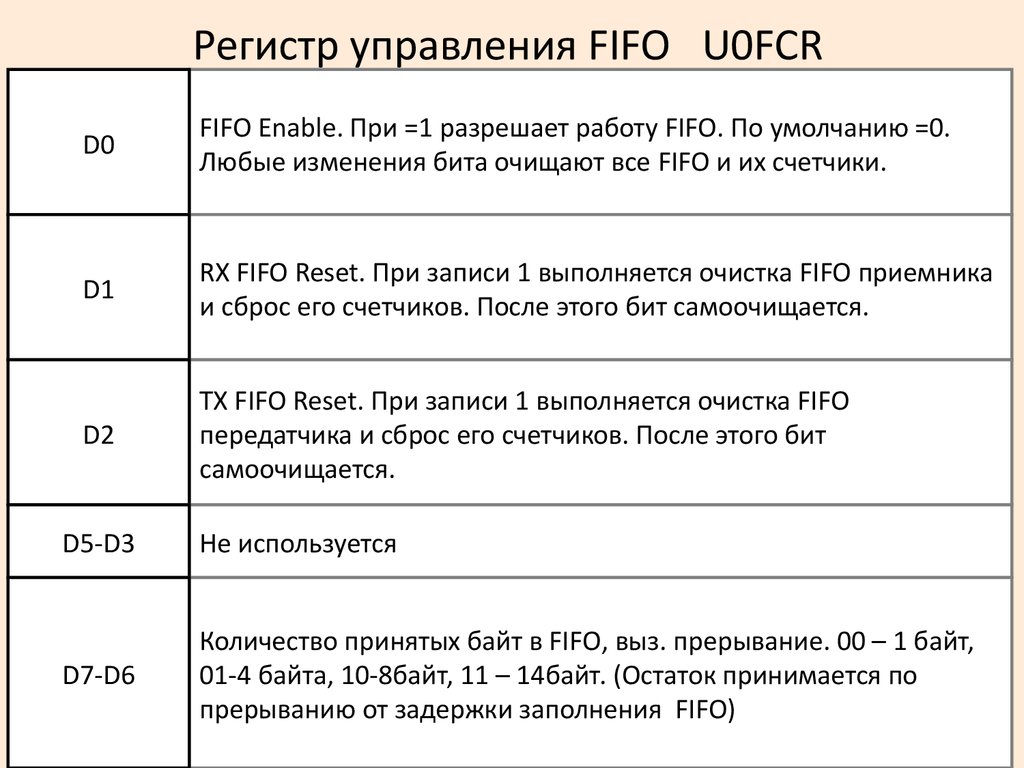

7. Регистр управления FIFO U0FCR

D0FIFO Enable. При =1 разрешает работу FIFO. По умолчанию =0.

Любые изменения бита очищают все FIFO и их счетчики.

D1

RX FIFO Reset. При записи 1 выполняется очистка FIFO приемника

и сброс его счетчиков. После этого бит самоочищается.

D2

TX FIFO Reset. При записи 1 выполняется очистка FIFO

передатчика и сброс его счетчиков. После этого бит

самоочищается.

D5-D3

Не используется

D7-D6

Количество принятых байт в FIFO, выз. прерывание. 00 – 1 байт,

01-4 байта, 10-8байт, 11 – 14байт. (Остаток принимается по

прерыванию от задержки заполнения FIFO)

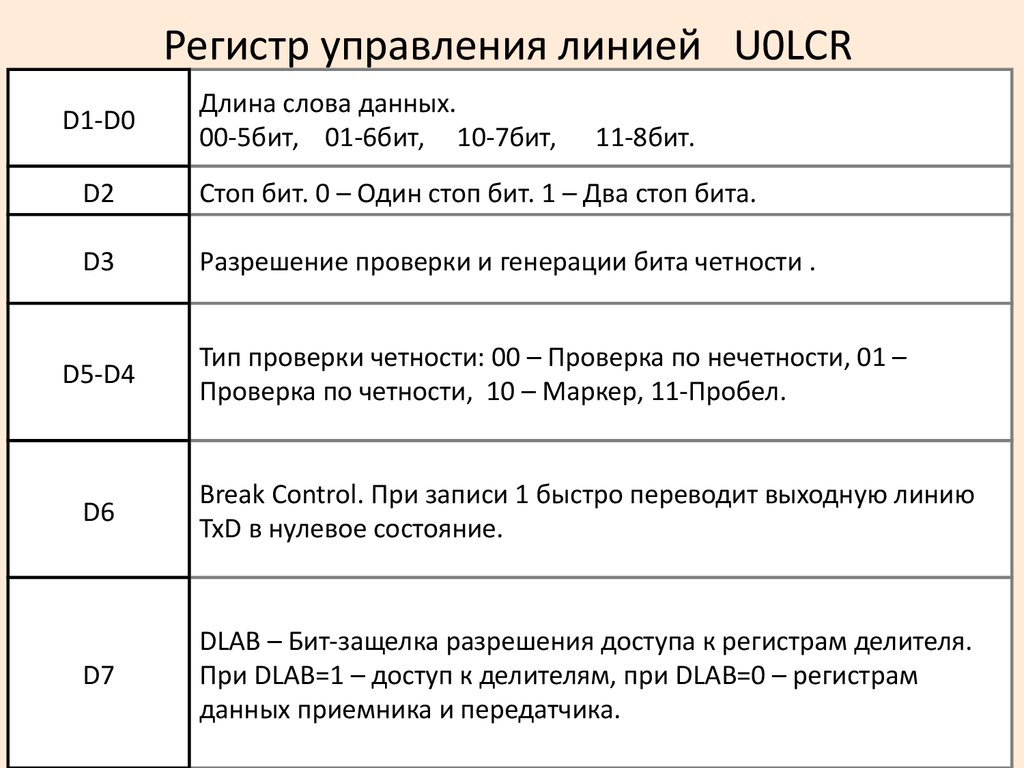

8. Регистр управления линией U0LCR

D1-D0Длина слова данных.

00-5бит, 01-6бит, 10-7бит,

11-8бит.

D2

Стоп бит. 0 – Один стоп бит. 1 – Два стоп бита.

D3

Разрешение проверки и генерации бита четности .

D5-D4

Тип проверки четности: 00 – Проверка по нечетности, 01 –

Проверка по четности, 10 – Маркер, 11-Пробел.

D6

Break Control. При записи 1 быстро переводит выходную линию

TxD в нулевое состояние.

D7

DLAB – Бит-защелка разрешения доступа к регистрам делителя.

При DLAB=1 – доступ к делителям, при DLAB=0 – регистрам

данных приемника и передатчика.

Электроника

Электроника