Похожие презентации:

Организация модулей запоминающих устройств

1. Организация модулей запоминающих устройств

2.

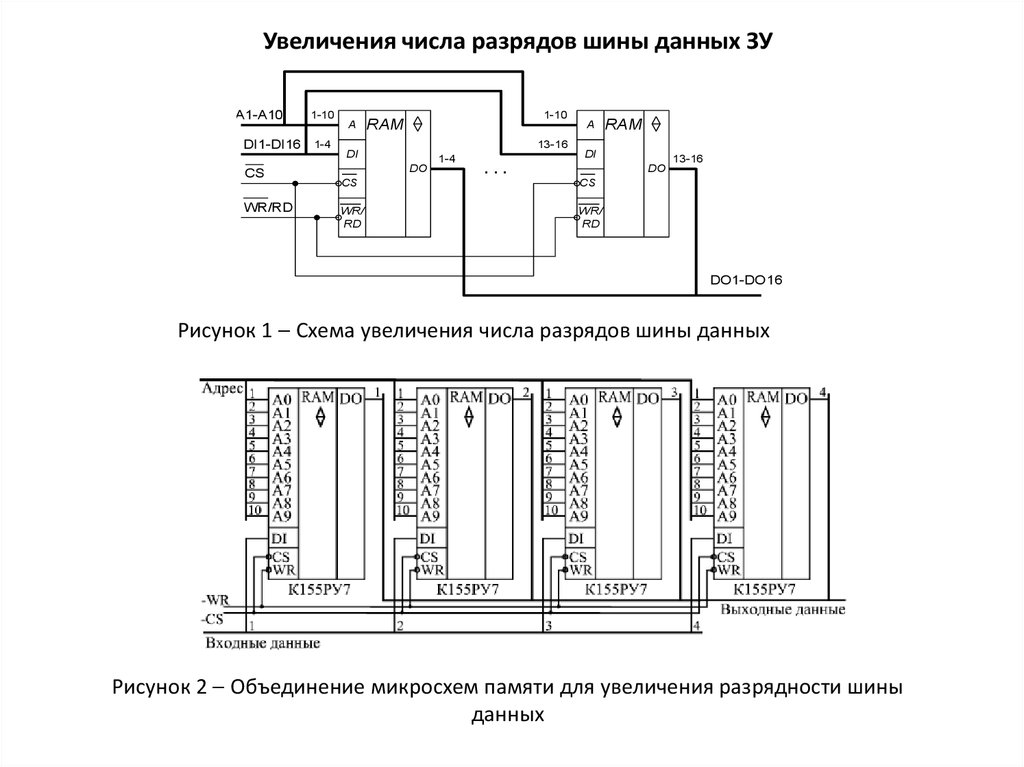

Увеличения числа разрядов шины данных ЗУA1-A10

1-10

DI1-DI16 1-4

CS

WR/RD

A

1-10

RAM

13-16

DI

DO

1-4

A

RAM

DI

...

DO

CS

CS

WR/

RD

WR/

RD

13-16

DO1-DO16

Рисунок 1 Схема увеличения числа разрядов шины данных

Рисунок 2 Объединение микросхем памяти для увеличения разрядности шины

данных

3.

AM

MM

A RAM

L=M-MM

A RAM

...

DI

DI

DO

DO

CS

WR/RD

WR/

RD

1.NC

...

CS

WR/

RD

1.1

1

...

DC

CS

CS

NR

A RAM

A RAM

DI

DI

DO

DO

CS

WR/

RD

DI

CS

WR/

RD NR.NC

NR.1

1

n

1

n

DO

Рисунок 3 Схема увеличения емкости ЗУ

Микросхемы ЗУ образуют матрицу NR NC. Старшие L разрядов входного

адреса поступают на дешифратор, выходы которого соединяются с входами CS

микросхем ЗУ соответствующих строк матрицы.

Входы и выходы данных одноименных разрядов микросхем ЗУ в столбцах

матрицы соединяются соответственно (предполагается, что выходы

невыбранных микросхем памяти находятся в состоянии высокого импеданса)

4.

Рисунок 4 Объединение микросхем памяти для увеличения разрядности шиныадреса

Дополнительный старший адресный разряд А16 управляет прохождением

сигнала –CS на одну из микросхем (при нулевом уровне на дополнительном

адресном разряде сигнал –CS проходит на левую по рисунку микросхему, при

единичном уровне – на правую по рисунку микросхему).

5.

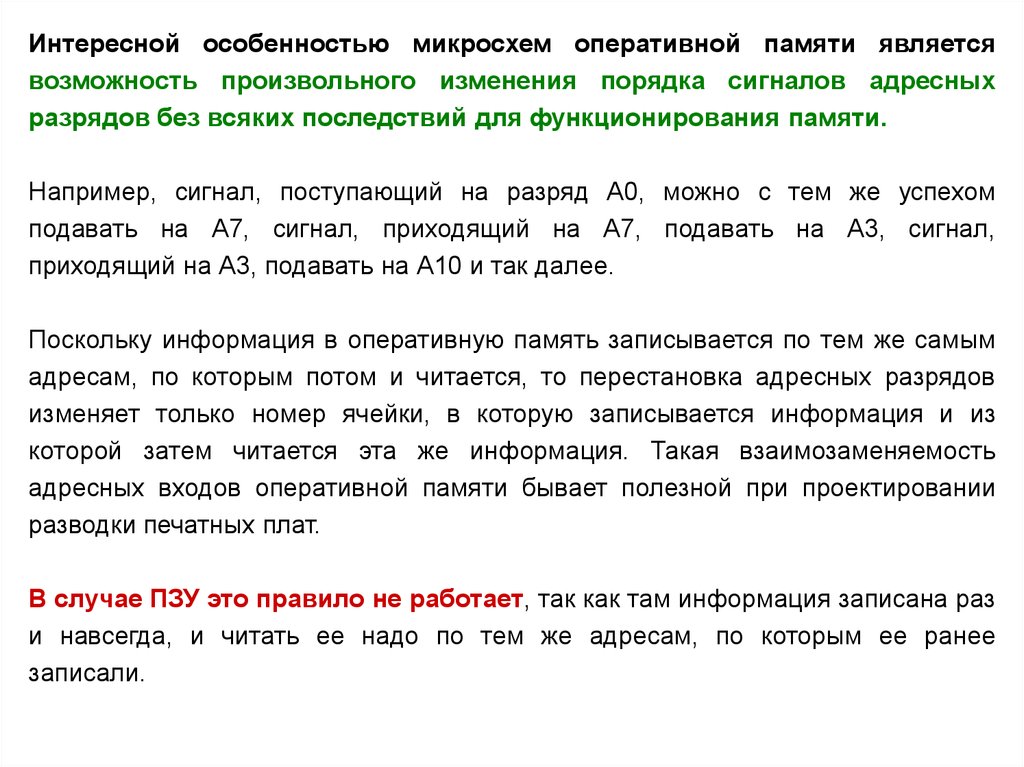

Интересной особенностью микросхем оперативной памяти являетсявозможность произвольного изменения порядка сигналов адресных

разрядов без всяких последствий для функционирования памяти.

Например, сигнал, поступающий на разряд А0, можно с тем же успехом

подавать на А7, сигнал, приходящий на А7, подавать на А3, сигнал,

приходящий на А3, подавать на А10 и так далее.

Поскольку информация в оперативную память записывается по тем же самым

адресам, по которым потом и читается, то перестановка адресных разрядов

изменяет только номер ячейки, в которую записывается информация и из

которой затем читается эта же информация. Такая взаимозаменяемость

адресных входов оперативной памяти бывает полезной при проектировании

разводки печатных плат.

В случае ПЗУ это правило не работает, так как там информация записана раз

и навсегда, и читать ее надо по тем же адресам, по которым ее ранее

записали.

6.

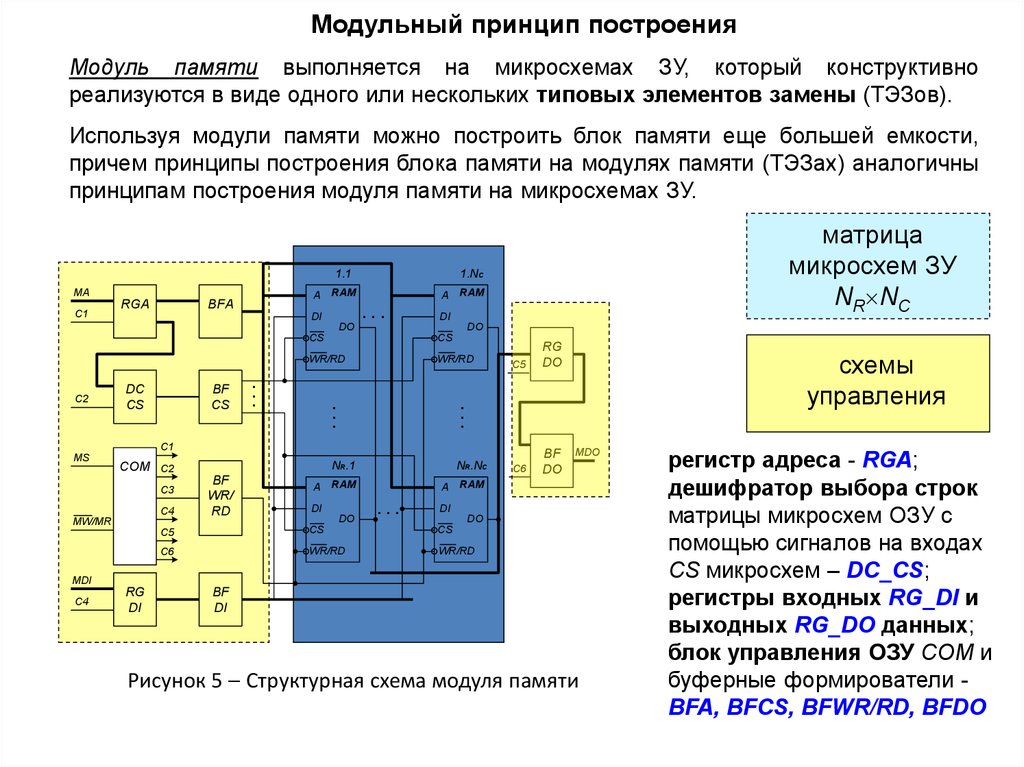

Модульный принцип построенияМодуль памяти выполняется на микросхемах ЗУ, который конструктивно

реализуются в виде одного или нескольких типовых элементов замены (ТЭЗов).

Используя модули памяти можно построить блок памяти еще большей емкости,

причем принципы построения блока памяти на модулях памяти (ТЭЗах) аналогичны

принципам построения модуля памяти на микросхемах ЗУ.

1.NC

1.1

MA

C1

A

BFA

RGA

RAM

A

...

DI

DO

CS

CS

WR/RD

WR/RD

...

...

...

BF

CS

DC

CS

RAM

DI

DO

C2

матрица

микросхем ЗУ

NR NC

NR.1

NR.NC

RAM

RAM

C5

RG

DO

C6

BF

DO

C1

MS

COM C2

C3

C4

MW/MR

BF

WR/

RD

A

DI

DO

A

...

схемы

управления

MDO

DI

DO

C5

CS

CS

C6

WR/RD

WR/RD

MDI

C4

RG

DI

BF

DI

Рисунок 5 Структурная схема модуля памяти

регистр адреса - RGA;

дешифратор выбора строк

матрицы микросхем ОЗУ с

помощью сигналов на входах

CS микросхем – DC_CS;

регистры входных RG_DI и

выходных RG_DO данных;

блок управления ОЗУ СОМ и

буферные формирователи ВFA, ВFCS, ВFWR/RD, ВFDO

7.

Постановка задачи проектирования модуля памятиИсходными данными для проектирования модуля памяти являются следующие:

1. емкость модуля памяти;

2. ограничения на значения внешних параметров модуля памяти (время

выборки, период обращения, потребляемая мощность, надежность,

температурный диапазон окружающей среды и др.);

3. электрические параметры и временное расположение входных и

выходных сигналов в режимах записи и считывания;

4. серии логических элементов, которые могут быть использованы в

схемах управления; некоторые специальные требования к модулю

памяти;

5. целевая функция проектирования.

8.

Процесс проектирования модуля памяти сводится к решению следующих задач:1. Выбор типа микросхемы ЗУ и определение их количества. В ряде случаев

тип используемой микросхемы ЗУ может задаваться, а не выбираться

произвольно.

2. Построение структурной схемы модуля памяти.

3. Выбор микросхем для реализации схем управления RGA (регистр адреса),

DC_CS (дешифратор выборки), RG_DI (регистр входных данных), RG_DO

(регистр выходных данных).

4. Расчёт электрического сопряжения микросхем памяти и схем управления, а так

же выбор элементов, используемых в качестве буферных формирователей.

5. Определение временных параметров модуля памяти. Построение временных

диаграмм работы модуля памяти в режимах записи и считывания.

6. Проектирование блока управления модуля памяти.

7. Расчет значений внешних параметров модуля памяти (потребляемая

мощность, потребляемый ток, тепловыделение, надёжность и др.).

8. Построение принципиальной электрической схемы модуля памяти.

9. Оформление результатов проектирования. Результаты проектирования

модуля памяти оформляются в виде технического описания и комплекта

электрических схем в соответствии с требованиями ГОСТ и ЕСКД. Эти

результаты являются исходными данными для конструирования модуля памяти.

Электроника

Электроника