Похожие презентации:

Разработка SATA - IO-link контроллера с программными интерфейсами Legacy и AHCI

1.

Выпускная квалификационная работаРазработка SATA - IO-link

контроллера с программными

интерфейсами Legacy и AHCI

Студент:Белянин И.В., ФРТК, 713 гр.

Научный руководитель:Петраков П.Ю.

2.

Развитие интерфейсов накопителейIDE

SATA

3.

Сравнение характеристик IDE и SATAIDE

Максимальная пропускная

способность

133 МБ/с (UDMA-6)

Способ передачи данных

параллельный интерфейс

Кодировка

нет

Методы контроля ошибок

CRC

Метод подключения устройств

master/slave

SATA

Максимальная пропускная

способность

SATA I — 150 МБ/c, SATA II 300 МБ/c

Способ передачи данных

последовательный интерфейс

Кодировка

8/10b

Методы контроля ошибок

CRC & Scrambling

Метод подключения устройств

точка-точка

4.

Постановка задачи-

Разработать

универсальный

SATA-контроллер,

удовлетворяющий следующим требованиям:

поддержка программных интерфейсов Legacy и

AHCI

контроллер обязан полностью соответствовать

стандартам SATA v2.5 и AHCI v1.3

интерфейс внешнего взаимодействия IO-link

использование

физического

уровня

фирмы

«Synopsys»

надежная работа в режимах SATA I — 1.5 GHz и

SATA II — 3 GHz

5.

Расположение контроллера вструктуре вычислительного

комплекса

Контроллер

может

располагаться

как

в

составе чипсета или

южного моста, так и

подключаться извне с

использованием

шин

PCI/PCI-X.

6.

Схема функциональных уровнейстандарта SATA

-

Commands and Application ― верхний

уровень, обрабатывающий поступающие

команды,

работающий

с

памятью,

выставляющий прерывания и т.д.;

-

Serial

Digital

Transport

транспортный

Control

уровень

выполняет

преобразование

информации

―

контрольной

или

данных,

которые

необходимо передать, в пакеты\фреймы

(Frame Information Structure, FIS);

-

Serial Digital Link Layer ― реализует

протокол звена данных, кодировка 8\10b;

-

Serial

Physical

физический

передачу

Interface

уровень

и

Plant

―

отвечает

за

данных

по

прием

последовательному каналу;

7.

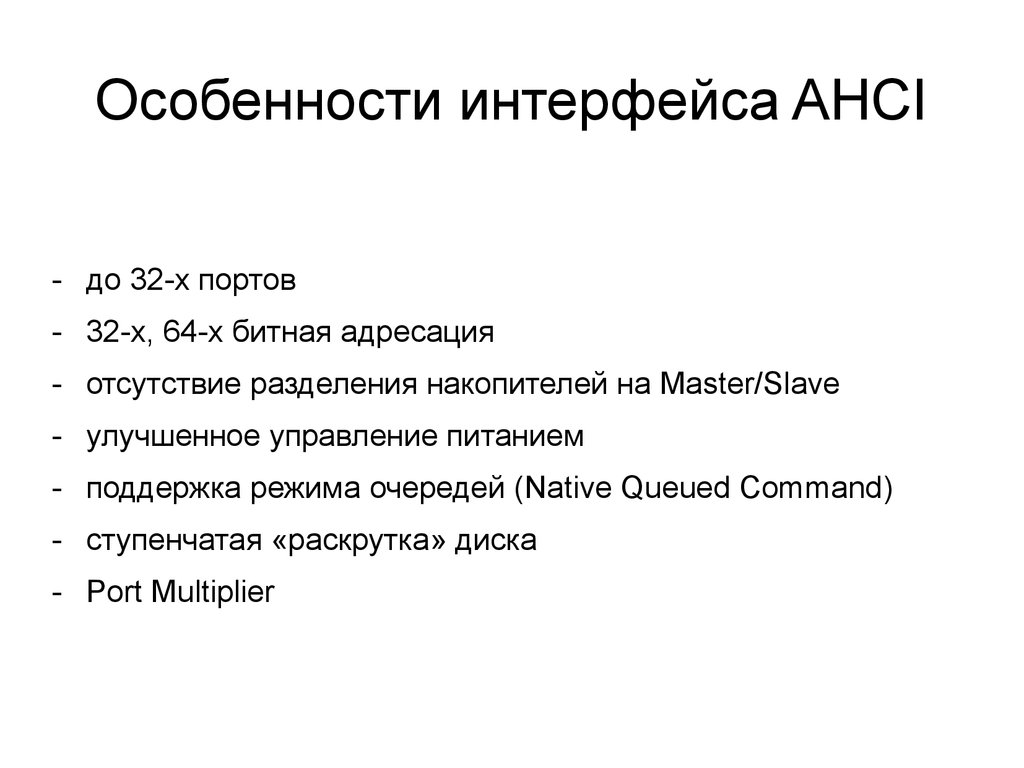

Особенности интерфейса AHCI- до 32-х портов

- 32-х, 64-х битная адресация

- отсутствие разделения накопителей на Master/Slave

- улучшенное управление питанием

- поддержка режима очередей (Native Queued Command)

- ступенчатая «раскрутка» диска

- Port Multiplier

8.

Конфигурационное пространство AHCI-

Конфигурационное

пространство

AHCI полностью совпадает с

конфигурационным

устройством

PCI контроллера.

Базовые адреса, расположенные в

конфигурационном пространстве:

один базовый адрес 24h (реализация

AHCI);

пять базовых адресов (интерфейс

Legacy);

9.

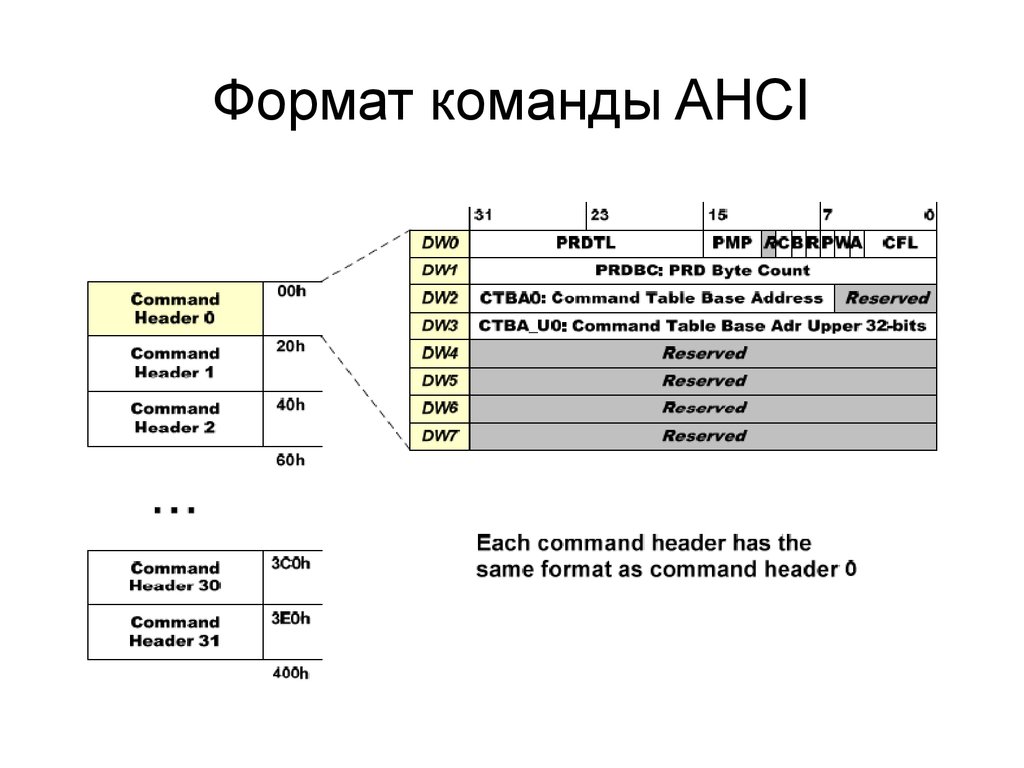

Формат команды AHCI10.

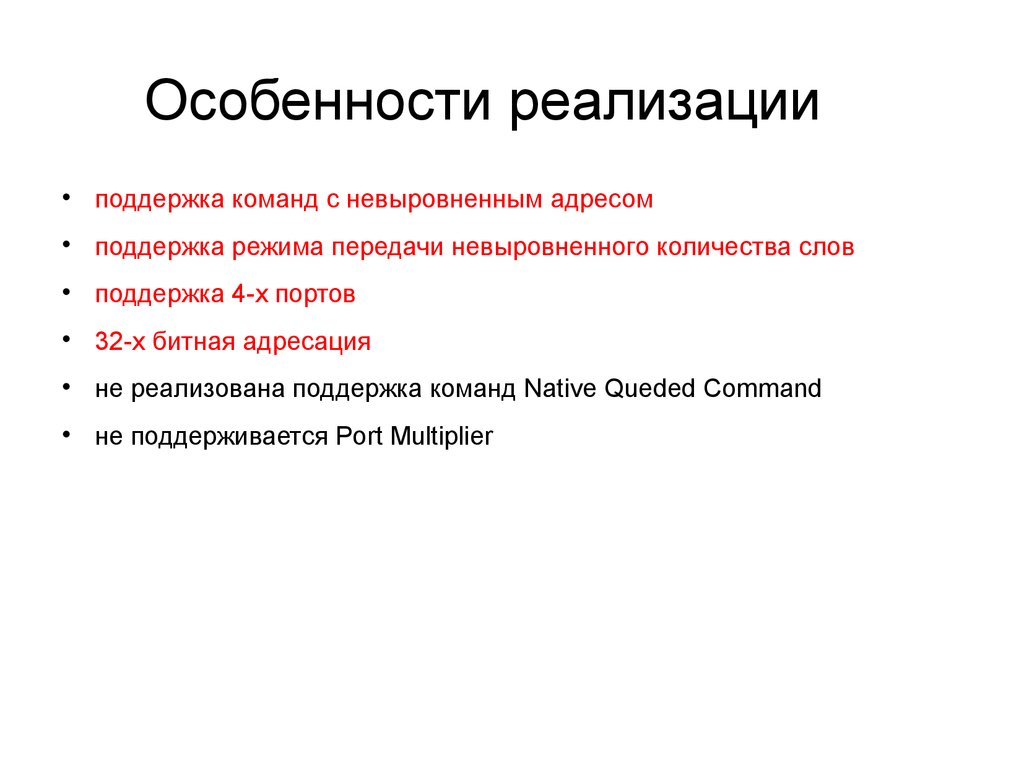

Особенности реализацииподдержка команд с невыровненным адресом

поддержка режима передачи невыровненного количества слов

поддержка 4-х портов

32-х битная адресация

не реализована поддержка команд Native Queded Command

не поддерживается Port Multiplier

11.

Реализация-

IO-link client ― модуль, отвечающий за

проведение транзакций на IO-link-интерфейсе;

-

SATA

―

IO-link

конфигурационное

Config

Space

пространство

―

(набор

управляющих регистров) совпадающее с PCI

Config Space;

-

DMA Arbiter ― модуль, обеспечивающий

арбитраж сигналов с разных портов;

-

AHCI HCSM (AHCI HBA Controller State

Machine) ― модуль, определяющий внешнее

поведение контроллера в режиме AHCI,

содержит в себе такие опции как глобальный

reset, бит AHCI enable, а также набор

регистров

отвечающих

за

поведение

устройства;

-

SATA Port ― модуль, включающий в себя,

модули отвечающие за обработку данных и

общение с диском, самая объемная часть

контроллера. К порту через SATA кабель

подключается накопитель данных.

12.

Внутреннее устройство модуля SATA-port13.

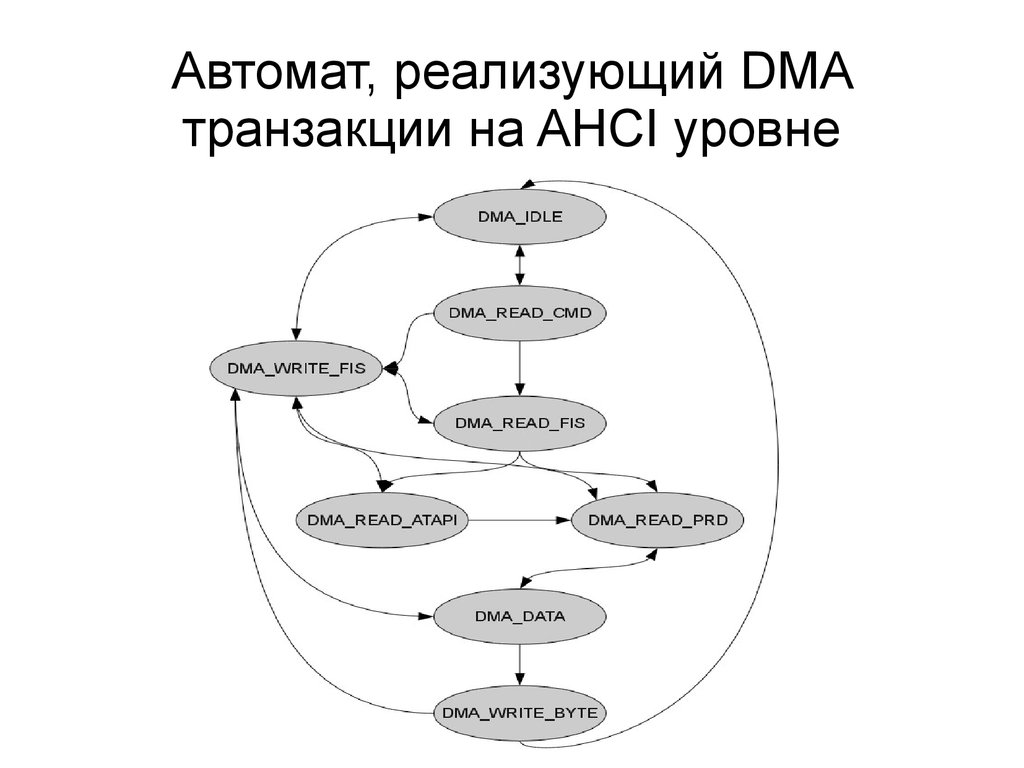

Автомат, реализующий DMAтранзакции на AHCI уровне

14.

МоделированиеПример выполнения команды на уровне Commands & Application с интерфейсом AHCI

-

Порядок выполнения теста:

инициализация диска(OOB sequence);

выполнение команды записи данных на диск по определенному адресу;

выполнение команды чтения данных с диска по тому же адресу;

cравнение данных в памяти;

смещение адреса и данных на фиксированную величину и повторение команды:

15.

Отладка на макетеИз-за отсутствия тестового стенда с

интерфейсом был использован PCI-интерфейс.

-

IO-link

Использованное тестовое оборудование:

ВК на основе микропроцессора МЦСТ «R150»

набор тестов, входящих в состав boot

макетная плата (4 разъема SATA, ПЛИС Xilinx Virtex-5,

SATA phy layer GTP-Dual Transceiver, 1 PCI разъем)

логический анализатор ПО ChipScope Analyzer

Принцип тестирования совпадает с уже использованным

при моделировании.

16.

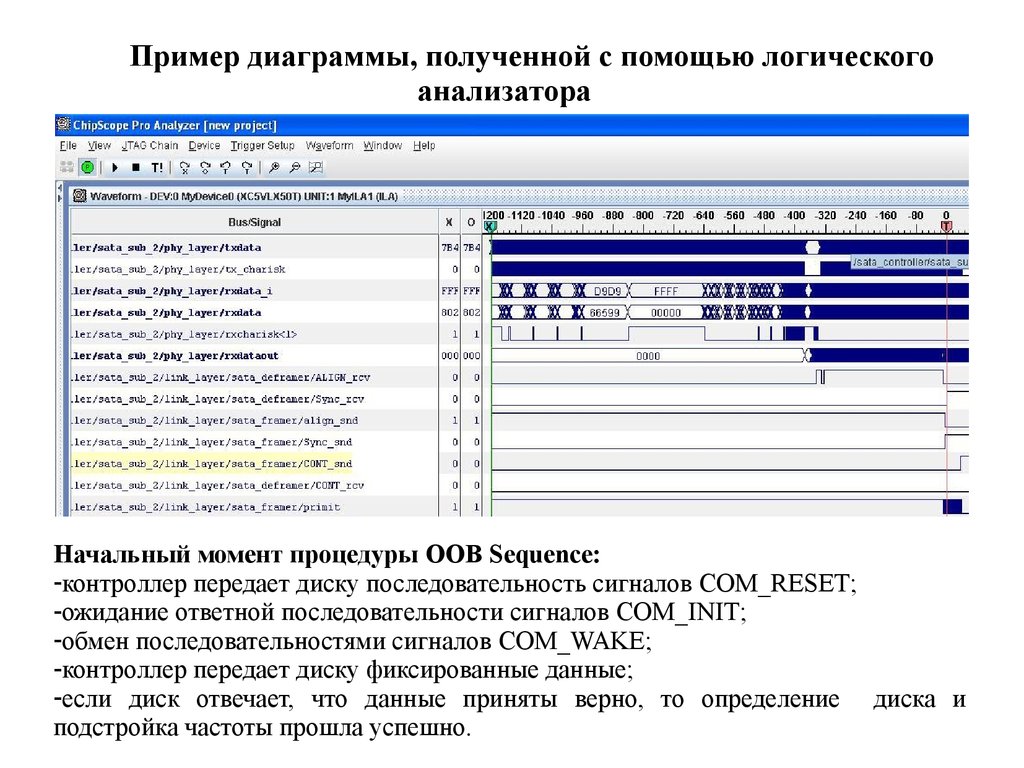

Пример диаграммы, полученной с помощью логическогоанализатора

Начальный момент процедуры OOB Sequence:

-контроллер передает диску последовательность сигналов COM_RESET;

-ожидание ответной последовательности сигналов COM_INIT;

-обмен последовательностями сигналов COM_WAKE;

-контроллер передает диску фиксированные данные;

-если диск отвечает, что данные приняты верно, то определение диска и

подстройка частоты прошла успешно.

17.

Результаты:- разработано RTL-описание универсального SATA- IO-link контроллера с

интерфейсами Legacy и AHCI;

- получен макет контроллера с PCI-интерфейсом;

- собран тестовый стенд и успешно проведены имеющиеся тесты

контроллера в составе стенда с использованием реальных SATA дисков

фирмы Maxtor

Перспективы:

проведение более сложных тестов, включающих загрузку

операционной системы с диска и имитацию работы пользователя.

реализация функции Native Queded Command

проведение отладки устройства на тестовом стенде с IO-linkинтерфейсом.

В конечном итоге данный контроллер будет реализован на кристалле

в составе южного моста, разработанного компанией ЗАО «МЦСТ».

Информатика

Информатика Электроника

Электроника