Похожие презентации:

Исследование триггеров

1.

Исследование триггеровЦель работы: Ознакомиться с работой основных типов триггеров RS, D, T.

1. Основные теоретические положения

Одно из наиболее распространённых импульсных устройств, относящихся к базовым

элементам цифровой техники – триггер. Триггером называют устройство, обладающее двумя

устойчивыми состояниями и способное скачком переходить из одного состояния в другое под

воздействием внешнего управляющего сигнала.

В современной электронике триггеры выполняются, как правило, в виде микросхем,

построенных на основе логических элементов. Триггеры можно классифицировать по

функциональному признаку и по способу управления. По функциональному признаку различают

триггеры RS, D, T, JK и других типов, по способу управления – асинхронные и синхронные

(тактируемые).

По виду входных сигналов триггеры можно разделить на статические и динамические.

Первые из них реагируют на уровни входных сигналов, а вторые – на перепады уровней

логических сигналов с “0” на “1” или с “1” на “0”.

1.1 RS – триггер

Данный триггер относится к асинхронным, так как переход его из одного состояния в

другое происходит только при поступлении сигналов на информационные (R, S) входы и не связан

с тактовыми сигналами.

Вход S называется установочным (от англ. Set – устанавливать), а вход R – входом сброса

(от англ. Reset – вновь устанавливать).

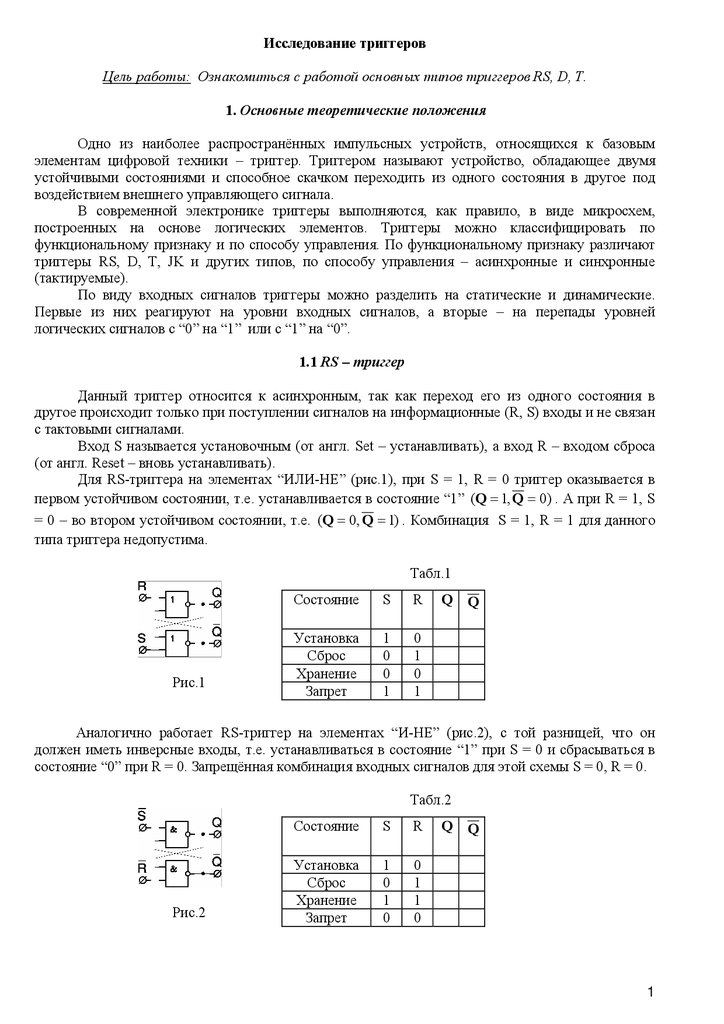

Для RS-триггера на элементах “ИЛИ-НЕ” (рис.1), при S = 1, R = 0 триггер оказывается в

первом устойчивом состоянии, т.е. устанавливается в состояние “1” (Q = 1, Q = 0) . А при R = 1, S

= 0 – во втором устойчивом состоянии, т.е. (Q = 0, Q = 1) . Комбинация S = 1, R = 1 для данного

типа триггера недопустима.

Табл.1

Рис.1

Состояние

S

R

Установка

Сброс

Хранение

Запрет

1

0

0

1

0

1

0

1

Q

Q

Аналогично работает RS-триггер на элементах “И-НЕ” (рис.2), с той разницей, что он

должен иметь инверсные входы, т.е. устанавливаться в состояние “1” при S = 0 и сбрасываться в

состояние “0” при R = 0. Запрещённая комбинация входных сигналов для этой схемы S = 0, R = 0.

Табл.2

Рис.2

Состояние

S

R

Установка

Сброс

Хранение

Запрет

1

0

1

0

0

1

1

0

Q

Q

1

2.

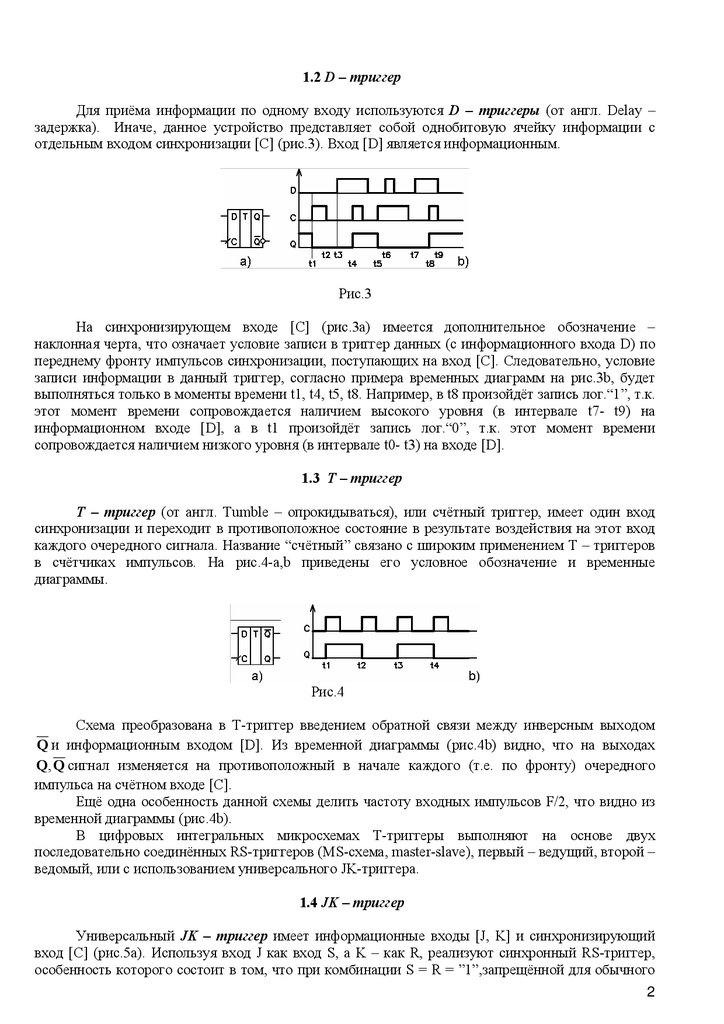

1.2 D – триггерДля приёма информации по одному входу используются D – триггеры (от англ. Delay –

задержка). Иначе, данное устройство представляет собой однобитовую ячейку информации с

отдельным входом синхронизации [C] (рис.3). Вход [D] является информационным.

Рис.3

На синхронизирующем входе [C] (рис.3а) имеется дополнительное обозначение –

наклонная черта, что означает условие записи в триггер данных (с информационного входа D) по

переднему фронту импульсов синхронизации, поступающих на вход [C]. Следовательно, условие

записи информации в данный триггер, согласно примера временных диаграмм на рис.3b, будет

выполняться только в моменты времени t1, t4, t5, t8. Например, в t8 произойдёт запись лог.“1”, т.к.

этот момент времени сопровождается наличием высокого уровня (в интервале t7- t9) на

информационном входе [D], а в t1 произойдёт запись лог.“0”, т.к. этот момент времени

сопровождается наличием низкого уровня (в интервале t0- t3) на входе [D].

1.3 T – триггер

T – триггер (от англ. Tumble – опрокидываться), или счётный триггер, имеет один вход

синхронизации и переходит в противоположное состояние в результате воздействия на этот вход

каждого очередного сигнала. Название “счётный” связано с широким применением T – триггеров

в счётчиках импульсов. На рис.4-a,b приведены его условное обозначение и временные

диаграммы.

Рис.4

Схема преобразована в T-триггер введением обратной связи между инверсным выходом

Q и информационным входом [D]. Из временной диаграммы (рис.4b) видно, что на выходах

Q, Q сигнал изменяется на противоположный в начале каждого (т.е. по фронту) очередного

импульса на счётном входе [С].

Ещё одна особенность данной схемы делить частоту входных импульсов F/2, что видно из

временной диаграммы (рис.4b).

В цифровых интегральных микросхемах Т-триггеры выполняют на основе двух

последовательно соединённых RS-триггеров (MS-схема, master-slave), первый – ведущий, второй –

ведомый, или с использованием универсального JK-триггера.

1.4 JK – триггер

Универсальный JK – триггер имеет информационные входы [J, K] и синхронизирующий

вход [C] (рис.5a). Используя вход J как вход S, а K – как R, реализуют синхронный RS-триггер,

особенность которого состоит в том, что при комбинации S = R = ”1”,запрещённой для обычного

2

3.

RS-триггера, он переключается (изменяет своё состояние на противоположное) на каждыйсинхронизирующий сигнал на входе [C].

Табл.3

Состояние

S

R

Установка

Сброс

Хранение

Инверсия

1

0

0

1

0

1

0

1

Q

Q

Рис.5

Так как при комбинации S = R = ”1”он переключается на каждый синхронизирующий

сигнал на входе [C], то соединив входы JK-триггера по схеме рис.5.b, можно получить T – триггер.

А добавлением инвертора на входе [K] (рис.5.с), схема преобразуется в D – триггер.

2. Практическое выполнение работы

Для практического выполнения задания, на универсальном стенде ОАВТ необходимо

установить плату N2 и карту-схему N2-A. Для подачи логических сигналов “0” и “1” на

исследуемые элементы, используются тумблер SA1 и кнопки SB1-SB3. Все элементы коммутации

имеют дополнительные формирователи одиночных импульсов для защиты от дребезга контактов.

2.1 Исследуйте работу RS-триггера на логических элементах “ИЛИ-НЕ”. На карточке ему

соответствует часть схемы с элементами D2.1, D2.2. Входные сигналы триггера по входу ”S”

поступают с кнопки SB3.2, по входу ”R” - с кн. SB2.2. В нормальном состоянии с кнопок SB3.2

(SB2.2) поступает сигнал, соответствующий уровню лог.“0”. При нажатии - сигнал уровня

лог.“1”. Уровни выходных сигналов по прямому выходу Q контролируются светодиодом N3,

по инверсному выходу Q , светодиодом N4. Данные исследования заносятся в табл.1.

2.2 Исследуйте работу RS-триггера на логических элементах “И-НЕ”. На карточке ему

соответствует часть схемы с элементами D1.1, D1.2. Входные сигналы триггера по входу ”S”

поступают с кнопки SB2.1, по входу ”R” - с кн. SB3.1. В нормальном состоянии с кнопок SB2.1

(SB3.1) поступает сигнал, соответствующий уровню лог.“1”. При нажатии - сигнал уровня

лог.“0”. Уровни выходных сигналов по прямому выходу Q контролируются светодиодом N3,

по инверсному выходу Q , светодиодом N4. Данные исследования заносятся в табл.2.

2.3 Исследуйте работу D-триггера. На карточке ему соответствует элемент D3.1. Сигналы на

информационный вход ”D” поступают с тумблера SA1, для которого уровень лог.“0”

соответствует нижнему положению переключателя. Разрешение записи данных в триггер

осуществляется кнопкой SB1. В нормальном состоянии с кнопки SB1 поступает сигнал,

соответствующий уровню лог.“1”. При нажатии - сигнал уровня лог.“0”. Уровни выходных

сигналов по прямому выходу Q контролируются светодиодом N2, по инверсному выходу Q ,

светодиодом N1.

3

4.

На рис.6 приведён пример подачи информационных и управляющих сигналов дляисследования данного триггера.

Рис.6

Дополните рис.6 и отобразите данные на прямом выходе Q триггера. Для помощи

приведены пояснения временных интервалов:

По входу данных ”D”:

t0-t3 - присутствует лог.”0” (тумблер SA1 в нижнем положении);

t3-t6 - присутствует лог.”1” (тумблер SA1 в верхнем положении);

По входу управления (разрешения записи) ”C”:

t0-t1 - присутствует лог.”1” (кнопка SB1 отжата);

t1-t2 - присутствует лог.”0” (кнопка SB1 нажата);

t1 - момент нажатия кнопки SB1;

t2 - момент отпускания кнопки SB1. При этом происходит смена логических уровней с “0”на

“1”, что является условием записи информации со входа ”D” в триггер.

2.4 Исследуйте работу T-триггера. На карточке ему соответствует элемент D3.2. Для

правильной работы схемы необходимо соединить на плате N2 стенда инверсный выход Q со

входом данных ”D”, с помощью технологической перемычки [Y1-X2]. Разрешение записи

данных в триггер, как и в предыдущем пункте, осуществляется кнопкой SB1. Уровни

выходных сигналов по прямому выходу Q контролируются светодиодом N1.

На рис.7 приведён пример подачи информационных и управляющих сигналов для

исследования данного триггера.

Рис.7

Дополните рис.7 и отобразите данные на прямом выходе Q триггера. Для помощи

приведены пояснения временных интервалов:

По входу управления (разрешения записи) ”C”:

t0-t1 - присутствует лог.”1” (кнопка SB1 отжата);

t1-t2 - присутствует лог.”0” (кнопка SB1 нажата);

t1 - момент нажатия кнопки SB1;

t2 - момент отпускания кнопки SB1. При этом происходит смена логических уровней с “0”на

“1”, что является условием записи информации со входа ”D” в триггер.

3. Указания к отчёту.

3.1 Результаты экспериментального исследования RS-триггеров заносятся в таблицы 1-2 и

анализируются, в соответствии с теоретическим материалом пункта 1.1.

4

5.

3.2 Результаты экспериментального исследования D и T-триггеров отображаются навременных диаграммах (рис.6-7) и анализируются, в соответствии с теоретическим материалом

пунктов 1.2 – 1.3.

3.3 Общие выводы по работе.

Приложение – 1: карта-схема N2-A

5

Электроника

Электроника