Похожие презентации:

Синхронная динамическая оперативная память

1.

Харьковский национальный университет радиоэлектроникиЛЕКЦИЯ 2–9

СИНХРОННАЯ ДИНАМИЧЕСКАЯ

ОПЕРАТИВНАЯ ПАМЯТЬ (SDRAM)

Кафедра КИТС

Кораблев Н.М.

2.

Харьковский национальный университет радиоэлектроникиSDR (Single Data Rate) SDRAM

SDRAM (Synchronous DRAM) – синхронная динамическая память с

произвольным доступом. Память работала синхронно с контроллером

памяти, что гарантировало завершение цикла чтения/записи строк в

заданное время. В SDRAM памяти было увеличено количество матриц

памяти с одной до двух, иногда до четырех. Это позволило во время

обращения к одной матрице памяти регенерировать строки другой

матрицы, что, в свою очередь, позволило поднять тактовую частоту

работы памяти, из-за уменьшения задержек на регенерацию.

В SDR SDRAM-памяти обеспечивается синхронизация всех

входных и выходных сигналов с положительными фронтами

импульсов тактового генератора.

Весь массив памяти SDRAM-модуля разделен на два независимых

банка. В SDR-памяти организована пакетная обработка данных, что

U cc 2

позволяет производить

обращение по новому адресу столбца ячейки

памяти на каждом тактовом цикле. Длина пакета (Burst Length, BL)

может составлять 2, 4 или 8 байт.

В SDR-памяти ядро памяти и буферы обмена работают в

синхронном режиме на одной и той же частоте. Передача каждого

бита из буфера происходит с каждым тактом работы ядра памяти.

Кафедра КИТС

Кораблев Н.М.

3.

Харьковский национальный университет радиоэлектроникиSDR (Single Data Rate) SDRAM

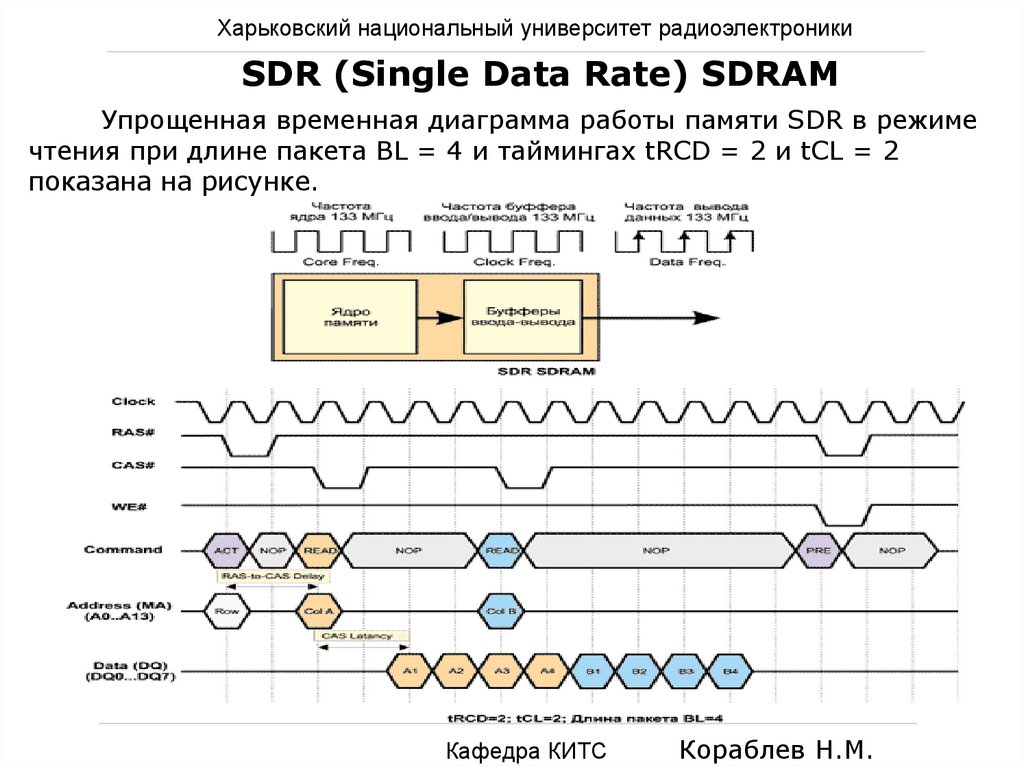

Упрощенная временная диаграмма работы памяти SDR в режиме

чтения при длине пакета BL = 4 и таймингах tRCD = 2 и tCL = 2

показана на рисунке.

U cc 2

Кафедра КИТС

Кораблев Н.М.

4.

Харьковский национальный университет радиоэлектроникиDDR (Double Data Rate) SDRAM

DDR SDRAM – синхронная динамическая память с произвольным

доступом и удвоенной частотой передачи данных. Обмен данными по

внешней шине идет не только по фронту тактового импульса, но и по

спаду. В результате, без увеличения тактовой частоты внешней шины

удваивается объем передаваемой информации.

Так как увеличить частоту работы оперативной памяти довольно

сложно, увеличили разрядность внутренней шины данных (от ячеек

матриц памяти до буферов ввода-вывода) и сделали ее в два раза

большей, чем разрядность внешней шины памяти (от контроллера

памяти до микросхемы памяти). Т.е. за 1 такт считывалось столько

данных, сколько могло передаваться по внешней шине только за два

такта (2n Prefetch - предвыборка 2n бит). Для памяти DDR минимальная

длина пакета составляет 2.

Отличительной

U cc 2особенностью DDR-памяти является реализация

четырех логических банков. Напряжение питания – 2,5V.

Из-за необходимости применять мультиплексор, для объединения

двух частей данных, передаваемых в оперативную память, и

демультиплексор, для разделения считываемых данных из памяти на

две части, сильно выросла латентность памяти. Латентность – это время

между запросом данных из памяти и временем, когда оперативная

память начнет выдавать требуемые данные.

Кафедра КИТС

Кораблев Н.М.

5.

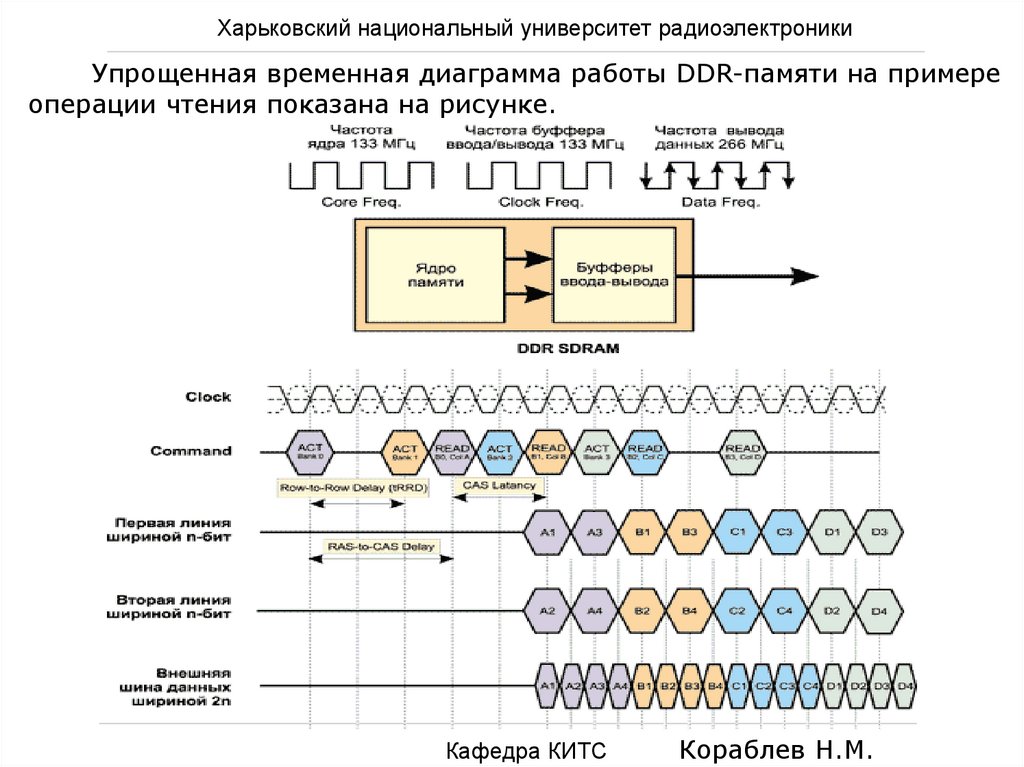

Харьковский национальный университет радиоэлектроникиУпрощенная временная диаграмма работы DDR-памяти на примере

операции чтения показана на рисунке.

Кафедра КИТС

Кораблев Н.М.

6.

Харьковский национальный университет радиоэлектроникиСтруктурная организация ИМС DDR объемом 32 Mb

(8192 строк, в каждой 512 блоков по 16 байт - 23 x29 x2x4=215=32 Mb)

CKE

CK#

CS#

WE#

CAS#

RAS#

CK

DC

команд

БЛУР

MX

адресов

строк

Счетчик

регистра

регенер.

13

DC –

регистр

адресов

строк

8192

Банки

0–3

8192х512х16

усилители

8192

13

A0 – A12

Блок

логического

управления

банками

Регистр

адресов

Управление

стробир.

операций I/O

16

Блок логики

управления

и формир.

потоков

данных

BA1, BA0

10

DQS

счетчик

регистр

столбцов

Кафедра КИТС

DC

столбцов

DM

1

Кораблев Н.М.

DQ0, DQ7

7.

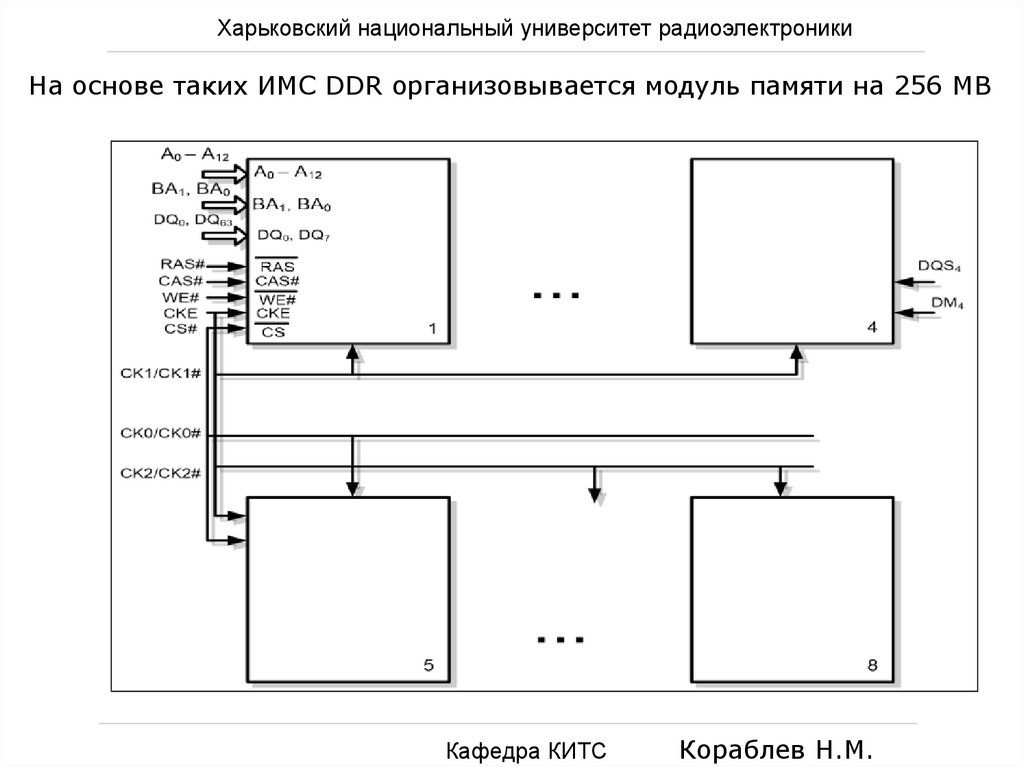

Харьковский национальный университет радиоэлектроникиНа основе таких ИМС DDR организовывается модуль памяти на 256 МВ

Кафедра КИТС

Кораблев Н.М.

8.

Харьковский национальный университет радиоэлектроникиDDR2 SDRAM

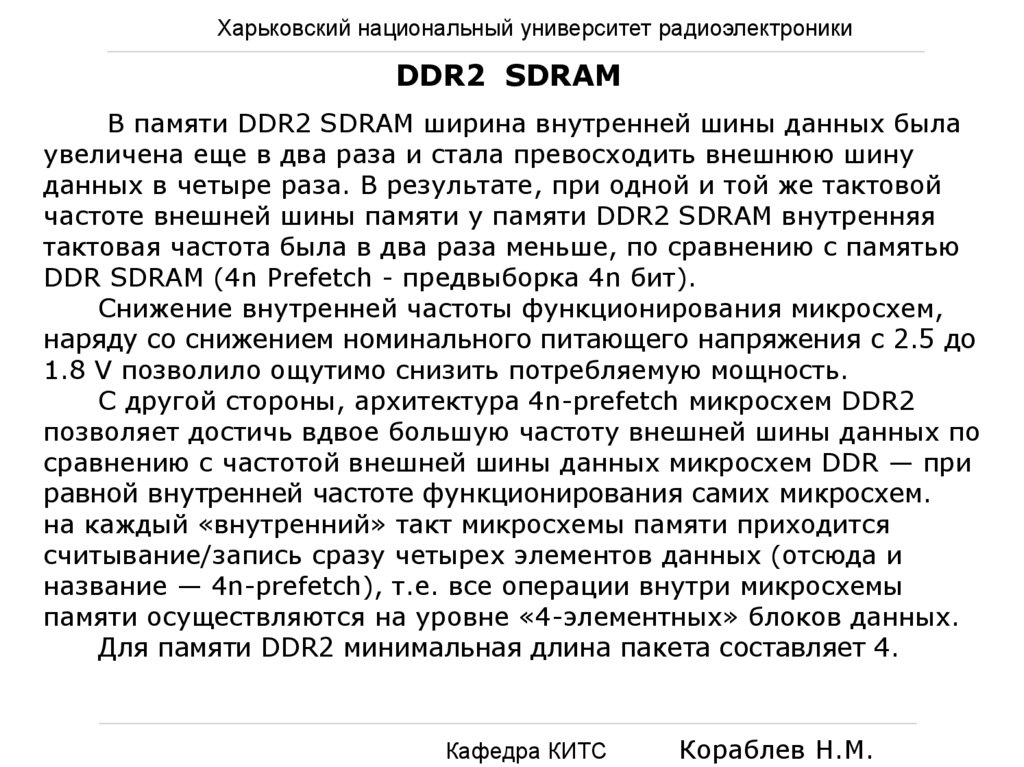

В памяти DDR2 SDRAM ширина внутренней шины данных была

увеличена еще в два раза и стала превосходить внешнюю шину

данных в четыре раза. В результате, при одной и той же тактовой

частоте внешней шины памяти у памяти DDR2 SDRAM внутренняя

тактовая частота была в два раза меньше, по сравнению с памятью

DDR SDRAM (4n Prefetch - предвыборка 4n бит).

Снижение внутренней частоты функционирования микросхем,

наряду со снижением номинального питающего напряжения с 2.5 до

1.8 V позволило ощутимо снизить потребляемую мощность.

С другой стороны, архитектура 4n-prefetch микросхем DDR2

позволяет достичь вдвое большую частоту внешней шины данных по

сравнению с частотой внешней шины данных микросхем DDR — при

равной внутренней частоте функционирования самих микросхем.

на каждый «внутренний» такт микросхемы памяти приходится

считывание/запись сразу четырех элементов данных (отсюда и

название — 4n-prefetch), т.е. все операции внутри микросхемы

памяти осуществляются на уровне «4-элементных» блоков данных.

Для памяти DDR2 минимальная длина пакета составляет 4.

Кафедра КИТС

Кораблев Н.М.

9.

Харьковский национальный университет радиоэлектроникиУпрощенная временная диаграмма работы DDR2-памяти на примере

операции чтения показана на рисунке.

Кафедра КИТС

Кораблев Н.М.

10.

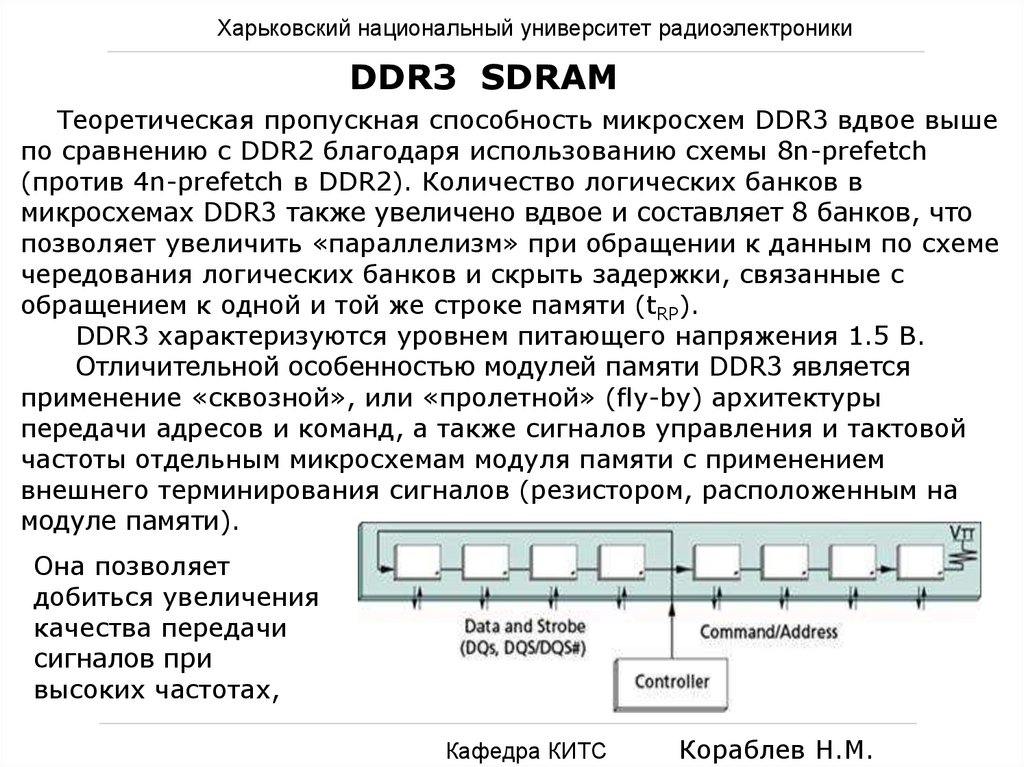

Харьковский национальный университет радиоэлектроникиDDR3 SDRAM

Теоретическая пропускная способность микросхем DDR3 вдвое выше

по сравнению с DDR2 благодаря использованию схемы 8n-prefetch

(против 4n-prefetch в DDR2). Количество логических банков в

микросхемах DDR3 также увеличено вдвое и составляет 8 банков, что

позволяет увеличить «параллелизм» при обращении к данным по схеме

чередования логических банков и скрыть задержки, связанные с

обращением к одной и той же строке памяти (tRP).

DDR3 характеризуются уровнем питающего напряжения 1.5 В.

Отличительной особенностью модулей памяти DDR3 является

применение «сквозной», или «пролетной» (fly-by) архитектуры

передачи адресов и команд, а также сигналов управления и тактовой

частоты отдельным микросхемам модуля памяти с применением

внешнего терминирования сигналов (резистором, расположенным на

модуле памяти).

Она позволяет

добиться увеличения

качества передачи

сигналов при

высоких частотах,

Кафедра КИТС

Кораблев Н.М.

11.

Харьковский национальный университет радиоэлектроникиDDR3 SDRAM

В модулях памяти DDR2 подача адресов и команд осуществляется

параллельно на все микросхемы модуля, в связи с чем, например, при

считывании данных, все восемь 8-битных элементов данных окажутся

доступными в один и тот же момент времени и контроллер памяти

сможет одновременно прочитать все 64 бита данных.

В модулях памяти DDR3 вследствие применения «пролетной»

архитектуры подачи адресов и команд каждая из микросхем модуля

получает команды и адреса с определенным отставанием

относительно предыдущей микросхемы, поэтому элементы данных,

соответствующие определенной микросхеме, также окажутся

доступными с некоторым отставанием. Для минимизации задержек, в

модулях памяти DDR3, по сравнению DDR2, реализован несколько

иной подход ко взаимодействию контроллера памяти с шиной данных

модуля памяти. Он называется «регулировкой уровня чтения/записи»

(read/write leveling) и позволяет контроллеру памяти использовать

определенное смещение по времени при приеме/передачи данных,

соответствующее «запаздыванию» поступления адресов и команд (а,

следовательно, и данных) в определенную микросхему модуля. Этим

достигается одновременность считывания (записи) данных из

микросхем (в микросхемы) модуля памяти.

Кафедра КИТС

Кораблев Н.М.

12.

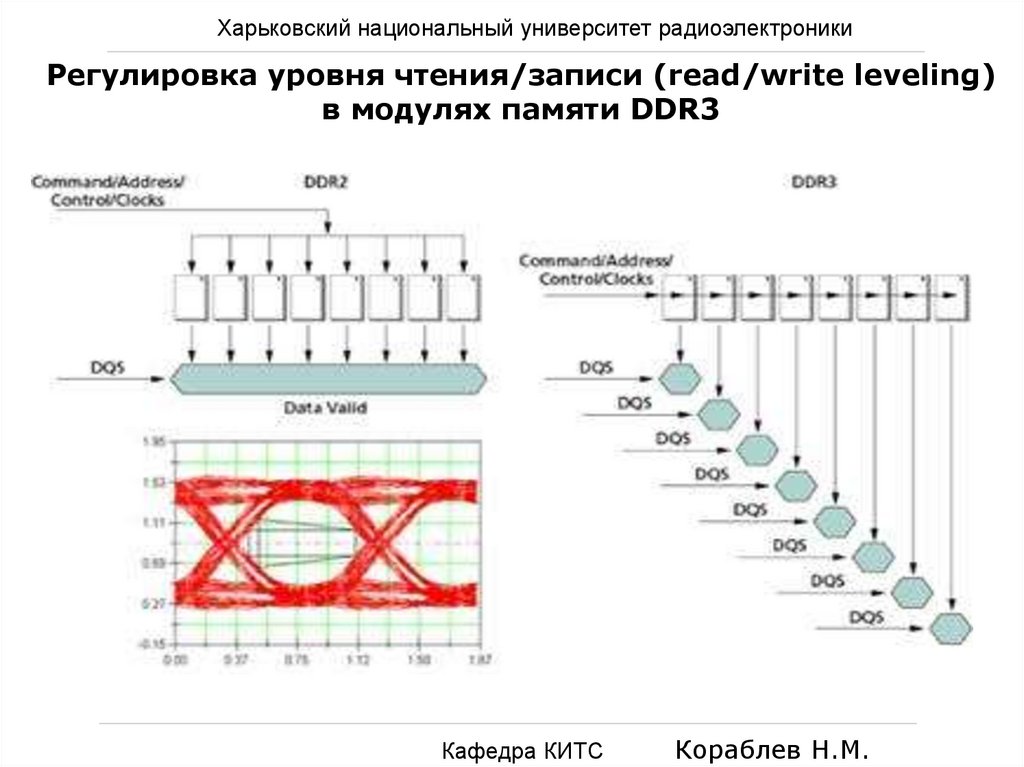

Харьковский национальный университет радиоэлектроникиРегулировка уровня чтения/записи (read/write leveling)

в модулях памяти DDR3

Кафедра КИТС

Кораблев Н.М.

13.

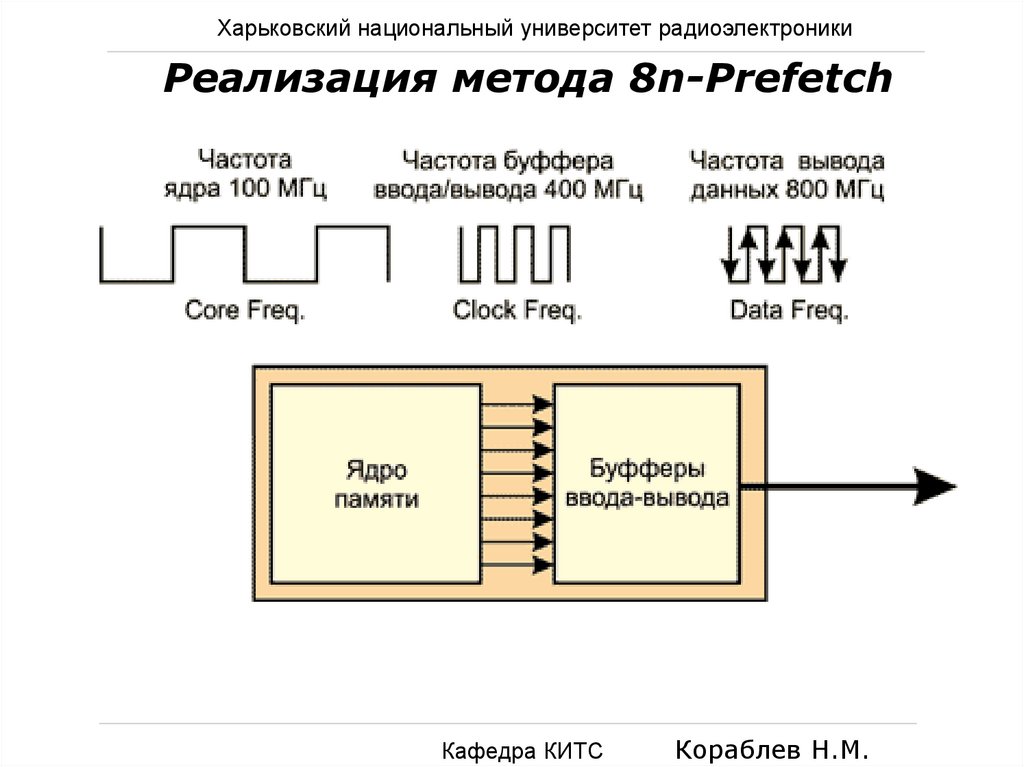

Харьковский национальный университет радиоэлектроникиРеализация метода 8n-Prefetch

Кафедра КИТС

Кораблев Н.М.

14.

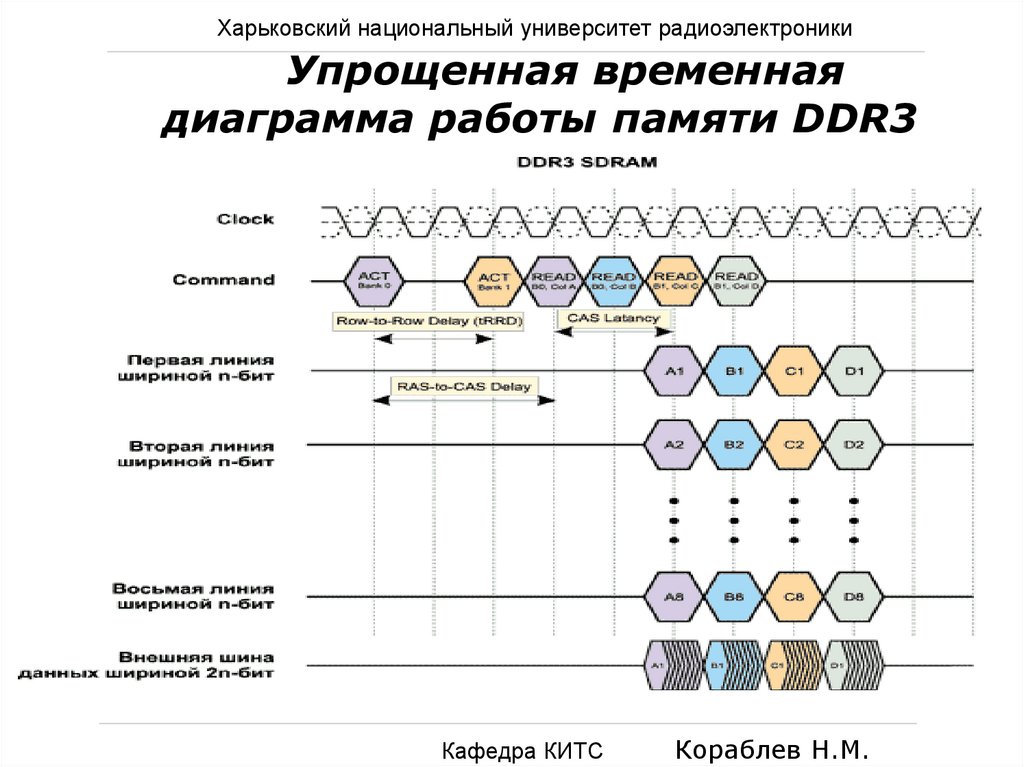

Харьковский национальный университет радиоэлектроникиУпрощенная временная

диаграмма работы памяти DDR3

Кафедра КИТС

Кораблев Н.М.

15.

Харьковский национальный университет радиоэлектроникиСтруктурная схема микросхем

памяти DDR3 объемом 1Г байт

Кафедра КИТС

Кораблев Н.М.

16.

Харьковский национальный университет радиоэлектроникиDDR4 SDRAM

DDR4 переняла архитектуру 2n-prefetch. Любой чип памяти

может состоять из двух или четырех отдельных групп банков.

Рассмотрим 8-гигабайтный DDR4-чип с шиной данных

шириной 4 бита. Он содержит 4 группы банков по 4 банка в

каждой. Внутри каждого банка находятся 131 072 (217) строки

емкостью 512 байт каждая. Для сравнения можно привести

характеристики аналогичного DDR3-решения. Такой чип

содержит 8 независимых банков. В каждом из банков

находятся 65 536 (216) строк, а в каждой строке — 2048 байт.

Как видно, длина каждой строки чипа DDR4 в четыре раза

меньше длины строки DDR3. Это означает, что DDR4

осуществляет «просмотр» банков быстрее, нежели DDR3. При

этом переключение между самими банками также происходит

гораздо быстрее.

Отметим, что для каждой группы банков предусмотрен

независимый выбор операций (активация, чтение, запись или

регенерация), что позволяет повысить эффективность и

пропускную способность памяти.

Кафедра КИТС

Кораблев Н.М.

17.

Харьковский национальный университет радиоэлектроникиDDR4 SDRAM

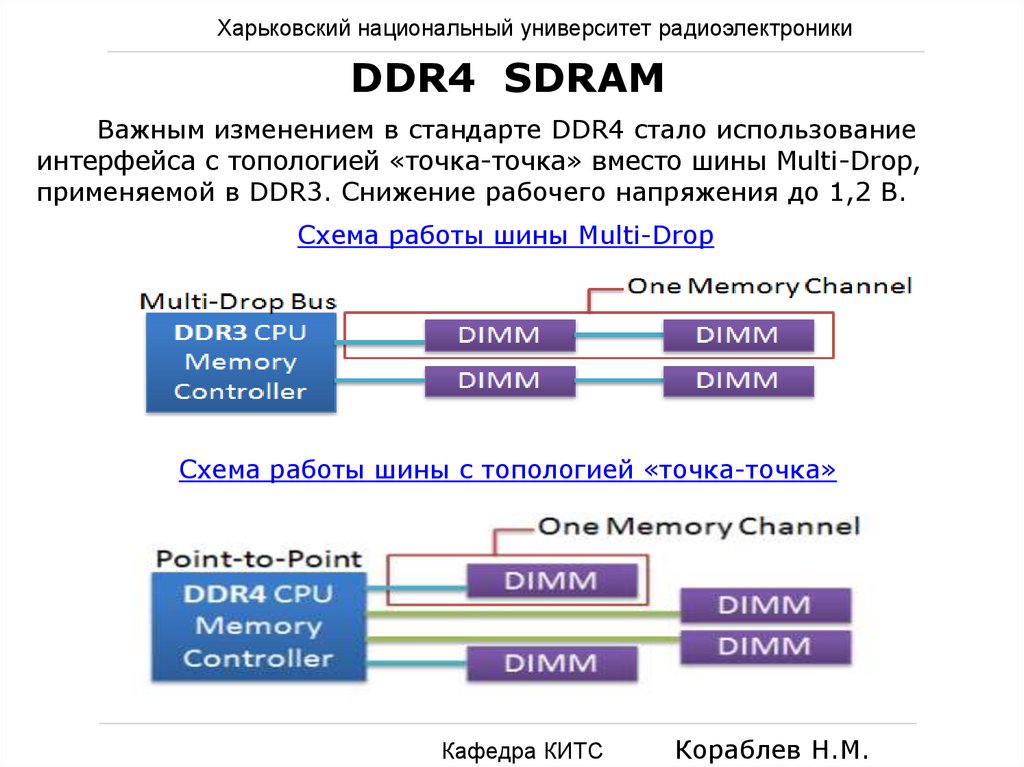

Важным изменением в стандарте DDR4 стало использование

интерфейса с топологией «точка-точка» вместо шины Multi-Drop,

применяемой в DDR3. Снижение рабочего напряжения до 1,2 В.

Схема работы шины Multi-Drop

Схема работы шины с топологией «точка-точка»

Кафедра КИТС

Кораблев Н.М.

18.

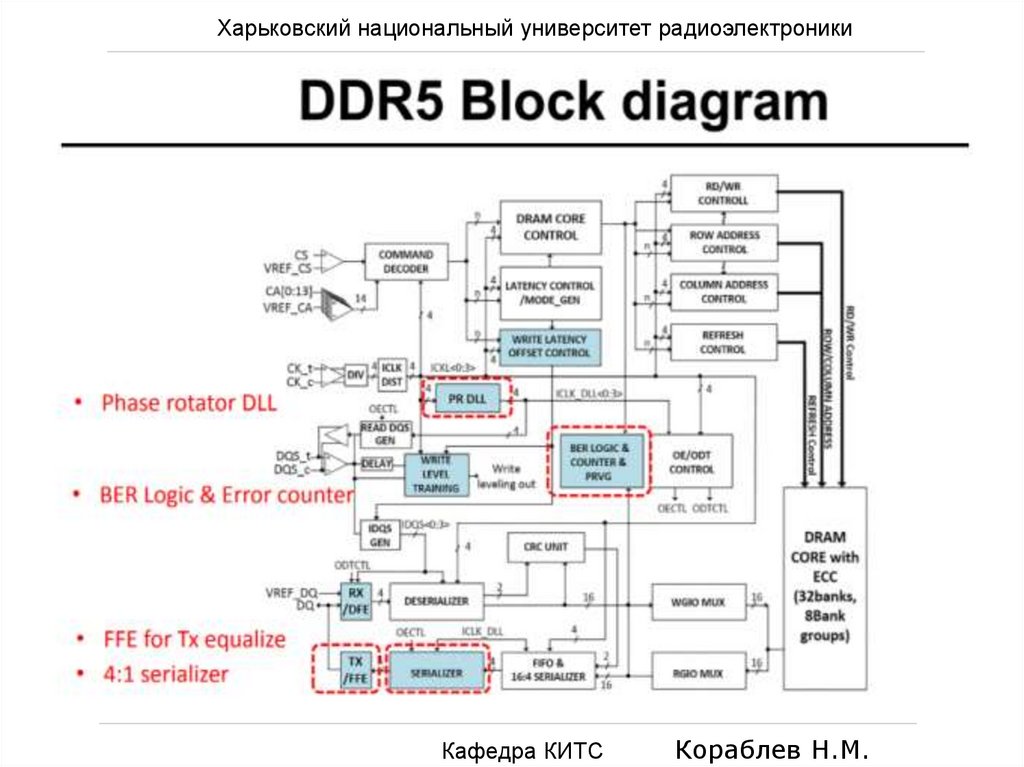

Харьковский национальный университет радиоэлектроникиDDR5 SDRAM

DDR5 — синхронная динамическая память с произвольным

доступом и удвоенной скоростью передачи данных пятого

поколения — новый перспективный стандарт оперативной

памяти. Новая спецификация обещает гораздо более высокую

производительность, чем у последнего внедрённого стандарта

DDR4, а также пониженное энергопотребление (1,1 В).

Оперативная память DDR5 будет отличаться удвоенной

ёмкостью и удвоенной производительностью по сравнению с

модулями DDR4 первого поколения.

Скорость передачи данных у DDR4 варьируется от 1600 до

3200 мегатранзакций в секунду (MT/sec). DDR5 увеличивает её

до 3200-6400 MT/sec.

На 3200 MT/sec, DDR4 имеет эффективную пропускную

способность 134,3 ГБ/с, DDR5 3200 обеспечит 182,5 ГБ/с, что

больше в 1,36х, а у DDR5 4800 прирост скорости составит

>1,85х.

Кафедра КИТС

Кораблев Н.М.

19.

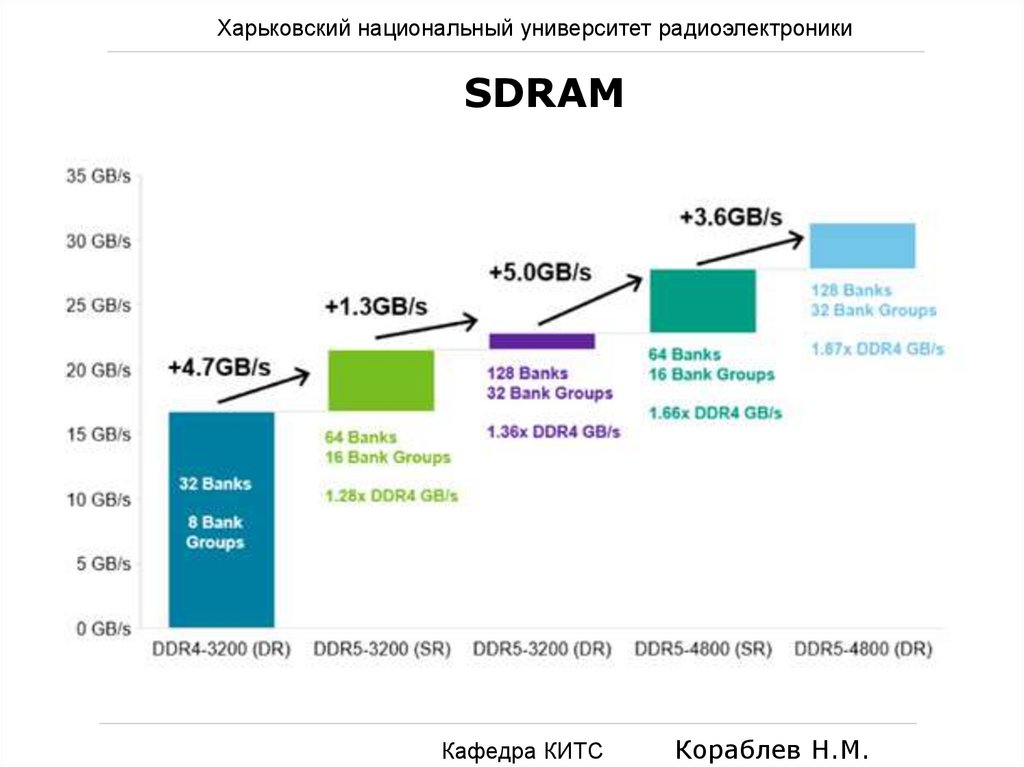

Харьковский национальный университет радиоэлектроникиSDRAM

Кафедра КИТС

Кораблев Н.М.

20.

Харьковский национальный университет радиоэлектроникиКафедра КИТС

Кораблев Н.М.

21.

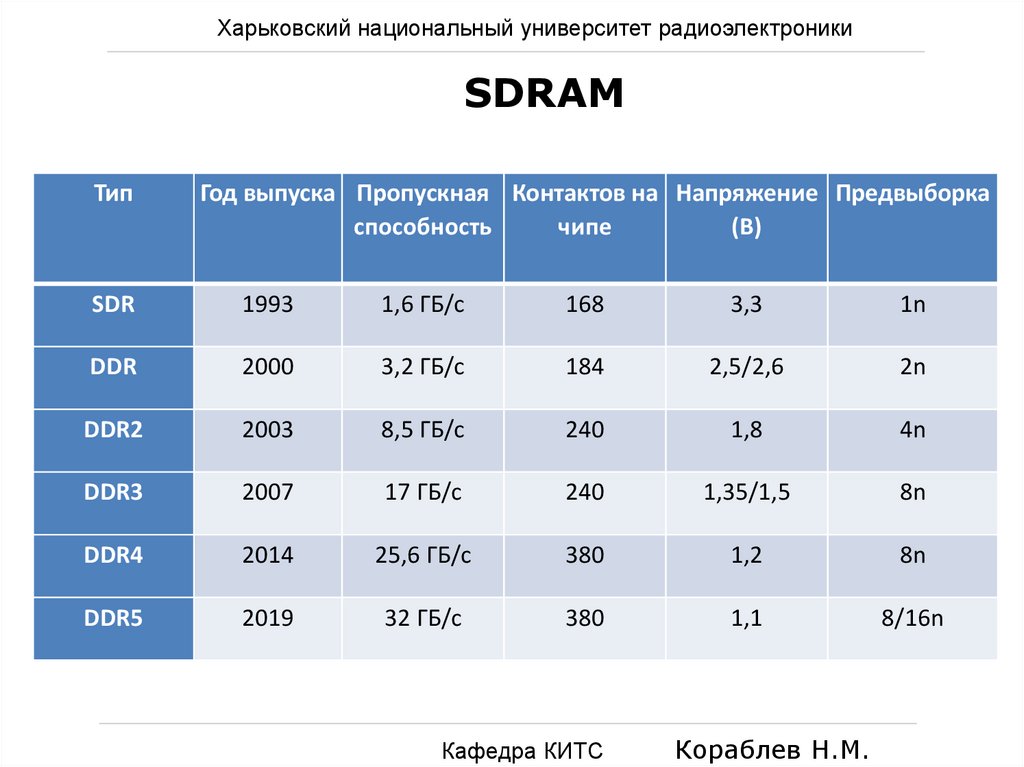

Харьковский национальный университет радиоэлектроникиSDRAM

Тип

Год выпуска Пропускная Контактов на Напряжение Предвыборка

способность

чипе

(В)

SDR

1993

1,6 ГБ/c

168

3,3

1n

DDR

2000

3,2 ГБ/c

184

2,5/2,6

2n

DDR2

2003

8,5 ГБ/c

240

1,8

4n

DDR3

2007

17 ГБ/c

240

1,35/1,5

8n

DDR4

2014

25,6 ГБ/c

380

1,2

8n

DDR5

2019

32 ГБ/c

380

1,1

8/16n

Кафедра КИТС

Кораблев Н.М.

22.

Харьковский национальный университет радиоэлектроникиДостоинства и недостатки

динамической памяти

Преимущества динамической памяти:

- низкая себестоимость;

- высокая степень упаковки, позволяющая создавать чипы

памяти большого объема.

Недостатки динамической памяти:

- относительно невысокое быстродействие, так как процесс

зарядки и разрядки конденсатора занимает гораздо больше

времени, чем переключение триггера;

- высокая латентность, в основном, из-за внутренней шины

данных, в несколько раз более широкой, чем внешняя, и

необходимости использования

мультиплексора/демультиплексора;

- необходимость регенерации заряда конденсатора, из-за его

быстрого саморазряда, ввиду микроскопических размеров.

Кафедра КИТС

Кораблев Н.М.

Электроника

Электроника