Похожие презентации:

Аппаратура цифровой обработки сигналов

1. ЛЕКЦЫЙНЫ КУРС «Апаратруа лічбавай апрацоўкі сігналаў» __________________________ ЛЕКЦИОННЫЙ КУРС «Аппаратура цифровой обработки

сигналов»2. Литература по курсу

Айфичер Э., Джервис Б. Цифровая обработка сигналов: практическийподход. – 2-е изд. – 2004. – 992 с.

Сергиенко А.Б. Цифровая обработка сигналов: Учебник для вузов. 2-е

изд. – СпБ.: Питер – 2007. – 751 с.: ил.

Сперанский В.С. Сигнальные процессоры и их применение в системах

телекоммуникаций и электроники. Учебное пособие для вузов. – М.: Горячая

линия-Телеком. – 2008. – 168 с.: ил.

Введение в цифровую фильтрацию / Под ред. Р. Богнера и

А. Константинидиса. – пер. с англ., под. ред Л.И. Филиппова – М.: Мир, 1976. –

216 с.

Гутников В. С. Фильтрация измерительных сигналов. – Ленинград:

Энергоатомиздат, 1990. – 190 с.

Калабеков Б.А. Микропроцессоры и их применение в системах

передачи и обработки сигналов: Учебное пособие для вузов. – М.: Радио и

связь, 1988. – 368 с.

Рабинер Л.Р., Голд Б. Теория и применение цифровой обработки

сигналов: Пер. с англ./ Под ред. Ю.Н. Александрова. М.: Мир, 1978.– 637 с.

Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения:

Справочник – 2-е изд., перераб. и доп. – М.: Радио и связь, 1990. – 512 с.

Сато Ю. Обработка сигналов. Первое знакомство. – 2002. – 175 с.: ил.

3. Общая классификация микропроцессорных средств

1. Микропроцессоры стандартной конфигурации, содержащиев своем составе арифметико-логическое устройство (АЛУ),

регистры и схемы управления.

2.

Однокристальные

микроконтроллеры

(ОМК,

ОЭВМ)

стандартной конфигурации с цифровыми портами. ОМК содержит в

своем составе не только АЛУ и регистры, но и дополнительные

модули, такие как память данных и память программ, таймеры,

порты ввода-вывода,

АЦП, ЦАП, аппаратные

драйверы

стандартных интерфейсов.

В настоящее время ОМК составляют

60-70% мирового рынка микропроцессорных средств.

Разновидностью ОМК являются PIC – контроллеры (Peripherial

Interface Controller) – микроконтроллеры с расширенными

возможностями по вводу-выводу.

Преимуществом ОМК является компактная система команд.

4. Общая классификация микропроцессорных средств

3. МSР (Mixed Signal Processor) – микропроцессоры свстроенным АЦП и аппаратным умножителем, предназначенные для

цифровой обработки аналоговых сигналов.

4. DSP (Digital Signal Processor) – микропроцессоры с

встроенным АЦП, система команд которых позволяет выполнять

базовую операцию «умножение с накоплением», предназначенные

для цифровой обработки аналоговых сигналов, для реализации

сложных вычислительных алгоритмов в реальном масштабе

времени. Типовыми задачами для реализации на основе DSP

являются алгоритмы преобразования Фурье, дискретной свертки,

цифровой фильтрации, корреляции.

Далее для обозначения термина «Цифровой сигнальный

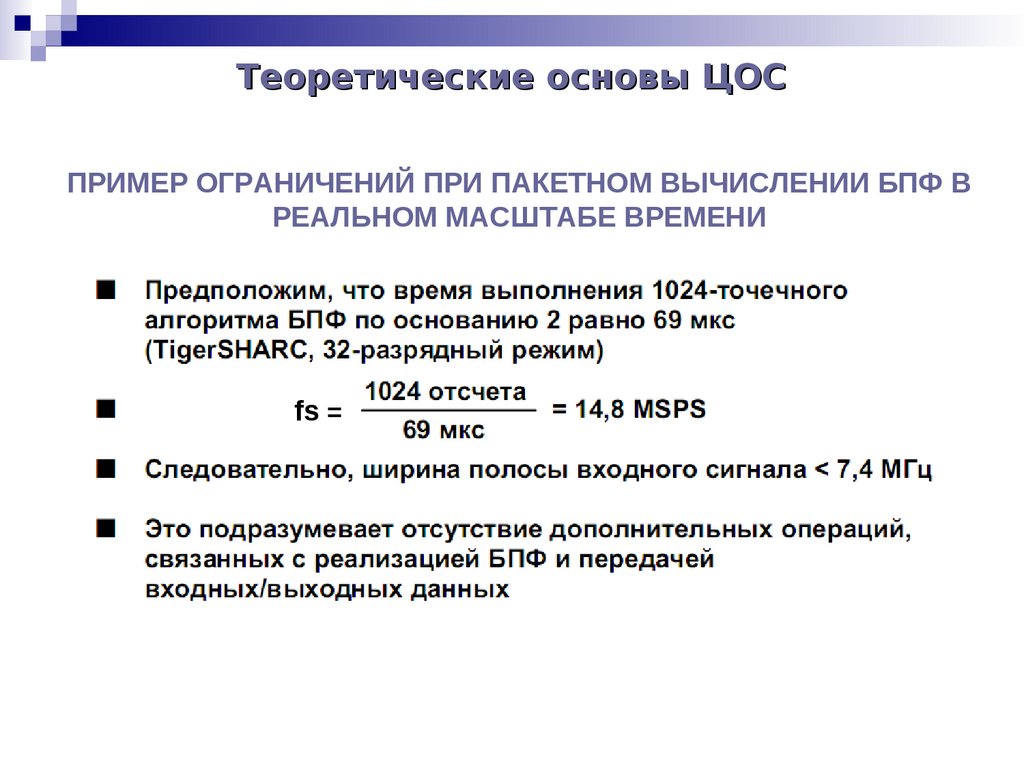

процессор» (Digital Signal Processor, DSP) в учебных материалах

будут использоваться также сокращения «ЛСП» (бел.), «ЦСП» (рус.)

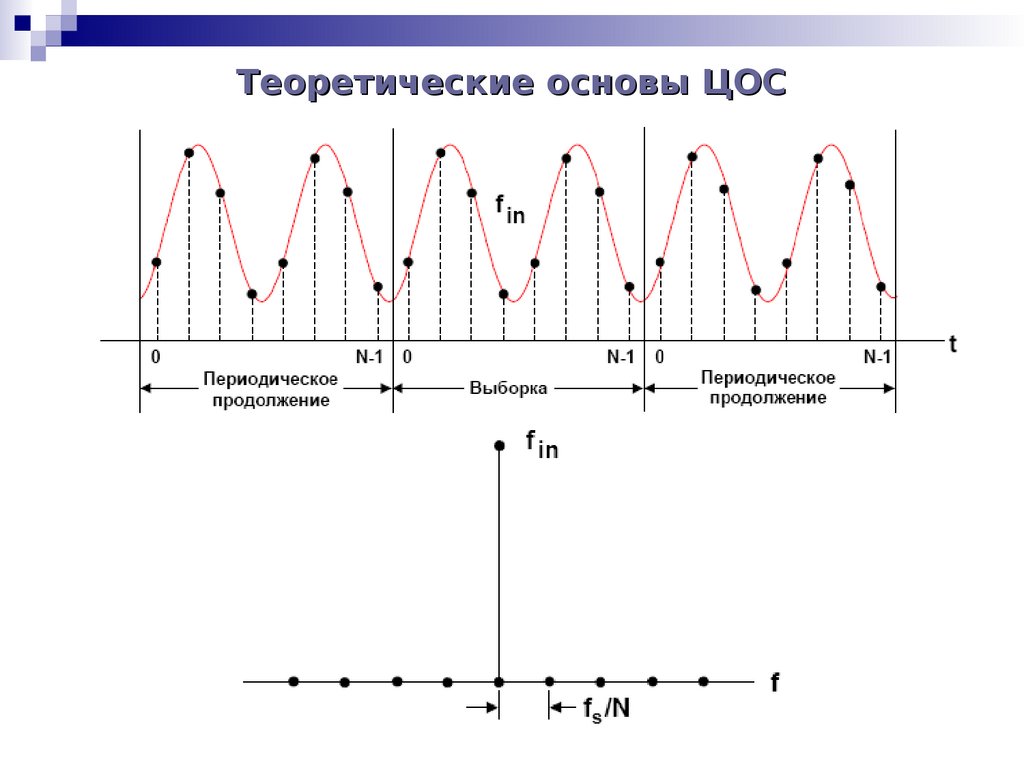

5. Общая классификация микропроцессорных средств

6. Обзор алгоритмов цифровой обработки сигналов

Термин «цифровая обработка сигналов» появился в1960-1970 г.г. Изначально

цифровая обработка сигналов

представляла собой узкую область исследований, основным

назначением

которой

было

моделирование

аналоговых

радиотехнических цепей и сигналов на ЭВМ.

В настоящее время цифровая обработка сигналов (ЦОС) – это

теория и множество практических приложений:

- информационно-измерительная техника;

- автоматика, телемеханика;

- мобильная связь;

- радиолокация;

- радионавигация;

- прикладная геодезия;

- медицина;

и т.д.

Наглядным

примером

практического

использования

достижений теории и техники цифровой обработки сигналов

является сотовый телефон.

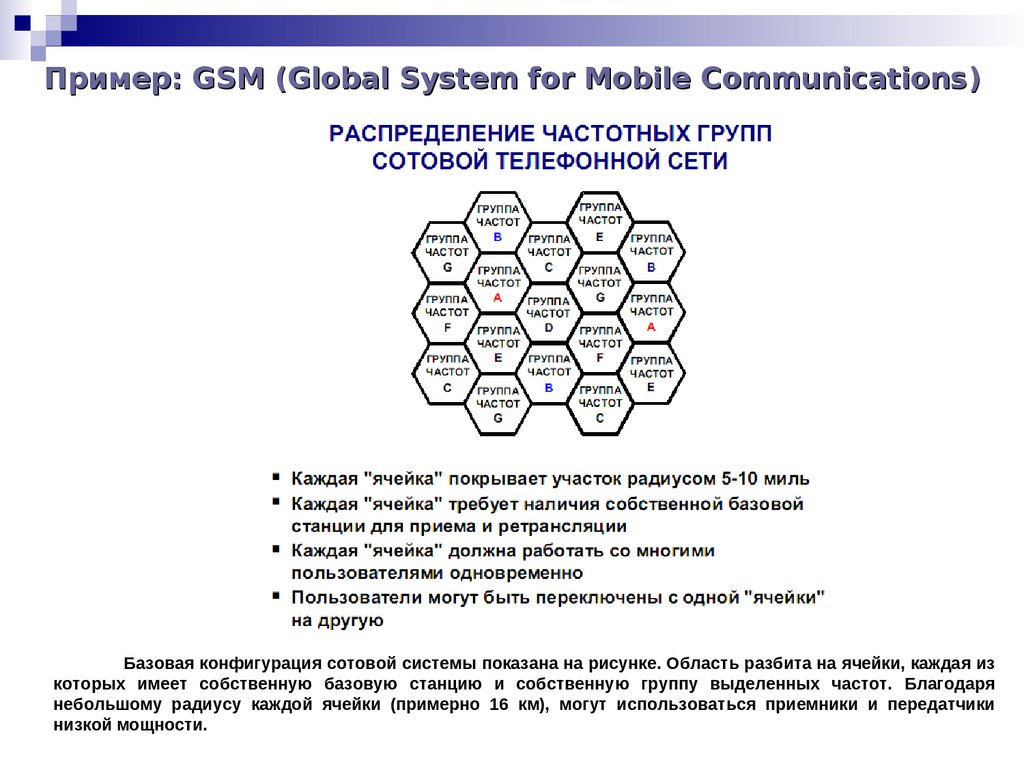

7. Пример: GSM (Global System for Mobile Communications)

Базовая конфигурация сотовой системы показана на рисунке. Область разбита на ячейки, каждая изкоторых имеет собственную базовую станцию и собственную группу выделенных частот. Благодаря

небольшому радиусу каждой ячейки (примерно 16 км), могут использоваться приемники и передатчики

низкой мощности.

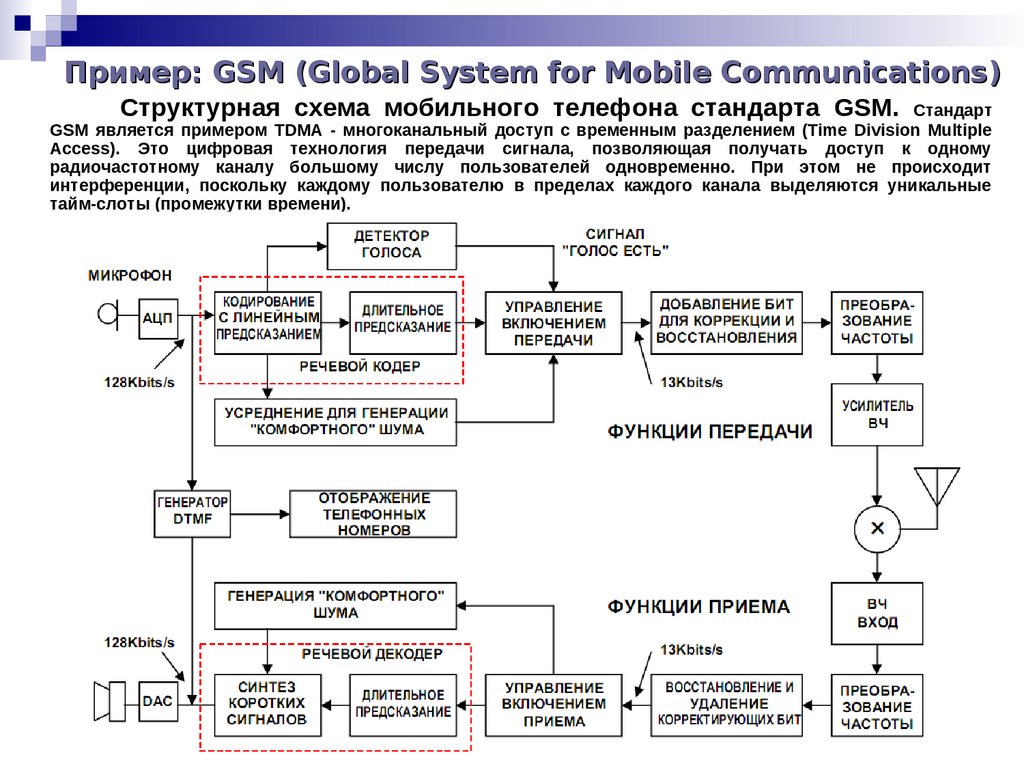

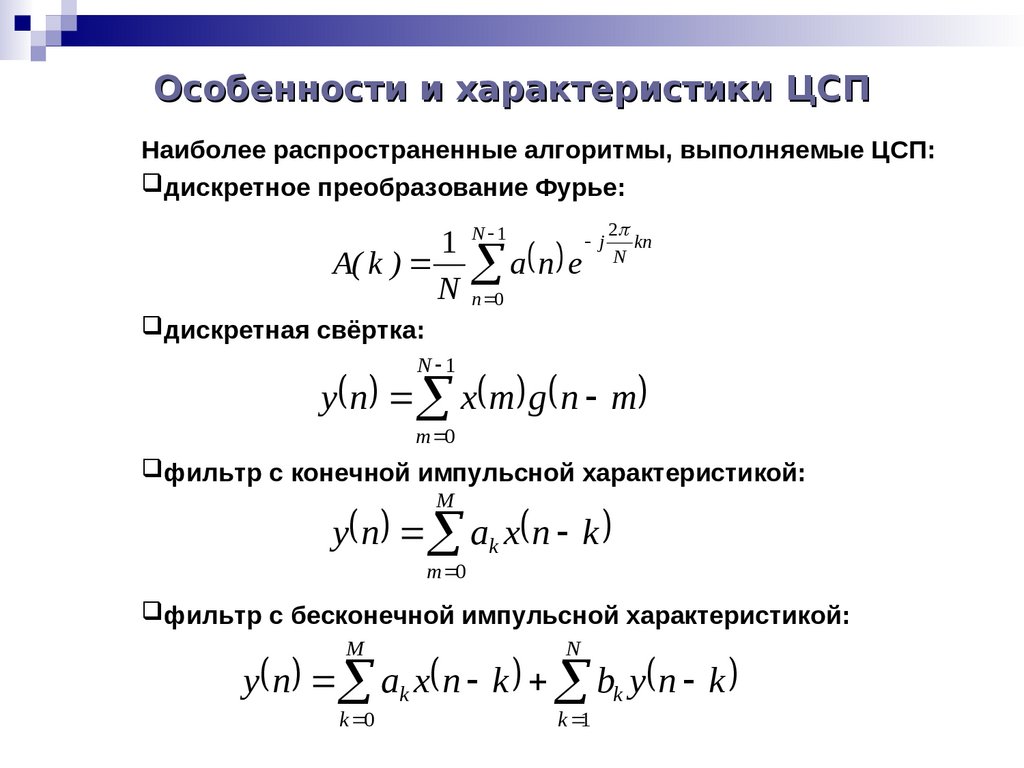

8. Пример: GSM (Global System for Mobile Communications)

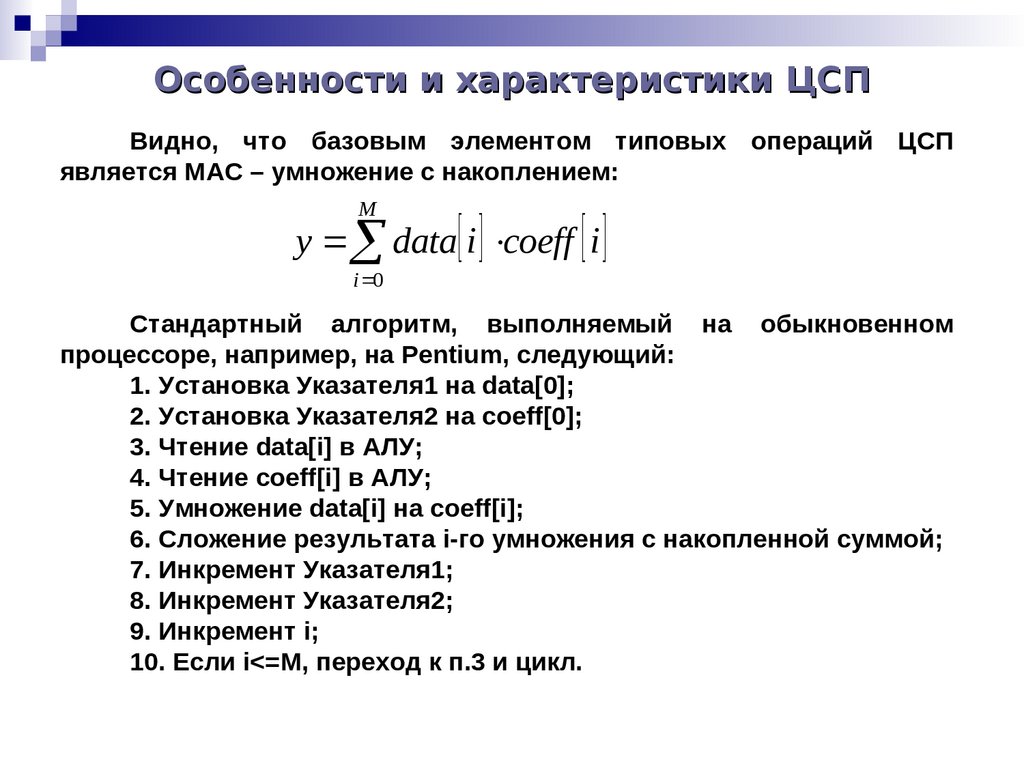

Структурная схема мобильного телефона стандарта GSM. СтандартGSM является примером TDMA - многоканальный доступ с временным разделением (Time Division Multiple

Access). Это цифровая технология передачи сигнала, позволяющая получать доступ к одному

радиочастотному каналу большому числу пользователей одновременно. При этом не происходит

интерференции, поскольку каждому пользователю в пределах каждого канала выделяются уникальные

тайм-слоты (промежутки времени).

9. Пример: GSM (Global System for Mobile Communications)

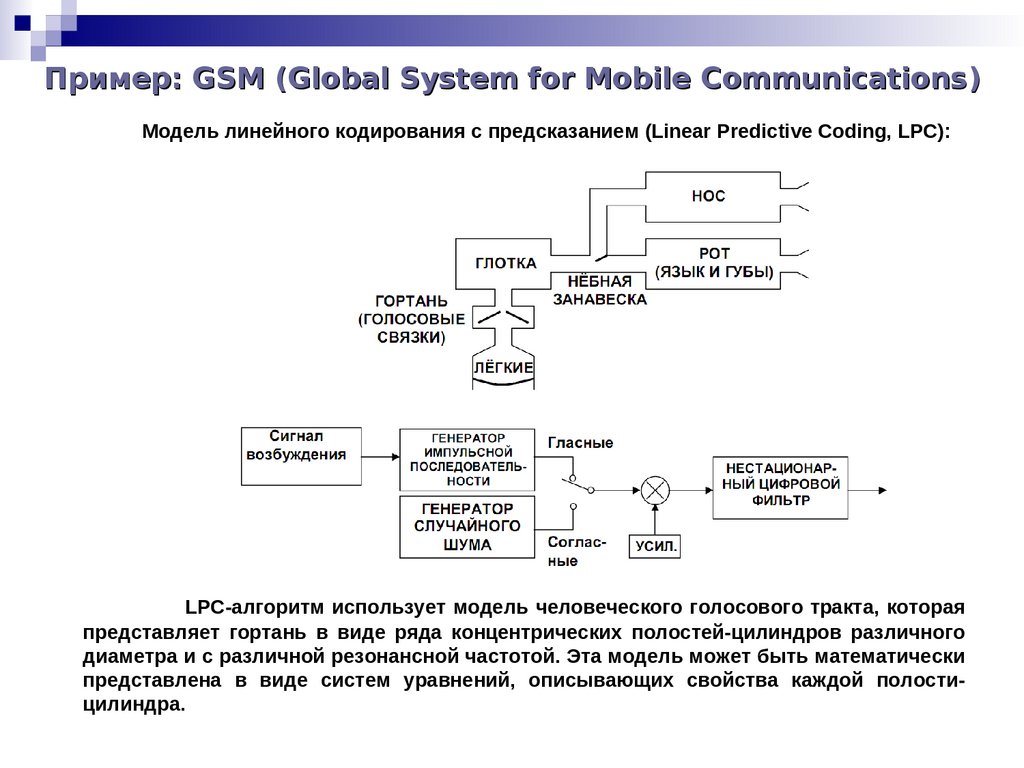

Модель линейного кодирования с предсказанием (Linear Predictive Coding, LPC):LPC-алгоритм использует модель человеческого голосового тракта, которая

представляет гортань в виде ряда концентрических полостей-цилиндров различного

диаметра и с различной резонансной частотой. Эта модель может быть математически

представлена в виде систем уравнений, описывающих свойства каждой полостицилиндра.

10. Пример: GSM (Global System for Mobile Communications)

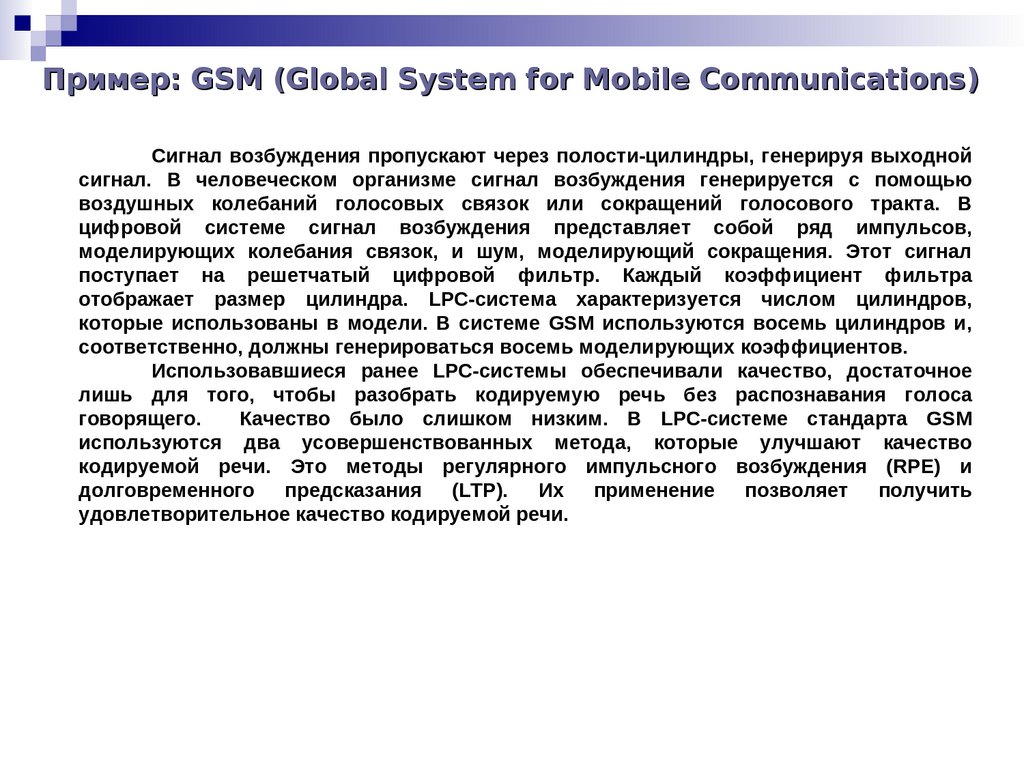

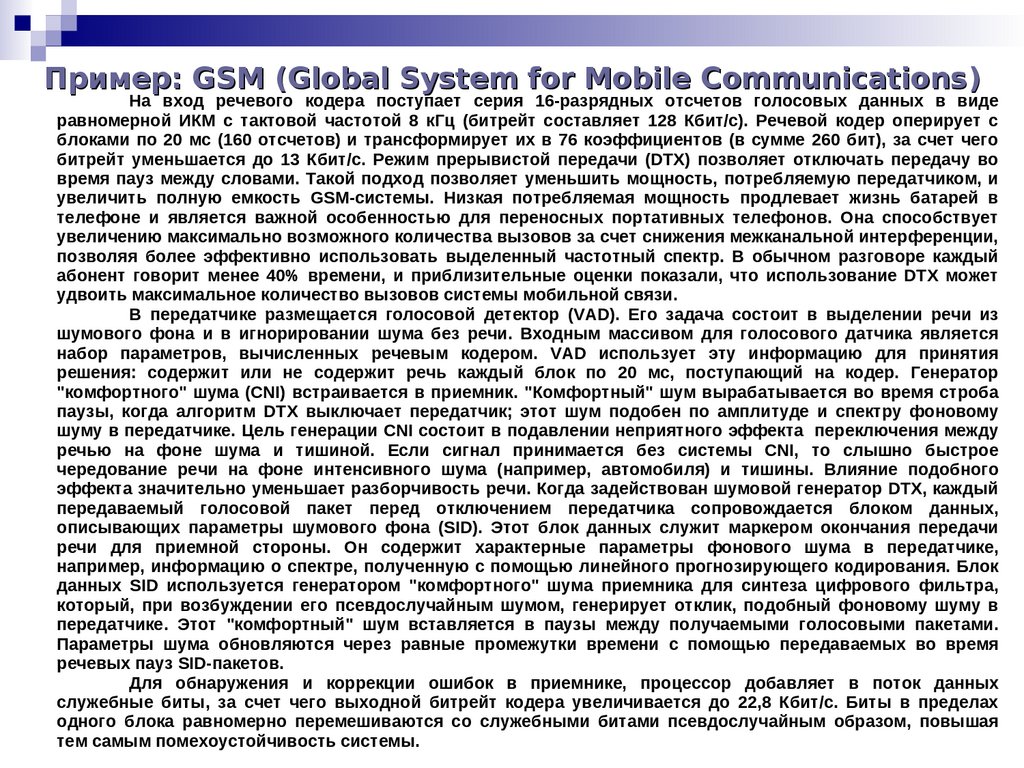

Сигнал возбуждения пропускают через полости-цилиндры, генерируя выходнойсигнал. В человеческом организме сигнал возбуждения генерируется с помощью

воздушных колебаний голосовых связок или сокращений голосового тракта. В

цифровой системе сигнал возбуждения представляет собой ряд импульсов,

моделирующих колебания связок, и шум, моделирующий сокращения. Этот сигнал

поступает на решетчатый цифровой фильтр. Каждый коэффициент фильтра

отображает размер цилиндра. LPC-система характеризуется числом цилиндров,

которые использованы в модели. В системе GSM используются восемь цилиндров и,

соответственно, должны генерироваться восемь моделирующих коэффициентов.

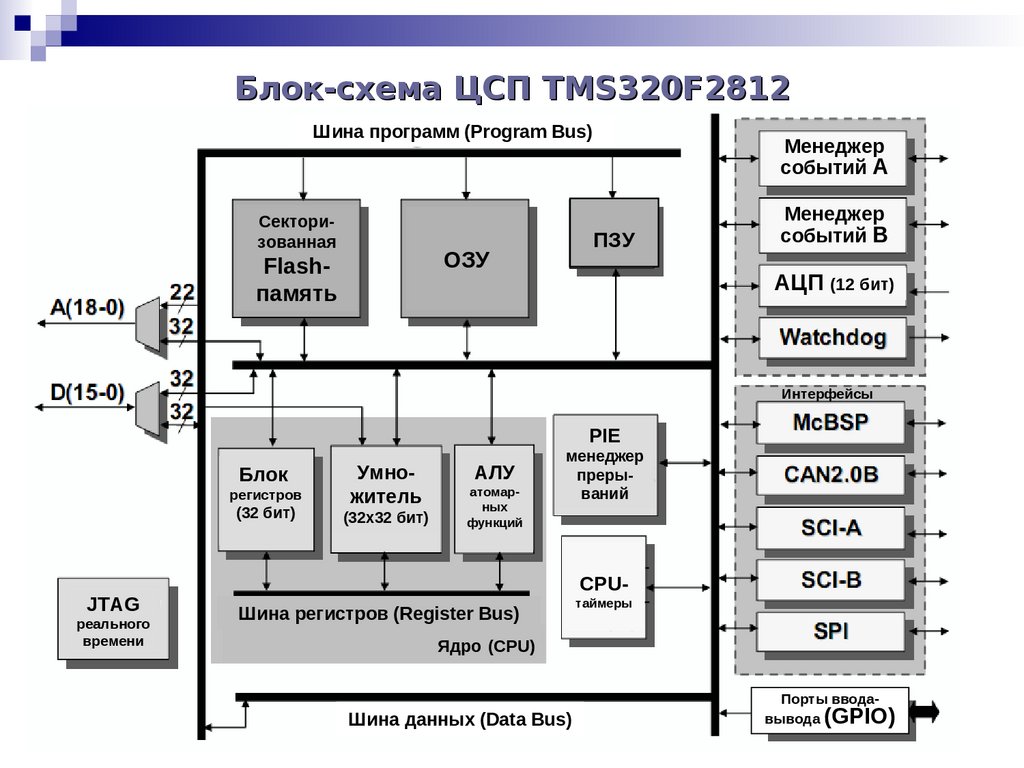

Использовавшиеся ранее LPC-системы обеспечивали качество, достаточное

лишь для того, чтобы разобрать кодируемую речь без распознавания голоса

говорящего.

Качество было слишком низким. В LPC-системе стандарта GSM

используются два усовершенствованных метода, которые улучшают качество

кодируемой речи. Это методы регулярного импульсного возбуждения (RPE) и ) и

долговременного

предсказания

(LTP).

Их

применение

позволяет

получить

удовлетворительное качество кодируемой речи.

11. Пример: GSM (Global System for Mobile Communications)

На вход речевого кодера поступает серия 16-разрядных отсчетов голосовых данных в видеравномерной ИКМ с тактовой частотой 8 кГц (битрейт составляет 128 Кбит/с). Речевой кодер оперирует с

блоками по 20 мс (160 отсчетов) и трансформирует их в 76 коэффициентов (в сумме 260 бит), за счет чего

битрейт уменьшается до 13 Кбит/с. Режим прерывистой передачи (DTX) позволяет отключать передачу во ) позволяет отключать передачу во

время пауз между словами. Такой подход позволяет уменьшить мощность, потребляемую передатчиком, и

увеличить полную емкость GSM-системы. Низкая потребляемая мощность продлевает жизнь батарей в

телефоне и является важной особенностью для переносных портативных телефонов. Она способствует

увеличению максимально возможного количества вызовов за счет снижения межканальной интерференции,

позволяя более эффективно использовать выделенный частотный спектр. В обычном разговоре каждый

абонент говорит менее 40% времени, и приблизительные оценки показали, что использование DTX) позволяет отключать передачу во может

удвоить максимальное количество вызовов системы мобильной связи.

В передатчике размещается голосовой детектор (VAD). Его задача состоит в выделении речи из

шумового фона и в игнорировании шума без речи. Входным массивом для голосового датчика является

набор параметров, вычисленных речевым кодером. VAD использует эту информацию для принятия

решения: содержит или не содержит речь каждый блок по 20 мс, поступающий на кодер. Генератор

"комфортного" шума (CNm) встраивается в приемник. "Комфортный" шум вырабатывается во время строба

паузы, когда алгоритм DTX) позволяет отключать передачу во выключает передатчик; этот шум подобен по амплитуде и спектру фоновому

шуму в передатчике. Цель генерации CNm состоит в подавлении неприятного эффекта переключения между

речью на фоне шума и тишиной. Если сигнал принимается без системы CNm, то слышно быстрое

чередование речи на фоне интенсивного шума (например, автомобиля) и тишины. Влияние подобного

эффекта значительно уменьшает разборчивость речи. Когда задействован шумовой генератор DTX) позволяет отключать передачу во , каждый

передаваемый голосовой пакет перед отключением передатчика сопровождается блоком данных,

описывающих параметры шумового фона (SmD). Этот блок данных служит маркером окончания передачи

речи для приемной стороны. Он содержит характерные параметры фонового шума в передатчике,

например, информацию о спектре, полученную с помощью линейного прогнозирующего кодирования. Блок

данных SmD используется генератором "комфортного" шума приемника для синтеза цифрового фильтра,

который, при возбуждении его псевдослучайным шумом, генерирует отклик, подобный фоновому шуму в

передатчике. Этот "комфортный" шум вставляется в паузы между получаемыми голосовыми пакетами.

Параметры шума обновляются через равные промежутки времени с помощью передаваемых во время

речевых пауз SmD-пакетов.

Для обнаружения и коррекции ошибок в приемнике, процессор добавляет в поток данных

служебные биты, за счет чего выходной битрейт кодера увеличивается до 22,8 Кбит/с. Биты в пределах

одного блока равномерно перемешиваются со служебными битами псевдослучайным образом, повышая

тем самым помехоустойчивость системы.

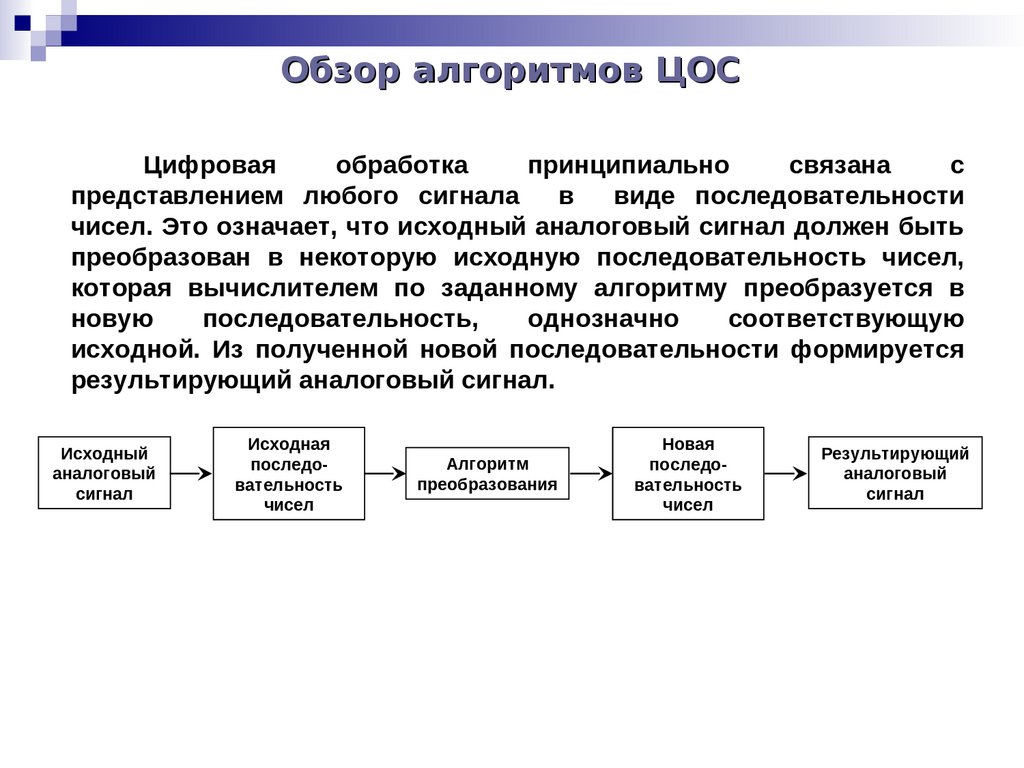

12. Обзор алгоритмов ЦОС

Цифроваяобработка

принципиально

связана

с

представлением любого сигнала

в

виде последовательности

чисел. Это означает, что исходный аналоговый сигнал должен быть

преобразован в некоторую исходную последовательность чисел,

которая вычислителем по заданному алгоритму преобразуется в

новую

последовательность,

однозначно

соответствующую

исходной. Из полученной новой последовательности формируется

результирующий аналоговый сигнал.

Исходный

аналоговый

сигнал

Исходная

последовательность

чисел

Алгоритм

преобразования

Новая

последовательность

чисел

Результирующий

аналоговый

сигнал

13. Обзор алгоритмов ЦОС

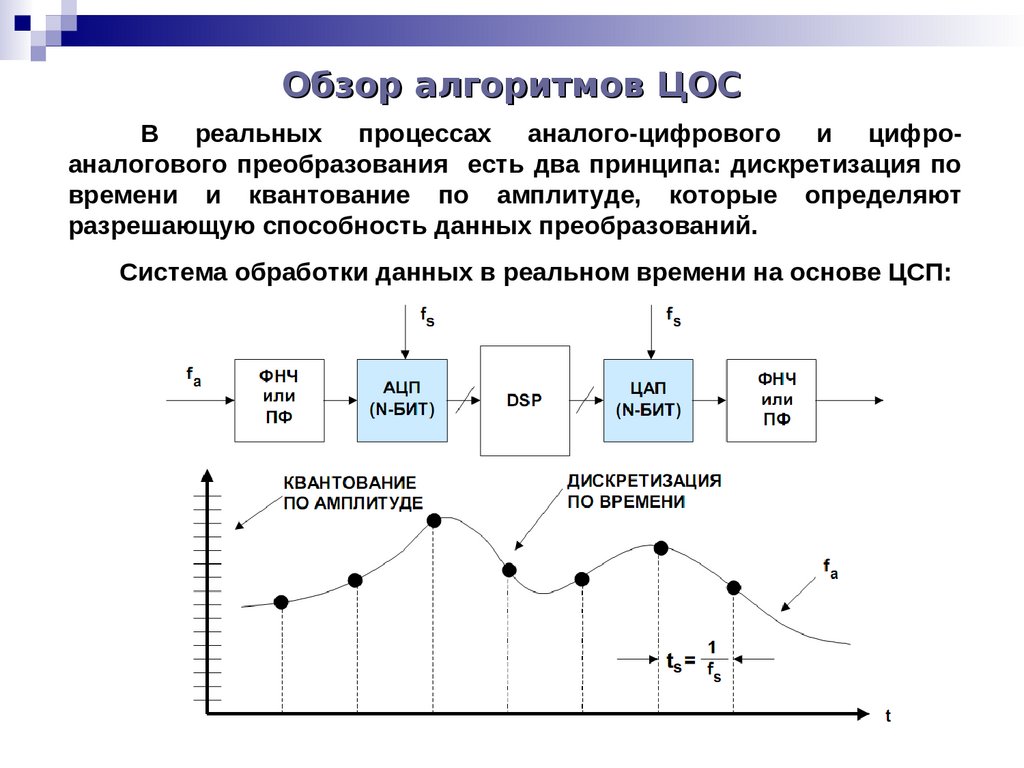

В реальных процессах аналого-цифрового и цифроаналогового преобразования есть два принципа: дискретизация повремени и квантование по амплитуде, которые определяют

разрешающую способность данных преобразований.

Система обработки данных в реальном времени на основе ЦСП:

14. Обзор алгоритмов ЦОС

Выборканепрерывных

аналоговых

данных

должна

осуществляться

через

интервал

дискретизации,

который

необходимо правильно выбирать для точного представления

первоначального аналогового сигнала. Чем больше число отсчетов

(более высокие частоты дискретизации), тем более точным будет

представление сигнала в цифровом виде. В случае малого числа

отсчетов может быть достигнуто критическое значение частоты

дискретизации, при котором теряется информация о сигнале. Это

следует

из

известной

теоремы

Котельникова:

частота

дискретизации fs сигнала должна быть по крайней мере в 2 раза

больше, чем наивысшая частота fM спектра сигнала:

fM ≤ fs/2

В зарубежной литературе данное соотношение часто называют

критерием Найквиста.

15. Обзор алгоритмов ЦОС

Аналого-цифровое преобразование осуществляется в двестадии.

Первая стадия – селективная задержка, где полученная

информация

–

мгновенное

значение

сигнала

в

момент

осуществления выборки. Обычно реализуется на устройстве

выборки-хранения.

Вторая стадия – N-разрядный АЦП преобразовывает

мгновенное значение напряжения в самое близкое целое число из 2N

возможных, что ведет к ошибке в каждой выборке на ±1/2 LSB (Least

Significant Bit – наименьший значащий бит). В итоге цифровой

выходной сигнал является эквивалентным непрерывному входному

сигналу плюс ошибка квантования, которая выступает в виде

добавленного к сигналу шума.

16. Обзор алгоритмов ЦОС

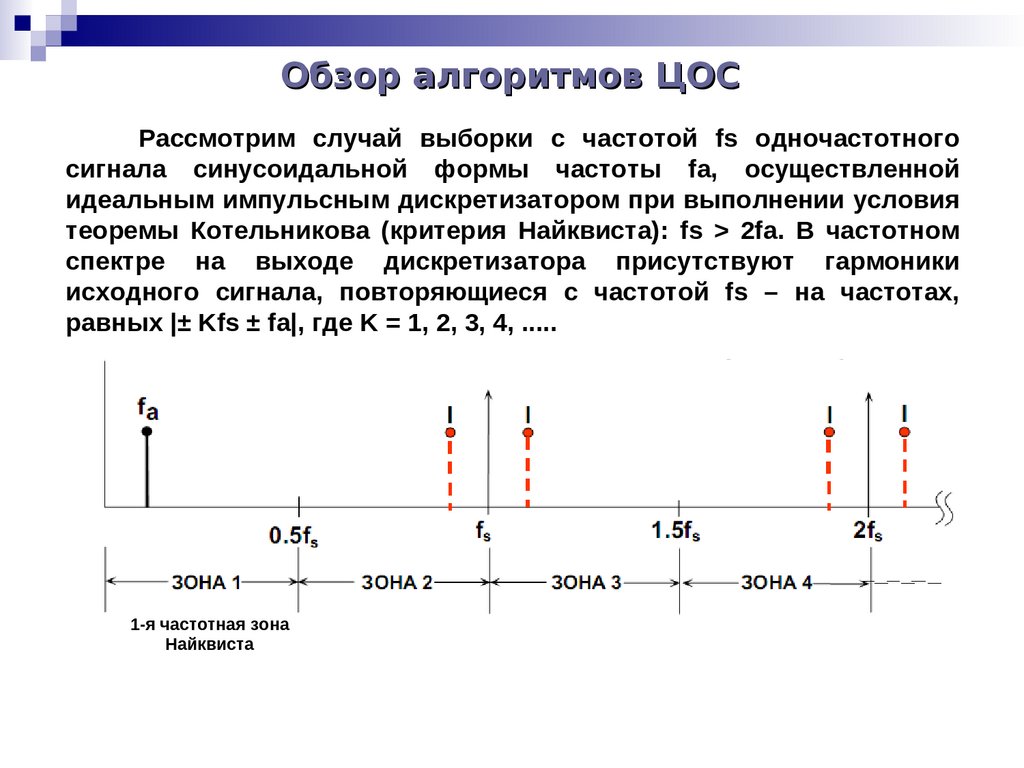

Рассмотрим случай выборки с частотой fs одночастотногосигнала синусоидальной формы частоты fa, осуществленной

идеальным импульсным дискретизатором при выполнении условия

теоремы Котельникова (критерия Найквиста): fs > 2fa. В частотном

спектре на выходе дискретизатора присутствуют гармоники

исходного сигнала, повторяющиеся с частотой fs – на частотах,

равных |± Kfs ± fa|, где K = 1, 2, 3, 4, .....

1-я частотная зона

Найквиста

17. Обзор алгоритмов ЦОС

Частотная зона Найквиста определяется как полоса спектра от0 до fs/2. Частотный спектр разделен на бесконечное число зон

Найквиста, каждая протяженностью по 0,5fs. На практике идеальный

дискретизатор заменяется на АЦП, используемый совместно с ЦСП.

Для работы ЦСП необходимо присутствие на входе только

компонент сигналов, частоты которых попадают в первую зону

Найквиста, то есть, в полосу от 0 до fs/2.

18. Обзор алгоритмов ЦОС

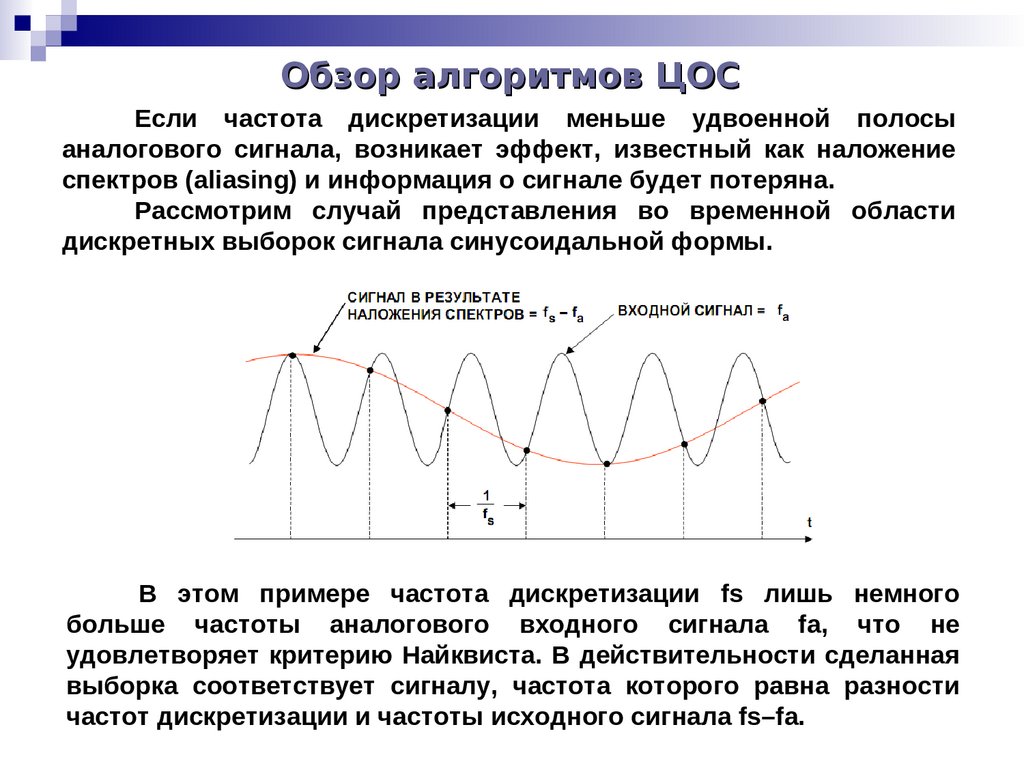

Если частота дискретизации меньше удвоенной полосыаналогового сигнала, возникает эффект, известный как наложение

спектров (aliasing) и информация о сигнале будет потеряна.

Рассмотрим случай представления во временной области

дискретных выборок сигнала синусоидальной формы.

В этом примере частота дискретизации fs лишь немного

больше частоты аналогового входного сигнала fa, что не

удовлетворяет критерию Найквиста. В действительности сделанная

выборка соответствует сигналу, частота которого равна разности

частот дискретизации и частоты исходного сигнала fs–fa.

19. Обзор алгоритмов ЦОС

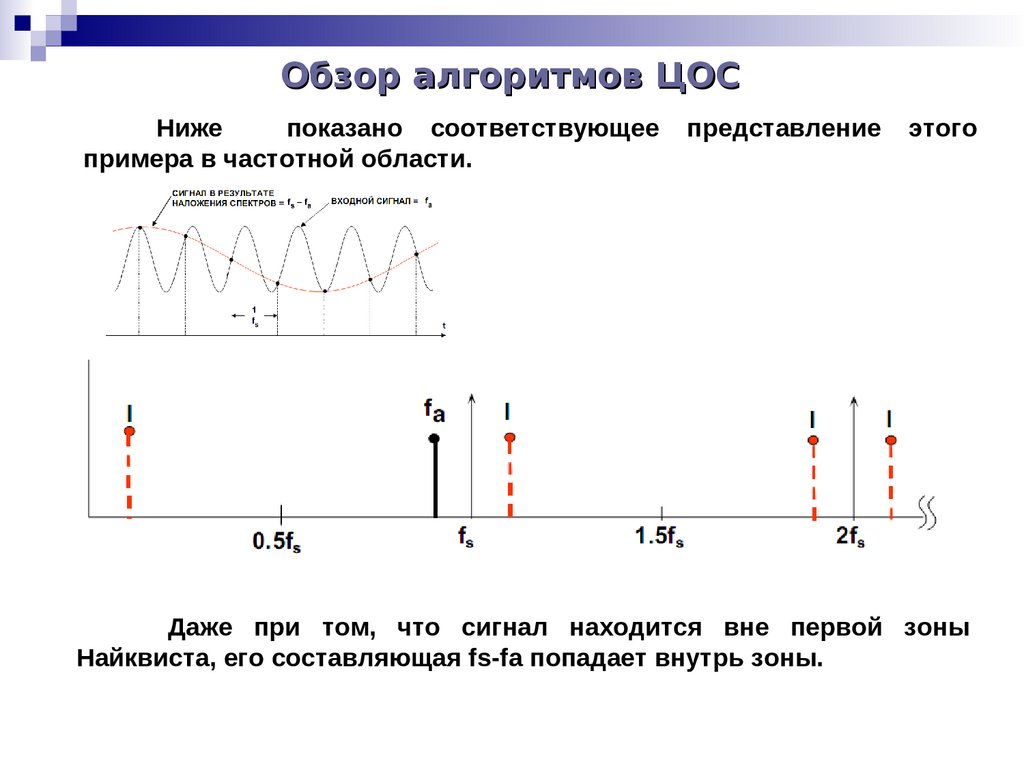

Нижепоказано соответствующее

примера в частотной области.

представление

этого

Даже при том, что сигнал находится вне первой зоны

Найквиста, его составляющая fs-fa попадает внутрь зоны.

20. Обзор алгоритмов ЦОС

Подразумевается, что перед дискретизатором (или АЦП)осуществляется аналоговая фильтрация, подавляющая гармоники,

частоты которых находятся вне полосы Найквиста и после

дискретизации попадают в ее пределы. Рабочая характеристика

фильтра будет зависеть от того, как близко частота внеполосного

сигнала отстоит от fs/2, а также будет определяться величиной

требуемого подавления.

Подлежащий дискретизации сигнал лежит в 1-й частотной зоне

Найквиста. Без фильтрации на входе идеального дискретизатора

любой частотный компонент (сигнал или шум), который находится за

пределами «полосы Найквиста» (т.е. в любой следующей зоне

Найквиста), будет создавать НЧ-составляющую в первой зоне

Найквиста. По этой причине ФНЧ используется почти со всеми АЦП

для подавления нежелательных сигналов.

21. Обзор алгоритмов ЦОС

В случае, когда наивысшая из интересующих нас частот равнаfa, фильтр пропускает сигналы, лежащие в полосе частот от 0 до fa,

тогда как сигналы с частотой выше fa ослабляются.

Если ширина полосы частот сигнала известна, минимальная

требуемая частота дискретизации может быть определена путем ее

умножения

на

коэффициент

2,1-2,5.

Увеличение

частоты

дискретизации снижает требования к предшествующему АЦП ФНЧ,

устраняющему эффект наложения спектра (antialiasing filter).

22. Пример: реализация FIR-фильтра на ЦСП

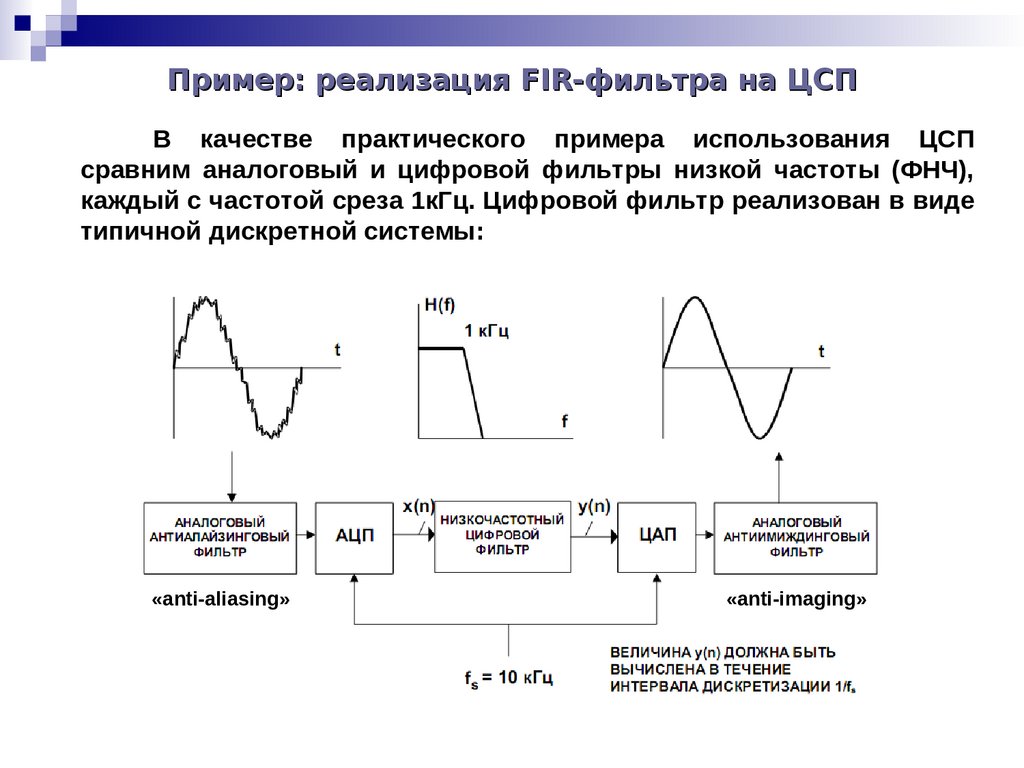

В качестве практического примера использования ЦСПсравним аналоговый и цифровой фильтры низкой частоты (ФНЧ),

каждый с частотой среза 1кГц. Цифровой фильтр реализован в виде

типичной дискретной системы:

«anti-aliasing»

«anti-imaging»

23. Пример: реализация FIR-фильтра на ЦСП

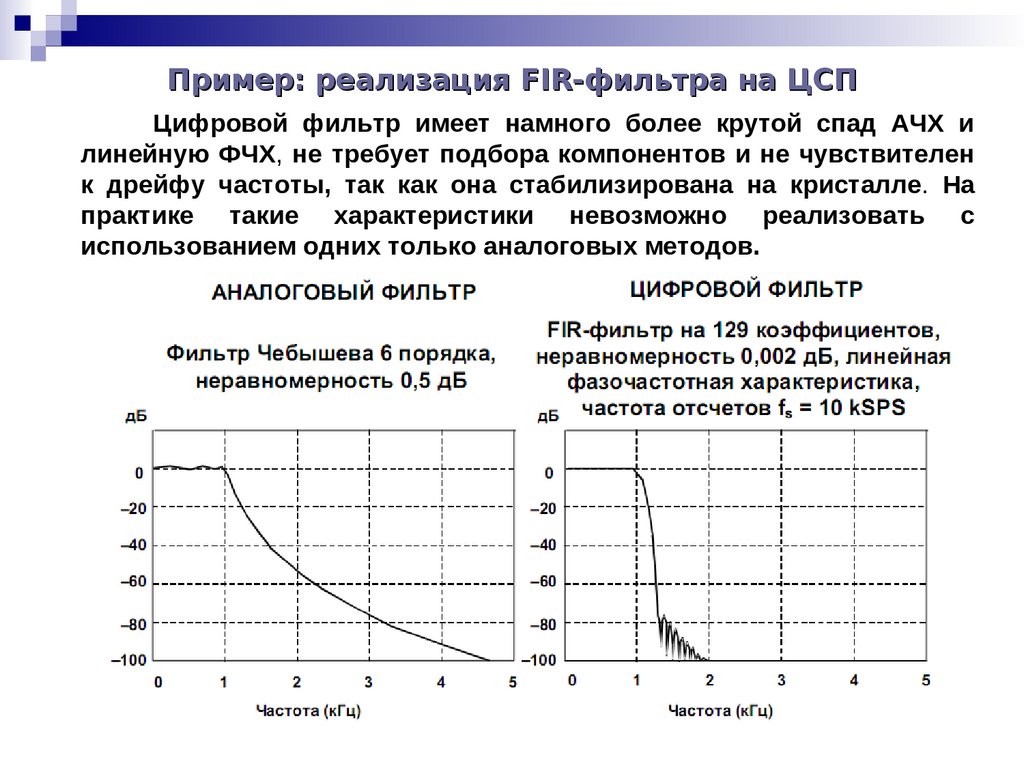

Цифровой фильтр имеет намного более крутой спад АЧХ илинейную ФЧХ, не требует подбора компонентов и не чувствителен

к дрейфу частоты, так как она стабилизирована на кристалле. На

практике такие характеристики невозможно реализовать с

использованием одних только аналоговых методов.

24. Обзор цифровой и аналоговой аппаратуры ЦОС

В настоящее время при решении задач обработкиизмерительных сигналов важно выбрать оптимальную комбинацию

аналоговых и цифровых методов. Невозможно обработать

физические аналоговые сигналы, используя только цифровые

методы, так как большинство первичных датчиков (микрофоны,

термопары,

тензорезисторы,

пьезоэлектрические

кристаллы,

головки накопителя на магнитных дисках и т.д.) являются

аналоговыми устройствами.

Большинство видов сигналов требуют наличия цепей

нормализации для дальнейшей обработки сигналов аналоговым или

цифровым методом.

Аналоговые цепи нормализации сигнала выполняют

следующие функции:

-усиления сигнала;

-запоминания и хранения сигнала;

-обнаружения сигнала на фоне шума;

-сжатия динамического диапазона;

-фильтрации;

-прочие (в зависимости от конкретной задачи).

25. Обзор цифровой и аналоговой аппаратуры ЦОС

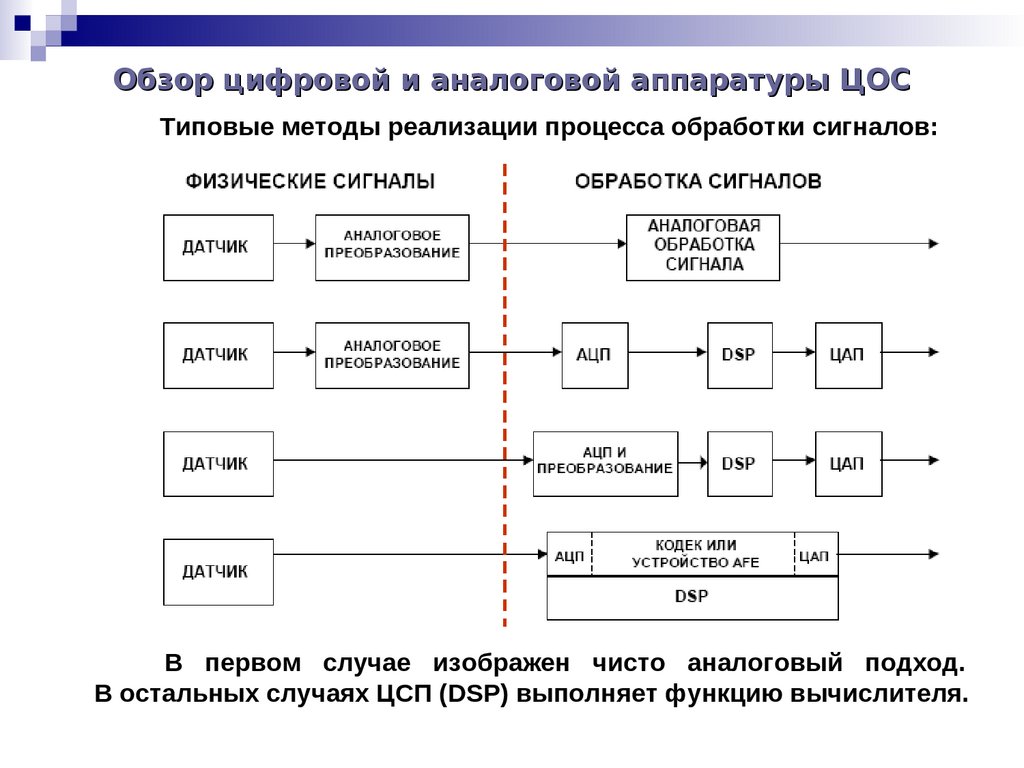

Типовые методы реализации процесса обработки сигналов:В первом случае изображен чисто аналоговый подход.

В остальных случаях ЦСП (DSP) выполняет функцию вычислителя.

26. Обзор цифровой и аналоговой аппаратуры ЦОС

В общем случае на месте DSP может находиться любойэлемент-вычислитель. Цифровая обработка сигнала в вычислителе

может выполняться на основе разнообразной элементной базы.

Вычислитель может быть реализован аппаратным способом

(устройство с жесткой логикой) и программным методом.

Элементная база включает различные непрограммируемые

(работающие не под управлением программы) и программируемые

устройства. К непрограммируемым элементам относятся:

интегральные схемы ASIC (Application Specific Integrated

Circuits – специализированные или проблемно-ориентированные

интегральные схемы),

CPLD

(Complex

Programmable

Logic

программируемые логические интегральные схемы),

Devices

–

FPGA (Field Programmable Gate Arrays – программируемые

вентильные матрицы);

FPAA (Field Programmable Analog Arrays – программируемые

аналоговые интегральные схемы).

27. Обзор цифровой и аналоговой аппаратуры ЦОС

Программируемымиэлементами

являются

микроконтроллеры, универсальные процессоры общего назначения

разного типа (RISC и CISC) и ЦСП.

Следует отметить, что устройства типа CPLD, FPGA, FPAA,

строго говоря, так же «программируются» с использованием

специальных

инструментальных

средств

разработки

для

реализации ими определенной функции. В результате получается

некоторая специализированная интегральная схема, которая может

выполнять функции в объеме от узла цифровой электроники (CPLD)

или простейшего фильтра (FPAA) до нескольких процессорных ядер

(FPGA) или сложнейших уникальных схем обработки аналоговых

сигналов (FPAA).

Лидерами в производстве PLD и FPGA являются компании

Altera и X) позволяет отключать передачу во ilinx, лидером в производстве FPAA является компания

Anadigm.

28. Обзор цифровой и аналоговой аппаратуры ЦОС

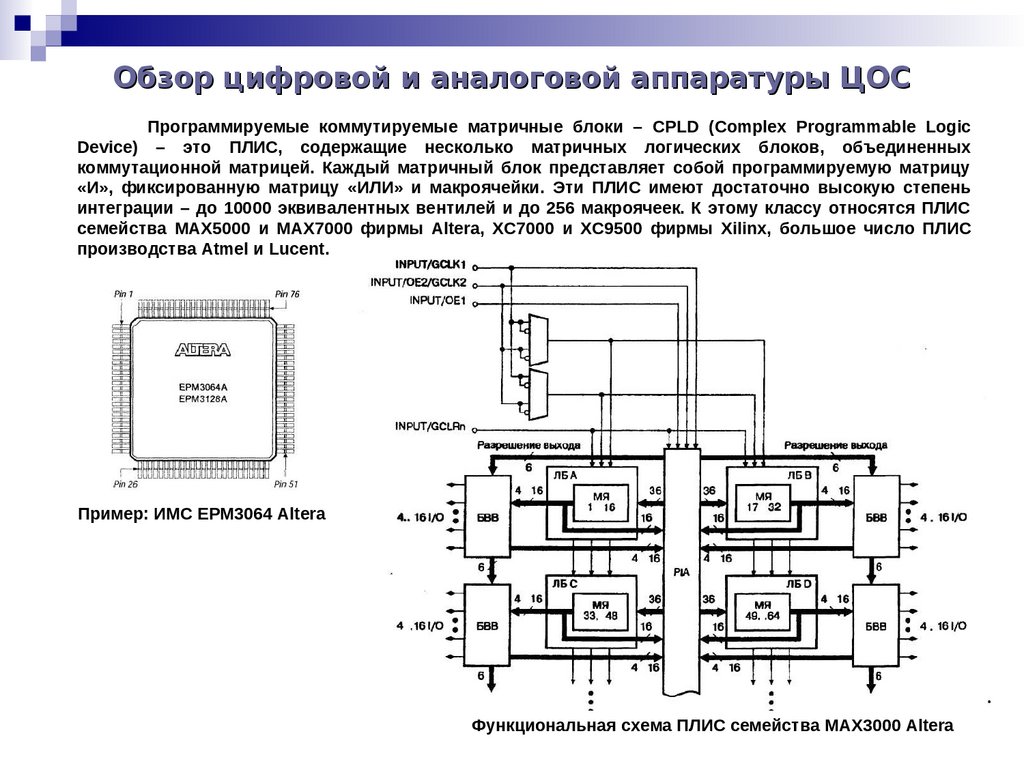

Программируемые коммутируемые матричные блоки – CPLD (Complex Programmable LogicDevice) – это ПЛИС, содержащие несколько матричных логических блоков, объединенных

коммутационной матрицей. Каждый матричный блок представляет собой программируемую матрицу

«И», фиксированную матрицу «ИЛИ» и макроячейки. Эти ПЛИС имеют достаточно высокую степень

интеграции – до 10000 эквивалентных вентилей и до 256 макроячеек. К этому классу относятся ПЛИС

семейства MAX) позволяет отключать передачу во 5000 и MAX) позволяет отключать передачу во 7000 фирмы Altera, X) позволяет отключать передачу во C7000 и X) позволяет отключать передачу во C9500 фирмы X) позволяет отключать передачу во ilinx, большое число ПЛИС

производства Atmel и Lucent.

Пример: ИМС E) и PM3064 Altera

Функциональная схема ПЛИС семейства MAX) позволяет отключать передачу во 3000 Altera

29. Обзор цифровой и аналоговой аппаратуры ЦОС

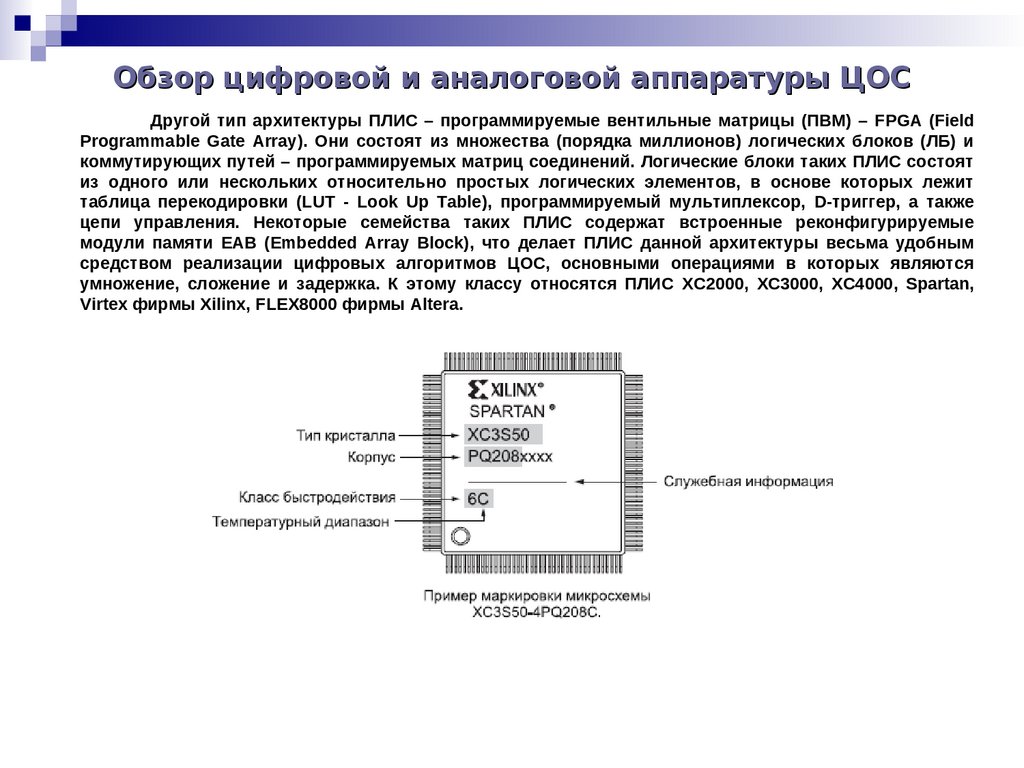

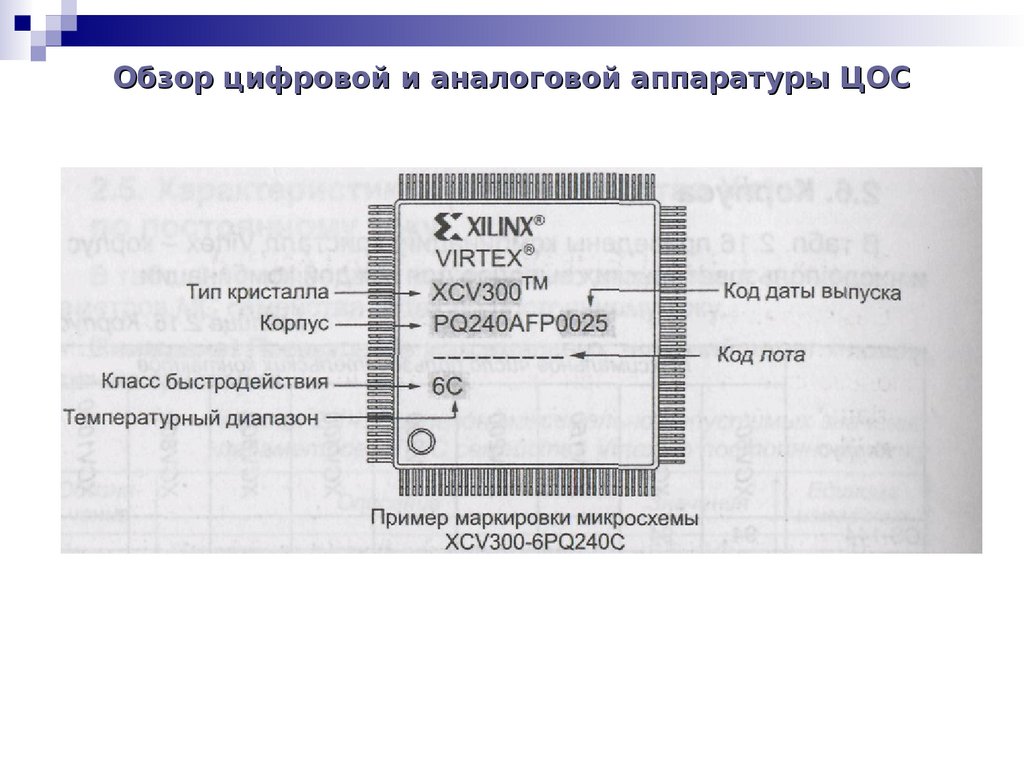

Другой тип архитектуры ПЛИС – программируемые вентильные матрицы (ПВМ) – FPGA (FieldProgrammable Gate Array). Они состоят из множества (порядка миллионов) логических блоков (ЛБ) и

коммутирующих путей – программируемых матриц соединений. Логические блоки таких ПЛИС состоят

из одного или нескольких относительно простых логических элементов, в основе которых лежит

таблица перекодировки (LUT - Look Up Table), программируемый мультиплексор, D-триггер, а также

цепи управления. Некоторые семейства таких ПЛИС содержат встроенные реконфигурируемые

модули памяти E) и AB (E) и mbedded Array Block), что делает ПЛИС данной архитектуры весьма удобным

средством реализации цифровых алгоритмов ЦОС, основными операциями в которых являются

умножение, сложение и задержка. К этому классу относятся ПЛИС X) позволяет отключать передачу во C2000, X) позволяет отключать передачу во C3000, X) позволяет отключать передачу во C4000, Spartan,

Virtex фирмы X) позволяет отключать передачу во ilinx, FLE) и X) позволяет отключать передачу во 8000 фирмы Altera.

30. Обзор цифровой и аналоговой аппаратуры ЦОС

Архитектура ПЛИС семейства Spartan-3 содержит 5 фундаментальных программируемыхэлементов:

1. Конфигурируемый Логический Блок – КЛБ. На базе КЛБ реализуется комбинаторная и синхронная

логика, включая базовые запоминающие элементы.

2. Блок ввода-вывода – БВВ. БВВ осуществляют коммутацию выводов корпуса микросхемы с

внутренней конфигурируемой логикой. БВВ поддерживают большинство сигнальных стандартов

ввода-вывода, существующих в настоящее время.

3. Блок памяти. Каждый блок может конфигурироваться как двухпортовое ОЗУ ёмкостью 18 кбит.

4. Блок умножителя. Встроенный умножитель 18x18 бит.

5. Цифровой блок управления синхронизацией – DCM (Digital Clock Manager).

31. Обзор цифровой и аналоговой аппаратуры ЦОС

32. Обзор цифровой и аналоговой аппаратуры ЦОС

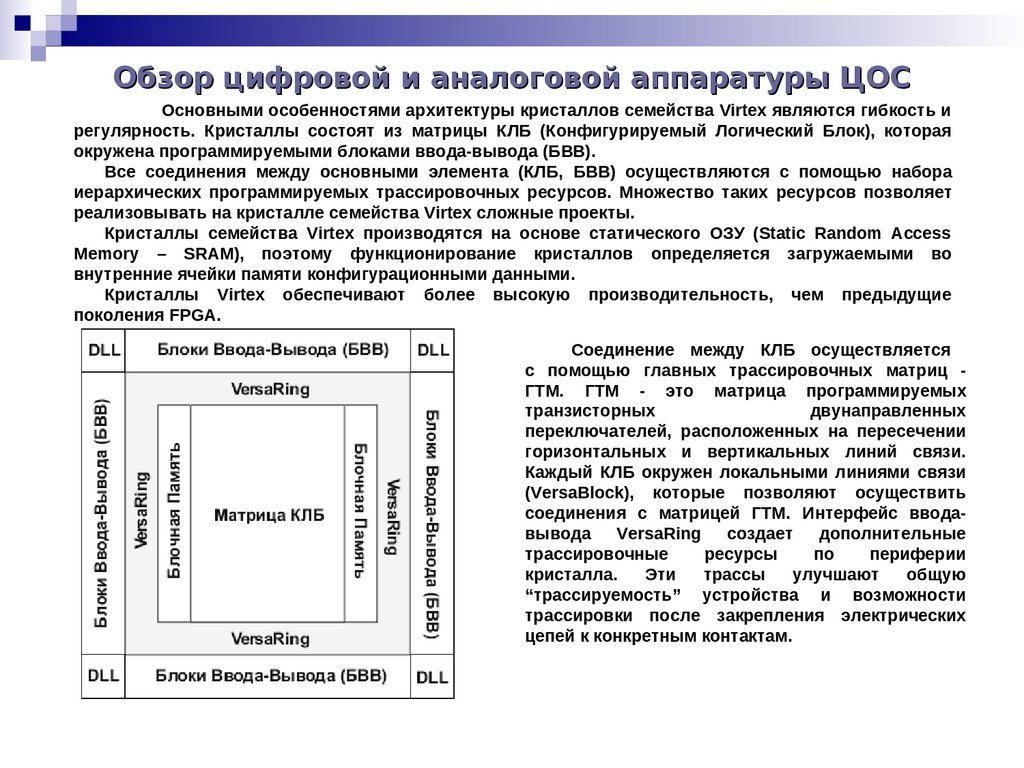

Основными особенностями архитектуры кристаллов семейства Virtex являются гибкость ирегулярность. Кристаллы состоят из матрицы КЛБ (Конфигурируемый Логический Блок), которая

окружена программируемыми блоками ввода-вывода (БВВ).

Все соединения между основными элемента (КЛБ, БВВ) осуществляются с помощью набора

иерархических программируемых трассировочных ресурсов. Множество таких ресурсов позволяет

реализовывать на кристалле семейства Virtex сложные проекты.

Кристаллы семейства Virtex производятся на основе статического ОЗУ (Static Random Access

Memory – SRAM), поэтому функционирование кристаллов определяется загружаемыми во

внутренние ячейки памяти конфигурационными данными.

Кристаллы Virtex обеспечивают более высокую производительность, чем предыдущие

поколения FPGA.

Соединение между КЛБ осуществляется

с помощью главных трассировочных матриц ГТМ. ГТМ - это матрица программируемых

транзисторных

двунаправленных

переключателей, расположенных на пересечении

горизонтальных и вертикальных линий связи.

Каждый КЛБ окружен локальными линиями связи

(VersaBlock), которые позволяют осуществить

соединения с матрицей ГТМ. Интерфейс вводавывода

VersaRing

создает

дополнительные

трассировочные

ресурсы

по

периферии

кристалла.

Эти

трассы

улучшают

общую

“трассируемость” устройства и возможности

трассировки после закрепления электрических

цепей к конкретным контактам.

33. Обзор цифровой и аналоговой аппаратуры ЦОС

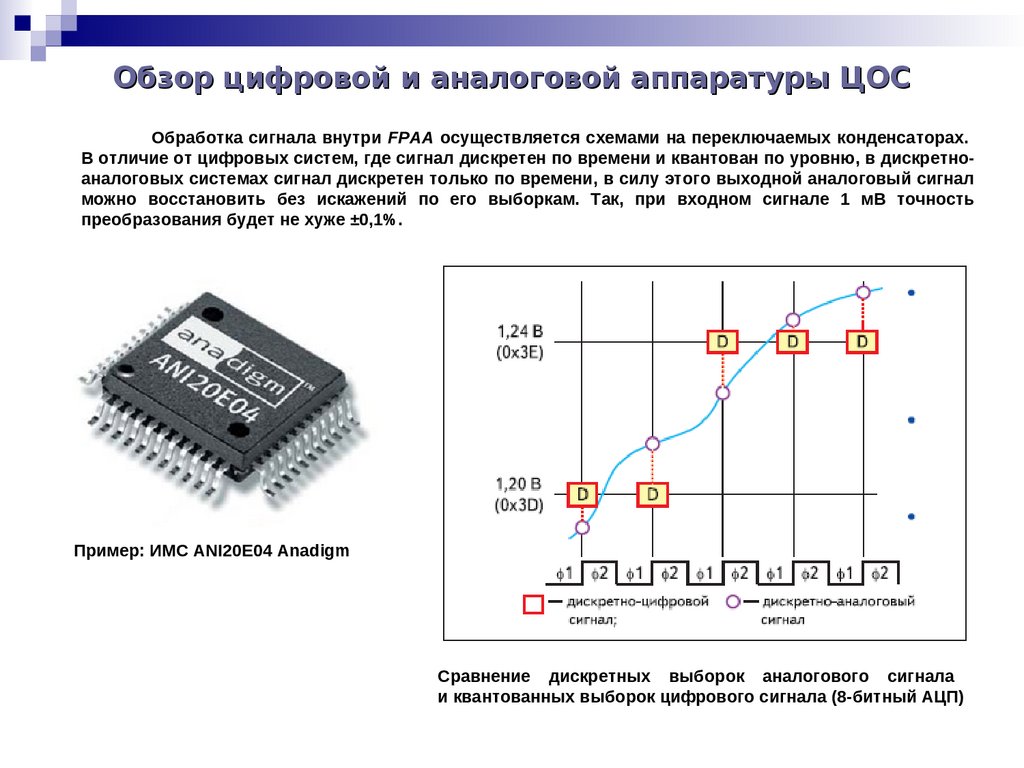

Обработка сигнала внутри FPAA осуществляется схемами на переключаемых конденсаторах.В отличие от цифровых систем, где сигнал дискретен по времени и квантован по уровню, в дискретноаналоговых системах сигнал дискретен только по времени, в силу этого выходной аналоговый сигнал

можно восстановить без искажений по его выборкам. Так, при входном сигнале 1 мВ точность

преобразования будет не хуже ±0,1%.

Пример: ИМС ANm20E) и 04 Anadigm

Сравнение дискретных выборок аналогового сигнала

и квантованных выборок цифрового сигнала (8-битный АЦП)

34. Обзор цифровой и аналоговой аппаратуры ЦОС

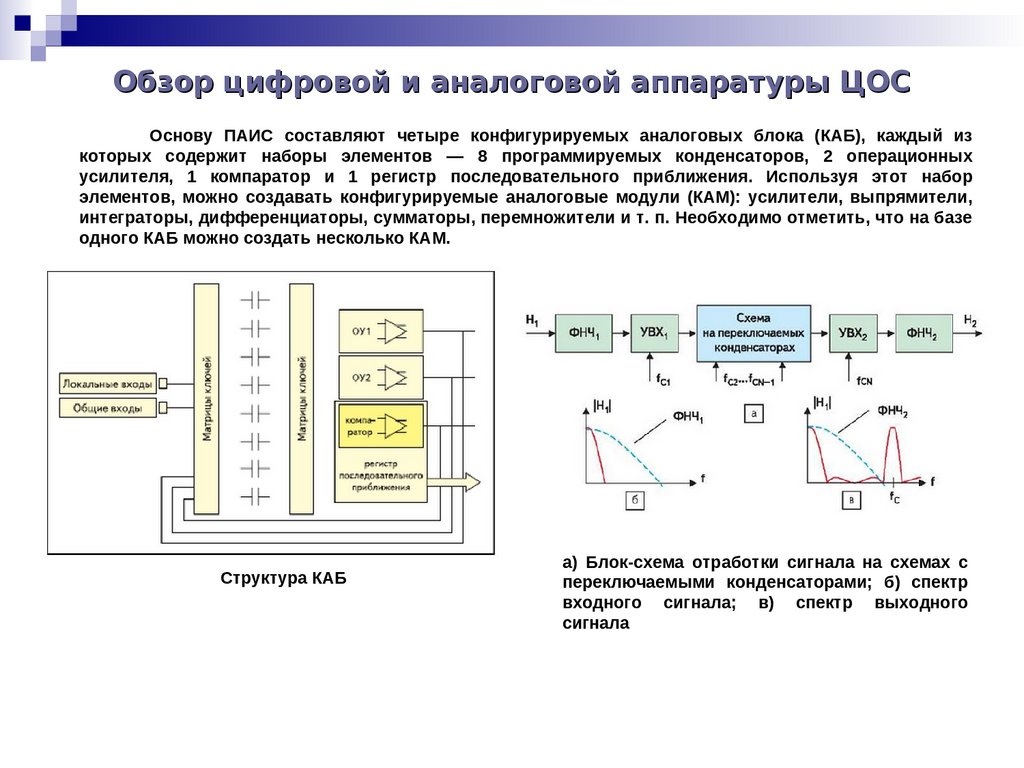

Основу ПАИС составляют четыре конфигурируемых аналоговых блока (КАБ), каждый изкоторых содержит наборы элементов — 8 программируемых конденсаторов, 2 операционных

усилителя, 1 компаратор и 1 регистр последовательного приближения. Используя этот набор

элементов, можно создавать конфигурируемые аналоговые модули (КАМ): усилители, выпрямители,

интеграторы, дифференциаторы, сумматоры, перемножители и т. п. Необходимо отметить, что на базе

одного КАБ можно создать несколько КАМ.

Структура КАБ

а) Блок-схема отработки сигнала на схемах с

переключаемыми конденсаторами; б) спектр

входного сигнала; в) спектр выходного

сигнала

35. Основные направления ЦОС

В настоящеенаправления ЦОС:

время

выделяют

линейная фильтрация;

спектральный анализ;

частотно-временной анализ;

адаптивная фильтрация;

нелинейная обработка;

многоскоростная обработка.

следующие

основные

36. Основные цели цифровой обработки сигналов

- Извлечение информации о сигнале (амплитуда, фаза, частота,спектральные составляющие, временные соотношения)

- Преобразование формата сигнала (телефония с разделением

каналов)

- Сжатие данных (модемы, сотовые телефоны, цифровое

телевидение, сжатие MPE) и G)

- Формирование сигналов обратной связи (управление

сложными промышленными процессами)

- Выделение сигнала из шума (фильтрация, автокорреляция,

свертка)

37. Теоретические основы ЦОС

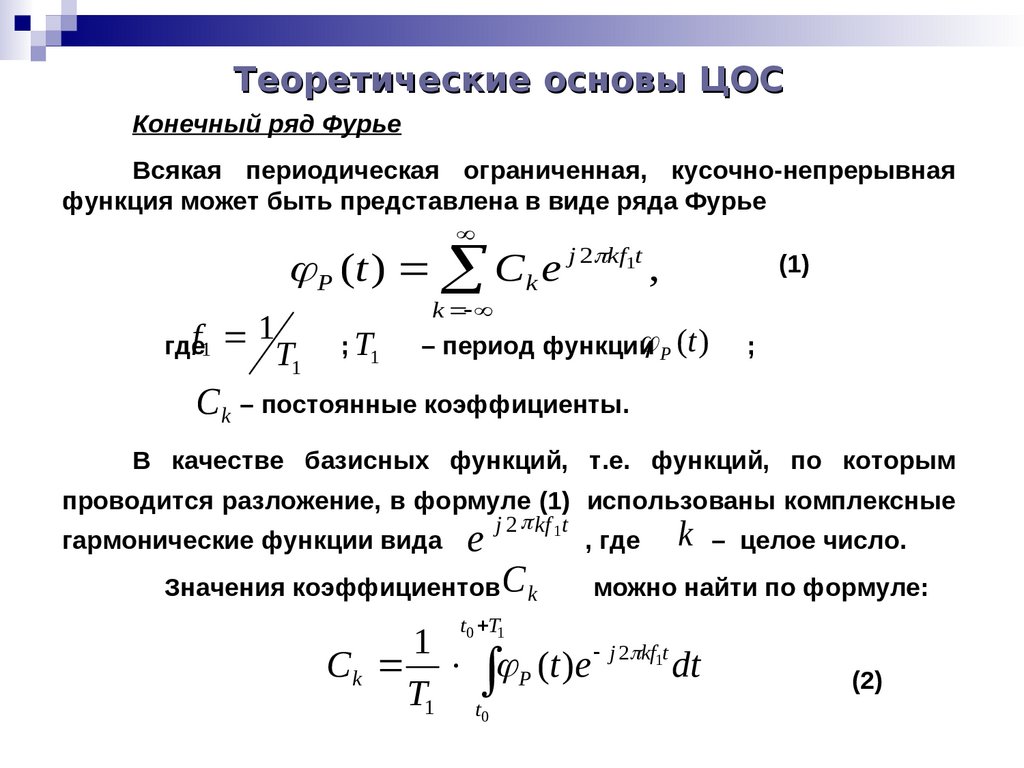

Конечный ряд ФурьеВсякая периодическая ограниченная, кусочно-непрерывная

функция может быть представлена в виде ряда Фурье

P (t ) Ck e j 2 kf t ,

(1)

1

f1

где

1

T1

k

; T1

P (t )

– период функции

;

C k – постоянные коэффициенты.

В качестве базисных функций, т.е. функций, по которым

проводится разложение, в формуле (1) использованы комплексные

гармонические функции вида

e

j 2 kf 1t

Значения коэффициентов C k

, где

k

– целое число.

можно найти по формуле:

t T

1 0 1

Ck P (t )e j 2 kf1t dt

T1 t0

(2)

38. Теоретические основы ЦОС

Ряд Фурье содержит бесконечное число членов. Именно вэтом случае можно поставить знак равенства между левой и правой

частью в формуле (1). На практике приходится ограничиваться

конечным числом членов, вследствие чего указанное равенство

соблюдается только приближенно.

Ряд Фурье имеет важное достоинство: при ограниченном

числе

членов

он

обеспечивает

наилучшее

в

смысле

среднеквадратичной погрешности приближение к исходной

функции. Это значит, что если в правой части соотношения (1) вести

суммирование от k = -n до k = n , где n – некоторое конечное число,

то наименьшая среднеквадратичная разность на периоде функции

p t

между левой и правой частями этого соотношения будет

Ck

иметь место в том случае, когда коэффициенты

определены по

формуле (2). При увеличении числа членов ряда Фурье до

бесконечности

среднеквадратичная

погрешность

разложения

стремится к нулю.

39. Теоретические основы ЦОС

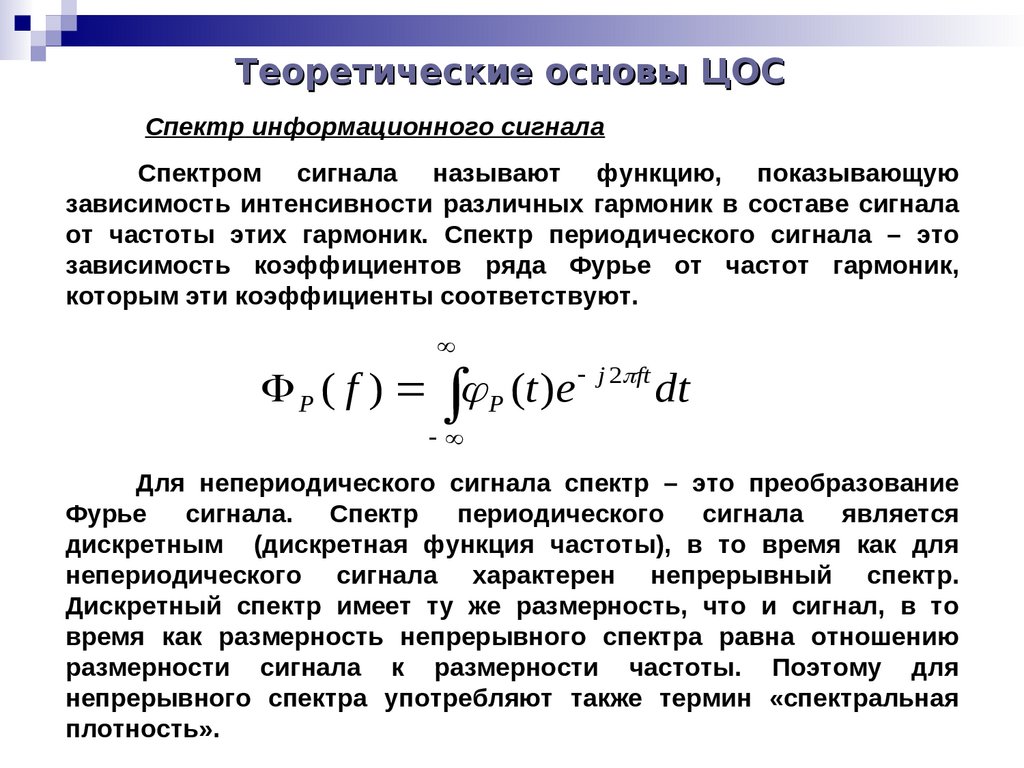

Спектр информационного сигналаСпектром сигнала называют функцию, показывающую

зависимость интенсивности различных гармоник в составе сигнала

от частоты этих гармоник. Спектр периодического сигнала – это

зависимость коэффициентов ряда Фурье от частот гармоник,

которым эти коэффициенты соответствуют.

P ( f ) P (t )e j 2 ft dt

Для непериодического сигнала спектр – это преобразование

Фурье

сигнала. Спектр

периодического

сигнала

является

дискретным (дискретная функция частоты), в то время как для

непериодического сигнала характерен непрерывный спектр.

Дискретный спектр имеет ту же размерность, что и сигнал, в то

время как размерность непрерывного спектра равна отношению

размерности сигнала к размерности частоты. Поэтому для

непрерывного спектра употребляют также термин «спектральная

плотность».

40. Теоретические основы ЦОС

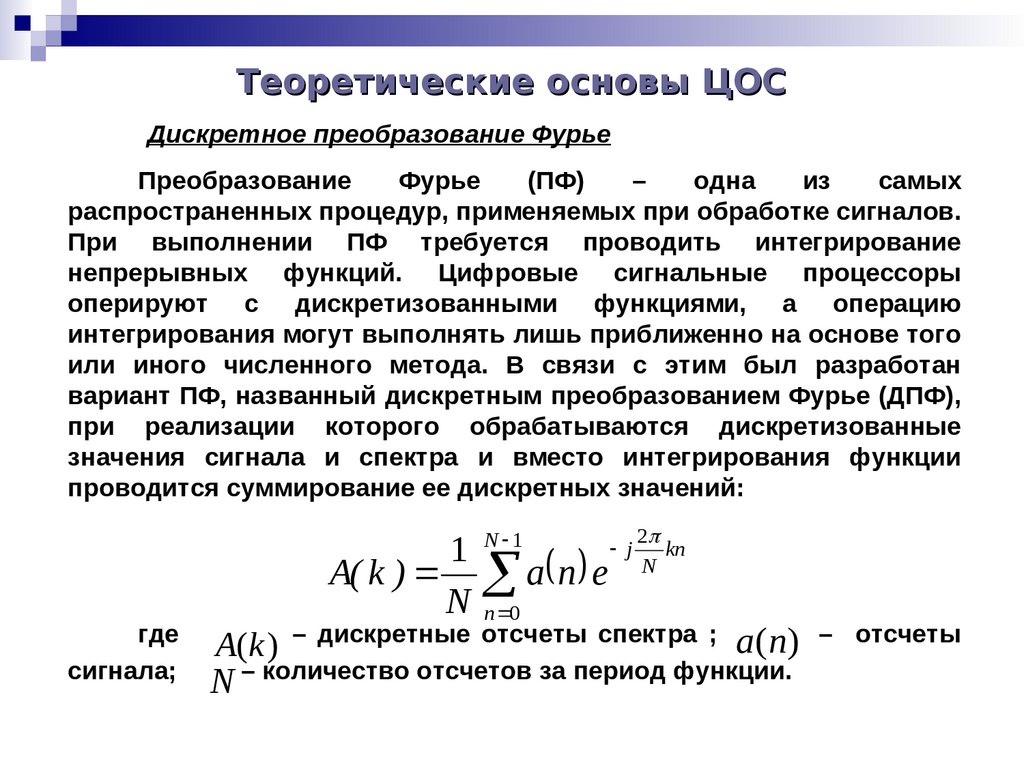

Дискретное преобразование ФурьеПреобразование

Фурье

(ПФ)

–

одна

из

самых

распространенных процедур, применяемых при обработке сигналов.

При выполнении ПФ требуется проводить интегрирование

непрерывных функций. Цифровые сигнальные процессоры

оперируют с дискретизованными функциями, а операцию

интегрирования могут выполнять лишь приближенно на основе того

или иного численного метода. В связи с этим был разработан

вариант ПФ, названный дискретным преобразованием Фурье (ДПФ),

при реализации которого обрабатываются дискретизованные

значения сигнала и спектра и вместо интегрирования функции

проводится суммирование ее дискретных значений:

где

сигнала;

1

A( k )

N

N 1

a n e

n 0

j

2

kn

N

A(k ) – дискретные отсчеты спектра ; a (n)

N – количество отсчетов за период функции.

– отсчеты

41. Теоретические основы ЦОС

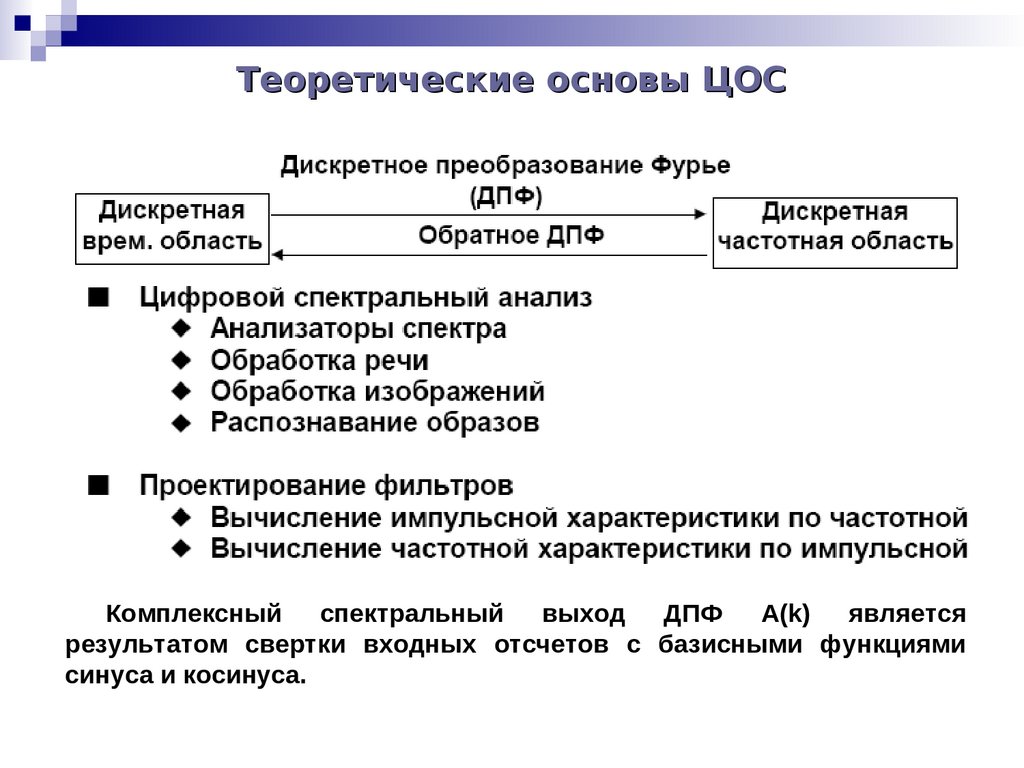

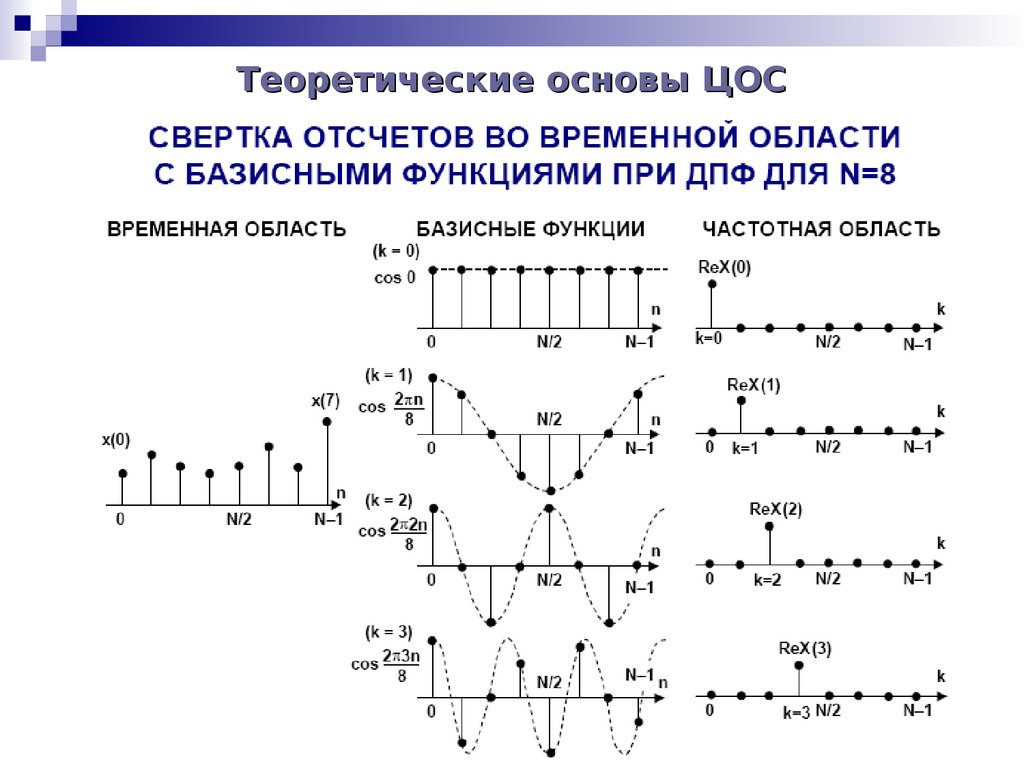

Комплексный спектральный выход ДПФA(k) является

результатом свертки входных отсчетов с базисными функциями

синуса и косинуса.

42. Теоретические основы ЦОС

43. Теоретические основы ЦОС

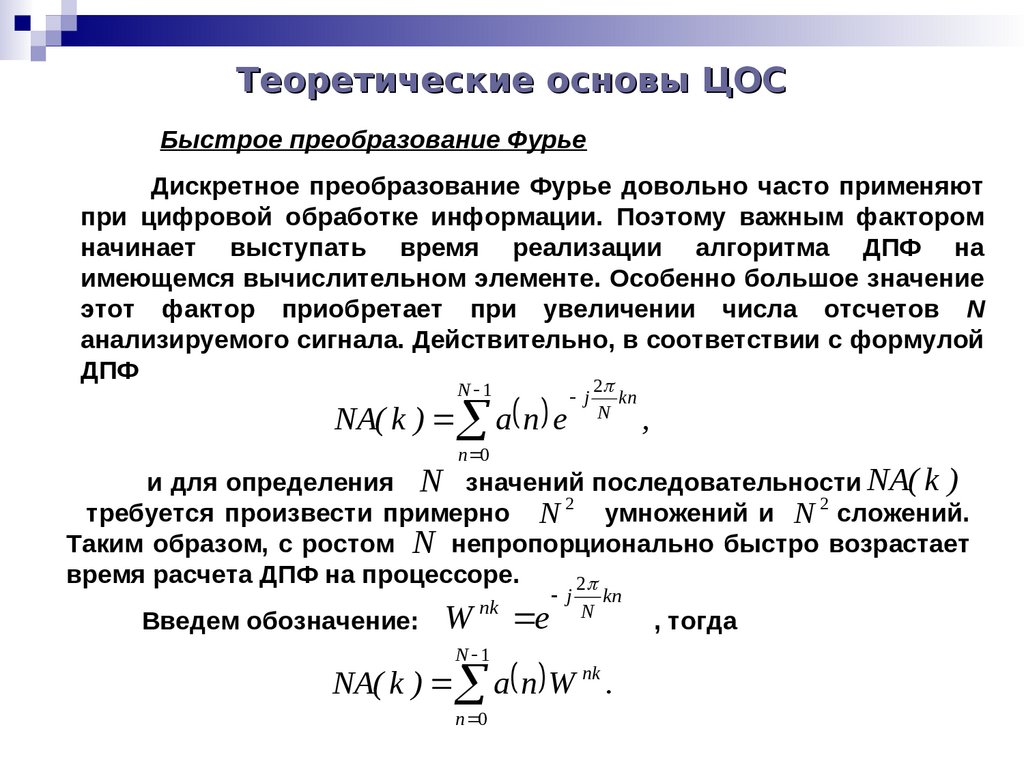

Быстрое преобразование ФурьеДискретное преобразование Фурье довольно часто применяют

при цифровой обработке информации. Поэтому важным фактором

начинает выступать время реализации алгоритма ДПФ на

имеющемся вычислительном элементе. Особенно большое значение

этот фактор приобретает при увеличении числа отсчетов N

анализируемого сигнала. Действительно, в соответствии с формулой

ДПФ

N 1

NA( k ) a n e

j

2

kn

N

,

n 0

и для определения N значений последовательности NA( k )

требуется произвести примерно N 2 умножений и N 2 сложений.

Таким образом, с ростом N непропорционально быстро возрастает

время расчета ДПФ на процессоре.

2

Введем обозначение:

W

nk

N 1

e

j

N

kn

NA( k ) a n W nk .

n 0

, тогда

44. Теоретические основы ЦОС

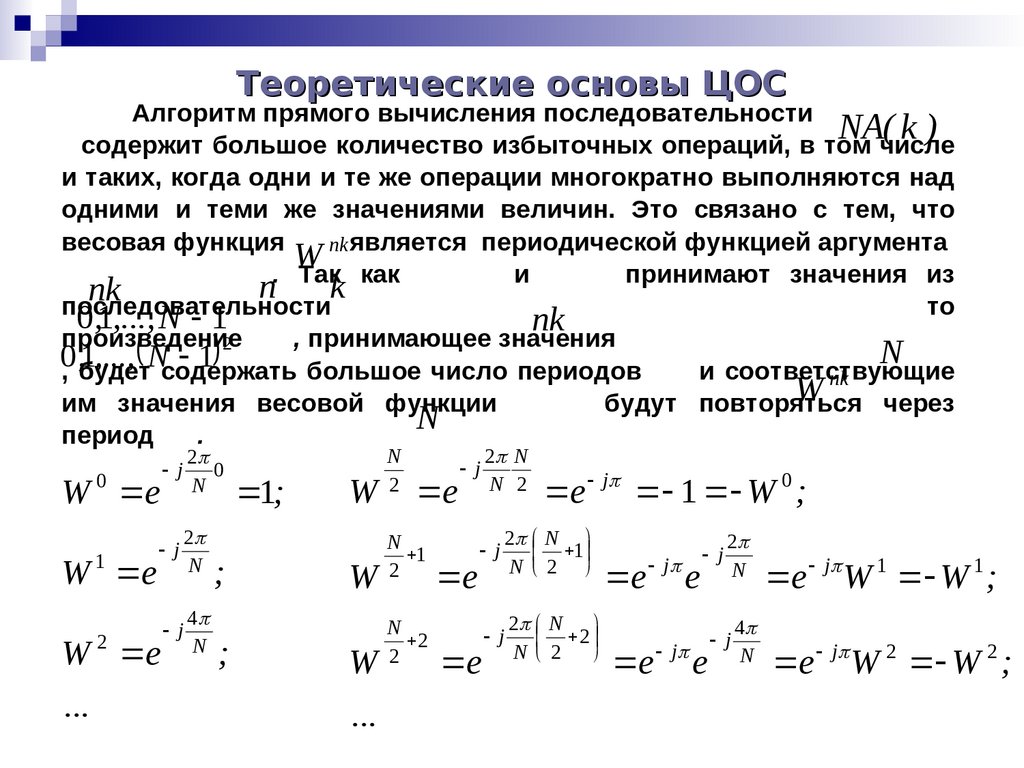

Алгоритм прямого вычисления последовательностиNA( k )

содержит большое количество избыточных операций, в том числе

и таких, когда одни и те же операции многократно выполняются над

одними и теми же значениями величин. Это связано с тем, что

весовая функция

nk является периодической функцией аргумента

W

. Так как

и

принимают значения из

n

k

nk

последовательности

то

0 ,1,..., N 1

nk

произведение

, принимающее значения

2

N

0, ,будет

1,..., Nсодержать

1

большое число периодов

и соответствующие

nk

W

им значения весовой функции

будут повторяться через

N

период

.

j

2

0

N

j

2

N

W 0 e

1

W e

2

W e

...

j

4

N

;

;

1;

W

W

W

...

N

2

e

N

1

2

N

2

2

j

e

2 N

N 2

j

e

e j 1 W 0 ;

2 N

1

N 2

j

2 N

2

N 2

e j e

j

e j e

2

N

j

4

N

e j W 1 W 1 ;

e j W 2 W 2 ;

45. Теоретические основы ЦОС

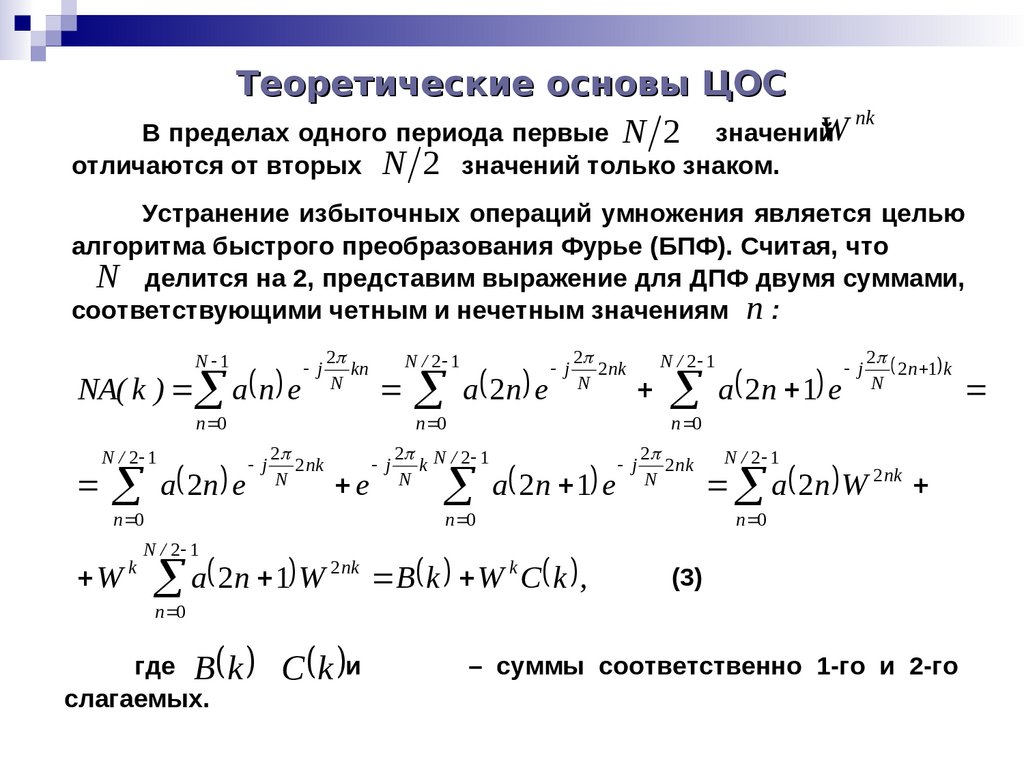

W nkВ пределах одного периода первые N 2 значений

отличаются от вторых N 2 значений только знаком.

Устранение избыточных операций умножения является целью

алгоритма быстрого преобразования Фурье (БПФ). Считая, что

N делится на 2, представим выражение для ДПФ двумя суммами,

соответствующими четным и нечетным значениям n :

N 1

NA( k ) a n e

j

2

kn

N

N / 2 1

n 0

N / 2 1

a 2n e

j

2

2 nk

N

W

2

2 nk

N

N / 2 1

n 0

e

n 0

k

a 2n e

j

j

2 N / 2 1

k

N

a 2n 1 e

a 2n 1 e

j

2

2 n 1 k

N

n 0

j

2

2 nk

N

n 0

N / 2 1

a 2n W 2 nk

n 0

N / 2 1

2 nk

k

a

2

n

1

W

B

k

W

C k ,

(3)

n 0

где B

слагаемых.

k

C k и

– суммы соответственно 1-го и 2-го

46. Теоретические основы ЦОС

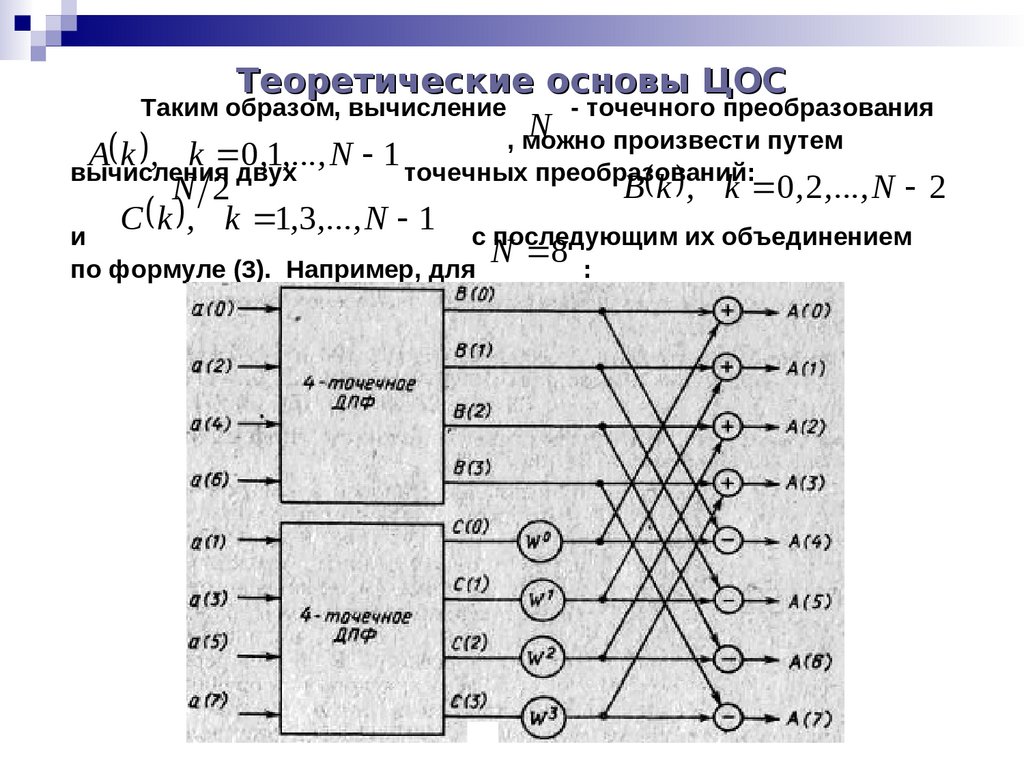

Таким образом, вычисление- точечного преобразования

N

, можно

произвести путем

A

k

,

k

0

,

1

,

...,

N

1

вычисления двух

точечных преобразований:

B k , k 0 , 2, ..., N 2

N 2

C k , k 1,3, ..., N 1 с последующим их объединением

и

N 8 :

по формуле (3). Например, для

47. Теоретические основы ЦОС

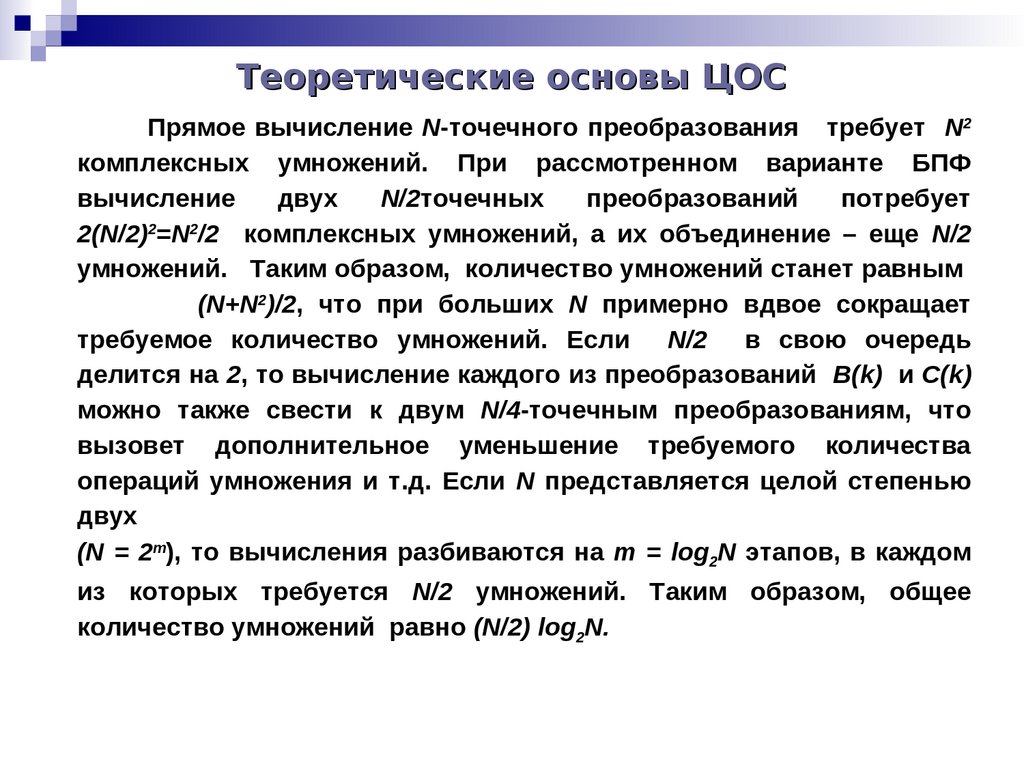

Прямое вычисление N-точечного преобразования требует N2комплексных умножений. При рассмотренном варианте БПФ

вычисление

двух

N/2точечных

преобразований

потребует

2(N/2)N/2)2=N2/2 комплексных умножений, а их объединение – еще N/2

умножений. Таким образом, количество умножений станет равным

(N/2)N+N2)/2, что при больших N примерно вдвое сокращает

требуемое количество умножений. Если N/2 в свою очередь

делится на 2, то вычисление каждого из преобразований B(N/2)k) и C(N/2)k)

можно также свести к двум N/4-точечным преобразованиям, что

вызовет дополнительное уменьшение требуемого количества

операций умножения и т.д. Если N представляется целой степенью

двух

(N/2)N = 2m), то вычисления разбиваются на т = log2N этапов, в каждом

из которых требуется N/2 умножений. Таким образом, общее

количество умножений равно (N/2)N/2) log2N.

48. Теоретические основы ЦОС

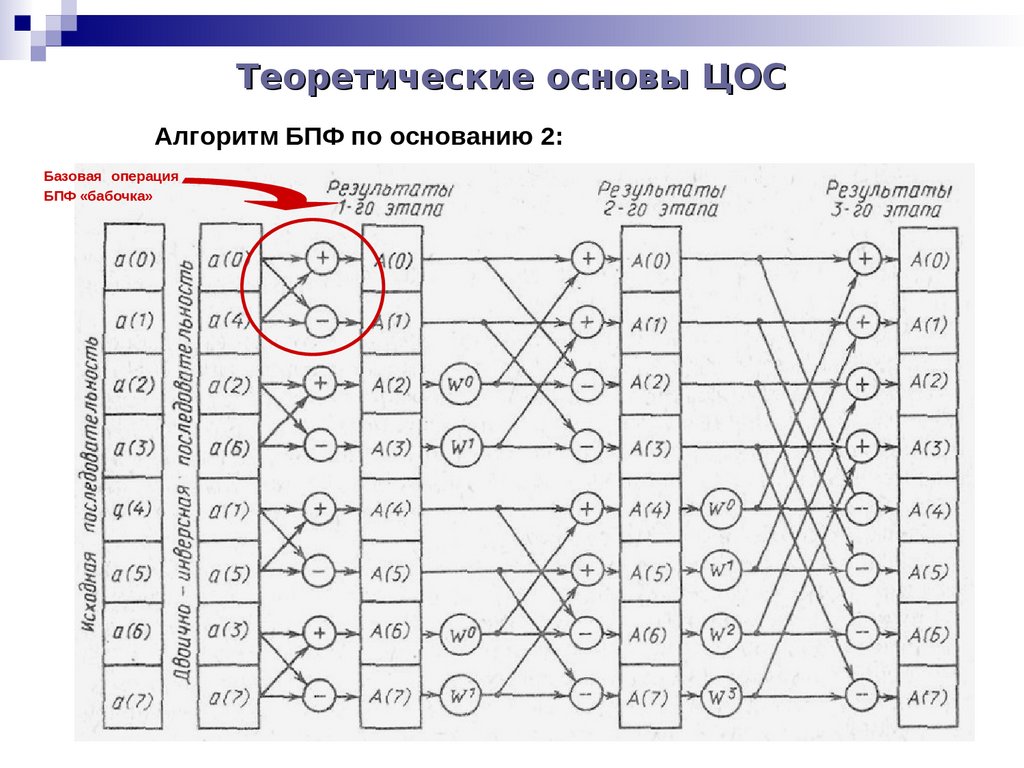

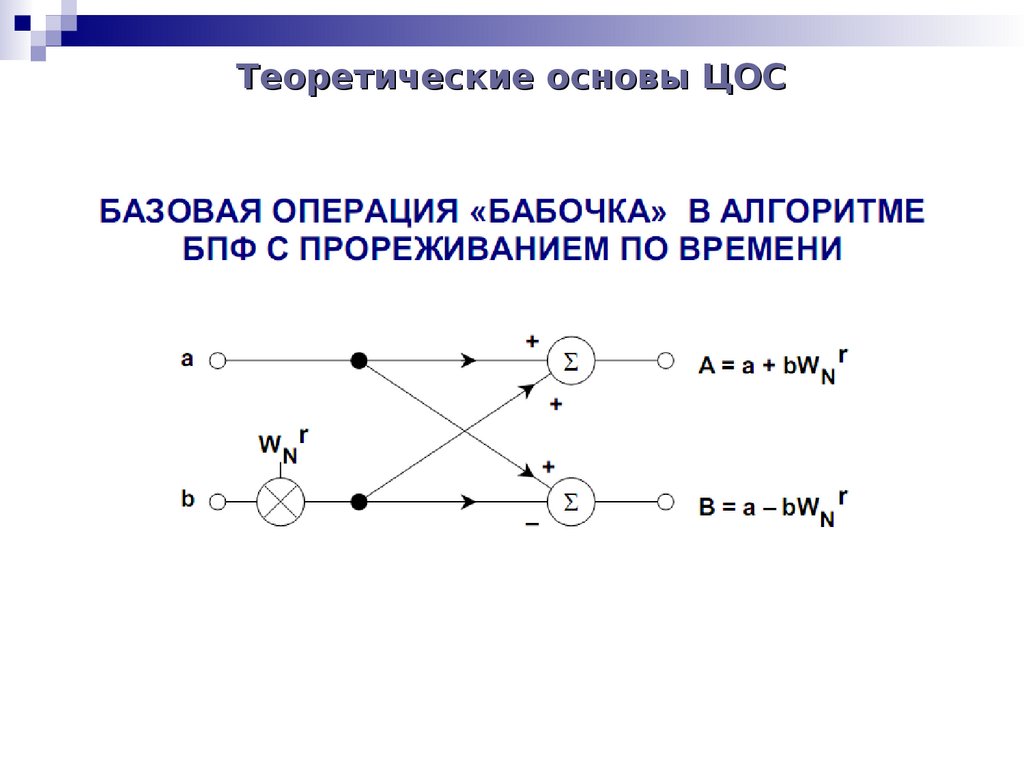

Алгоритм БПФ по основанию 2:Базовая операция

БПФ «бабочка»

49. Теоретические основы ЦОС

50. Теоретические основы ЦОС

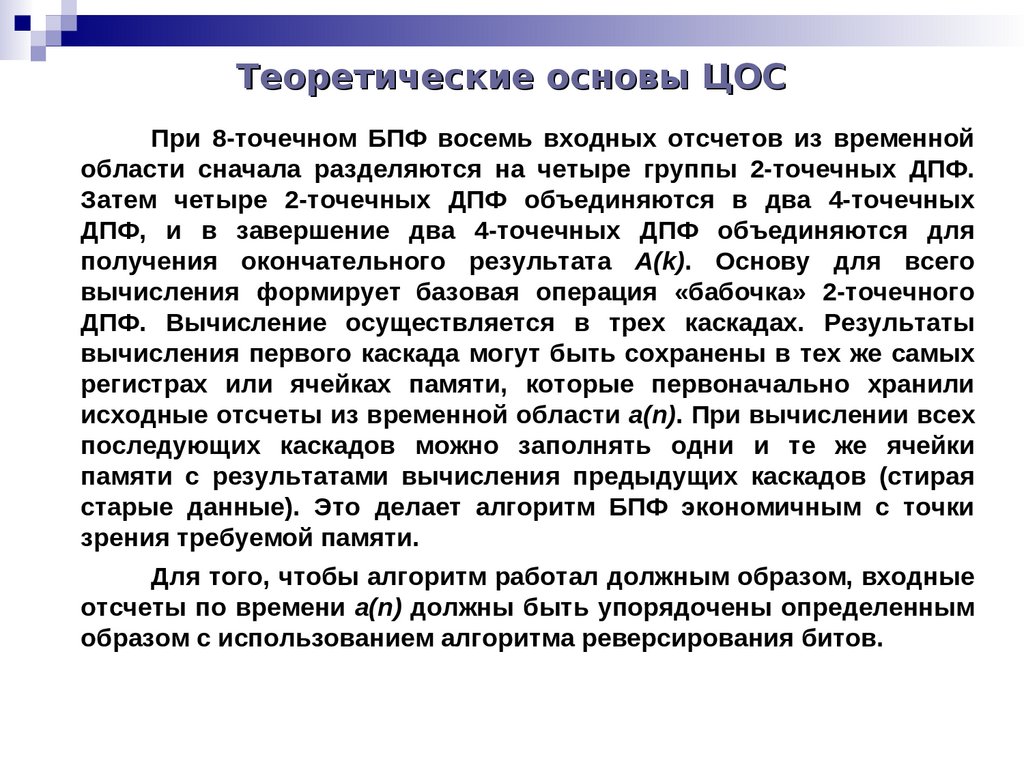

При 8-точечном БПФ восемь входных отсчетов из временнойобласти сначала разделяются на четыре группы 2-точечных ДПФ.

Затем четыре 2-точечных ДПФ объединяются в два 4-точечных

ДПФ, и в завершение два 4-точечных ДПФ объединяются для

получения окончательного результата A(N/2)k). Основу для всего

вычисления формирует базовая операция «бабочка» 2-точечного

ДПФ. Вычисление осуществляется в трех каскадах. Результаты

вычисления первого каскада могут быть сохранены в тех же самых

регистрах или ячейках памяти, которые первоначально хранили

исходные отсчеты из временной области a(N/2)n). При вычислении всех

последующих каскадов можно заполнять одни и те же ячейки

памяти с результатами вычисления предыдущих каскадов (стирая

старые данные). Это делает алгоритм БПФ экономичным с точки

зрения требуемой памяти.

Для того, чтобы алгоритм работал должным образом, входные

отсчеты по времени a(N/2)n) должны быть упорядочены определенным

образом с использованием алгоритма реверсирования битов.

51. Теоретические основы ЦОС

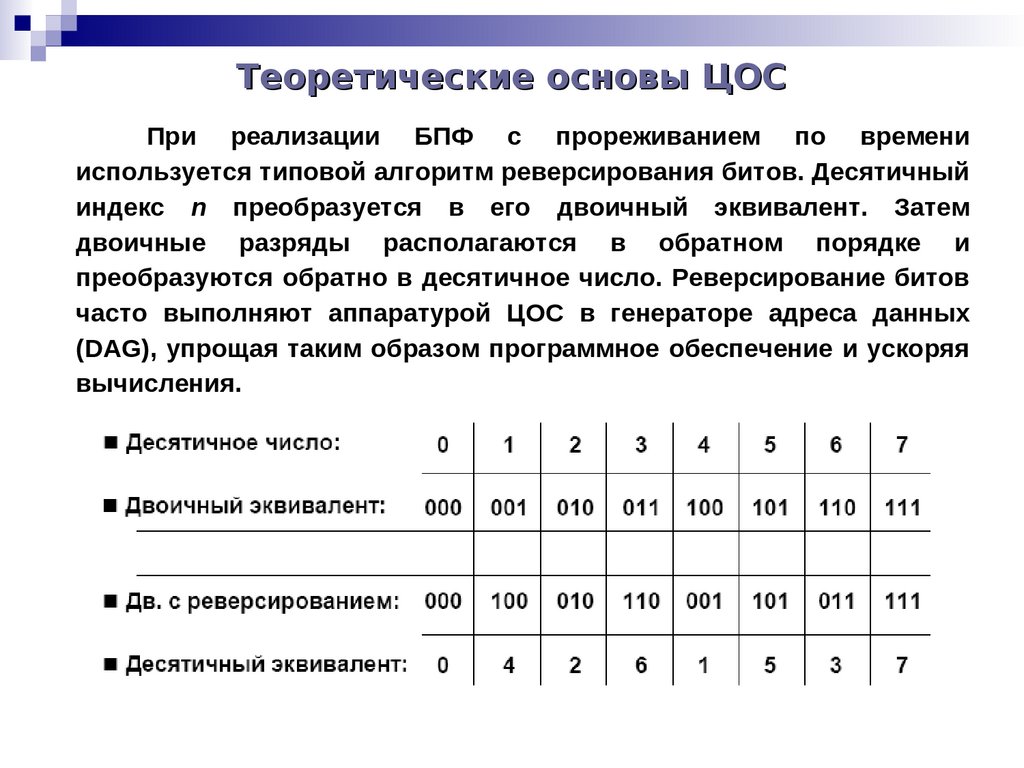

При реализации БПФ с прореживанием по временииспользуется типовой алгоритм реверсирования битов. Десятичный

индекс n преобразуется в его двоичный эквивалент. Затем

двоичные разряды располагаются в обратном порядке и

преобразуются обратно в десятичное число. Реверсирование битов

часто выполняют аппаратурой ЦОС в генераторе адреса данных

(DAG), упрощая таким образом программное обеспечение и ускоряя

вычисления.

52. Теоретические основы ЦОС

53. Теоретические основы ЦОС

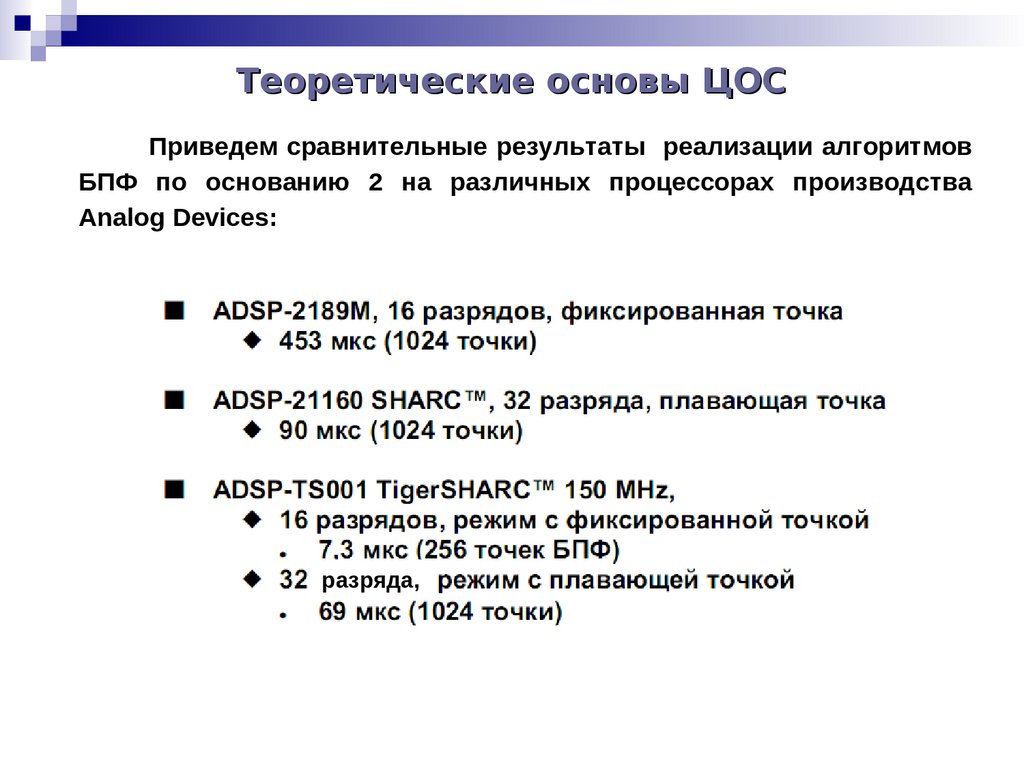

Приведем сравнительные результаты реализации алгоритмовБПФ по основанию 2 на различных процессорах производства

Analog Devices:

разряда,

54. Теоретические основы ЦОС

Требования к ЦСП для реализации алгоритмов БПФ вреальном масштабе времени

Существует два основных способа обработки сигналов в

реальном масштабе времени: обработка одного отсчета в каждый

момент времени (непрерывная обработка) и обработка одного

пакета данных в каждый момент времени (пакетная обработка).

Системы, основанные на непрерывной обработке, такие как

цифровой фильтр, получают данные в виде одного отсчета в

каждый момент времени. В каждом такте новый отсчет поступает в

систему, а обработанный отсчет передается на выход.

Системы, основанные на пакетной обработке, такие как

построенный на БПФ цифровой анализатор спектра, получают

данные в виде целого пакета отсчетов. Происходит обработка всего

пакета исходных данных, результатом которой является пакет

преобразованных выходных данных.

55. Теоретические основы ЦОС

Для обеспечения функционирования в реальном масштабевремени при пакетной обработке полный расчет БПФ должен

выполняться в промежутке, соответствующем времени накопления

одного пакета данных и равном N/fs, где fs – частота дискретизации,

N – число отсчетов в пакете данных. Предполагается, что, пока

производится вычисление БПФ текущего пакета данных, ЦСП

накапливает данные для следующего пакета. Накопление данных

является одной из сфер, где важную роль играют архитектурные

особенности ЦСП. Непрерывное получение данных облегчается

благодаря возможностям гибкой адресации данных в ЦСП в

сочетании с использованием каналов прямого доступа к памяти

(Direct Memory Access, DMA).

56. Теоретические основы ЦОС

ПРИМЕР ОГРАНИЧЕНИЙ ПРИ ПАКЕТНОМ ВЫЧИСЛЕНИИ БПФ ВРЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ

fs =

57. Теоретические основы ЦОС

Эффект расширения спектра анализируемого сигнала при БПФЭффект расширения спектра анализируемого сигнала при

вычислении БПФ может быть лучше всего проиллюстрирован на

примере выполнения N-точечного БПФ с синусоидальным входным

сигналом.

Рассмотрим два случая.

В первом случае соотношение между частотой дискретизации и

частотой входного синусоидального сигнала таково, что в выборке

содержится в точности целое число периодов синусоидального

сигнала. При таких условиях форма входного сигнала представляет

собой непрерывную синусоидальную функцию, и на выходе БПФ

будет один ненулевой частотный отсчет, соответствующий частоте

входного сигнала.

58. Теоретические основы ЦОС

59. Теоретические основы ЦОС

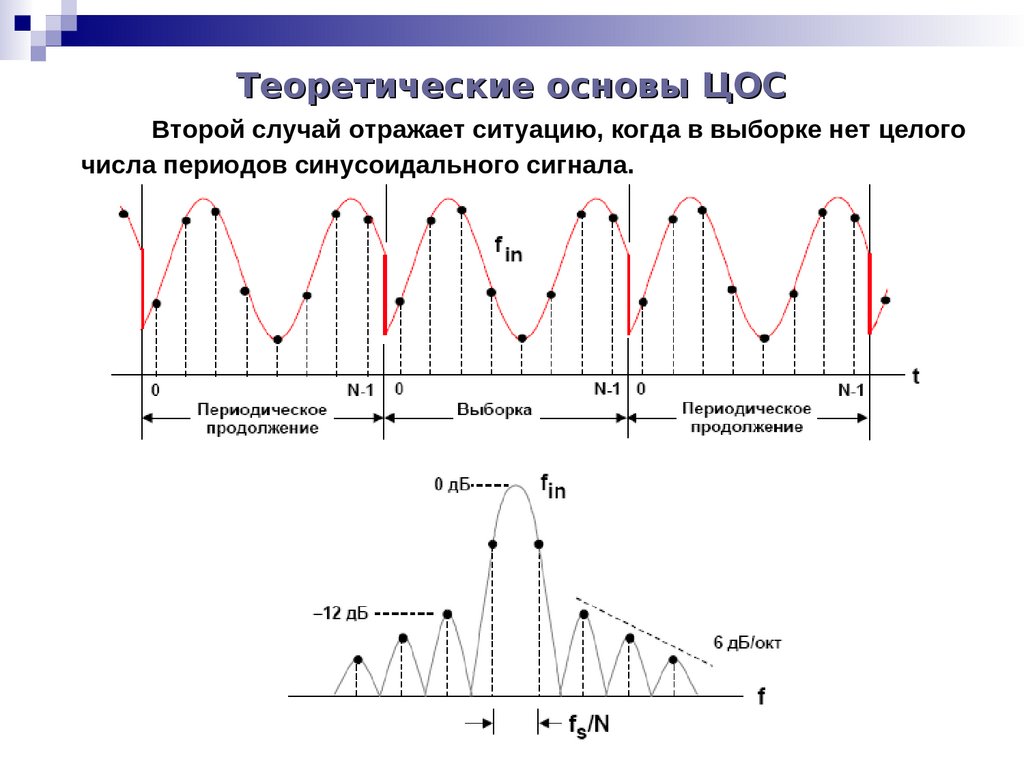

Второй случай отражает ситуацию, когда в выборке нет целогочисла периодов синусоидального сигнала.

60. Теоретические основы ЦОС

Разрывы, которые образуются в конечных точках выборки,приводят к расширению спектра анализируемого сигнала

вследствие появления дополнительных гармоник. Кроме появления

боковых лепестков, происходит расширение основного лепестка,

что приводит к снижению разрешающей способности по частоте.

Этот

процесс

эквивалентен

перемножению

входного

синусоидального

сигнала

с

прямоугольным

импульсом.

Перемножение сигналов во временной области эквивалентно

свертке их спектров.

Прямоугольный

импульс

имеет

известную

частотную

характеристику sin(x)/x и связанные с этим широкий основной

лепесток и боковые лепестки, причем первый боковой лепесток

только на 12 дБ ниже основного, а боковые лепестки имеют спад

только 6 дБ/окт.

61. Теоретические основы ЦОС

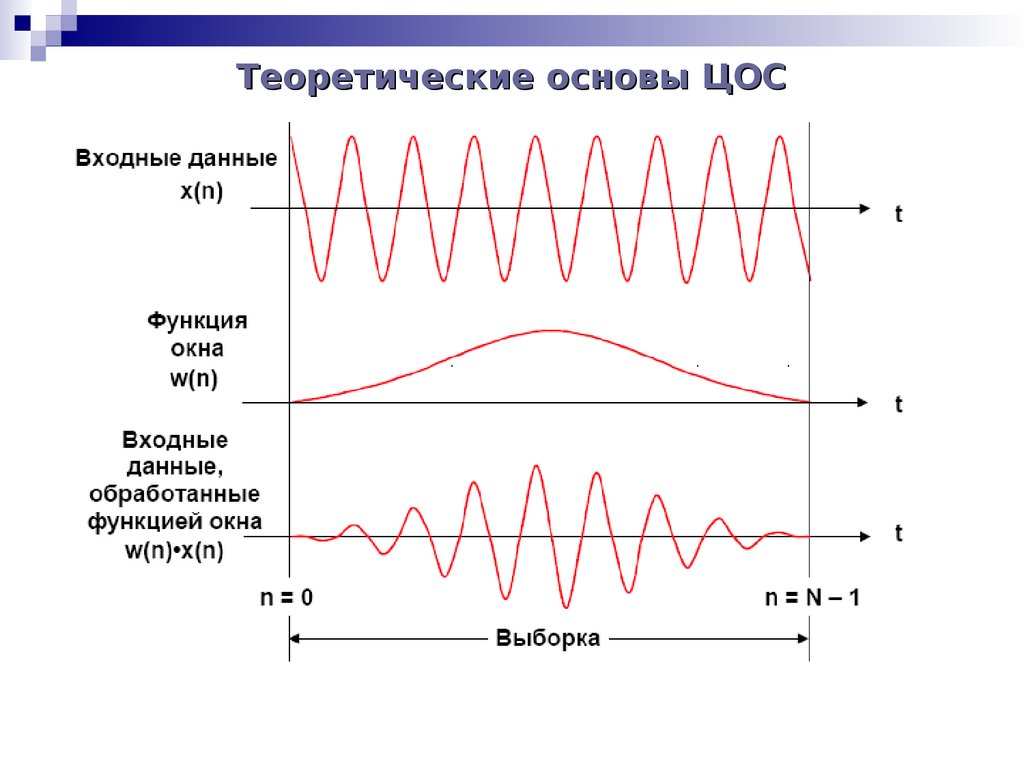

Эффект расширения основного лепестка и появления боковыхлепестков

значительно

ухудшает

основное

преимущество

преобразования Фурье – его частотную избирательность.

Поскольку

в

практических

приложениях

БПФ

для

спектрального анализа точные входные частоты неизвестны,

следует предпринять меры для уменьшения боковых лепестков. Это

достигается выбором оконной функции с более сложной формой,

чем прямоугольная. Входные отсчеты по времени умножаются на

соответствующую функцию окна, что влечет за собой обнуление

сигнала на краях выборки.

62. Теоретические основы ЦОС

63. Теоретические основы ЦОС

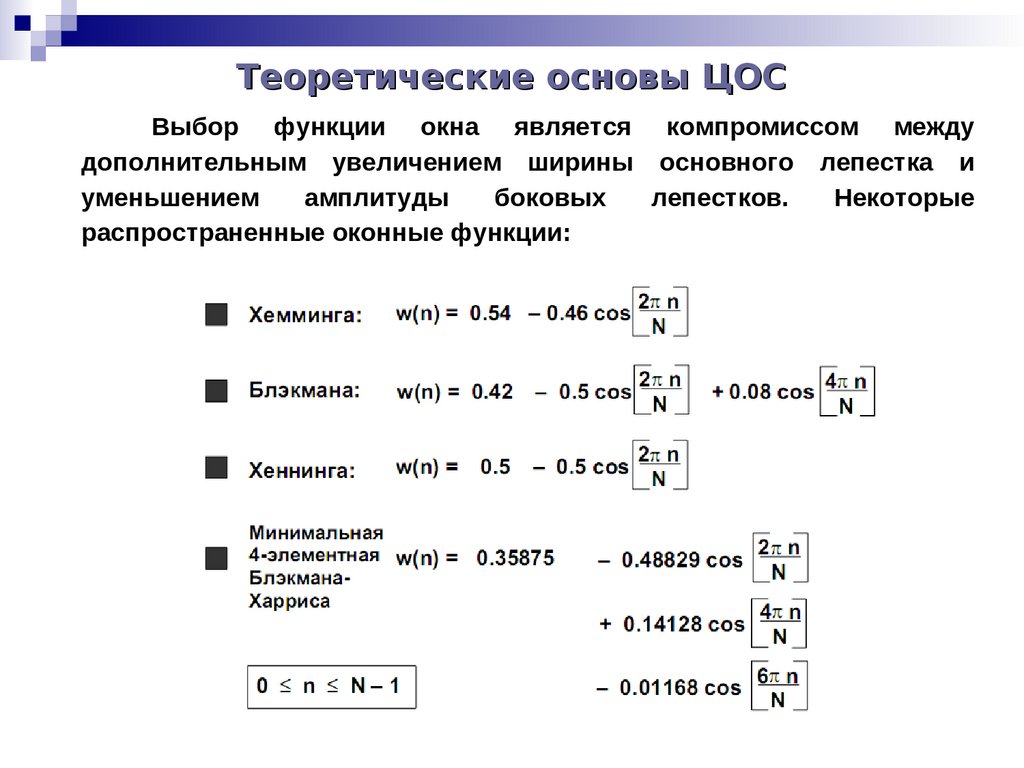

Выбор функции окна является компромиссом междудополнительным увеличением ширины основного лепестка и

уменьшением

амплитуды

боковых

лепестков.

Некоторые

распространенные оконные функции:

64. Теоретические основы ЦОС

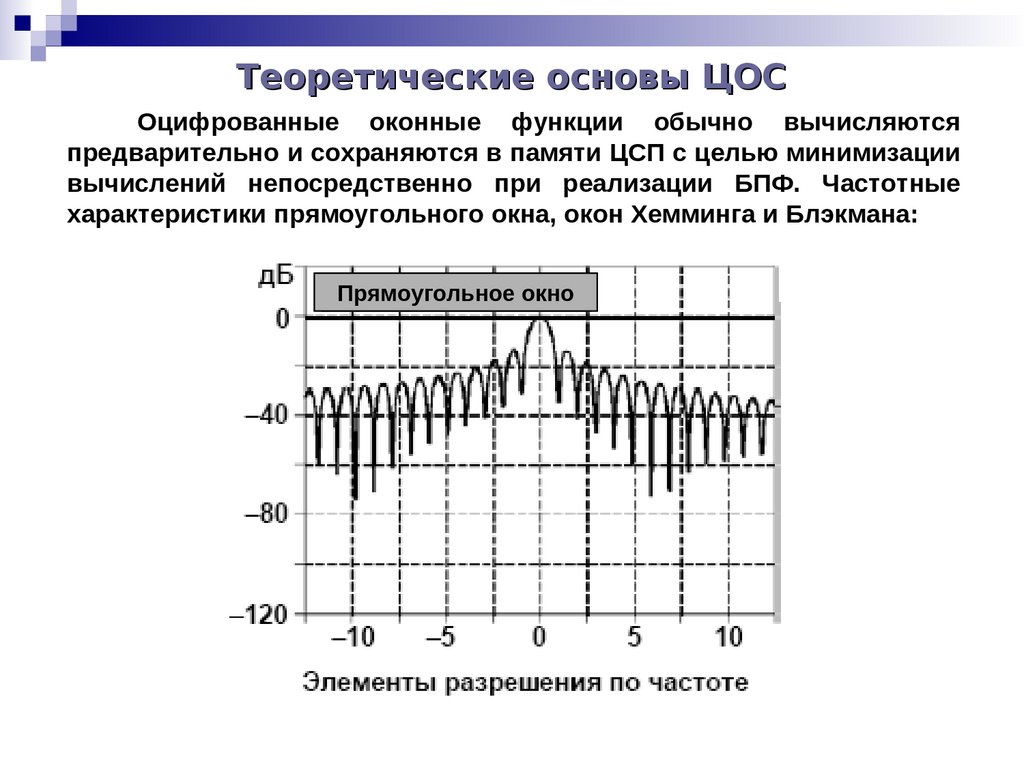

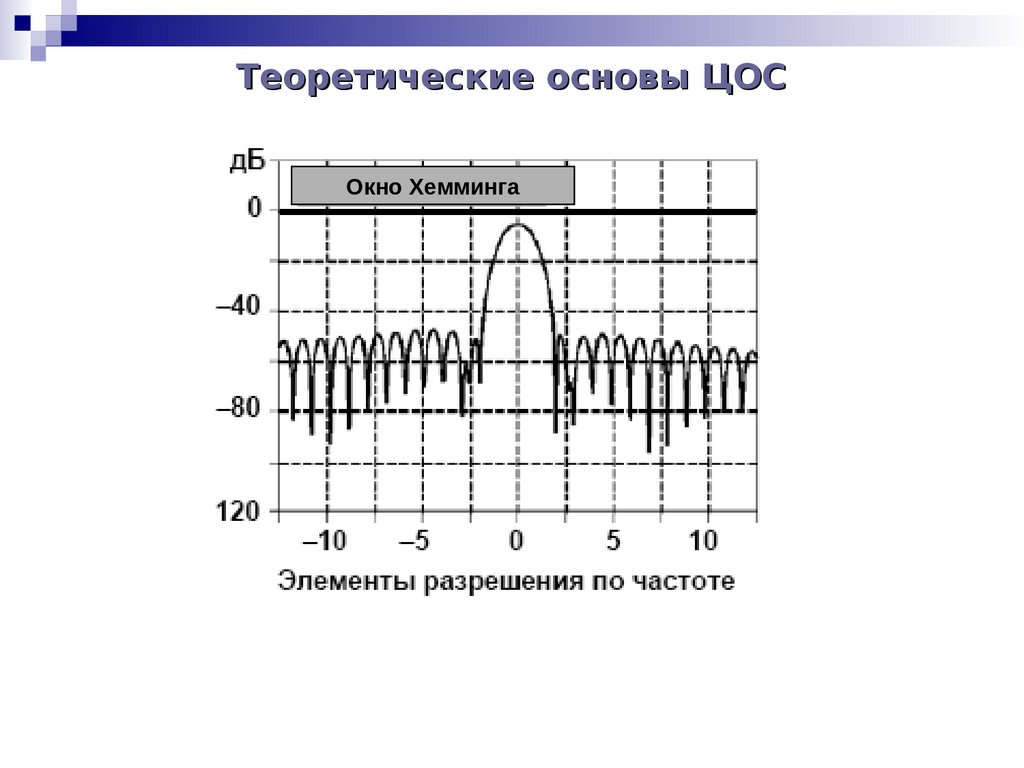

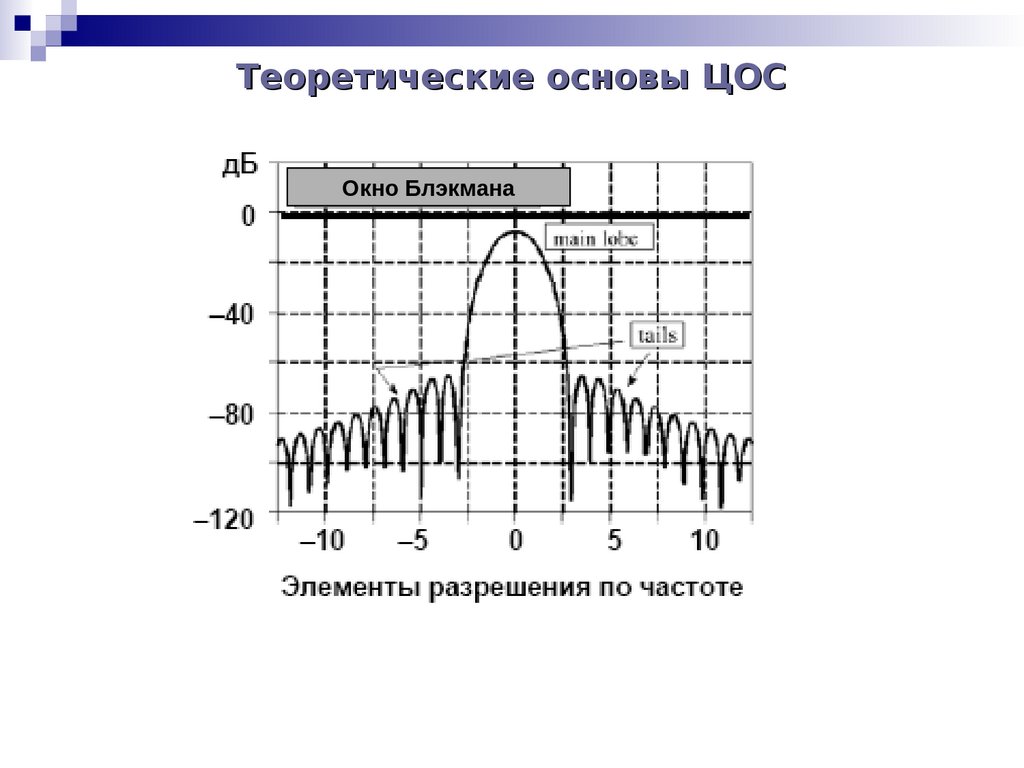

Оцифрованные оконные функции обычно вычисляютсяпредварительно и сохраняются в памяти ЦСП с целью минимизации

вычислений непосредственно при реализации БПФ. Частотные

характеристики прямоугольного окна, окон Хемминга и Блэкмана:

Прямоугольное окно

65. Теоретические основы ЦОС

Окно Хемминга66. Теоретические основы ЦОС

Окно Блэкмана67. Теоретические основы ЦОС

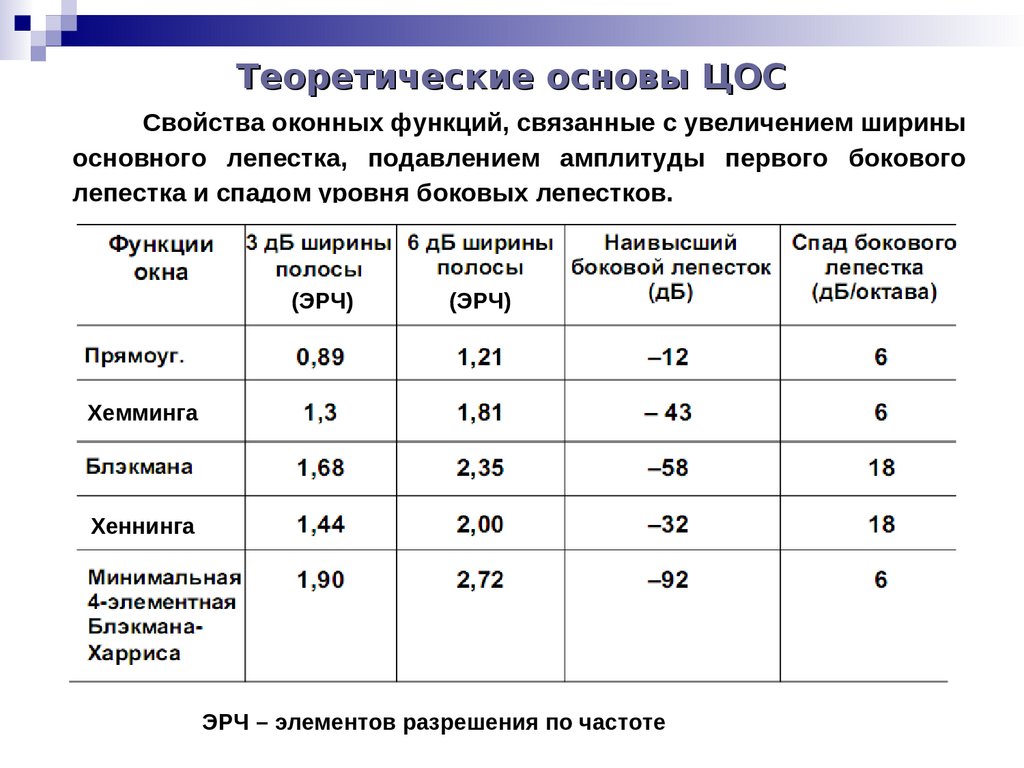

Свойства оконных функций, связанные с увеличением шириныосновного лепестка, подавлением амплитуды первого бокового

лепестка и спадом уровня боковых лепестков.

(ЭРЧ)

(ЭРЧ)

Хемминга

Хеннинга

ЭРЧ – элементов разрешения по частоте

68. Теоретические основы ЦОС

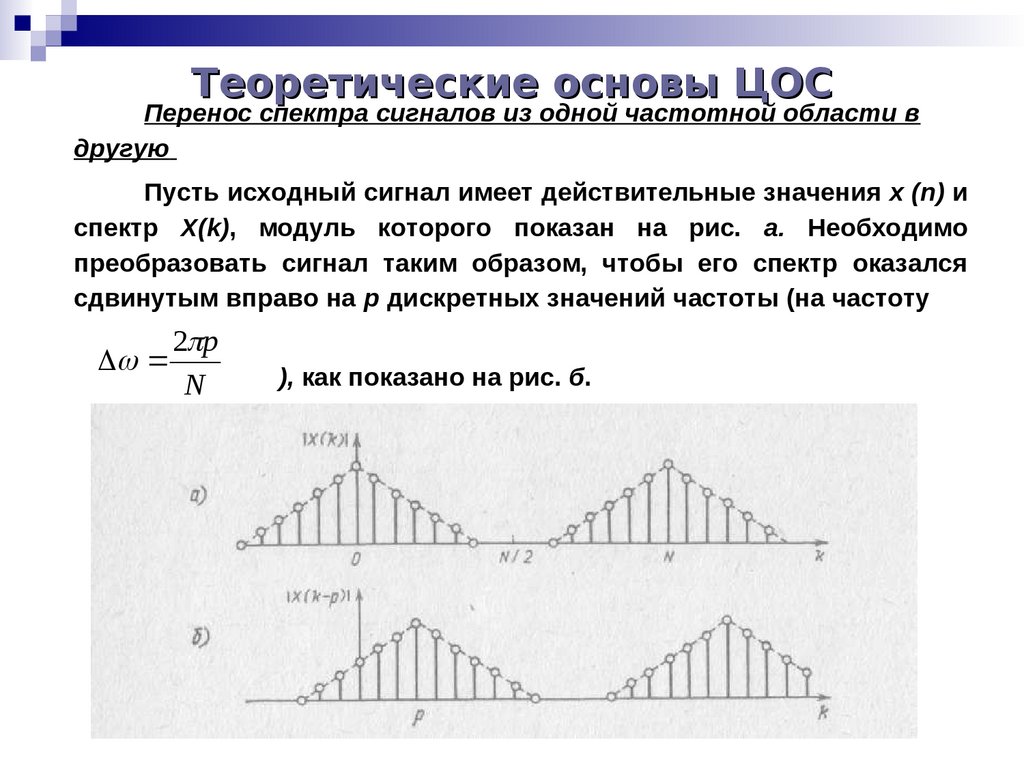

Перенос спектра сигналов из одной частотной области вдругую

Пусть исходный сигнал имеет действительные значения х (N/2)n) и

спектр X(N/2)k), модуль которого показан на рис. а. Необходимо

преобразовать сигнал таким образом, чтобы его спектр оказался

сдвинутым вправо на р дискретных значений частоты (на частоту

2 p

N

), как показано на рис. б.

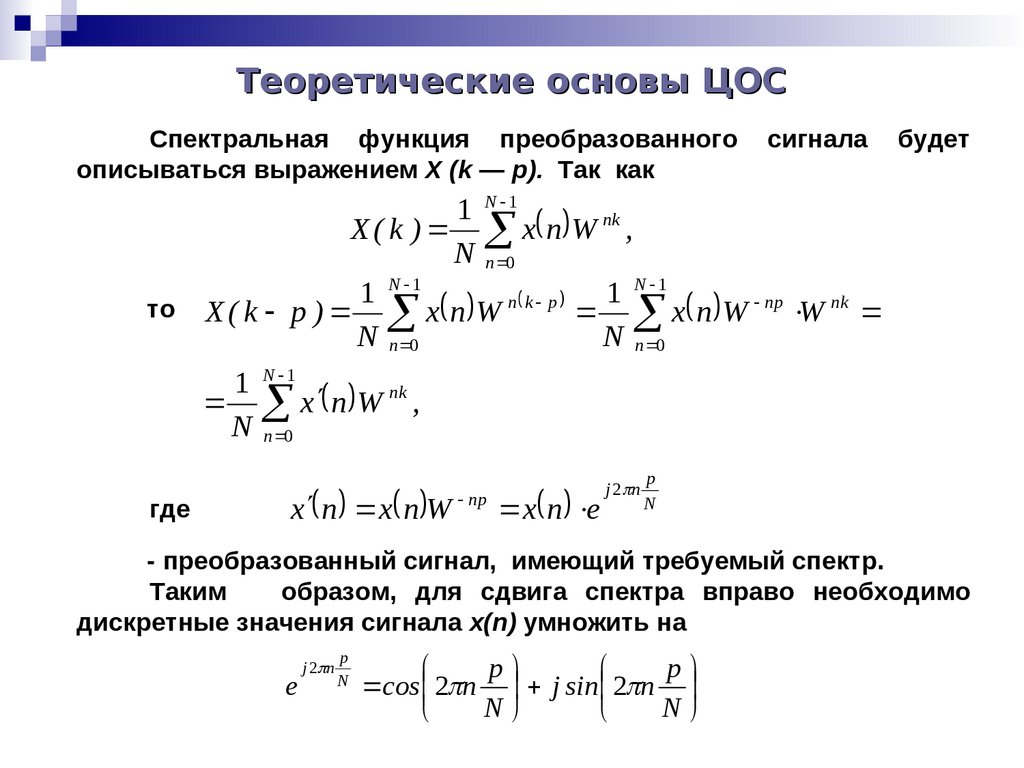

69. Теоретические основы ЦОС

Спектральная функция преобразованногоописываться выражением X (N/2)k — р). Так как

сигнала

будет

1 N 1

X ( k ) x n W nk ,

N n 0

N 1

N 1

1

1

n k p

то X ( k p ) x n W

x n W np W nk

N n 0

N n 0

1

N

где

N 1

nk

x

n

W

,

n 0

x n x n W

np

x n e

j 2 n

p

N

- преобразованный сигнал, имеющий требуемый спектр.

Таким

образом, для сдвига спектра вправо необходимо

дискретные значения сигнала х(N/2)n) умножить на

e

j 2 n

p

N

p

p

cos 2 n j sin 2 n

N

N

70. Теоретические основы ЦОС

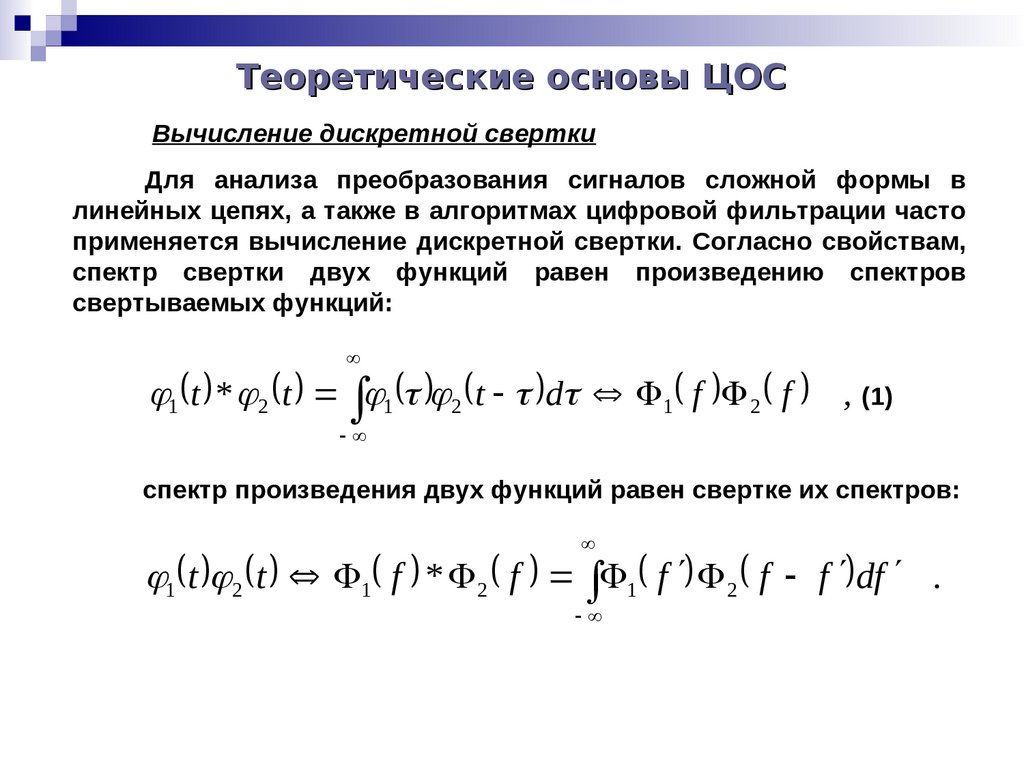

Вычисление дискретной сверткиДля анализа преобразования сигналов сложной формы в

линейных цепях, а также в алгоритмах цифровой фильтрации часто

применяется вычисление дискретной свертки. Согласно свойствам,

спектр свертки двух функций равен произведению спектров

свертываемых функций:

1 t * 2 t 1 2 t d 1 f 2 f , (1)

спектр произведения двух функций равен свертке их спектров:

1 t 2 t 1 f * 2 f 1 f 2 f f df .

71. Теоретические основы ЦОС

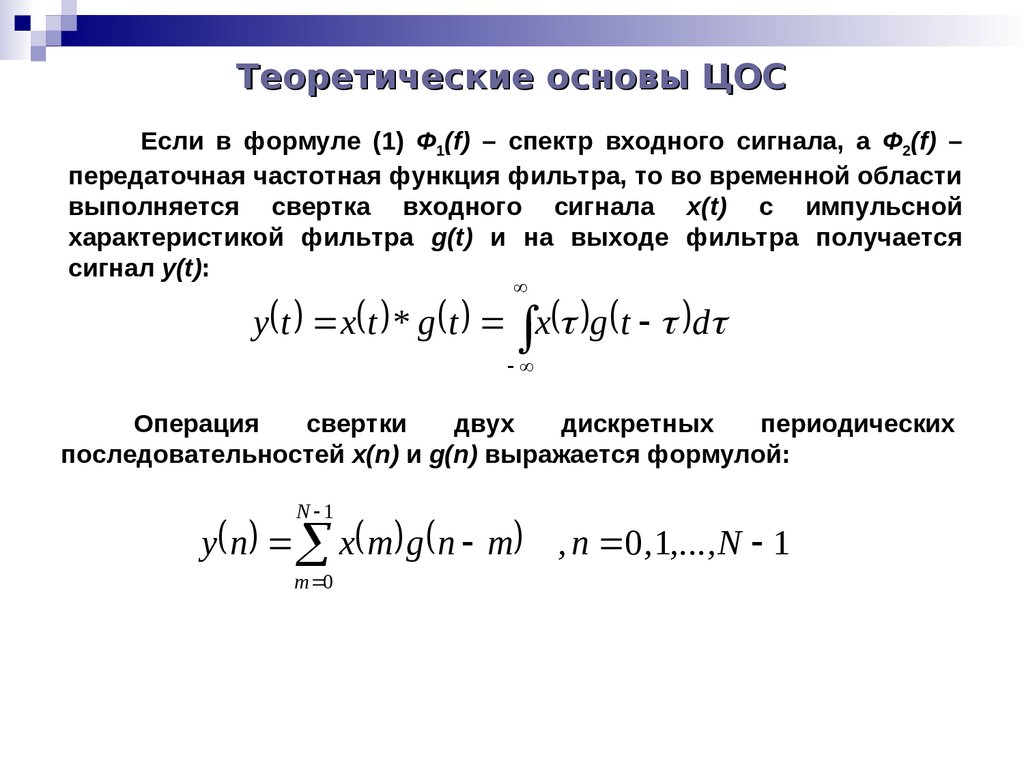

Если в формуле (1) Ф1(N/2)f) – спектр входного сигнала, а Ф2(N/2)f) –передаточная частотная функция фильтра, то во временной области

выполняется свертка входного сигнала x(N/2)t) с импульсной

характеристикой фильтра g(N/2)t) и на выходе фильтра получается

сигнал y(N/2)t):

y t x t * g t x g t d

Операция

свертки

двух

дискретных

периодических

последовательностей x(N/2)n) и g(N/2)n) выражается формулой:

N 1

y n x m g n m , n 0,1,..., N 1

m 0

72. Теоретические основы ЦОС

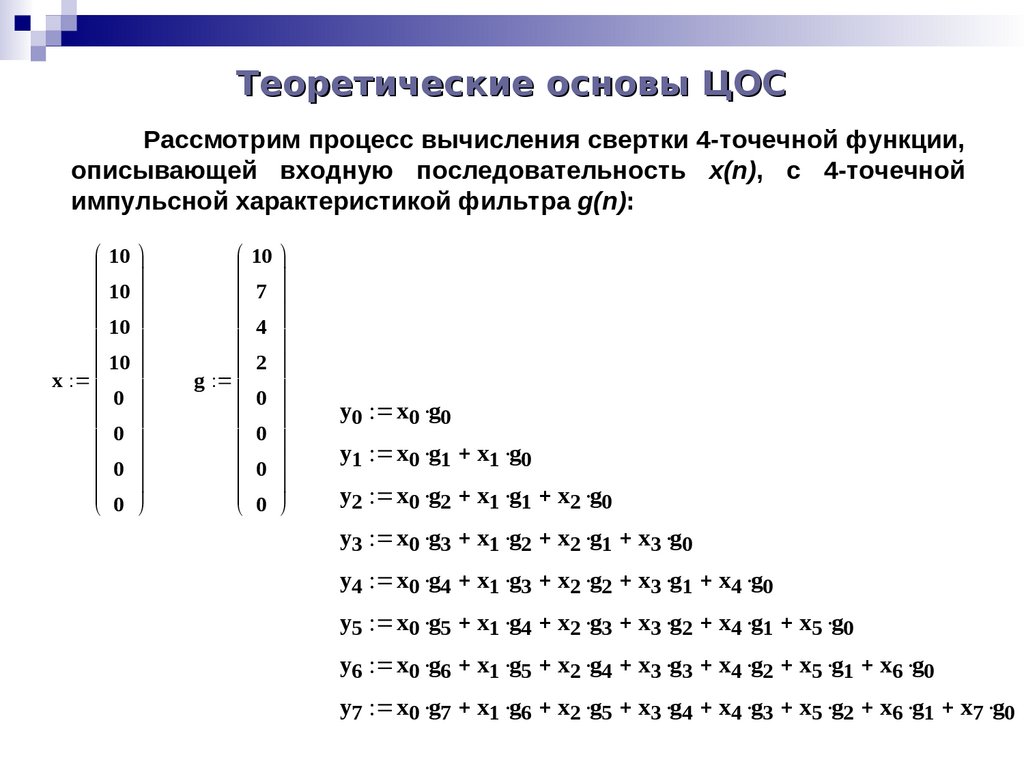

Рассмотрим процесс вычисления свертки 4-точечной функции,описывающей входную последовательность x(N/2)n), с 4-точечной

импульсной характеристикой фильтра g(N/2)n):

10

10

10

10

x

0

0

0

0

10

7

4

2

g

0

0

0

0

y0 x0 g0

y1 x0 g1 x1 g0

y2 x0 g2 x1 g1 x2 g0

y3 x0 g3 x1 g2 x2 g1 x3 g0

y4 x0 g4 x1 g3 x2 g2 x3 g1 x4 g0

y5 x0 g5 x1 g4 x2 g3 x3 g2 x4 g1 x5 g0

y6 x0 g6 x1 g5 x2 g4 x3 g3 x4 g2 x5 g1 x6 g0

y7 x0 g7 x1 g6 x2 g5 x3 g4 x4 g3 x5 g2 x6 g1 x7 g0

73. Теоретические основы ЦОС

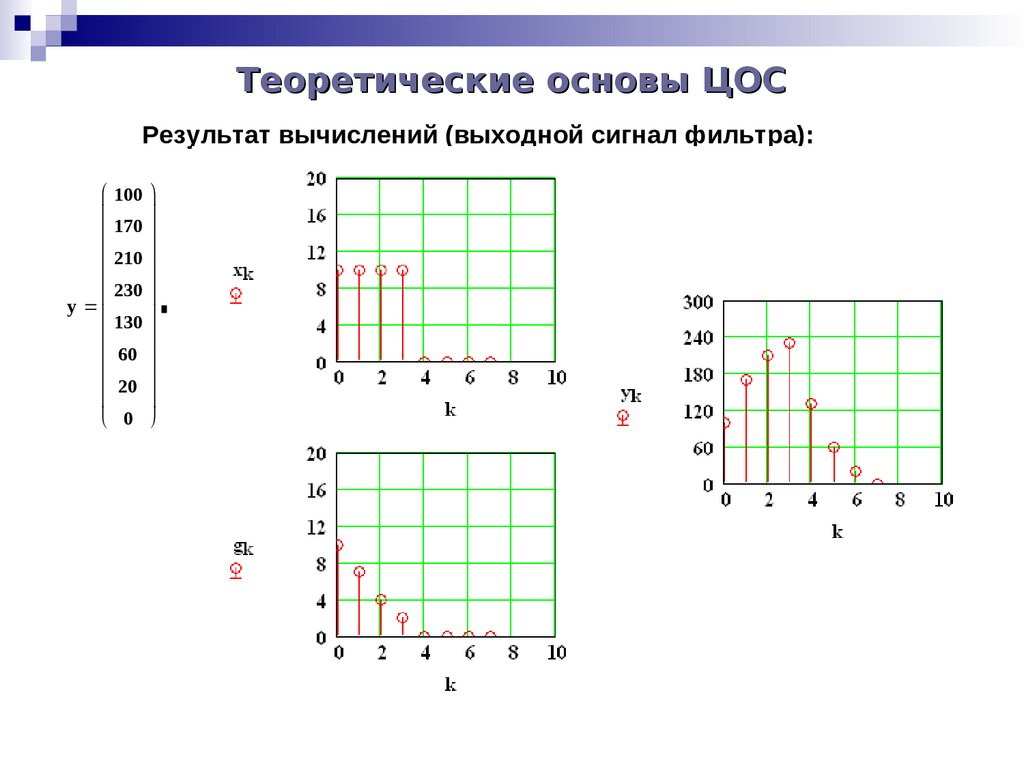

Результат вычислений (выходной сигнал фильтра):100

170

210

230

y

130

60

20

0

74. Теоретические основы ЦОС

Схема фильтра с прямым выполнением свертки:x(N/2)t)

x(N/2)m)

ФНЧ

УВХ

АЦП

Вычислитель

Упр.

Адрес

ПЗУ

таблица

дискретных

отсчетов

импульсной

функции

g(m)

дискретная

свертка

последовательностей x(m) и

g(n-m)

y(N/2)n)

y(N/2)t)

ЦАП

ФНЧ

g(N/2)n-m)

Требуется

≈ N умножений

действительных чисел

2

75. Теоретические основы ЦОС

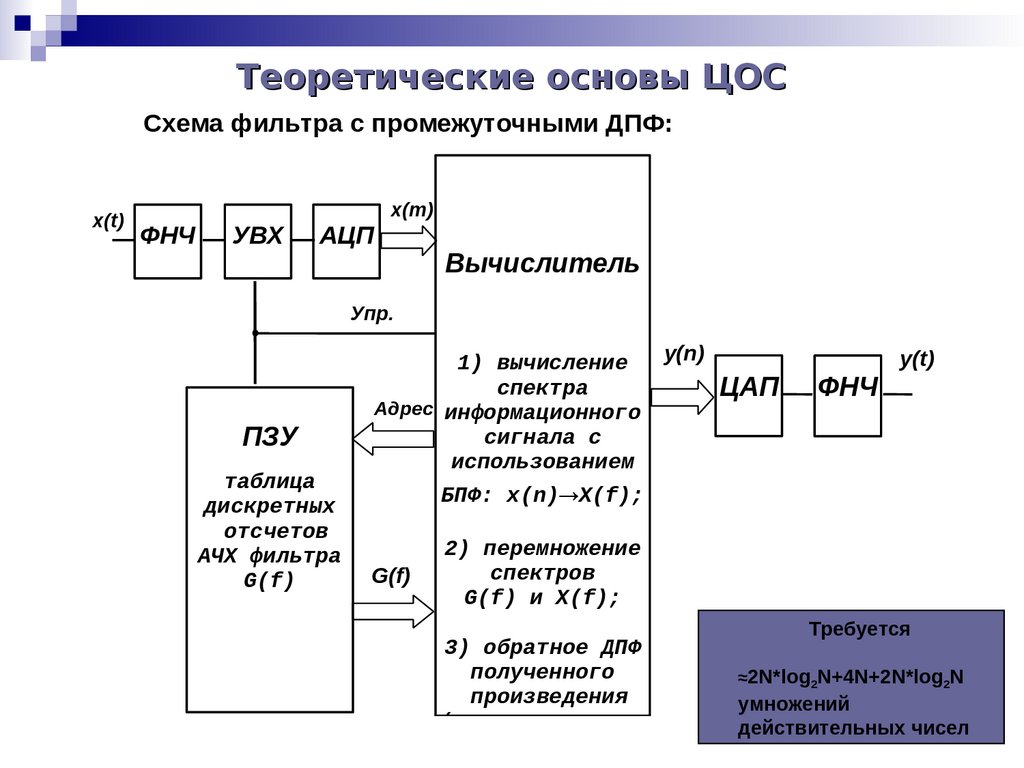

Схема фильтра с промежуточными ДПФ:x(N/2)t)

x(N/2)m)

ФНЧ

УВХ

АЦП

Вычислитель

Упр.

ПЗУ

таблица

дискретных

отсчетов

АЧХ фильтра

G(f)

1) вычисление

спектра

Адрес информационного

сигнала с

использованием

y(N/2)n)

y(N/2)t)

ЦАП

ФНЧ

БПФ: x(n)→X(f);

G(N/2)f)

2) перемножение

спектров

G(f) и X(f);

3) обратное ДПФ

полученного

произведения

(с использованием

Требуется

≈2N*log2N+4N+2N*log2N

умножений

действительных чисел

76. Теоретические основы ЦОС

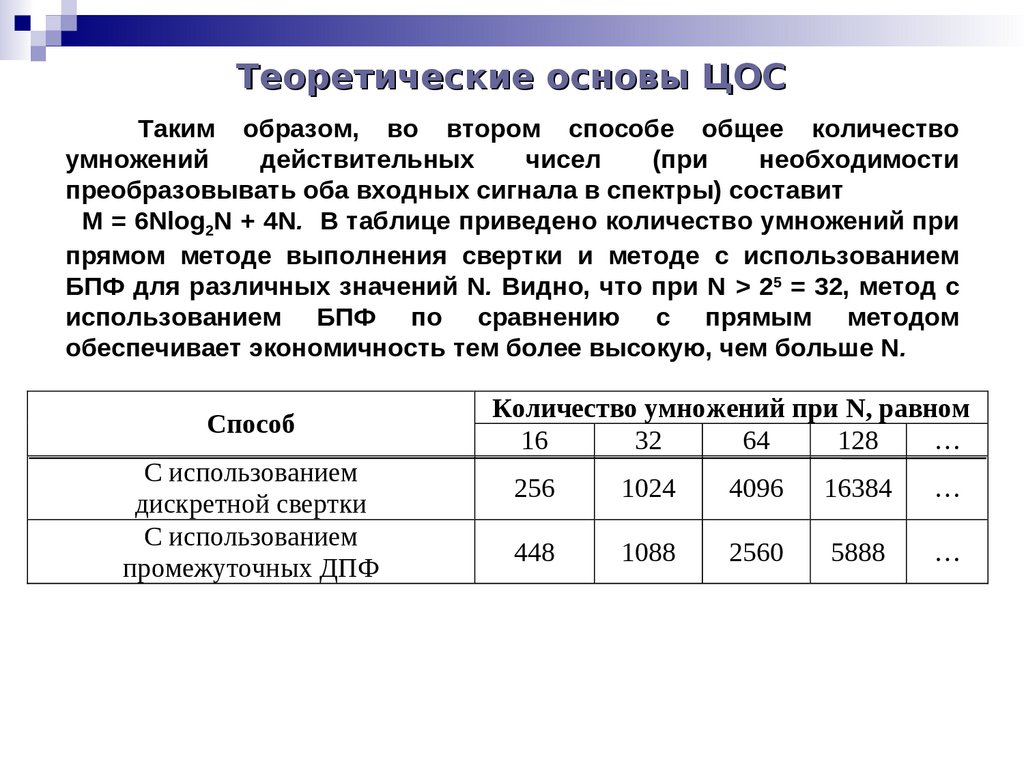

Таким образом, во втором способе общее количествоумножений

действительных

чисел

(при

необходимости

преобразовывать оба входных сигнала в спектры) составит

М = 6Nlog2N + 4N. В таблице приведено количество умножений при

прямом методе выполнения свертки и методе с использованием

БПФ для различных значений N. Видно, что при N > 25 = 32, метод с

использованием БПФ по сравнению с прямым методом

обеспечивает экономичность тем более высокую, чем больше N.

Способ

С использованием

дискретной свертки

С использованием

промежуточных ДПФ

Количество умножений при N, равном

16

32

64

128

…

256

1024

4096

16384

…

448

1088

2560

5888

…

77. Тэарэтычныя асновы ЛАС

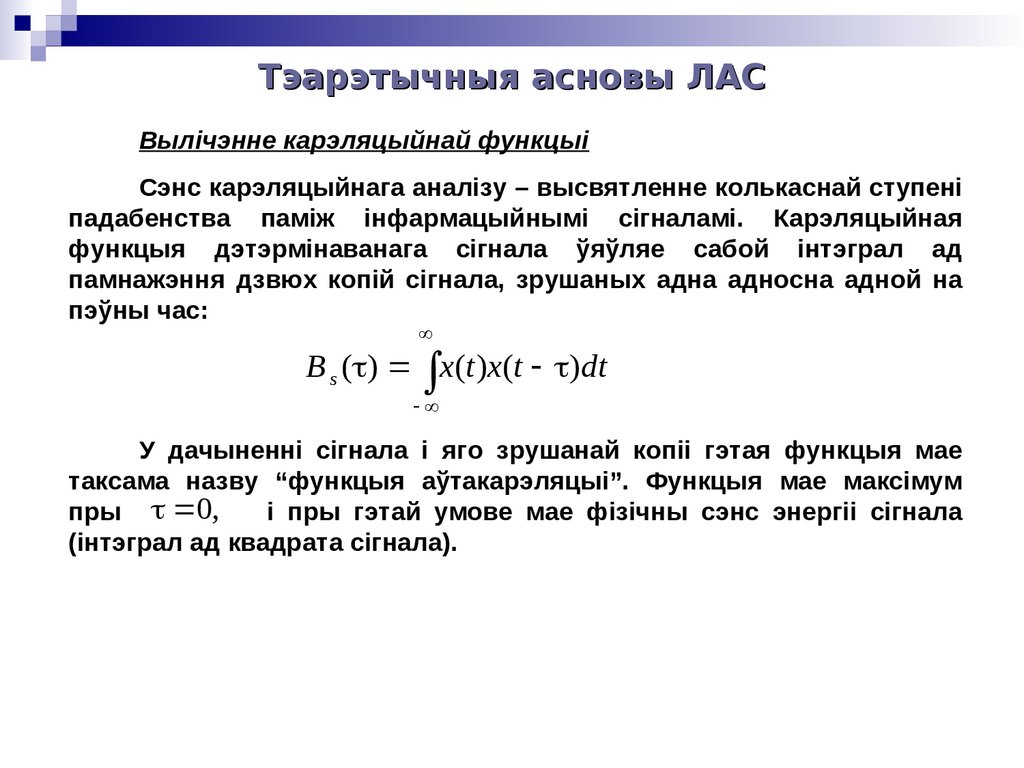

Вылічэнне карэляцыйнай функцыіСэнс карэляцыйнага аналізу – высвятленне колькаснай ступені

падабенства паміж інфармацыйнымі сігналамі. Карэляцыйная

функцыя дэтэрмінаванага сігнала ўяўляе сабой інтэграл ад

памнажэння дзвюх копій сігнала, зрушаных адна адносна адной на

пэўны час:

B s ( ) x(t )x(t )dt

У дачыненні сігнала і яго зрушанай копіі гэтая функцыя мае

таксама назву “функцыя аўтакарэляцыі”. Функцыя мае максімум

пры 0,

і пры гэтай умове мае фізічны сэнс энергіі сігнала

(інтэграл ад квадрата сігнала).

78. Тэарэтычныя асновы ЛАС

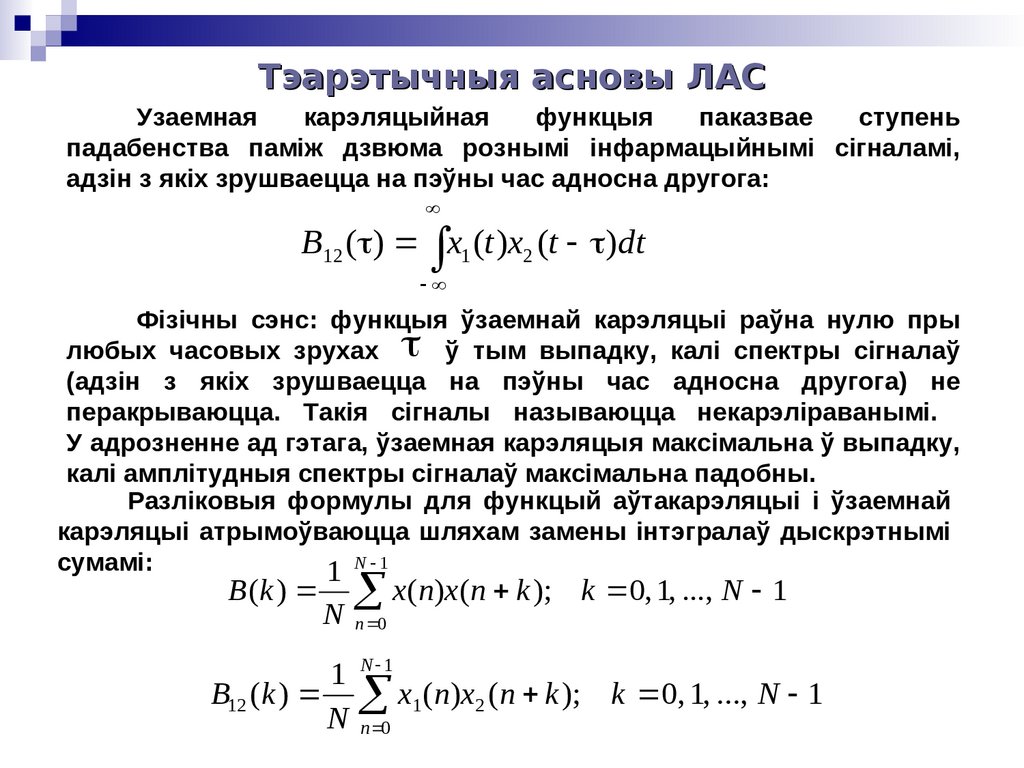

Узаемнаякарэляцыйная

функцыя

паказвае

ступень

падабенства паміж дзвюма рознымі інфармацыйнымі сігналамі,

адзін з якіх зрушваецца на пэўны час адносна другога:

B12 ( ) x1 (t )x2 (t )dt

Фізічны сэнс: функцыя ўзаемнай карэляцыі раўна нулю пры

любых часовых зрухах

ў тым выпадку, калі спектры сігналаў

(адзін з якіх зрушваецца на пэўны час адносна другога) не

перакрываюцца. Такія сігналы называюцца некарэліраванымі.

У адрозненне ад гэтага, ўзаемная карэляцыя максімальна ў выпадку,

калі амплітудныя спектры сігналаў максімальна падобны.

Разліковыя формулы для функцый аўтакарэляцыі і ўзаемнай

карэляцыі атрымоўваюцца шляхам замены інтэгралаў дыскрэтнымі

сумамі:

1 N 1

B(k )

x(n)x(n k );

N

k 0, 1, ..., N 1

n 0

1

B12 (k )

N

N 1

x (n)x (n k );

1

n 0

2

k 0, 1, ..., N 1

79. Особенности и характеристики ЦСП

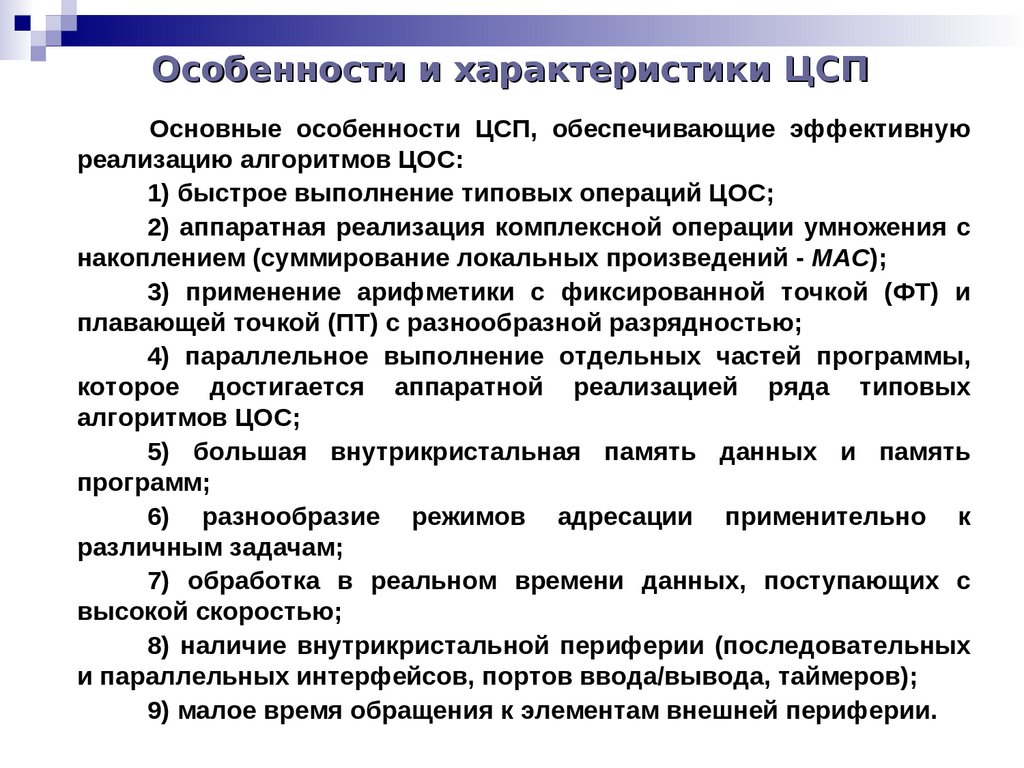

Основные особенности ЦСП, обеспечивающие эффективнуюреализацию алгоритмов ЦОС:

1) быстрое выполнение типовых операций ЦОС;

2) аппаратная реализация комплексной операции умножения с

накоплением (суммирование локальных произведений - МАС);

3) применение арифметики с фиксированной точкой (ФТ) и

плавающей точкой (ПТ) с разнообразной разрядностью;

4) параллельное выполнение отдельных частей программы,

которое достигается аппаратной реализацией ряда типовых

алгоритмов ЦОС;

5) большая внутрикристальная память данных и память

программ;

6) разнообразие режимов адресации применительно к

различным задачам;

7) обработка в реальном времени данных, поступающих с

высокой скоростью;

8) наличие внутрикристальной периферии (последовательных

и параллельных интерфейсов, портов ввода/вывода, таймеров);

9) малое время обращения к элементам внешней периферии.

80. Особенности и характеристики ЦСП

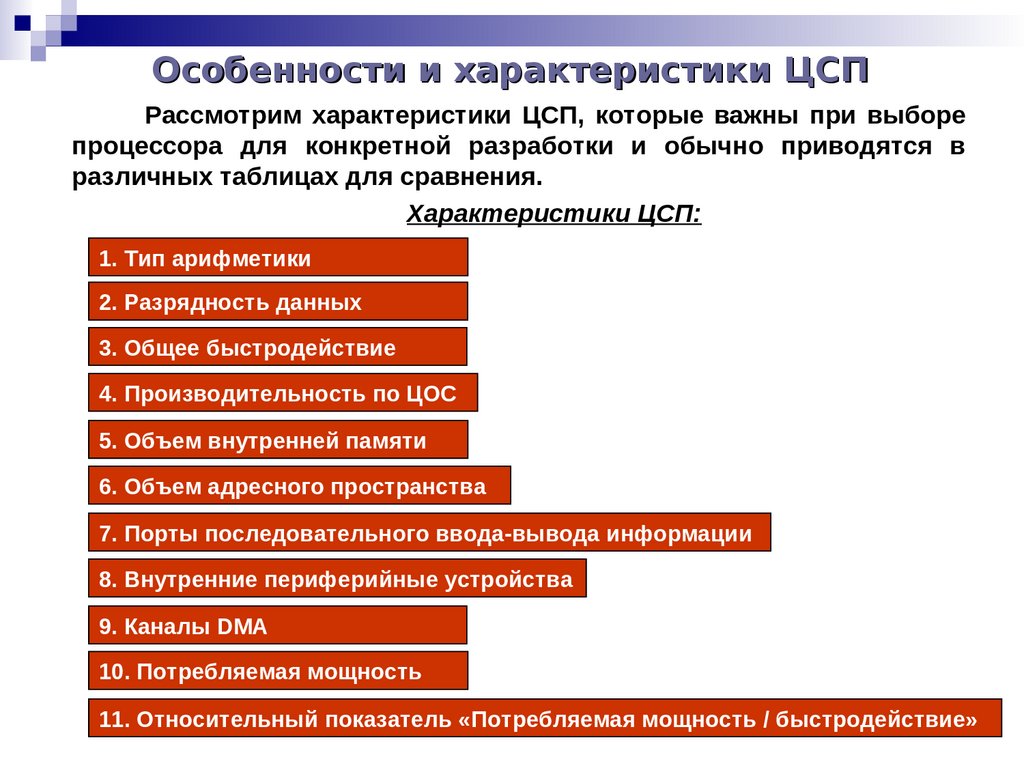

Рассмотрим характеристики ЦСП, которые важны при выборепроцессора для конкретной разработки и обычно приводятся в

различных таблицах для сравнения.

Характеристики ЦСП:

1. Тип арифметики

2. Разрядность данных

3. Общее быстродействие

4. Производительность по ЦОС

5. Объем внутренней памяти

6. Объем адресного пространства

7. Порты последовательного ввода-вывода информации

8. Внутренние периферийные устройства

9. Каналы DMA

10. Потребляемая мощность

11. Относительный показатель «Потребляемая мощность / быстродействие»

81. Особенности и характеристики ЦСП

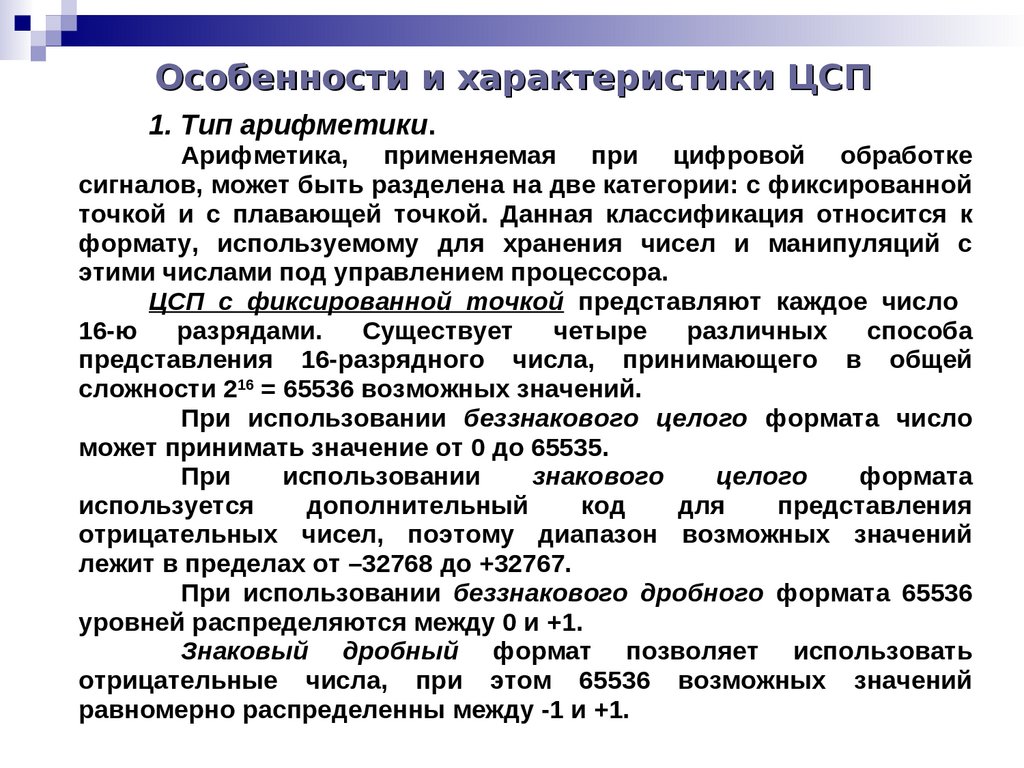

1. Тип арифметики.Арифметика, применяемая при цифровой обработке

сигналов, может быть разделена на две категории: с фиксированной

точкой и с плавающей точкой. Данная классификация относится к

формату, используемому для хранения чисел и манипуляций с

этими числами под управлением процессора.

ЦСП с фиксированной точкой представляют каждое число

16-ю

разрядами.

Существует

четыре

различных

способа

представления 16-разрядного числа, принимающего в общей

сложности 216 = 65536 возможных значений.

При использовании беззнакового целого формата число

может принимать значение от 0 до 65535.

При

использовании

знакового

целого

формата

используется

дополнительный

код

для

представления

отрицательных чисел, поэтому диапазон возможных значений

лежит в пределах от –32768 до +32767.

При использовании беззнакового дробного формата 65536

уровней распределяются между 0 и +1.

Знаковый дробный формат позволяет использовать

отрицательные числа, при этом 65536 возможных значений

равномерно распределенны между -1 и +1.

82. Особенности и характеристики ЦСП

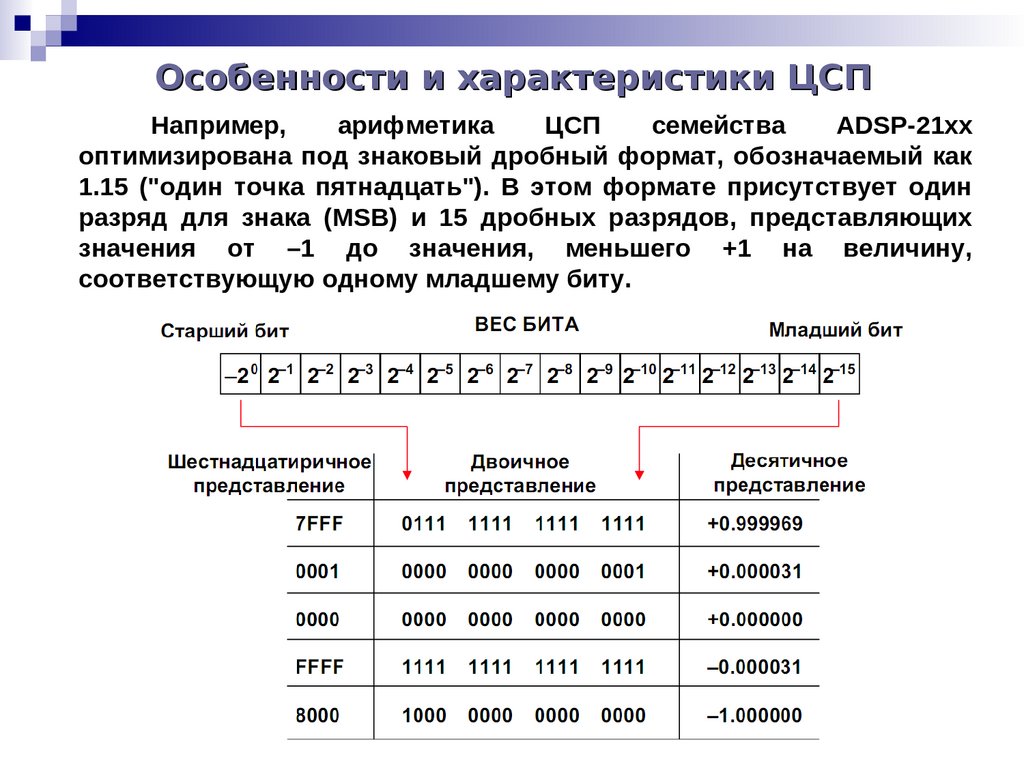

Например,арифметика

ЦСП

семейства

ADSP-21xx

оптимизирована под знаковый дробный формат, обозначаемый как

1.15 ("один точка пятнадцать"). В этом формате присутствует один

разряд для знака (MSB) и 15 дробных разрядов, представляющих

значения от –1 до значения, меньшего +1 на величину,

соответствующую одному младшему биту.

83. Особенности и характеристики ЦСП

Этот подход может быть обобщенно обозначен, как "m.Q", гдеm - число битов слева от точки, отделяющей дробную часть, а

Q - число битов справа от точки. Например, беззнаковое целое

число представляется как формат 16.0. Для большинства

приложений цифровой обработки сигналов предполагается

использование дробных форматов числа. Дробные числа имеют

превосходство, которое заключается в том, что результат

умножения двух дробных чисел меньше каждого из сомножителей.

ЦСП с плавающей точкой обычно используют минимум

32 разряда для представления каждого числа. Это приводит к

возможности

представления

гораздо

большего

количества

различных значений, чем в 16-разрядном ЦСП с фиксированной

точкой, а точнее 232 = 4294967296. Плавающая точка существенно

увеличивает диапазон значений, который может быть представлен в

рамках 32-разрядного представления. Наиболее распространенный

стандарт с плавающей точкой – стандарт ANSm/mE) и E) и E) и 754-1985, где

самое большое и самое маленькое возможные числа равны

±3,4×1038 и ±1,2×10–38 соответственно.

84. Особенности и характеристики ЦСП

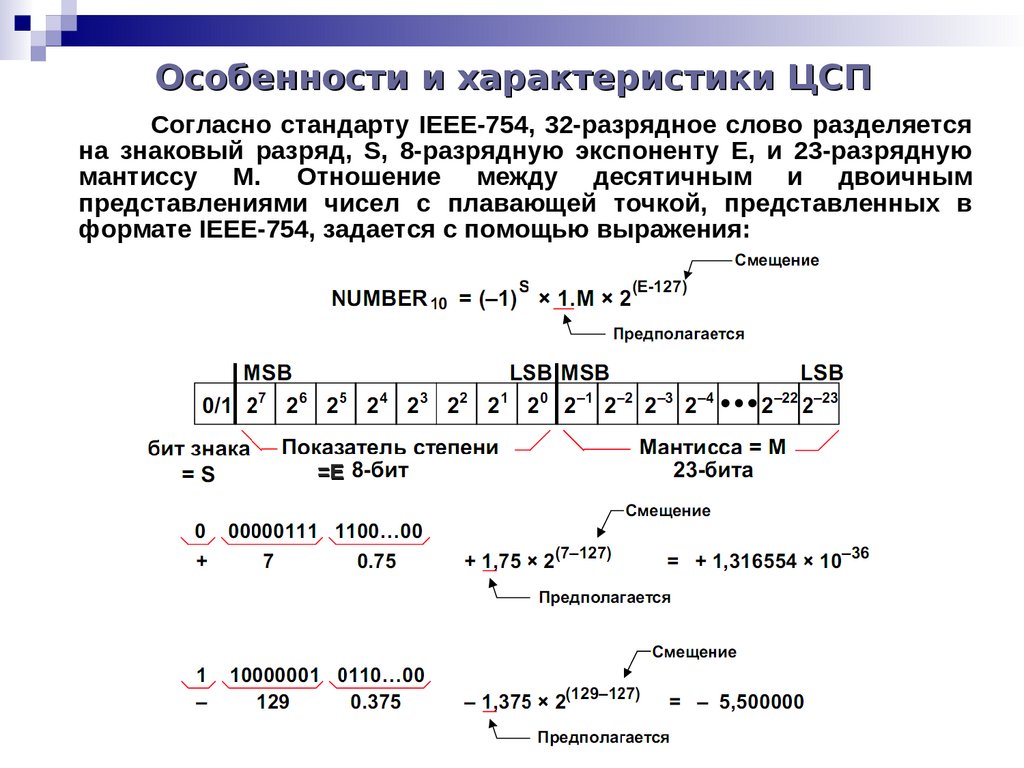

Согласно стандарту mE) и E) и E) и -754, 32-разрядное слово разделяетсяна знаковый разряд, S, 8-разрядную экспоненту Е, и 23-разрядную

мантиссу М. Отношение между десятичным и двоичным

представлениями чисел с плавающей точкой, представленных в

формате mE) и E) и E) и -754, задается с помощью выражения:

=E) и

85. Особенности и характеристики ЦСП

Преимущества арифметики с плавающей точкой:- более широкий динамический диапазон, обеспечиваемый

32-разрядной арифметикой с плавающей точкой;

- процессор с плавающей точкой более прост в

программировании, т.к. минимизируются проблемы, связанные с

фиксированной точкой (переполнение, потеря разрядов,

масштабирование данных, ошибки округления);

- затраты времени на разработку программного обеспечения

при использовании ЦСП с плавающей точкой значительно

сокращаются.

Недостаток: ЦСП с плавающей точкой могут

значительно выше, чем ЦСП с фиксированной точкой.

стоить

86. Особенности и характеристики ЦСП

2. Разрядность данных. Все обычные ЦСП с плавающейточкой используют слово данных длиной в 32 бита. Для ЦСП с

фиксированной точкой обычный размер слова данных - 16 бит.

87. Особенности и характеристики ЦСП

3. Общее быстродействие. Одним из самых важныхпараметров с точки зрения конкретных применений является

быстродействие процессора. Для характеристики быстродействия

ЦСП анализируют параметры: тактовая частота, время командного

цикла, MmPS, MOPS (MFLOPS).

3.1. Тактовая частота работы процессора и связанное с ней время командного цикла. Как

правило, при описаниях процессоров обычно указывается внешняя тактовая частота, подаваемая на

процессор. Она может отличаться от внутренней частоты работы из-за наличия системы деления или

умножения частоты. Для последних процессоров, в которых внешняя частота может изменяться в

широких пределах, чаще указывают внутреннюю частоту работы процессора.

3.2. Время командного цикла связано с внутренней частотой работы процессора. Так как

отдельная операция в процессоре может выполняться как за несколько циклов, так и за один, время

командного цикла является самой неоднозначной характеристикой быстродействия процессора. К тому

же, в некоторых процессорах используется параллельное выполнение команд и параллельная работа

нескольких операционных модулей. Поэтому время цикла полностью не характеризует реально

выполняемую процессором работу.

3.3. Количество миллионов команд, выполняемых за секунду MIPS (N/2)Million instructions per

second). В ЦСП используются различные команды, в том числе комбинированные, в соответствии с

которыми одновременно выполняется несколько операций. Кроме того, существуют процессоры с

несколькими АЛУ, в которых применяются длинные команды. Таким образом, одной команде в разных

процессорах соответствует различная выполняемая работа. Поэтому характеристика MIPS неоднозначно

определяет быстродействие процессора.

3.4. Количество миллионов операций за секунду MOPS (Millions operations per second) или

Количество миллионов операций с плавающей точкой за секунду MFLOPS (Millions of floating-point

operations per second). Эта характеристика учитывает выполнение параллельных команд и

одновременную работу нескольких операционных модулей. С учетом того, что к выполняемым операциям

относят и выборки команд, и запись в память полученных результатов, MOPS неточно характеризует

реальное быстродействие.

88. Особенности и характеристики ЦСП

4.Производительность

по

ЦОС.

Возможный путь

определения производительности состоит в выборе единой

простой операции для целей сравнения. Для прикладных программ

ЦОС естественным является выбор операции умножения с

накоплением MAC, которая является основной для алгоритмов ЦОС.

Однако следует учесть, что в данных алгоритмах применяются и

другие операции, помимо этой.

89. Особенности и характеристики ЦСП

Наиболее распространенные алгоритмы, выполняемые ЦСП:дискретное преобразование Фурье:

1

A( k )

N

N 1

a n e

j

2

kn

N

n 0

дискретная свёртка:

N 1

y n x m g n m

m 0

фильтр с конечной импульсной характеристикой:

M

y n ak x n k

m 0

фильтр с бесконечной импульсной характеристикой:

M

N

k 0

k 1

y n ak x n k bk y n k

90. Особенности и характеристики ЦСП

Видно, что базовым элементом типовых операций ЦСПявляется MAC – умножение с накоплением:

M

y data i coeff i

i 0

Стандартный алгоритм, выполняемый на обыкновенном

процессоре, например, на Pentium, следующий:

1. Установка Указателя1 на data[0];

2. Установка Указателя2 на coeff[0];

3. Чтение data[i] в АЛУ;

4. Чтение coeff[i] в АЛУ;

5. Умножение data[i] на coeff[i];

6. Сложение результата i-го умножения с накопленной суммой;

7. Инкремент Указателя1;

8. Инкремент Указателя2;

9. Инкремент i;

10. Если i<=M, переход к п.3 и цикл.

91. Особенности и характеристики ЦСП

Шаги с 3-го по 8-й (6 элементарных операций) являютсябазовой операцией MAC и выполняются ЦСП за один машинный

цикл. Например, ЦСП TMS320F2812 фирмы Texas mnstruments

выполняет операцию MAC для M=3 за 10 машинных циклов, что

соответствует времени 66 нс при тактовой частоте 150 МГц.

92. Особенности и характеристики ЦСП

5. Объем внутренней памяти (ROM, RAM, Flash, cash).Эти характеристики определяют многие параметры и возможности

разрабатываемой системы. Наличие памяти типа ПЗУ (ROM),

программируемого при изготовлении процессора, позволяет

заказывать ЦСП с записанной программой работы системы. Память

типа РПЗУ (flash) позволяет неоднократно перезаписывать

программу и данные в процессоре, в том числе и непосредственно

на изготовленной плате системы. Объем и разновидности

внутренней ОЗУ определяют возможности построения системы в

отношении хранения массивов данных без использования внешней

памяти.

93. Особенности и характеристики ЦСП

6. Объем адресного пространства памяти определяетсяразрядностью шины адреса и характеризует возможный общий

объем памяти, используемой в системе.

7.

Порты

последовательного

ввода-вывода

информации. Их количество и разновидности определяют

возможности системы с

внешними устройствами.

8.

Внутренние

точки

зрения

периферийные

связи

с

различными

устройства.

В

процессорах существуют периферийные устройства, которые

условно можно разделить на устройства общего применения (типа

таймеров) и проблемно-ориентированные устройства (АЦП,

кодеки, компандеры, экспандеры, сопроцессоры и т.д.). Последние

облегчают построение специализированных цифровых систем,

например, обработки звука.

9. Каналы DMA (Direct Memory Access). Прямой доступ к

памяти позволяет общаться с внешними устройствами, в том числе

записывать отсчеты входного сигнала (выводить полученные

отсчеты выходного сигнала) без использования ресурсов и затрат

времени. Наличие нескольких каналов DMA облегчает построение

высокопроизводительных систем ЦОС.

94. Особенности и характеристики ЦСП

10.Потребляемая

мощность.

Это

характеристика

процессора, особенно важная при построении переносимых систем

с батарейным питанием. Потребляемая мощность существенно

зависит от выполняемой программы и, как правило, не приводится.

Многие производители предлагают низковольтные (3,3 В, 2,5 В

или 1,8 В) версии процессоров, которые потребляют гораздо

меньшую мощность, чем 5-вольтовые эквиваленты при той же

производительности. Процессор может работать в различных

режимах, в том числе в режиме ожидания (Idle), при нахождении в

котором ряд внутренних модулей отключается и не потребляет

энергии.

11.

Относительный

показатель

«Потребляемая

мощность / быстродействие». Свойством любых электронных

устройств, в том числе и ЦСП, является повышение потребления

мощности при увеличении быстродействия. Поэтому используют

удельные относительные показатели потребления мощности,

отнесенные к единице быстродействия. Иногда в такие удельные

показатели включают и стоимость процессора.

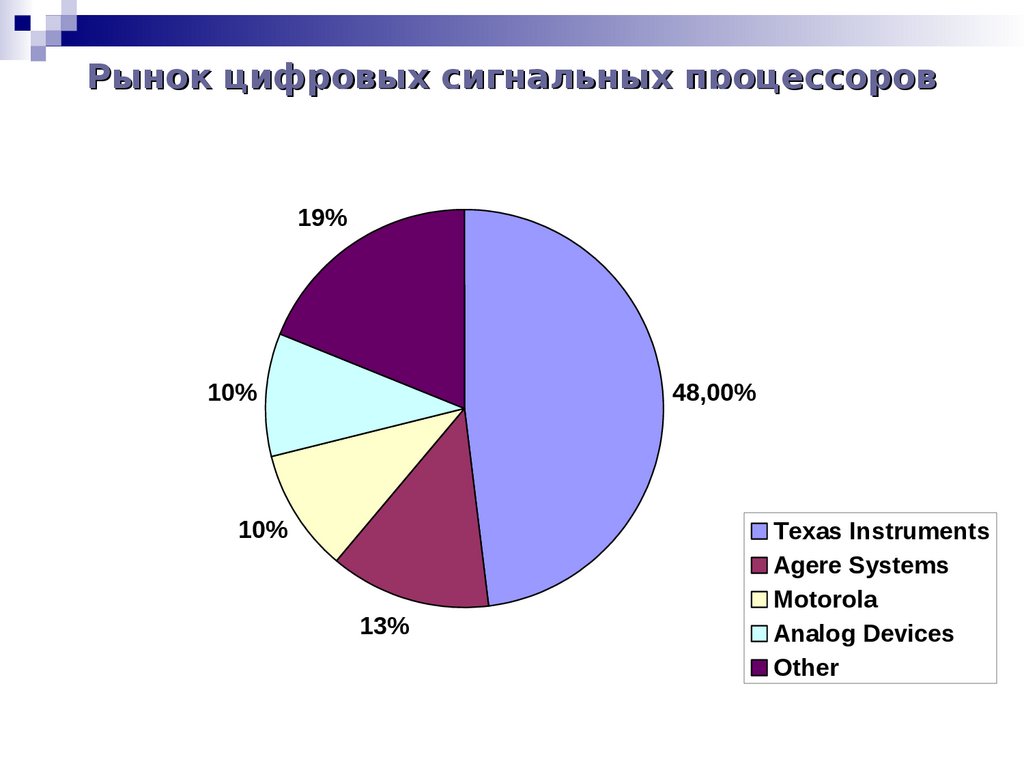

95. Рынок цифровых сигнальных процессоров

АПРАВПРDSP Market Share 2003

АПРАВПР

source : Forward Concepts, 2004

АПР

19%

10%

48,00%

10%

13%

Texas mnstruments

Agere Systems

Motorola

Analog Devices

Other

96. Рынок цифровых сигнальных процессоров (2013 г.)

Компании-лидерырынка

1

2

3

4

5

6

7

8

9

10

Company Name

Texas mnstruments

Freescale

Semiconductor

Analog Devices

Philips Semiconductors

Agere Systems

Toshiba

DSP Group

NE) и C E) и lectronics

Fujitsu

mntersil

Other Companies

Total

Доля рынка

DSP

54,3%

14,1%

8,0%

7,5%

7,3%

4,9%

2,2%

0,6%

0,4%

0,3%

0,5%

100,0%

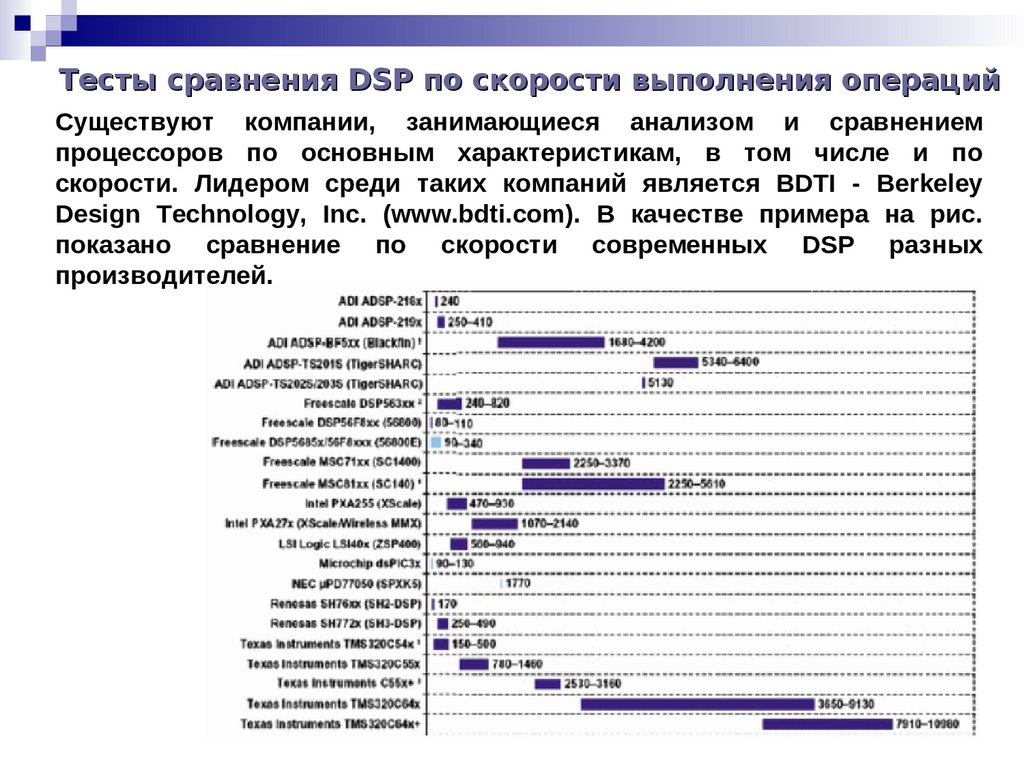

97. Тесты сравнения DSP по скорости выполнения операций

Существуют компании, занимающиеся анализом и сравнениемпроцессоров по основным характеристикам, в том числе и по

скорости. Лидером среди таких компаний является BDTm - Berkeley

Design Technology, mnc. (www.bdti.com). В качестве примера на рис.

показано сравнение по скорости современных DSP разных

производителей.

98. Выводы и рекомендации по выбору типа DSP

Как показано ранее, правильный выбор DSP сильно зависит отприложения: процессор может хорошо подходить для одних

приложений, но абсолютно не подходить для других. При выборе

процессора нужно определить самые важные в конкретном случае

характеристики и расставить их по степени важности. Затем в

соответствии с этими критериями отобрать возможных кандидатов и,

наконец, выбрать из подходящих лучший, обращая внимание на

дополнительные,

не

критичные

характеристики.

При

этом

целесообразно воспользоваться оценкой характеристик процессоров,

производимой какой-либо авторитетной компанией (например, BTDm).

Следует помнить, что BTDm производит оценку DSP не только по

быстродействию, но и по другим критериям: эффективности памяти,

энергопотреблению и т.д.

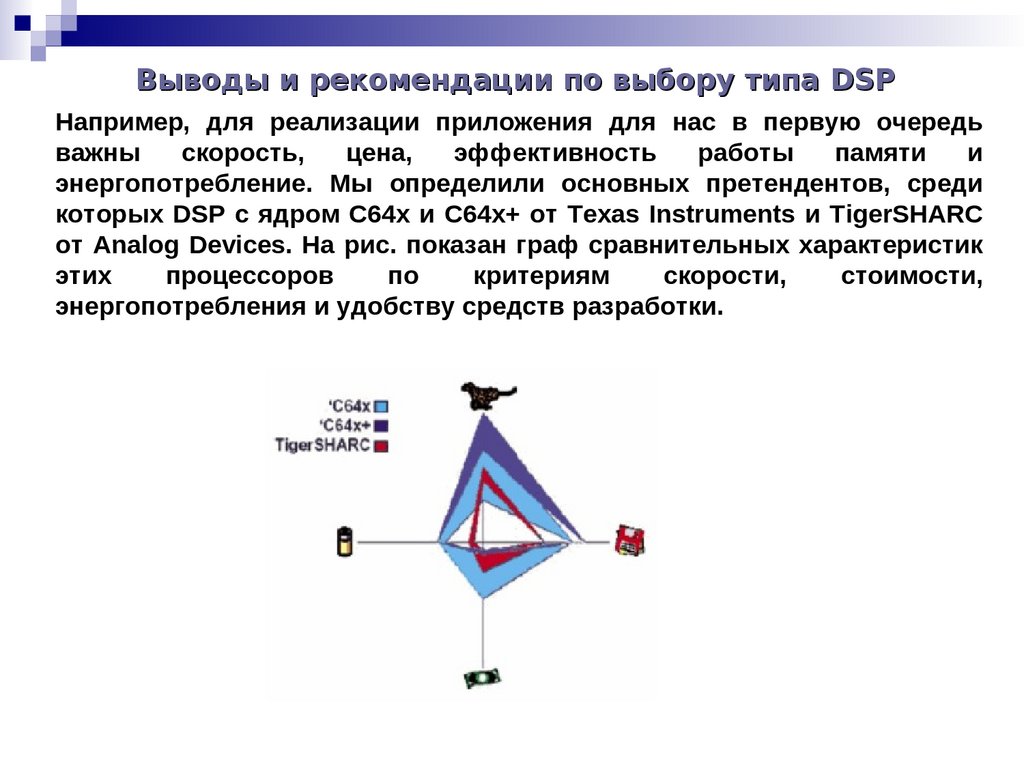

99. Выводы и рекомендации по выбору типа DSP

Например, для реализации приложения для нас в первую очередьважны

скорость,

цена,

эффективность

работы

памяти

и

энергопотребление. Мы определили основных претендентов, среди

которых DSP с ядром C64x и C64x+ от Texas mnstruments и TigerSHARC

от Analog Devices. На рис. показан граф сравнительных характеристик

этих

процессоров

по

критериям

скорости,

стоимости,

энергопотребления и удобству средств разработки.

100. Выводы и рекомендации по выбору типа DSP

Приоритеты. Если нам в первую очередь необходима высокаяскорость и низкая цена, следует выбрать DSP от Texas mnstruments.

Если мы конструируем мобильное устройство и нам нужно низкое

энергопотребление, причем мы готовы пожертвовать скоростью,

целесообразно выбрать DSP от Analog Devices. Не исключена

вероятность того, что выбранные процессоры окажутся очень близки

по ключевым параметрам. В этом случае выбор будет определяться

некритичными характеристиками: доступностью средств отладки,

предыдущим опытом разработчика, доступностью компонентов и т.д.

Тщательный выбор цифрового сигнального процессора еще на

начальном этапе разработки может помочь избавиться от излишних

затрат, связанных с выбором неподходящего DSP, и сократить как

время разработки в целом, так и время и средства на выявление

ошибок.

101. Цифровые сигнальные процессоры Texas Instruments

Семейства цифровых сигнальных процессоров имикроконтроллеров и, оптимизированных под задачи ЦОС,

выпускаемые Texas mnstruments

MSP430

Lowest Power

MCU

C2000™ DSP C5000™ DSP C6000™ DSP

DaVinci™

DSP

Digital Control

Personal DSP

DSP

Video

DSP

mnfrastructure

DSP

Портативные

Системы

Портативная

Системы

Системы

измерительные

управления

бытовая

защиты

видеообработк

устройства с электропривода

техника,

информации,

и,

малым

ми и электро- аудиосистемы

обработки

видеонаблюден

потреблением оборудованием,

изображений и

ия

измерения и

видео,

видеотелефони

автоматики

телекоммуника

и, IPции

контроллеры,

102. Цифровые сигнальные процессоры Texas Instruments

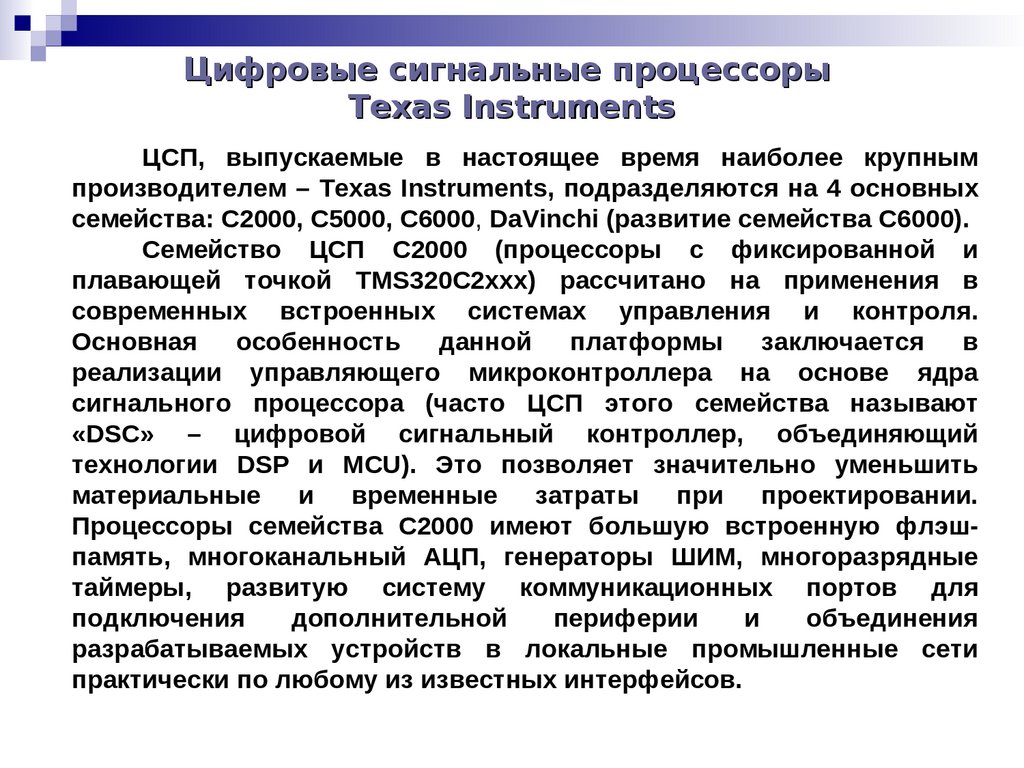

ЦСП, выпускаемые в настоящее время наиболее крупнымпроизводителем – Texas mnstruments, подразделяются на 4 основных

семейства: C2000, C5000, С6000, DaVinchi (развитие семейства С6000).

Семейство ЦСП C2000 (процессоры с фиксированной и

плавающей точкой TMS320C2xxx) рассчитано на применения в

современных встроенных системах управления и контроля.

Основная

особенность

данной

платформы заключается

в

реализации управляющего микроконтроллера на основе ядра

сигнального процессора (часто ЦCП этого семейства называют

«DSC» – цифровой сигнальный контроллер, объединяющий

технологии DSP и MCU). Это позволяет значительно уменьшить

материальные и временные затраты при проектировании.

Процессоры семейства C2000 имеют большую встроенную флэшпамять, многоканальный АЦП, генераторы ШИМ, многоразрядные

таймеры, развитую систему коммуникационных портов для

подключения

дополнительной

периферии

и

объединения

разрабатываемых устройств в локальные промышленные сети

практически по любому из известных интерфейсов.

103.

С2000: Области примененияЦифровое управление двигателями

Возобновляемая энергия

Электроинст

ру-мент

Преобразователи энергии ветра

Электровелосипед

Бытовая

техника

Преобразователи энергии солнца

Источники питанияПреобразовател

и постоянного

тока

Промышленные

приводы &

устройства

управления

C200

0

Светодиодное

уличное

освещение

Источники

бесперебойног

о питания

Выпрямители

еременного/постоянного

тока

Авто HID

Радары /

предотвращени

е столкновений

Гибридный электрический

транспорт

Электрический

усилитель руля

Автомобилестроение

Освещение

Коммуникация

по силовым

линиям

RFID

Считыватели

Лазерная

локация

Medical

Oxygen

Concentrator

s

Светодиодна

я ТВ

подсветка

Оптически

е сети

Измерение и управление

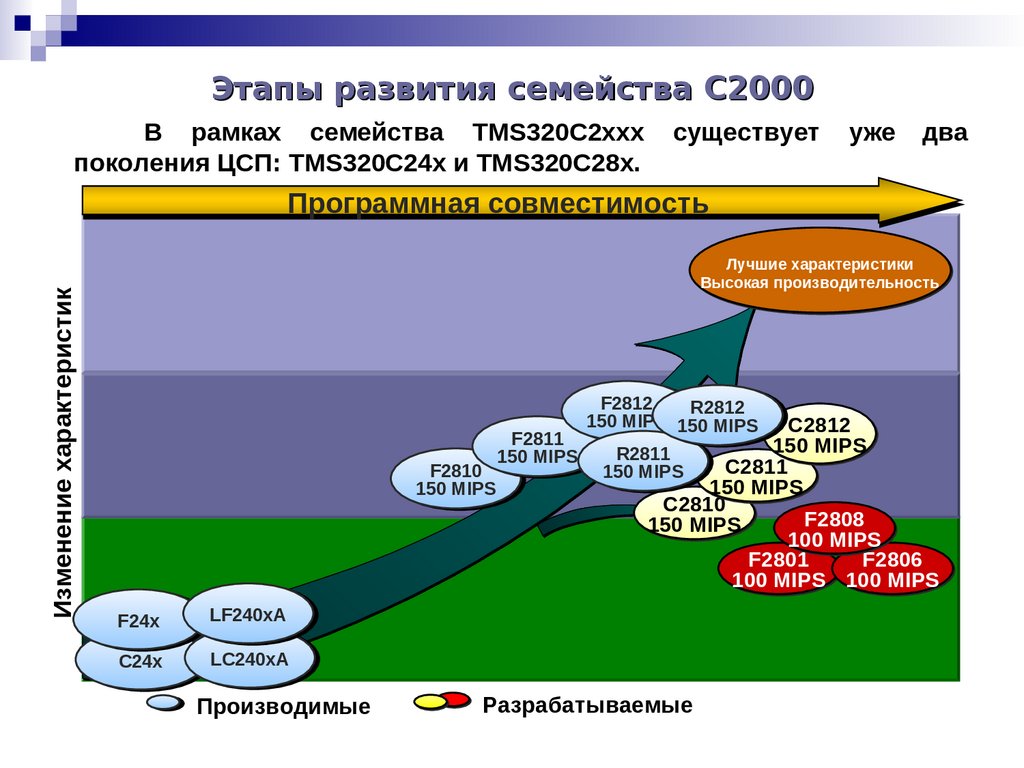

104. Этапы развития семейства C2000

В рамках семейства TMS320C2xxxпоколения ЦСП: TMS320C24x и TMS320C28x.

существует

уже

два

Изменение характеристик

Программная совместимость

Лучшие характеристики

Высокая производительность

F2812

F2812

R2812

R2812

150

150 MmPS

MmPS 150

150 MmPS

MmPS C2812

F2811

F2811

150 MmPS

R2811

R2811

150

150 MmPS

MmPS

C2811

F2810

150

F2810

150 MmPS

MmPS

150

MmPS

150

150 MmPS

MmPS

C2810

150 MmPS

F2808

100 MmPS

F2801

F2806

100 MmPS 100 MmPS

F24x

F24x

LF240xA

LF240xA

C24x

C24x

LC240xA

LC240xA

Производимые

Разрабатываемые

105.

Семейство С28: Выпускаемые серии иосновные направления развития

Серийно

выпускаемые

Образцы

Перспективы

Фиксированная

точка

(100-176 выводов),

≈ 10-20$ F2823

x

60 – 150 MГц

F281x

32 – 512 Кб Flash

3Ph PWM/QE) и P

F280x

12-битный АЦП,

2 схемы выборки

/хранения, (до 12.5 MSPS)

• CAN, McBSP

• UART, SPm

серия DelfinoTM

(176-256 выводов),

(Плавающая точка)

≈ 8-18$

C2834

x

F2833

x

• Высокая

производительность

• Богатая периферия

• 200-300 MГц

• 196-516 Кб ОЗУ

• АЦП с внешней

синхронизацией

• Низкое энергопотребление

в активном режиме

• 100-150 MГц

• 128-512 Кб

Flash

• 52-68 Кб ОЗУ

серия PiccoloTM

(38-80 выводов),

Будущ

ие

≈ 2-6$

F2803

x

F2802

x

• 40-60 MГц

• 16-64 Кб Flash

• Аналоговые

компараторы

Будущ

ие

• Низкое

энергопотребление

• Малые габариты

• 60MГц

• CLA

• 32-128 Кб Flash

• CAN, LmN

Более 80 микросхем, совместимых по коду

106. Цифровые сигнальные процессоры Texas Instruments

Архитектура ЦСП с фиксированной точкой семейства C5000оптимизирована

по

соотношению

«производительность/

энергопотребление». Основная сфера применений - мобильные

телекоммуникационные

системы,

мультимедиа,

системы

шифрования данных и т.д. Процессоры семейства C5000 обладают

развитой периферией, включающей интерфейсы m2C, USB, набор

универсальных последовательных портов с возможностью

селекции каналов и буферизации, что позволяет настраивать их для

работы с внешними потоками данных всех используемых

стандартов.

107. Цифровые сигнальные процессоры Texas Instruments

ЦСП с плавающей точкой семейства С6000 построены на базеоригинальной архитектуры VelociTm, использующей преимущества

процессорной технологии VLmW (Very Long mnstruction Word или

инструкция с длинным командным словом). Семейство С6000

обладает

специальными

возможностями

для

обработки

информационных пакетов, создания аппаратуры широкополосного

доступа.

Ключевой

особенностью

семейства

C6000

является

быстродействие. Типичные применения – профессиональная

обработка аудио- и видеосигналов, цифровое радио (Software

defined radio, SDR).

Имеются следующие подсемейства:

- C64xx (с фиксированной точкой);

- C67xx (с плавающей точкой);

- C64x+ (семейство «DaVinci», оптимизированное для

видеообработки).

108. Основные характеристики ЦСП семейства С28x

Базовым ЦСП семейства C28x, обеспечивающим аналогоцифровое преобразование, реализацию алгоритмов цифровойфильтрации, широтно-импульсного модулятора, функций времени,

поддержку стандартных интерфейсов, является TMS320F2812.

ЦСП TMS320F28x обеспечивают производительность до

150 МГц на ядре центрального процессора. Для других серий ЦСП

семейства С28x (F280x, F281x, F2823x, F2833x, C2834x, F2802x,

F2803x), тактовая частота может находиться в пределах от 40 до 300

МГц.

Особенностью семейства C28x является возможность не

только разработки, но и отладки программного обеспечения на

языке высокого уровня C/C++, а также высокая эффективность

создаваемого компилятором кода.

TMS320F2812

109. Блок-схема ЦСП TMS320F2812

Шина программ (Program Bus)Секторизованная

ПЗУ

ОЗУ

Flashпамять

Менеджер

событий А

Менеджер

событий B

АЦП (12 бит)

Интерфейсы

PmE) и

Блок

регистров

(32 бит)

JTAG

реального

времени

Умножитель

(32x32 бит)

АЛУ

атомарных

функций

менеджер

прерываний

CPUШина регистров (Register Bus)

таймеры

Ядро (CPU)

Шина данных (Data Bus)

Порты вводавывода

(GPmO)

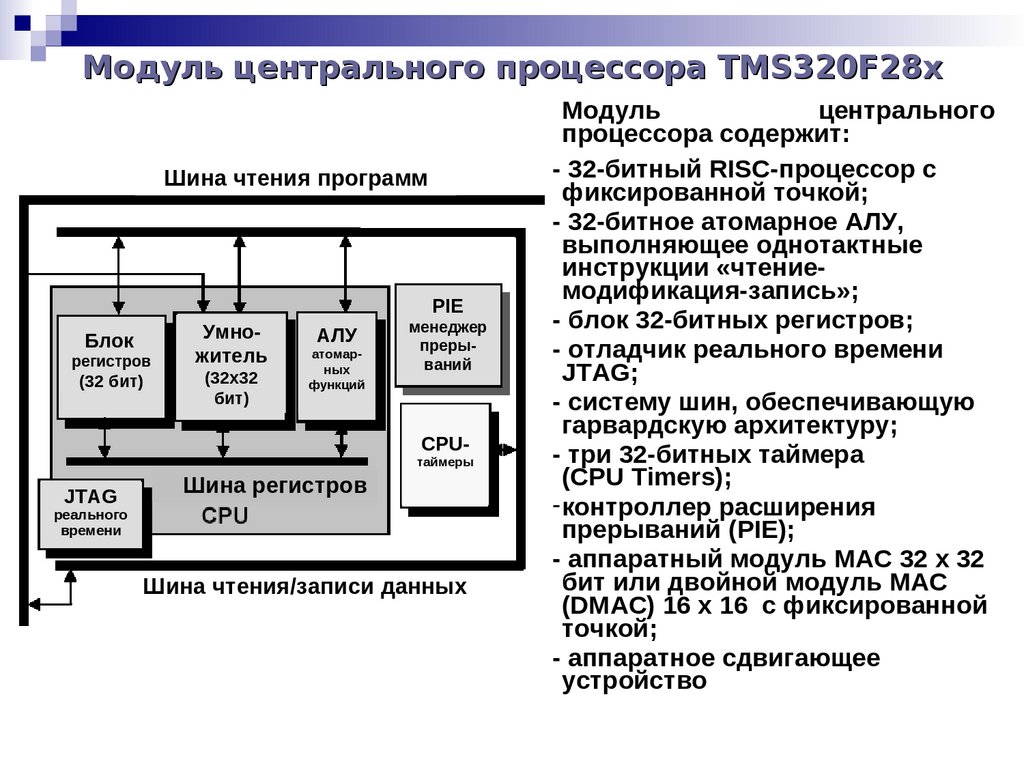

110. Модуль центрального процессора С28x

В целом укрупненная структура ЦСП TMS320F2812 может бытьпредставлена в виде 4-х блоков:

1.

2.

3.

4.

Система внутренних и внешних шин

Модуль центрального процессора

Модуль памяти

Модуль периферийных устройств

Для обеспечения возможности работы в одном машинном цикле с

двумя операндами, находящимися в памяти, ЦСП имеет гарвардскую

архитектуру, т.е. оснащен двумя независимыми шинами: шиной

программ (Program Bus) и шиной данных (Data Bus)

111. Основные характеристики ЦСП семейства С28x

ЦСП TMS320F2812 имеет высокопроизводительную статическуюКМОП-технологию. Максимальная тактовая частота ядра составляет

150 MГц (время цикла 6,67 нс). Напряжение питания: на ядре –

1,8 В @ 135 МГц; 1,9 В @ 150 МГц; на периферийных модулях – 3,3 В.

ЦСП поддерживает периферийное сканирование по стандарту JTAG

при высокой скорости передачи отладочной информации (до 20 Mбит/

с).

TMS320F2812 содержит в своем составе периферийный модуль

управления электроприводами – два модуля управления событиями

(E) и vent Manager - E) и VA, E) и VB), а также периферийные последовательные

порты:

- синхронный последовательный интерфейс SPm;

два

асинхронных

последовательных

порта

SCm,

использующих стандарт UART;

- контроллер сети CAN (Controller Area Network) с

расширенными возможностями;

- многоканальный буферизованный последовательный порт

(Multichannel Buffered Serial Port - McBSP).

Количество встроенных портов для различных ЦСП семейства

C28x, может быть различным. Некоторые ЦСП семейства C28x имеют в

своем составе, помимо перечисленных, также и интерфейсы m2C, LmN

(например, серии F2802x, F2803x).

112. Карта памяти ЦСП TMS320F2812

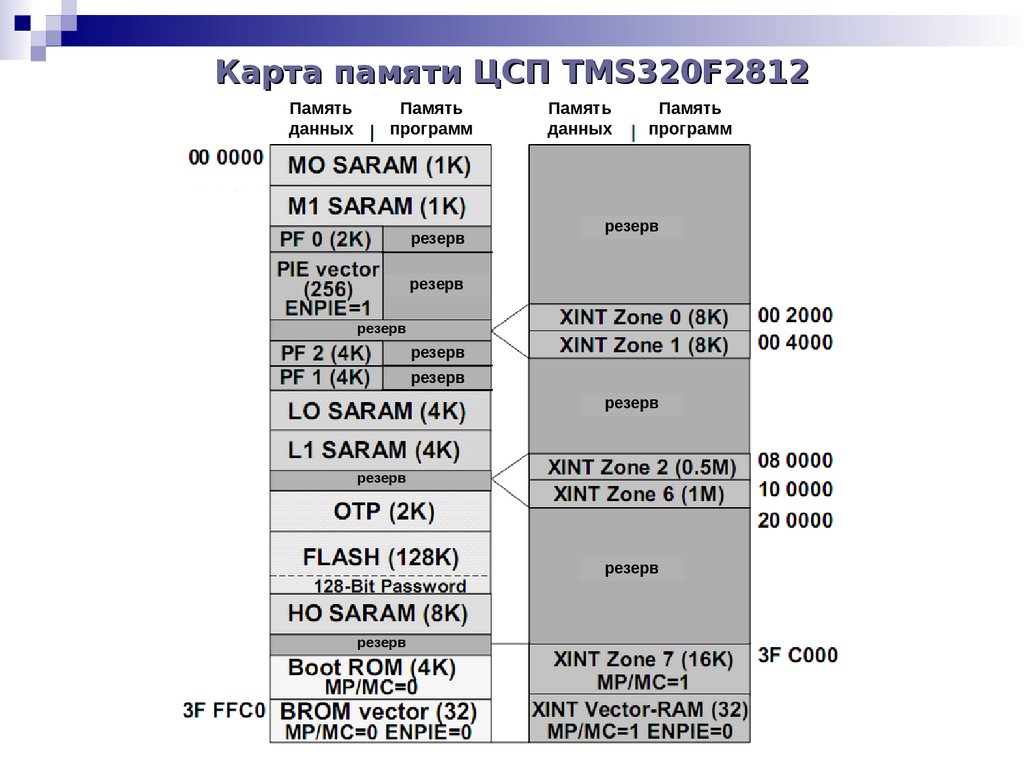

Памятьданных

Память

программ

резерв

Память

данных

Память

программ

резерв

резерв

резерв

резерв

резерв

резерв

резерв

резерв

резерв

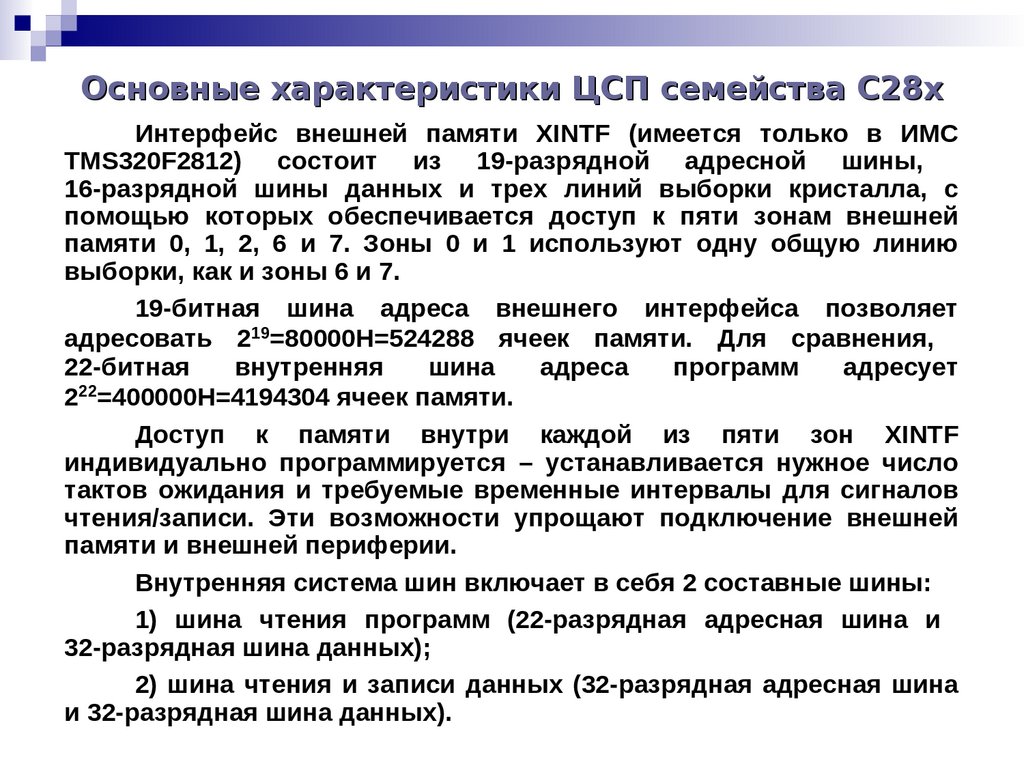

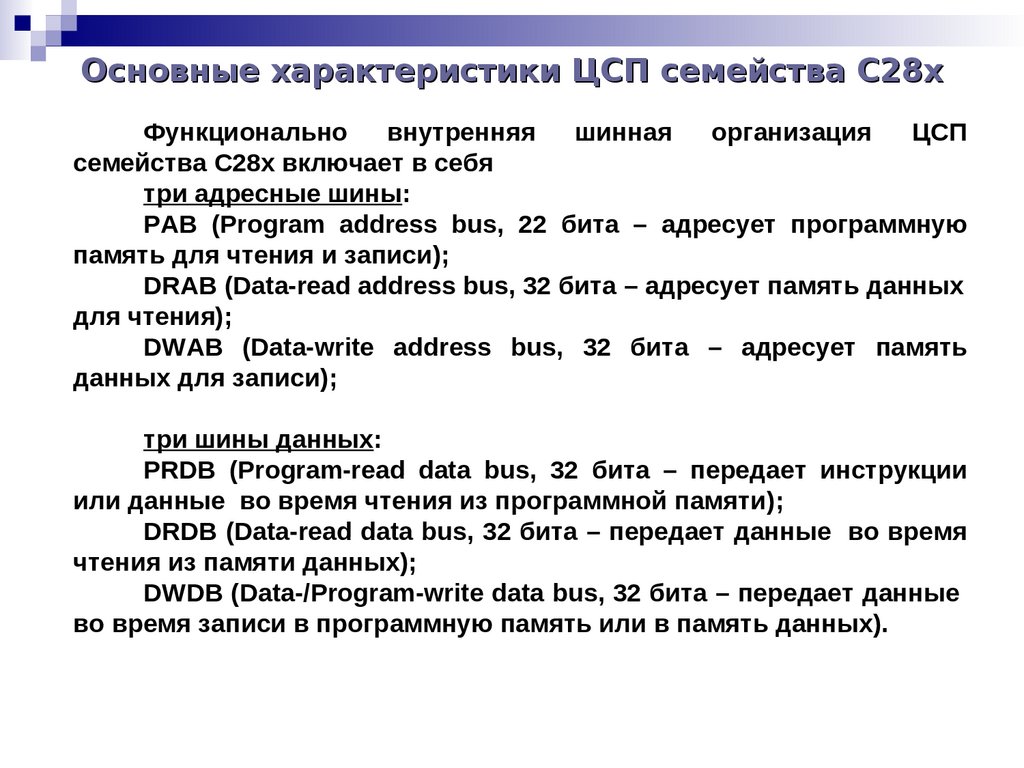

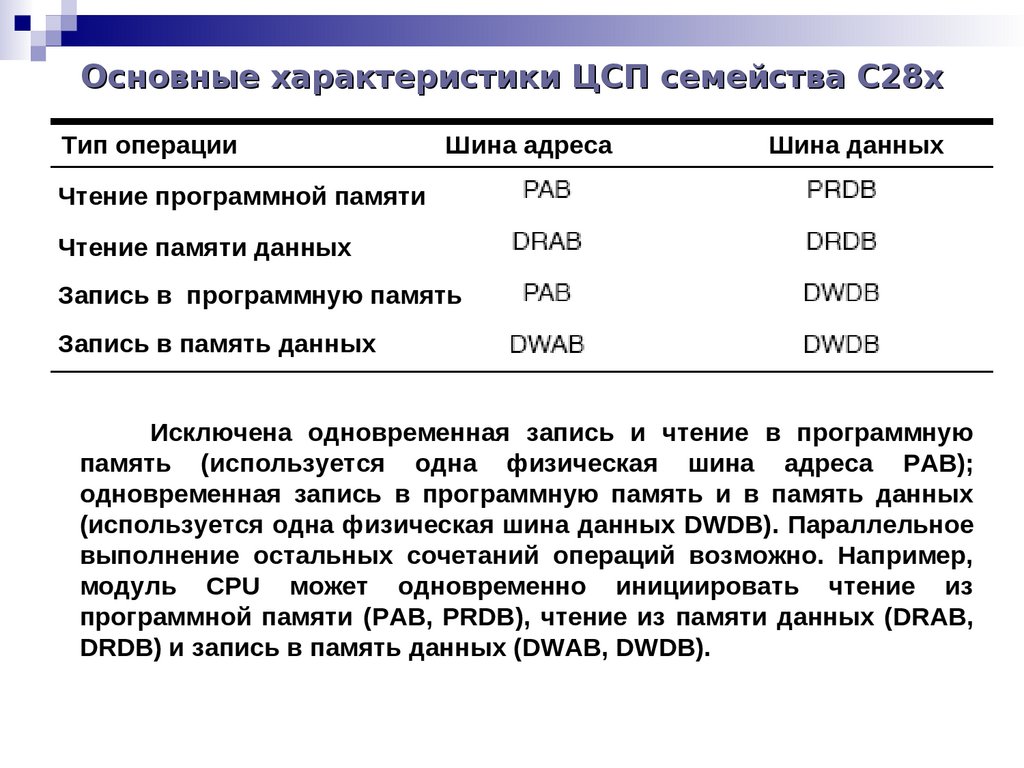

113. Основные характеристики ЦСП семейства С28x

В качестве памяти данных используется исключительно ОЗУоднократного доступа общим объёмом 18 Кслов, состоящее из

5 банков – М0, M1 (2x1К), L0, L1 (2x4К) и Н0 (8К). Каждый банк

отображается и на память программ, и на память данных. По решению

программиста память используется либо в качестве памяти программ,

либо в качестве памяти данных.

Память программ включает в себя: стандартное ПЗУ (ROM)

объемом до 128K x 16, однократно записываемая память (OTP ROM)

1K x 16 и загрузочное ПЗУ (Boot ROM) 4K x 16.

В ЦСП F2812 объём встроенной флэш-памяти составляет 128 Кслов

(4 сектора по 8К и 6 секторов по 16К). Flash-память ЦСП семейства С28х

разбита на секторы, что позволяет пользователю программировать

лишь часть памяти, не осуществляя предварительного полного

стирания.

Специальный ключ защиты (Security Code) защищает флэш-память,

ROM, OTP ROM, блоки L0/L1 SARAM. Для всех ЦСП семейства С28x этот

пароль 128-битный, за исключением TMS320F283x (256 бит).

ЦСП семейства С28x содержат три сегмента (фрейма) регистров

встроенной периферии, предназначенных для управления режимами и

хранения данных внутренних периферийных устройств. Эти регистры

расположены прямо в адресном пространстве памяти, т.е. доступны

не только как регистры с именами, но и как ячейки памяти с

определенными адресами.

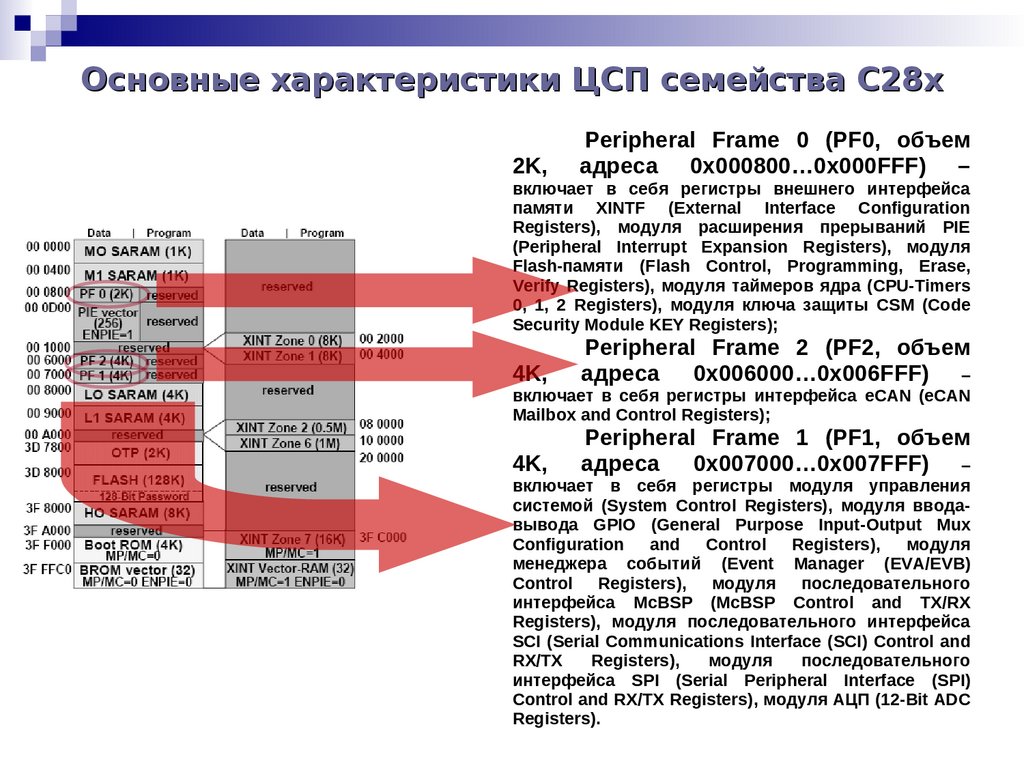

114. Основные характеристики ЦСП семейства С28x

2K,Peripheral Frame 0 (PF0, объем

адреса 0x000800…0x000FFF) –

включает в себя регистры внешнего интерфейса

памяти X) позволяет отключать передачу во mNTF (E) и xternal mnterface Configuration

Registers), модуля расширения прерываний PmE) и

(Peripheral mnterrupt E) и xpansion Registers), модуля

Flash-памяти (Flash Control, Programming, E) и rase,

Verify Registers), модуля таймеров ядра (CPU-Timers

0, 1, 2 Registers), модуля ключа защиты CSM (Code

Security Module KE) и Y Registers);

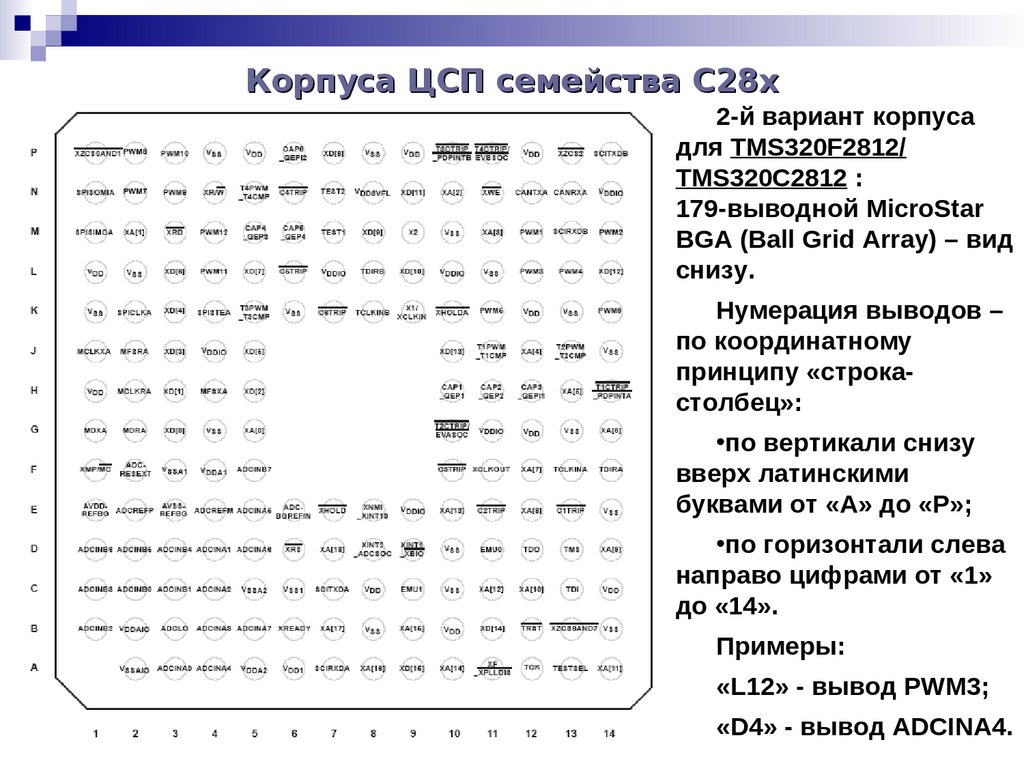

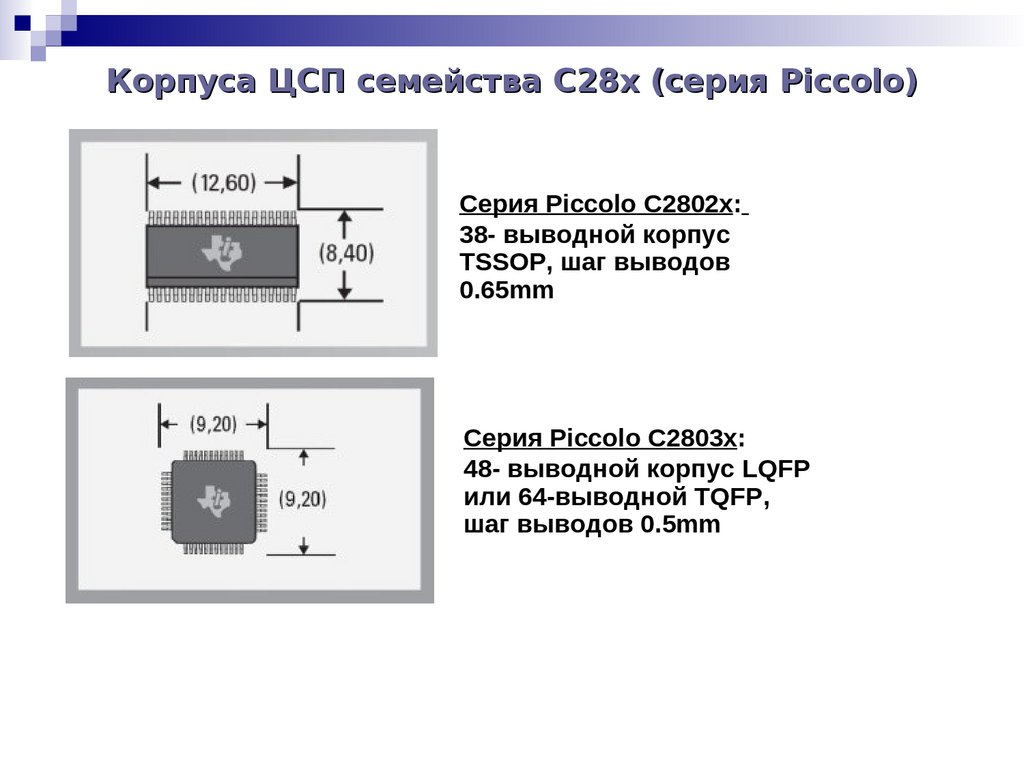

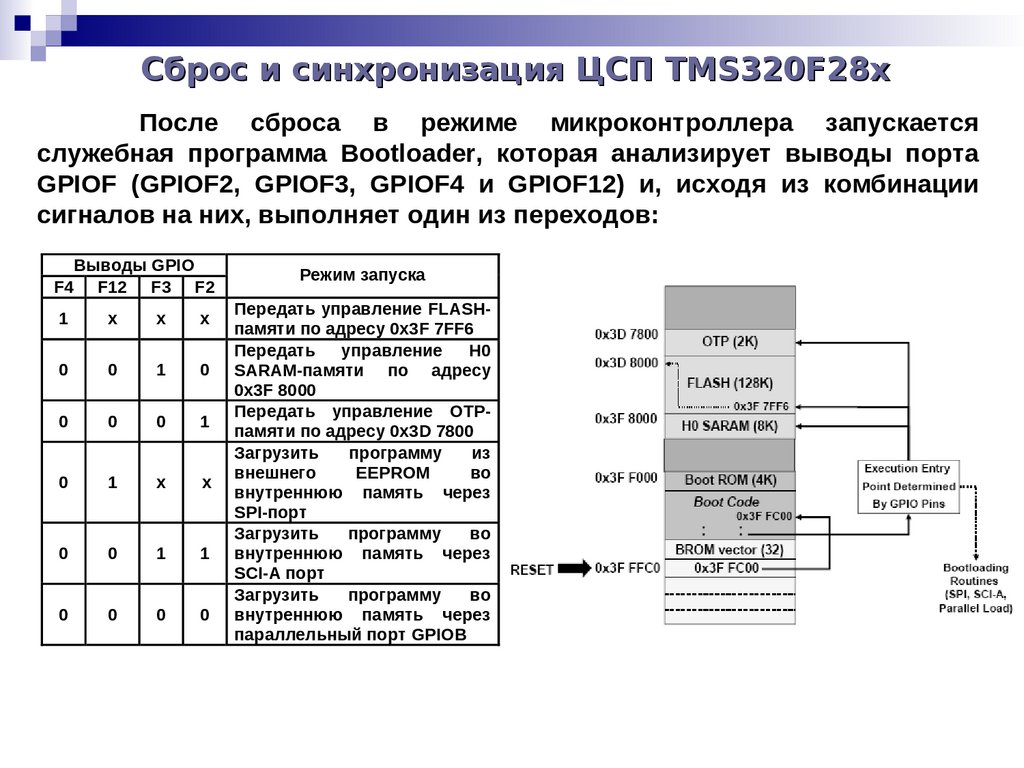

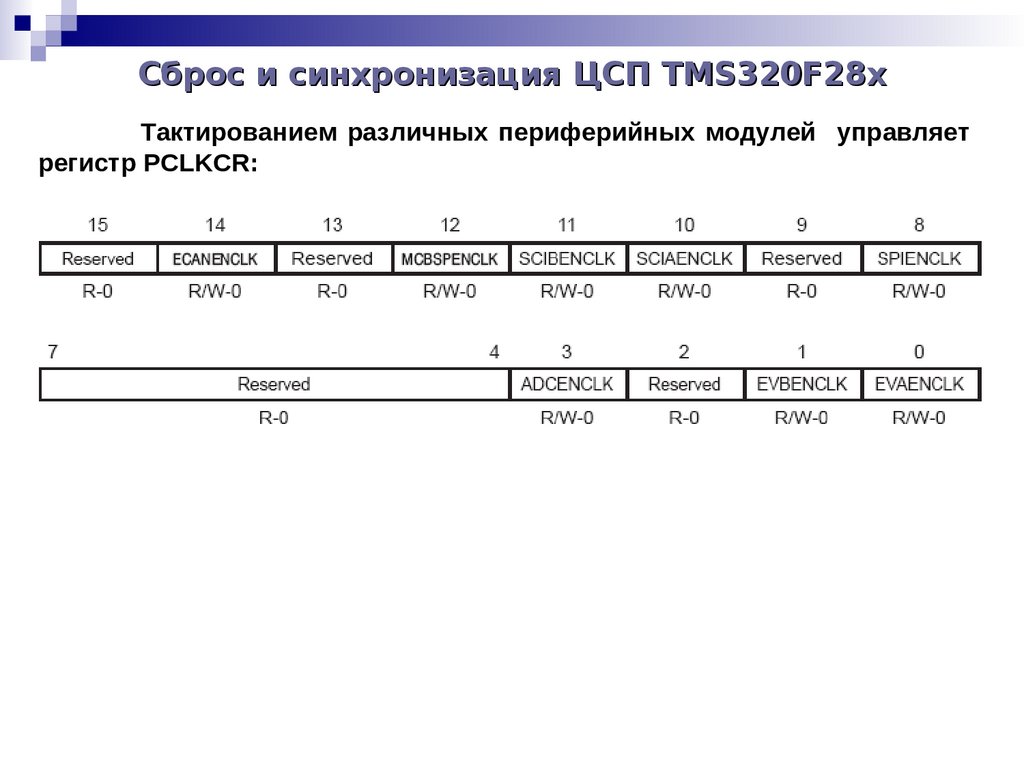

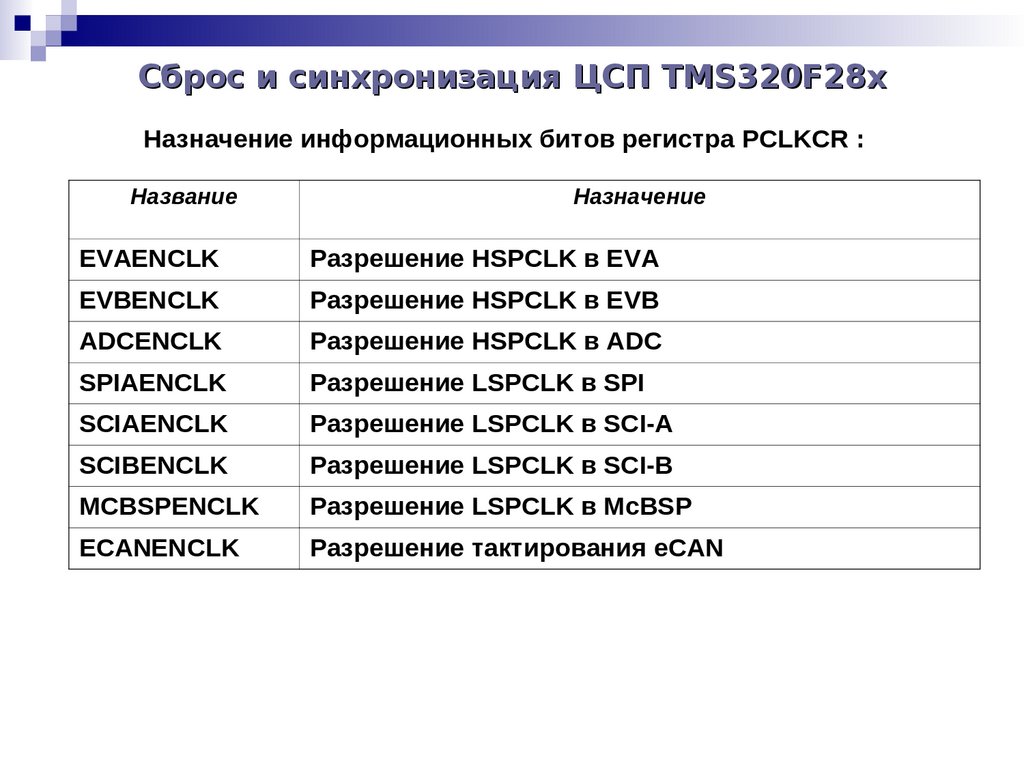

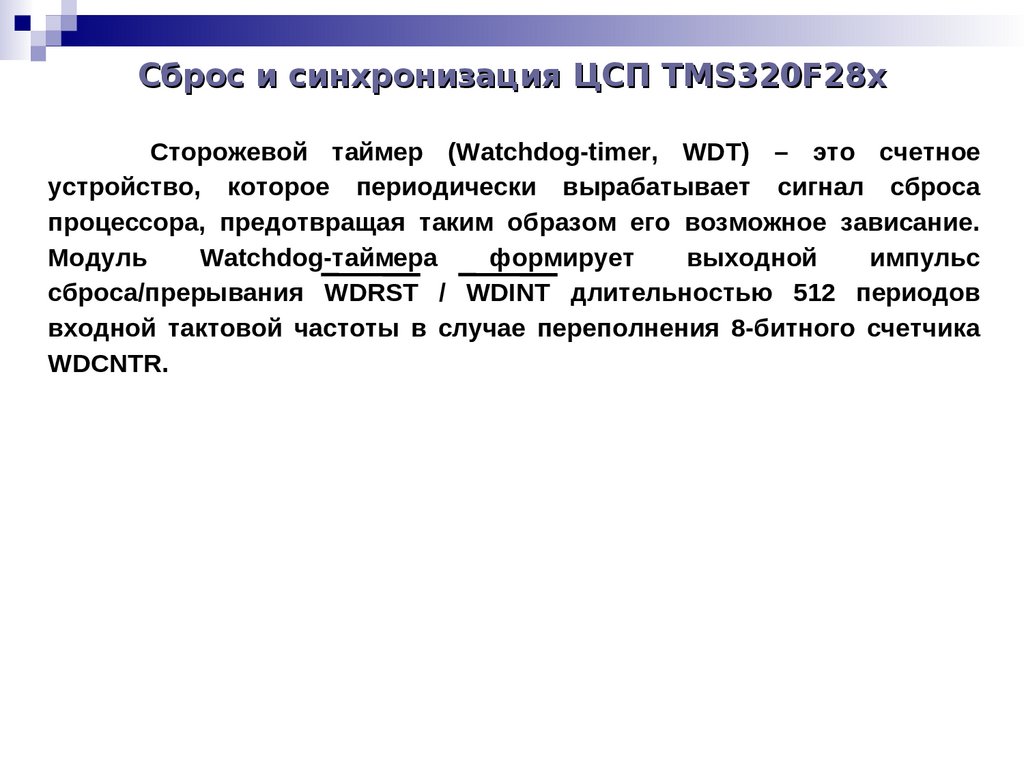

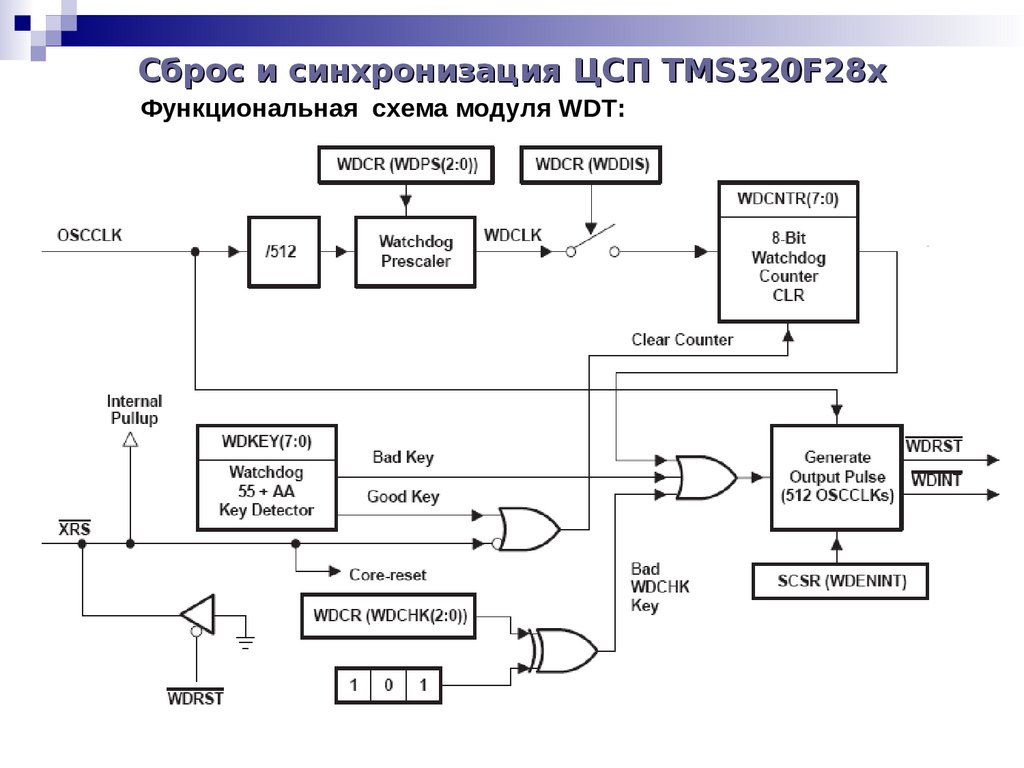

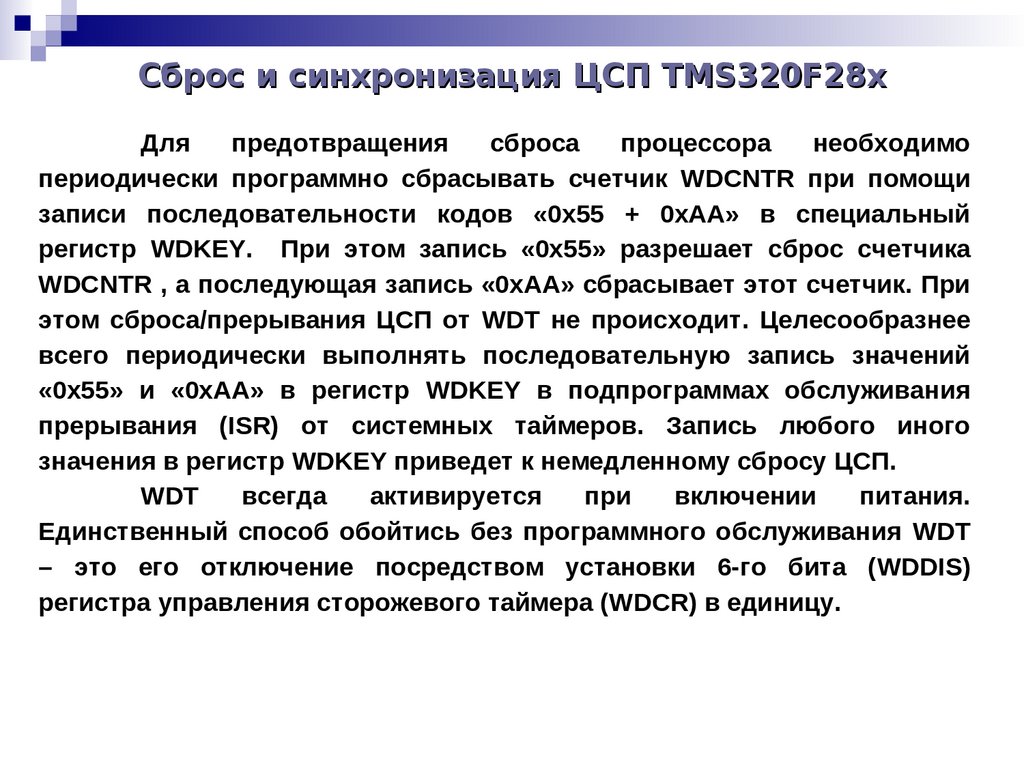

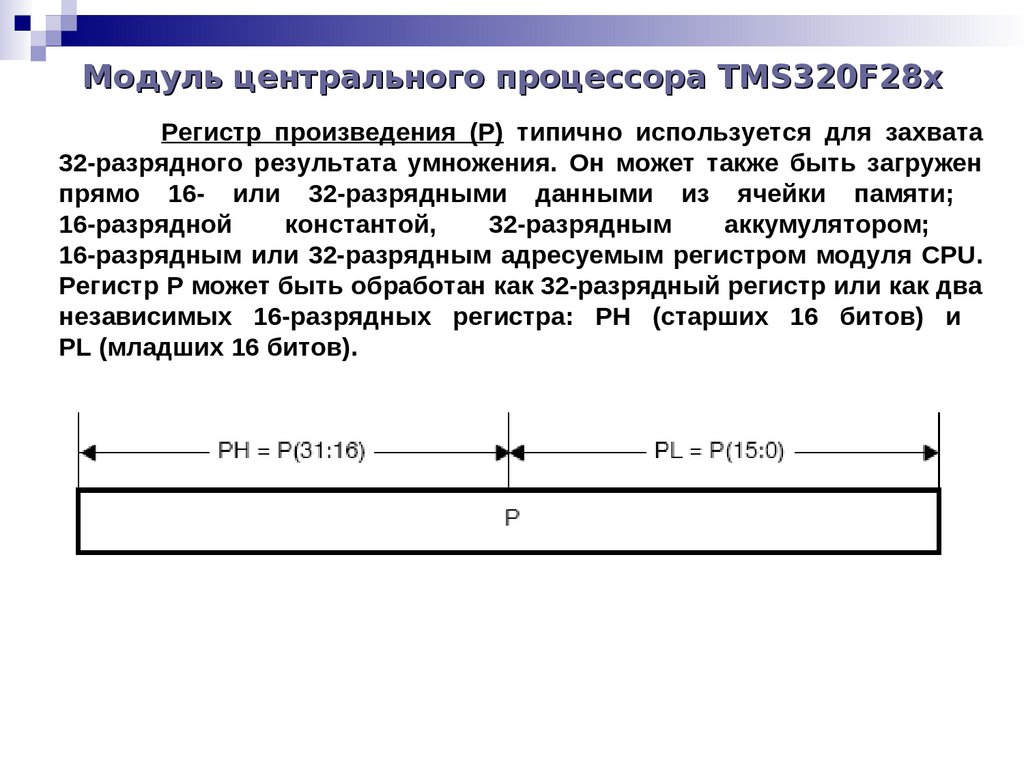

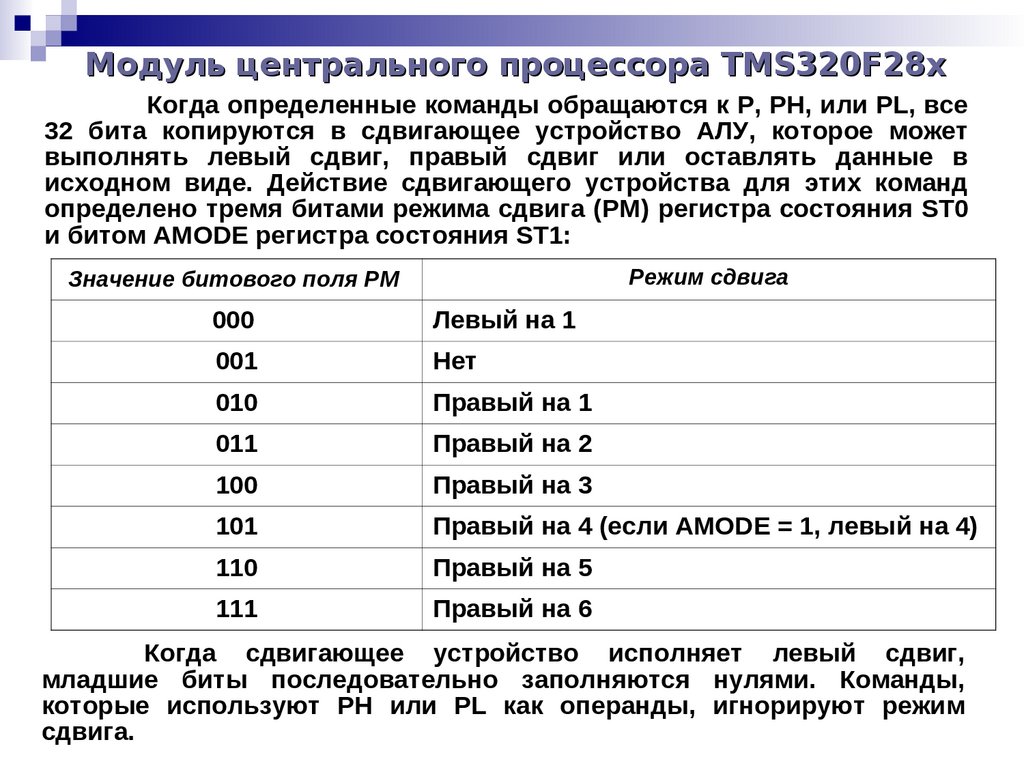

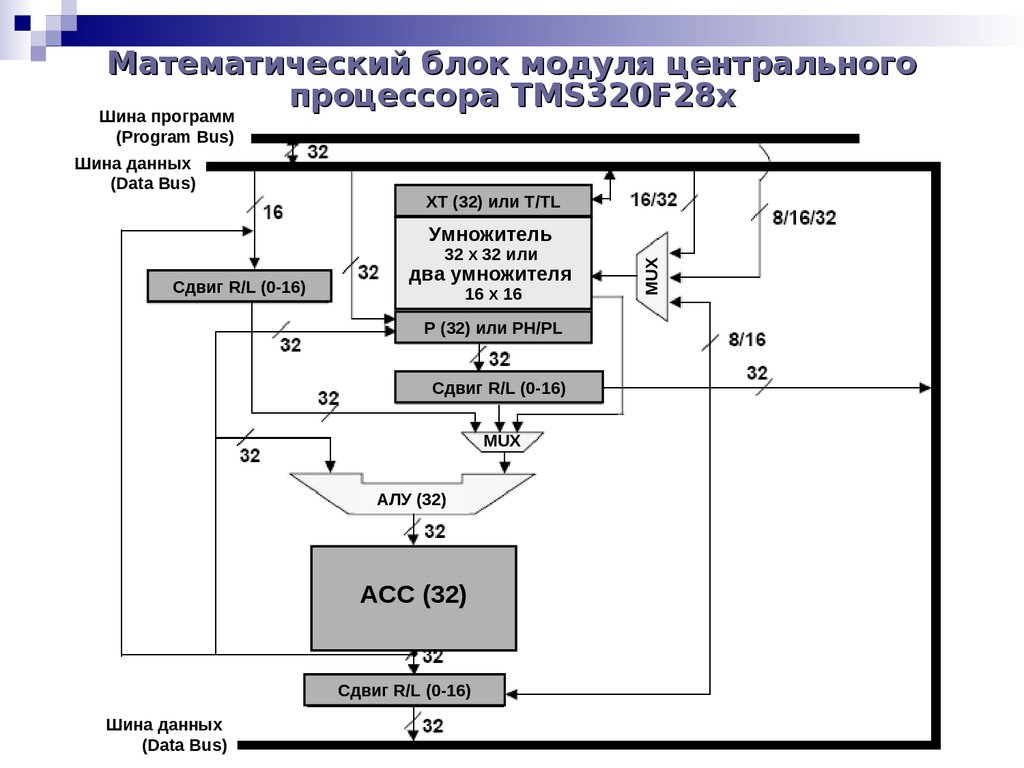

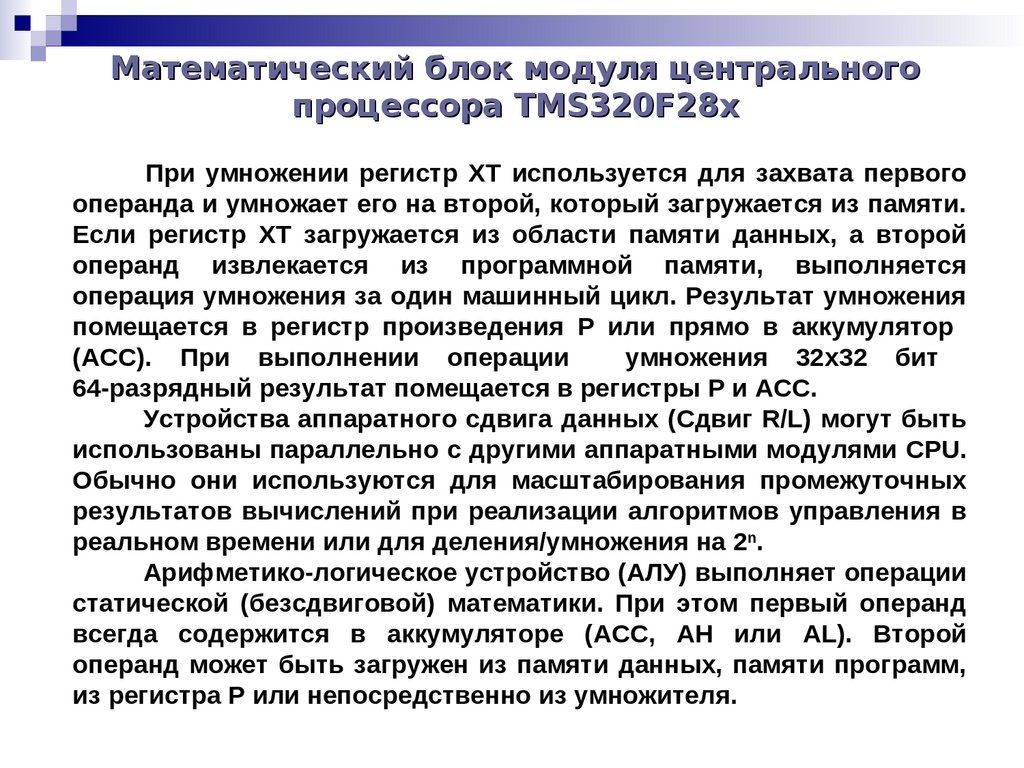

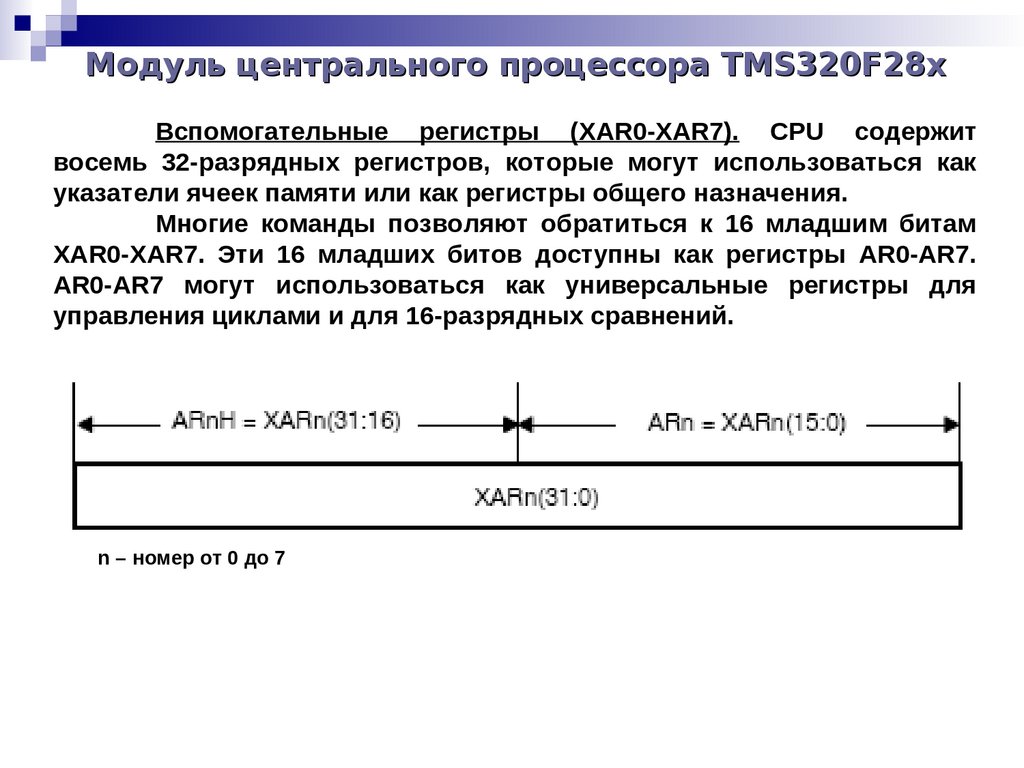

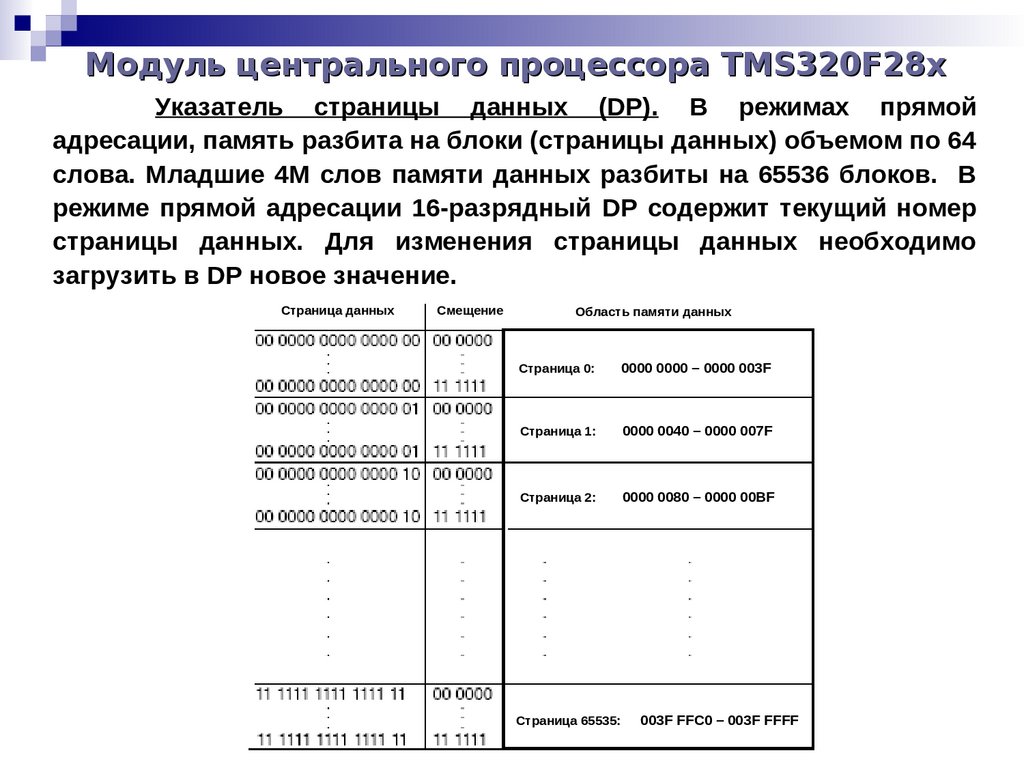

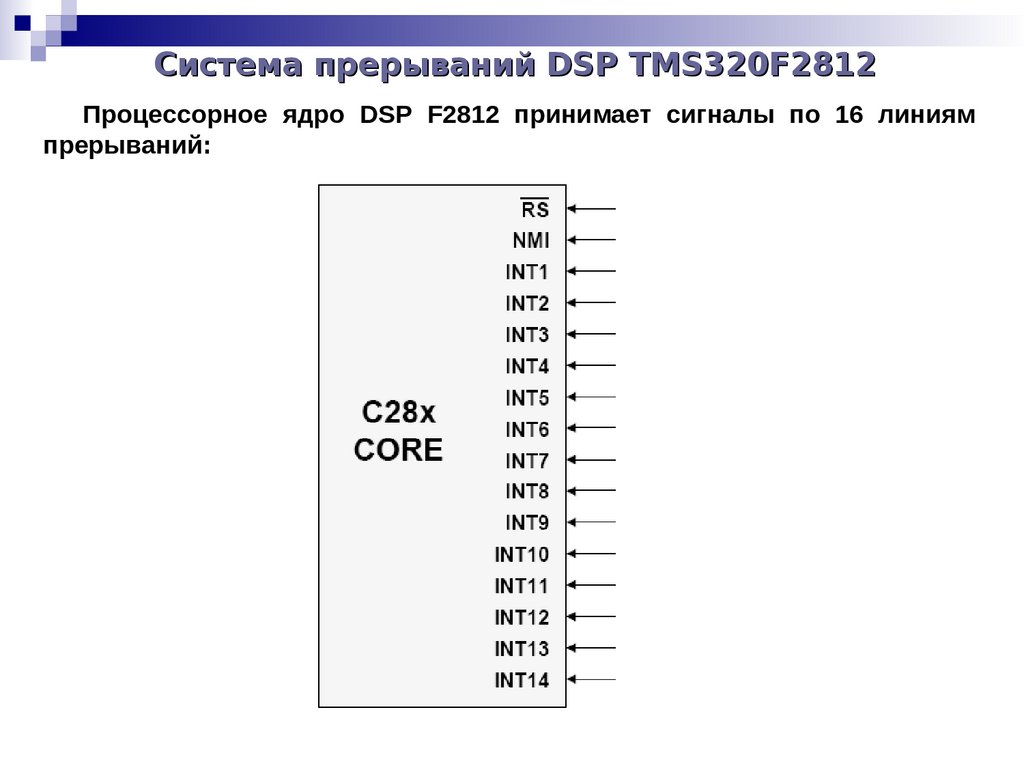

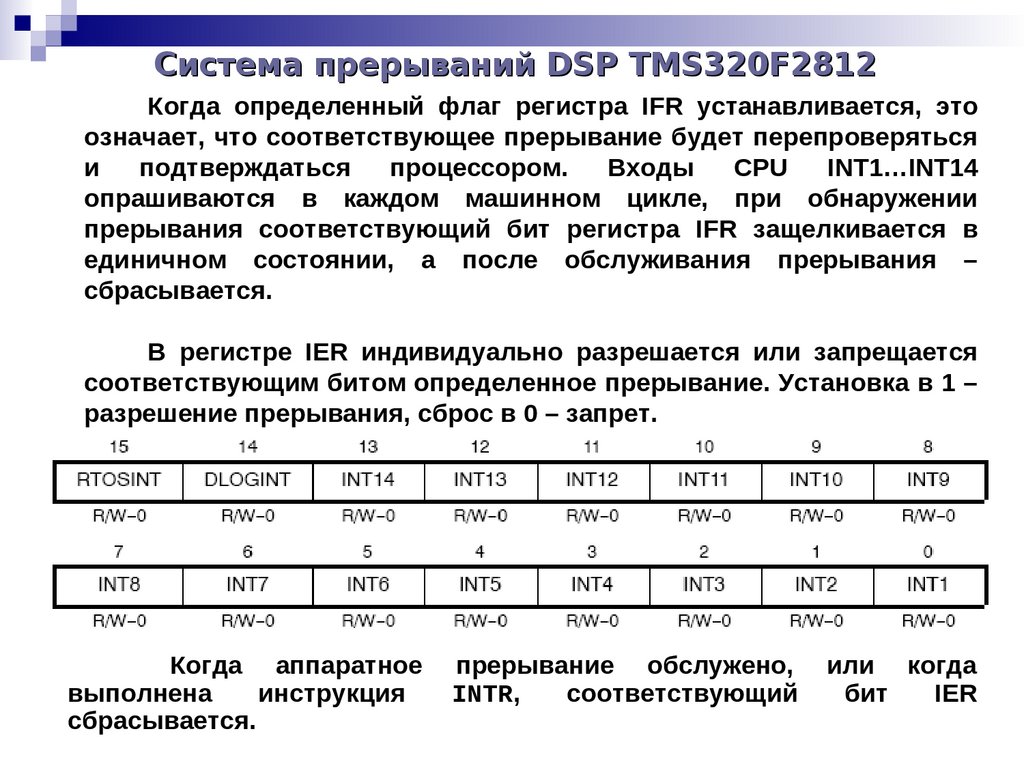

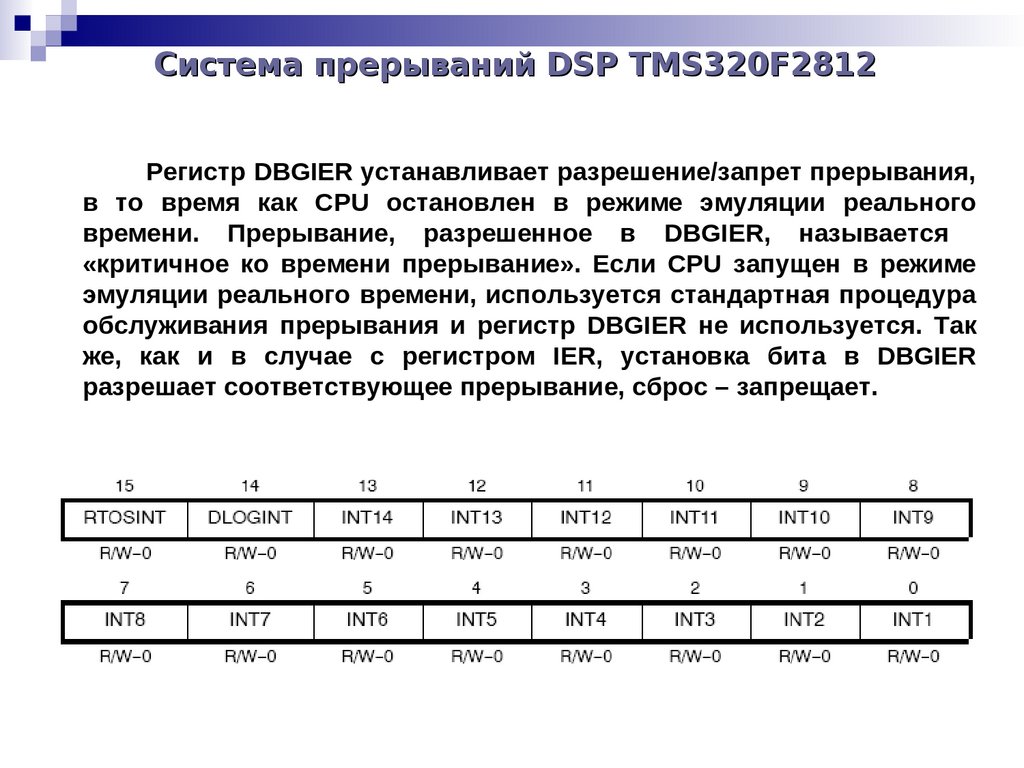

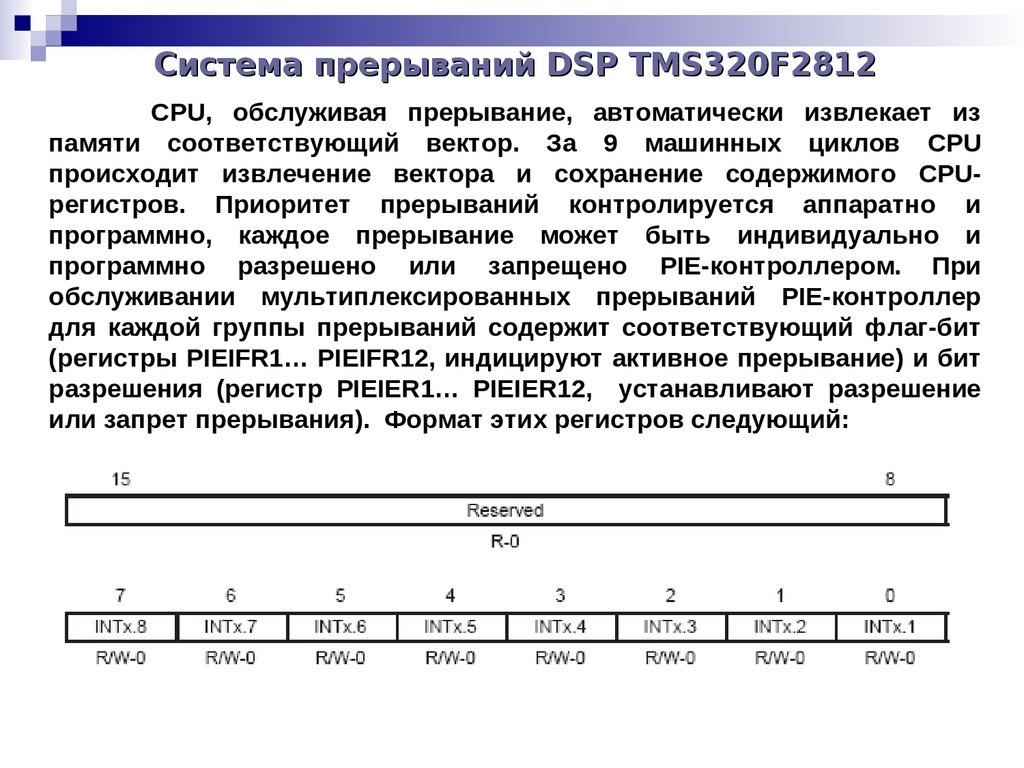

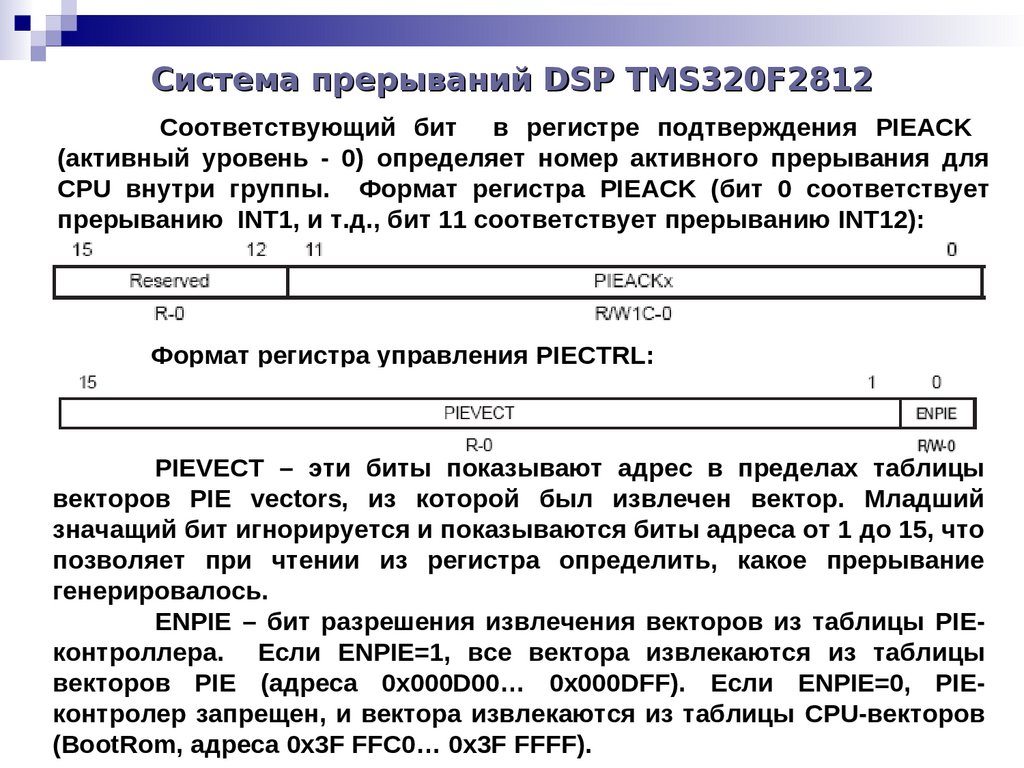

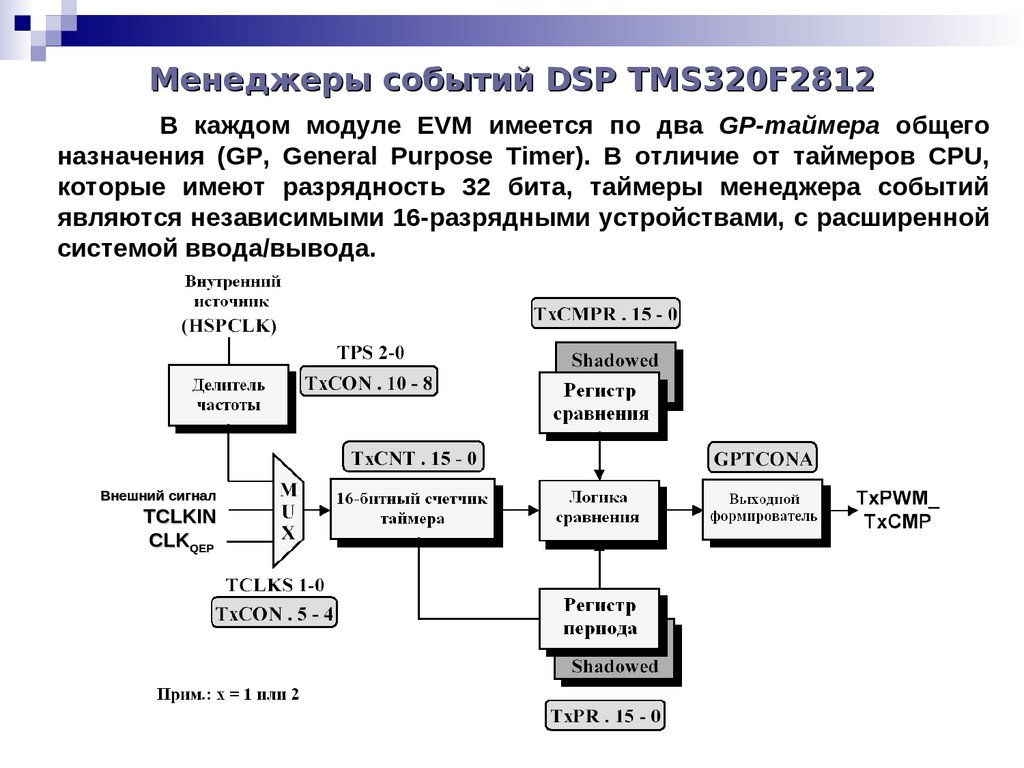

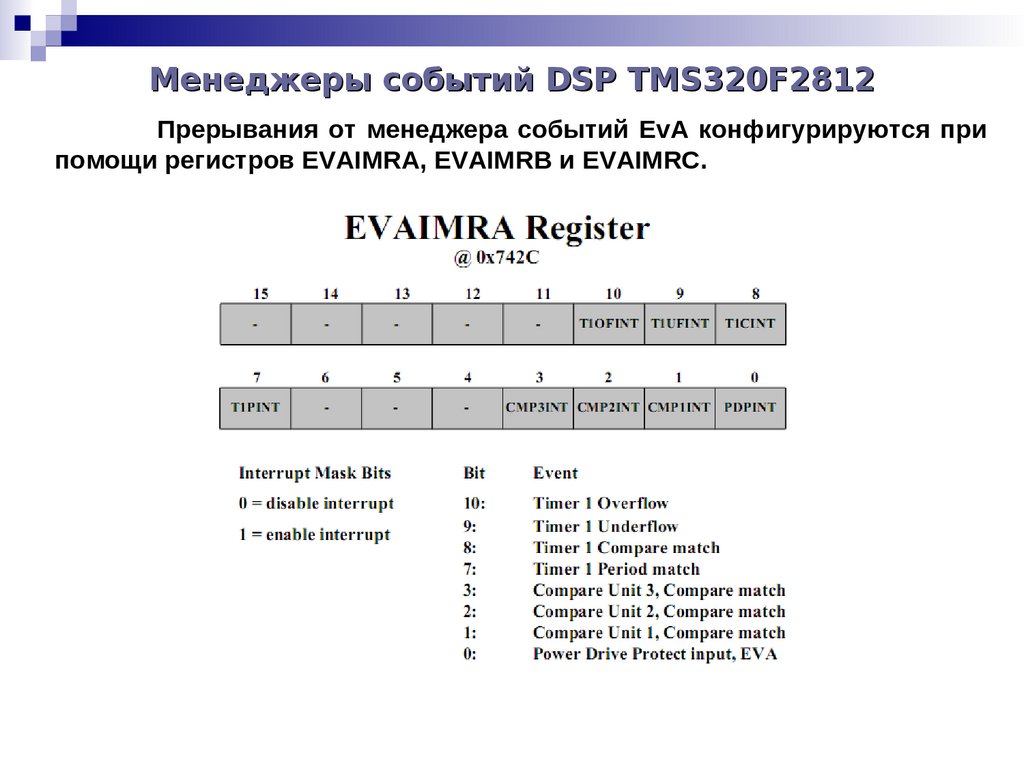

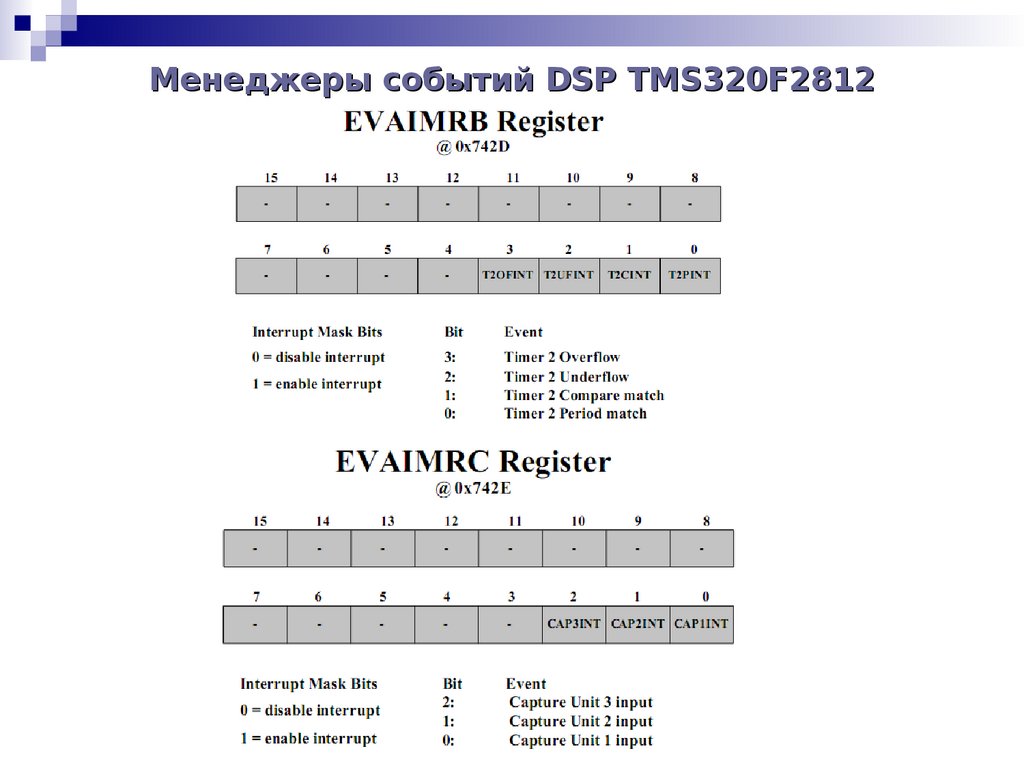

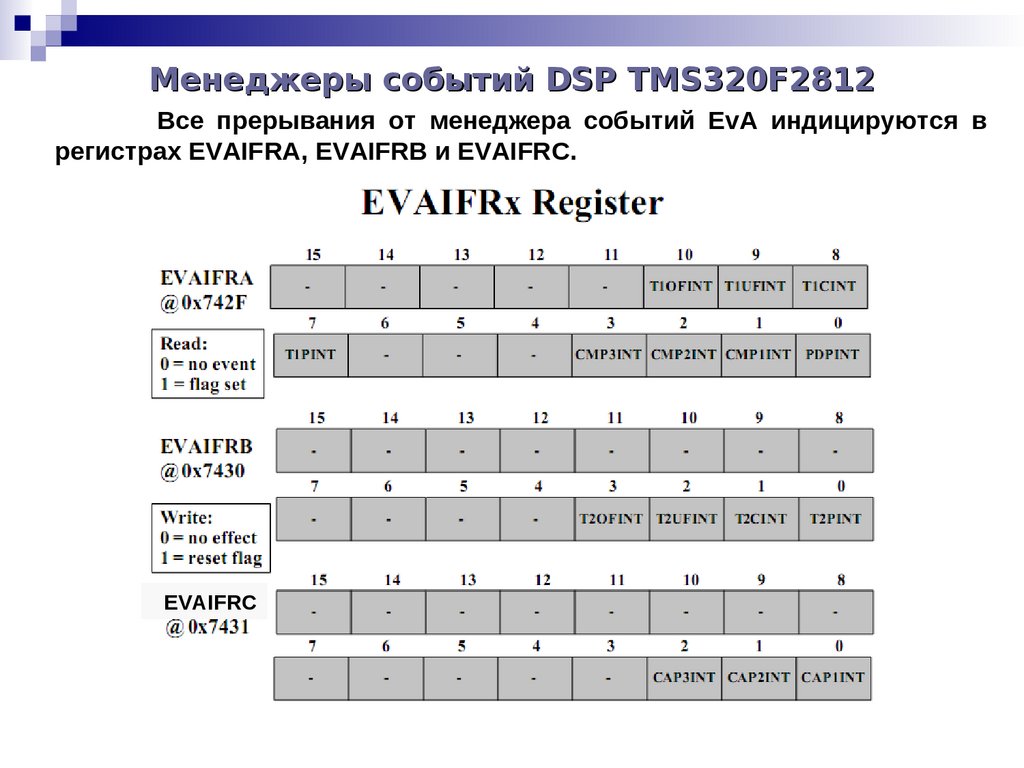

4K,