Похожие презентации:

Система команд и способы адресации процессоров ЭВМ

1.

Тема 2.Занятие .

Система команд и способы

адресации процессоров ЭВМ

2.

Учебные вопросы:1. Система и форматы команд.

2. Способы адресации

процессоров

3.

1. Система иформаты команд

4.

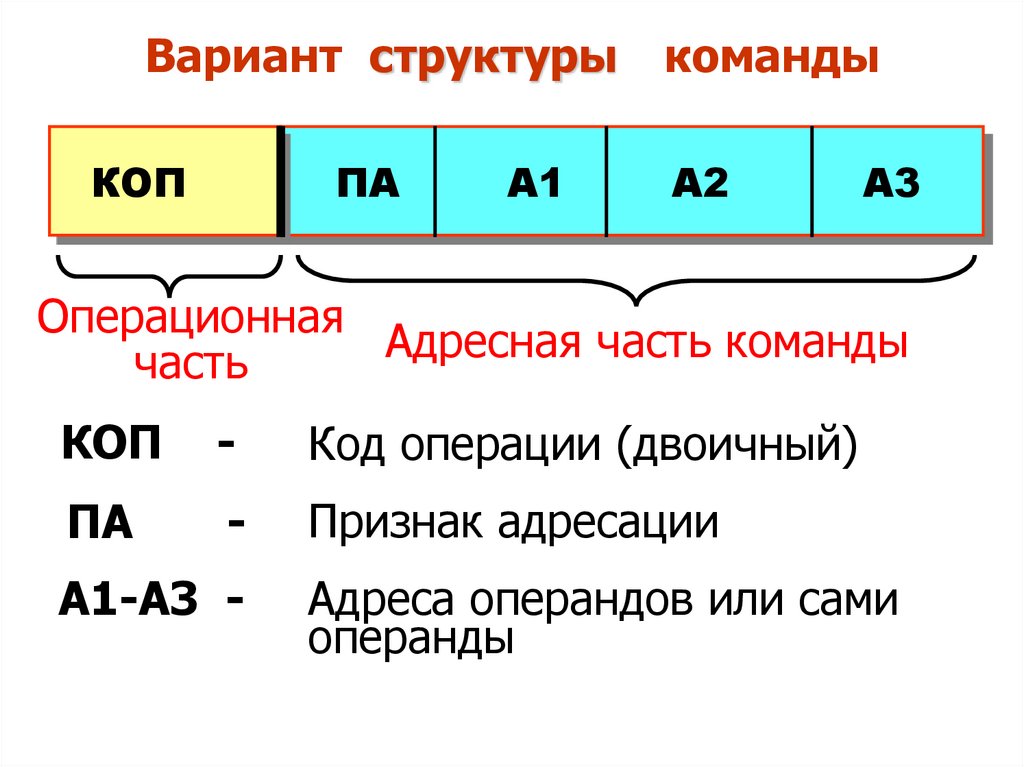

Вариант структурыКОП

ПА

А1

команды

А2

А3

Операционная

Адресная

часть

команды

часть

КОП

-

Код операции (двоичный)

ПА

-

Признак адресации

А1-А3 -

Адреса операндов или сами

операнды

5.

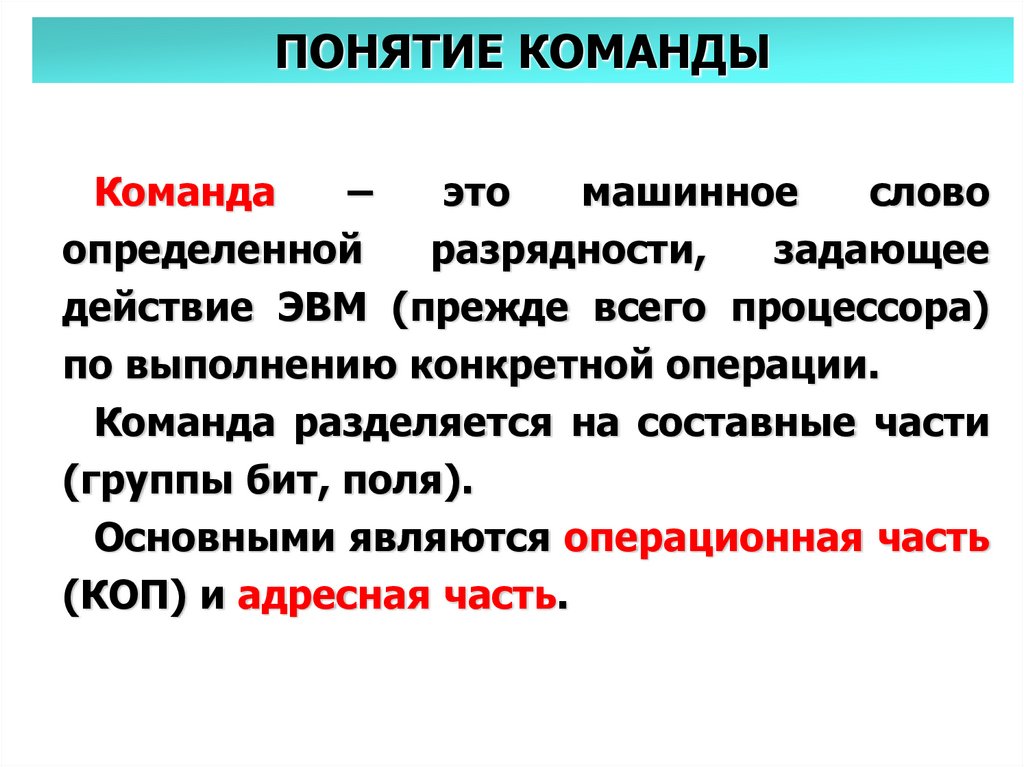

ПОНЯТИЕ КОМАНДЫКоманда

–

это

машинное

слово

определенной

разрядности,

задающее

действие ЭВМ (прежде всего процессора)

по выполнению конкретной операции.

Команда разделяется на составные части

(группы бит, поля).

Основными являются операционная часть

(КОП) и адресная часть.

6.

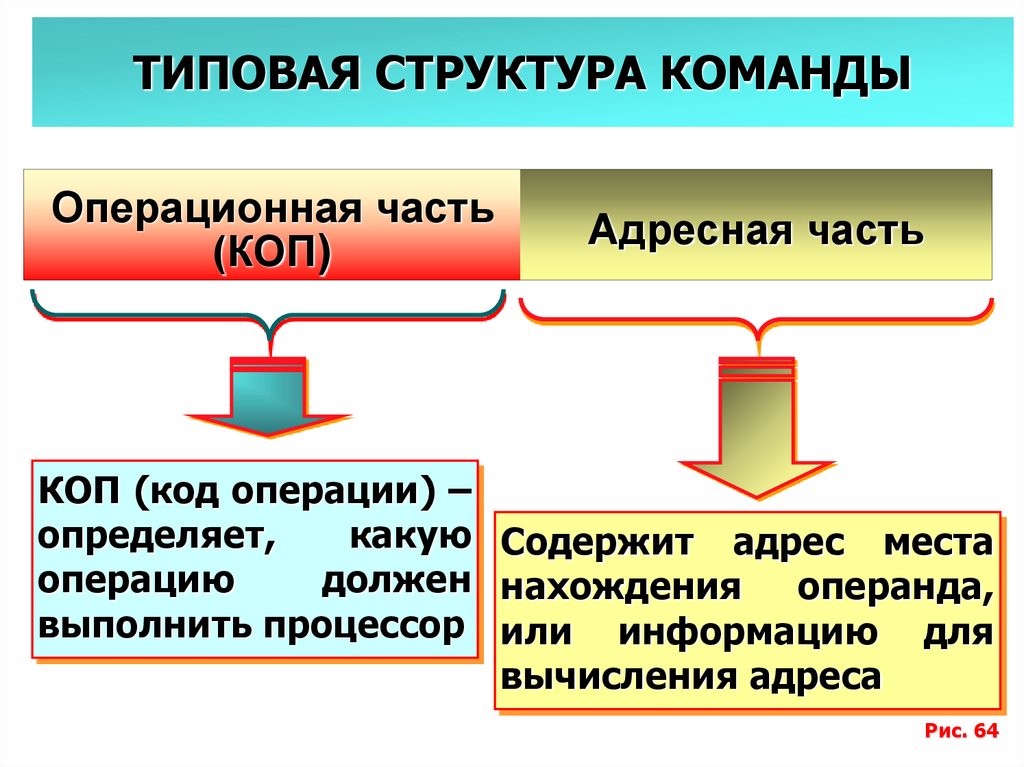

ТИПОВАЯ СТРУКТУРА КОМАНДЫОперационная часть

(КОП)

Адресная часть

КОП (код операции) –

определяет,

какую Содержит адрес места

операцию

должен нахождения операнда,

выполнить процессор или информацию для

вычисления адреса

Рис. 64

7.

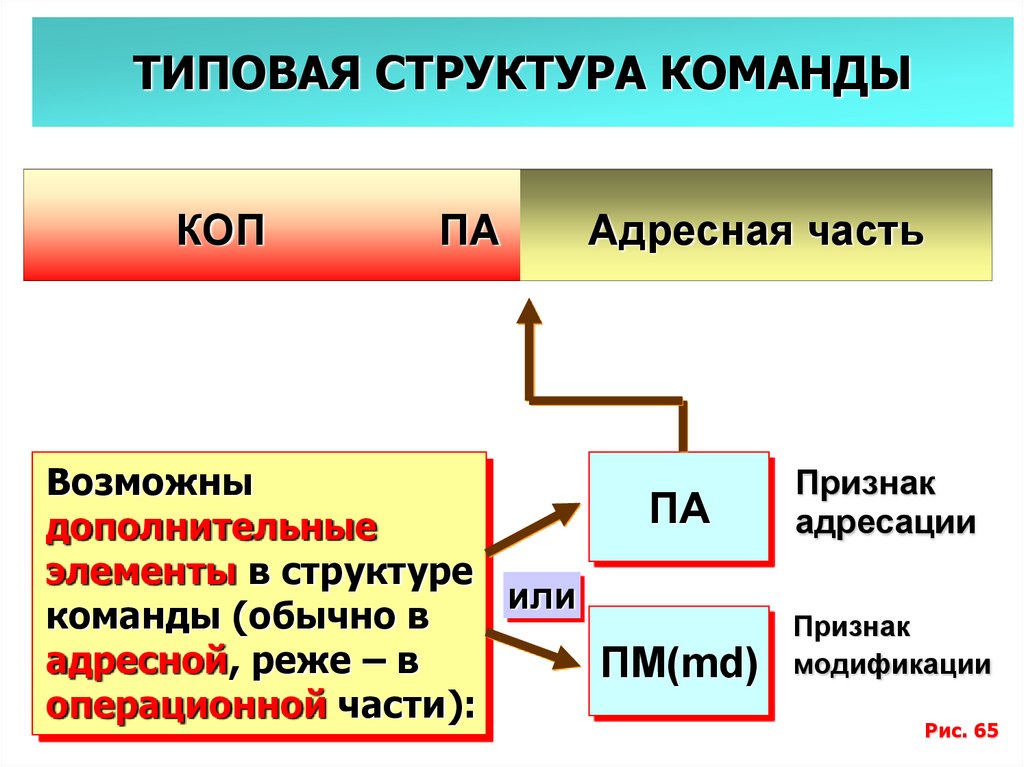

ТИПОВАЯ СТРУКТУРА КОМАНДЫОперационная часть

КОП

КОП)

ПА ПААдресная

Адресная

часть

часть

(КОП

Признак

Возможны

ПА

адресации

дополнительные

элементы в структуре

или

команды (обычно в

Признак

адресной, реже – в

ПМ(md) модификации

операционной части):

Рис. 65

8.

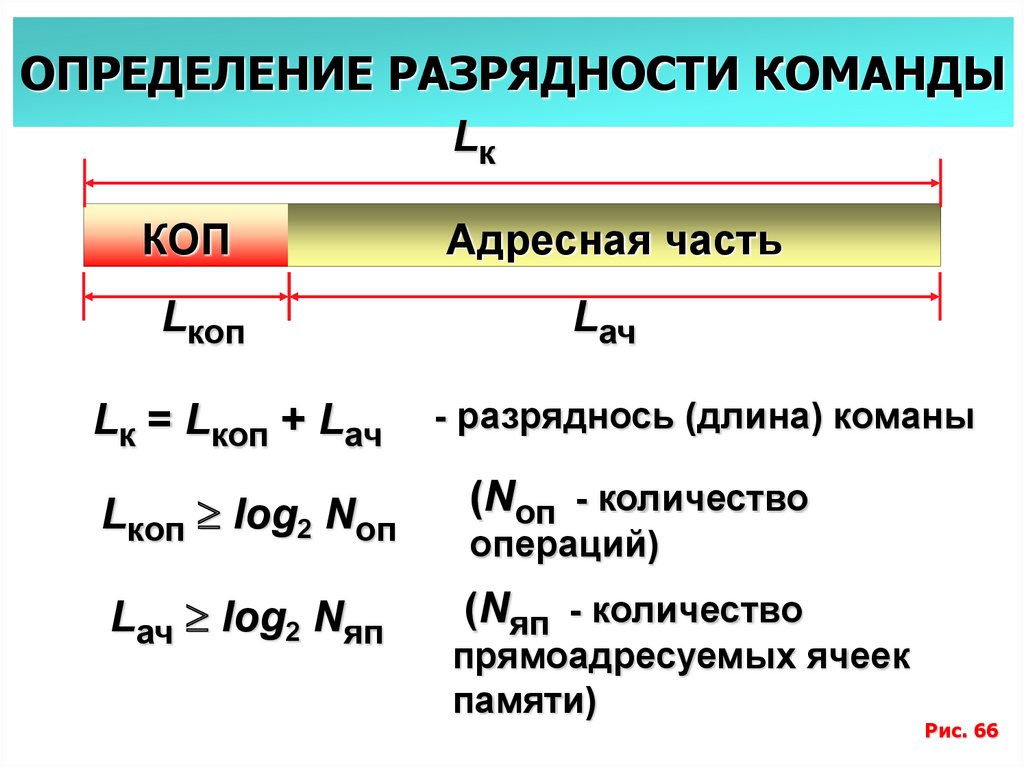

ОПРЕДЕЛЕНИЕ РАЗРЯДНОСТИ КОМАНДЫLк

КОП

Lкоп

Lк = Lкоп + Lач

Адресная часть

Lач

- разряднось (длина) команы

Lкоп log2 Nоп

(Nоп - количество

Lач log2 Nяп

(Nяп - количество

операций)

прямоадресуемых ячеек

памяти)

Рис. 66

9.

РАЗНОВИДНОСТИ КОМАНДТрехадресная

КОП

А1

А2

А3

А1, А2 – адреса первого и второго операндов; А3 – адрес результата

Двухадресная

КОП

А1

А2

А1, А2 – адреса первого и второго операндов;

результат операции помещается на место одного из операндов

Одноадресная

А1 – адрес первого операндов;

размещаются в регистре-аккумуляторе

Безадресная

КОП

второй

операнд

А1

и

результат

КОП

Рис. 67

10.

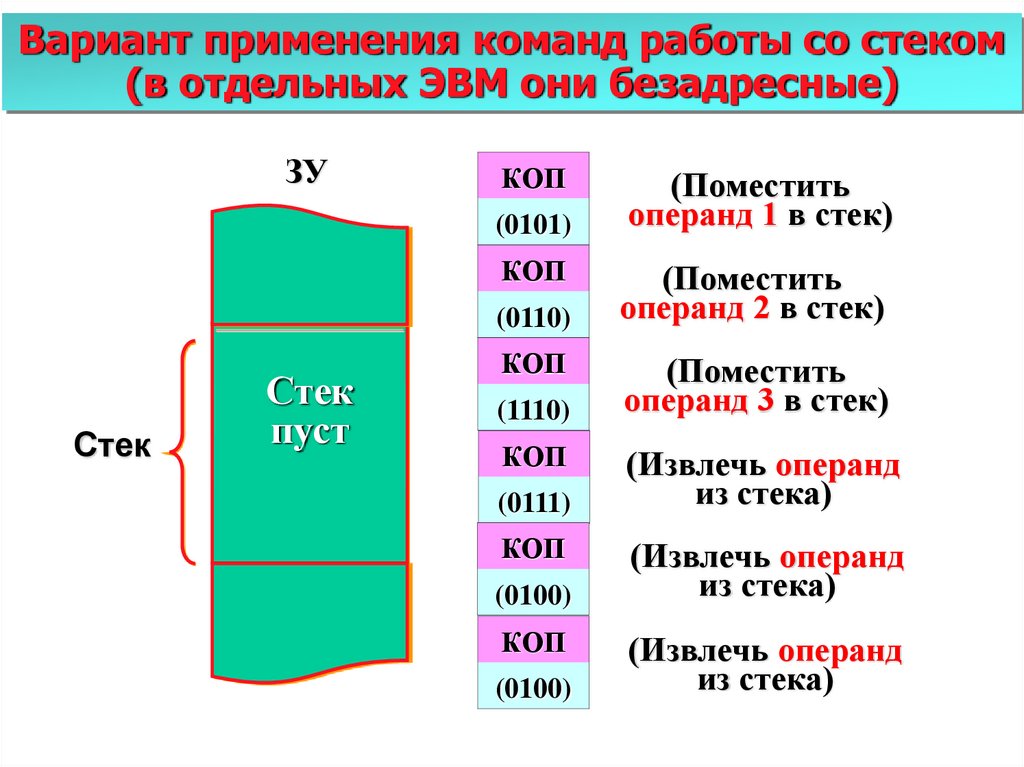

Вариант применения команд работы со стеком(в отдельных ЭВМ они безадресные)

ЗУ

КОП

(0101)

КОП

(0110)

Стек

Операнд 321

Стек 21

Операнд

(1110)

Операнд 1

КОП

пуст

КОП

(0111)

КОП

(0100)

КОП

(0100)

(Поместить

операнд 1 в стек)

(Поместить

операнд 2 в стек)

(Поместить

операнд 3 в стек)

(Извлечь операнд

из стека)

(Извлечь операнд

из стека)

(Извлечь операнд

из стека)

11.

ВЫВОДЫ:Реализация в ЭВМ команд тех или иных

форматов требует учета ряда факторов:

1.

затрат времени на выборку и выполнение

команд;

степени сложности реализуемых

алгоритмов;

особенностей

аппаратной

реализации

процессора

12.

2. Способы адресациипроцессоров

13.

ПОНЯТИЕ СПОСОБА АДРЕСАЦИИС целью сокращения длины команды в

современных ЭВМ выполняются различные

манипуляции адресом, именуемые режимами

адресации, способами адресации или просто

адресациями.

Способ

адресации

определяет

порядок

вычисления

исполнительного

адреса

операнда на основе информации, имеющейся

в адресной части

14.

ВИДЫ И СУЩНОСТЬ АДРЕСАЦИЙНепосредственная

адресация

Прямая адресация

Косвенная

адресация

!

Адресация со

смещением

В команде

находится операнд

В команде указан

адрес операнда

В команде указан

адрес адреса операнда

(т.е., косвенный адрес)

В команде указан адрес

операнда, смещенный

относительно начала

программного модуля

или массива данных

Рис. 72

15.

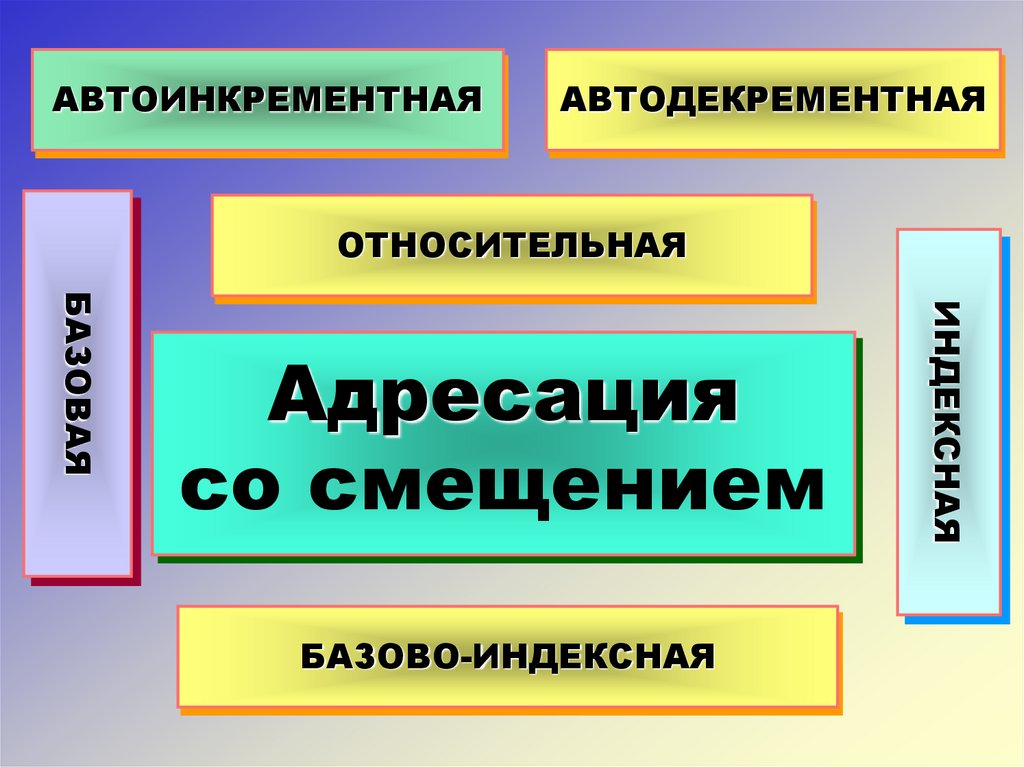

ВОЗМОЖНЫЕ ВАРИАНТЫ ОТДЕЛЬНЫХСПОСОБОВ АДРЕСАЦИИ

Непосредственная

адресация

Прямая

адресация

Кроме

того, каждая из них

Косвеннная

может использоваться со

адресация

смещением различной

величины, или без смещения

Адресация со

смещением

ВАРИАНТОВ НЕ ИМЕЕТ

РЕГИСТРОВАЯ

КОСВЕННАЯ РЕГИСТРОВАЯ

ОТНОСИТЕЛЬНАЯ

БАЗОВАЯ

ИНДЕКСНАЯ

БАЗОВО-ИНДЕКСНАЯ

АВТОИНКРЕМЕНТНАЯ

АВТОДЕКРЕМЕНТНАЯ

Рис. 73

16.

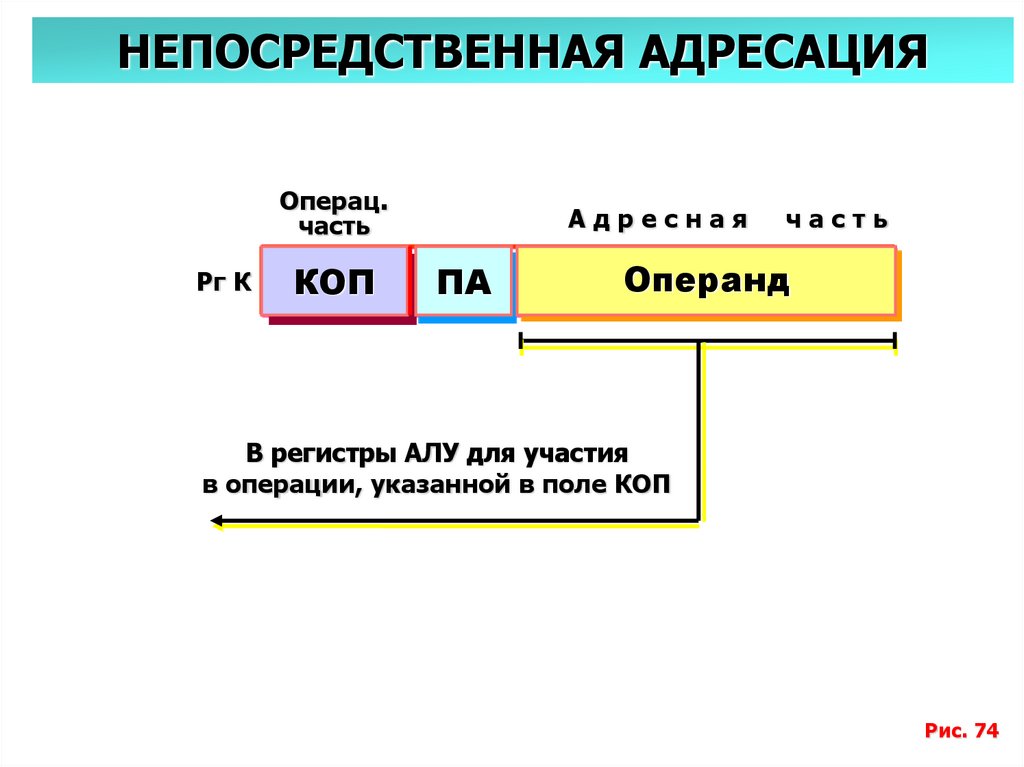

НЕПОСРЕДСТВЕННАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

часть

Операнд

В регистры АЛУ для участия

в операции, указанной в поле КОП

Рис. 74

17.

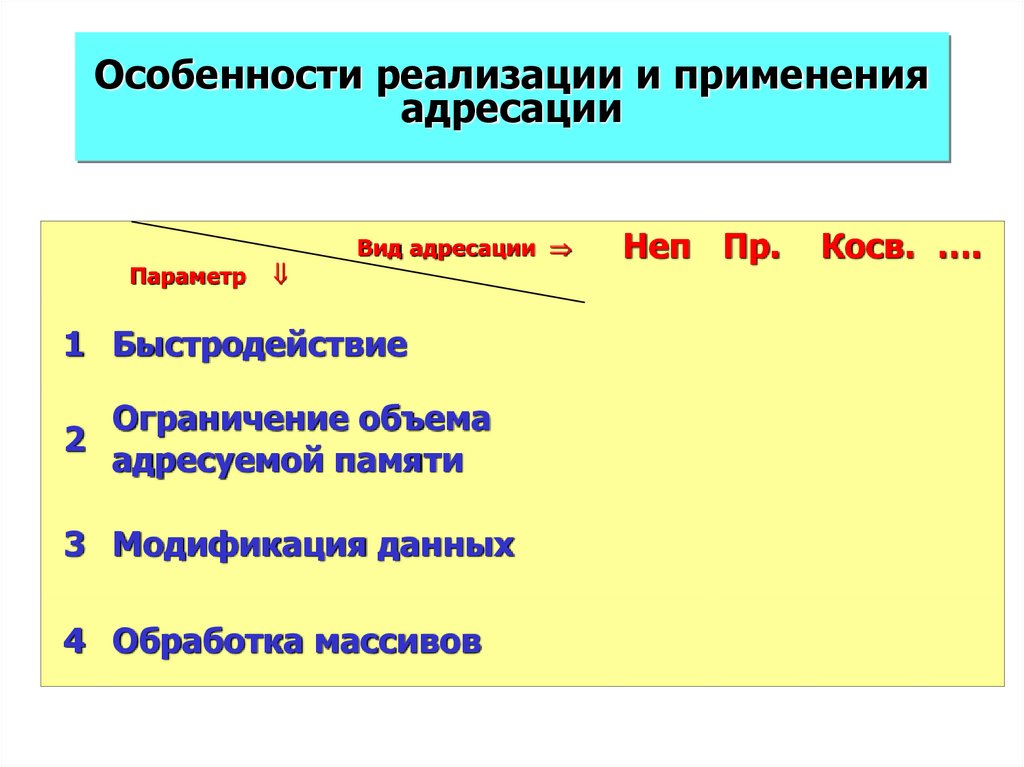

Особенности реализации и примененияадресации

Вид адресации

Параметр

1 Быстродействие

Ограничение объема

2

адресуемой памяти

3 Модификация данных

4 Обработка массивов

Неп Пр.

Косв. ….

18.

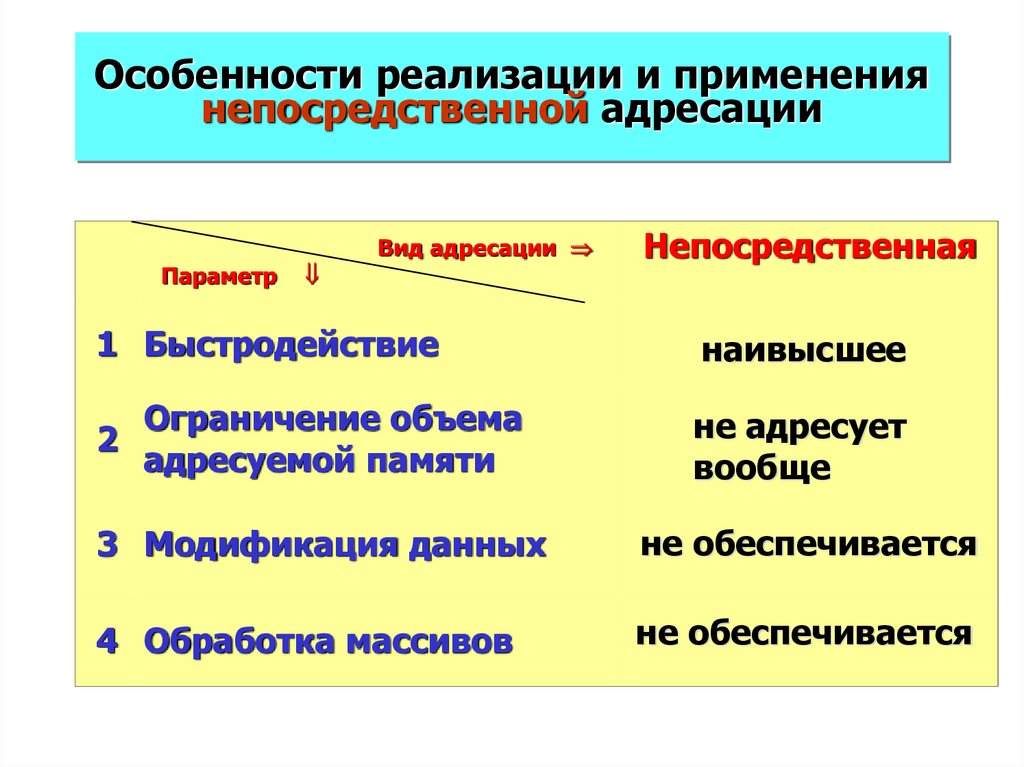

Особенности реализации и применениянепосредственной адресации

Вид адресации

Параметр

Непосредственная

1 Быстродействие

наивысшее

Ограничение объема

2

адресуемой памяти

не адресует

вообще

3 Модификация данных

не обеспечивается

4 Обработка массивов

не обеспечивается

19.

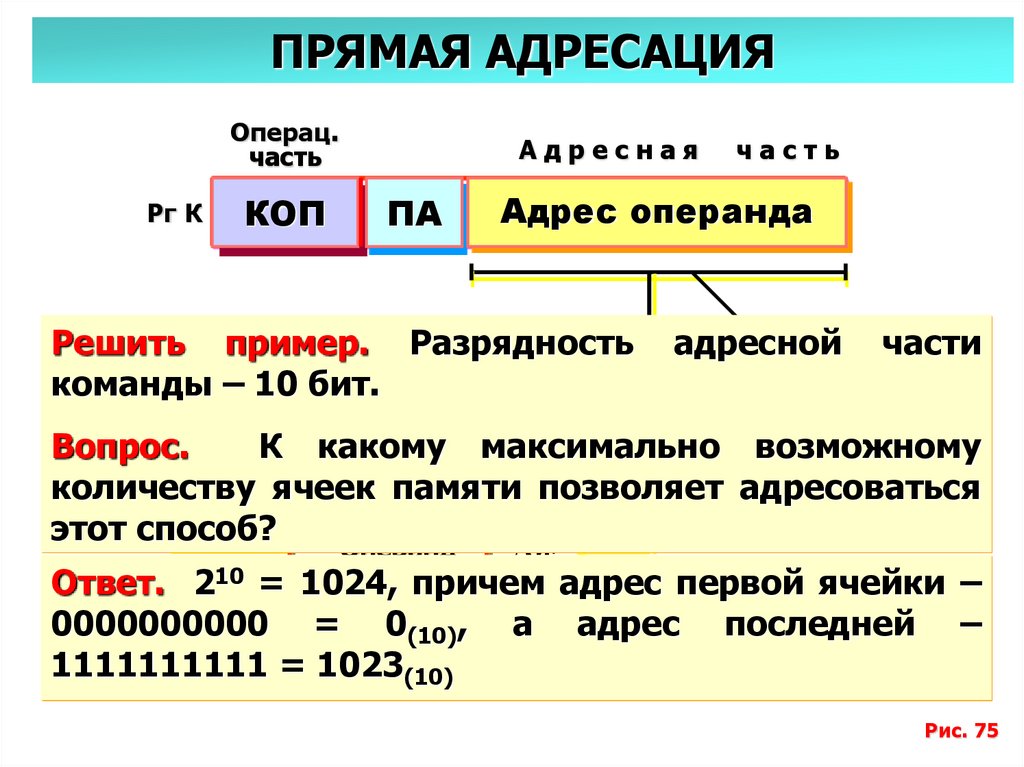

ПРЯМАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

Адрес операнда

Решить пример. ЗУРазрядность

команды – 10 бит.

в АЛУ

Вопрос.

процессора К

часть

адресной

части

Адрес

исполнительный

(номер ячейки ЗУ)

A0

какому максимально

возможному

.

количеству ячеек памяти. позволяет адресоваться

этот способ?

Aиi

Операнд

Ответ. 210 = 1024, причем

. адрес первой ячейки –

0000000000 = 0(10), а

адрес последней –

.

1111111111 = 1023(10)

An

Рис. 75

20.

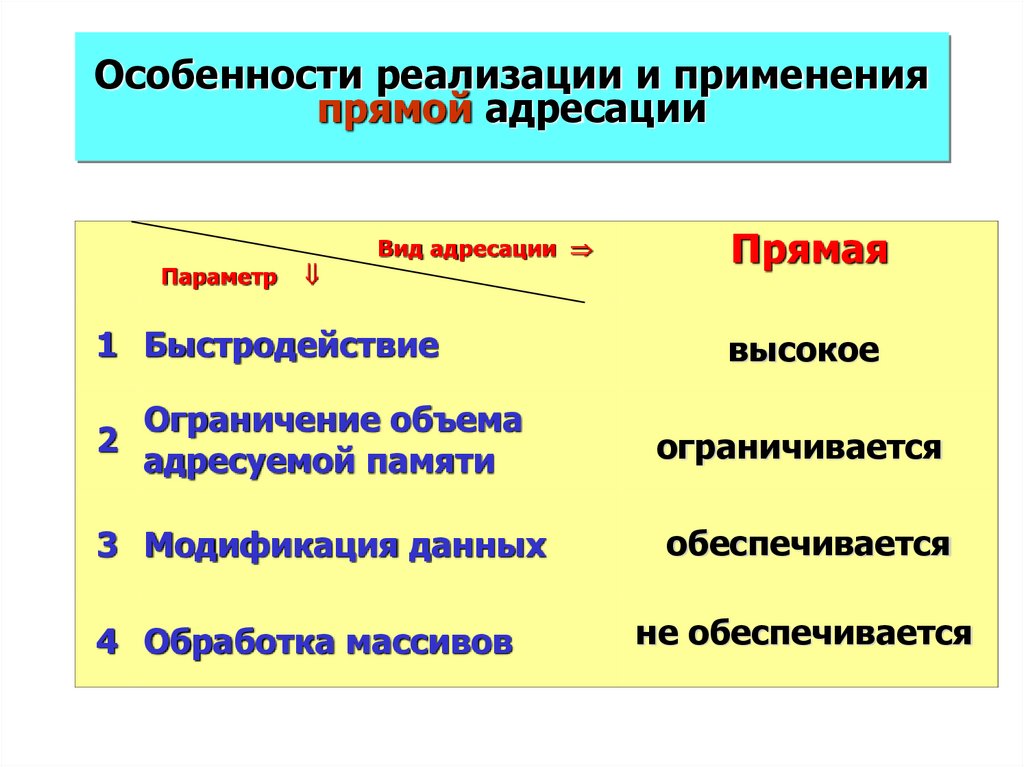

Особенности реализации и примененияпрямой адресации

Вид адресации

Параметр

1 Быстродействие

Прямая

высокое

Ограничение объема

2

адресуемой памяти

ограничивается

3 Модификация данных

обеспечивается

4 Обработка массивов

не обеспечивается

21.

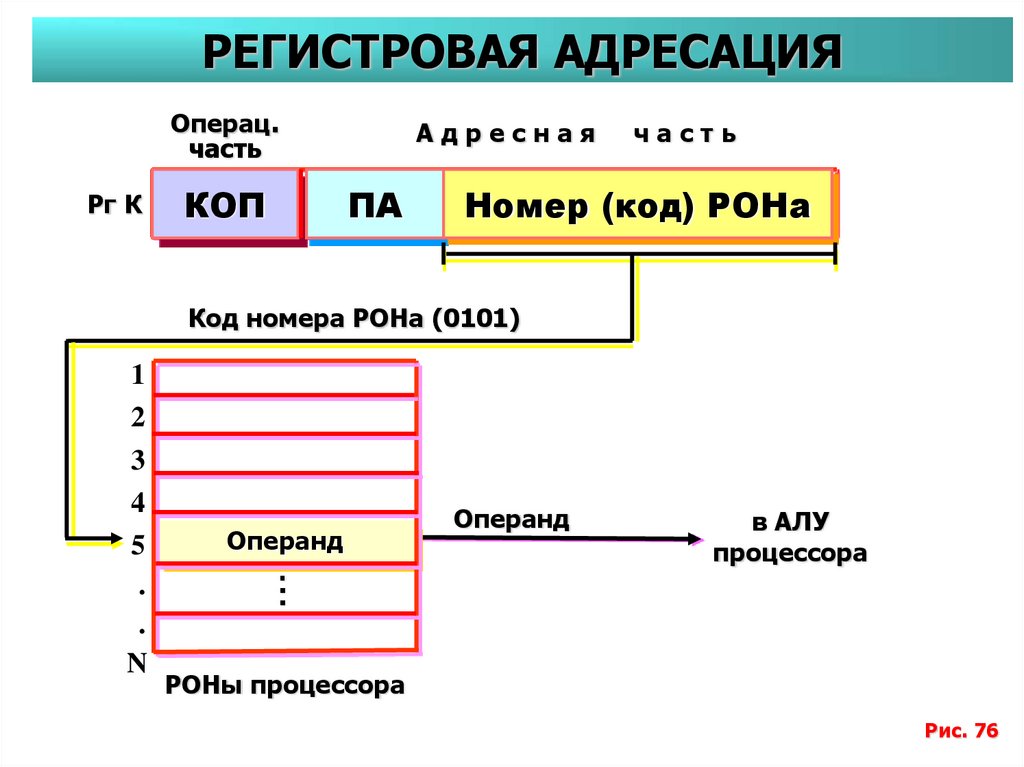

РЕГИСТРОВАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

часть

Номер (код) РОНа

Код номера РОНа (0101)

1

2

3

4

5

.

.

N

Операнд

..

.

Операнд

в АЛУ

процессора

РОНы процессора

Рис. 76

22.

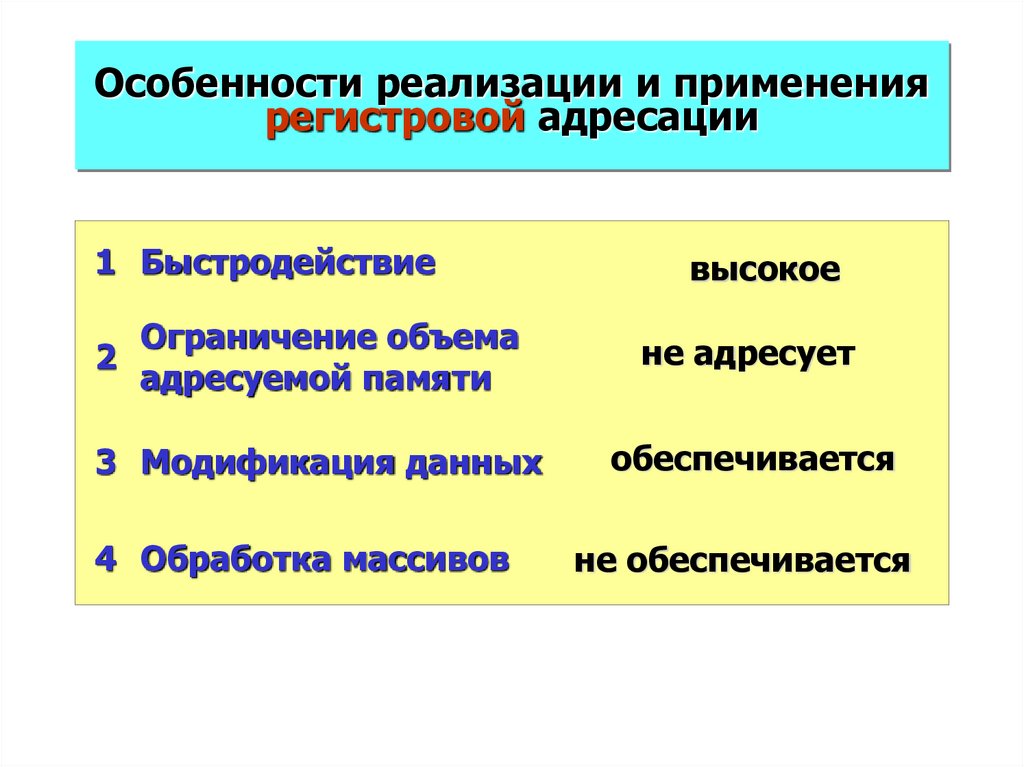

Особенности реализации и применениярегистровой адресации

1 Быстродействие

2

Ограничение объема

адресуемой памяти

3 Модификация данных

4 Обработка массивов

высокое

не адресует

обеспечивается

не обеспечивается

23.

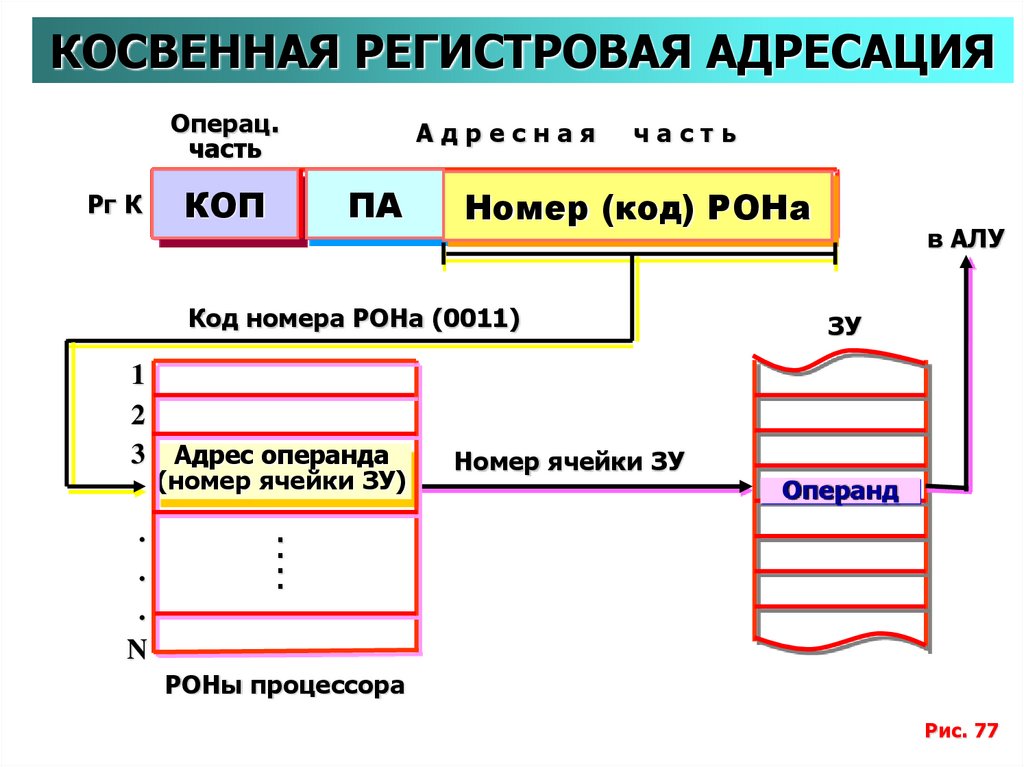

КОСВЕННАЯ РЕГИСТРОВАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

часть

Номер (код) РОНа

Код номера РОНа (0011)

1

2

3

.

.

.

N

Адрес операнда

(номер ячейки ЗУ)

Номер ячейки ЗУ

в АЛУ

ЗУ

Операнд

.

.

.

.

РОНы процессора

Рис. 77

24.

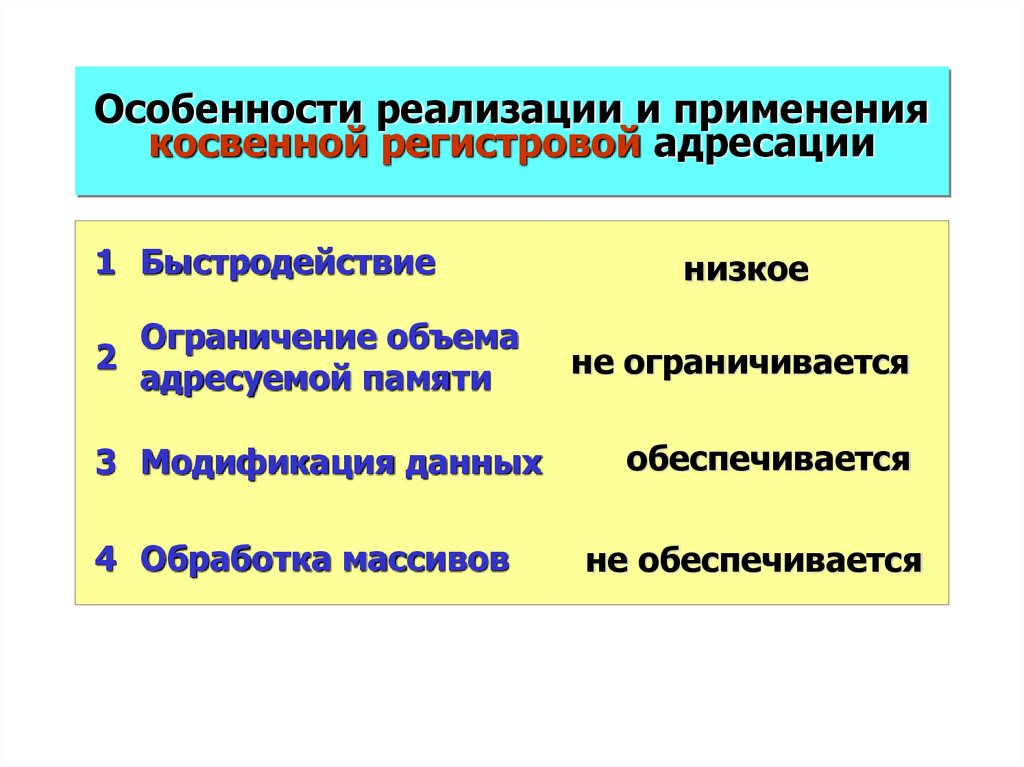

Особенности реализации и применениякосвенной регистровой адресации

1 Быстродействие

2

Ограничение объема

адресуемой памяти

3 Модификация данных

4 Обработка массивов

низкое

не ограничивается

обеспечивается

не обеспечивается

25.

АВТОИНКРЕМЕНТНАЯАВТОДЕКРЕМЕНТНАЯ

ОТНОСИТЕЛЬНАЯ

БАЗОВО-ИНДЕКСНАЯ

ИНДЕКСНАЯ

БАЗОВАЯ

Адресация

со смещением

26.

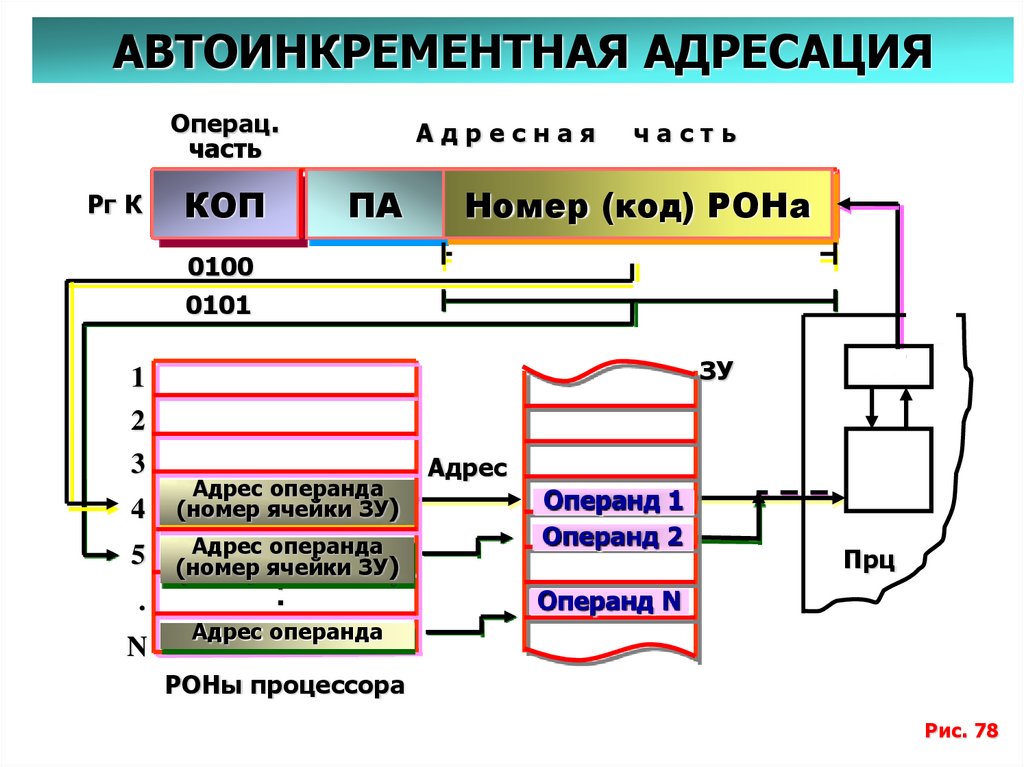

АВТОИНКРЕМЕНТНАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

часть

Номер (код) РОНа

0100

0101

+1

ЗУ

1

2

3

4

Адрес операнда

(номер ячейки ЗУ)

5

Адрес операнда

(номер ячейки ЗУ)

.

N

.

.

УУ

АЛУ

Адрес

Операнд 1

Операнд 2

Прц

Операнд N

Адрес операнда

РОНы процессора

Рис. 78

27.

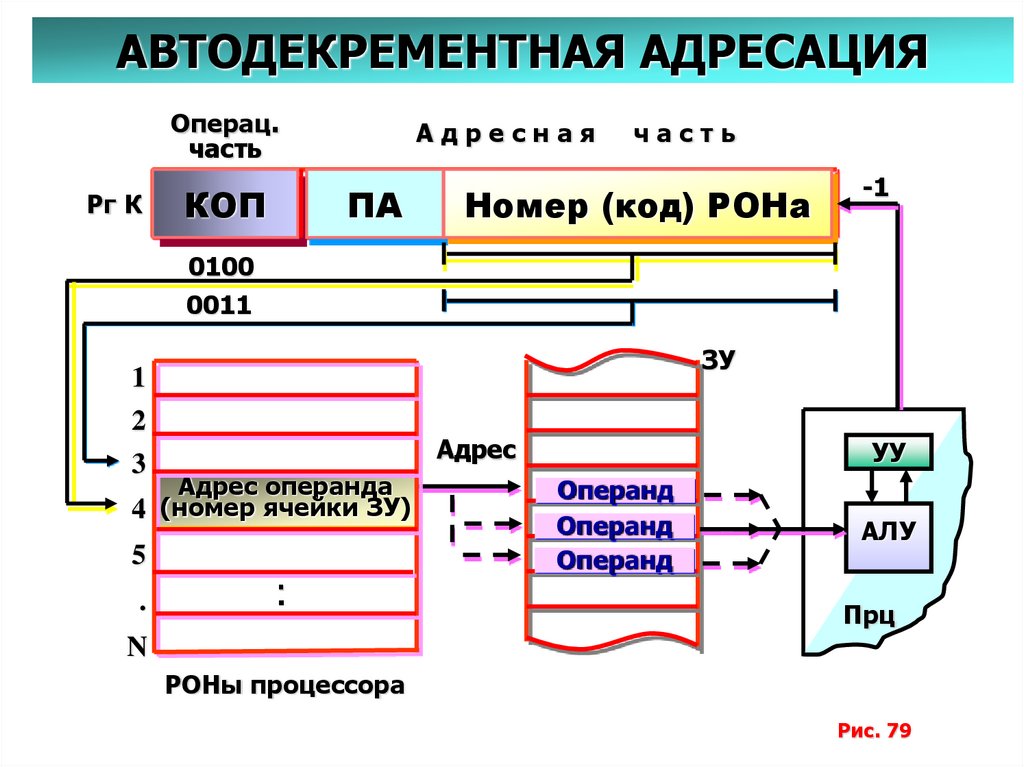

АВТОДЕКРЕМЕНТНАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

часть

Номер (код) РОНа

-1

0100

0011

ЗУ

1

2

3

Адрес

Адрес операнда

4 (номер ячейки ЗУ)

5

.

.

.

УУ

Операнд

Операнд

Операнд

АЛУ

Прц

N

РОНы процессора

Рис. 79

28.

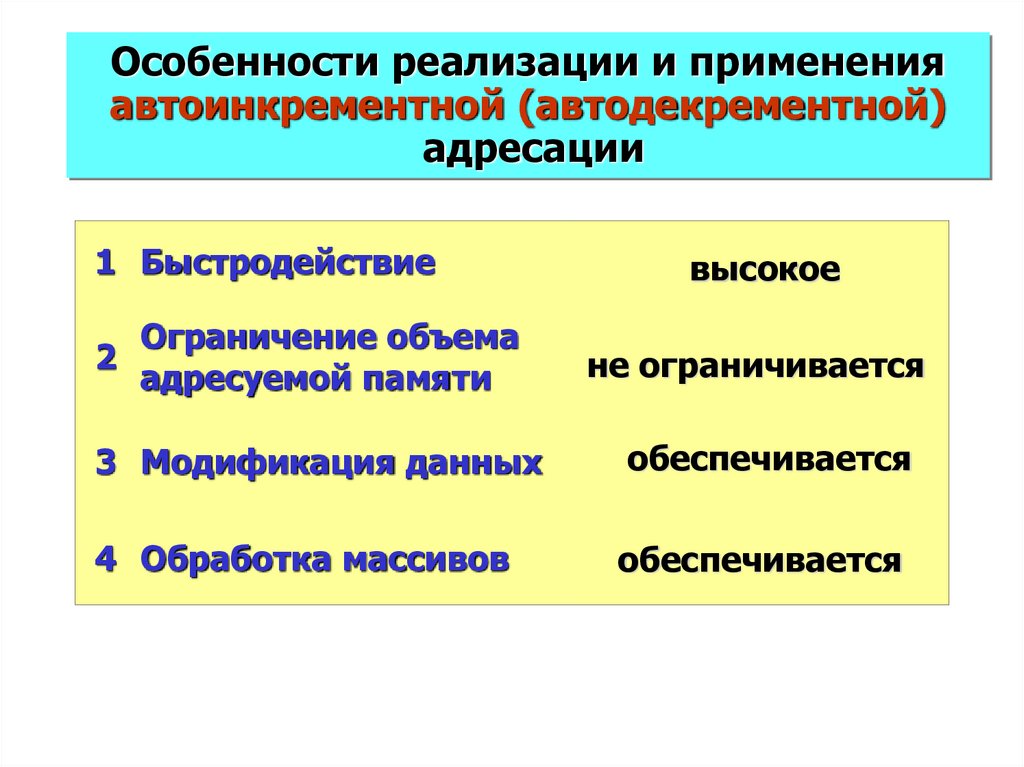

Особенности реализации и примененияавтоинкрементной (автодекрементной)

адресации

1 Быстродействие

2

Ограничение объема

адресуемой памяти

высокое

не ограничивается

3 Модификация данных

обеспечивается

4 Обработка массивов

обеспечивается

29.

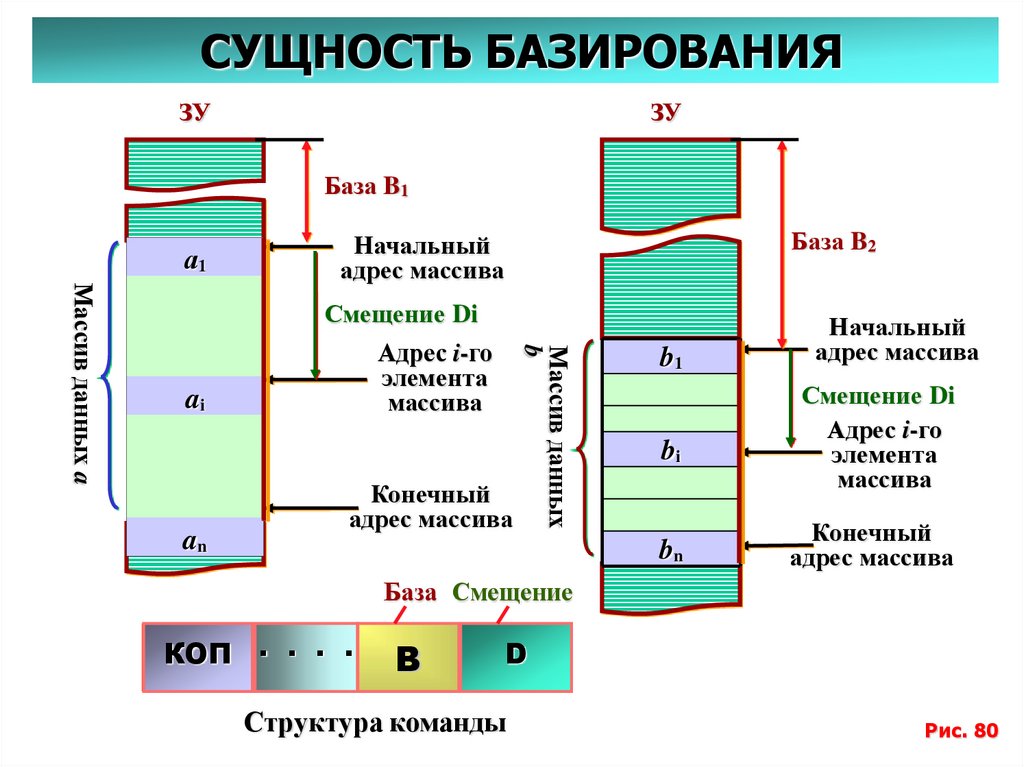

СУЩНОСТЬ БАЗИРОВАНИЯЗУ

ЗУ

База B1

а1

База B2

Смещение Di

Адрес i-го

элемента

массива

ai

an

Конечный

адрес массива

Массив данных

b

Массив данных a

Начальный

адрес массива

b1

bi

bn

Начальный

адрес массива

Смещение Di

Адрес i-го

элемента

массива

Конечный

адрес массива

База Смещение

КОП . . . .

B

D

Структура команды

Рис. 80

30.

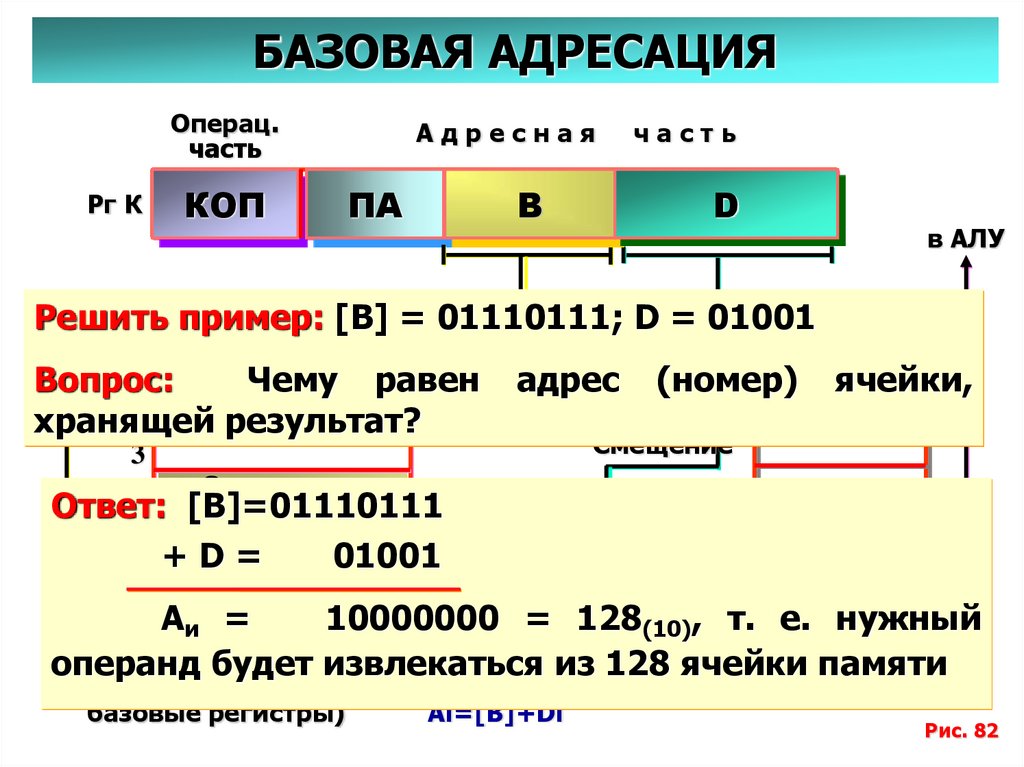

БАЗОВАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

B

часть

D

(0100) Код

номера [B]

базового

регистра

Решить

пример:

= 01110111;

D = 01001

1

Вопрос:

Чему равен

2

хранящей

результат?

адрес

(номер)

в АЛУ

ЗУ

ячейки,

Смещение

3

Содержится

4

База

Ответ:начальный

[B]=01110111

адрес

Операнд

. (база) массива

=

01001

. + D данных

. А =

10000000 = 128(10), т. е. нужный

и

СМ

N

операнд

будет извлекаться из 128 ячейки памяти

РОНы (или отдельные

базовые регистры)

Ai=[B]+Di

Рис. 82

31.

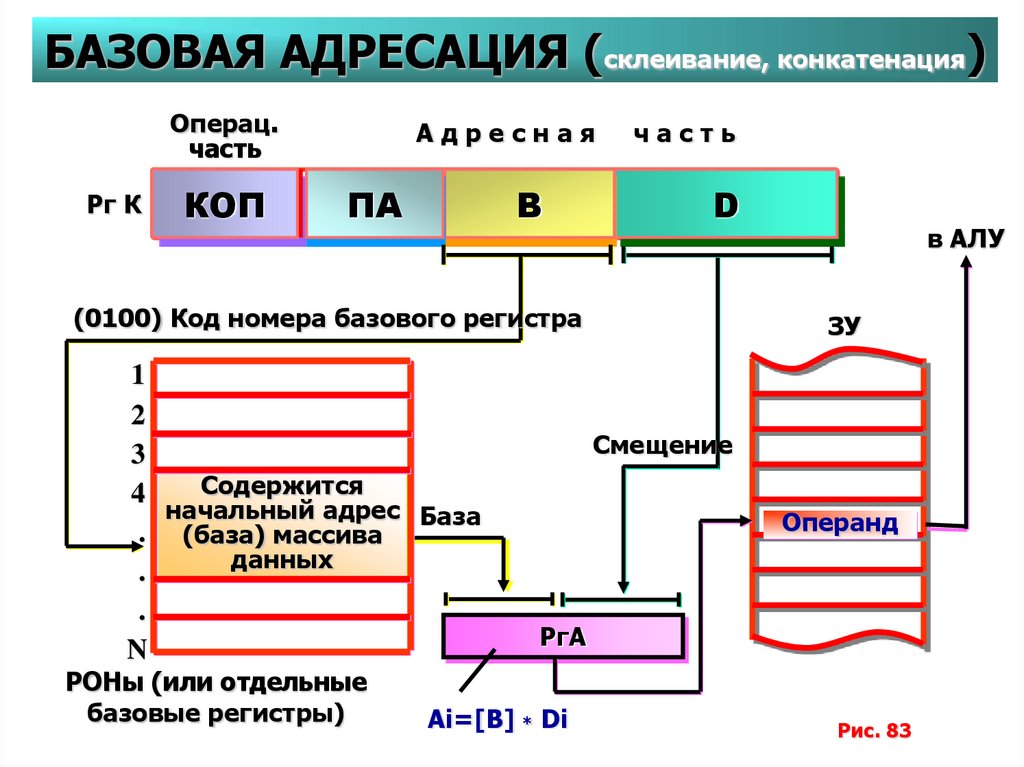

БАЗОВАЯ АДРЕСАЦИЯ (склеивание, конкатенация)Операц.

часть

Рг К

КОП

Адресная

ПА

B

часть

D

(0100) Код номера базового регистра

1

2

3

Содержится

4

начальный адрес База

. (база) массива

данных

.

.

N

РОНы (или отдельные

базовые регистры)

в АЛУ

ЗУ

Смещение

Операнд

РгА

Ai=[B] * Di

Рис. 83

32.

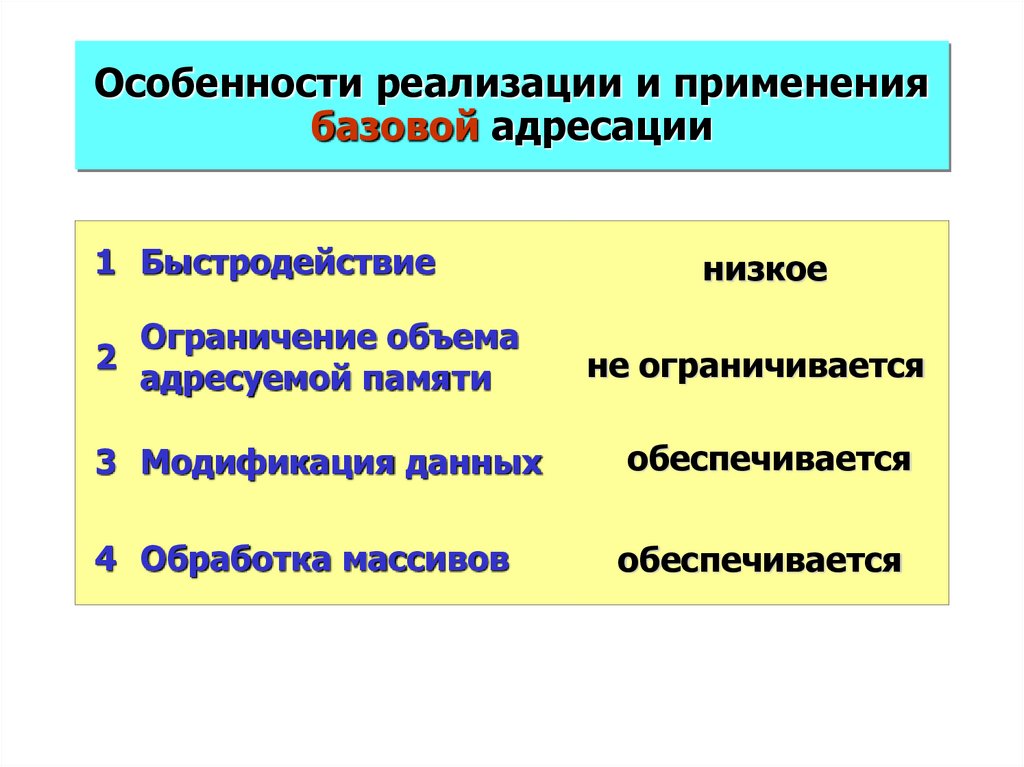

Особенности реализации и применениябазовой адресации

1 Быстродействие

2

Ограничение объема

адресуемой памяти

низкое

не ограничивается

3 Модификация данных

обеспечивается

4 Обработка массивов

обеспечивается

33.

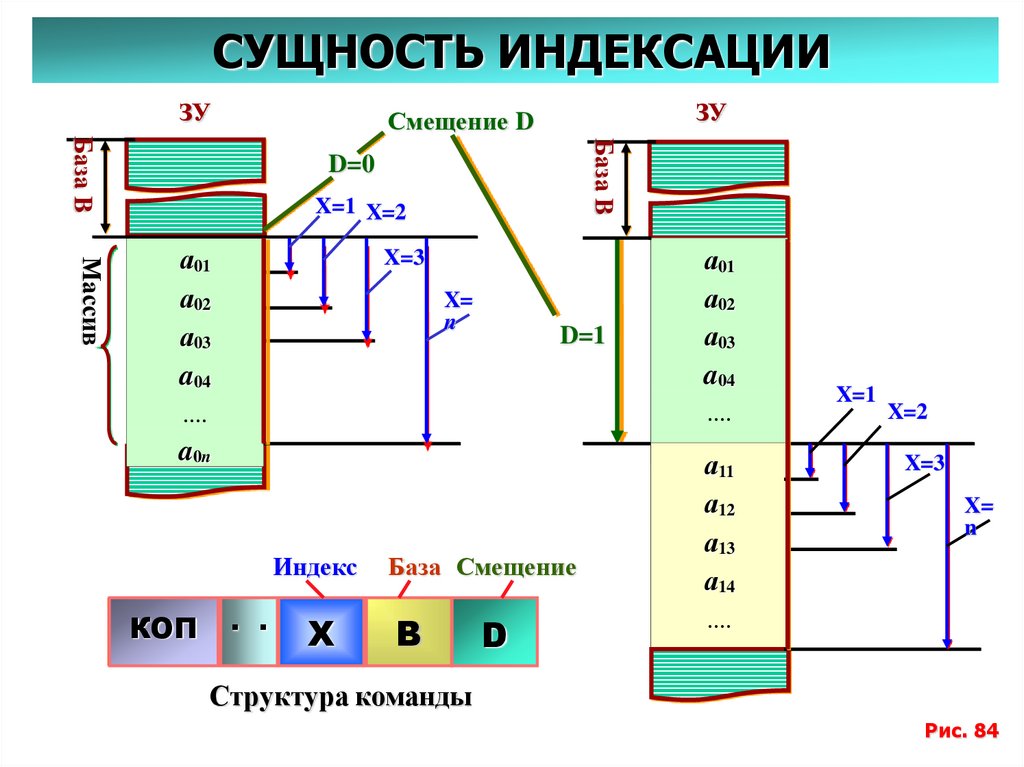

СУЩНОСТЬ ИНДЕКСАЦИИЗУ

ЗУ

Смещение D

База B

База B

D=0

X=1 X=2

Массив

а01

а02

а03

a04

X=3

X=

n

D=1

а01

а02

а03

a04

….

….

a0n

a0n

а11

а12

а13

а14

Индекс

КОП

. .

X

База Смещение

B

D

X=1

X=2

X=3

X=

n

….

a1n

Структура команды

Рис. 84

34.

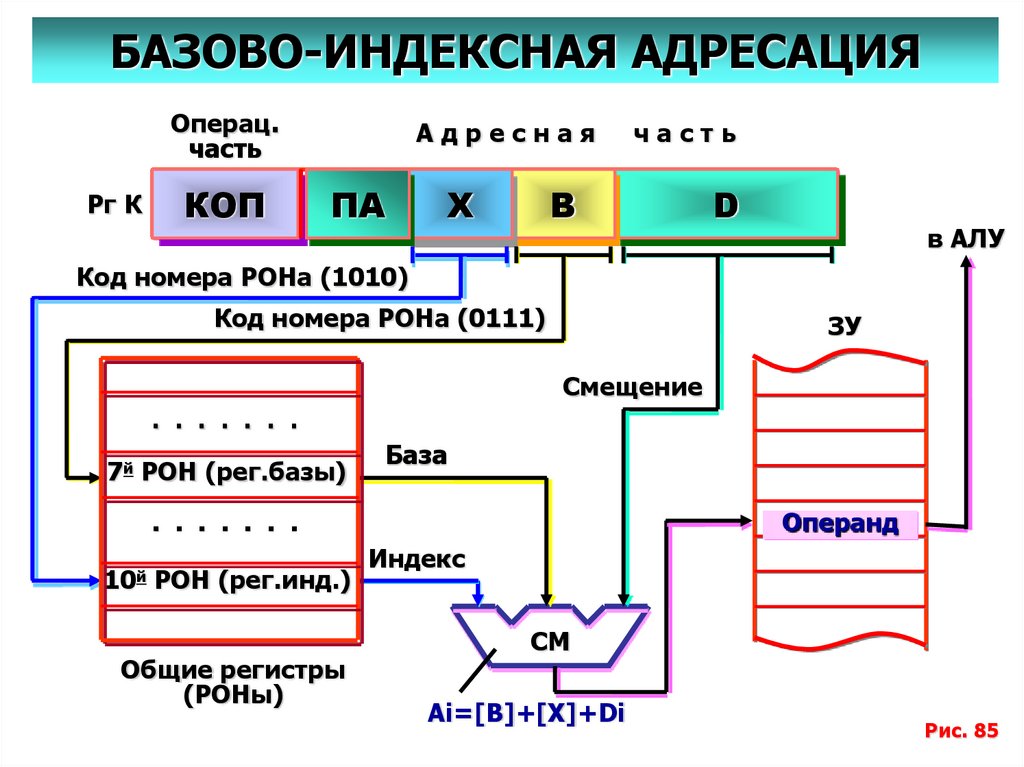

БАЗОВО-ИНДЕКСНАЯ АДРЕСАЦИЯОперац.

часть

Рг К

КОП

Адресная

ПА

X

часть

B

D

в АЛУ

Код номера РОНа (1010)

Код номера РОНа (0111)

ЗУ

Смещение

. . . . . . .

7й РОН (рег.базы)

База

. . . . . . .

10 РОН (рег.инд.)

й

Общие регистры

(РОНы)

Операнд

Индекс

СМ

Ai=[B]+[X]+Di

Рис. 85

35.

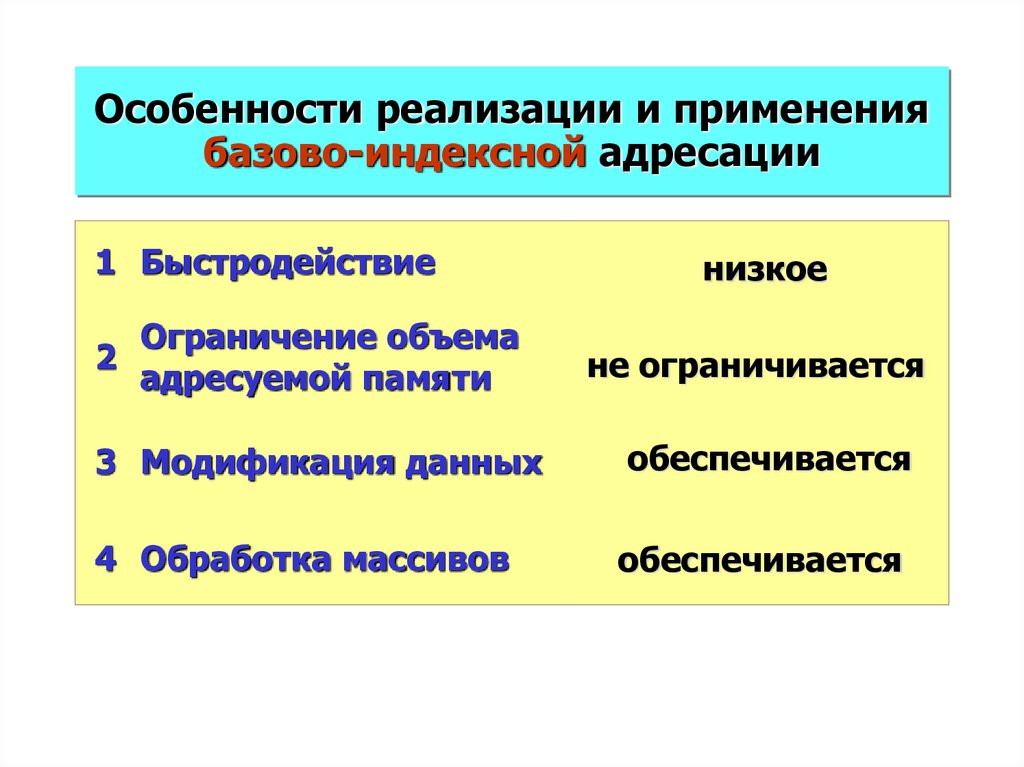

Особенности реализации и применениябазово-индексной адресации

1 Быстродействие

2

Ограничение объема

адресуемой памяти

низкое

не ограничивается

3 Модификация данных

обеспечивается

4 Обработка массивов

обеспечивается

36.

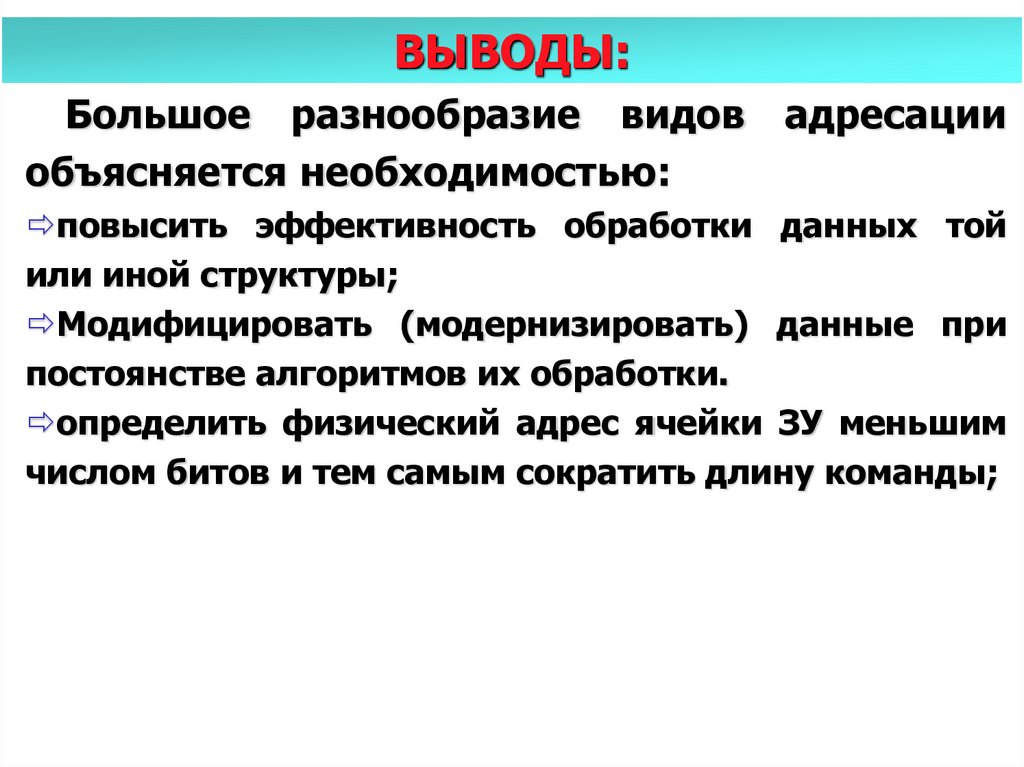

ВЫВОДЫ:Большое разнообразие видов адресации

объясняется необходимостью:

повысить эффективность обработки данных той

или иной структуры;

Модифицировать (модернизировать) данные при

постоянстве алгоритмов их обработки.

определить физический адрес ячейки ЗУ меньшим

числом битов и тем самым сократить длину команды;

Электроника

Электроника