Похожие презентации:

Jedec Standards

1. JEDEC Standards

-Nicole Okamoto and Widah SaiedAll figures from Jedec Standard JESD51-12

www.jedec.org

2. JEDEC Introduction

JEDEC was founded in 1960 and stands for the JointElectron Device Engineering Council.

JEDEC is the standardization body of the Electronic

Industries Alliance, which helps develop standards on

electronic components, consumer electronics, electronic

information, telecommunications, and internet security.

JEDEC issues often used standards for device interfaces,

such as RAM and DDR SDRAM(double-data-rate

synchronous dynamic random access memory), which is a

type of memory in integrated circuits used in computers.

Wikipedia,http://en.wikipedia.org/wiki/JEDEC

3. JEDEC Introduction

JEDEC Philosophy:JEDEC standards and publications are designed toserve the public interest through eliminating misunderstandings

between manufacturers and purchasers, facilitating interchangeability

and improvement of products.

JEDEC has 2700 participants, appointed by 270 companies work in 50

committees. The world community accepts the publications and

standards that they generate.

Jedec, http://www.jedec.org/

4. Examples of standards

JESD 22-A103C HIGH TEMPERATURE STORAGE LIFE:The test is applicable for evaluation, screening, monitoring,

and/or qualification of all solid state devices.

High Temperature storage test is typically used to determine

the effect of time and temperature, under storage

conditions, for thermally activated failure mechanisms of

solid state electronic devices

During the test elevated temperatures (accelerated test

conditions) are used without electrical stress applied.

5. Examples of standards

JESD 22-A104C TEMPERATURE CYCLING: This standard provides amethod for determining solid state devices capability to withstand extreme

temperature cycling.

JESD 22-A106B

THERMAL SHOCK: This test is conducted to determine the resistance

of a part to sudden exposure to extreme changes in temperature and

to the effect of alternate exposures to these extremes.

6. JESD 51 Methodology for the Thermal Measurement of Component Packages

JESD51-1 Integrated Circuit Thermal Measurement Method – Electrical TestMethod

JESD51-2 Integrated Circuit Thermal Test Method Environmental Conditions –

Natural Convection

JESD51-3 Low Effective Thermal Conductivity Test Board for Leaded Surface

Mount Packages

JESD51-4 Thermal Test Chip Guideline

JESD51-5 Extension of Thermal Test Board Standards for Packages with Direct

Thermal Attachment Mechanisms

JESD51-6 Integrated Circuit Thermal Test Method Environmental Conditions –

Forced Convection

JESD51-7 High Effective Thermal Conductivity Test Board for Leaded Surface

Mount Packages

7. JESD 51 cont.

JESD51-8 Integrated Circuit Thermal Test Method Environmental Conditions –Junction to Board

JESD51-9 Test Boards for Area Array Surface Mount Package Thermal

Measurements

JESD51-10 Test Boards for Through-Hole Perimeter Leaded Package Thermal

Measurements

JESD51-11 Test Boards for Through-Hole Area Array Leaded Package Thermal

Measurements

JESD51-12 Guidelines for Reporting and Using Electronic Package Thermal

Information

8.

9. JESD 22-A103C High Temperature Storage Life

Scope: Determine the effect of time and temperature, under storageconditions, of thermally activated failure mechanisms of solid state

electronic devices.

Jedec Standard,http://www.jedec.org/download/search/22a103c.pdf

10. Apparatus of Test

The apparatus is a temperature controlled chambercapable of maintaining the entire sample population

at a specified testing temperature.

11. Method of Testing

The samples will be stored at one of the temperature conditionsgiven in Table 1:

Table 1: High Temperature Storage Conditions

Condition A: +125(-0/+10) ºC

Condition B: +150(-0/+10) ºC

Condition C: +175(-0/+10) ºC

Condition D: +200(-0/+10) ºC

Condition E: +250(-0/+10) ºC

Condition F: +300(-0/+10) ºC

Condition G: +85(-0/+10) ºC

12. Method of Testing

Typically, the sample is tested under condition B for 1000 hours, butother conditions or durations may be used.

Note: the rate of temperature increase should be low to prevent

overstress of the sample that would not occur under normal conditions.

The failure criteria for a sample is:

The part can no longer function as designed

Cracking, chipping, or breaking of the package as long as the package

performance was critical to the performance of the sample. However, if the

damage was due to fixtures or handling, then failure is not attributed to

the test.

13. Method of Testing

Things to be specified:Sample size and number of failures

Time and conditions

Whether intermediate measurements were taken

14. JESD51-12 Guidelines for Reporting and Using Electronic Package Thermal Information

qJA junction-to-still ambient air resistance (natural convectionq JA

Tj Ta

P

qJMA junction-to-moving air resistance (forced convection)

15.

16. Deviations During Application

Results during application may vary since theapplication may differ from the following test

conditions:

Power dissipation

Air velocity, direction, turbulence

Power and number of adjacent components and boards

PCB orientation and size

Two-sided vs. one-sided mounting

Die size

Copper trace thickness and widths

Environment (for example, natural convection tests are done

in a chamber 1 ft3)

17. Conduction resistances

qjctop, qjcbot – junction to top of case and bottom ofcase resistances, respectively

q JCx

qjb – junction to board resistances

TJ Tcase

P

Leaded package: measure Tboard to foot of lead

Surface mount package: measure board trace within 1

mm of package

These resistances are found by forcing all of the

heat flow to go out the respective surface, which

may not match reality

18. Thermal Characterization Parameter

ΨJT – junction to top thermal characterizationΨJB – junction to board thermal characterization

The equations are the same as those for thermal

resistance q except that the power P is now the total

power, not just the power in that direction. For

example, if only 5% of your total heat loss is down

through the PCB, your P would still be your total

power.

These can help with estimates of junction

temperature for object already under use where

temperatures can be measured and there is no heat

sink present (instead of for the design phase)

19. Compact Models

Two-resistor model: good for hand calculations butnot really accurate

20. DELPHI Compact Models

These are mathematical models, not thermalresistance model

Provided by some component manufacturers

21. Effect of Package Construction on Thermal Results

2s0p: two signal planes, zero power planes onlaminate substrate for plastic ball grid array packages

Added copper improves performance

22. Effect of PCB Design

More copper to spread heat means betterperformance.

23. Effect of Multiple Packages

24. Effect of PCB size

On setups where a lot of heat is carried away by thecopper in the PCB, the larger the PCB the better the

performance – more heat transfer area.

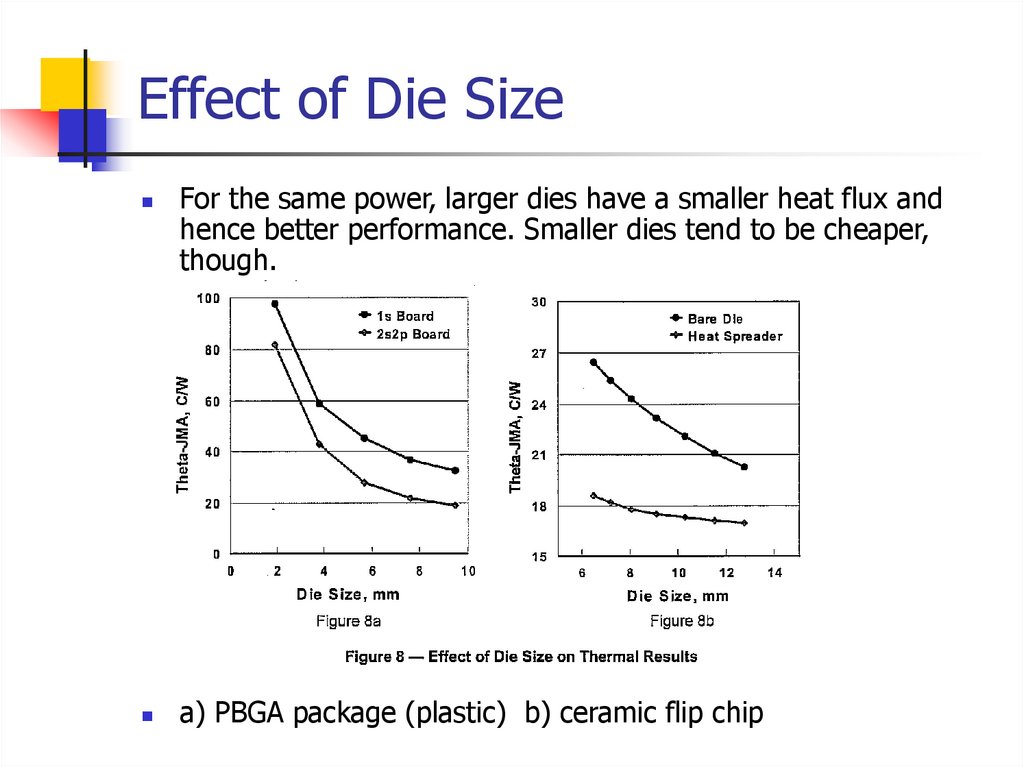

25. Effect of Die Size

For the same power, larger dies have a smaller heat flux andhence better performance. Smaller dies tend to be cheaper,

though.

a) PBGA package (plastic) b) ceramic flip chip

26. Effect of Die Power Level

As power levels go up, so do surface temperatures.This increases natural convection and radiation,

decreasing qJA

27. Reporting Requirement Examples

28. Reporting Requirement Examples

29. Reference

Jedec the Standards Resource for the World Semiconductor Industry (October 2006). http://www.jedec.org.

Jedec Standard JESD 22-A103C High Temperature Storage Temperature . Retrieved October 2006.

http://www.jedec.org/download/search/22a103c.pdf.

Jedec Standard JESD51-12 Guidelines for Reporting and Using Electronic Package Thermal Information.

Retreived October 2006. www.jedec.org.

Wikipedia the Free Encyclopedia(October 2006). Jedec. Retrieved October 2006.

http://en.wikipedia.org/wiki/JEDEC .

Право

Право