Похожие презентации:

Базові матричні кристали (Gate Array - GA). Програмовані користувачем вентильні матриці. Лекція 2-11

1.

Харківський національний університет радіоелектронікиЛЕКЦІЯ 2-11

Базові матричні кристали

(Gate Array - GA)

Програмовані користувачем вентильні

матриці (FPGA – Field Programmable

Gate Array)

Кафедра КІТС

Корабльов М.М.

2.

Харківський національний університет радіоелектронікиБазові матричні кристали (Gate Array - GA)

Базові матричні кристали (БМК) належать до напівзамовних схем.

БМК є універсальними кристалами-заготовками, розташованими на

напівпровідниковій пластині. БМК програмують, утворюючи відповідні

з’єднання фотолітографією металевих шарів:

а) у маскових програмованих БМК, (Mask Programmable Gate Arrays,

MPGA) - видаляючи непотрібні з’єднання, або навпаки,

б) утворюючи потрібні з’єднання за допомогою лазерного променю

у програмованих лазером БМК (Laser Programmable Gate Arrays, LPGA).

Для виготовлення спеціалізованих ВІС на основі БМК проектуються і

виготовляються фотошаблони або програми, які необхідні для

формування електричних зв’язків за заданою принциповою

електричною схемою або руйнування металевих з’єднань електронним

променем. Як правило, для реалізації електричних з’єднань необхідно

від 1 до 3 шарів металізації або міжшарових з’єднань.

Функціональні елементи різного ступеня складності формуються з

базових комірок на основі бібліотеки топологій функціональних

елементів, спроектованих щодо конкретного складу й розташування

комірок матриці.

Кафедра КІТС

Корабльов М.М.

3.

Харківський національний університет радіоелектронікиБазові матричні кристали (Gate Array - GA)

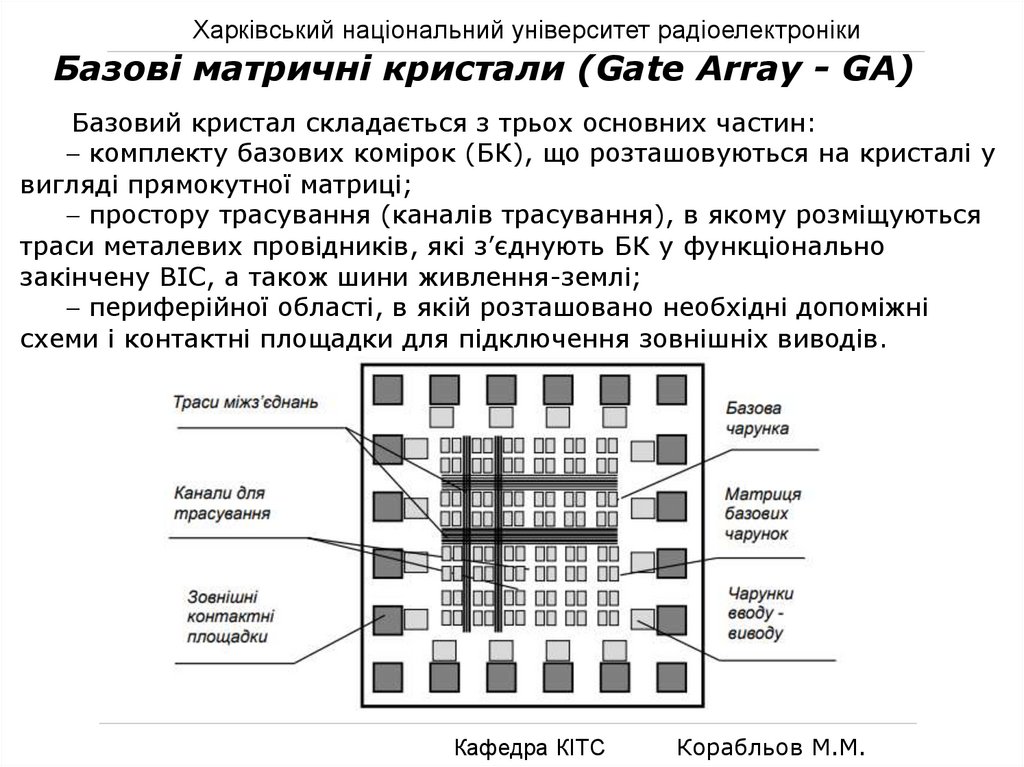

Базовий кристал складається з трьох основних частин:

комплекту базових комірок (БК), що розташовуються на кристалі у

вигляді прямокутної матриці;

простору трасування (каналів трасування), в якому розміщуються

траси металевих провідників, які з’єднують БК у функціонально

закінчену ВІС, а також шини живлення-землі;

периферійної області, в якій розташовано необхідні допоміжні

схеми і контактні площадки для підключення зовнішніх виводів.

Кафедра КІТС

Корабльов М.М.

4.

Харківський національний університет радіоелектронікиБазові матричні кристали (Gate Array - GA)

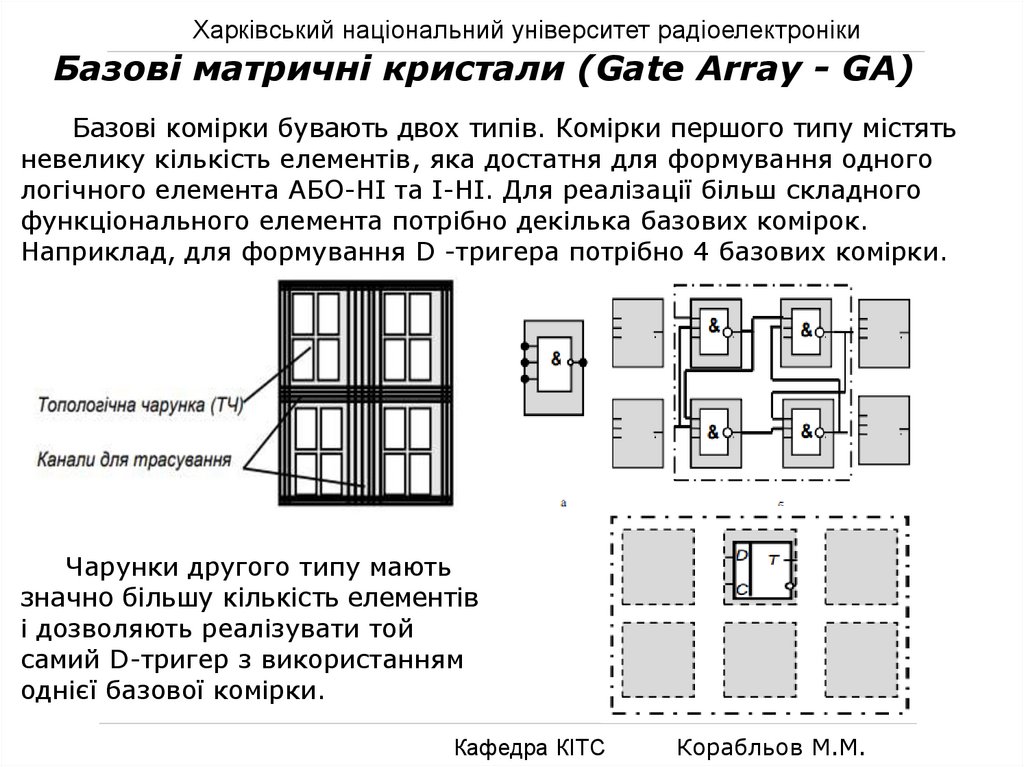

Базові комірки бувають двох типів. Комірки першого типу містять

невелику кількість елементів, яка достатня для формування одного

логічного елемента АБО-НІ та І-НІ. Для реалізації більш складного

функціонального елемента потрібно декілька базових комірок.

Наприклад, для формування D -тригера потрібно 4 базових комірки.

Чарунки другого типу мають

значно більшу кількість елементів

і дозволяють реалізувати той

самий D-тригер з використанням

однієї базової комірки.

Кафедра КІТС

Корабльов М.М.

5.

Харківський національний університет радіоелектронікиБазові матричні кристали (Gate Array - GA)

Для спрощення проектування матричних ВІС широко

використовуються бібліотеки функціональних елементів (БФЕ).

БФЕ містить схеми електричні та креслення специфікації БК для

виконання схемотехнічних і логічних функцій.

Креслення специфікації БК – це способи з’єднання елементів

комірки або комірок БМК, які забезпечують реалізацію заданого

функціонального елемента.

Бібліотечні елементи першого рівня формуються на основі тих

елементів, що входять до складу топологічної комірки БМК. Елементи

першого рівня за своїми логічними можливостями еквівалентні 1...20

елементам І-НІ (АБО-НІ). Вони виконують функції різних логічних

елементів, тригерів, мультиплексорів, дешифраторів тощо.

З використанням БК з розширеним набором елементів,

макроелементи першого рівня можуть складатися з простих цифрових

вузлів: регістрів; лічильників; суматорів с числом розрядів 2...4 та ін.

Макроелементи другого рівня реалізуються на базі декількох поруч

розташованих БК. Вони виконують функції досить складних цифрових

вузлів: багаторозрядних лічильників; регістрів; перетворювачів кодів;

арифметико-логічних пристроїв та ін.

Кафедра КІТС

Корабльов М.М.

6.

Харківський національний університет радіоелектронікиБазові матричні кристали (Gate Array - GA)

Макроелементи третього рівня – це складні функціональні пристрої,

які включаються до БМК високого ступеня інтеграції.

Склад макроелементів третього рівня:

мікропроцесорні секції;

контролери;

програмовані логічні пристрої;

вузли оперативних і постійних запам’ятовувальних пристроїв та ін.

Макроелементи третього рівня реалізуються на базі макроелементів

першого й другого рівнів.

До складу БФЕ входять також допоміжні елементи:

вхідні й вихідні транслятори;

буферні каскади для передачі сигналів довгими внутрішніми

зв’язками на кристалі;

спеціальні джерела напруги або струмів.

Вони виконуються на базі спеціалізованих периферійних або

внутрішніх комірок БМК. Транслятори перетворюють рівні напруги

внутрішніх сигналів БМК у рівні напруги, що характерні для зовнішніх

кіл.

Кафедра КІТС

Корабльов М.М.

7.

Харківський національний університет радіоелектронікиБМК з однорідними логічними комірками

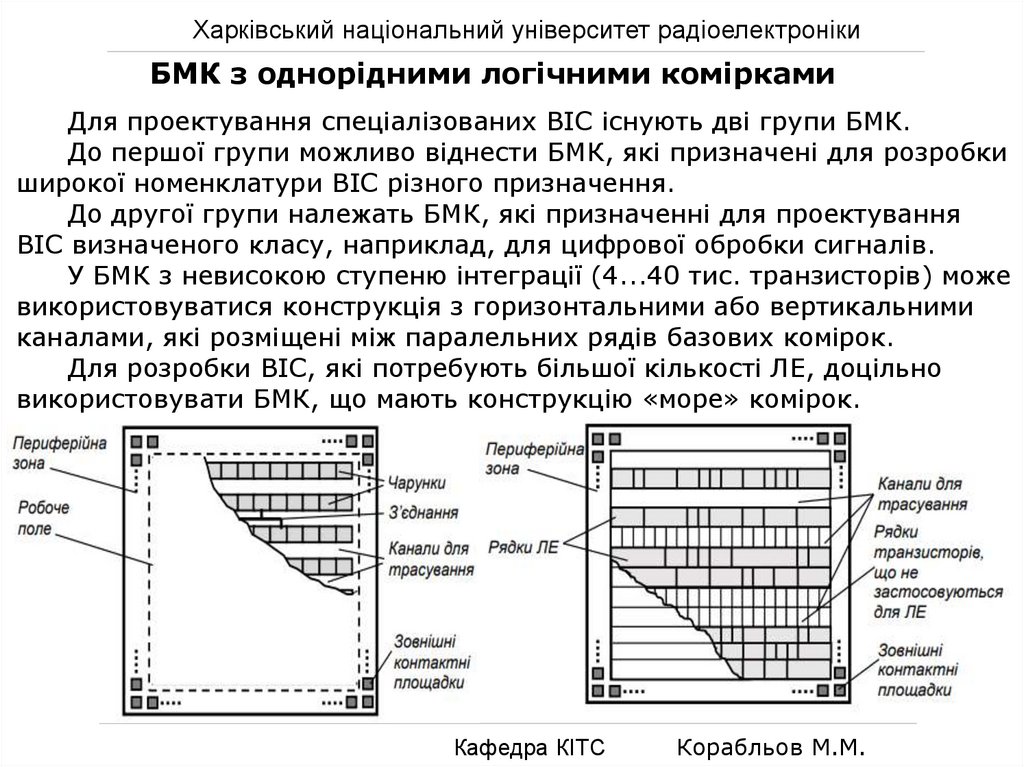

Для проектування спеціалізованих ВІС існують дві групи БМК.

До першої групи можливо віднести БМК, які призначені для розробки

широкої номенклатури ВІС різного призначення.

До другої групи належать БМК, які призначенні для проектування

ВІС визначеного класу, наприклад, для цифрової обробки сигналів.

У БМК з невисокою ступеню інтеграції (4...40 тис. транзисторів) може

використовуватися конструкція з горизонтальними або вертикальними

каналами, які розміщені між паралельних рядів базових комірок.

Для розробки ВІС, які потребують більшої кількості ЛЕ, доцільно

використовувати БМК, що мають конструкцію «море» комірок.

Кафедра КІТС

Корабльов М.М.

8.

Харківський національний університет радіоелектронікиБлокова архітектура БМК

БМК високого ступеня інтеграції реалізуються у вигляді декількох

блоків – підматриць. Кожен з блоків має структуру БМК меншого

ступеня інтеграції, а між ними розташовуються горизонтальні та

вертикальні канали для з’єднань.

Друга група БМК з блоковою структурою містить у своєму складі

функціонально закінчені блоки (АЛП, ОЗП, ПЗП), спеціалізовані

елементи – макрокомірки (тригери, регістри тощо).

Кафедра КІТС

Корабльов М.М.

9.

Харківський національний університет радіоелектронікиБлокова архітектура БМК

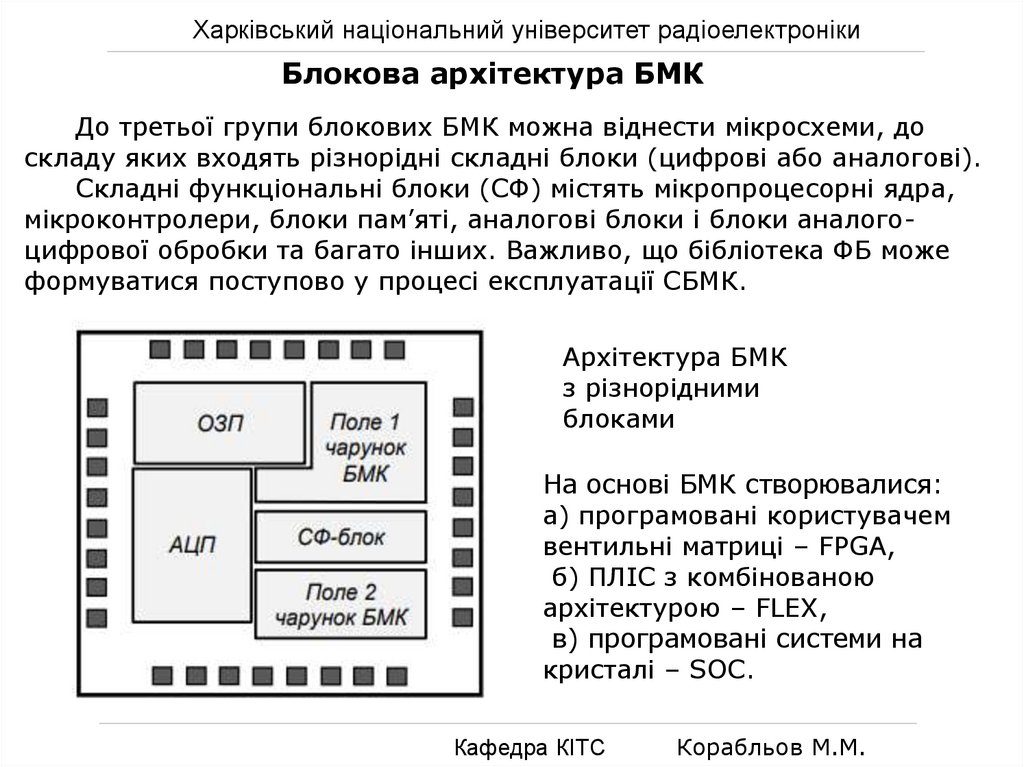

До третьої групи блокових БМК можна віднести мікросхеми, до

складу яких входять різнорідні складні блоки (цифрові або аналогові).

Складні функціональні блоки (СФ) містять мікропроцесорні ядра,

мікроконтролери, блоки пам’яті, аналогові блоки і блоки аналогоцифрової обробки та багато інших. Важливо, що бібліотека ФБ може

формуватися поступово у процесі експлуатації СБМК.

Архітектура БМК

з різнорідними

блоками

На основі БМК створювалися:

а) програмовані користувачем

вентильні матриці – FPGA,

б) ПЛІС з комбінованою

архітектурою – FLEX,

в) програмовані системи на

кристалі – SOC.

Кафедра КІТС

Корабльов М.М.

10.

Харківський національний університет радіоелектронікиПрограмовані користувачем вентильні матриці

(FPGA – Field Programmable Gate Array)

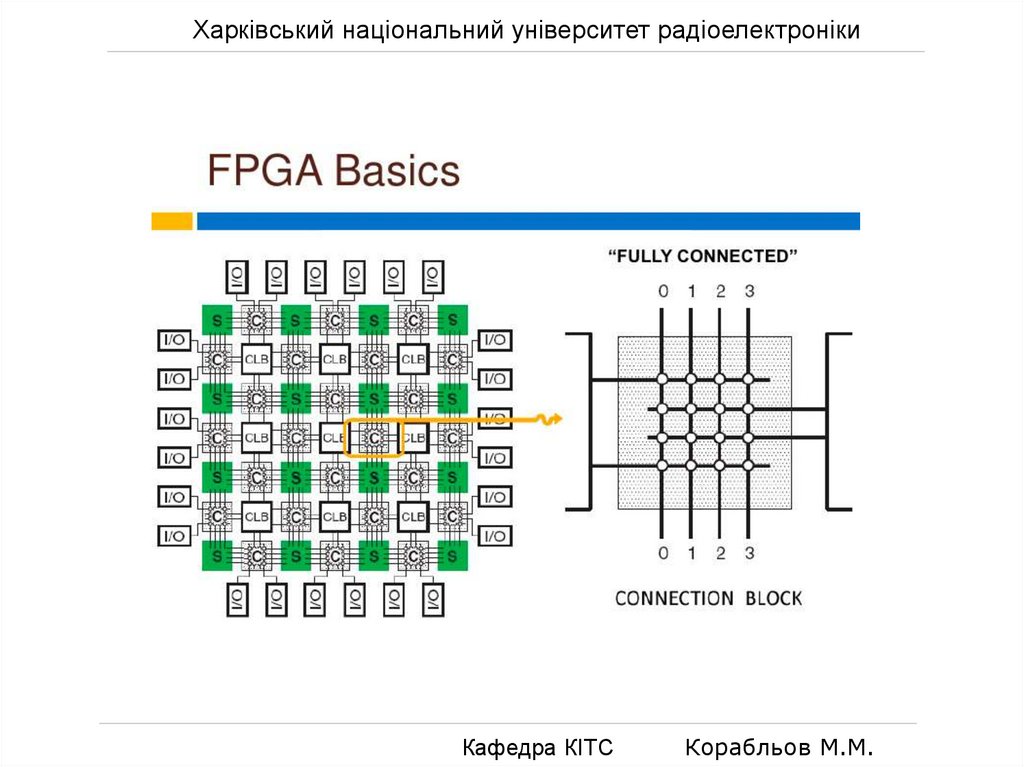

Програмовані користувачем вентильні матриці (ПКВМ - FPGA) мають

архітектуру, подібну до БМК.

FPGA являють собою мікросхеми високого рівня інтеграції, що

містять у внутрішній ділянці матрицю конфігурованих логічних блоків

(CLB), систему їх міжз'єднань, розміщену між рядками і стовпцями

матриці, а в периферійній ділянці - блоки введення-виведення (БВВ).

Базова архітектура FPGA складається з тисяч фундаментальних

елементів (конфігурованих логічних блоків CLB), оточених системою

програмованих взаємозв'язків, яка направляє сигнали між CLB.

Залежно від виробника, CLB може також називатися логічним блоком

(LB),логічним елементом (LE) або логічною коміркою (LC).

Всі частини FPGA є конфігурованими (реконфігурованими) причому,

на відміну від обчислювальних матриць, засобами користувачів.

При конфігуруванні FPGA CLB налаштовуються на виконання

необхідних операцій перетворення даних, а система міжз'єднань - на

необхідні зв'язку між CLB.

Кафедра КІТС

Корабльов М.М.

11.

Харківський національний університет радіоелектронікиПрограмовані користувачем вентильні матриці

(FPGA – Field Programmable Gate Array)

Кафедра КІТС

Корабльов М.М.

12.

Харківський національний університет радіоелектронікиКафедра КІТС

Корабльов М.М.

13.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA (CLB)

Для характеристики CLB застосовують поняття «зернистість» або

«гранульованість» (Granularity) і «функціональність» (Functionality).

Перша властивість демонструє, наскільки дрібними є частини, з яких

можливо реалізовувати потрібні схеми, друга – наскільки великі логічні

можливості КЛБ.

Програмування «дрібнозернистих» кристалів здійснюється за

допомогою перепалюваних перемичок (fuse) або нарощуваних

перемичок – пробиваних діелектричних прошарків (antifuse).

Мікросхеми FPGA на «великозернистих» КЛБ включають матрицю

КЛБ, лінії зв’язку, які з’єднані між собою програмованими

перемикаючими блоками (ППБ), та блоки введення/виведення.

ЛБ можуть бути виконані у вигляді простих логічних вентилів,

логічних модулів на основі мультиплексорів, логічних модулів на основі

програмованих ЗП (LUT).

При реалізації на простих логічних вентилях (дрібнозернисті CLB)

блоки складаються найчастіше з транзисторних компліментарних пар, з

яких збираються КМОП логічні елементи.

У разі реалізації CLB на програмованих мультиплексорах вихідна

величина описується деякою породжуючою функцією, що відповідає

використанню всіх входів схеми як інформаційних.

Кафедра КІТС

Корабльов М.М.

14.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

Фірма Actel у своєму сімействі мікросхем застосовує CLB на основі

мультиплексорів. Функціональна характеристика для цього блоку

має вигляд:

Залежно від значення сигналів на входах КЛБ, можливо

реалізувати 702 відмінних комбінаційних функції. Для програмування

фірма Actel застосовує технологію нарощування перемичок antifuse.

Кафедра КІТС

Корабльов М.М.

15.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

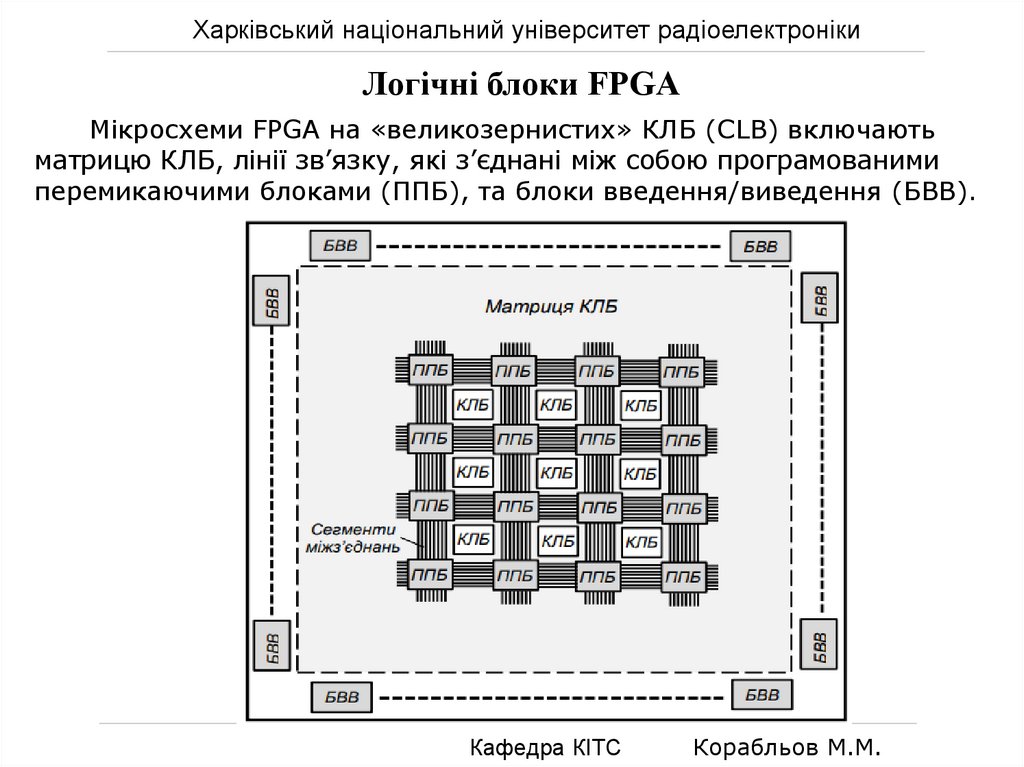

Мікросхеми FPGA на «великозернистих» КЛБ (CLB) включають

матрицю КЛБ, лінії зв’язку, які з’єднані між собою програмованими

перемикаючими блоками (ППБ), та блоки введення/виведення (БВВ).

Кафедра КІТС

Корабльов М.М.

16.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

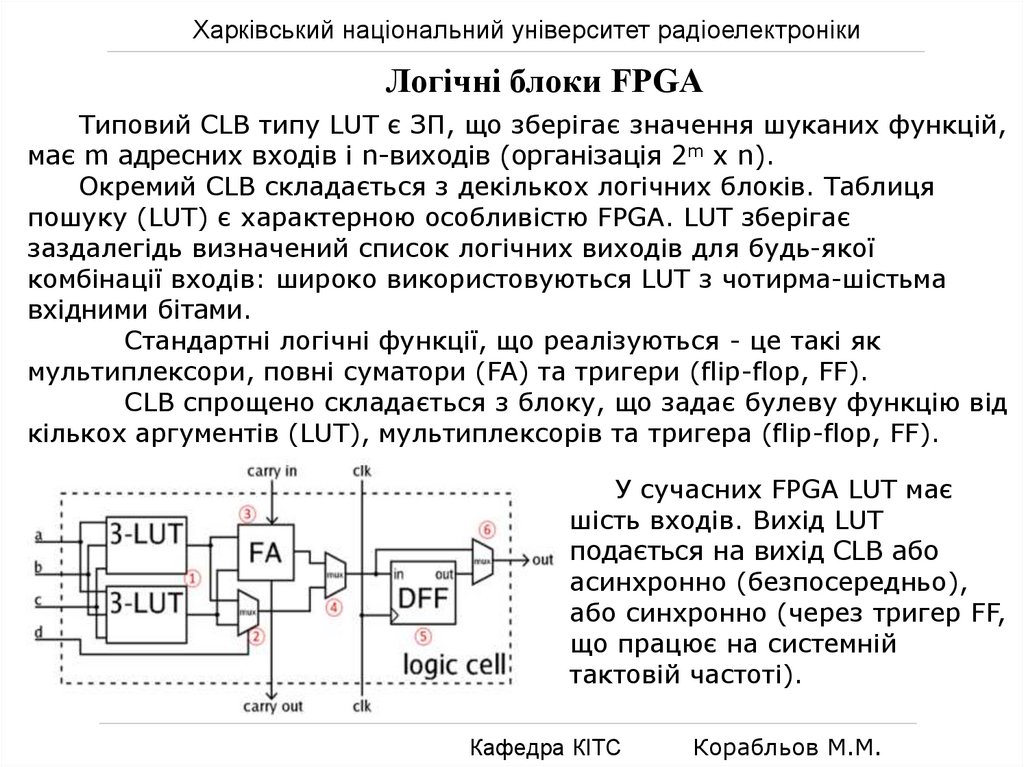

Типовий CLB типу LUT є ЗП, що зберігає значення шуканих функцій,

має m адресних входів і n-виходів (організація 2m x n).

Окремий CLB складається з декількох логічних блоків. Таблиця

пошуку (LUT) є характерною особливістю FPGA. LUT зберігає

заздалегідь визначений список логічних виходів для будь-якої

комбінації входів: широко використовуються LUT з чотирма-шістьма

вхідними бітами.

Стандартні логічні функції, що реалізуються - це такі як

мультиплексори, повні суматори (FA) та тригери (flip-flop, FF).

CLB спрощено складається з блоку, що задає булеву функцію від

кількох аргументів (LUT), мультиплексорів та тригера (flip-flop, FF).

У сучасних FPGA LUT має

шість входів. Вихід LUT

подається на вихід CLB або

асинхронно (безпосередньо),

або синхронно (через тригер FF,

що працює на системній

тактовій частоті).

Кафедра КІТС

Корабльов М.М.

17.

Харківський національний університет радіоелектронікиПринципи реалізації LUT

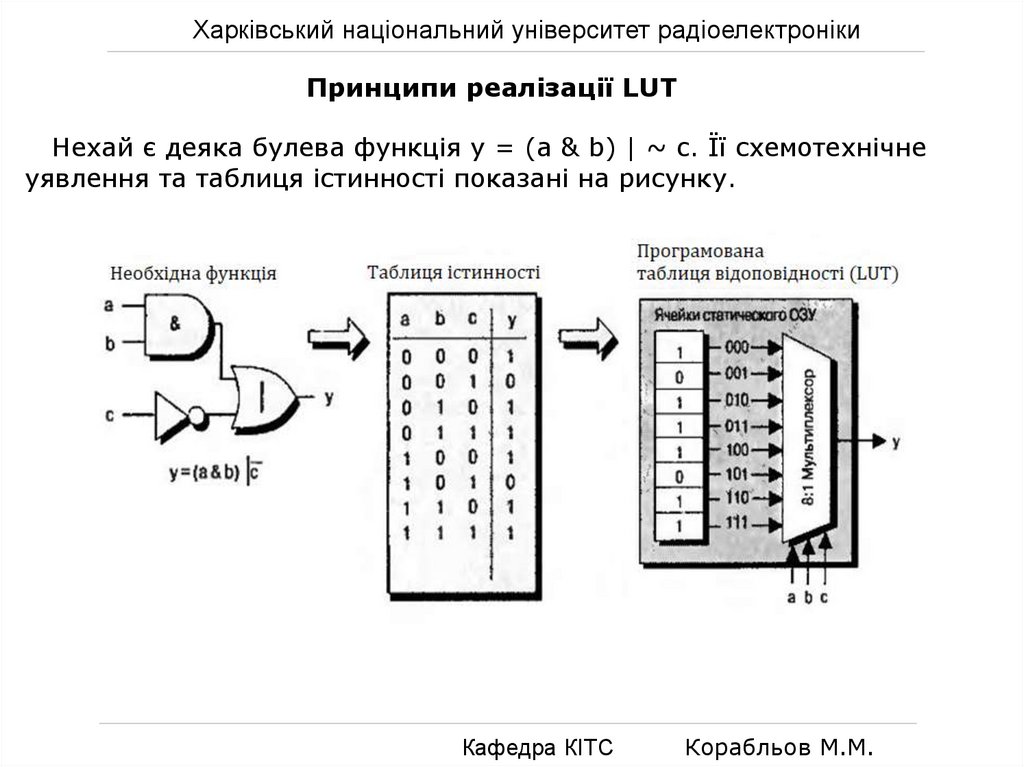

Нехай є деяка булева функція y = (a & b) | ~ c. Її схемотехнічне

уявлення та таблиця істинності показані на рисунку.

Кафедра КІТС

Корабльов М.М.

18.

Харківський національний університет радіоелектронікиПринципи реалізації LUT

4-входовий LUT, що реалізує таблицю істинності (truth table)

комбінаційної функції Y.

Кафедра КІТС

Корабльов М.М.

19.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

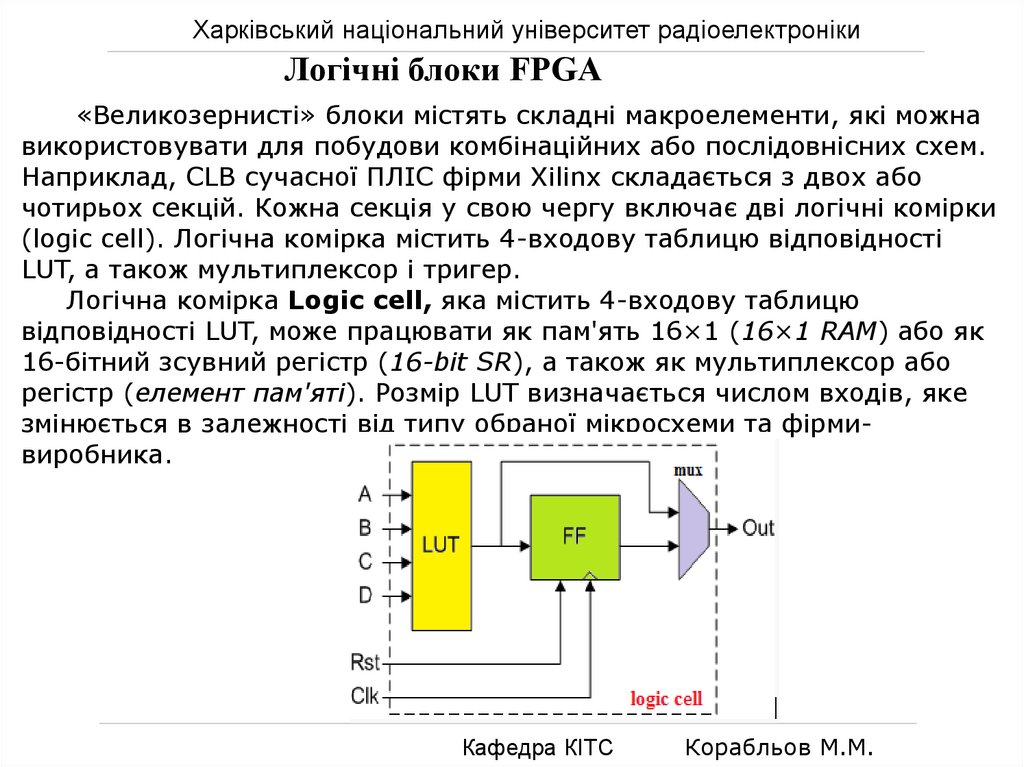

«Великозернисті» блоки містять складні макроелементи, які можна

використовувати для побудови комбінаційних або послідовнісних схем.

Наприклад, CLB сучасної ПЛІС фірми Xilinx складається з двох або

чотирьох секцій. Кожна секція у свою чергу включає дві логічні комірки

(logic cell). Логічна комірка містить 4-входову таблицю відповідності

LUT, а також мультиплексор і тригер.

Логічна комірка Logic cell, яка містить 4-входову таблицю

відповідності LUT, може працювати як пам'ять 16×1 (16×1 RAM) або як

16-бітний зсувний регістр (16-bit SR), а також як мультиплексор або

регістр (елемент пам'яті). Розмір LUT визначається числом входів, яке

змінюється в залежності від типу обраної мікросхеми та фірмивиробника.

Кафедра КІТС

Корабльов М.М.

20.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

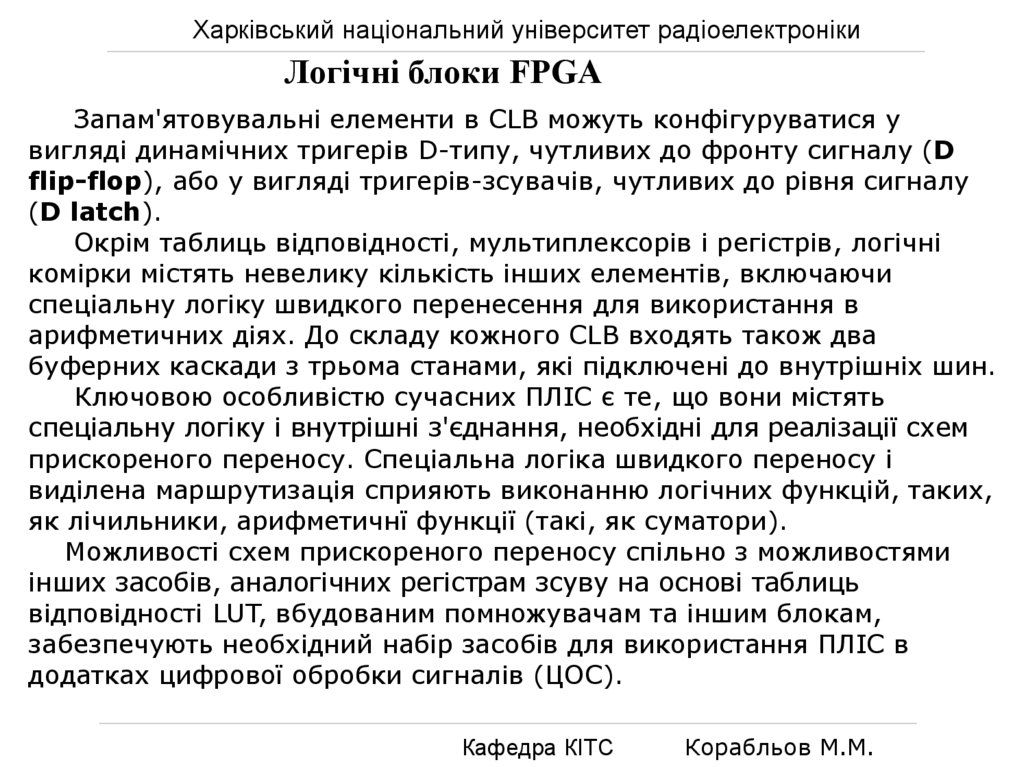

Запам'ятовувальні елементи в CLB можуть конфігуруватися у

вигляді динамічних тригерів D-типу, чутливих до фронту сигналу (D

flip-flop), або у вигляді тригерів-зсувачів, чутливих до рівня сигналу

(D latch).

Окрім таблиць відповідності, мультиплексорів і регістрів, логічні

комірки містять невелику кількість інших елементів, включаючи

спеціальну логіку швидкого перенесення для використання в

арифметичних діях. До складу кожного CLB входять також два

буферних каскади з трьома станами, які підключені до внутрішніх шин.

Ключовою особливістю сучасних ПЛІС є те, що вони містять

спеціальну логіку і внутрішні з'єднання, необхідні для реалізації схем

прискореного переносу. Спеціальна логіка швидкого переносу і

виділена маршрутизація сприяють виконанню логічних функцій, таких,

як лічильники, арифметичнї функції (такі, як суматори).

Можливості схем прискореного переносу спільно з можливостями

інших засобів, аналогічних регістрам зсуву на основі таблиць

відповідності LUT, вбудованим помножувачам та іншим блокам,

забезпечують необхідний набір засобів для використання ПЛІС в

додатках цифрової обробки сигналів (ЦОС).

Кафедра КІТС

Корабльов М.М.

21.

Харківський національний університет радіоелектронікиЛогічні блоки FPGA

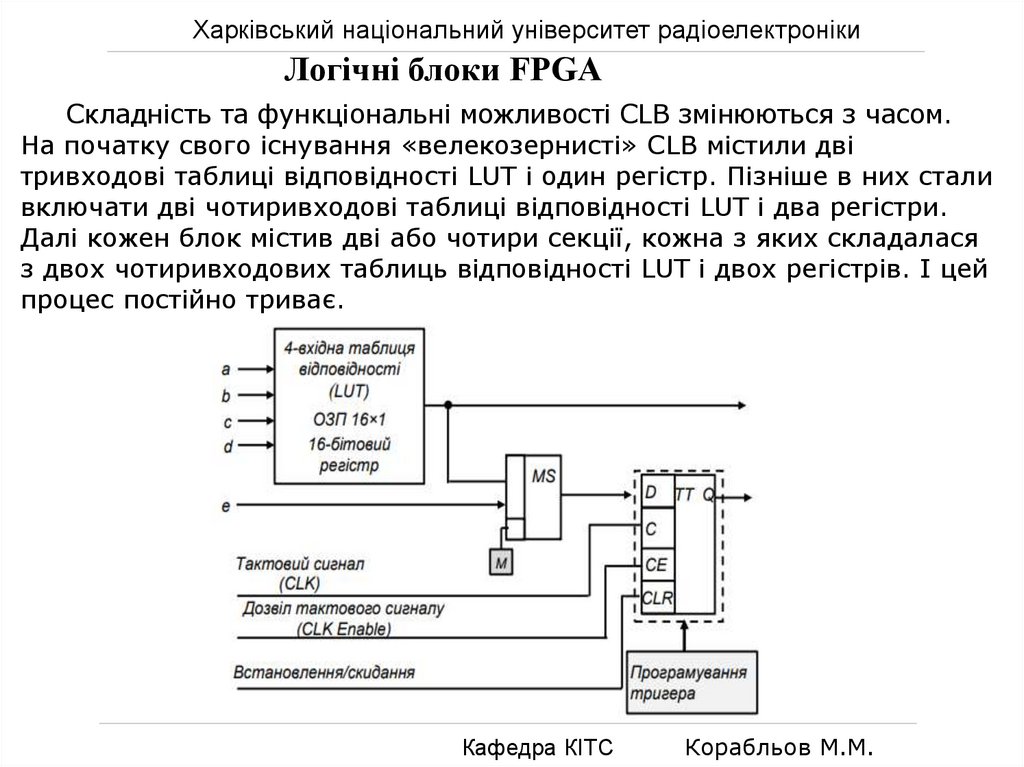

Складність та функціональні можливості CLB змінюються з часом.

На початку свого існування «велекозернисті» CLB містили дві

тривходові таблиці відповідності LUT і один регістр. Пізніше в них стали

включати дві чотиривходові таблиці відповідності LUT і два регістри.

Далі кожен блок містив дві або чотири секції, кожна з яких складалася

з двох чотиривходових таблиць відповідності LUT і двох регістрів. І цей

процес постійно триває.

Кафедра КІТС

Корабльов М.М.

22.

Харківський національний університет радіоелектронікиТипова структура CLB FPGA з тригерною пам'яттю

Кафедра КІТС

Корабльов М.М.

23.

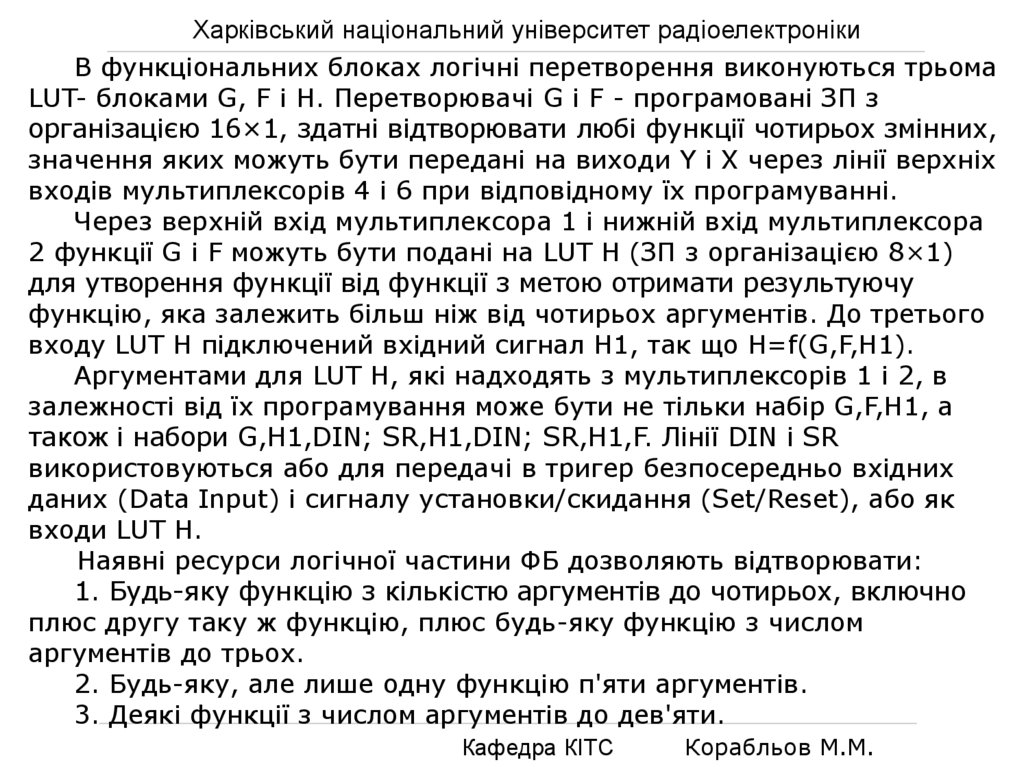

Харківський національний університет радіоелектронікиВ функціональних блоках логічні перетворення виконуються трьома

LUT- блоками G, F і H. Перетворювачі G і F - програмовані ЗП з

організацією 16×1, здатні відтворювати любі функції чотирьох змінних,

значення яких можуть бути передані на виходи Y і X через лінії верхніх

входів мультиплексорів 4 і 6 при відповідному їх програмуванні.

Через верхній вхід мультиплексора 1 і нижній вхід мультиплексора

2 функції G і F можуть бути подані на LUT Н (ЗП з організацією 8×1)

для утворення функції від функції з метою отримати результуючу

функцію, яка залежить більш ніж від чотирьох аргументів. До третього

входу LUT Н підключений вхідний сигнал Н1, так що Н=f(G,F,H1).

Аргументами для LUT Н, які надходять з мультиплексорів 1 і 2, в

залежності від їх програмування може бути не тільки набір G,F,H1, а

також і набори G,H1,DIN; SR,H1,DIN; SR,H1,F. Лінії DIN і SR

використовуються або для передачі в тригер безпосередньо вхідних

даних (Data Input) і сигналу установки/скидання (Set/Reset), або як

входи LUT Н.

Наявні ресурси логічної частини ФБ дозволяють відтворювати:

1. Будь-яку функцію з кількістю аргументів до чотирьох, включно

плюс другу таку ж функцію, плюс будь-яку функцію з числом

аргументів до трьох.

2. Будь-яку, але лише одну функцію п'яти аргументів.

3. Деякі функції з числом аргументів до дев'яти.

Кафедра КІТС

Корабльов М.М.

24.

Харківський національний університет радіоелектронікиБлоки введення-виведення FPGA

БВВ забезпечують інтерфейс між висновками корпусу та її

внутрішніми логічними схемами. Кожному виводу надається БВВ, який

може бути конфігурований на: вхід, вихід, двонаправлений обмін.

З цією метою до кожного БВВ входить: вхідний буфер, вихідний

буфер, вхідний тригер, вихідний тригер, мультиплексори для

конфігурації, схеми керування.

Вихідний сигнал можна отримувати в прямій або в інверсній формі в

залежності від програмування мультиплексора 2. Цей сигнал може

передаватися на вихідний буфер безпосередньо або зніматися з

тригера при відповідному програмуванні мультиплексора 5.

Сигнали Т і GTS (Global Tri-State), згідно з логікою АБО, керують

переводом буфера в третій стан, причому активний рівень сигналу Т

програмується за допомогою мультиплексора 1. Сам буфер має

програмовану крутизну фронту вихідного сигналу і його рівні

формуються за стандартами КМОН/ТТЛ.

Тракт вводу сигнала містить вхідний буфер 2, тригер 2,

програмовані мультиплексори 3, 4, 6, елемент затримки (DEL) і

програмовані схеми задання визначених потенціалів виводу. Вхідний

сигнал в залежності від програмування мультиплексорів 3 і 4 або

надходить безпосередньо в систему комутації FPGA по вхідним лініям І1

і І2, або фіксується тригером і з його виходу передається на ці лінії.

Кафедра КІТС

Корабльов М.М.

25.

Харківський національний університет радіоелектронікиБлоки введення-виведення FPGA

Кафедра КІТС

Корабльов М.М.

26.

Харківський національний університет радіоелектронікиСистема міжз’єднань FPGA

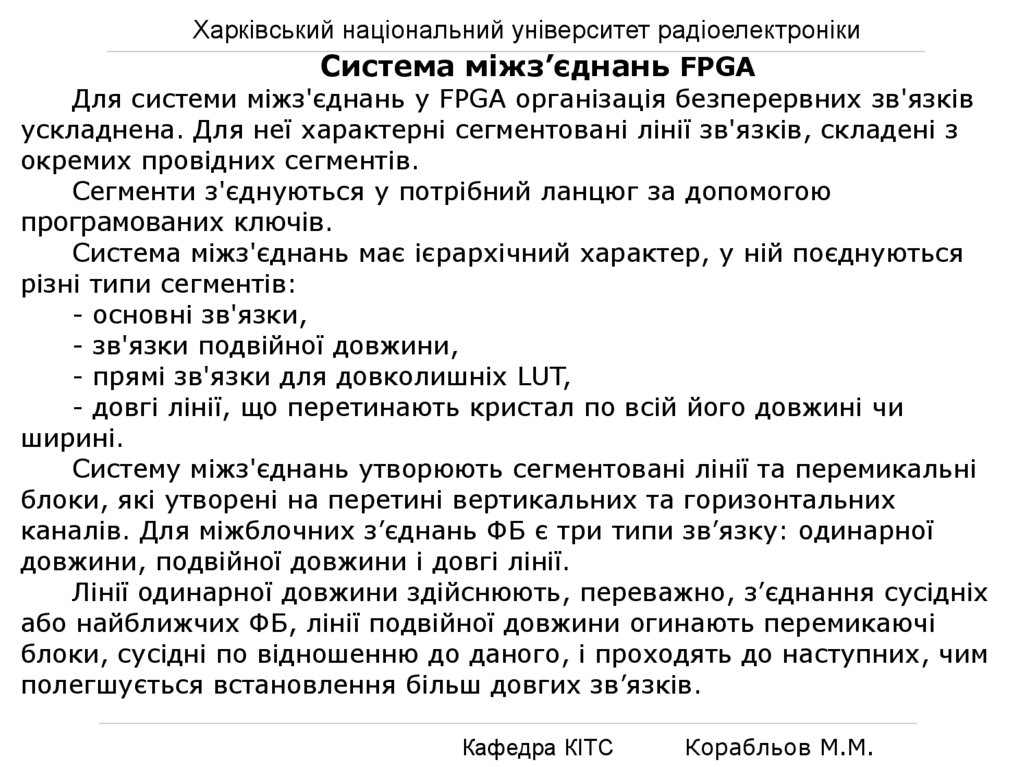

Для системи міжз'єднань у FPGA організація безперервних зв'язків

ускладнена. Для неї характерні сегментовані лінії зв'язків, складені з

окремих провідних сегментів.

Сегменти з'єднуються у потрібний ланцюг за допомогою

програмованих ключів.

Система міжз'єднань має ієрархічний характер, у ній поєднуються

різні типи сегментів:

- основні зв'язки,

- зв'язки подвійної довжини,

- прямі зв'язки для довколишніх LUT,

- довгі лінії, що перетинають кристал по всій його довжині чи

ширині.

Систему міжз'єднань утворюють сегментовані лінії та перемикальні

блоки, які утворені на перетині вертикальних та горизонтальних

каналів. Для міжблочних з’єднань ФБ є три типи зв’язку: одинарної

довжини, подвійної довжини і довгі лінії.

Лінії одинарної довжини здійснюють, переважно, з’єднання сусідніх

або найближчих ФБ, лінії подвійної довжини огинають перемикаючі

блоки, сусідні по відношенню до даного, і проходять до наступних, чим

полегшується встановлення більш довгих зв’язків.

Кафедра КІТС

Корабльов М.М.

27.

Харківський національний університет радіоелектронікиСистема міжз'єднань FPGA

Кафедра КІТС

Корабльов М.М.

28.

Харківський національний університет радіоелектронікиСистема міжз'єднань FPGA

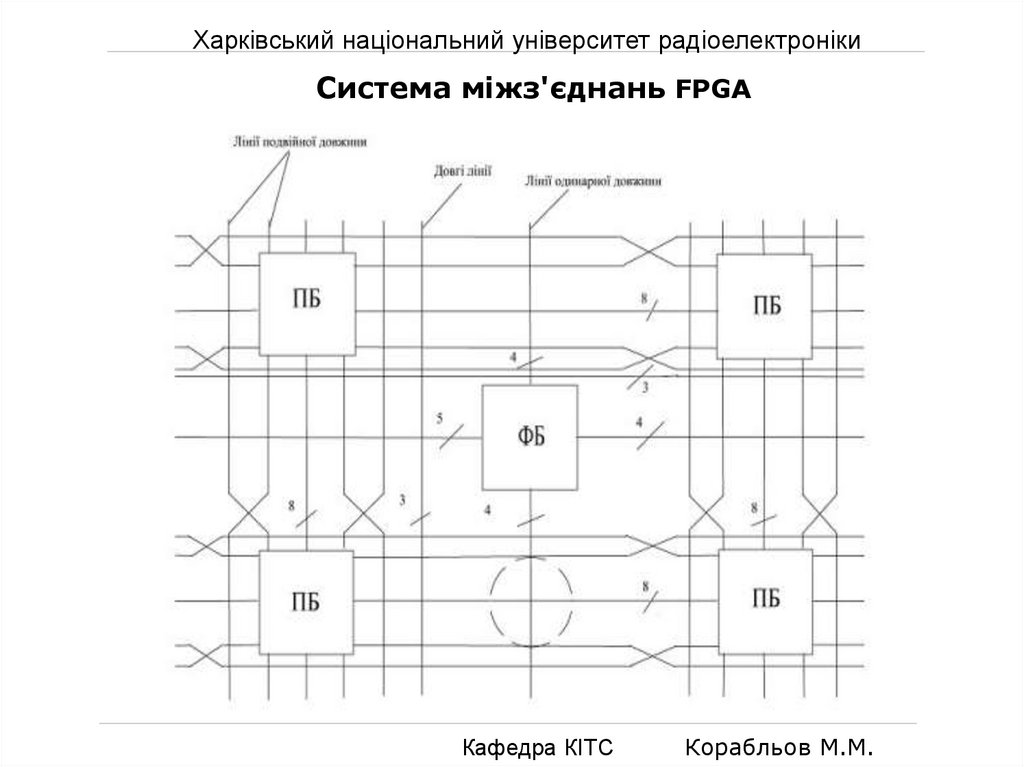

Блоки CLB знаходяться в комутаційній матриці, яка задає

з'єднання входів та виходів блоків CLB.

На кожному перетині провідників знаходиться шість перемикаючих

ключів, керованих своїми комірками конфігураційної пам'яті.

Відкриваючи одні та закриваючи інші, можна забезпечити різну

комутацію сигналів між CLB.

До числа FPGA за прийнятою класифікацією потрапляють

мікросхеми з числом еквівалентних вентилів від 100 до 15 000 з

системними частотами від 50 до 85 МГц і числом висновків 100-300.

Кафедра КІТС

Корабльов М.М.

29.

Харківський національний університет радіоелектронікиХарактеристики ПЛІС FPGA фірми Xilinx

FPGA сімейства Virtex

Сімейство Virtex представлено дев’ятьма типами кристалів, які

містять від 384 до 6144 конфігурованих логічних блоків (відповідно

від 50 000 до 1 000 000 системних елементів), які виготовляються по

технології 120 нм з п’ятишаровою металізацією.

Характерними особливостями сімейства Virtex є:

1) висока швидкодія з системними частотами до 200 МГц;

2) використання чотирьох спеціальних схем цифрового

автоналаштування затримок (DLL), які виконують функції множення,

ділення і зсуву фаз тактових частот, забезпечуючі розширені

можливості керування синхронізацією;

3) використання чотирьох глобальних мереж, що надають

можливість розподілу сигналів синхронізації всередині кристалів;

4) наявність двох видів внутрішньої оперативної пам’яті:

розподіленої Distribut RAM, реалізованої на базі чотирьохвходових

LUT, конфігурованих логічних блоків CLB і вбудованої блочної пам’яті

Block Select RAM, яка може бути організована як синхронний

двопортовий ОЗП;

5) використання спеціальної логіки прискореного переносу для

виконання високошвидкісних арифметичних операцій;

Кафедра КІТС

Корабльов М.М.

30.

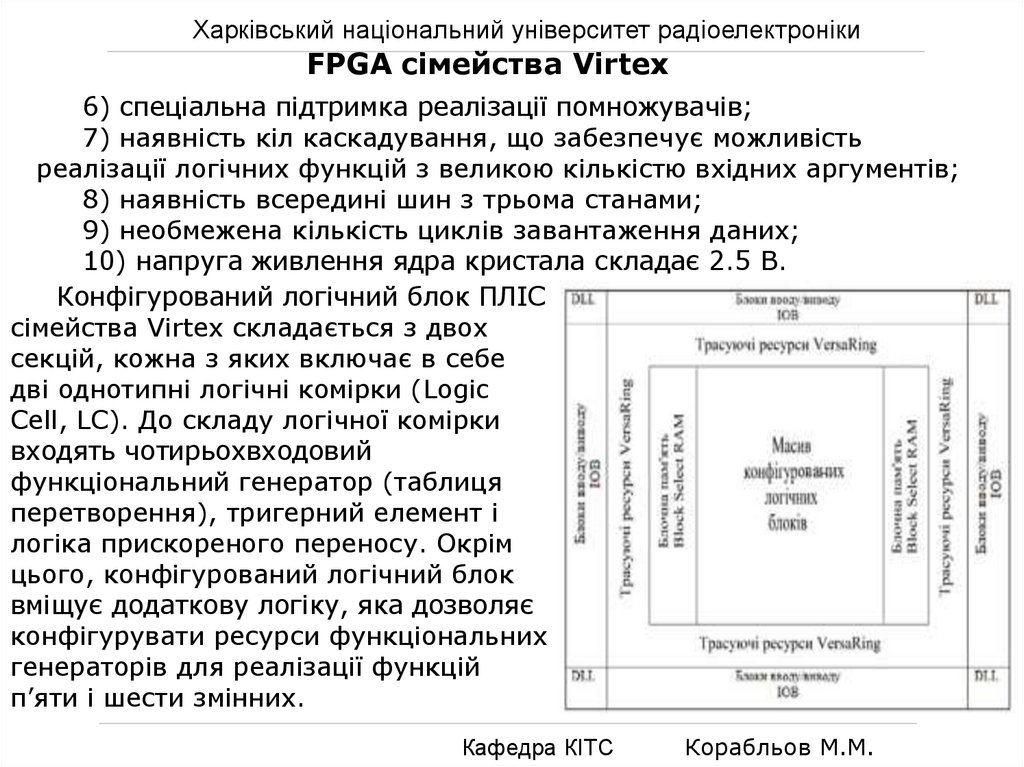

Харківський національний університет радіоелектронікиFPGA сімейства Virtex

6) спеціальна підтримка реалізації помножувачів;

7) наявність кіл каскадування, що забезпечує можливість

реалізації логічних функцій з великою кількістю вхідних аргументів;

8) наявність всередині шин з трьома станами;

9) необмежена кількість циклів завантаження даних;

10) напруга живлення ядра кристала складає 2.5 В.

Конфігурований логічний блок ПЛІС

сімейства Virtex складається з двох

секцій, кожна з яких включає в себе

дві однотипні логічні комірки (Logic

Cell, LC). До складу логічної комірки

входять чотирьохвходовий

функціональний генератор (таблиця

перетворення), тригерний елемент і

логіка прискореного переносу. Окрім

цього, конфігурований логічний блок

вміщує додаткову логіку, яка дозволяє

конфігурувати ресурси функціональних

генераторів для реалізації функцій

п’яти і шести змінних.

Кафедра КІТС

Корабльов М.М.

31.

Харківський національний університет радіоелектронікиХарактеристики ПЛІС FPGA фірми Xilinx

Архітектури FPGA сімейства Spartan-6

Кафедра КІТС

Корабльов М.М.

32.

Харківський національний університет радіоелектронікиАрхітектури FPGA сімейства Spartan

Ефективне поєднання апаратної і програмної частин сімейства ПЛІС

FPGA Spartan-6 має такі особливості:

1) зростає продуктивність системи з ефективною дворегістровою

таблицею відповідності LUT, яка має шість входів;

2) PCI Express із інтегрованими блоками;

3) підключення восьми малопотужних (по 150 мВ кожний) 3.2 Гбіт/с

GTP послідовних приймачів;

4) підтримка швидкості доступу до 800 Мбіт/с, використовуючи

вбудовані контролери пам’яті;

5) вбудовані DSP-блоки, які використовують малопотужні 390 МГц

секції цифрової обробки сигналів DSP48A1 із блоками перемножувачів

18х18;

6) використання працюючих на декількох напругах

мультистандартних SelectIO блоків із дешевими HSTL та SSTL

інтерфейсами пам’яті;

7) блоки керування синхронізацією, які складаються з двох DCMs і

одного PLL;

8) тактова частота 1 ГГц.

Кафедра КІТС

Корабльов М.М.

33.

Харківський національний університет радіоелектронікиАрхітектури FPGA сімейства Spartan

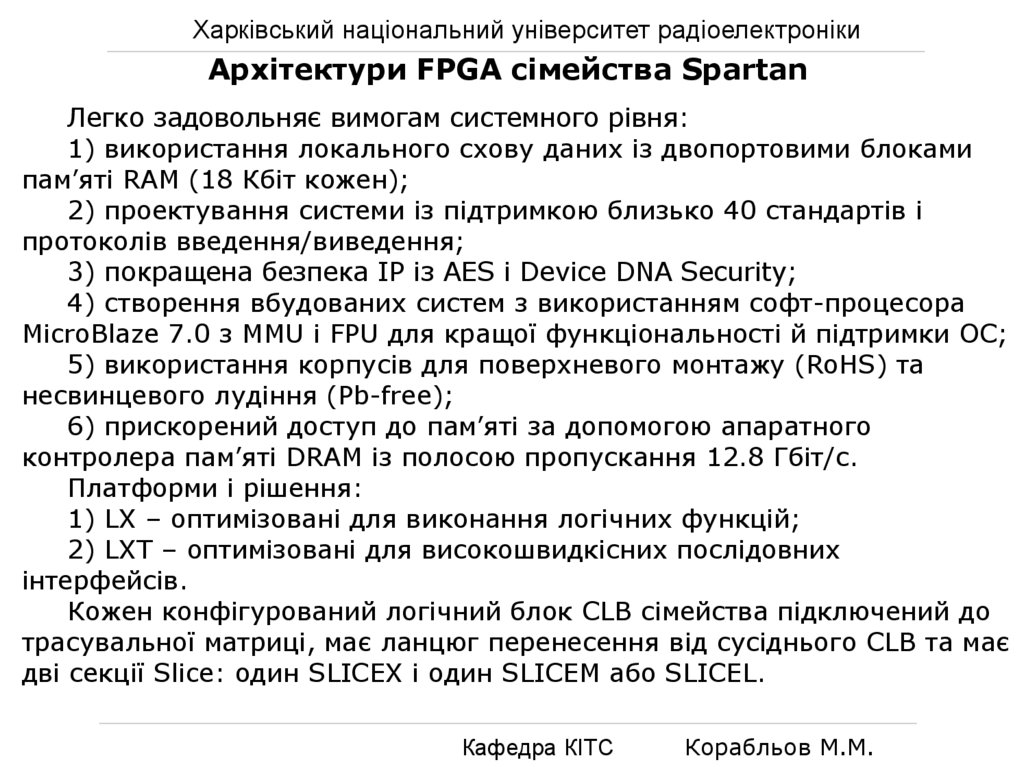

Легко задовольняє вимогам системного рівня:

1) використання локального схову даних із двопортовими блоками

пам’яті RAM (18 Кбіт кожен);

2) проектування системи із підтримкою близько 40 стандартів і

протоколів введення/виведення;

3) покращена безпека IP із AES і Device DNA Security;

4) створення вбудованих систем з використанням софт-процесора

MicroBlaze 7.0 з MMU і FPU для кращої функціональності й підтримки ОС;

5) використання корпусів для поверхневого монтажу (RoHS) та

несвинцевого лудіння (Pb-free);

6) прискорений доступ до пам’яті за допомогою апаратного

контролера пам’яті DRAM із полосою пропускання 12.8 Гбіт/с.

Платформи і рішення:

1) LX – оптимізовані для виконання логічних функцій;

2) LXT – оптимізовані для високошвидкісних послідовних

інтерфейсів.

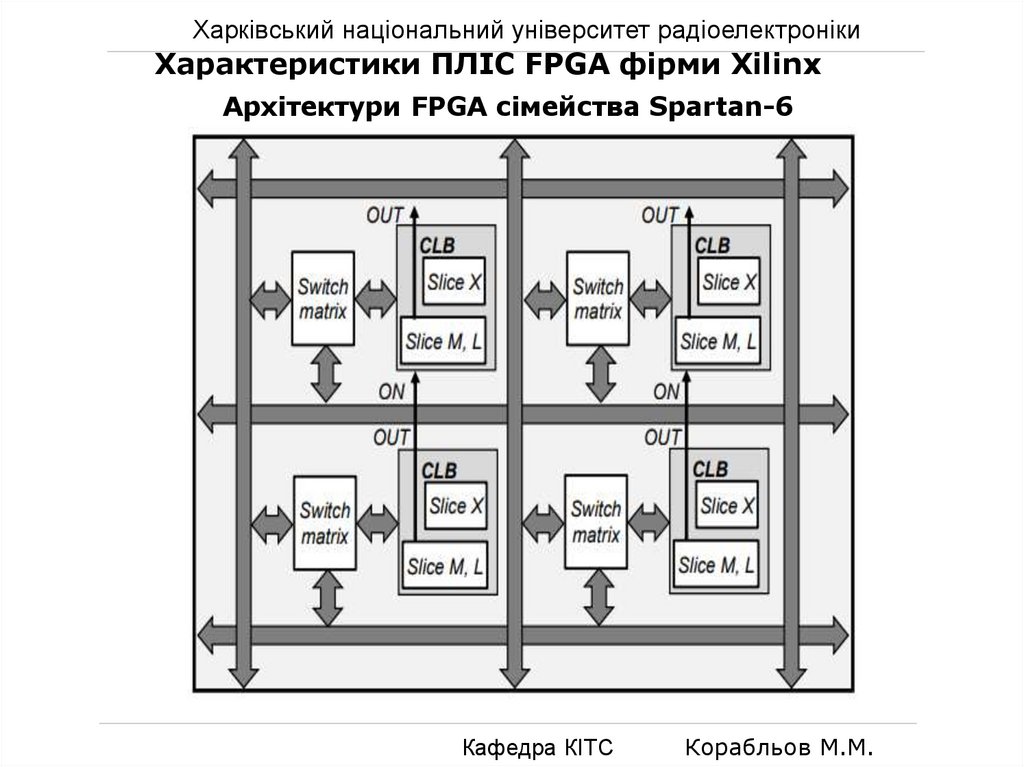

Кожен конфігурований логічний блок CLB сімейства підключений до

трасувальної матриці, має ланцюг перенесення від сусіднього CLB та має

дві секції Slice: один SLICEX і один SLICEM або SLICEL.

Кафедра КІТС

Корабльов М.М.

34.

Харківський національний університет радіоелектронікиАрхітектури FPGA сімейства Spartan

Найбільш складна секція – SLICEM, яка містить такі компоненти:

1) 4 таблиці перетворення LUT-6, кожна з яких має шість входів і може

конфігуруватися як 4 регістри по 32 розряди, що можуть використовуватися як

регістри зсуву;

2) 4 блоки розподіленої пам’яті RAM по 64 біти кожен (загалом 256 біт);

3) кола швидкого переносу CARRY, які потрібні для побудови суматорів;

4) розширювані мультиплексори MUX;

5) 8 регістрів для зберігання результату.

Кафедра КІТС

Корабльов М.М.

35.

Харківський національний університет радіоелектронікиАрхітектури FPGA сімейства Spartan

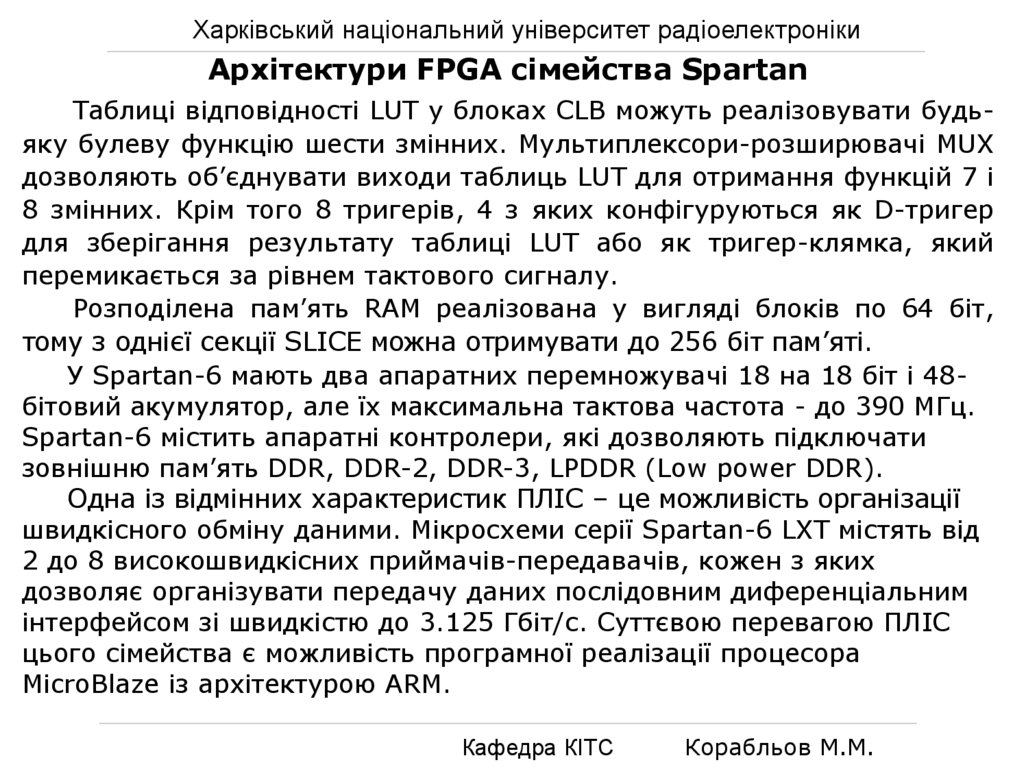

Таблиці відповідності LUT у блоках CLB можуть реалізовувати будьяку булеву функцію шести змінних. Мультиплексори-розширювачі MUX

дозволяють об’єднувати виходи таблиць LUT для отримання функцій 7 і

8 змінних. Крім того 8 тригерів, 4 з яких конфігуруються як D-тригер

для зберігання результату таблиці LUT або як тригер-клямка, який

перемикається за рівнем тактового сигналу.

Розподілена пам’ять RAM реалізована у вигляді блоків по 64 біт,

тому з однієї секції SLICE можна отримувати до 256 біт пам’яті.

У Spartan-6 мають два апаратних перемножувачі 18 на 18 біт і 48бітовий акумулятор, але їх максимальна тактова частота - до 390 МГц.

Spartan-6 містить апаратні контролери, які дозволяють підключати

зовнішню пам’ять DDR, DDR-2, DDR-3, LPDDR (Low power DDR).

Одна із відмінних характеристик ПЛІС – це можливість організації

швидкісного обміну даними. Мікросхеми серії Spartan-6 LXT містять від

2 до 8 високошвидкісних приймачів-передавачів, кожен з яких

дозволяє організувати передачу даних послідовним диференціальним

інтерфейсом зі швидкістю до 3.125 Гбіт/с. Суттєвою перевагою ПЛІС

цього сімейства є можливість програмної реалізації процесора

MicroBlaze із архітектурою ARM.

Кафедра КІТС

Корабльов М.М.

36.

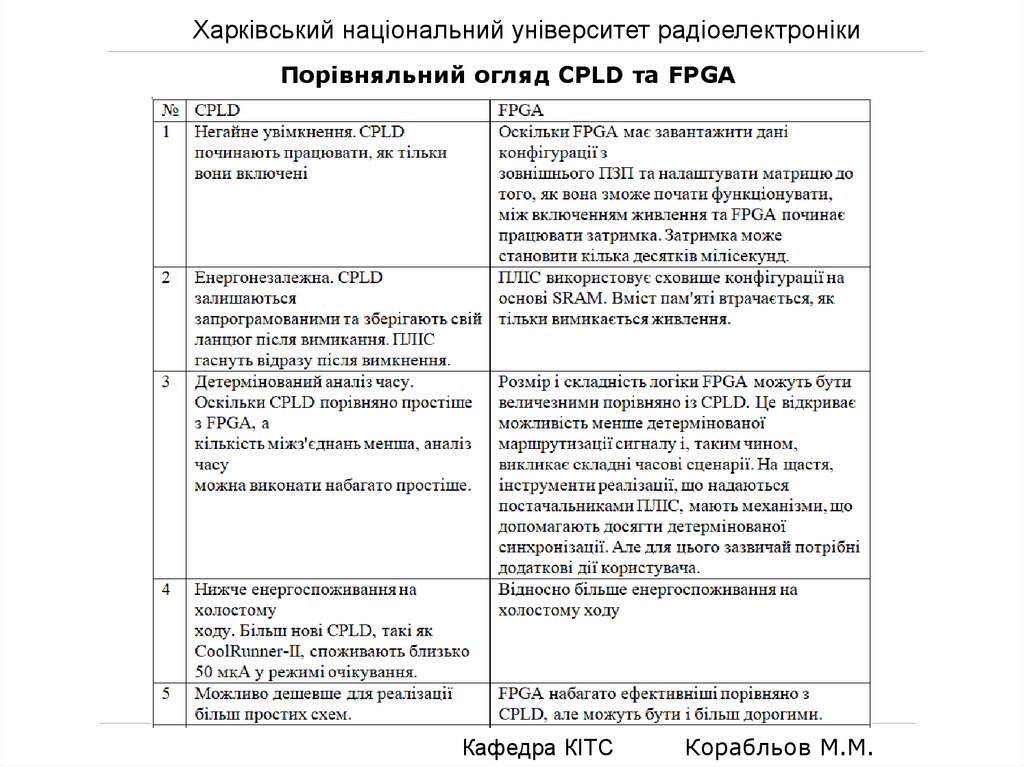

Харківський національний університет радіоелектронікиПорівняльний огляд CPLD та FPGA

Кафедра КІТС

Корабльов М.М.

37.

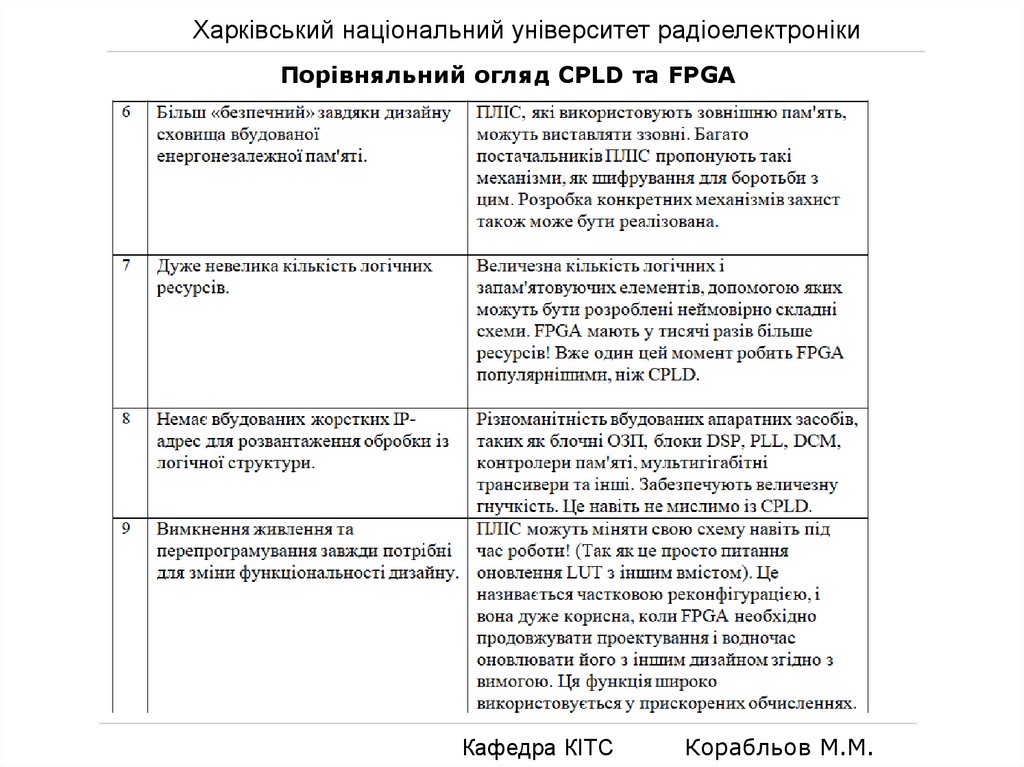

Харківський національний університет радіоелектронікиПорівняльний огляд CPLD та FPGA

Кафедра КІТС

Корабльов М.М.

38.

Харківський національний університет радіоелектронікиКонтрольні питання

1. Програмовані користувачем вентильні матриці

(FPGA).

2. Функціональні блоки FPGA.

3. Блоки введення-виведення FPGA.

4. Система міжз'єднань FPGA.

5. Порівняльний огляд CPLD та FPGA.

Кафедра КІТС

Корабльов М.М.

Электроника

Электроника