Похожие презентации:

ПЛІС з комбінованою архітектурою (FLEX – Flexible Logic Element MatriX). Лекція 2-12

1.

Харківський національний університет радіоелектронікиЛЕКЦІЯ 2-12

ПЛІС з комбінованою

архітектурою(FLEX –

Flexible Logic Element MatriX)

Програмовані системи на

кристалах (PSOC, SOPC, SOC)

Кафедра КІТС

Корабльов М.М.

2.

Харківський національний університет радіоелектронікиПЛІС з комбінованою архітектурою

(FLEX – Flexible Logic Element MatriX)

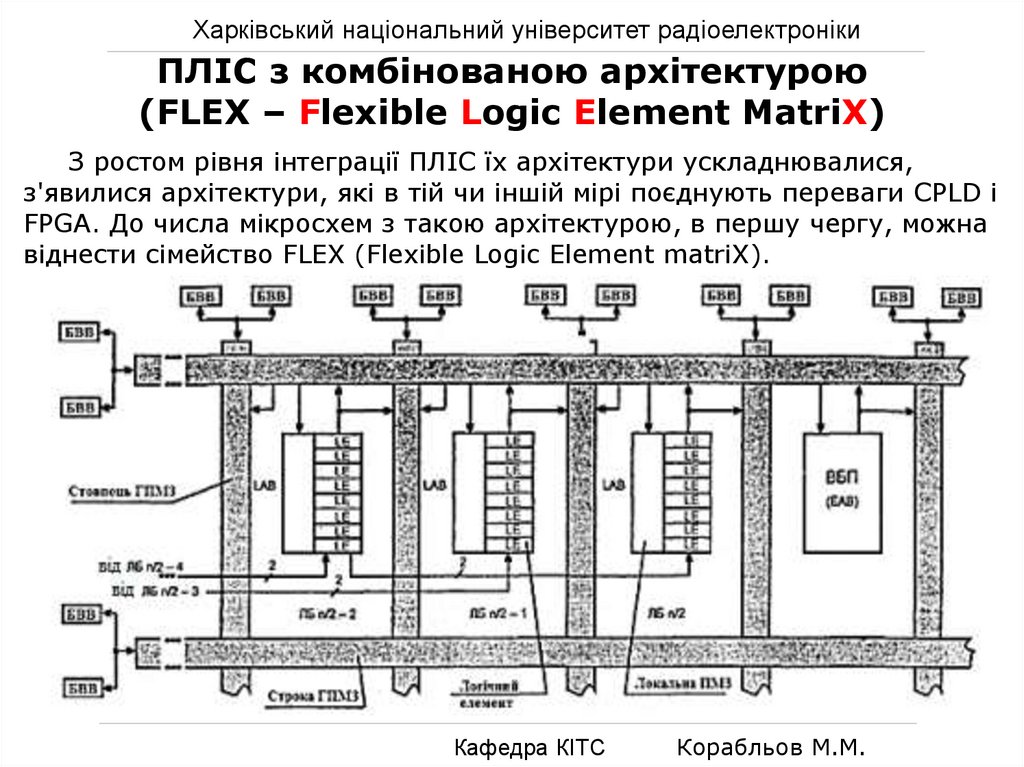

З ростом рівня інтеграції ПЛІС їх архітектури ускладнювалися,

з'явилися архітектури, які в тій чи іншій мірі поєднують переваги CPLD і

FPGA. До числа мікросхем з такою архітектурою, в першу чергу, можна

віднести сімейство FLEX (Flexible Logic Element matriХ).

Кафедра КІТС

Корабльов М.М.

3.

Харківський національний університет радіоелектронікиМікросхеми сімейства FLEX мають функціональні блоки (LABs, Logic

Array Blocks) з логічними елементами ЛЕ (LEs, Logic Elements), що

містять функціональні перетворювачі ФП табличного типу (LUTs).

Функціональні блоки розташовані у вигляді матриці, між їх рядками і

стовпцями проходять горизонтальні і вертикальні канали трасування,

що характерно для FPGA. У той же час, траси в каналі не сегментовані,

а неперервні, що типово для CPLD.

Система комутації має два рівні міжз'єднань - глобальний і

локальний. Локальна програмована матриця з'єднань (ЛПМЗ)

забезпечує міжз'єднання логічних елементів ЛЕ, з яких складаються

функціональні блоки - LABs. До складу LAB входять 8 логічних

елементів. З'єднання між блоками LAB забезпечуються глобальною

програмованою матрицею з'єднань (ГПМЗ), до кінців рядків і стовпців

якої підключаються блоки вводу / виводу (IOBs, Input/Output Blocks).

У середині рядків вбудований блок пам'яті (EABs, Embedded Array

Blocks). Його ємність дорівнює 2048 біт і він може конфігуруватися як

ЗП з організацією 256x8, або 512x4, або 1024x2, або 2048x1 і

використовуватися не тільки для зберігання даних, але і як табличний

ФП для реалізації складних логічних функцій з числом аргументів 8-10

(зокрема, на блоках EАВs будуються швидкодіючі арифметико-логічні

пристрої (АЛП), перемножувачі 4x4, тощо).

Кафедра КІТС

Корабльов М.М.

4.

Харківський національний університет радіоелектронікиЛогічні елементи FLEX

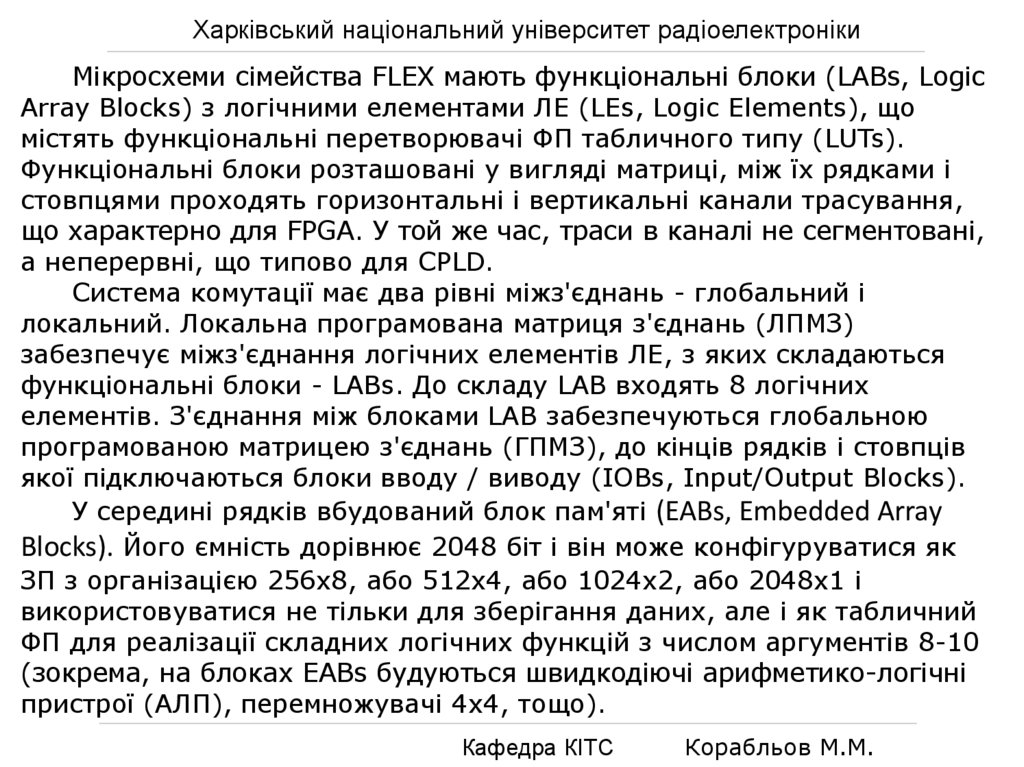

Логічні елементи (ЛЕ) сімейства FLEX мають у своїй основі 4входові функціональні перетворювачі ФП табличного типу (LUT).

Особливістю схем, які можуть бути з них побудовані, є наявність

спеціальних трактів перенесення, що утворюються з ланцюжків схем

перенесення СП, і трактів каскадування, що утворюються зі схем

каскадування СК з безпосередніми і швидкодіючими зв'язками між

логічними елементами по вказаних трактах.

Кафедра КІТС

Корабльов М.М.

5.

Харківський національний університет радіоелектронікиЛогічні елементи FLEX

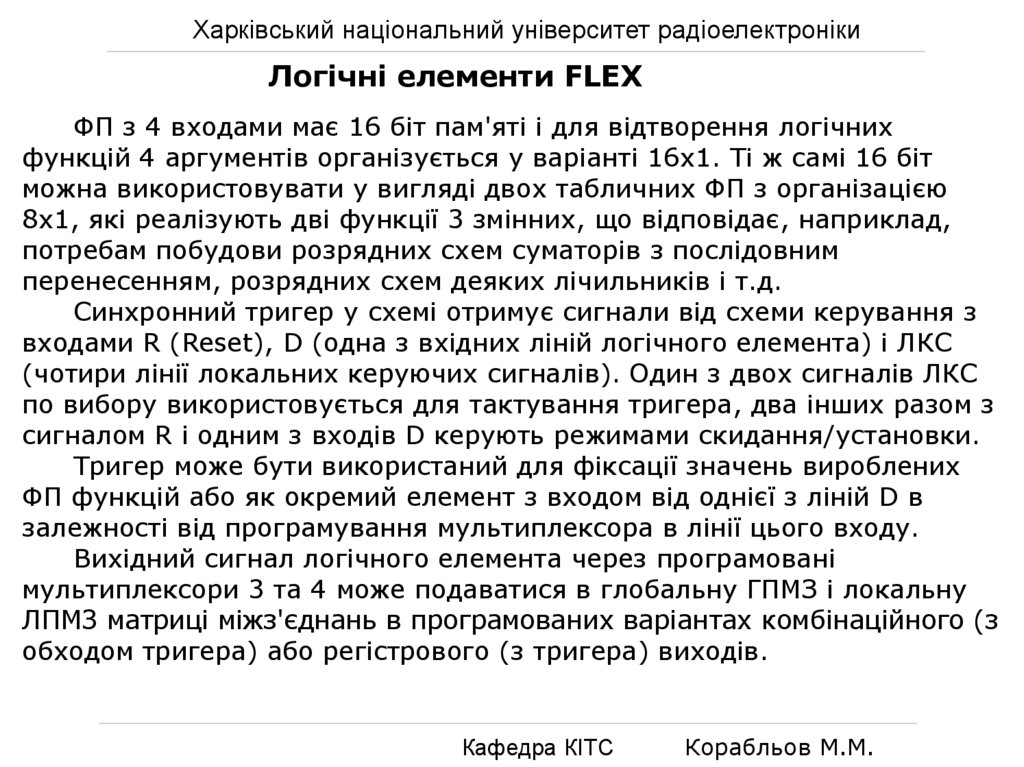

ФП з 4 входами має 16 біт пам'яті і для відтворення логічних

функцій 4 аргументів організується у варіанті 16x1. Ті ж самі 16 біт

можна використовувати у вигляді двох табличних ФП з організацією

8x1, які реалізують дві функції 3 змінних, що відповідає, наприклад,

потребам побудови розрядних схем суматорів з послідовним

перенесенням, розрядних схем деяких лічильників і т.д.

Синхронний тригер у схемі отримує сигнали від схеми керування з

входами R (Reset), D (одна з вхідних ліній логічного елемента) і ЛКС

(чотири лінії локальних керуючих сигналів). Один з двох сигналів ЛКС

по вибору використовується для тактування тригера, два інших разом з

сигналом R і одним з входів D керують режимами скидання/установки.

Тригер може бути використаний для фіксації значень вироблених

ФП функцій або як окремий елемент з входом від однієї з ліній D в

залежності від програмування мультиплексора в лінії цього входу.

Вихідний сигнал логічного елемента через програмовані

мультиплексори 3 та 4 може подаватися в глобальну ГПМЗ і локальну

ЛПМЗ матриці міжз'єднань в програмованих варіантах комбінаційного (з

обходом тригера) або регістрового (з тригера) виходів.

Кафедра КІТС

Корабльов М.М.

6.

Харківський національний університет радіоелектронікиЛогічні елементи FLEX

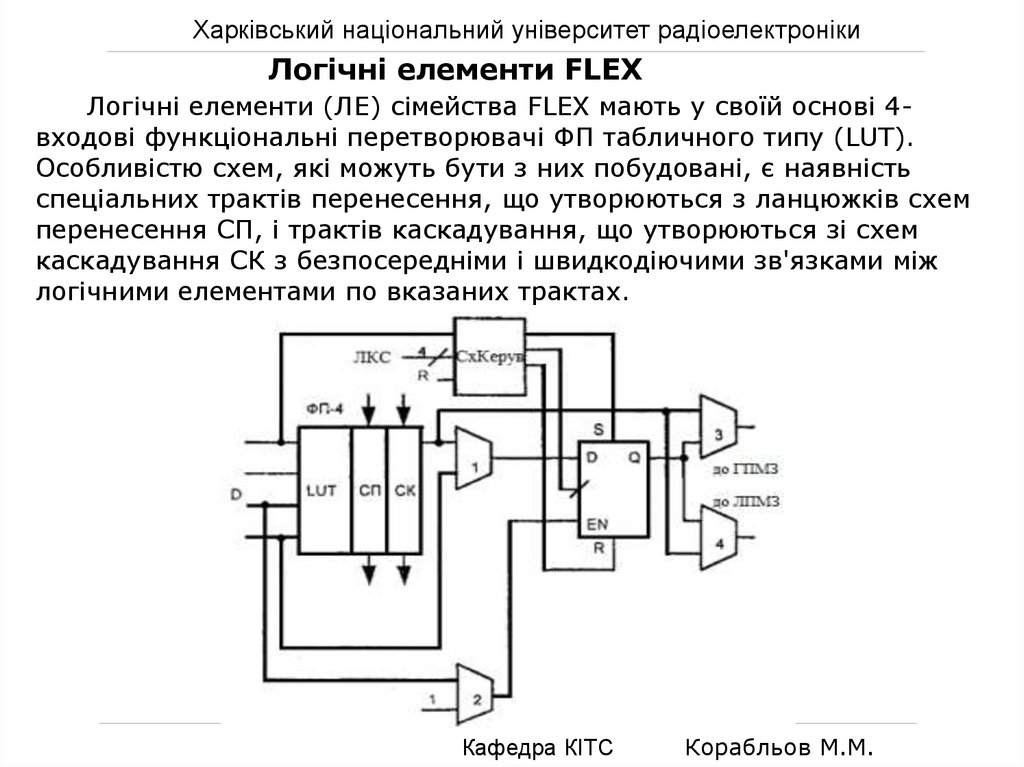

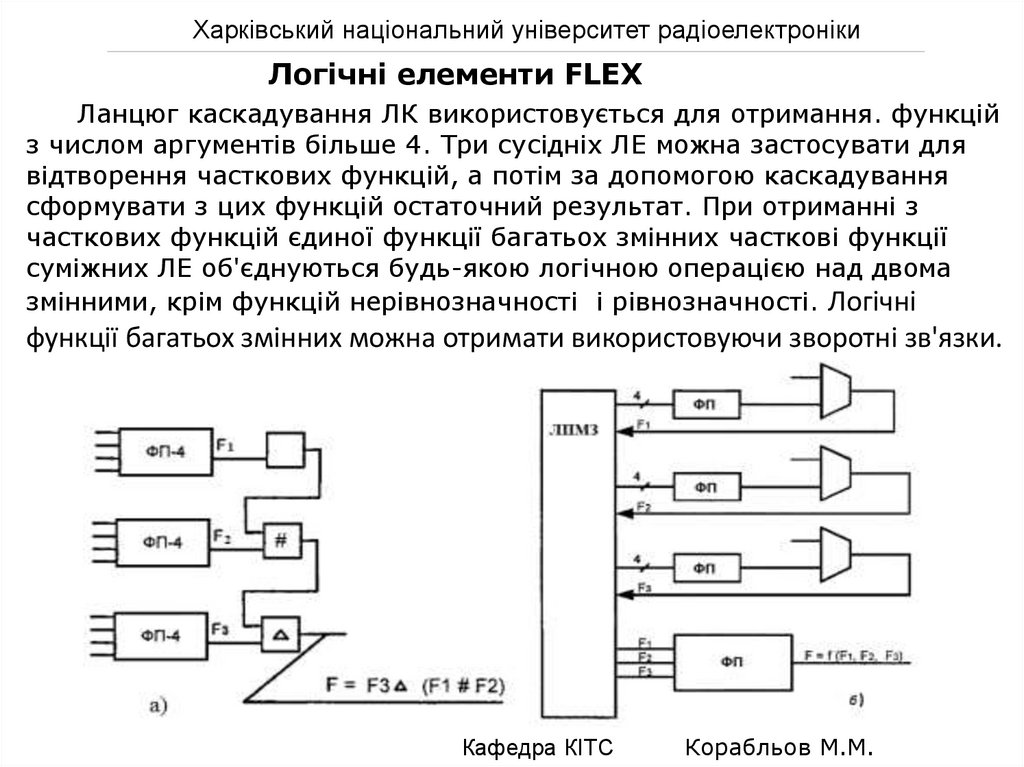

Ланцюг каскадування ЛК використовується для отримання. функцій

з числом аргументів більше 4. Три сусідніх ЛЕ можна застосувати для

відтворення часткових функцій, а потім за допомогою каскадування

сформувати з цих функцій остаточний результат. При отриманні з

часткових функцій єдиної функції багатьох змінних часткові функції

суміжних ЛЕ об'єднуються будь-якою логічною операцією над двома

змінними, крім функцій нерівнозначності і рівнозначності. Логічні

функції багатьох змінних можна отримати використовуючи зворотні зв'язки.

Кафедра КІТС

Корабльов М.М.

7.

Харківський національний університет радіоелектронікиВбудовані блоки пам'яті FLEX

Кафедра КІТС

Корабльов М.М.

8.

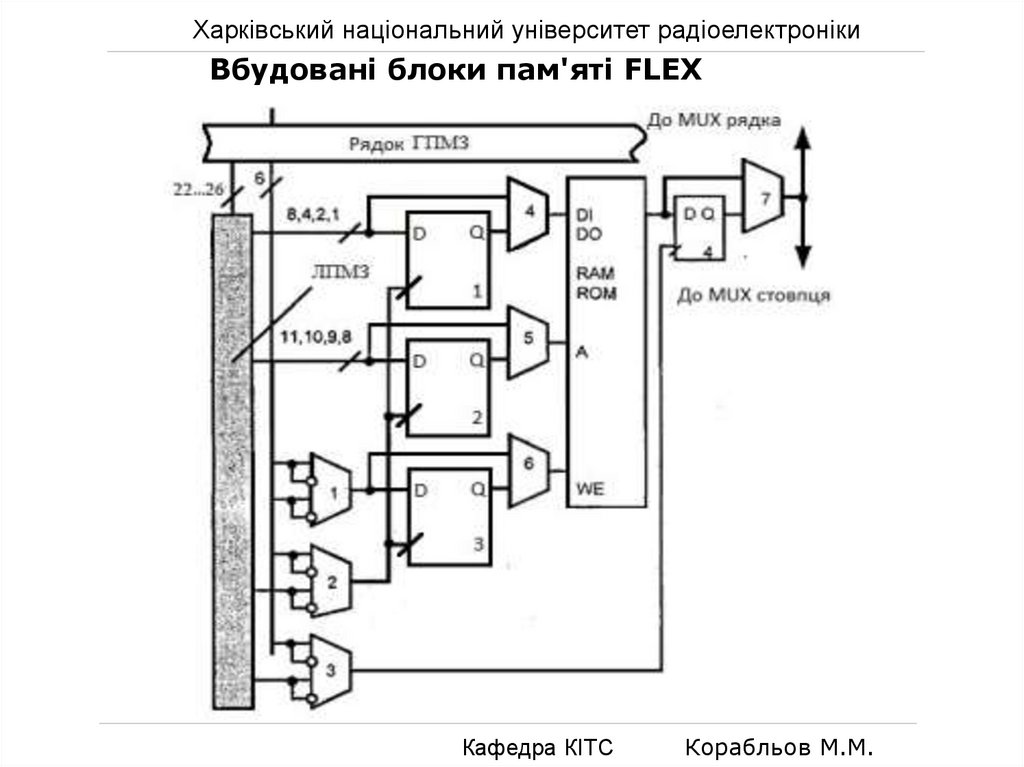

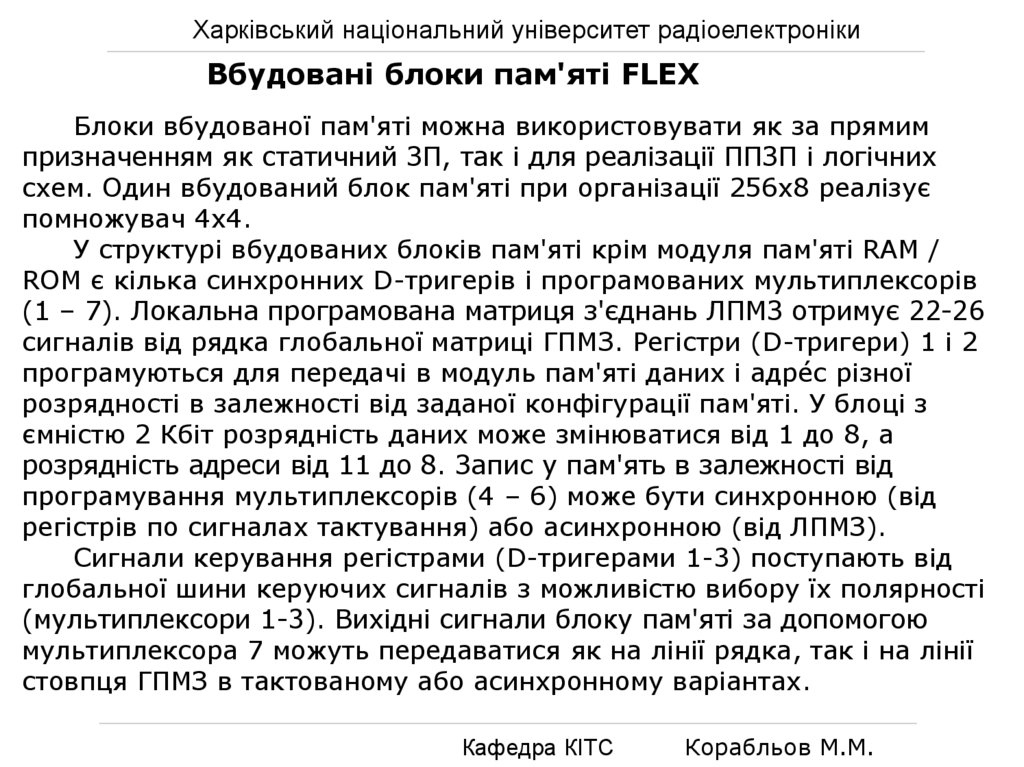

Харківський національний університет радіоелектронікиВбудовані блоки пам'яті FLEX

Блоки вбудованої пам'яті можна використовувати як за прямим

призначенням як статичний ЗП, так і для реалізації ППЗП і логічних

схем. Один вбудований блок пам'яті при організації 256х8 реалізує

помножувач 4x4.

У структурі вбудованих блоків пам'яті крім модуля пам'яті RAM /

ROM є кілька синхронних D-тригерів і програмованих мультиплексорів

(1 – 7). Локальна програмована матриця з'єднань ЛПМЗ отримує 22-26

сигналів від рядка глобальної матриці ГПМЗ. Регістри (D-тригери) 1 і 2

програмуються для передачі в модуль пам'яті даних і адрéс різної

розрядності в залежності від заданої конфігурації пам'яті. У блоці з

ємністю 2 Кбіт розрядність даних може змінюватися від 1 до 8, а

розрядність адреси від 11 до 8. Запис у пам'ять в залежності від

програмування мультиплексорів (4 – 6) може бути синхронною (від

регістрів по сигналах тактування) або асинхронною (від ЛПМЗ).

Сигнали керування регістрами (D-тригерами 1-3) поступають від

глобальної шини керуючих сигналів з можливістю вибору їх полярності

(мультиплексори 1-3). Вихідні сигнали блоку пам'яті за допомогою

мультиплексора 7 можуть передаватися як на лінії рядка, так і на лінії

стовпця ГПМЗ в тактованому або асинхронному варіантах.

Кафедра КІТС

Корабльов М.М.

9.

Харківський національний університет радіоелектронікиПрограмовані системи на кристалі

(PSOC, SOPC, SOC)

Загальна характеристика та класифікація SOC

SOC діляться на однорідні та блокові.

У однорідних SOC різні блоки системи реалізуються одними і тими

же апаратними засобами. Однорідність тут розуміється лише як ознака

конфігурованості усіх областей кристала, оскільки ці області містять

однотипні програмовані схемні ресурси.

В однорідних SOC реалізовані блоки можуть розміщуватися в різних

областях і створюватися відповідним програмуванням. За своїми

архітектурними ознаками однорідні SOC, як правило, відносяться до

структур комбінованого типу, в яких поєднуються ознаки CPLD і FPGA з

перевагою ознак FPGA.

При розробці систем використовуються так звані одиниці

інтелектуальності (ІР). IP – заздалегідь реалізовані мегафункції, що

параметризуються, для створення тих чи інших частин системи. Всі

блоки системи є повністю синтезованими, що переміщуються і можуть

розташовуватися в різних областях кристала.

В однорідних SOC рівень інтеграції вже дозволяє конфігурувати на

кристалі області процесора, пам'яті і периферійних схем, об'єднувати

віртуальні компоненти (soft-ядра, IP) різних розробників.

Кафедра КІТС

Корабльов М.М.

10.

Харківський національний університет радіоелектронікиБлокові SOC діляться на 2 групи :

1. Мають апаратні ядра процесорів (найбільш універсальні).

2. Не мають апаратних ядер процесорів.

SOC блочного типу включають як програмовані, так і фіксовані

області. Програмовані області реалізуються як FPGA.

Блокові SOPC мають апаратні ядра, що реалізуються як ASIC

(Application Specific Integration Circuit - спеціалізовані інтегральні

схеми).

HARD-ядра реалізуються замовним способом, як правило, не

мають засобів конфігурування та оптимізовані на виконання заданої

конкретної функції. Для зменшення втрат універсальних SOC з HARDядрами, для них підбирають такі функціональні блоки, які є широко

поширеними і в інших чіпах.

Реалізація функцій апаратними ядрами вимагає значно меншої

площі кристала, ніж в однорідних SOC.

Швидкодія блокових SOC вища, але знижена універсальність.

Зараз основним ядром складних блокових SOC нерідко служить

мікропроцесор або мікроконтролер. Характерними прикладами hardядер, крім мікропроцесорів і мікроконтролерів, можуть служити блоки

для реалізації інтерфейсів різних шин, множильні пристрої для систем

цифрової обробки сигналів.

Кафедра КІТС

Корабльов М.М.

11.

Харківський національний університет радіоелектронікиSOPC з однорідною структурою

(на прикладі APEX 20K фірми Altera)

Кафедра КІТС

Корабльов М.М.

12.

Харківський національний університет радіоелектронікиПЛІС типу PSOC з однорідною структурою виробляють різні фірми:

Altera – сімейство APEX 20K, Stratix;

Xilinx – сімейство Virtex;

Actel – сімейство proASIC та ін.

У мікросхемах сімейства APEX з тригерною пам’яттю конфігурації

програмуються усі основні області кристалу. Мікросхеми побудовані за

архітектурою, яку назвали Multicore. Логічні функції реалізуються за

допомогою функціональних перетворювачів (LUT) і логічних матриць

(PAL). Об’єднуються характерні ознаки CPLD і FPGA. Мікросхема має

вбудовану пам’ять і розвинуту гнучку систему інтерфейсів.

У кожній клітинці, що утворена шинами швидких з’єднань,

розташовані функціональні ресурси трьох типів:

логічні перетворювачі типу LUT;

логічні блоки подібні до макрокомірок, які розміщувалися у

попередній серії CPLD типу MAX 7000;

вбудовані блоки пам’яті (EAB - Embedded System Blocks).

Вбудовані блоки пам'яті містять засоби для реалізації ДНФ, які

зручні для отримання функцій керуючої логіки, зокрема, декодерів і

автоматів з пам'яттю.

Табличні блоки добре пристосовані для реалізації складних

алгоритмів обробки сигналів і побудови вузлів і пристроїв, що містять

велику кількість тригерів.

Кафедра КІТС

Корабльов М.М.

13.

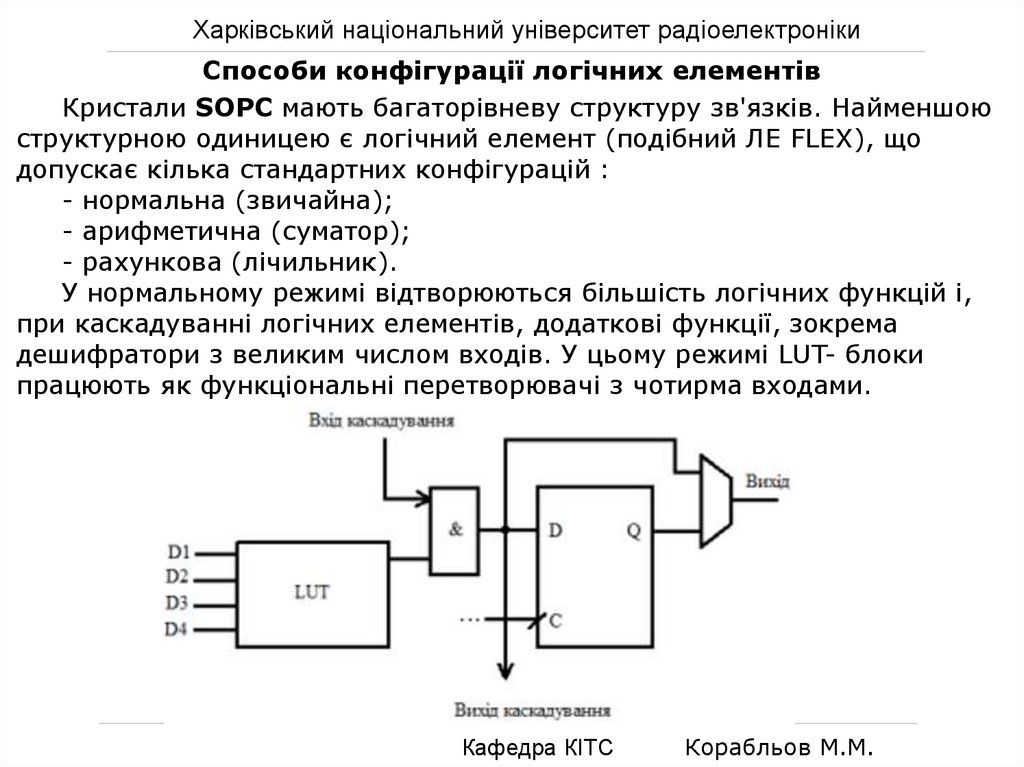

Харківський національний університет радіоелектронікиСпособи конфігурації логічних елементів

Кристали SOPC мають багаторівневу структуру зв'язків. Найменшою

структурною одиницею є логічний елемент (подібний ЛЕ FLEX), що

допускає кілька стандартних конфігурацій :

- нормальна (звичайна);

- арифметична (суматор);

- рахункова (лічильник).

У нормальному режимі відтворюються більшість логічних функцій і,

при каскадуванні логічних елементів, додаткові функції, зокрема

дешифратори з великим числом входів. У цьому режимі LUT- блоки

працюють як функціональні перетворювачі з чотирма входами.

Кафедра КІТС

Корабльов М.М.

14.

Харківський національний університет радіоелектронікиСпособи конфігурації логічних елементів

У арифметичному режимі LUT- блок конфігурується як два

тривходових функціональних перетворювача, один з яких служить для

вироблення функцій переносів, а інший - для функцій трьох аргументів,

реалізованих у розрядних схемах пристрою.

У режимі лічильника до схеми, відповідної арифметичному режиму,

додаються елементи, що забезпечують функції дозволу рахунку,

реверсу, скидання і завантаження лічильника.

Кафедра КІТС

Корабльов М.М.

15.

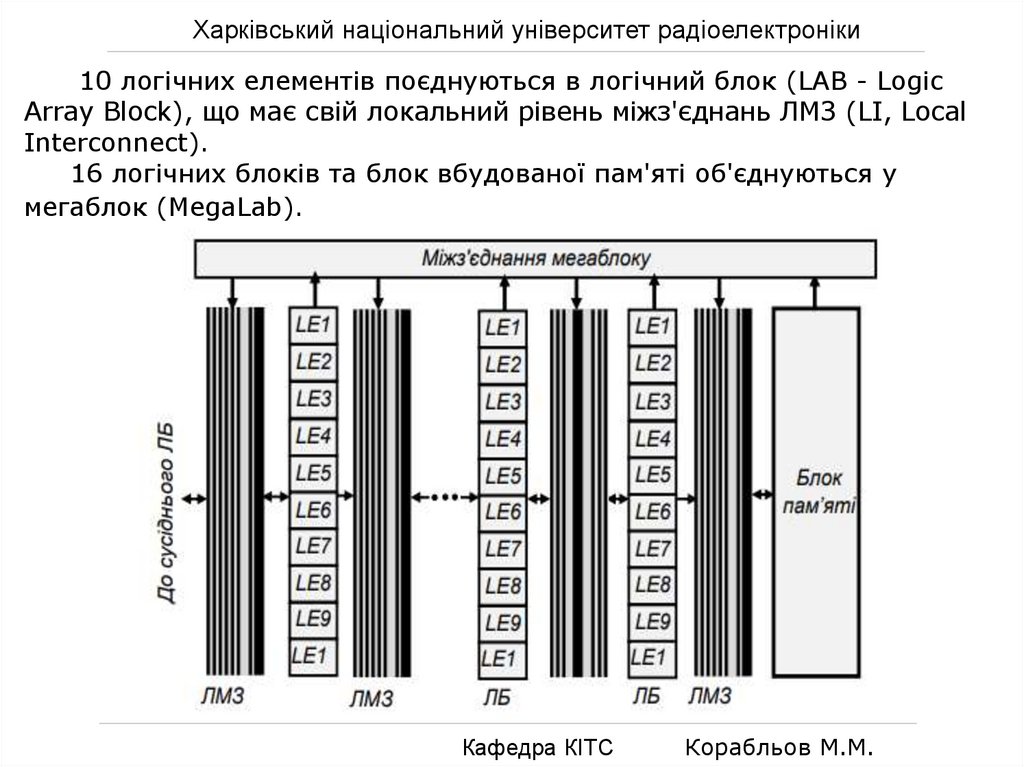

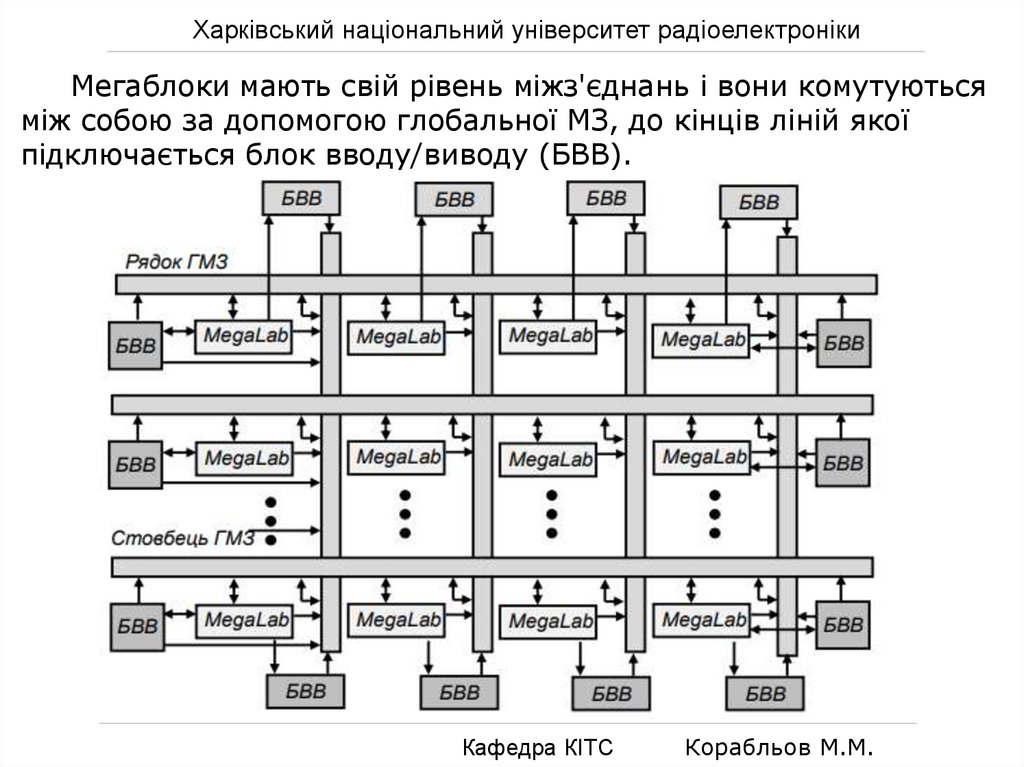

Харківський національний університет радіоелектроніки10 логічних елементів поєднуються в логічний блок (LAB - Logic

Array Block), що має свій локальний рівень міжз'єднань ЛМЗ (LI, Local

Interconnect).

16 логічних блоків та блок вбудованої пам'яті об'єднуються у

мегаблок (MegaLab).

Кафедра КІТС

Корабльов М.М.

16.

Харківський національний університет радіоелектронікиМегаблоки мають свій рівень міжз'єднань і вони комутуються

між собою за допомогою глобальної МЗ, до кінців ліній якої

підключається блок вводу/виводу (БВВ).

Кафедра КІТС

Корабльов М.М.

17.

Харківський національний університет радіоелектронікиОсновні характеристики ПЛІС сімейства APEX20K(KE)

(залежно від типу мікросхеми):

кількість еквівалентних системних вентилів: 263 000 - 2

670 000;

кількість вбудованих блоків пам’яті від 26 до 264;

максимальний об’єм пам’яті, біт - від 53 248 до 540 672;

кількість макрокомірок від 416 до 4224;

кількість виводів користувача від 252 до 780;

напруга живлення ядра 2,5 В (1,8 В);

рівні сигналів введення/виведення (1,8 В) 2,5; 3,3 і 5,0 В;

схема підтримує інтерфейсні стандарти: LVDS, PCI

Для мікросхем сімейства APEX розроблене soft - ядро

процесора Nios. Nios – це 16/32-розрядний RISC-процесор зі

змінюваною конвеєрною архітектурою. Реалізується на основі

приблизно 1000 логічних елементів. Займає від 12% до 1,5%

логічних ресурсів кристала (залежно від різновиду мікросхеми).

Кафедра КІТС

Корабльов М.М.

18.

Харківський національний університет радіоелектронікиSOC з блочними структурами

У складі блочних SOPC можуть бути або відсутні процесорні

ядра. У складі блочних SOC з процесорними ядрами можна виділити

чотири основні частини: процесор, FPGA, інтерфейс між ними і інтерфейс

із зовнішнім середовищем.

ПЛІС типу «система на кристалі» з вбудованими блоками включають у

себе програмовані й фіксовані області. У фіксованих областях чітко

реалізовані блоки, що виконують певні функції – апаратні ядра (Hard

cores, hard-ядра). В інших областях кристала розміщується програмована

користувачем частина.

Розглянемо SOC з блоковою структурою на прикладі сімейства

Excalibur фірми Altera. В основі SoC лежить FPGA АРЕХ20КЕ логічною

ємністю від 100 тис. до 1 млн вентилів. В SoC реалізуване стандартне

апаратне процесорне ядро 32-розрядного RISC-процесора ARM9 на

одному кристалі з логічною матрицею АРЕХ. Процесорне ядро працює на

частоті до 200 МГц.

Excalibur містить внутрішній однопортовий СОЗП ємністю до 250 кбайт

і двопортовий СОЗП ємністю до 120 кбайт.

Кількість програмованих користувачем виводів I/O – від 173 до 521.

На кристалах сімейства розташовано фіксовані периферійні вузли

універсальних асинхронних прийомопередавачів і таймерів.

Кафедра КІТС

Корабльов М.М.

19.

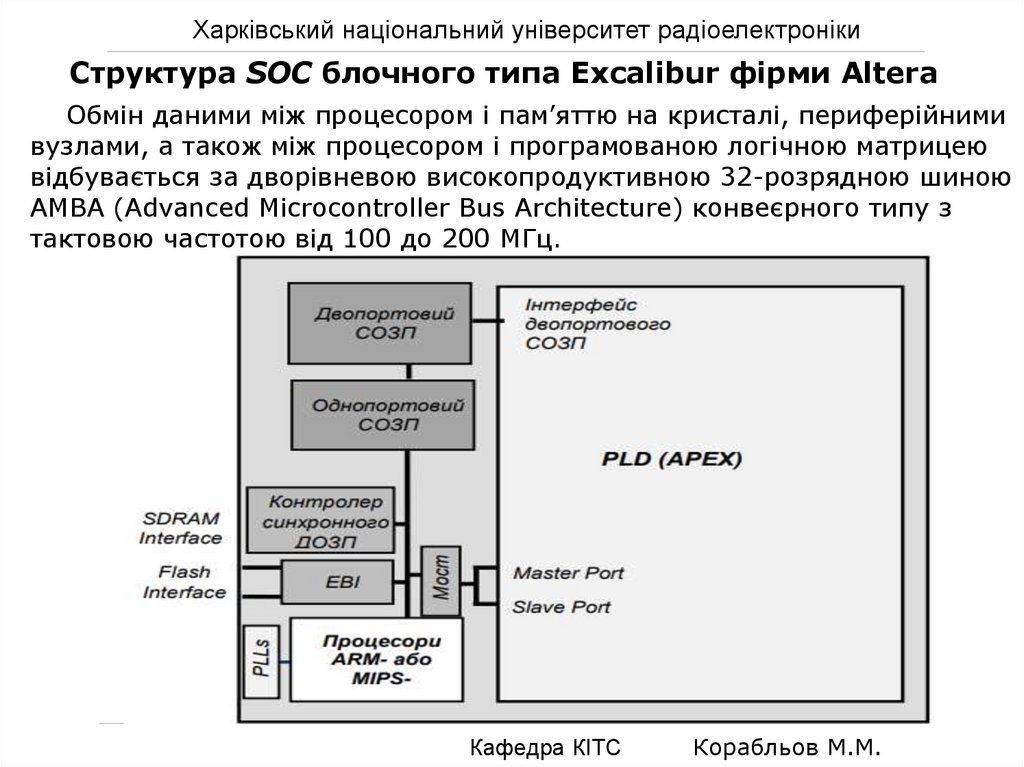

Харківський національний університет радіоелектронікиСтруктура SOC блочного типа Excalibur фірми Altera

Обмін даними між процесором і пам’яттю на кристалі, периферійними

вузлами, а також між процесором і програмованою логічною матрицею

відбувається за дворівневою високопродуктивною 32-розрядною шиною

АМВА (Advanced Microcontroller Bus Architecture) конвеєрного типу з

тактовою частотою від 100 до 200 МГц.

Кафедра КІТС

Корабльов М.М.

20.

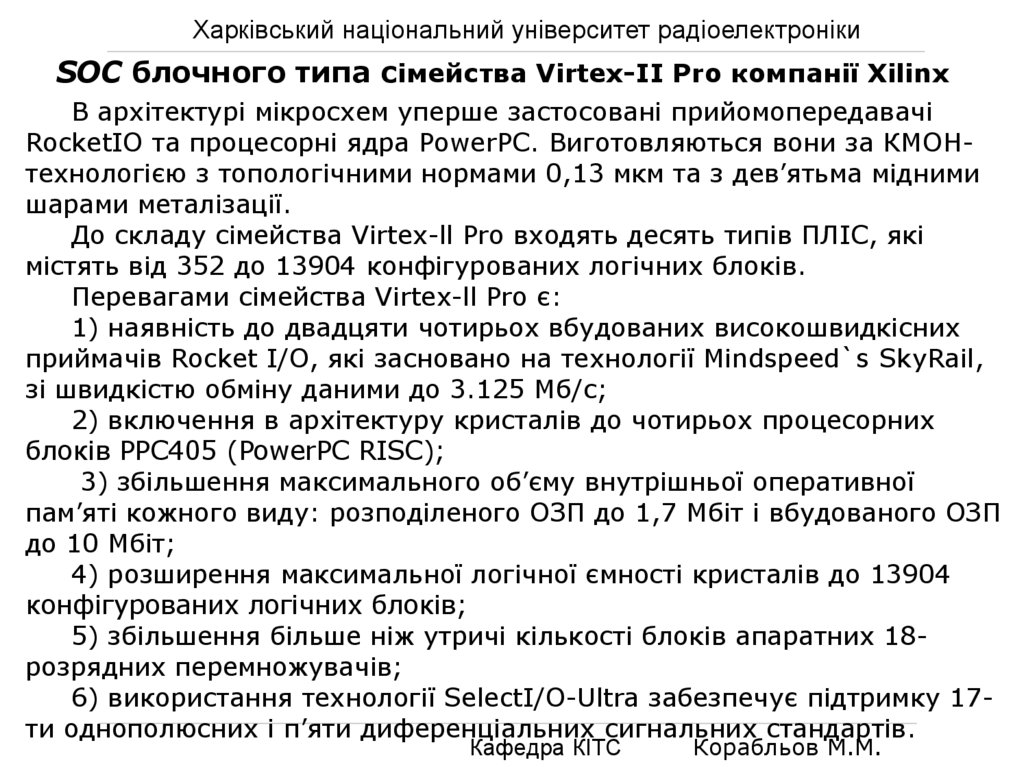

Харківський національний університет радіоелектронікиSOC блочного типа сімейства Virtex-II Pro компанії Xilinx

В архітектурі мікросхем уперше застосовані прийомопередавачі

RocketIO та процесорні ядра PowerPC. Виготовляються вони за КМОНтехнологією з топологічними нормами 0,13 мкм та з дев’ятьма мідними

шарами металізації.

До складу сімейства Virtex-ll Pro входять десять типів ПЛІС, які

містять від 352 до 13904 конфігурованих логічних блоків.

Перевагами сімейства Virtex-ll Pro є:

1) наявність до двадцяти чотирьох вбудованих високошвидкісних

приймачів Rocket I/O, які засновано на технології Mindspeed`s SkyRail,

зі швидкістю обміну даними до 3.125 Мб/с;

2) включення в архітектуру кристалів до чотирьох процесорних

блоків PPC405 (PowerPC RISC);

3) збільшення максимального об’єму внутрішньої оперативної

пам’яті кожного виду: розподіленого ОЗП до 1,7 Мбіт і вбудованого ОЗП

до 10 Мбіт;

4) розширення максимальної логічної ємності кристалів до 13904

конфігурованих логічних блоків;

5) збільшення більше ніж утричі кількості блоків апаратних 18розрядних перемножувачів;

6) використання технології SelectI/O-Ultra забезпечує підтримку 17ти однополюсних і п’яти диференціальних сигнальних стандартів.

Кафедра КІТС

Корабльов М.М.

21.

Харківський національний університет радіоелектронікиSOC блочного типа сімейства Virtex-II Pro компанії Xilinx

Кафедра КІТС

Корабльов М.М.

22.

Харківський національний університет радіоелектронікиSOC блочного типа сімейства Virtex-II Pro компанії Xilinx

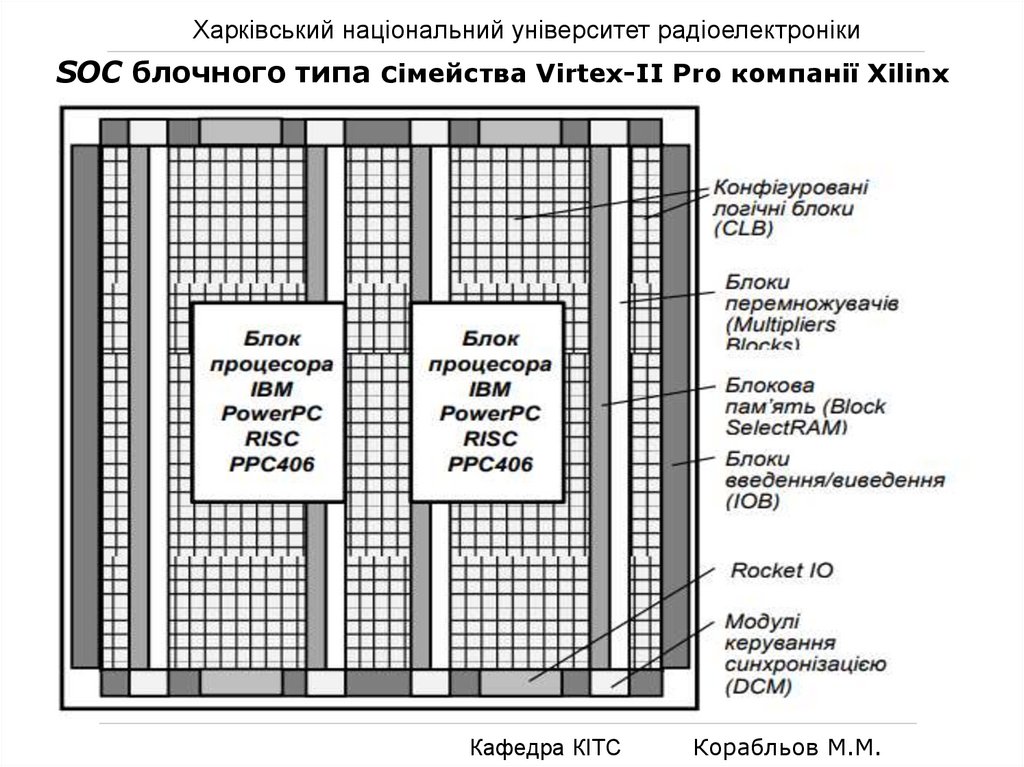

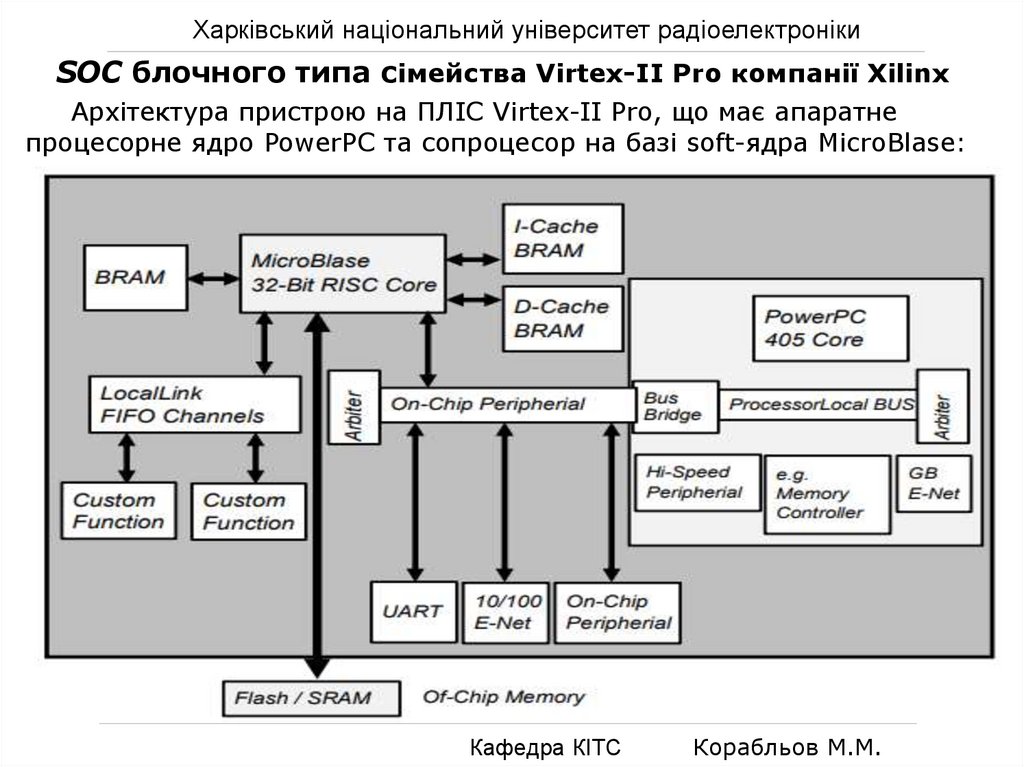

В архітектурі ПЛІС Virtex-II Pro можна виділити модулі загального

призначення і спеціалізовані модулі.

У модулі загального призначення входять:

конфігуровані логічні блоки (CLB);

блокові ОЗП (Block SelectRAM) з об’ємом пам’яті у блоці 18 кбіт;

блоки множення (Multipliers Blocks) – до 556, 18×18 біт.

RocketIO є повністю дуплексним послідовним прийомопередавачем

(SERDES), що підтримує з’єднання від 2 до 24 каналів з пропускною

здатністю від 622 Мбіт/с до 3,125 Гбіт/с.

Процесорний блок PowerPC – це вбудоване hard-ядро на тактову

частоту до 400 МГц з гарвардською архітектурою, п’ятиcтупеневим

конвеєрним трактом передачі даних, апаратними засобами

множення/ділення. Блок також містить тридцять два 32-розрядних

регістра загального призначення, асоціативні двонаправлені схеми кешпам’яті команд і даних ємністю 16 Кбіт кожна, блок управління

пам’яттю, 64-входові буфери трансляції/перегляду (TLB, Translation Look

aside Buffers), інтерфейс вбудованої спеціальної пам’яті. Розміри

сторінки можуть змінюватися в межах від 1К до 16 Мбіт. Є вбудований

таймер.

Кафедра КІТС

Корабльов М.М.

23.

Харківський національний університет радіоелектронікиSOC блочного типа сімейства Virtex-II Pro компанії Xilinx

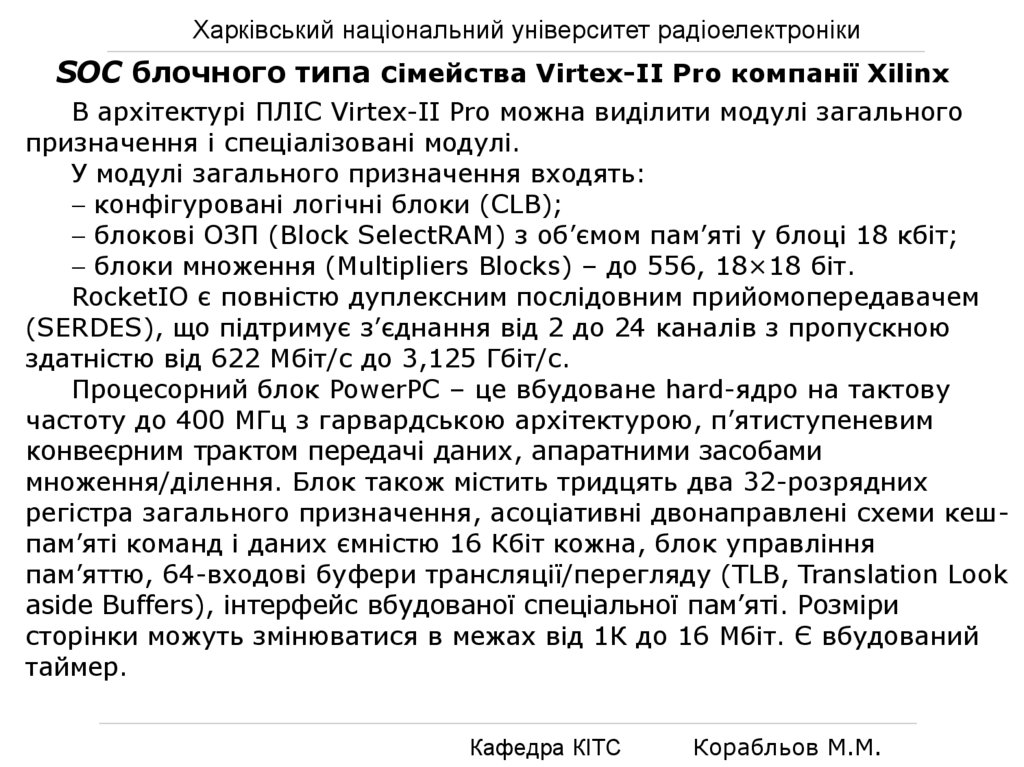

Архітектура пристрою на ПЛІС Virtex-II Pro, що має апаратне

процесорне ядро PowerPC та сопроцесор на базі soft-ядра MicroBlase:

Кафедра КІТС

Корабльов М.М.

24.

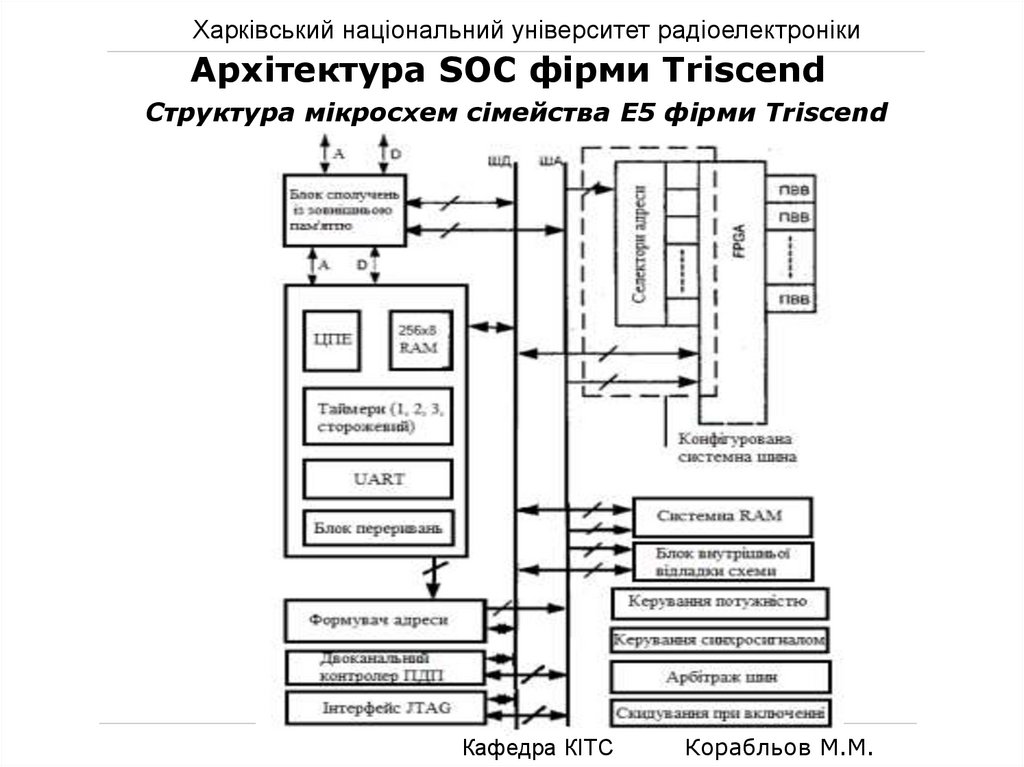

Харківський національний університет радіоелектронікиАрхітектура SOC фірми Triscend

Структура мікросхем сімейства Е5 фірми Triscend

Кафедра КІТС

Корабльов М.М.

25.

Харківський національний університет радіоелектронікиАрхітектура SOC фірми Triscend

Структура мікросхем сімейства Е5 фірми Triscend

До складу мікросхем цього сімейства входять наступні основні блоки:

• Мікроконтролерне ядро з тривалістю командного циклу 4 такта.

• FPGA з числом логічних комірок типу LUT (від 256 до 3200).

• Високопродуктивна конфігурована системна шина CSI (Configurable

System Interconnect) з двома 8-розрядними шинами даних, 32-розрядною

шиною адреси і адресними селекторами.

• Блок програмованих портів вводу / виводу ПВВ (PIO, Programmable

Input-Output port) з програмуванням звичайних або розширених

вихідних потоків.

• Блок сполучення із зовнішньою пам'яттю для підключення до SOC

зовнішніх запам'ятовуючих пристроїв.

• Контролер прямого доступу до пам'яті DMA (Direct Memory Access) з

двома незалежними каналами.

• Блок інтерфейсу JTAG для завантаження пам'яті конфігурації та

виконуваної програми і для налагодження пристроїв.

• Спеціальний блок внутрішнього налагодження (In-System Debugging

Hardware Breakpoint Unit), що дозволяє задавати різні умови зупинки при

виконанні мікроконтролером програми.

• Блок керування енергоспоживанням.

• Система тактування із зовнішнім або внутрішнім генератором.

Кафедра КІТС

Корабльов М.М.

26.

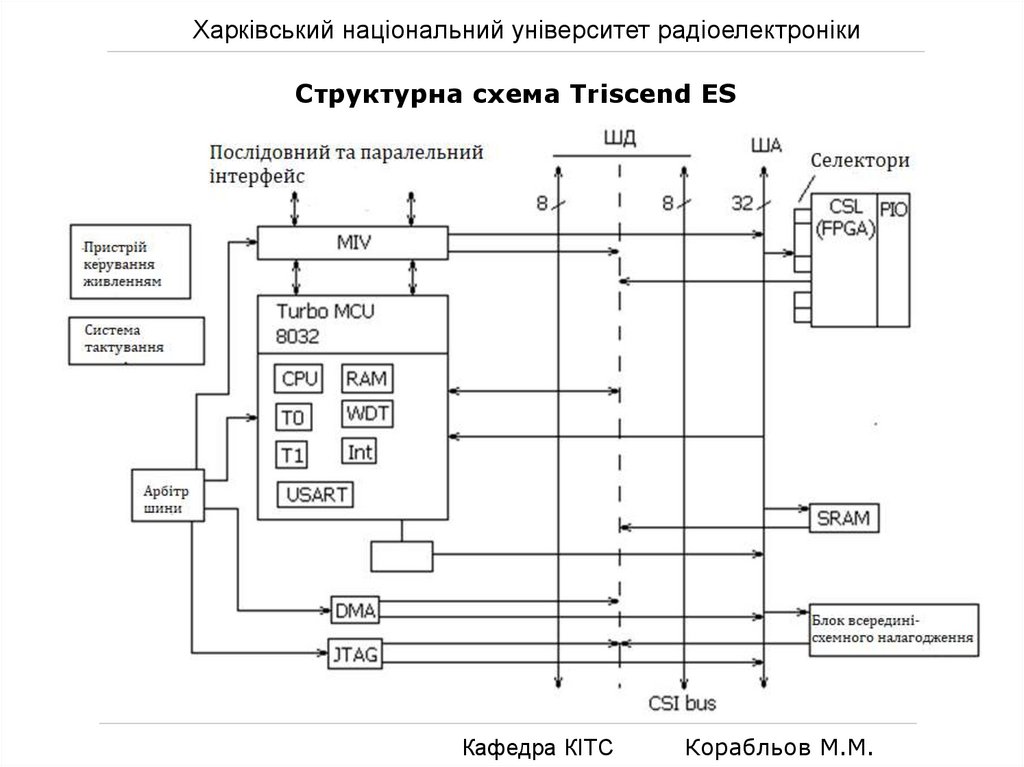

Харківський національний університет радіоелектронікиСтруктурна схема Triscend ES

Кафедра КІТС

Корабльов М.М.

27.

Харківський національний університет радіоелектронікиСтруктурна схема Triscend ES

MCU – мікропроцесорний пристрій.

CSL - конфігурована системна логіка.

PIO – порти вводу/виводу.

CSI – конфігураційна система передачі.

DMA – контролер ПДП.

MIV - контролер зовнішньої пам'яті обсягом до 256 Кбайт.

Користувач може програмувати CSL, PIO та CSI.

Для проектування використовується пакет System

Designer:

1. AVR Assembler v.1.3

2. Редактор мови опису апаратури HDL planer (VHDL –

Verilog)

3. Синтезатор мови опису апаратури (скорочена

бібліотека логічних елементів FPGA, Atmel)

4. Середовище розміщення та розведення FPGA.

Кафедра КІТС

Корабльов М.М.

28.

Харківський національний університет радіоелектроніки32-розрядні мікроконтролери на основі ядра ARM7TDMI

Кафедра КІТС

Корабльов М.М.

29.

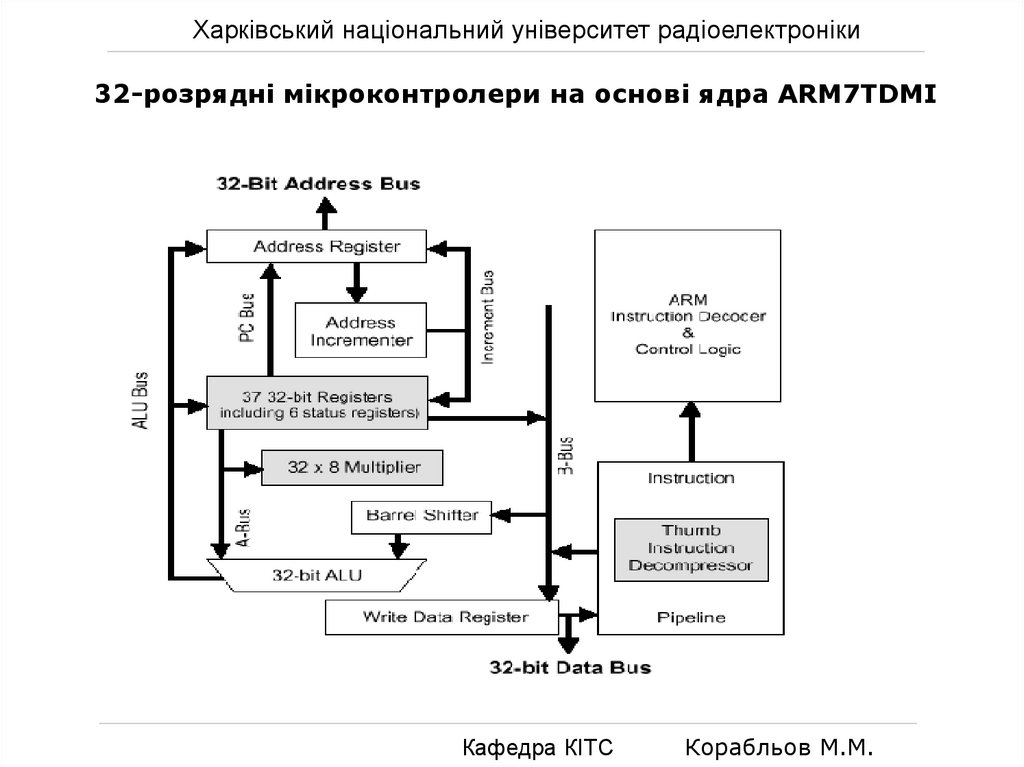

Харківський національний університет радіоелектроніки32-розрядні мікроконтролери на основі ядра ARM7TDMI

Основні характеристики:

- 32-розрядний процесор RISC.

- 32-розрядна адресація - лінійний адресний простір у 4

Гбайти.

- Тридцять один 32-розрядний регістр загального

призначення та шість регістрів стану.

- Регістри адресів, запису та конвеєра.

- Циклічний зсувний пристрій та перемножувач.

- Трирівневий конвеєр (вибірка команди, її декодування

та виконання).

- Швидкий відгук на переривання застосувань реального

масштабу часу.

- Підтримка систем віртуальної пам'яті.

Кафедра КІТС

Корабльов М.М.

30.

Харківський національний університет радіоелектроніки32-розрядні мікроконтролери на основі ядра ARM7TDMI

32-розрядна система команд ядра ARM7 містить

одинадцять базових типів команд :

- два типи команд використовують вбудований

арифметико-логічний пристрій, циклічний зсувний

пристрій та помножувач при операціях над даними у

банку з 31 регістру, форматом по 32 розряди кожен;

- три класи команд управління переміщенням даних між

пам'яттю та регістрами, один оптимізований на

забезпечення гнучкості адресації, інший під швидке

контекстне перемикання та третій під підкачування

даних;

- три команди управляють потоком та рівнем привілею

виконання;

- три типи команд призначені керувати зовнішніми

співпроцесорами, що дозволяє розширити функціональні

можливості системи команд поза ядра.

Кафедра КІТС

Корабльов М.М.

31.

Харківський національний університет радіоелектроніки32-розрядні мікроконтролери на основі ядра ARM7TDMI

Кафедра КІТС

Корабльов М.М.

32.

Харківський національний університет радіоелектроніки32-розрядні мікроконтролери на основі ядра ARM7TDMI

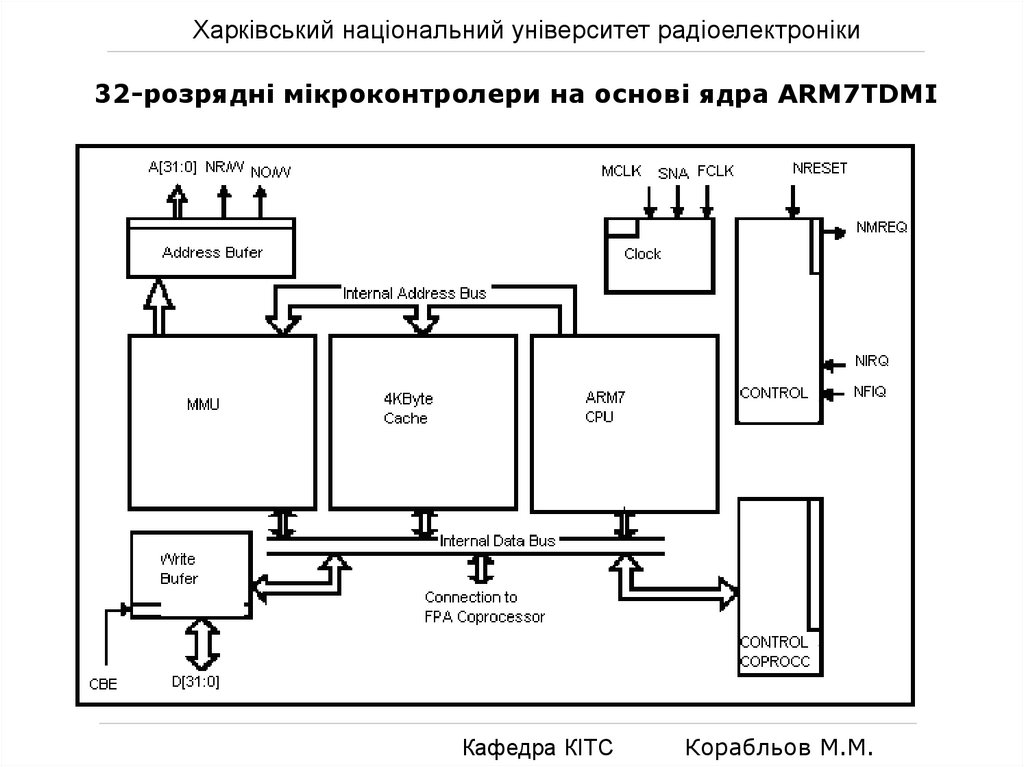

Інтерфейс із пам'яттю у процесора ARM7TDMI

організовується такими основними елементами:

- 32-розрядною шиною адреси, що визначає адресу

комірки пам'яті, яку необхідно використовувати.

- 32-розрядною двонаправленою шиною передачі даних

D[31:0], плюс двома окремими односпрямованими шинами

даних DIN[31:0] та DOUT[31:0], через які переміщуються

команди та дані. Дані можуть мати формат слова, півслова

або байту.

- сигналами управління, що визначають, наприклад,

формат даних, що переміщуються, і напрямок їх передачі і,

крім того, рівень пріоритету.

Кафедра КІТС

Корабльов М.М.

33.

Харківський національний університет радіоелектронікиКонтрольні питання

1. ПЛІС з комбінованою архітектурою(FLEX).

2. Системи на кристалі (SOPC), структури та

основні характеристики.

3. SOPC з однорідною структурою.

4. SOPC з блочними структурами.

5. Структура SOPC блочного типу микросхемы

FPSLIC (Atmel).

6. SOPS блочного типу фірми Altera.

7. Структурна схема Triscend ES.

8. 32-розрядні мікроконтролери на основі ядра

ARM7TDMI.

Кафедра КІТС

Корабльов М.М.

Электроника

Электроника