Похожие презентации:

Булевы выражения. Глава 2

1.

Глава 2 :: ТемыВведение

Булевы выражения

Булева алгебра

От логики к логическим элементам

Многоуровневая комбинационная

логика

Что за X и Z?

Карты Карно

Базовые комбинационные блоки

Временные характеристик

Глава 2 <1>

2.

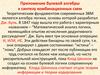

ВведениеЛогическая схема состоит из:

• Входов

• Выходов

• Функциональной спецификации

• Временной спецификации

functional spec

inputs

outputs

timing spec

Глава 2 <2>

3.

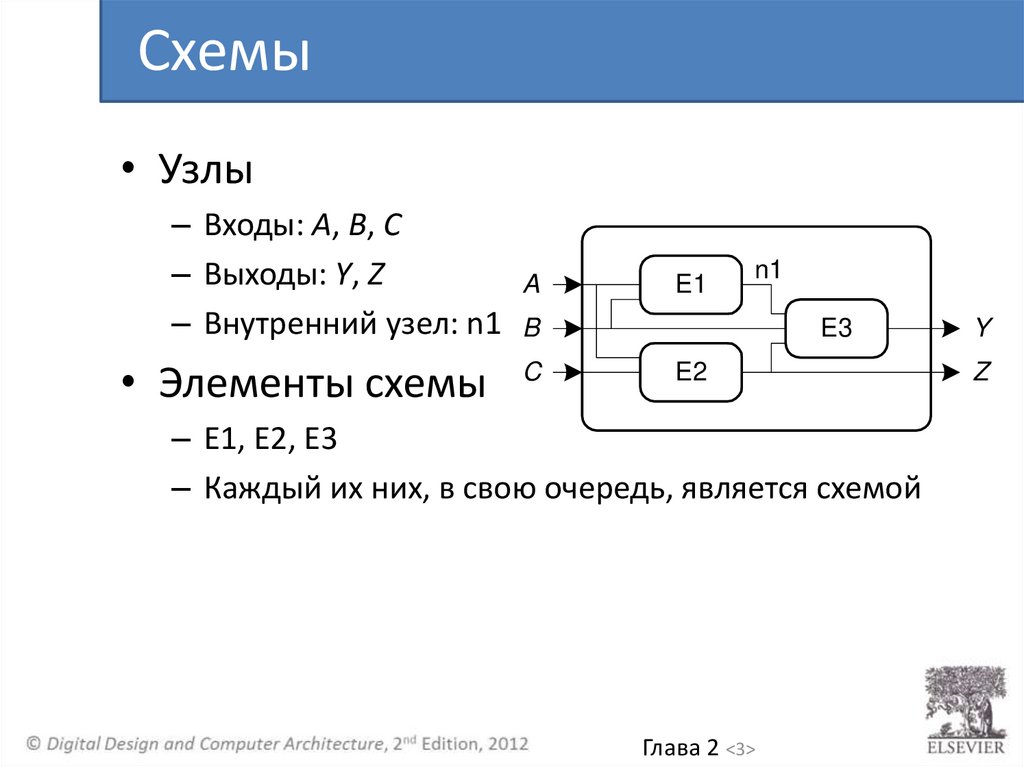

Схемы• Узлы

– Входы: A, B, C

– Выходы: Y, Z

– Внутренний узел: n1

• Элементы схемы

A

E1

n1

B

C

E3

E2

– E1, E2, E3

– Каждый их них, в свою очередь, является схемой

Глава 2 <3>

Y

Z

4.

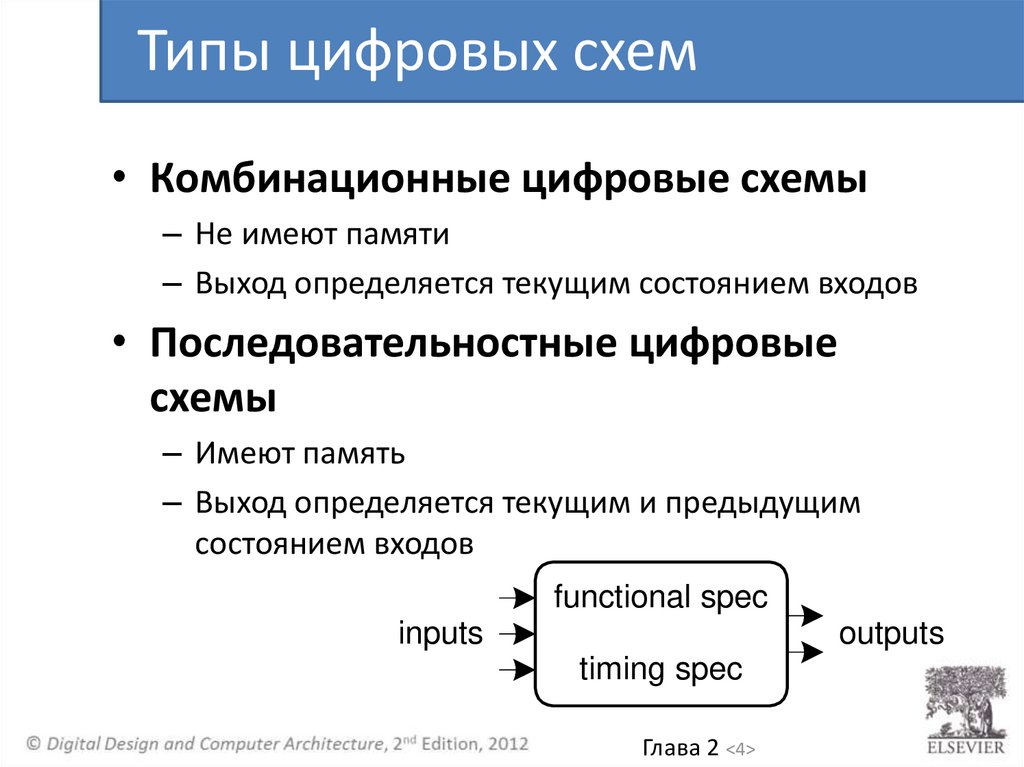

Типы цифровых схем• Комбинационные цифровые схемы

– Не имеют памяти

– Выход определяется текущим состоянием входов

• Последовательностные цифровые

схемы

– Имеют память

– Выход определяется текущим и предыдущим

состоянием входов

functional spec

inputs

outputs

timing spec

Глава 2 <4>

5.

Правила комбинационной композиции• Каждый элемент сам является

комбинационным

• Каждое узел схемы является или входом,

или подсоединен к одномуединственному выходу другого элемента

• Схема не содержит циклических путей

• Пример:

Глава 2 <5>

6.

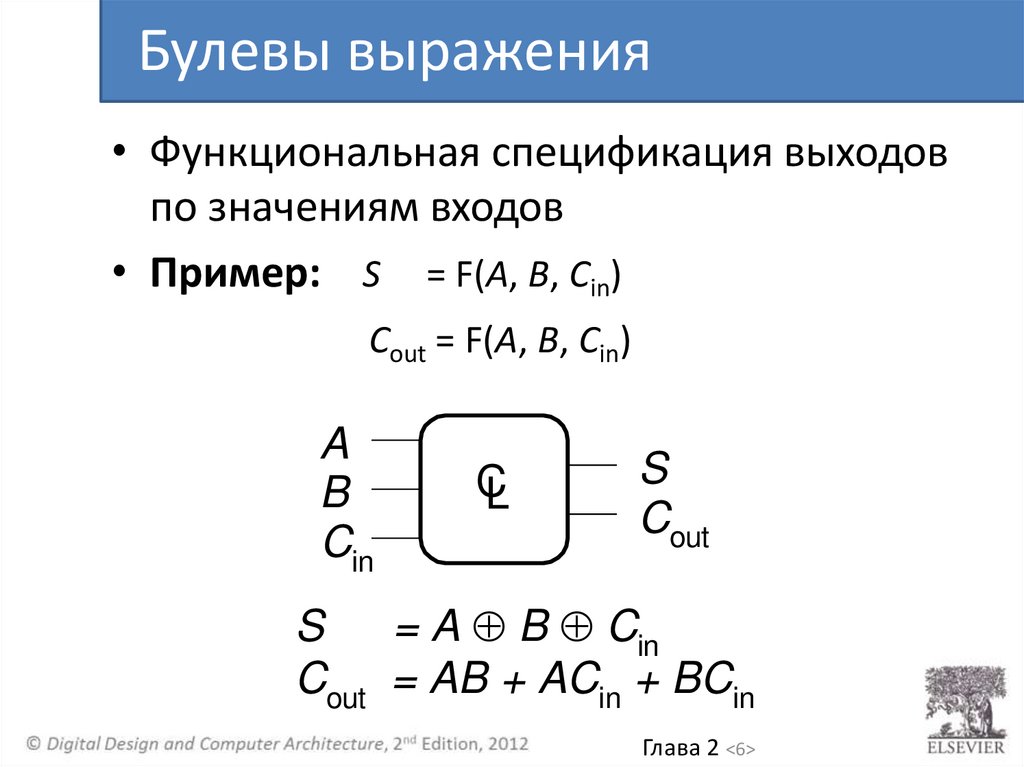

Булевы выражения• Функциональная спецификация выходов

по значениям входов

• Пример: S = F(A, B, Cin)

Cout = F(A, B, Cin)

A

B

Cin

C

L

S

Cout

S

= A B Cin

Cout = AB + ACin + BCin

Глава 2 <6>

7.

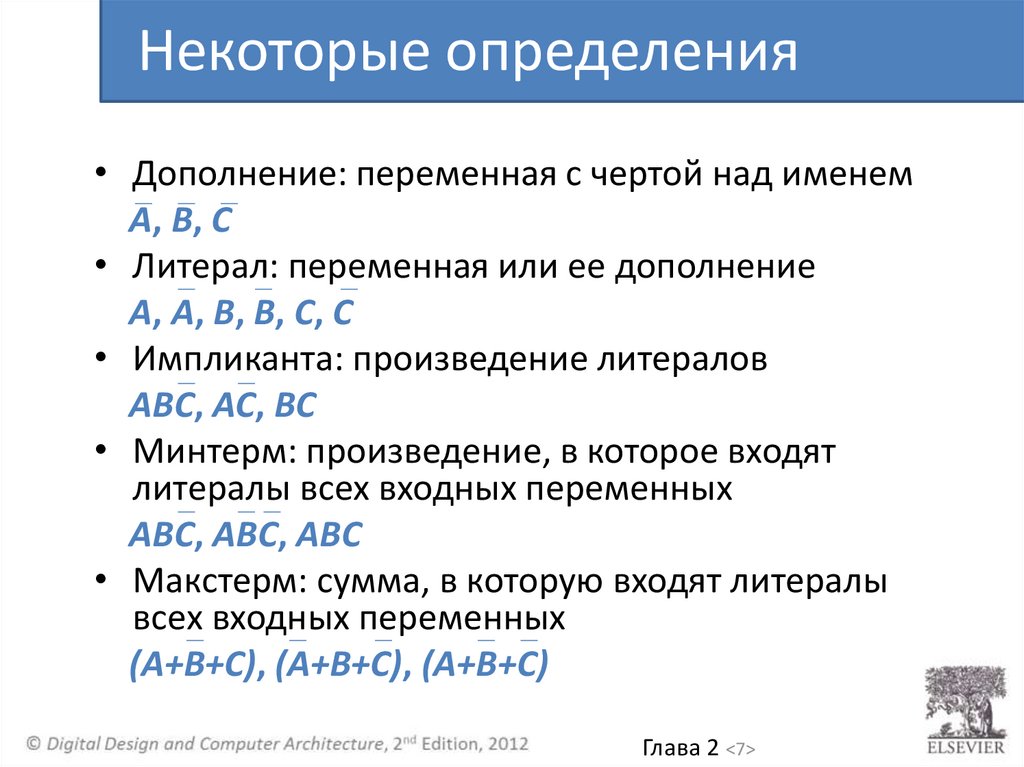

Некоторые определения• Дополнение: переменная с чертой над именем

A, B, C

• Литерал: переменная или ее дополнение

A, A, B, B, C, C

• Импликанта: произведение литералов

ABC, AC, BC

• Минтерм: произведение, в которое входят

литералы всех входных переменных

ABC, ABC, ABC

• Макстерм: сумма, в которую входят литералы

всех входных переменных

(A+B+C), (A+B+C), (A+B+C)

Глава 2 <7>

8.

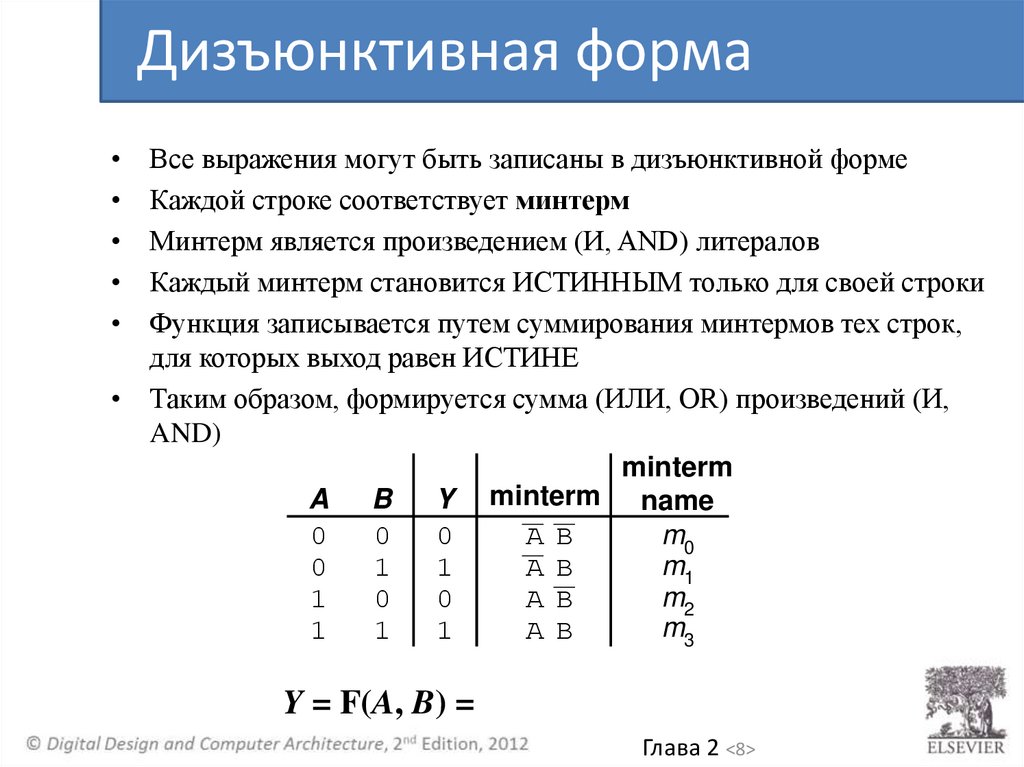

Дизъюнктивная формаВсе выражения могут быть записаны в дизъюнктивной форме

Каждой строке соответствует минтерм

Минтерм является произведением (И, AND) литералов

Каждый минтерм становится ИСТИННЫМ только для своей строки

Функция записывается путем суммирования минтермов тех строк,

для которых выход равен ИСТИНЕ

• Таким образом, формируется сумма (ИЛИ, OR) произведений (И,

AND)

minterm

A

B

Y minterm name

0

0

0

A B

m0

m1

0

1

1

A B

m2

1

0

0

A B

m3

1

1

1

A B

Y = F(A, B) =

Глава 2 <8>

9.

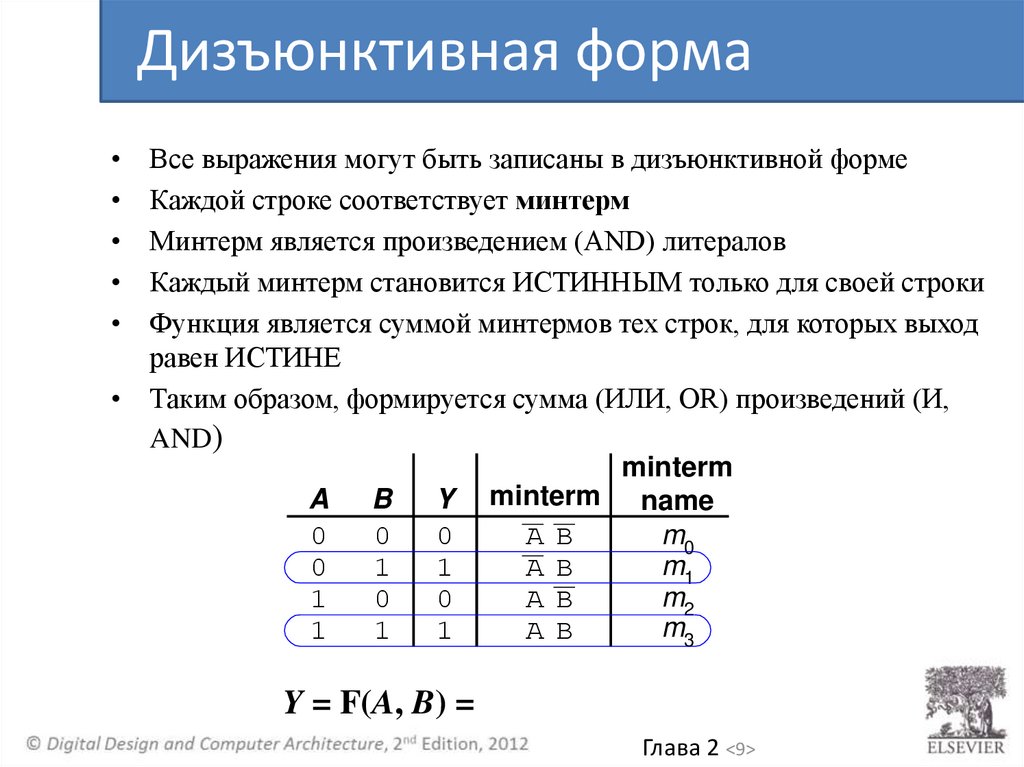

Дизъюнктивная формаВсе выражения могут быть записаны в дизъюнктивной форме

Каждой строке соответствует минтерм

Минтерм является произведением (AND) литералов

Каждый минтерм становится ИСТИННЫМ только для своей строки

Функция является суммой минтермов тех строк, для которых выход

равен ИСТИНЕ

• Таким образом, формируется сумма (ИЛИ, OR) произведений (И,

AND)

minterm

A

B

Y minterm name

0

0

0

A B

m0

m1

0

1

1

A B

m2

1

0

0

A B

m3

1

1

1

A B

Y = F(A, B) =

Глава 2 <9>

10.

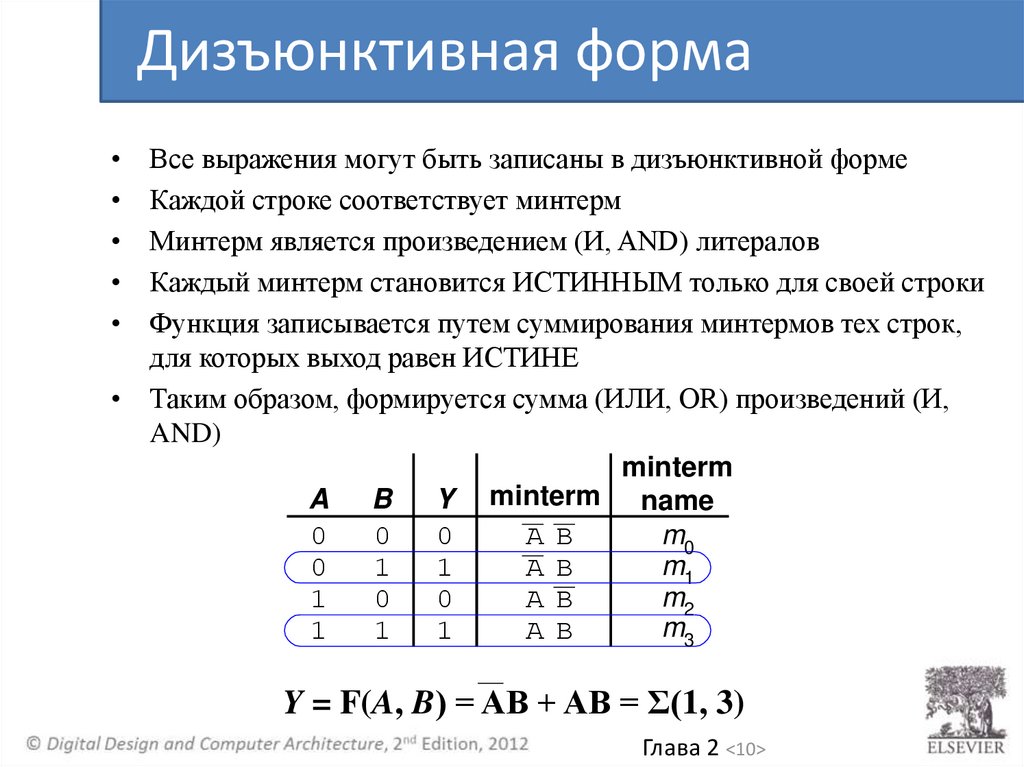

Дизъюнктивная формаВсе выражения могут быть записаны в дизъюнктивной форме

Каждой строке соответствует минтерм

Минтерм является произведением (И, AND) литералов

Каждый минтерм становится ИСТИННЫМ только для своей строки

Функция записывается путем суммирования минтермов тех строк,

для которых выход равен ИСТИНЕ

• Таким образом, формируется сумма (ИЛИ, OR) произведений (И,

AND)

minterm

A

B

Y minterm name

0

0

0

A B

m0

m1

0

1

1

A B

m2

1

0

0

A B

m3

1

1

1

A B

Y = F(A, B) = AB + AB = Σ(1, 3)

Глава 2 <10>

11.

Конъюнктивная форма• Все булевы выражения могут быть записаны в конъюнктивной

форме

• Каждой строке соответствует макстерм

• Макстерм является суммой (ИЛИ, OR) литералов

• Каждый макстерм становится ЛОЖНЫМ только для своей строки

• Функция является произведением макстермов тех строк, для

которых выход равен ЛОЖЬ

• Таким образом, формируется произведение (И, AND) сумм (ИЛИ,

OR)

A

0

0

1

1

B

0

1

0

1

Y

0

1

0

1

maxterm

maxterm name

A

A

A

A

+

+

+

+

B

B

B

B

M0

M1

M2

M3

Y = F(A, B) = (A + B)(A + B) = Π(0, 2)

Глава 2 <11>

12.

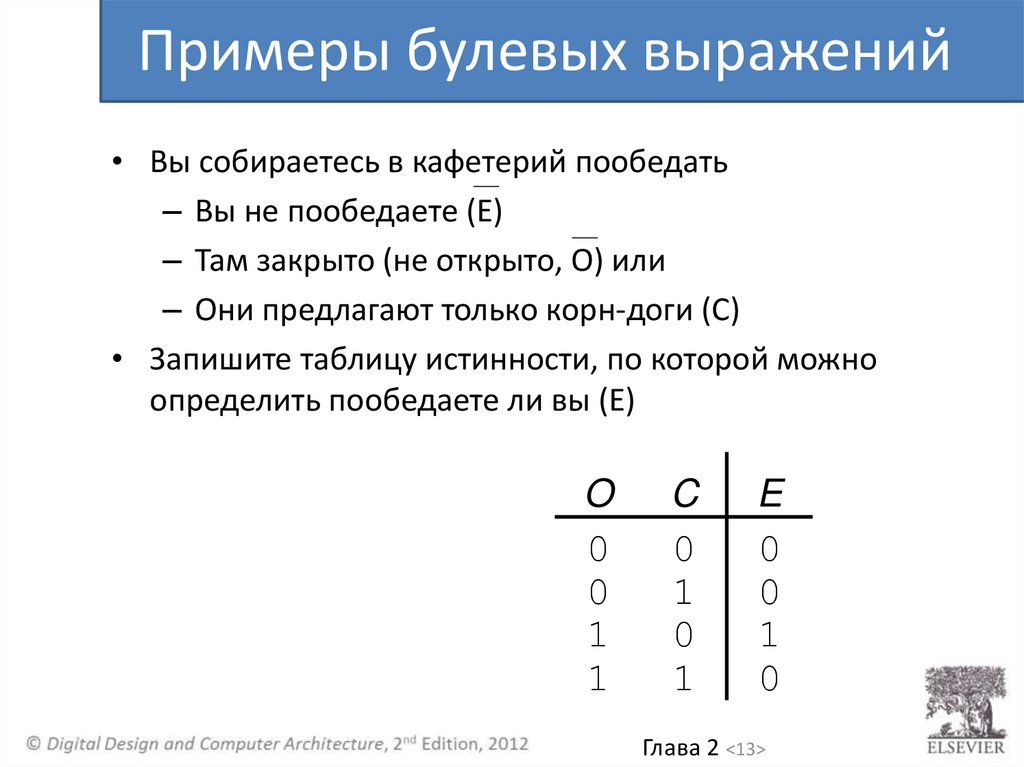

Примеры булевых выражений• Вы собираетесь в кафетерий пообедать

– Вы не пообедаете (E)

– Там закрыто (не открыто, O) или

– Они предлагают только корн-доги (C)

• Запишите таблицу истинности, по которой можно

определить пообедаете ли вы (E)

O

0

0

1

1

C

0

1

0

1

E

Глава 2 <12>

13.

Примеры булевых выражений• Вы собираетесь в кафетерий пообедать

– Вы не пообедаете (E)

– Там закрыто (не открыто, O) или

– Они предлагают только корн-доги (C)

• Запишите таблицу истинности, по которой можно

определить пообедаете ли вы (E)

O

0

0

1

1

C

0

1

0

1

E

0

0

1

0

Глава 2 <13>

14.

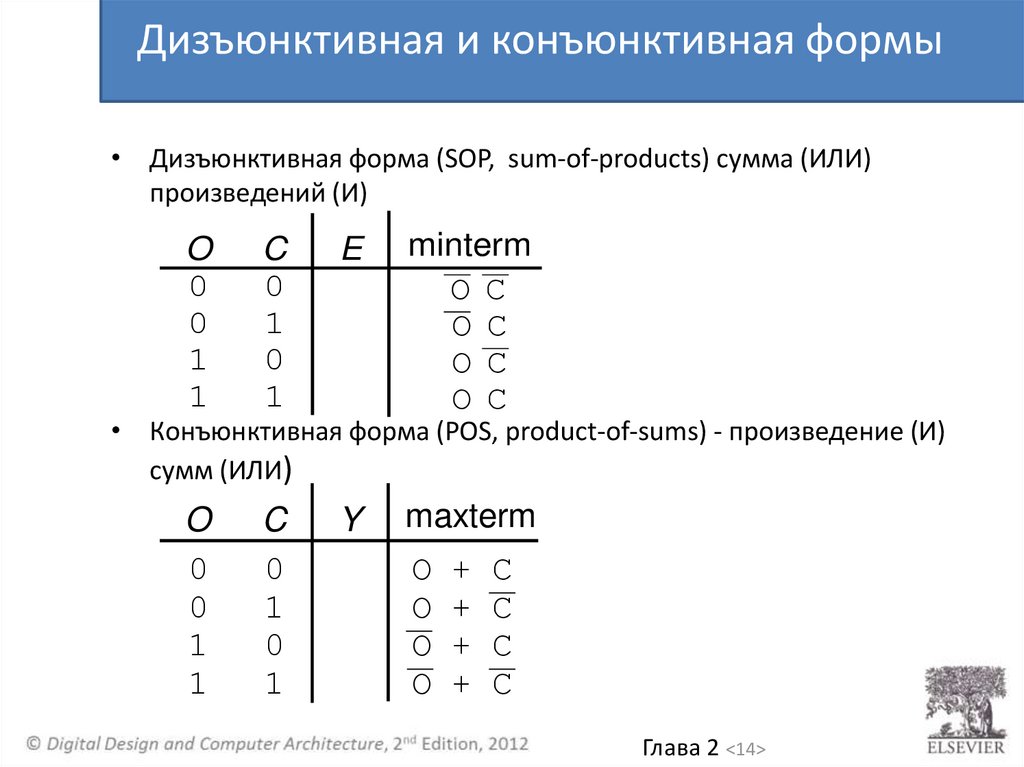

Дизъюнктивная и конъюнктивная формы• Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ)

произведений (И)

O

0

0

1

1

C

0

1

0

1

E

minterm

O C

O C

O C

O C

• Конъюнктивная форма (POS, product-of-sums) - произведение (И)

сумм (ИЛИ)

O

0

0

1

1

C

0

1

0

1

Y

maxterm

O

O

O

O

+

+

+

+

C

C

C

C

Глава 2 <14>

15.

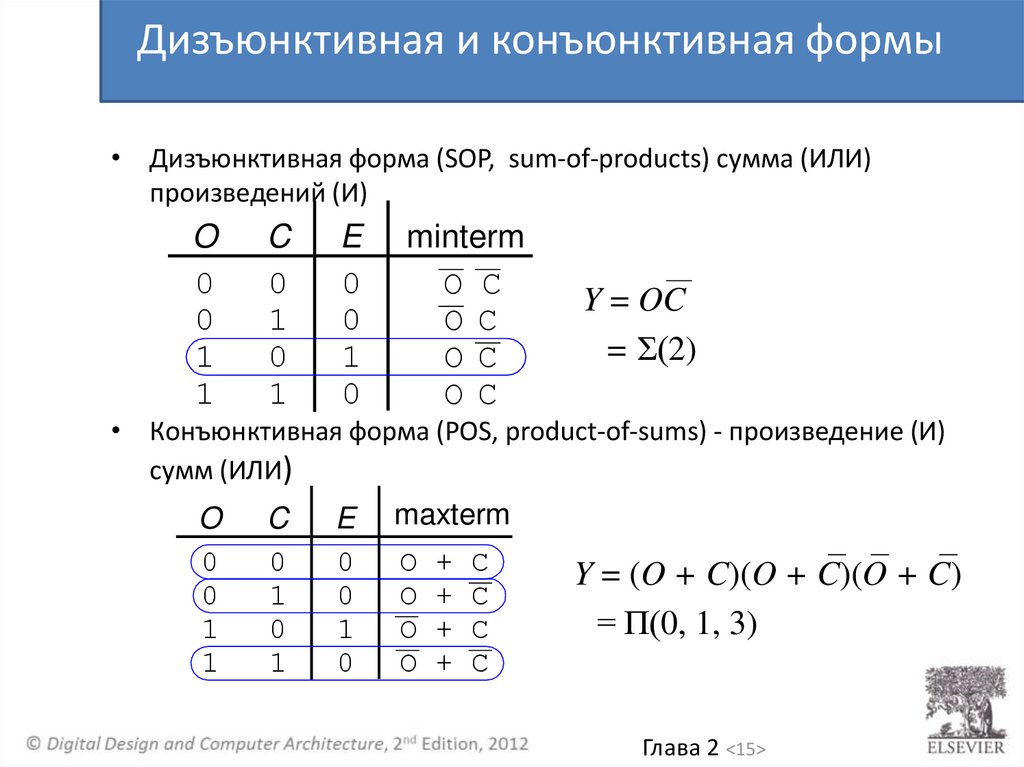

Дизъюнктивная и конъюнктивная формы• Дизъюнктивная форма (SOP, sum-of-products) сумма (ИЛИ)

произведений (И)

O

0

0

1

1

C

0

1

0

1

E

0

0

1

0

minterm

O C

O C

O C

O C

Y = OC

= Σ(2)

• Конъюнктивная форма (POS, product-of-sums) - произведение (И)

сумм (ИЛИ)

O

0

0

1

1

C

0

1

0

1

E

0

0

1

0

maxterm

O

O

O

O

+

+

+

+

C

C

C

C

Y = (O + C)(O + C)(O + C)

= Π(0, 1, 3)

Глава 2 <15>

16.

Булева алгебра• Аксиомы и теоремы позволяют упрощать

булевы выражения

• Подобно обычной алгебре, но проще:

переменные принимают только два

значения (0 или 1)

• Двойственность аксиом и теорем:

– Можно взаимно заменить И и ИЛИ, 0 и 1

Глава 2 <16>

17.

Булевы аксиомыГлава 2 <17>

18.

T1: Теорема идентичности• B 1=B

• B+0=B

Глава 2 <18>

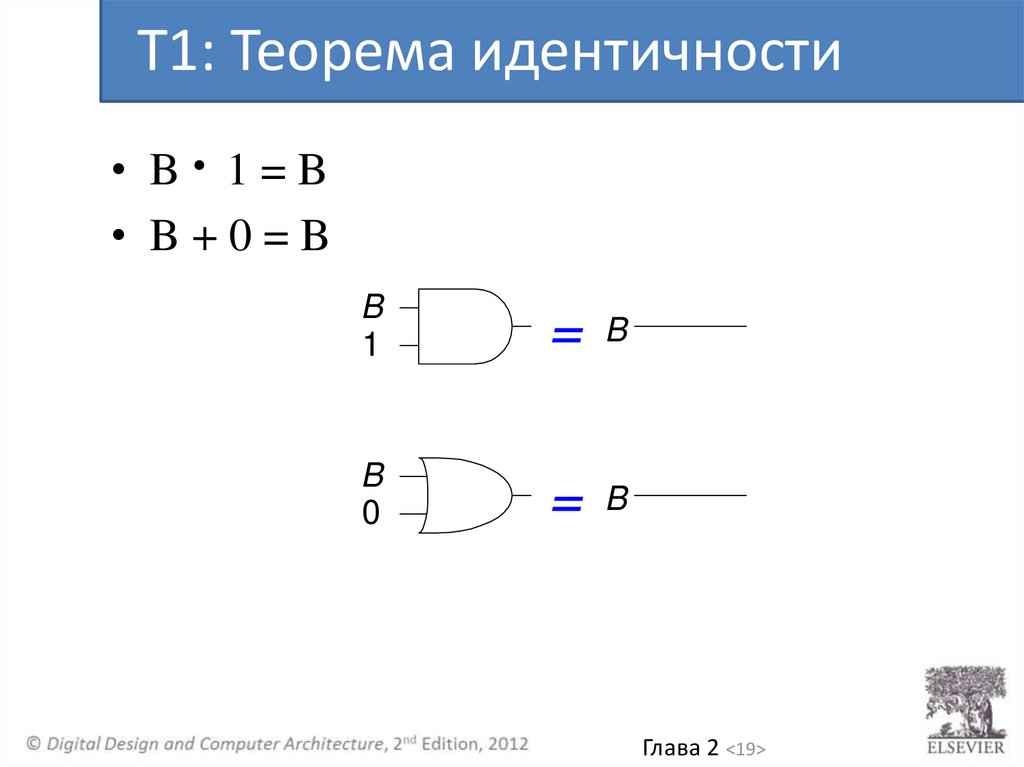

19.

T1: Теорема идентичности• B 1=B

• B+0=B

B

1

=

B

B

0

=

B

Глава 2 <19>

20.

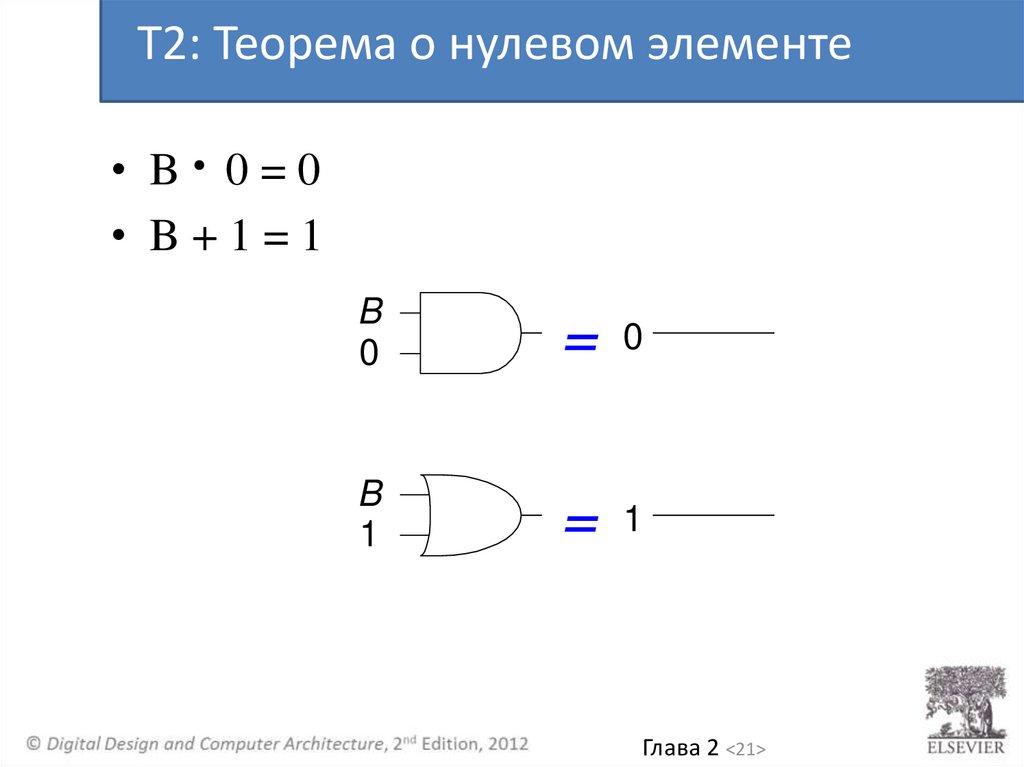

T2: Теорема о нулевом элементе• B 0=0

• B+1=1

Глава 2 <20>

21.

T2: Теорема о нулевом элементе• B 0=0

• B+1=1

B

0

=

0

B

1

=

1

Глава 2 <21>

22.

T3: Теорема об идемпотентности• B B=B

• B+B=B

Глава 2 <22>

23.

T3: Теорема об идемпотентности• B B=B

• B+B=B

B

B

=

B

B

B

=

B

Глава 2 <23>

24.

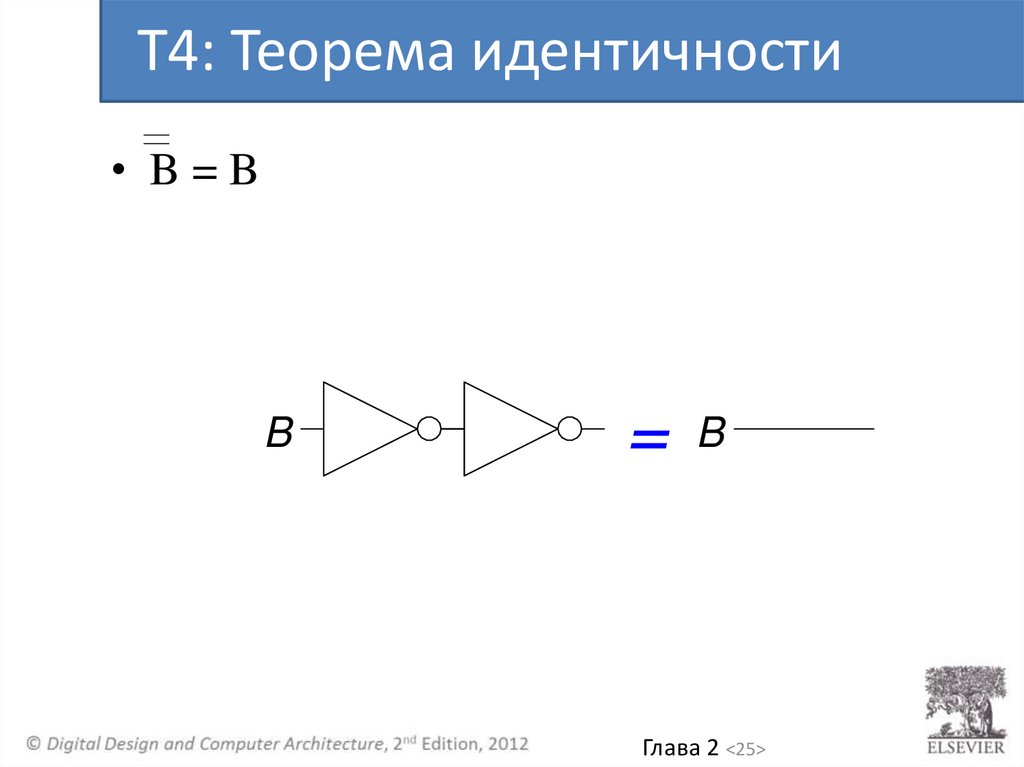

T4: Теорема идентичности• B=B

Глава 2 <24>

25.

T4: Теорема идентичности• B=B

B

=

B

Глава 2 <25>

26.

T5: Теорема о дополнительности• B B=0

• B+B=1

Глава 2 <26>

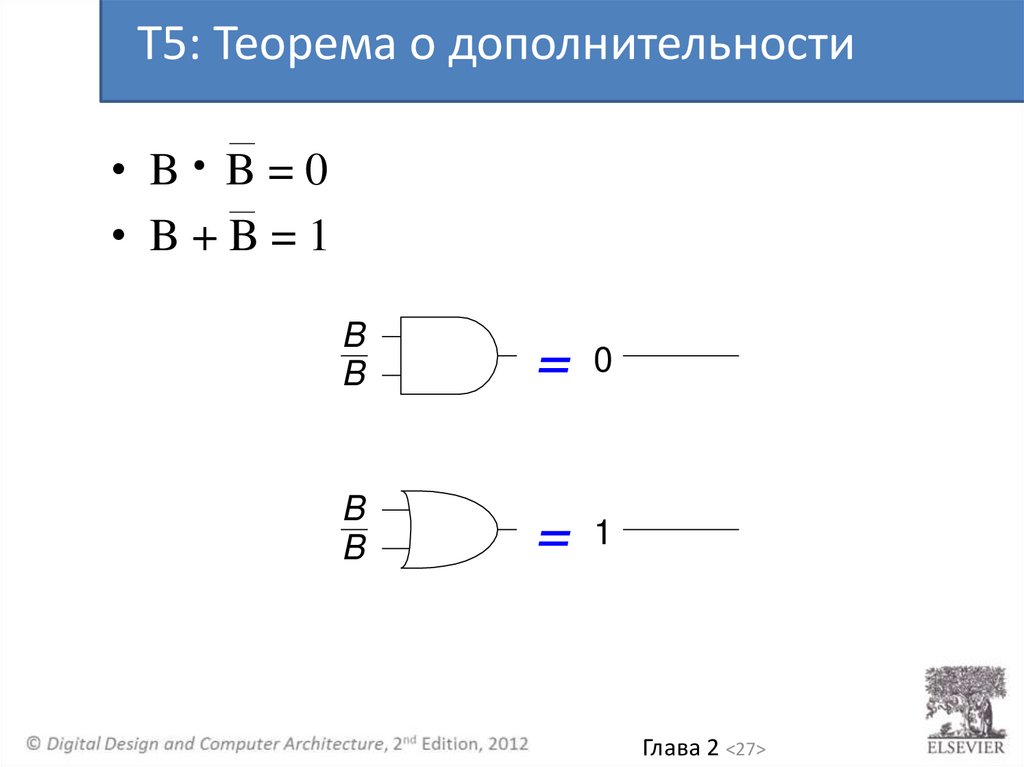

27.

T5: Теорема о дополнительности• B B=0

• B+B=1

B

B

=

0

B

B

=

1

Глава 2 <27>

28.

Булевы теоремы, обзорГлава 2 <28>

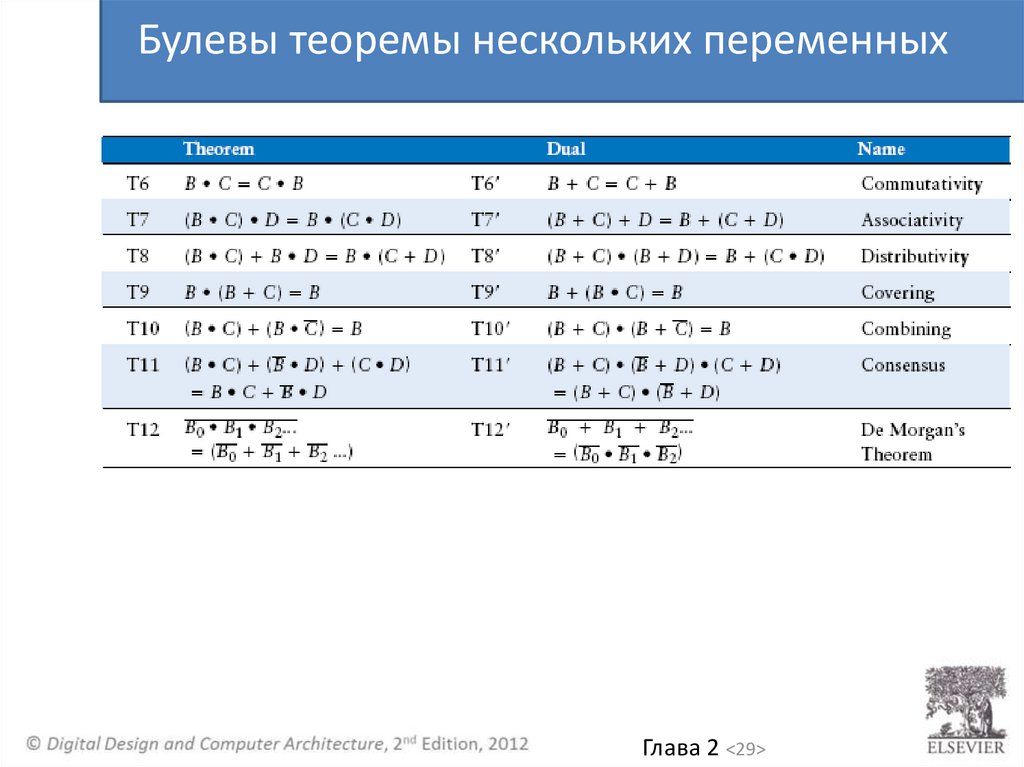

29.

Булевы теоремы нескольких переменныхГлава 2 <29>

30.

Упрощение булевых выраженийПример 1:

• Y = AB + AB

Глава 2 <30>

31.

Упрощение булевых выраженийПример 1:

• Y = AB + AB

= B(A + A)

= B(1)

=B

T8

T5’

T1

Глава 2 <31>

32.

Упрощение булевых выраженийПример 2:

• Y = A(AB + ABC)

Глава 2 <32>

33.

Упрощение булевых выраженийПример 2:

• Y = A(AB + ABC)

= A(AB(1 + C))

= A(AB(1))

= A(AB)

= (AA)B

= AB

T8

T2’

T1

T7

T3

Глава 2 <33>

34.

Теорема де Моргана• Y = AB = A + B

• Y=A+B=A B

A

B

Y

A

B

Y

A

B

Y

A

B

Y

Глава 2 <34>

35.

Перемещение инверсии• Назад:

– Изменить тип элемента

– Добавить инверсию на входы

A

B

Y

A

B

Y

A

B

Y

• Вперед:

– Изменить тип элемента

– Добавить инверсию на выход

A

B

Y

Глава 2 <35>

36.

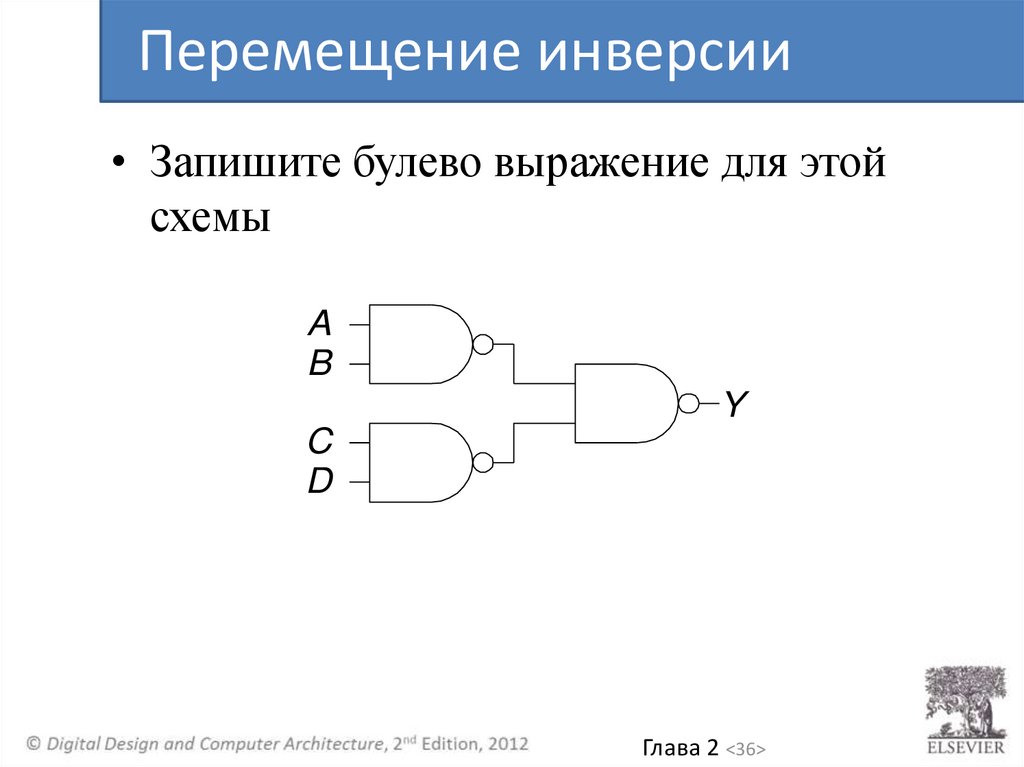

Перемещение инверсии• Запишите булево выражение для этой

схемы

A

B

Y

C

D

Глава 2 <36>

37.

Перемещение инверсии• Запишите булево выражение для этой

схемы

A

B

Y

C

D

Y = AB + CD

Глава 2 <37>

38.

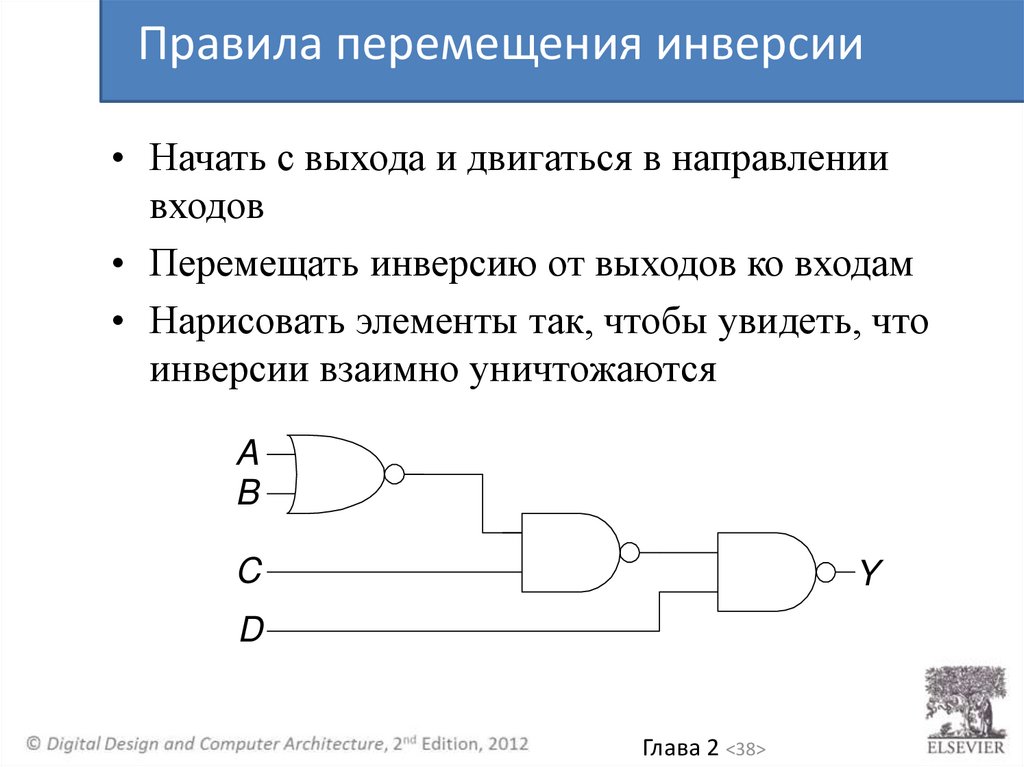

Правила перемещения инверсии• Начать с выхода и двигаться в направлении

входов

• Перемещать инверсию от выходов ко входам

• Нарисовать элементы так, чтобы увидеть, что

инверсии взаимно уничтожаются

A

B

C

Y

D

Глава 2 <38>

39.

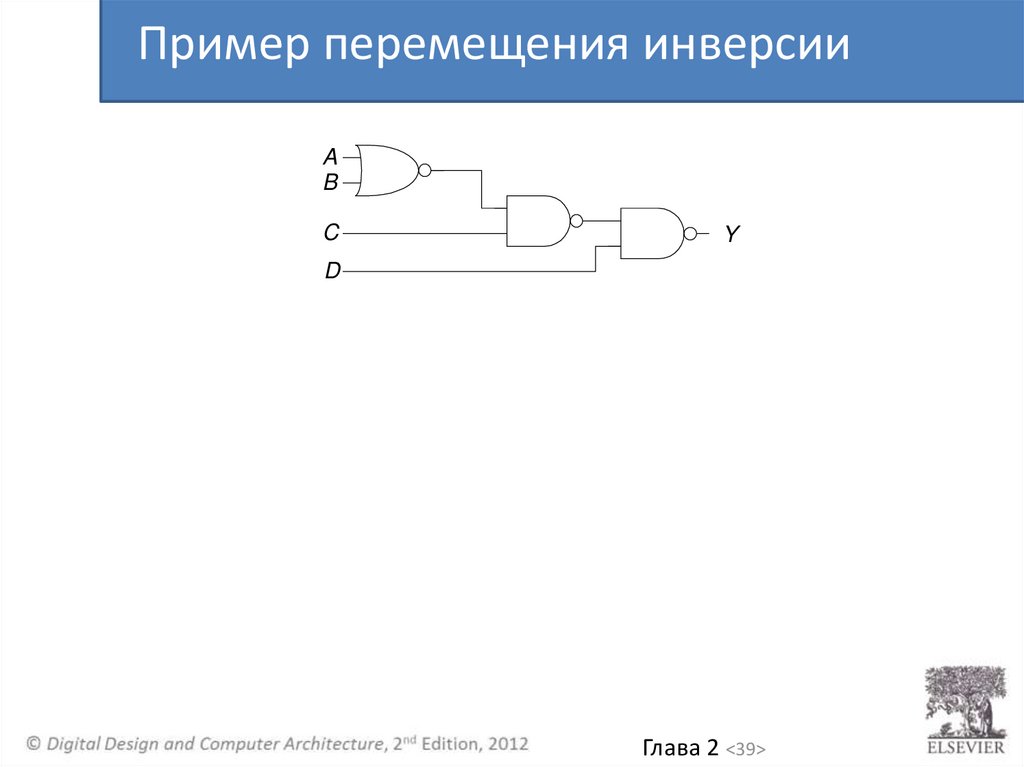

Пример перемещения инверсииA

B

C

Y

D

Глава 2 <39>

40.

Пример перемещения инверсииA

B

C

no output

bubble

Y

D

Глава 2 <40>

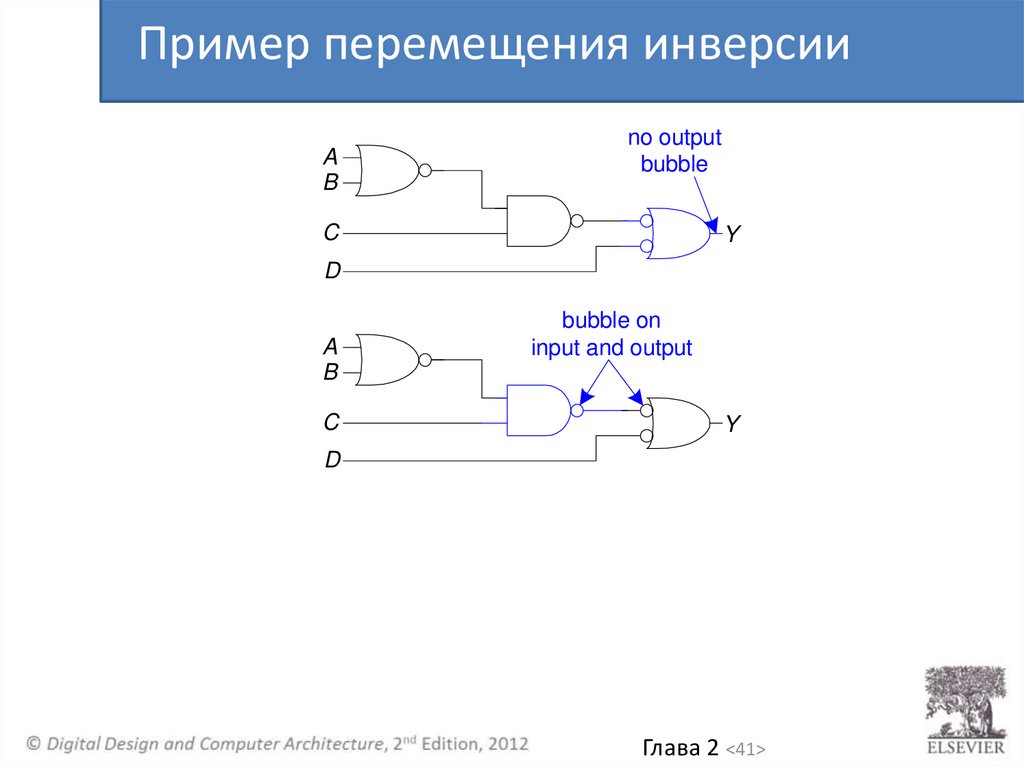

41.

Пример перемещения инверсииA

B

no output

bubble

C

Y

D

A

B

C

bubble on

input and output

Y

D

Глава 2 <41>

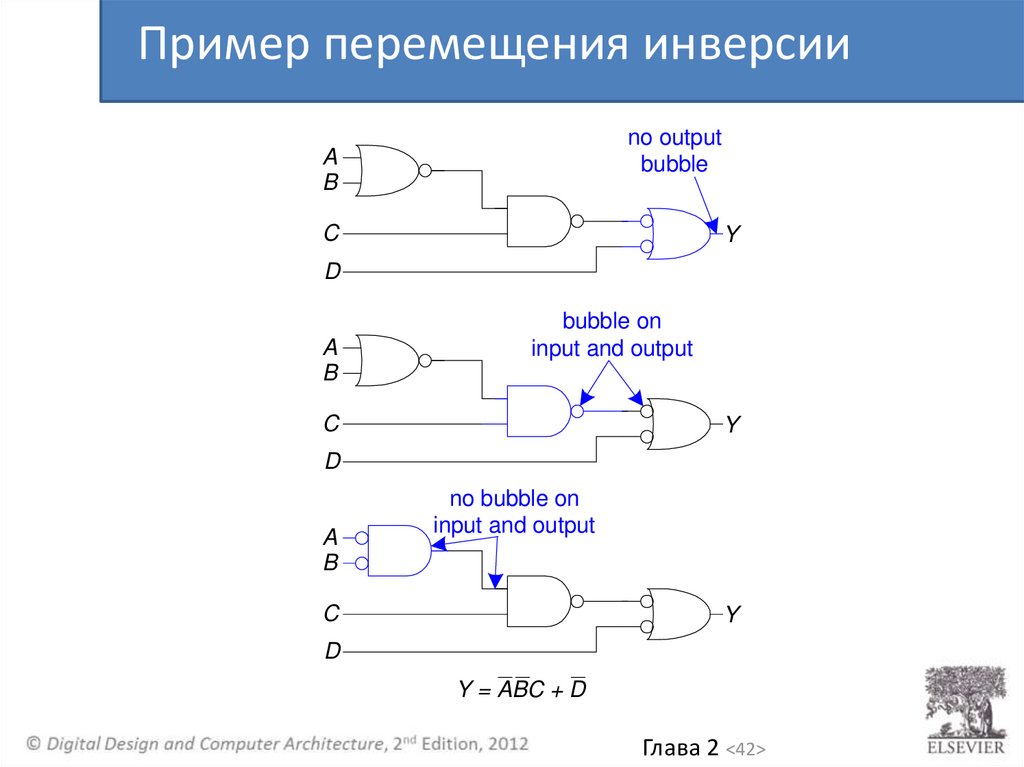

42.

Пример перемещения инверсииno output

bubble

A

B

C

Y

D

A

B

bubble on

input and output

C

Y

D

A

B

no bubble on

input and output

C

Y

D

Y = ABC + D

Глава 2 <42>

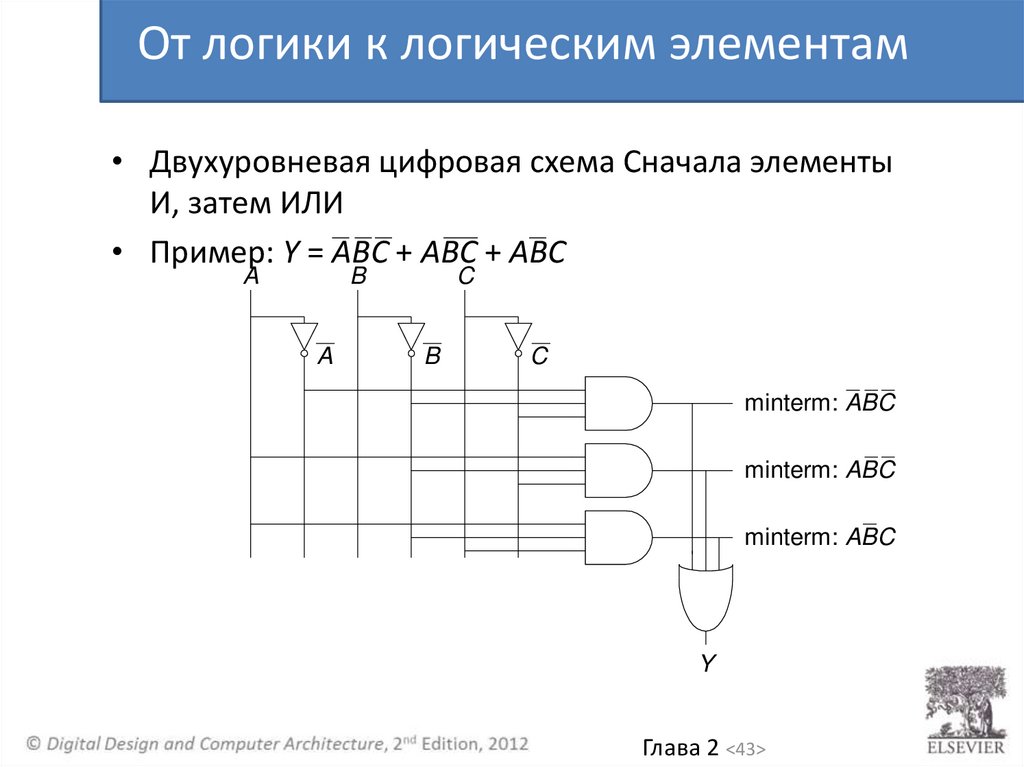

43.

От логики к логическим элементам• Двухуровневая цифровая схема Сначала элементы

И, затем ИЛИ

• Пример: Y = ABC + ABC + ABC

A

B

A

C

B

C

minterm: ABC

minterm: ABC

minterm: ABC

Y

Глава 2 <43>

44.

Правила изображения принципиальных схем• Входы слева (или сверху)

• Выходы справа (или внизу)

• Информация передается от

элементов, расположенных слева, к

элементам, расположенным справа

• Для проводников стараться

использовать прямые линии

Глава 2 <44>

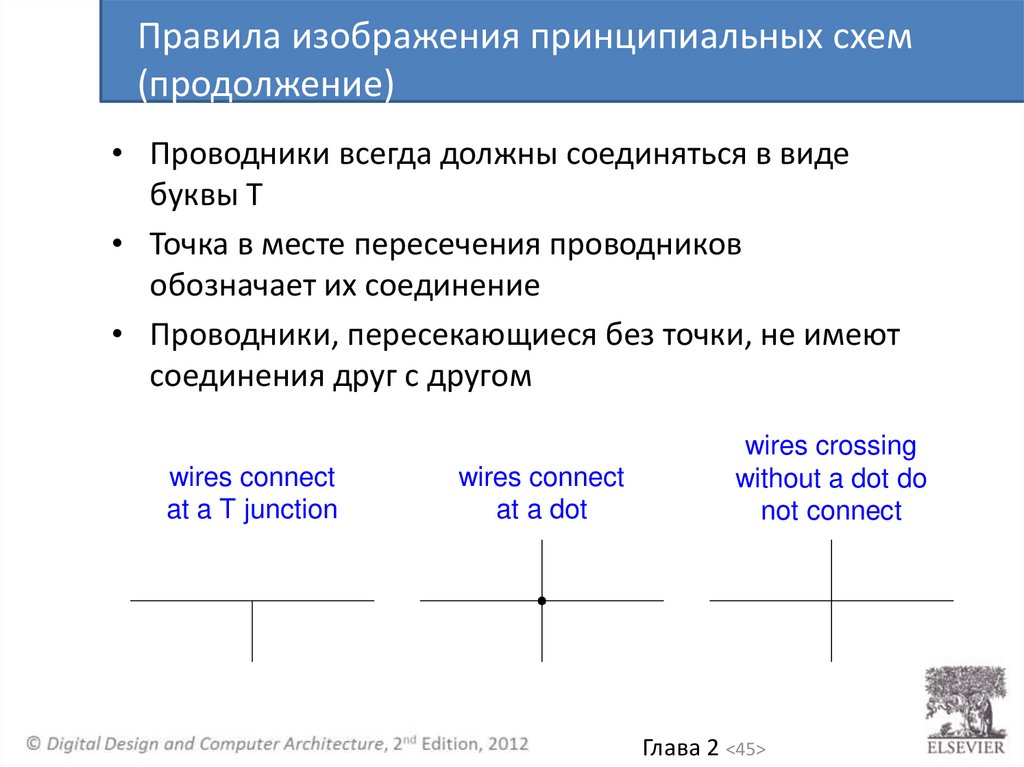

45.

Правила изображения принципиальных схем(продолжение)

• Проводники всегда должны соединяться в виде

буквы Т

• Точка в месте пересечения проводников

обозначает их соединение

• Проводники, пересекающиеся без точки, не имеют

соединения друг с другом

wires connect

at a T junction

wires connect

at a dot

wires crossing

without a dot do

not connect

Глава 2 <45>

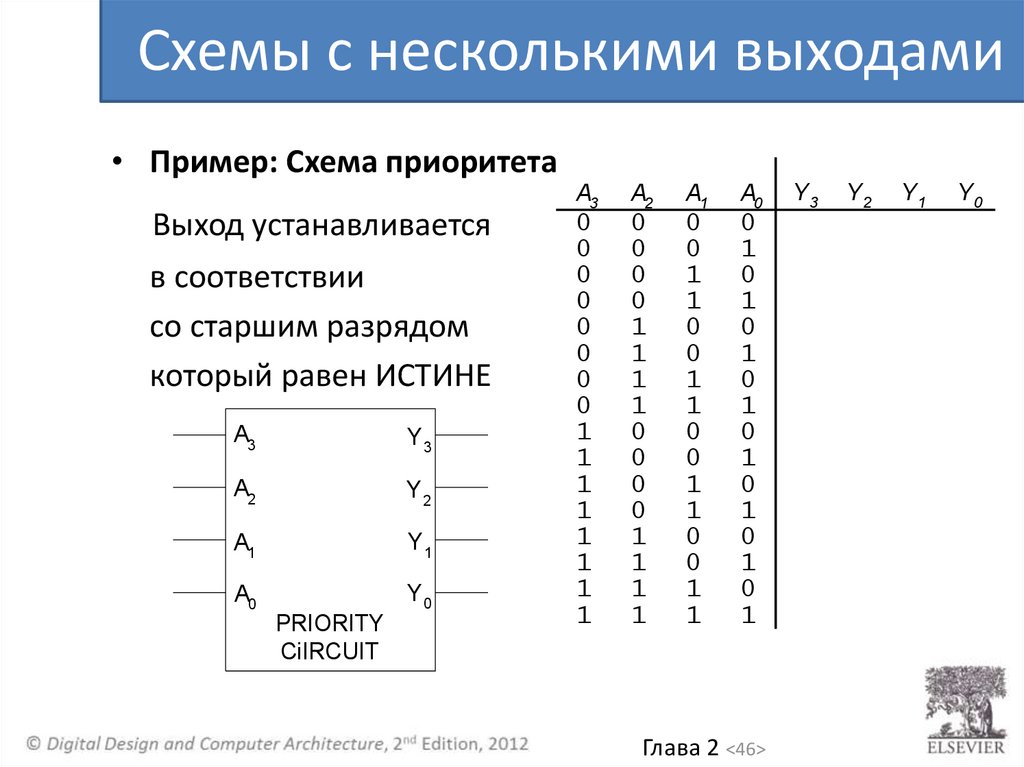

46.

Схемы с несколькими выходами• Пример: Схема приоритета

Выход устанавливается

в соответствии

со старшим разрядом

который равен ИСТИНЕ

A3

Y3

A2

Y2

A1

Y1

A0

Y0

PRIORITY

CiIRCUIT

A3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

A2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Глава 2 <46>

Y3

Y2

Y1

Y0

47.

Схемы с несколькими выходами• Пример: Схема приоритета

Выход устанавливается

в соответствии

со старшим входом

который равен ИСТИНЕ

A3

Y3

A2

Y2

A1

Y1

A0

Y0

PRIORITY

CiIRCUIT

A3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

A2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Глава 2 <47>

Y3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Y2

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

Y1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Y0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

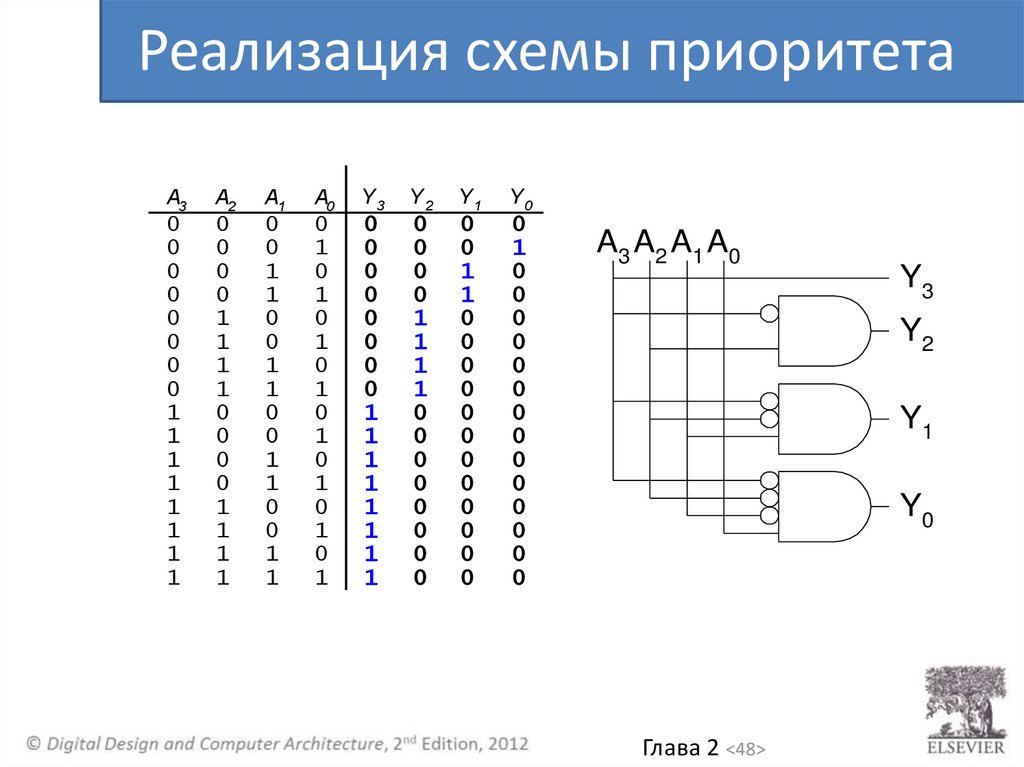

48.

Реализация схемы приоритетаA3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

A2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Y2

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

Y1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Y0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

A3 A 2 A1 A0

Y3

Y2

Y1

Y0

Глава 2 <48>

49.

Безразличное значениеA3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

A2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

A1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

A0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Y2

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

Y1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Y0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

A3

0

0

0

0

1

A2

0

0

0

1

X

A1

0

0

1

X

X

A0

0

1

X

X

X

Глава 2 <49>

Y3

0

0

0

0

1

Y2

0

0

0

1

0

Y1

0

0

1

0

0

Y0

0

1

0

0

0

50.

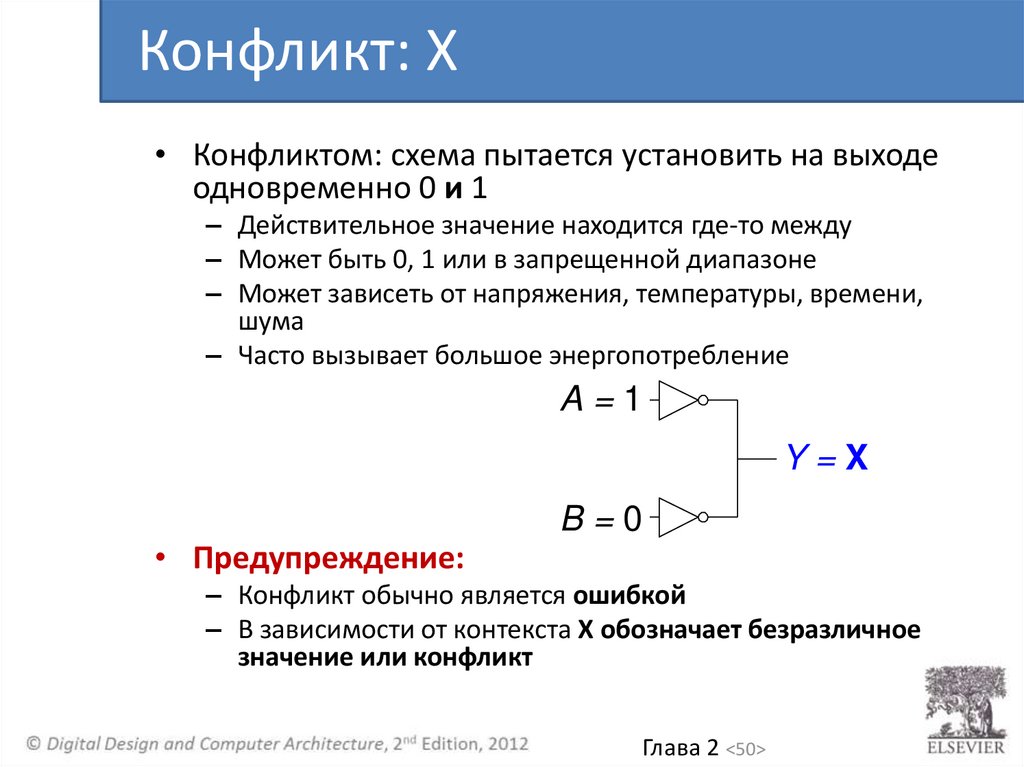

Конфликт: X• Конфликтом: схема пытается установить на выходе

одновременно 0 и 1

– Действительное значение находится где-то между

– Может быть 0, 1 или в запрещенной диапазоне

– Может зависеть от напряжения, температуры, времени,

шума

– Часто вызывает большое энергопотребление

A=1

Y=X

• Предупреждение:

B=0

– Конфликт обычно является ошибкой

– В зависимости от контекста X обозначает безразличное

значение или конфликт

Глава 2 <50>

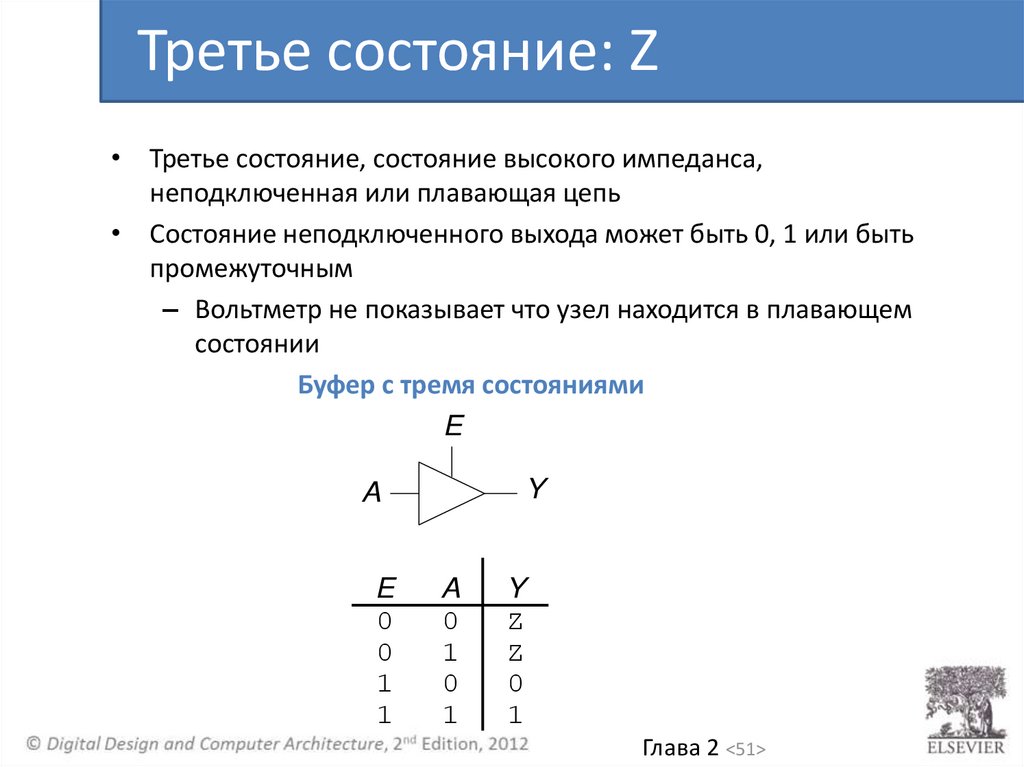

51.

Третье состояние: Z• Третье состояние, состояние высокого импеданса,

неподключенная или плавающая цепь

• Состояние неподключенного выхода может быть 0, 1 или быть

промежуточным

– Вольтметр не показывает что узел находится в плавающем

состоянии

Буфер с тремя состояниями

E

Y

A

E

0

0

1

1

A

0

1

0

1

Y

Z

Z

0

1

Глава 2 <51>

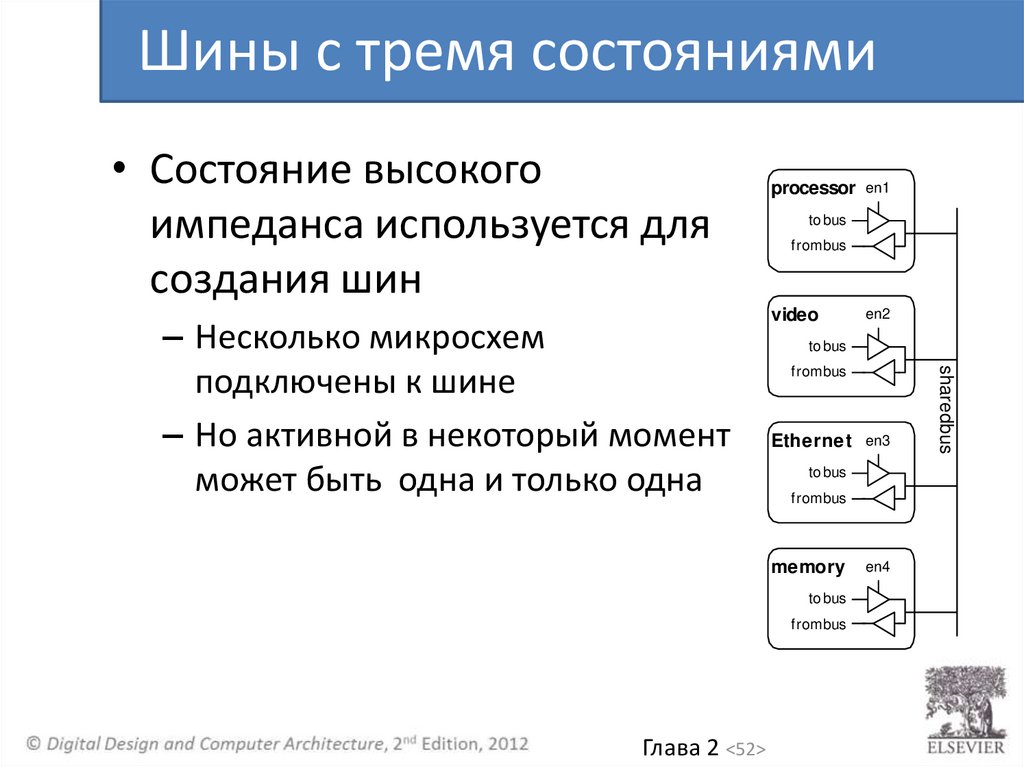

52.

Шины с тремя состояниями• Состояние высокого

импеданса используется для

создания шин

to bus

from bus

video

en2

to bus

from bus

Ethernet

en3

to bus

from bus

memory

to bus

from bus

Глава 2 <52>

en1

en4

sharedbus

– Несколько микросхем

подключены к шине

– Но активной в некоторый момент

может быть одна и только одна

processor

53.

Карты Карно• Булевы выражения можно упростить путем

комбинирования термов

• Карты Карно позволяют наглядно

минимизировать выражение

• PA + PA = P

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Y

1

1

0

0

0

0

0

0

Y

Y

AB

00

01

11

10

0

1

0

0

0

1

1

0

0

0

C

AB

C

00

01

11

10

0 ABC

ABC

ABC

ABC

1 ABC

ABC

ABC

ABC

Глава 2 <53>

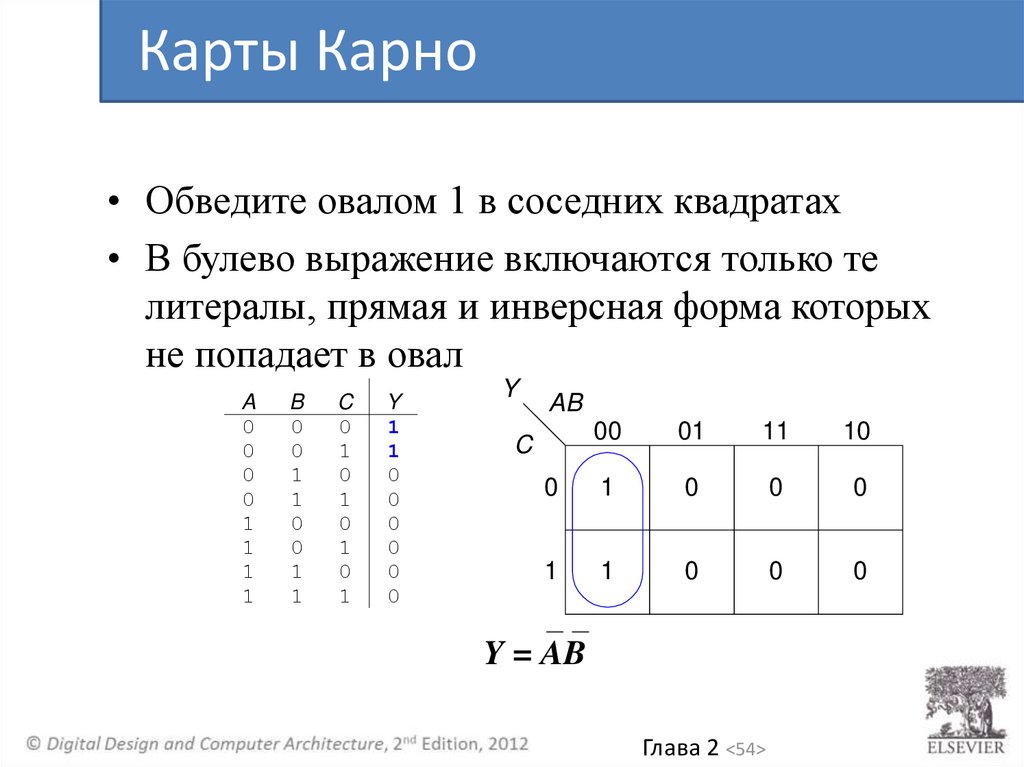

54.

Карты Карно• Обведите овалом 1 в соседних квадратах

• В булево выражение включаются только те

литералы, прямая и инверсная форма которых

не попадает в овал

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Y

1

1

0

0

0

0

0

0

Y

AB

00

01

11

10

0

1

0

0

0

1

1

0

0

0

C

Y = AB

Глава 2 <54>

55.

Карты Карно - три входаY

AB

01

11

10

0 ABC

ABC

ABC

ABC

1 ABC

ABC

ABC

ABC

C

00

Truth Table

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

K-Map

Y

0

0

1

1

0

0

0

1

Y

AB

C

00

01

11

0

1

Глава 2 <55>

10

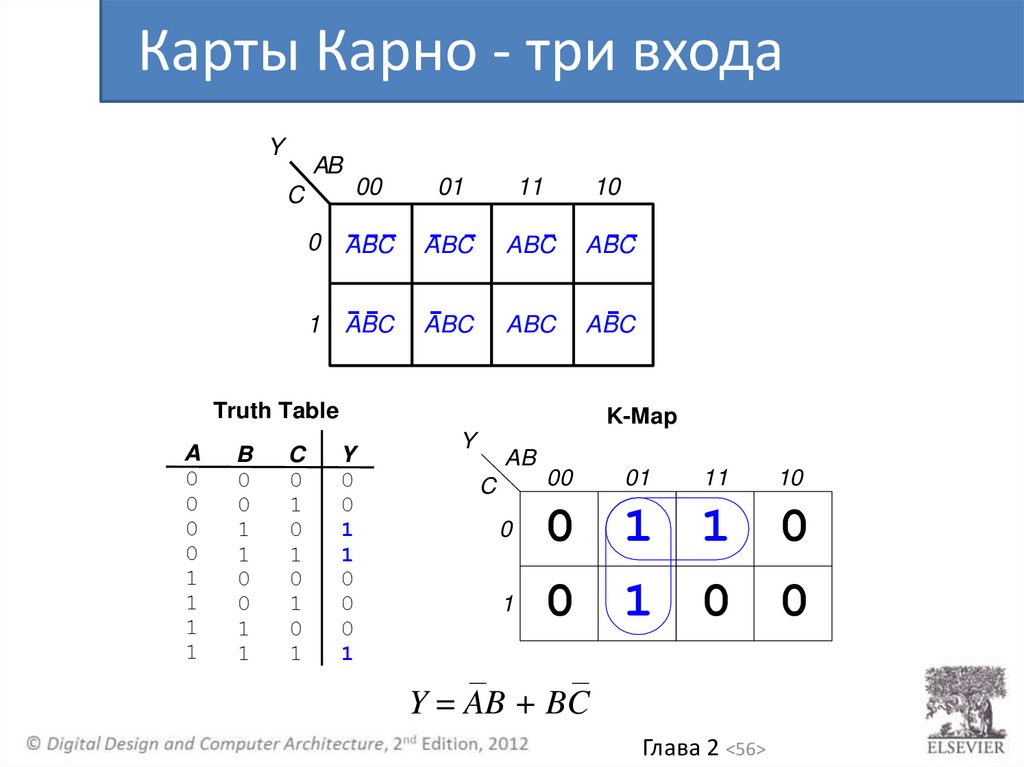

56.

Карты Карно - три входаY

AB

01

11

10

0 ABC

ABC

ABC

ABC

1 ABC

ABC

ABC

ABC

C

00

Truth Table

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

K-Map

Y

0

0

1

1

0

0

0

1

Y

AB

C

0

1

00

01

11

10

0 1 1 0

0 1 0 0

Y = AB + BC

Глава 2 <56>

57.

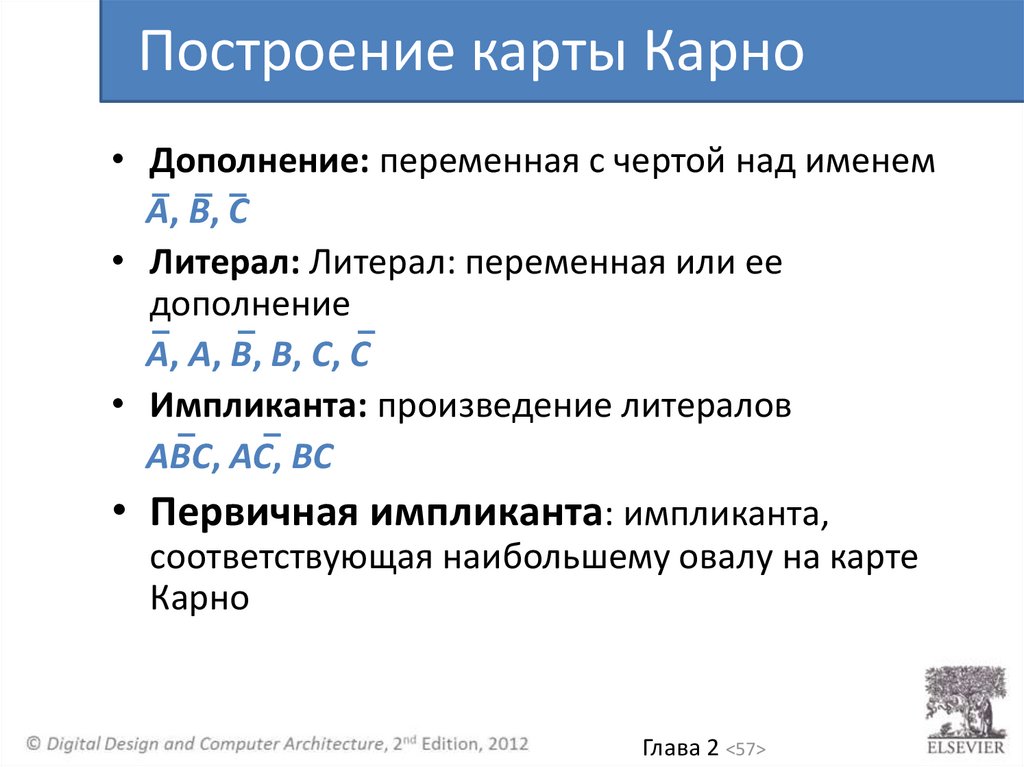

Построение карты Карно• Дополнение: переменная с чертой над именем

A, B, C

• Литерал: Литерал: переменная или ее

дополнение

A, A, B, B, C, C

• Импликанта: произведение литералов

ABC, AC, BC

• Первичная импликанта: импликанта,

соответствующая наибольшему овалу на карте

Карно

Глава 2 <57>

58.

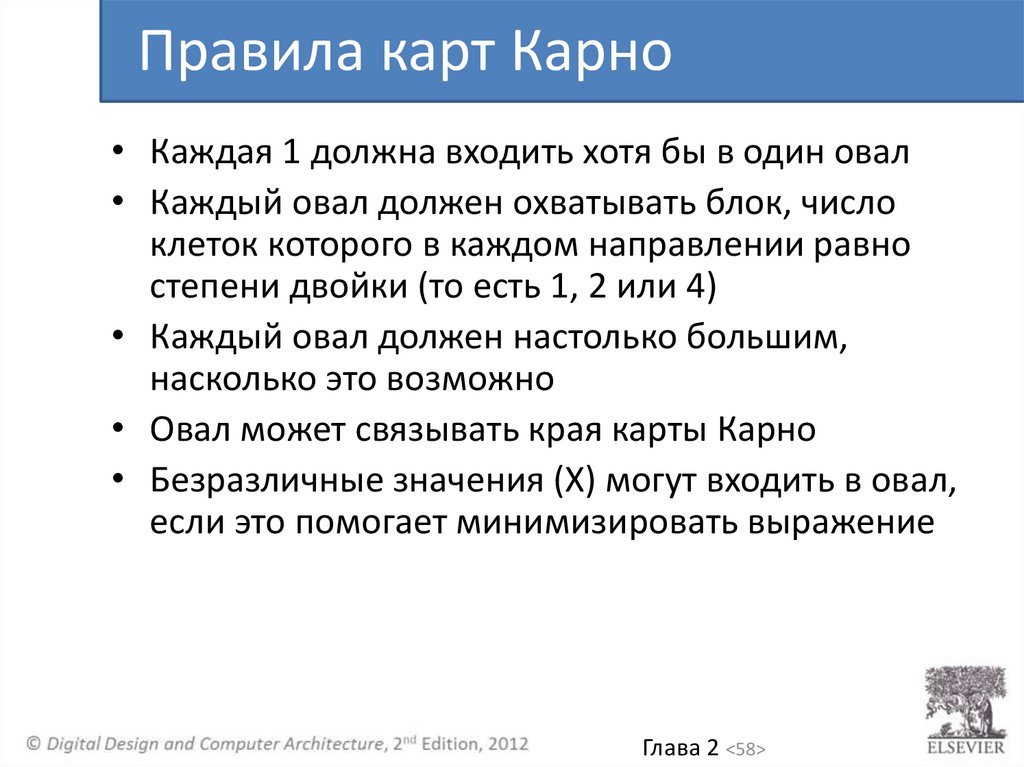

Правила карт Карно• Каждая 1 должна входить хотя бы в один овал

• Каждый овал должен охватывать блок, число

клеток которого в каждом направлении равно

степени двойки (то есть 1, 2 или 4)

• Каждый овал должен настолько большим,

насколько это возможно

• Овал может связывать края карты Карно

• Безразличные значения (X) могут входить в овал,

если это помогает минимизировать выражение

Глава 2 <58>

59.

Карты Карно - четыре входаA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

1

1

1

1

1

1

0

0

0

0

0

Y

CD

AB

00

01

11

00

01

11

10

Глава 2 <59>

10

60.

Карты Карно - четыре входаA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

1

1

1

1

1

1

0

0

0

0

0

Y

AB

00

01

11

10

00

1

0

0

1

01

0

1

0

1

11

1

1

0

0

10

1

1

0

1

CD

Глава 2 <60>

61.

Карты Карно - четыре входаA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

1

1

1

1

1

1

0

0

0

0

0

Y

AB

00

01

11

10

00

1

0

0

1

01

0

1

0

1

11

1

1

0

0

10

1

1

0

1

CD

Y = AC + ABD + ABC + BD

Глава 2 <61>

62.

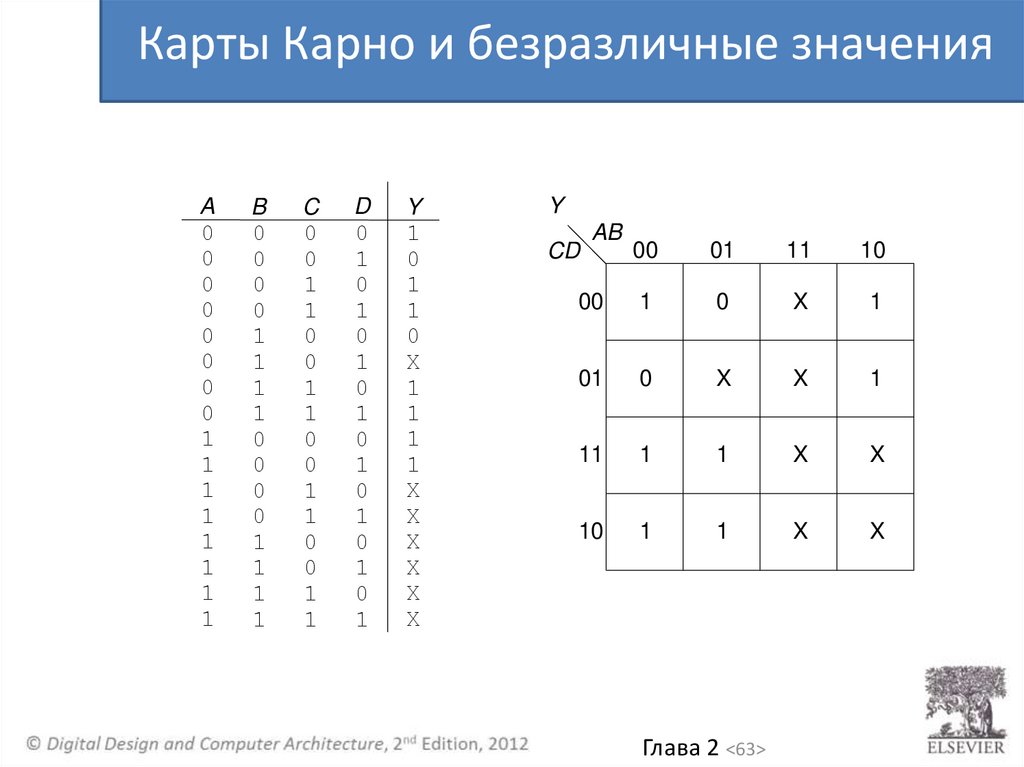

Карты Карно и безразличные значенияA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

X

1

1

1

1

X

X

X

X

X

X

Y

CD

AB

00

01

00

01

11

10

Глава 2 <62>

11

10

63.

Карты Карно и безразличные значенияA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

X

1

1

1

1

X

X

X

X

X

X

Y

AB

00

01

11

10

00

1

0

X

1

01

0

X

X

1

11

1

1

X

X

10

1

1

X

X

CD

Глава 2 <63>

64.

Карты Карно и безразличные значенияA

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Y

1

0

1

1

0

X

1

1

1

1

X

X

X

X

X

X

Y

AB

00

01

11

10

00

1

0

X

1

01

0

X

X

1

11

1

1

X

X

10

1

1

X

X

CD

Y = A + BD + C

Глава 2 <64>

65.

Базовые комбинационные блоки• Мультиплексоры

• Дешифраторы

Глава 2 <65>

66.

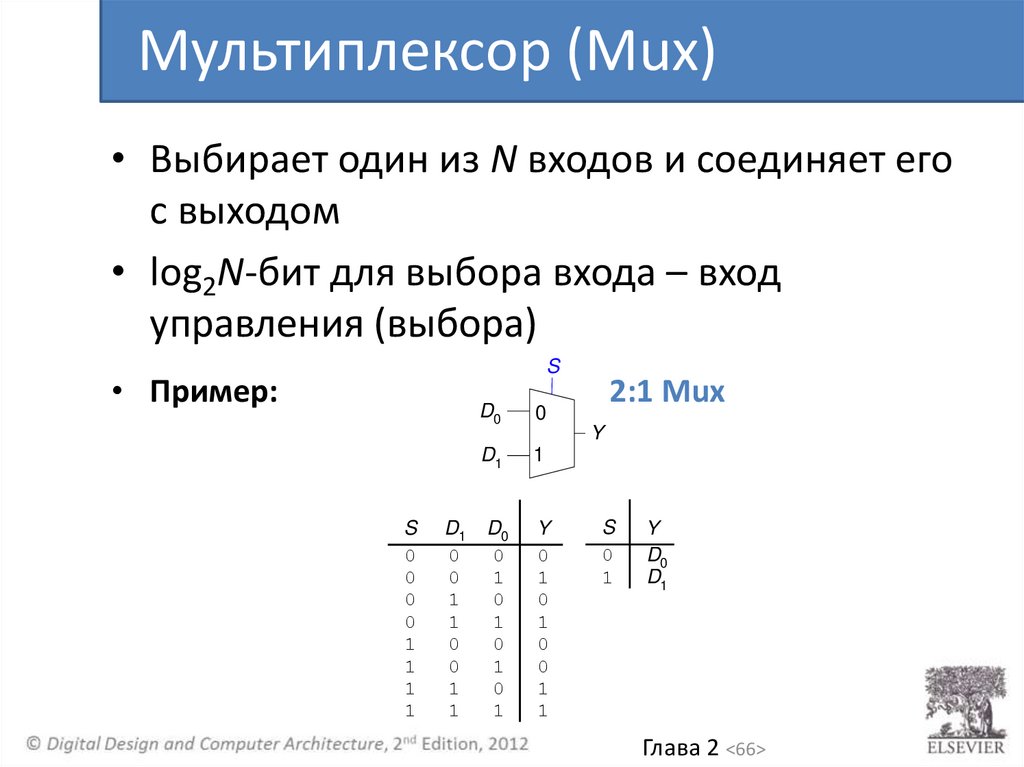

Мультиплексор (Mux)• Выбирает один из N входов и соединяет его

с выходом

• log2N-бит для выбора входа – вход

управления (выбора)

S

• Пример:

S

0

0

0

0

1

1

1

1

D1

0

0

1

1

0

0

1

1

D0

0

D1

1

D0

0

1

0

1

0

1

0

1

2:1 Mux

Y

Y

0

1

0

1

0

0

1

1

S

0

1

Y

D0

D1

Глава 2 <66>

67.

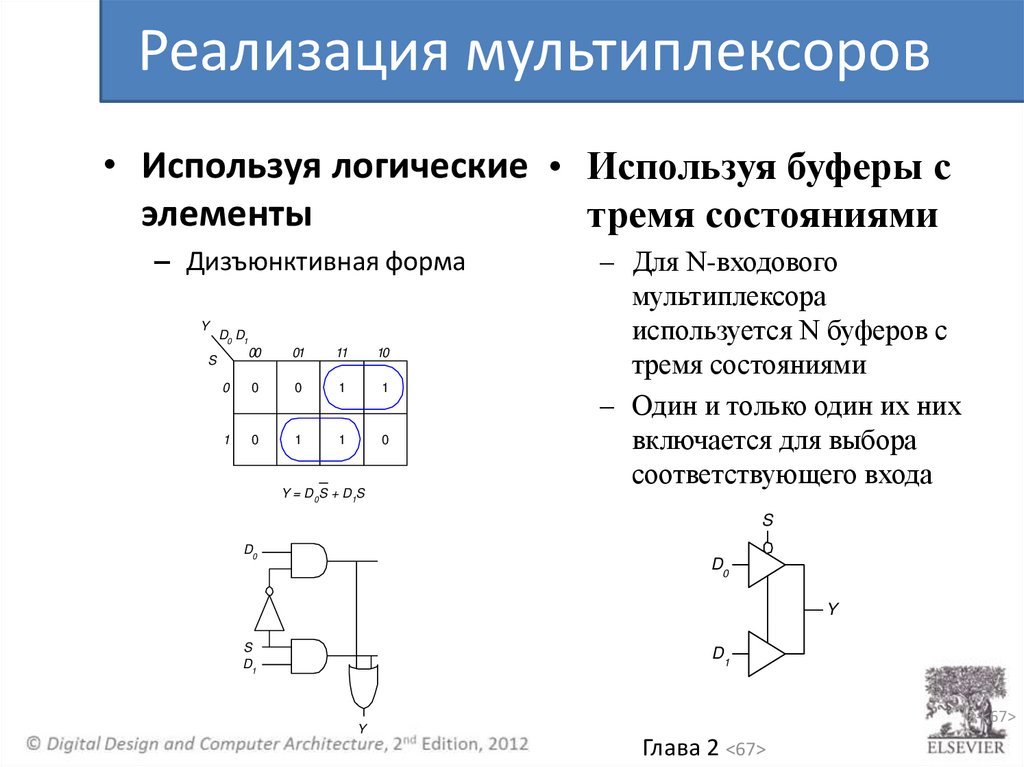

Реализация мультиплексоров• Используя логические • Используя буферы с

элементы

тремя состояниями

– Дизъюнктивная форма

Y

S

D0 D1

00

01

11

10

0

0

0

1

1

1

0

1

1

0

Y = D 0S + D1S

– Для N-входового

мультиплексора

используется N буферов с

тремя состояниями

– Один и только один их них

включается для выбора

соответствующего входа

S

D0

D0

Y

S

D1

D1

Y

2-<67>

Глава 2 <67>

68.

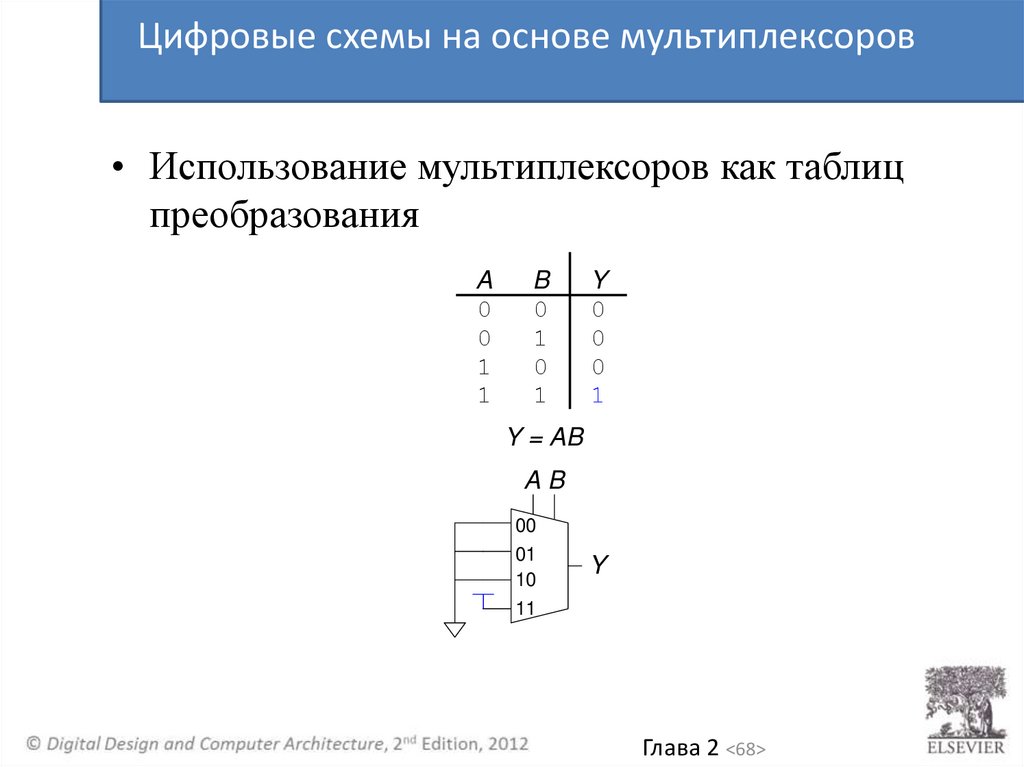

Цифровые схемы на основе мультиплексоров• Использование мультиплексоров как таблиц

преобразования

A

0

0

1

1

B

0

1

0

1

Y

0

0

0

1

Y = AB

AB

00

01

10

Y

11

Глава 2 <68>

69.

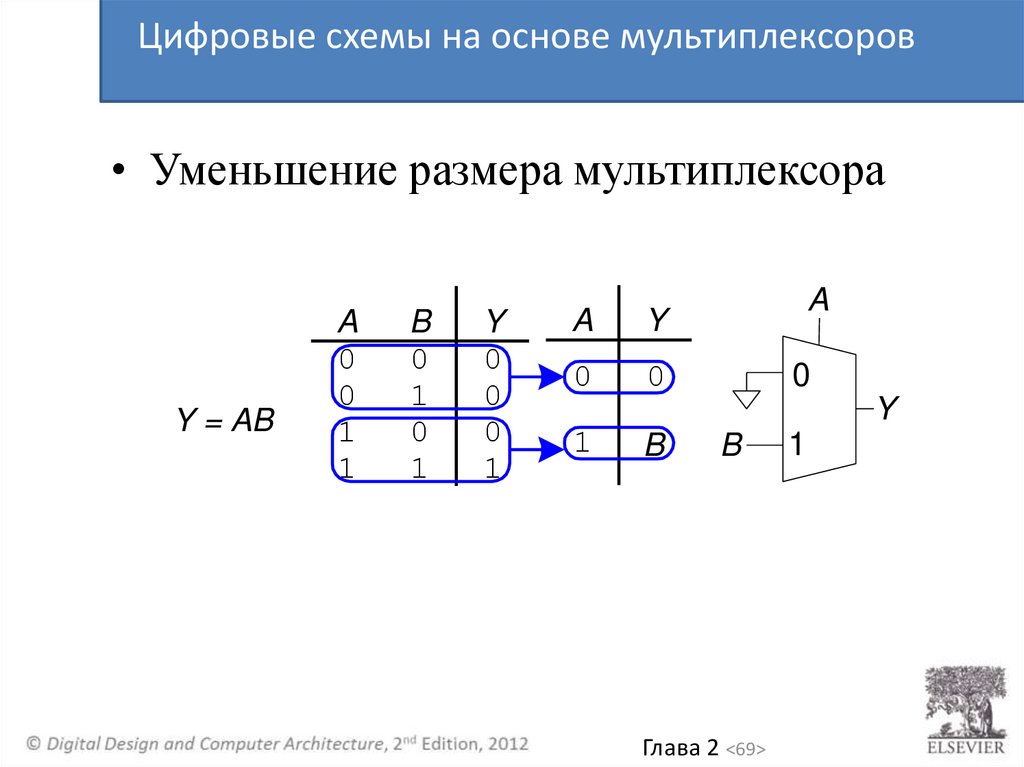

Цифровые схемы на основе мультиплексоров• Уменьшение размера мультиплексора

Y = AB

A

0

0

1

1

B

0

1

0

1

Y

0

0

0

1

A

Y

0

0

1

A

0

Y

B

B

Глава 2 <69>

1

70.

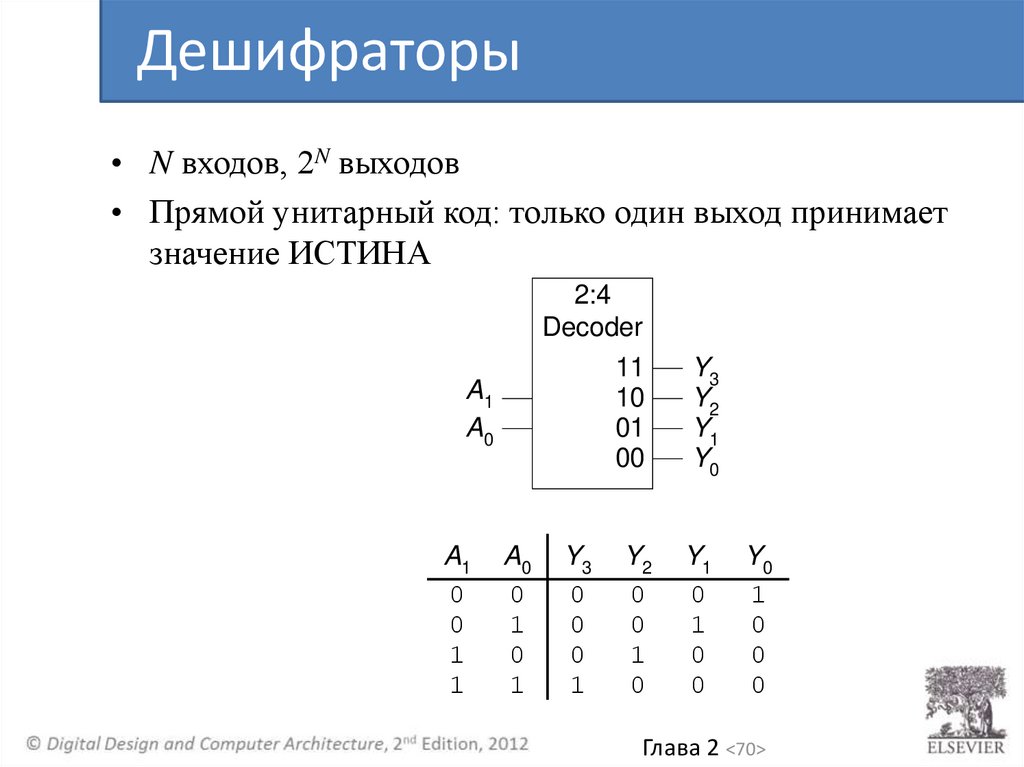

Дешифраторы• N входов, 2N выходов

• Прямой унитарный код: только один выход принимает

значение ИСТИНА

2:4

Decoder

A1

A0

A1

0

0

1

1

A0

0

1

0

1

Y3

0

0

0

1

11

10

01

00

Y3

Y2

Y1

Y0

Y2

0

0

1

0

Y1

0

1

0

0

Y0

1

0

0

0

Глава 2 <70>

71.

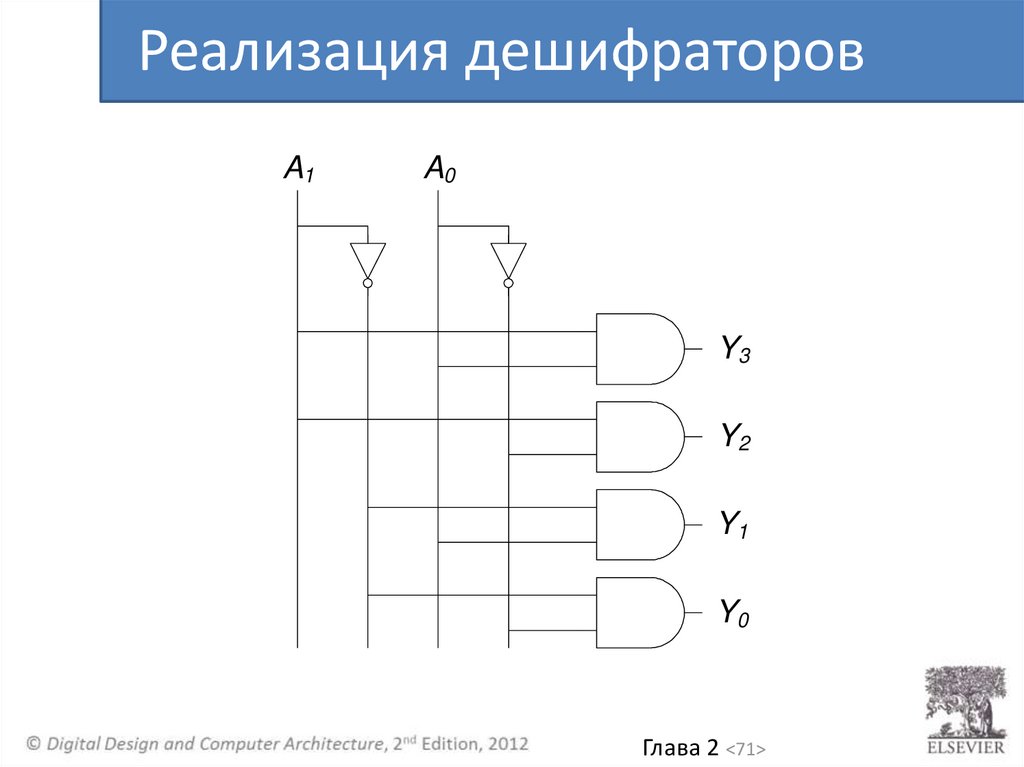

Реализация дешифраторовA1

A0

Y3

Y2

Y1

Y0

Глава 2 <71>

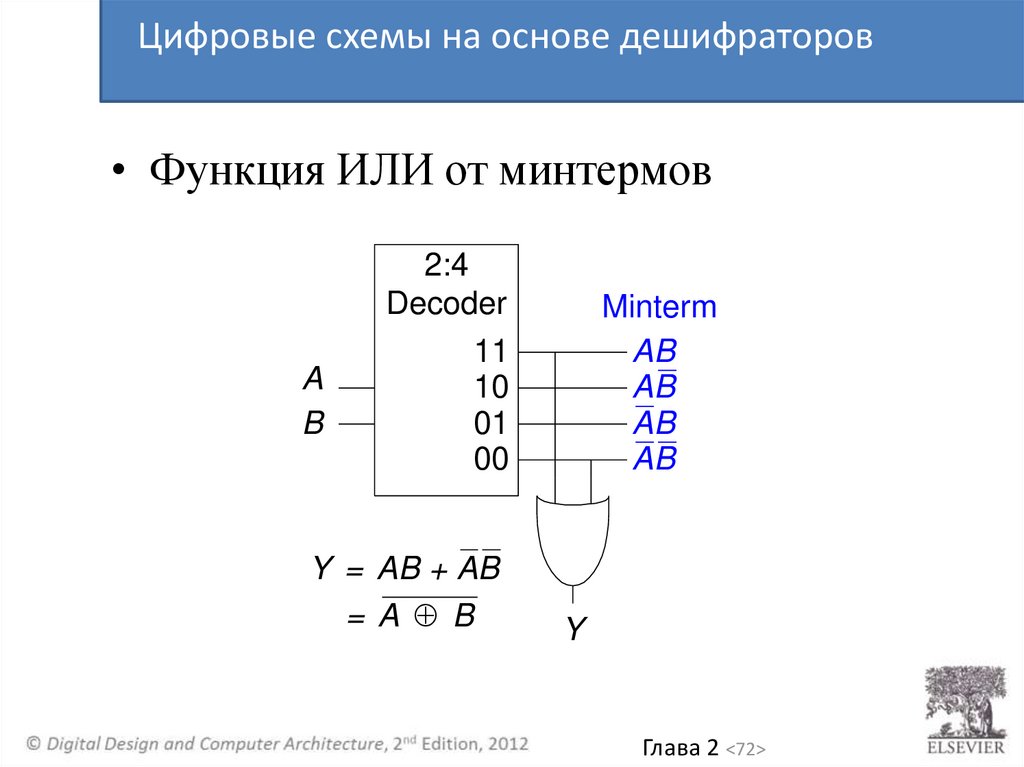

72.

Цифровые схемы на основе дешифраторов• Функция ИЛИ от минтермов

A

B

2:4

Decoder

11

10

01

00

Y = AB + AB

= A B

Minterm

AB

AB

AB

AB

Y

Глава 2 <72>

73.

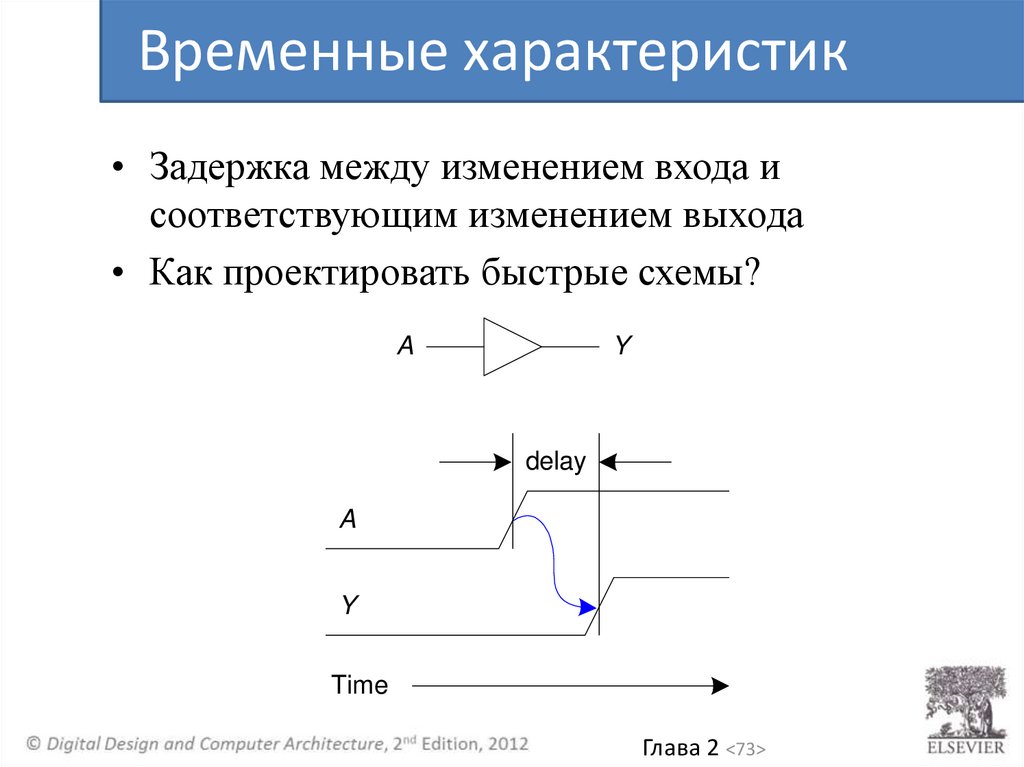

Временные характеристик• Задержка между изменением входа и

соответствующим изменением выхода

• Как проектировать быстрые схемы?

Y

A

delay

A

Y

Time

Глава 2 <73>

74.

Задержки распространения и реакции• Задержка распространения tpd = максимальная

задержка тракта вход-выход

• Задержка реакции tcd = минимальная задержка тракта

вход-выход

A

Y

tpd

A

Y

tcd

Time

Глава 2 <74>

75.

Задержки распространения и реакции• Задержки обусловлены

– Емкостями и сопротивлениями в цепях

– Конечностью скорости света

• Причины, по которым tpd и tcd могут различаться

– Разные задержки нарастания и спада сигнала

– Несколько входов и выходов, одни из которых

быстрее, чем другие

– Замедление работы схемы при повышении

температуры и ускорение при охлаждении

Глава 2 <75>

76.

Критический (длинный) и кратчайший путиCritical Path

A

B

n1

n2

C

Y

D

Short Path

Критический (длинный) путь tpd = 2tpd_AND + tpd_OR

Кратчайший путь tcd = tcd_AND

Глава 2 <76>

77.

Импульсные помехи• Одиночное изменение на входного сигнала

вызывает несколько изменений сигнала на

выходе

Глава 2 <77>

78.

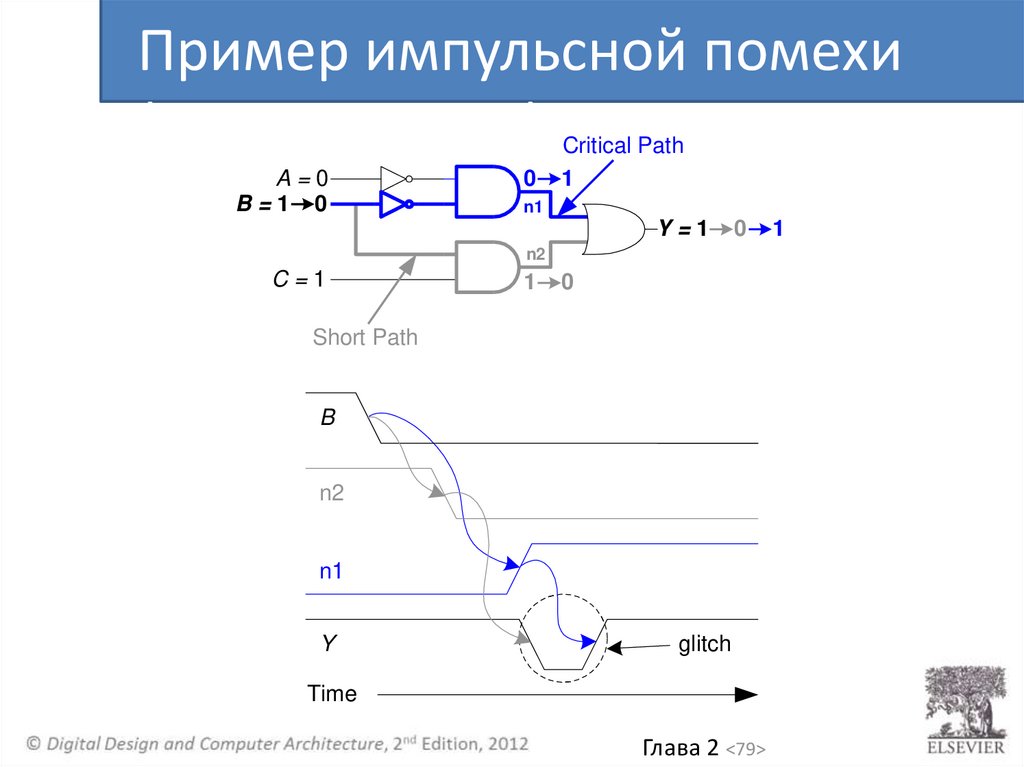

Пример импульсной помехи• Что происходит когда A = 0, C = 1, а B

изменяется с 1 до 0?

A

B

Y

C

Y

AB

00

01

11

10

0

1

0

0

0

1

1

1

1

0

C

Y = AB + BC

Глава 2 <78>

79.

Пример импульсной помехи(продолжение)

A=0

B=1 0

0

Critical Path

1

n1

Y=1

0

n2

C=1

1

0

Short Path

B

n2

n1

Y

glitch

Time

Глава 2 <79>

1

80.

Борьба с импульсными помехамиY

AB

00

01

11

10

0

1

0

0

0

1

1

1

1

0

C

AC

Y = AB + BC + AC

A=0

B=1 0

Y=1

C=1

Глава 2 <80>

81.

Почему импульсные помехи важны?• Импульсные помехи не являются серьезной

проблемой при проектировании синхронных

схем (глава 3)

• Важно уметь распознавать их при

моделировании или на экране осциллографа

• От всех импульсных помех невозможно

избавиться - одновременные изменения

нескольких входов могут привести к

появлению таких помех

Глава 2 <81>

Математика

Математика Базы данных

Базы данных