Похожие презентации:

Вычислительные системы, сети и телекоммуникации

1. Вычислительные системы, сети и телекоммуникации

Микропроцессор2.

Микропроцессор3.

Функции микропроцессора• Вычисление адресов команд и данных

• Выборка из памяти и дешифрация команд

• Переход к следующей команде

• Выборка данных из ОП, МПП, и регистров внешних

устройств

• Запись данных в ОП, МПП и регистры внешних устройств

• Обработка данных

• Обработка прерываний

• Выработка управляющих сигналов для всех прочих узлов ПК

4.

Характеристики микропроцессора• Разрядность шины данных

количество разрядов, над которыми одновременно могут

выполняться операции

• Разрядность шины адреса

определяет адресное пространство

– Адресное пространство

максимальное количество ячеек памяти, которое может быть

непосредственно адресовано микропроцессором

• Рабочая тактовая частота

определяет внутреннее быстродействие микропроцессора

• Система команд

набор команд, которые может выполнять микропроцессор

5.

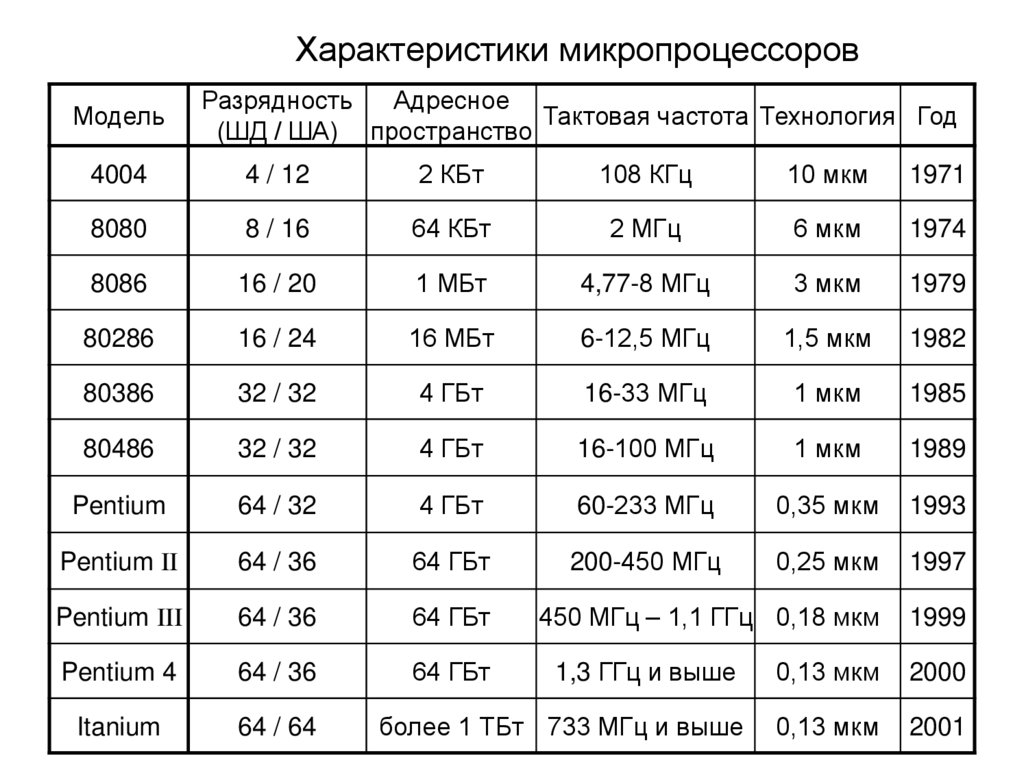

Характеристики микропроцессоровМодель

Разрядность

Адресное

Тактовая частота Технология Год

(ШД / ША) пространство

4004

4 / 12

2 КБт

108 КГц

10 мкм

1971

8080

8 / 16

64 КБт

2 МГц

6 мкм

1974

8086

16 / 20

1 МБт

4,77-8 МГц

3 мкм

1979

80286

16 / 24

16 МБт

6-12,5 МГц

1,5 мкм

1982

80386

32 / 32

4 ГБт

16-33 МГц

1 мкм

1985

80486

32 / 32

4 ГБт

16-100 МГц

1 мкм

1989

Pentium

64 / 32

4 ГБт

60-233 МГц

0,35 мкм

1993

Pentium II

64 / 36

64 ГБт

200-450 МГц

0,25 мкм

1997

Pentium III

64 / 36

64 ГБт

450 МГц – 1,1 ГГц 0,18 мкм

1999

Pentium 4

64 / 36

64 ГБт

1,3 ГГц и выше

0,13 мкм

2000

Itanium

64 / 64

более 1 ТБт 733 МГц и выше

0,13 мкм

2001

6.

Правило (закон) Мура«Число транзисторов на единицу площади будет удваиваться каждый год» (1965)

Число транзисторов

Pentium 4

Pentium III

Pentium II

Pentium

100 000 000

10 000 000

80486

1 000 000

80386

80286

100 000

8086

8080

10 000

4004

1 000

1970

1975

1980

1985

1990

1995

2000

7.

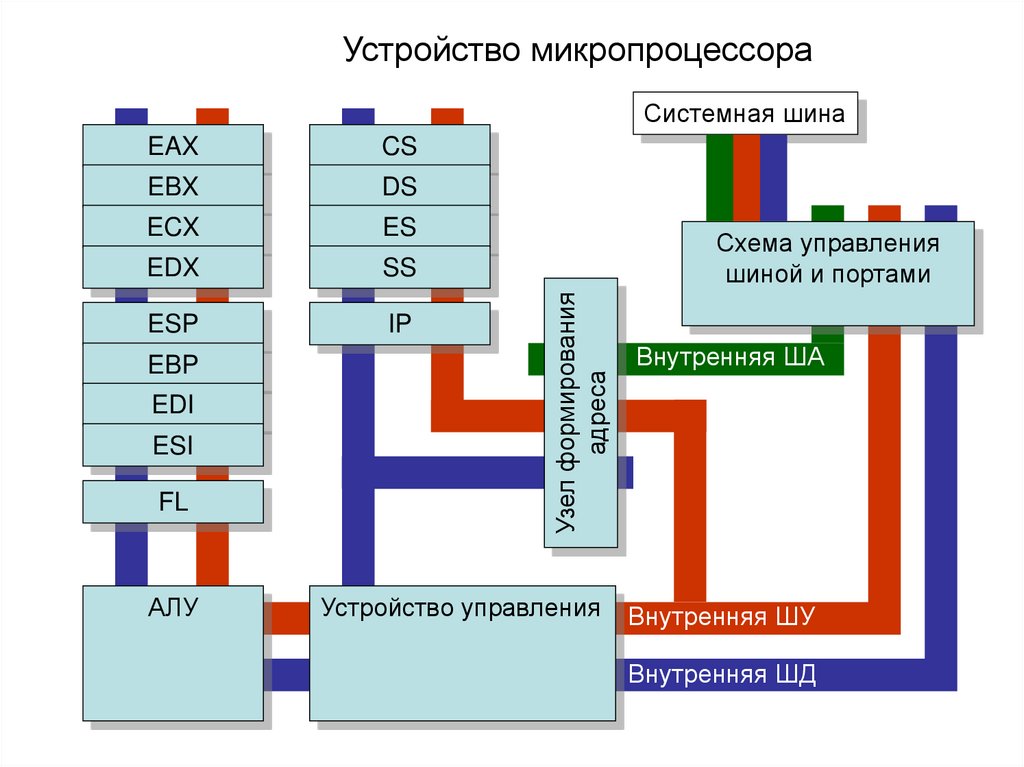

Устройство микропроцессораСистемная шина

CS

EBX

DS

ECX

ES

EDX

SS

ESP

IP

EBP

EDI

ESI

FL

АЛУ

Схема управления

шиной и портами

Узел формирования

адреса

EAX

Устройство управления

Внутренняя ША

Внутренняя ШУ

Внутренняя ШД

8.

Регистры общего назначенияКаждый из регистров общего назначения может

использоваться для временного хранения любых данных.

3130 2928 27262524232221 2019 18 17 1615141312 11 10 9 8 7 6 5 4 3 2 1 0

AH

AL

AX

EAX

• В 32-битном регистре EAX можно выделить 16-битную

часть AX и две 8-битные части AH и AL

• EBX содержит BX, BH и BL

• ECX содержит CX, CH и CL

• EDX содержит DX, DH и DL

9.

Регистры сегментов и смещенийCS хранит начальный адрес кода программы

DS хранит начальный адрес данных

ES хранит начальный адрес дополнительного блока данных

SS хранит начальный адрес стековой области памяти

IP хранит смещение адреса очередной команды программы

ESP хранит смещение вершины (текущего адреса) стека

EBP - смещение адреса локальных данных (хранятся в стеке)

ESI и EDI хранят, соответственно, смещение адреса

источника и приемника данных при строковых операциях

Регистры EBP, ESI, EDI могут использоваться как регистры

общего назначения

10.

Регистр флаговРегистр флагов

DF IF TF OF SF ZF AF PF CF

CF – флаг переноса при арифметических операциях и сдвигах

PF – флаг четности количества единичных битах результата

AF –логический переноса в двоично-десятичной арифметике

ZF – флаг нуля, то есть равенство нулю результата

SF – флаг знака результата арифметических операций

OF – флаг переполнения при арифметических операциях

TF – флаг трассировки (пошагового режима) процессора

IF – флаг разрешения прерываний (флаг прерываний)

DF – флаг направления при строковых операциях

11.

Вычисление адреса ячейки памятиCS

DS

ES

ESP

EBP

EDI

ESI

SS

Узел формирования

адреса

IP

Устройство управления

Вычисление адреса

команды

Устройство управления

подает сигнал на

внутреннюю шину

управления для

выборки значений

регистров CS и IP.

16 * CS + IP

Значения из CS и

IP передаются

узлу формирования

адреса,

где они преобразуются

в адрес ячейки памяти.

12.

Вычисление адреса ячейки памятиCS

DS

ES

ESP

EBP

EDI

ESI

SS

Узел формирования

адреса

IP

Устройство управления

Вычисление адреса

позиции в стеке

Устройство управления

подает сигнал на

внутреннюю шину

управления для

выборки значений

регистров SS и ESP.

16 * SS + ESP

Значения из SS и

ESP передаются

узлу формирования

адреса,

где они преобразуются

в адрес ячейки памяти.

13.

Работа устройства управленияПЗУ

do! микропрограмм

Схема управления

шиной и портами

Из основной памяти команда

считывается в регистр команд.

IP

По коду команды дешифратор

выбирает соответствующую

Устройство управления микропрограмму в ПЗУ.

Микропрограмма выполняется.

Схемы вычисления

Затем в устройстве управления

адреса следующей

вычисляется адрес следующей

команды

команды,который записывается

в регистр IP.

После этого процесс повторяется.

Дешифратор

Регистр команд

команд

Основная

память

14.

Машинный циклIP

Устройство управления

Схемы вычисления

адреса следующей

команды

Дешифратор

команд

ПЗУ

микропрограмм

Схема управления

шиной и портами

Регистр команд

Основная

память

15.

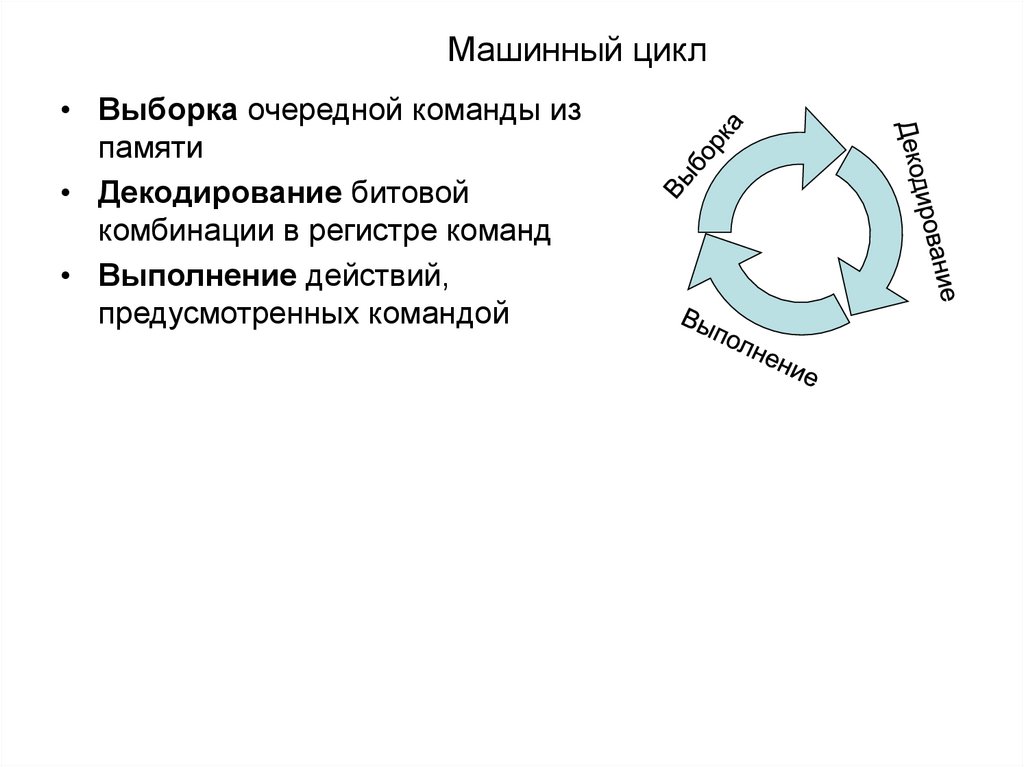

Машинный цикл• Выборка очередной команды из

памяти

• Декодирование битовой

комбинации в регистре команд

• Выполнение действий,

предусмотренных командой

Программирование

Программирование