Похожие презентации:

Архитектура вычислительных систем и компьютерных сетей

1.

Архитектуравычислительных систем и

компьютерных сетей

Специальность

«Математическое обеспечение и администрирование

информационных систем»

2 курс, 3 семестр

51 час лекций

экзамен

2.

Ссылка для удалённыхзанятий:

https://discord.gg/ycDaUt3

Ссылка на список вопросов

и тем рефератов

https://disk.yandex.ru/d/TtzX_kRKaN17hQ

04.09.2024

Тема 6.Классификация

архитектур

2

3.

Литература:• Майерс Г. Архитектура ЭВМ (в 2 т.). М.

Мир, 1989.

• Таненбаум Э. Архитектура компьютера.

СПб., Питер, 2002.

• Олифер В.Г., Олифер Н.А.

Компьютерные сети. СПб., Питер, 2001.

• Степанов А.Н. Архитектура

вычислительных систем и

компьютерных сетей, Питер, 2007

04.09.2024

Тема 6.Классификация

архитектур

3

4.

Архитектура компьютера представляет собойсовокупность сведений об основных устройствах

компьютера и их назначении, о способах

представления программ и данных в компьютере, об

особенностях его организации и функционирования.

04.09.2024

Тема 6.Классификация

архитектур

4

5.

Тема 1. Основные устройства компьютера и ихтехнические характеристики

В состав любого современного компьютера входят:

память — группа устройств, которые обеспечивают хранение

программ и данных;

процессор — одно или несколько устройств, которые

обеспечивают задаваемую программой обработку данных;

устройства ввода/вывода — группа устройств, которые

обеспечивают обмен, то есть прием и передачу данных между

пользователем и машиной или между двумя или более

машинами.

04.09.2024

Тема 6.Классификация

архитектур

5

6.

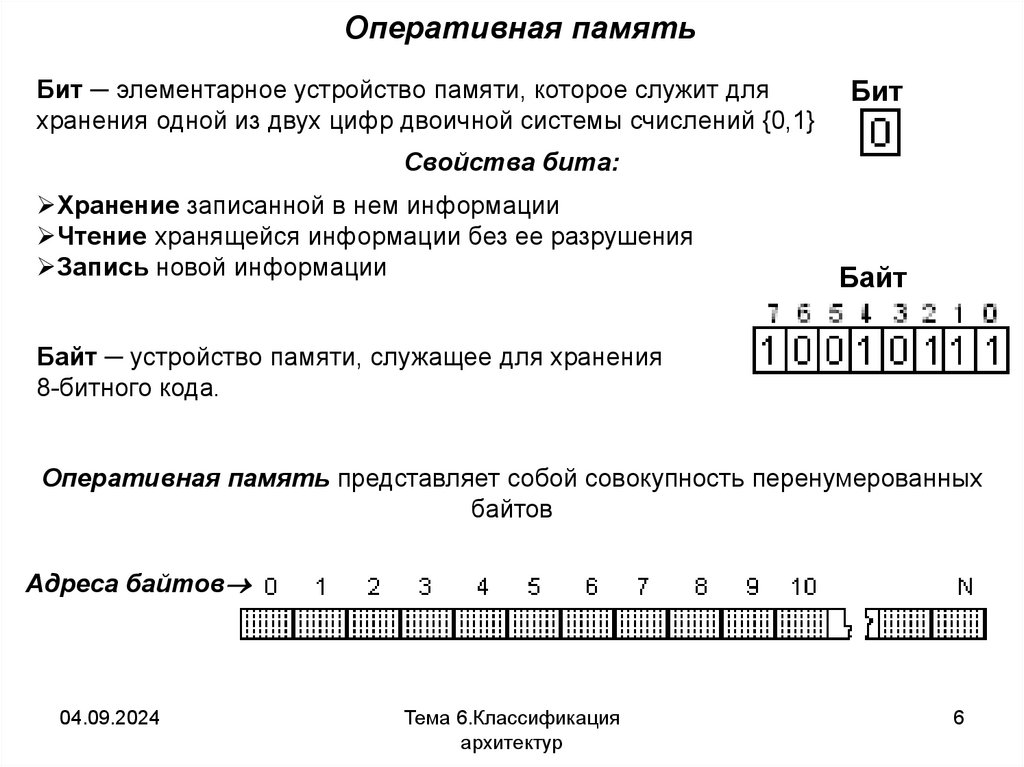

Оперативная памятьБит ─ элементарное устройство памяти, которое служит для

хранения одной из двух цифр двоичной системы счислений {0,1}

Бит

Свойства бита:

Хранение записанной в нем информации

Чтение хранящейся информации без ее разрушения

Запись новой информации

Байт

Байт ─ устройство памяти, служащее для хранения

8-битного кода.

Оперативная память представляет собой совокупность перенумерованных

байтов

Адреса байтов

04.09.2024

Тема 6.Классификация

архитектур

6

7.

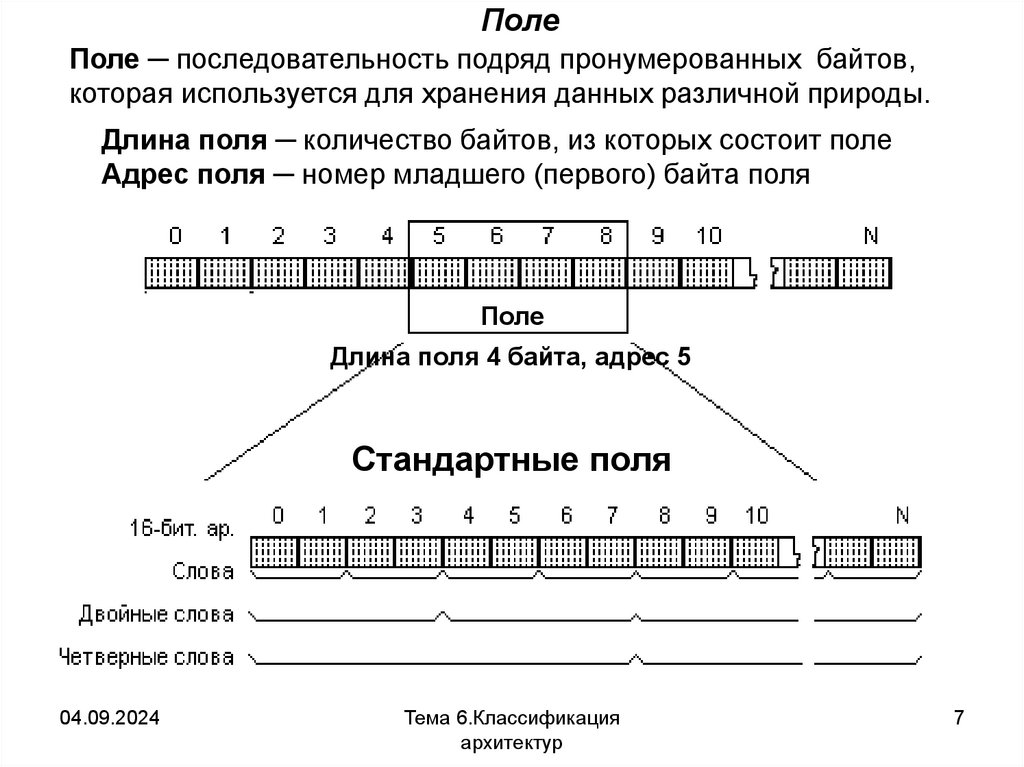

ПолеПоле ─ последовательность подряд пронумерованных байтов,

которая используется для хранения данных различной природы.

Длина поля ─ количество байтов, из которых состоит поле

Адрес поля ─ номер младшего (первого) байта поля

Поле

Длина поля 4 байта, адрес 5

Стандартные поля

04.09.2024

Тема 6.Классификация

архитектур

7

8.

ПроцессорСистемой команд процессора называется набор элементарных действий,

которые могут быть выполнены процессором (сложить, умножить, сравнить

два числа и т.д.). Система команд процессора определяется его моделью.

Машинная команда ─ указание на выполнение отдельного элементарного

действия, принадлежащего системе команд процессора

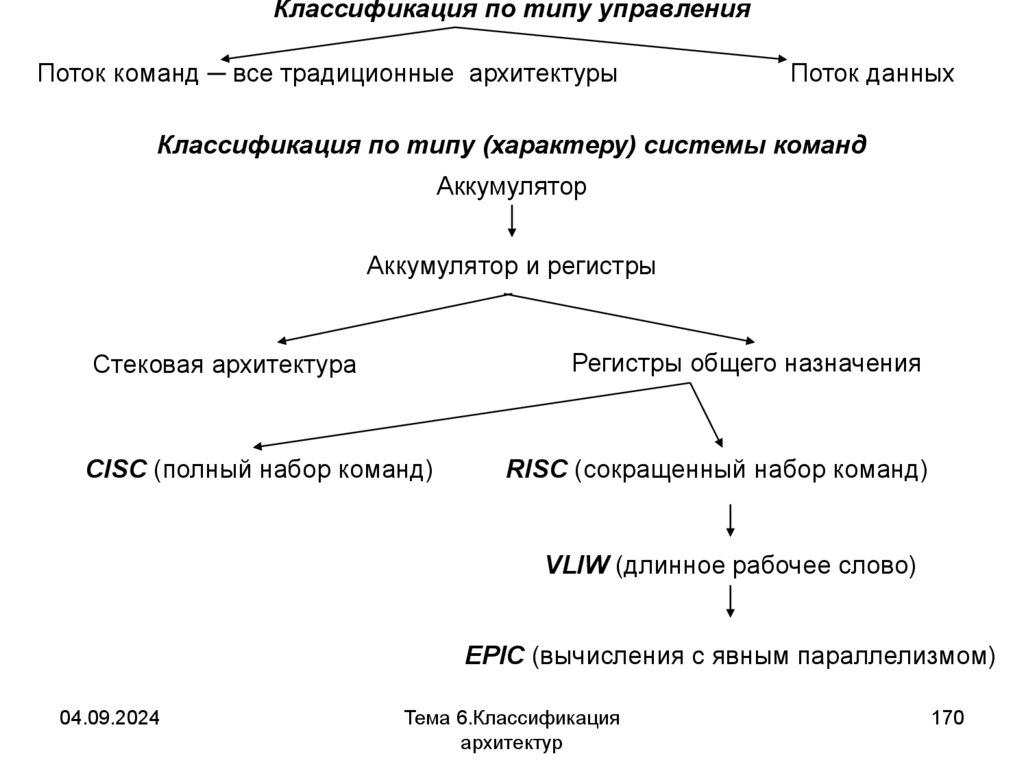

Классификация архитектур по типу машинных команд:

CISC ─ Complete Instruction Set Computer (Code)

RISC ─ Reduced Instruction Set Computer (Code)

VLIW ─ Very Large Instruction Wоrd

Конкретная последовательность машинных команд, которая обеспечивает

необходимую пользователю обработку данных, называется программой.

04.09.2024

Тема 6.Классификация

архитектур

8

9.

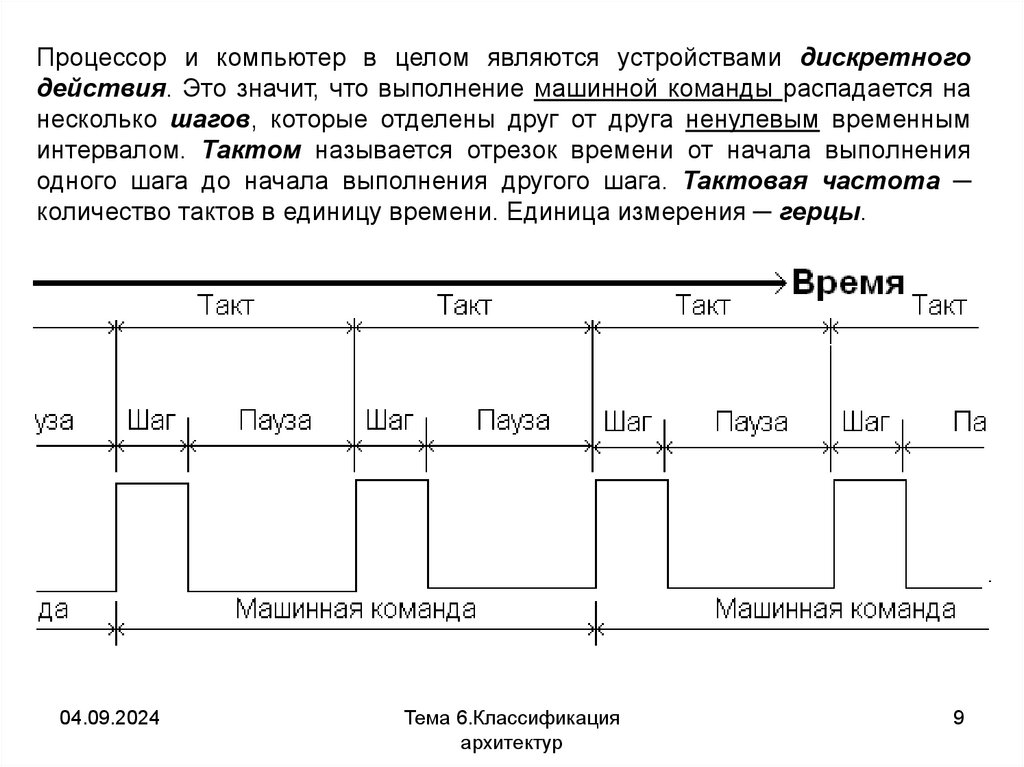

Процессор и компьютер в целом являются устройствами дискретногодействия. Это значит, что выполнение машинной команды распадается на

несколько шагов, которые отделены друг от друга ненулевым временным

интервалом. Тактом называется отрезок времени от начала выполнения

одного шага до начала выполнения другого шага. Тактовая частота ─

количество тактов в единицу времени. Единица измерения ─ герцы.

04.09.2024

Тема 6.Классификация

архитектур

9

10.

Машинное слово — максимальное количество байтов памяти, котороеможет быть обработано процессором за один такт.

Комплекс, состоящий из пучка проводов, по каждому из которых передается

один бит данных, и электронных схем, которые обеспечивают правильную

передачу информации внутри компьютера, называется шиной. Количество

проводов в шине называется разрядностью шины.

Участок шины, который используется для передачи данных, называется

шиной данных, участок шины, который используется для передачи адреса

поля оперативной памяти, называется адресной шиной.

Разрядность адресной шины определяет максимально возможный объём

оперативной памяти, который принято называть адресным пространством.

04.09.2024

Тема 6.Классификация

архитектур

10

11.

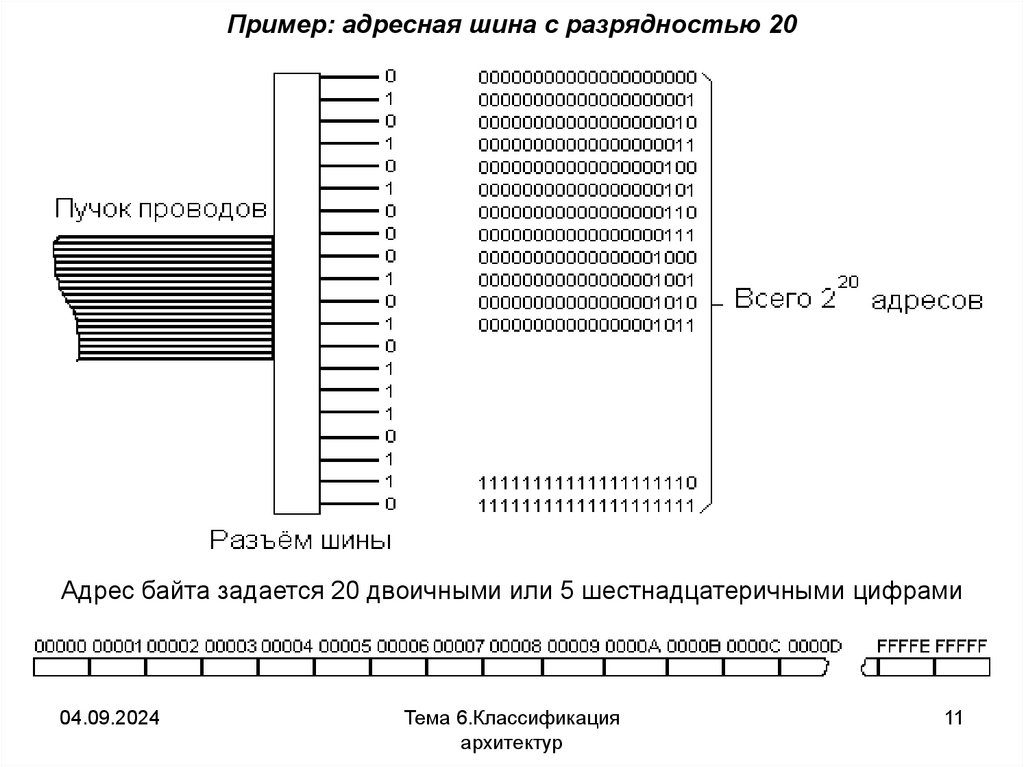

Пример: адресная шина с разрядностью 20Адрес байта задается 20 двоичными или 5 шестнадцатеричными цифрами

04.09.2024

Тема 6.Классификация

архитектур

11

12.

Тема 2. Архитектура микропроцессора iAPX 8086компьютера IPM PC/AT.

iAPX ─ Intel Advanced Processor Architecture, Intel ─ Integrated Electronics

IBM PC/AT ─ International Business Machines Advanced Technology.

Шинная, шестнадцатибитная (машинное слово 2 байта), СISC архитектура,

двадцатиразрядная адресная шина

Упрощенная схема компьютера с шинной архитектурой

04.09.2024

Тема 6.Классификация

архитектур

12

13.

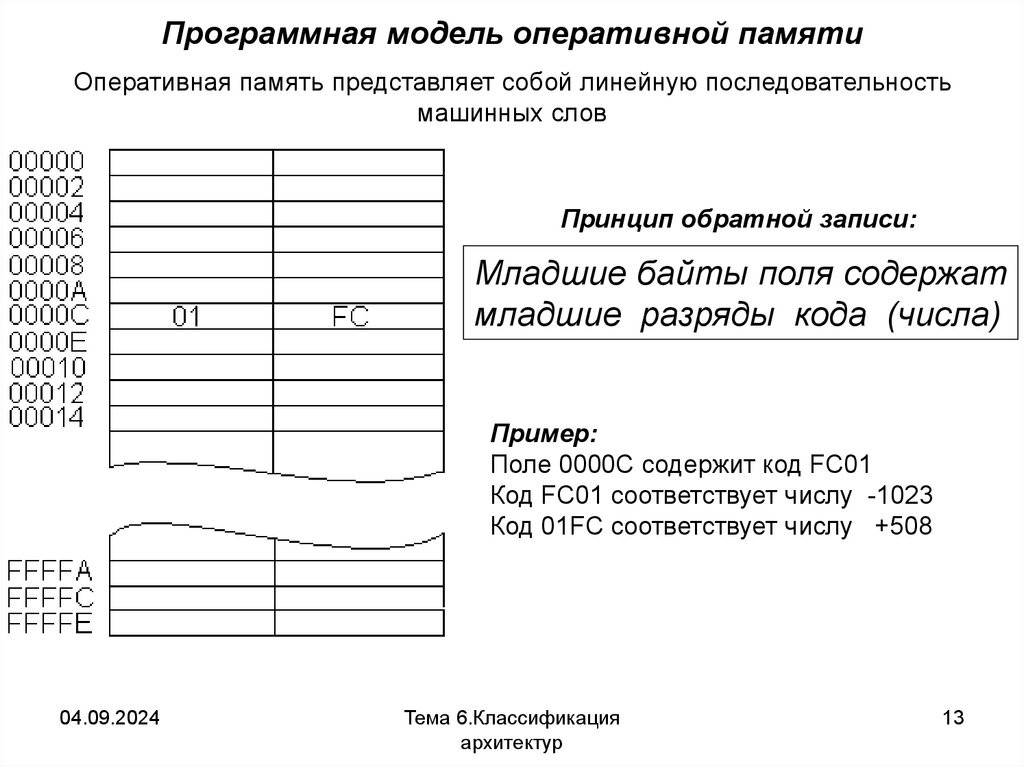

Программная модель оперативной памятиОперативная память представляет собой линейную последовательность

машинных слов

Принцип обратной записи:

Младшие байты поля содержат

младшие разряды кода (числа)

Пример:

Поле 0000С содержит код FC01

Код FC01 соответствует числу -1023

Код 01FC соответствует числу +508

04.09.2024

Тема 6.Классификация

архитектур

13

14.

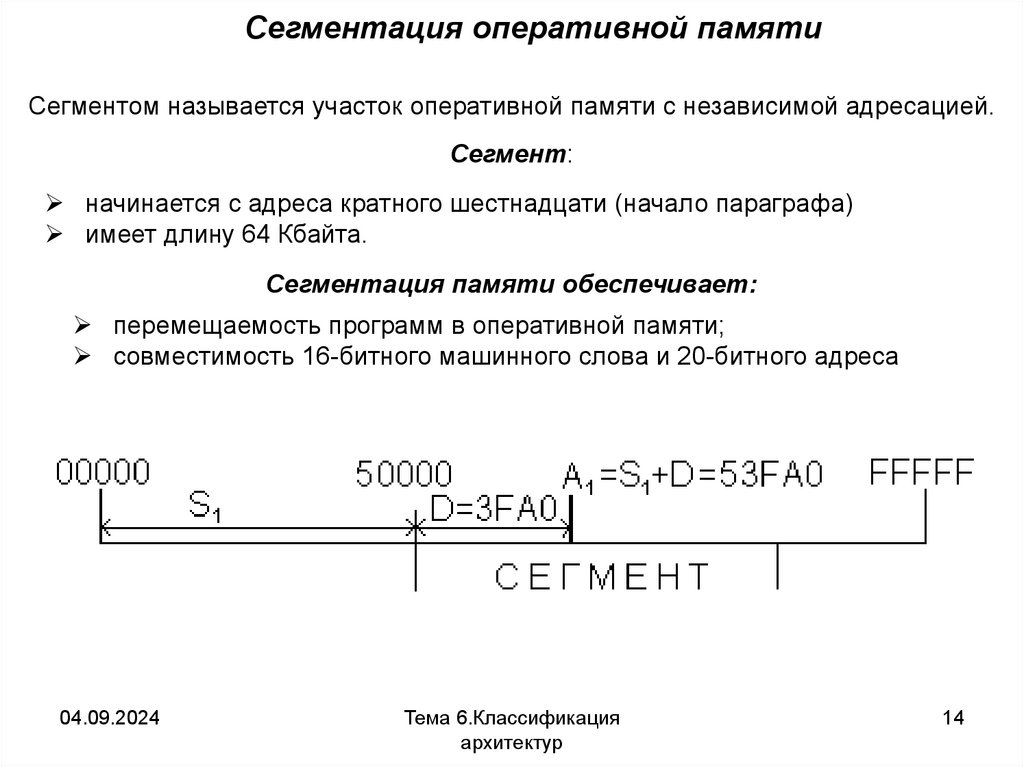

Сегментация оперативной памятиСегментом называется участок оперативной памяти с независимой адресацией.

Сегмент:

начинается с адреса кратного шестнадцати (начало параграфа)

имеет длину 64 Кбайта.

Сегментация памяти обеспечивает:

перемещаемость программ в оперативной памяти;

совместимость 16-битного машинного слова и 20-битного адреса

04.09.2024

Тема 6.Классификация

архитектур

14

15.

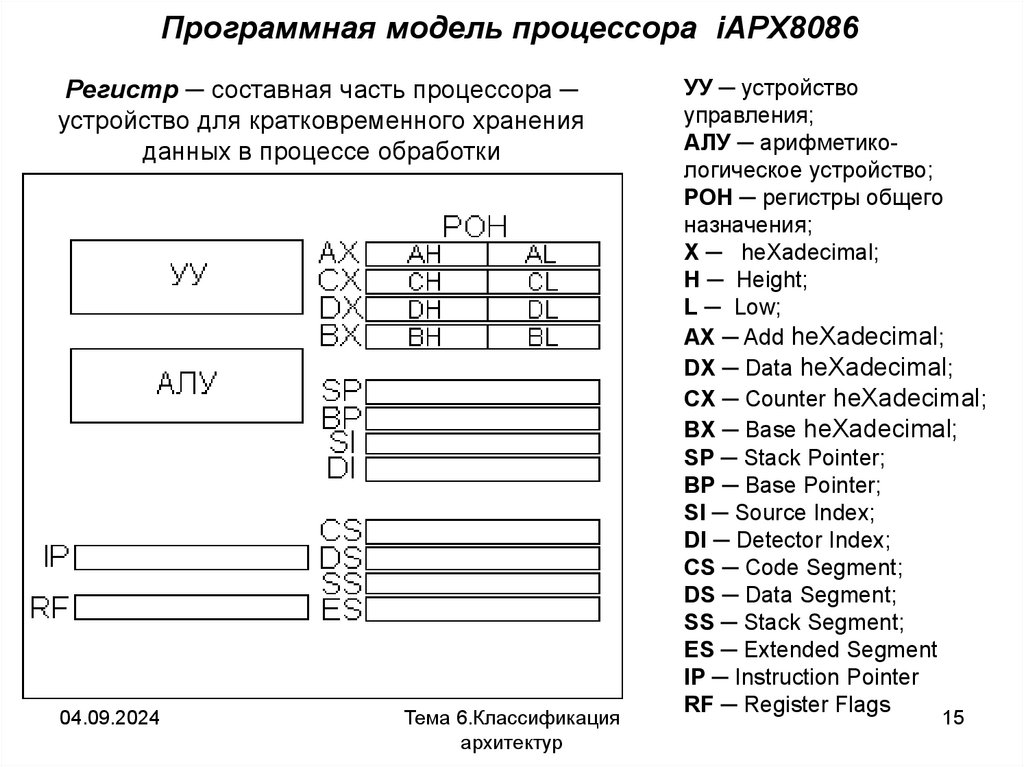

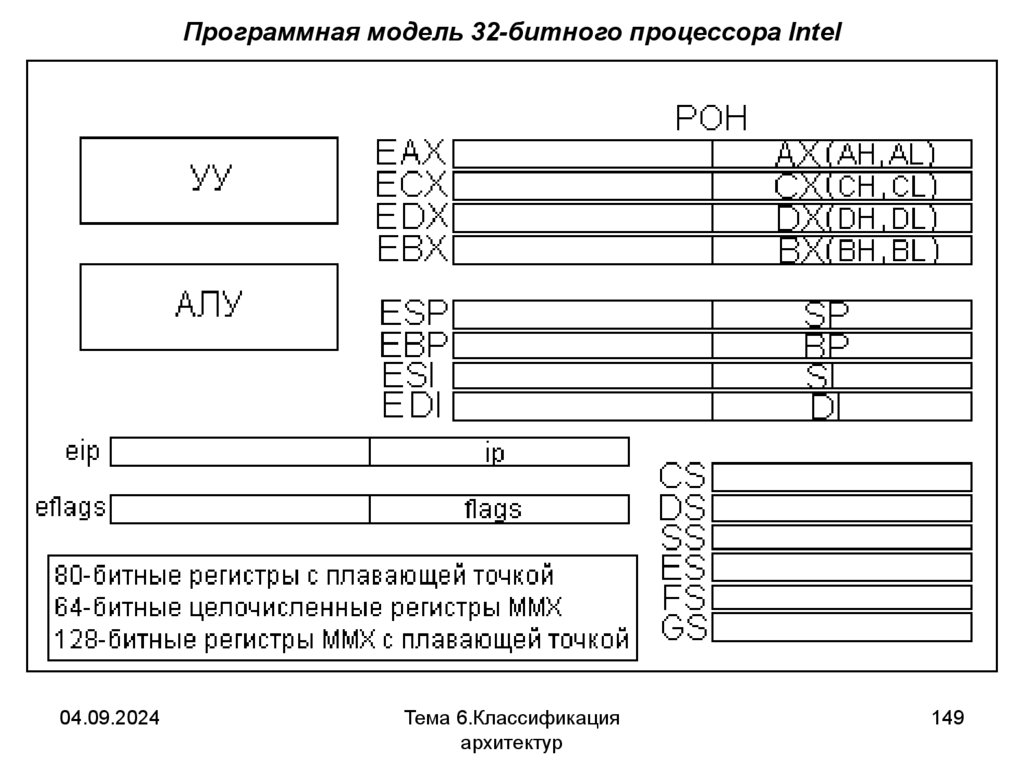

Программная модель процессора iAPX8086Регистр ─ составная часть процессора ─

устройство для кратковременного хранения

данных в процессе обработки

04.09.2024

Тема 6.Классификация

архитектур

УУ ─ устройство

управления;

АЛУ ─ арифметикологическое устройство;

РОН ─ регистры общего

назначения;

X ─ heXadecimal;

H ─ Height;

L ─ Low;

AX ─ Add heXadecimal;

DX ─ Data heXadecimal;

CX ─ Counter heXadecimal;

BX ─ Base heXadecimal;

SP ─ Stack Pointer;

BP ─ Base Pointer;

SI ─ Source Index;

DI ─ Detector Index;

CS ─ Code Segment;

DS ─ Data Segment;

SS ─ Stack Segment;

ES ─ Extended Segment

IP ─ Instruction Pointer

RF ─ Register Flags

15

16.

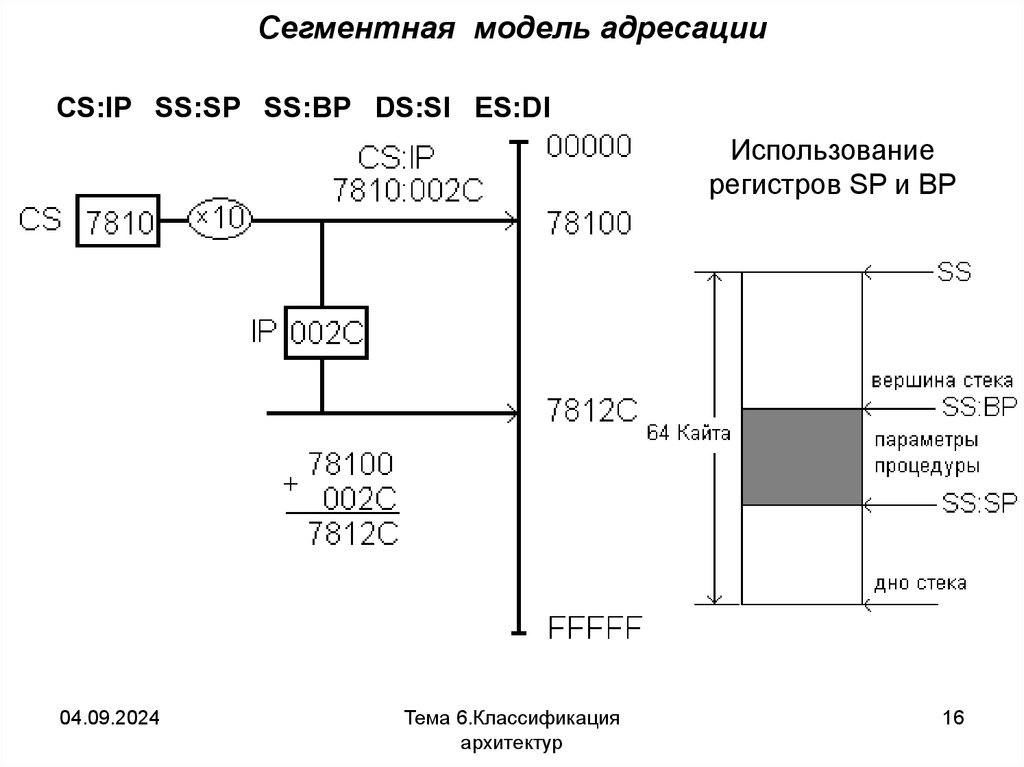

Сегментная модель адресацииCS:IP SS:SP SS:BP DS:SI ES:DI

Использование

регистров SP и BP

04.09.2024

Тема 6.Классификация

архитектур

16

17.

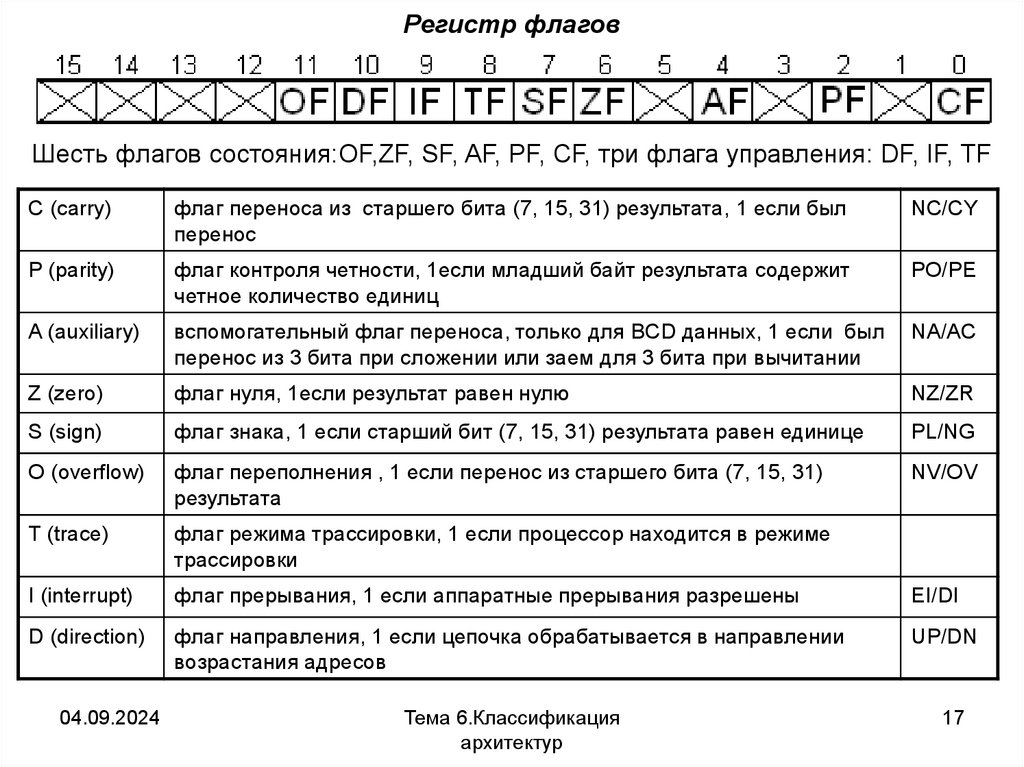

Регистр флаговШесть флагов состояния:OF,ZF, SF, AF, PF, CF, три флага управления: DF, IF, TF

С (carry)

флаг переноса из старшего бита (7, 15, 31) результата, 1 если был

перенос

NC/CY

P (parity)

флаг контроля четности, 1если младший байт результата содержит

четное количество единиц

PO/PE

A (auxiliary)

вспомогательный флаг переноса, только для BCD данных, 1 если был

перенос из 3 бита при сложении или заем для 3 бита при вычитании

NA/AC

Z (zero)

флаг нуля, 1если результат равен нулю

NZ/ZR

S (sign)

флаг знака, 1 если старший бит (7, 15, 31) результата равен единице

PL/NG

O (overflow)

флаг переполнения , 1 если перенос из старшего бита (7, 15, 31)

результата

NV/OV

T (trace)

флаг режима трассировки, 1 если процессор находится в режиме

трассировки

I (interrupt)

флаг прерывания, 1 если аппаратные прерывания разрешены

EI/DI

D (direction)

флаг направления, 1 если цепочка обрабатывается в направлении

возрастания адресов

UP/DN

Тема 6.Классификация

архитектур

17

04.09.2024

18.

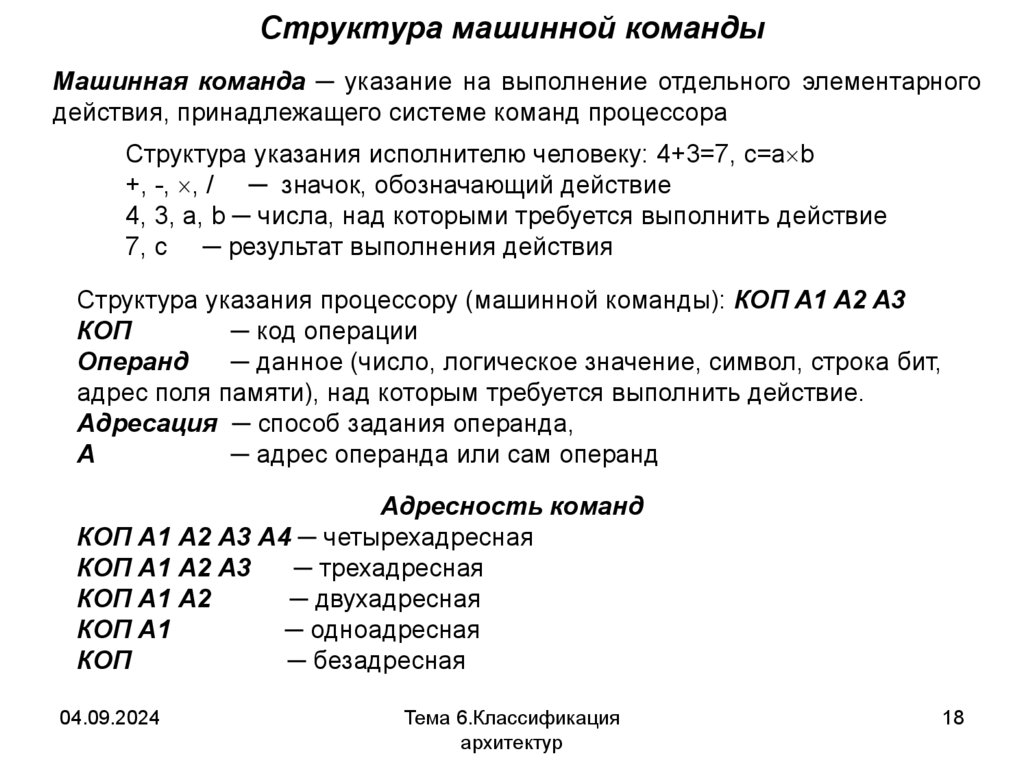

Структура машинной командыМашинная команда ─ указание на выполнение отдельного элементарного

действия, принадлежащего системе команд процессора

Структура указания исполнителю человеку: 4+3=7, c=a b

+, -, , / ─ значок, обозначающий действие

4, 3, a, b ─ числа, над которыми требуется выполнить действие

7, c ─ результат выполнения действия

Структура указания процессору (машинной команды): КОП A1 A2 A3

КОП

─ код операции

Операнд

─ данное (число, логическое значение, символ, строка бит,

адрес поля памяти), над которым требуется выполнить действие.

Адресация ─ способ задания операнда,

A

─ адрес операнда или сам операнд

Адресность команд

КОП А1 А2 А3 А4 ─ четырехадресная

КОП А1 А2 А3

─ трехадресная

КОП А1 А2

─ двухадресная

КОП А1

─ одноадресная

КОП

─ безадресная

04.09.2024

Тема 6.Классификация

архитектур

18

19.

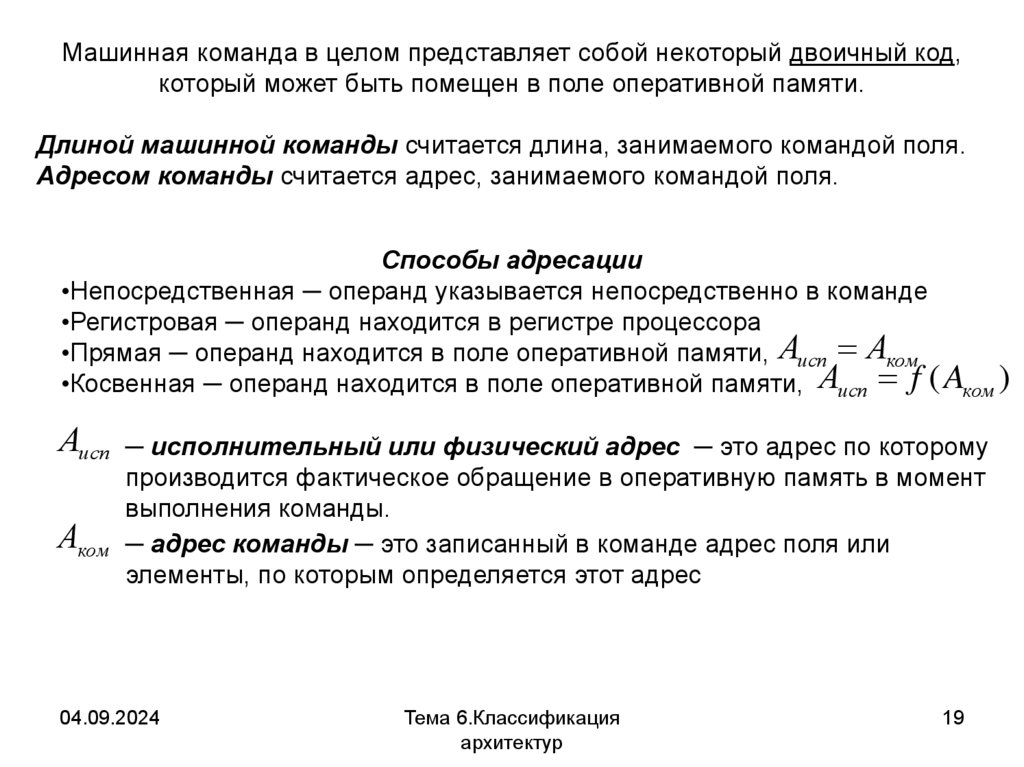

Машинная команда в целом представляет собой некоторый двоичный код,который может быть помещен в поле оперативной памяти.

Длиной машинной команды считается длина, занимаемого командой поля.

Адресом команды считается адрес, занимаемого командой поля.

Способы адресации

•Непосредственная ─ операнд указывается непосредственно в команде

•Регистровая ─ операнд находится в регистре процессора

•Прямая ─ операнд находится в поле оперативной памяти, Аисп Аком

•Косвенная ─ операнд находится в поле оперативной памяти, Аисп f ( Aком )

Аисп ─ исполнительный или физический адрес ─ это адрес по которому

производится фактическое обращение в оперативную память в момент

выполнения команды.

Аком ─ адрес команды ─ это записанный в команде адрес поля или

элементы, по которым определяется этот адрес

04.09.2024

Тема 6.Классификация

архитектур

19

20.

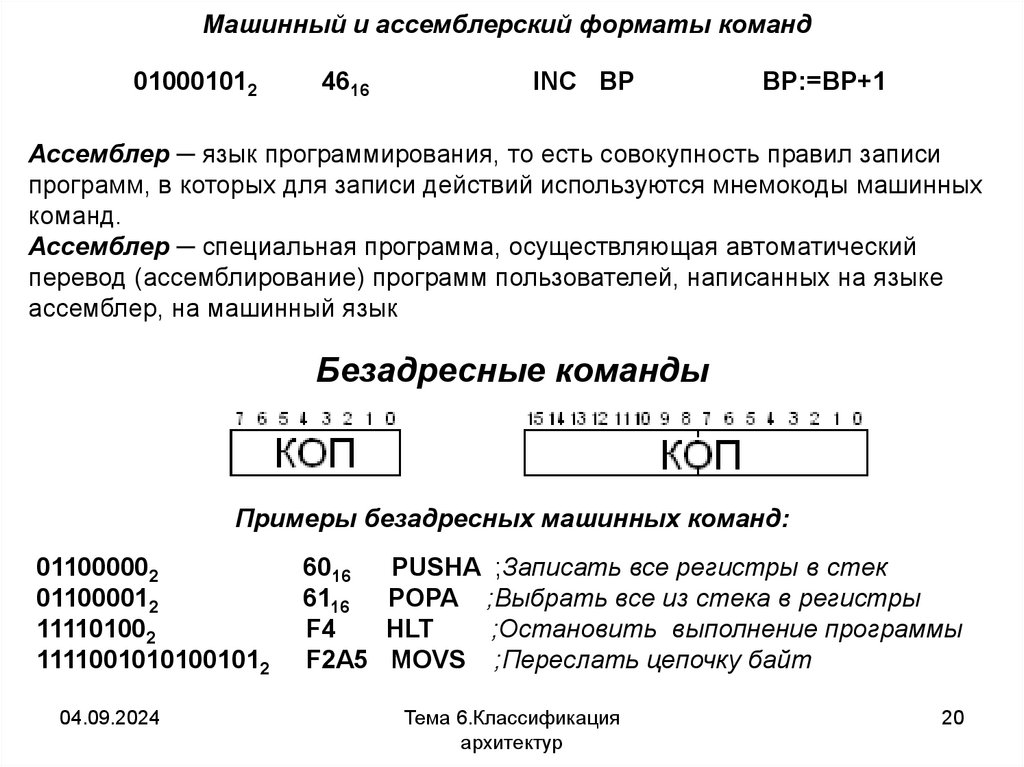

Машинный и ассемблерский форматы команд010001012

4616

INC BP

BP:=BP+1

Ассемблер ─ язык программирования, то есть совокупность правил записи

программ, в которых для записи действий используются мнемокоды машинных

команд.

Ассемблер ─ специальная программа, осуществляющая автоматический

перевод (ассемблирование) программ пользователей, написанных на языке

ассемблер, на машинный язык

Безадресные команды

Примеры безадресных машинных команд:

011000002

011000012

111101002

11110010101001012

04.09.2024

6016

PUSHA ;Записать все регистры в стек

6116 POPA ;Выбрать все из стека в регистры

F4

HLT

;Остановить выполнение программы

F2A5 MOVS ;Переслать цепочку байт

Тема 6.Классификация

архитектур

20

21.

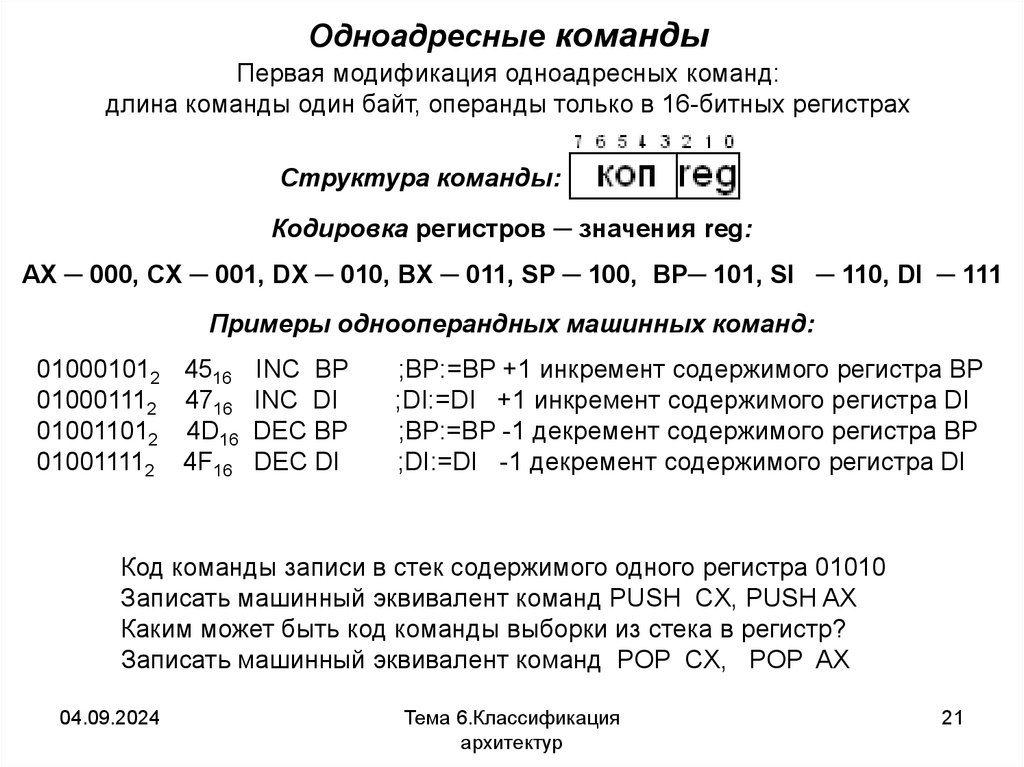

Одноадресные командыПервая модификация одноадресных команд:

длина команды один байт, операнды только в 16-битных регистрах

Структура команды:

Кодировка регистров ─ значения reg:

AX ─ 000, CX ─ 001, DX ─ 010, BX ─ 011, SP ─ 100, BP─ 101, SI ─ 110, DI ─ 111

Примеры однооперандных машинных команд:

010001012 4516 INC BP

010001112 4716 INC DI

010011012 4D16 DEC BP

010011112 4F16 DEC DI

;BP:=BP +1 инкремент содержимого регистра BP

;DI:=DI +1 инкремент содержимого регистра DI

;BP:=BP -1 декремент содержимого регистра BP

;DI:=DI -1 декремент содержимого регистра DI

Код команды записи в стек содержимого одного регистра 01010

Записать машинный эквивалент команд PUSH CX, PUSH AX

Каким может быть код команды выборки из стека в регистр?

Записать машинный эквивалент команд POP CX, POP AX

04.09.2024

Тема 6.Классификация

архитектур

21

22.

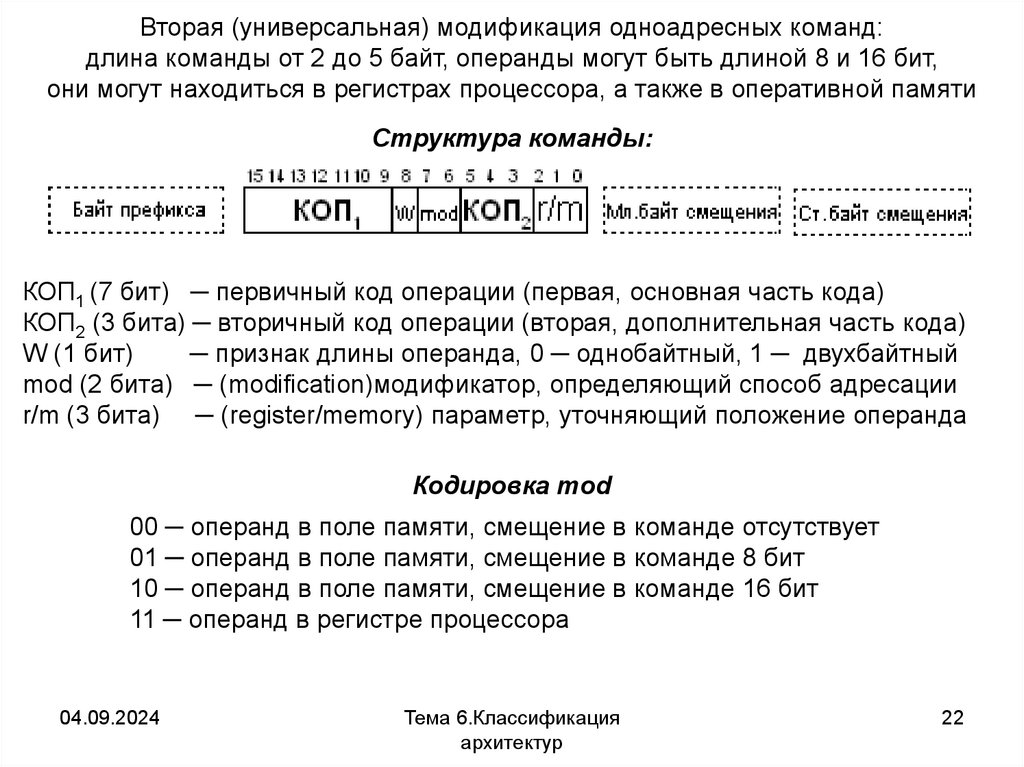

Вторая (универсальная) модификация одноадресных команд:длина команды от 2 до 5 байт, операнды могут быть длиной 8 и 16 бит,

они могут находиться в регистрах процессора, а также в оперативной памяти

Структура команды:

КОП1 (7 бит) ─ первичный код операции (первая, основная часть кода)

КОП2 (3 бита) ─ вторичный код операции (вторая, дополнительная часть кода)

W (1 бит)

─ признак длины операнда, 0 ─ однобайтный, 1 ─ двухбайтный

mod (2 бита) ─ (modification)модификатор, определяющий способ адресации

r/m (3 бита) ─ (register/memory) параметр, уточняющий положение операнда

Кодировка mod

00 ─ операнд в поле памяти, смещение в команде отсутствует

01 ─ операнд в поле памяти, смещение в команде 8 бит

10 ─ операнд в поле памяти, смещение в команде 16 бит

11 ─ операнд в регистре процессора

04.09.2024

Тема 6.Классификация

архитектур

22

23.

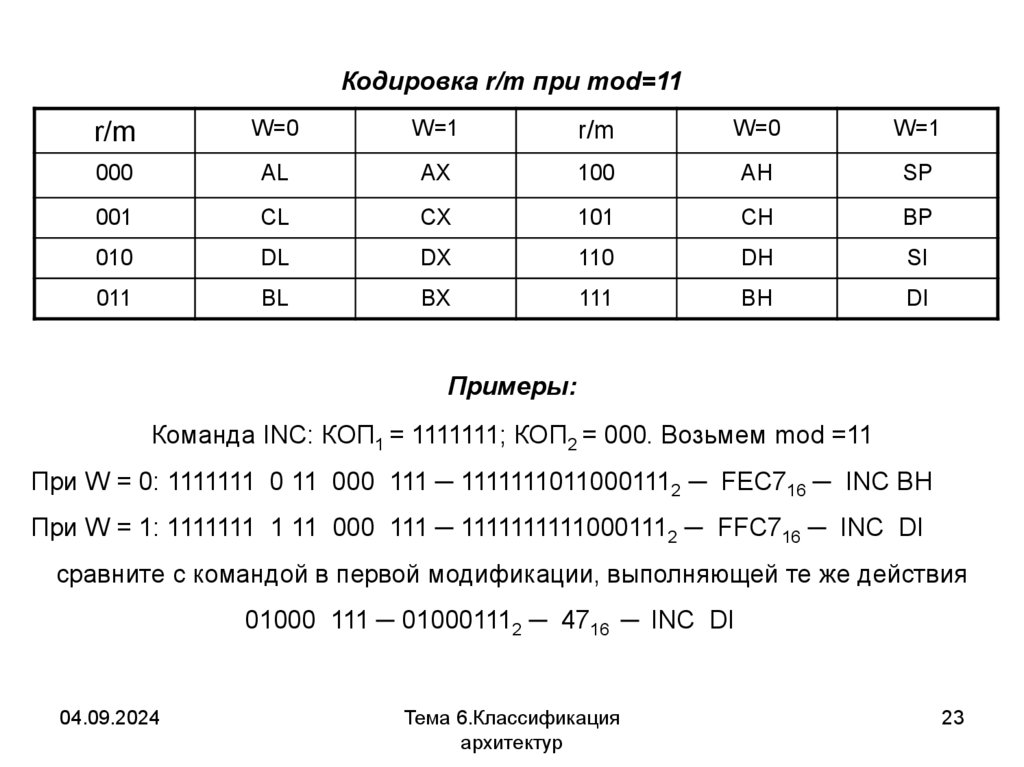

Кодировка r/m при mod=11r/m

W=0

W=1

r/m

W=0

W=1

000

AL

AX

100

AH

SP

001

CL

CX

101

CH

BP

010

DL

DX

110

DH

SI

011

BL

BX

111

BH

DI

Примеры:

Команда INC: КОП1 = 1111111; КОП2 = 000. Возьмем mod =11

При W = 0: 1111111 0 11 000 111 ─ 11111110110001112 ─ FEC716 ─ INC BH

При W = 1: 1111111 1 11 000 111 ─ 11111111110001112 ─ FFC716 ─ INC DI

сравните с командой в первой модификации, выполняющей те же действия

01000 111 ─ 010001112 ─ 4716 ─ INC DI

04.09.2024

Тема 6.Классификация

архитектур

23

24.

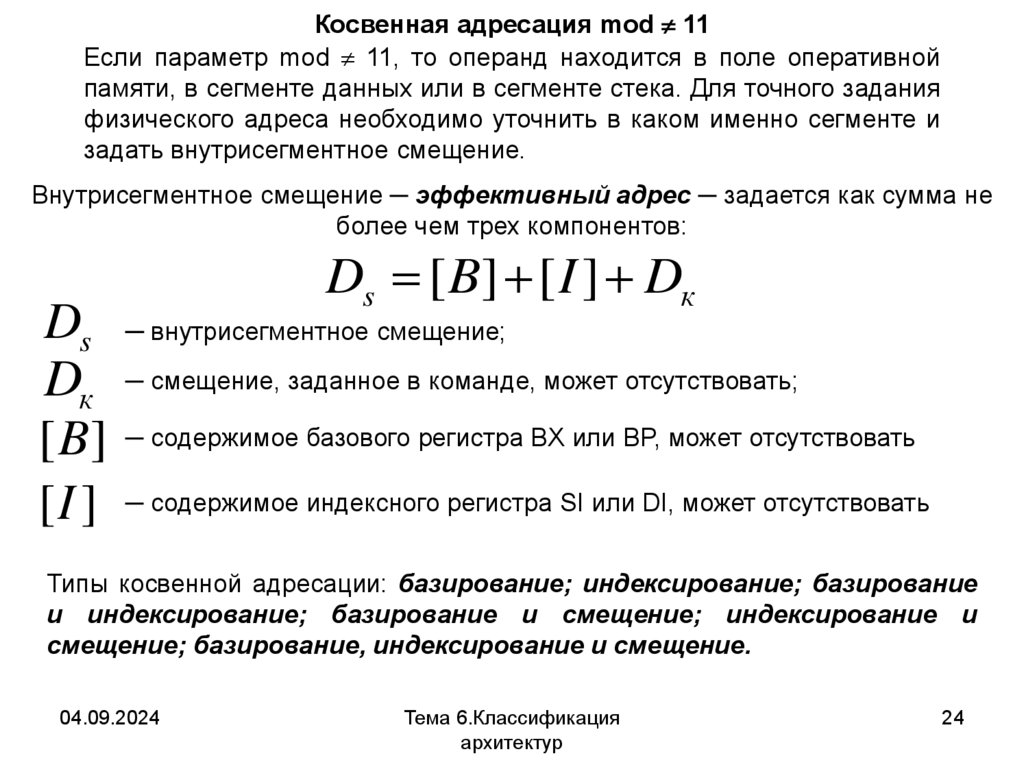

Косвенная адресация mod 11Если параметр mod 11, то операнд находится в поле оперативной

памяти, в сегменте данных или в сегменте стека. Для точного задания

физического адреса необходимо уточнить в каком именно сегменте и

задать внутрисегментное смещение.

Внутрисегментное смещение ─ эффективный адрес ─ задается как сумма не

более чем трех компонентов:

Ds [ B] [ I ] Dк

Ds ─ внутрисегментное смещение;

Dк ─ смещение, заданное в команде, может отсутствовать;

[B ] ─ содержимое базового регистра BX или BP, может отсутствовать

[I ] ─ содержимое индексного регистра SI или DI, может отсутствовать

Типы косвенной адресации: базирование; индексирование; базирование

и индексирование; базирование и смещение; индексирование и

смещение; базирование, индексирование и смещение.

04.09.2024

Тема 6.Классификация

архитектур

24

25.

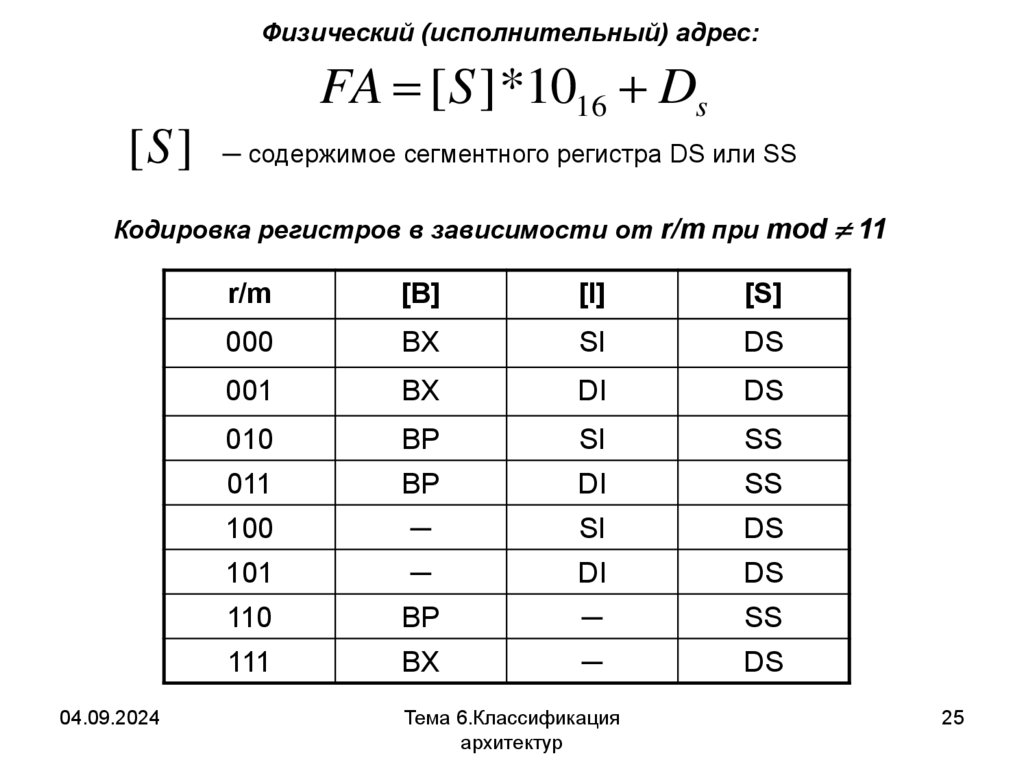

Физический (исполнительный) адрес:FA [ S ] *1016 Ds

[S ] ─ содержимое сегментного регистра DS или SS

Кодировка регистров в зависимости от r/m при mod 11

04.09.2024

r/m

[B]

[I]

[S]

000

BX

SI

DS

001

BX

DI

DS

010

BP

SI

SS

011

BP

DI

SS

100

─

SI

DS

101

─

DI

DS

110

BP

─

SS

111

BX

─

DS

Тема 6.Классификация

архитектур

25

26.

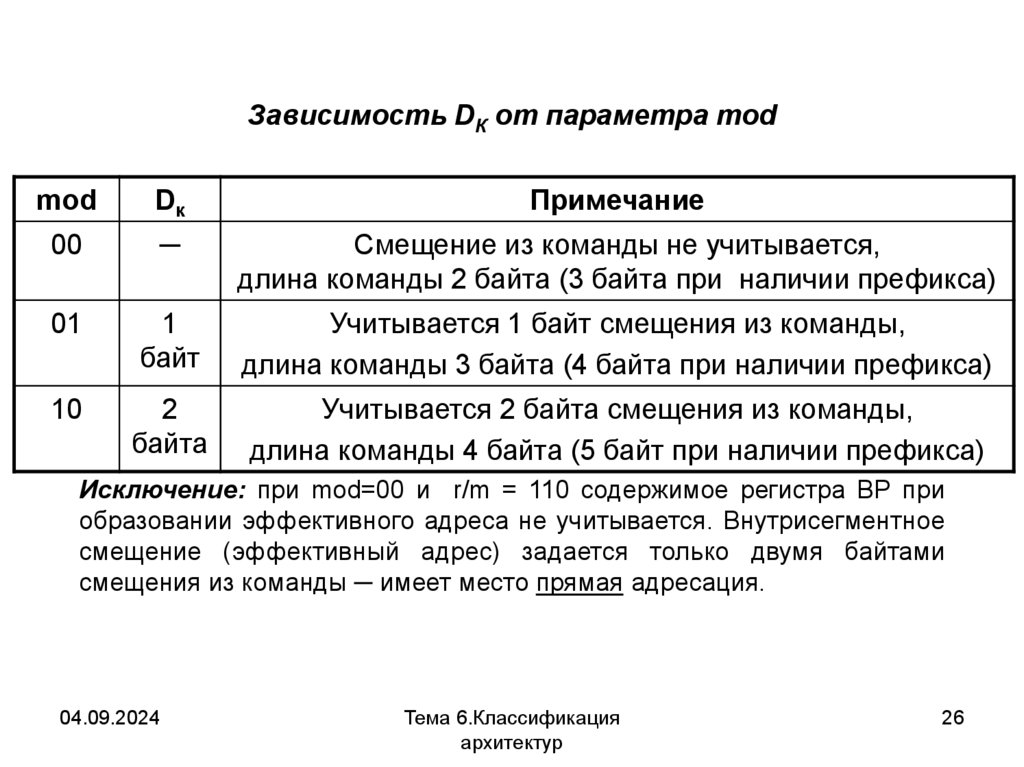

Зависимость DК от параметра modmod

Dк

Примечание

00

─

Смещение из команды не учитывается,

длина команды 2 байта (3 байта при наличии префикса)

01

1

байт

Учитывается 1 байт смещения из команды,

длина команды 3 байта (4 байта при наличии префикса)

10

2

байта

Учитывается 2 байта смещения из команды,

длина команды 4 байта (5 байт при наличии префикса)

Исключение: при mod=00 и r/m = 110 содержимое регистра BP при

образовании эффективного адреса не учитывается. Внутрисегментное

смещение (эффективный адрес) задается только двумя байтами

смещения из команды ─ имеет место прямая адресация.

04.09.2024

Тема 6.Классификация

архитектур

26

27.

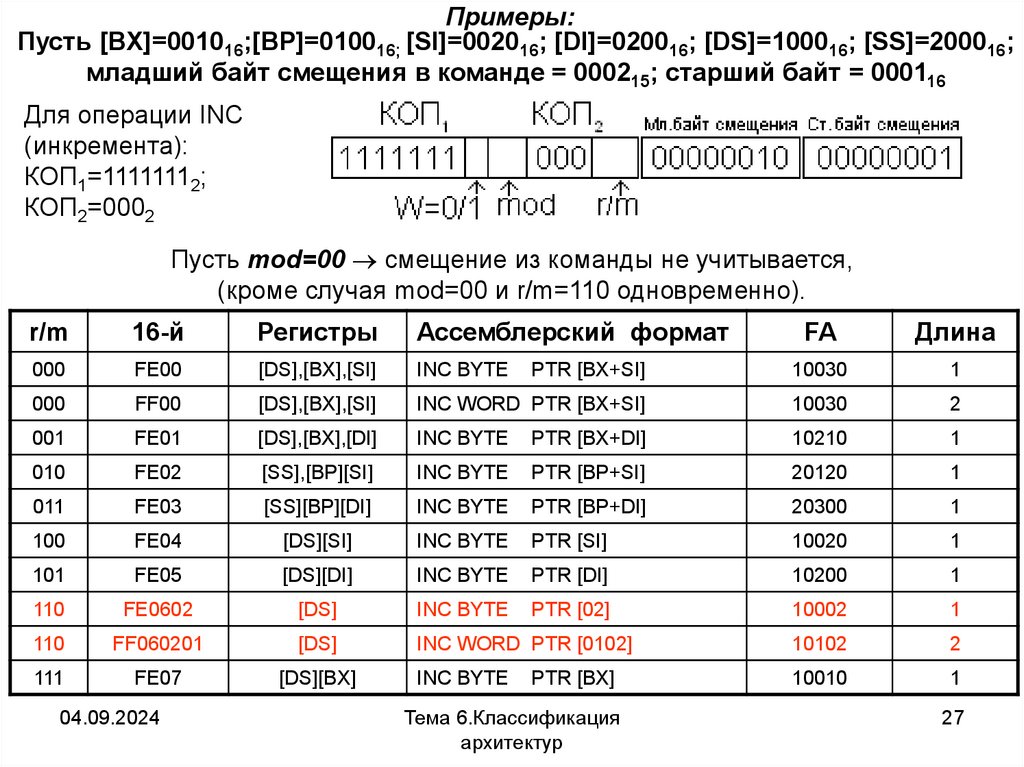

Примеры:Пусть [BX]=001016;[BP]=010016; [SI]=002016; [DI]=020016; [DS]=100016; [SS]=200016;

младший байт смещения в команде = 000215; старший байт = 000116

Для операции INC

(инкремента):

КОП1=11111112;

КОП2=0002

Пусть mod=00 смещение из команды не учитывается,

(кроме случая mod=00 и r/m=110 одновременно).

r/m

16-й

Регистры

Ассемблерский формат

FA

Длина

000

FE00

[DS],[BX],[SI]

INC BYTE

PTR [BX+SI]

10030

1

000

FF00

[DS],[BX],[SI]

INC WORD PTR [BX+SI]

10030

2

001

FE01

[DS],[BX],[DI]

INC BYTE

PTR [BX+DI]

10210

1

010

FE02

[SS],[BP][SI]

INC BYTE

PTR [BP+SI]

20120

1

011

FE03

[SS][BP][DI]

INC BYTE

PTR [BP+DI]

20300

1

100

FE04

[DS][SI]

INC BYTE

PTR [SI]

10020

1

101

FE05

[DS][DI]

INC BYTE

PTR [DI]

10200

1

110

FE0602

[DS]

INC BYTE

PTR [02]

10002

1

110

FF060201

[DS]

INC WORD PTR [0102]

10102

2

111

FE07

[DS][BX]

INC BYTE

10010

1

04.09.2024

PTR [BX]

Тема 6.Классификация

архитектур

27

28.

Пусть mod=01 из команды берется младший байт смещенияr/m

16-й

Регистры

Ассемблерский формат

FA

Длина

000

FE4002

[DS],[BX],[SI]

INC BYTE

PTR [BX+SI+02]

10032

1

000

FF4002

[DS],[BX],[SI]

INC WORD PTR [BX+SI+02]

10032

2

001

FE4102

[DS],[BX],[DI]

INC BYTE

PTR [BX+DI+02]

10212

1

010

FE4202

[SS],[BP][SI]

INC BYTE

PTR [BP+SI+02]

20122

1

011

FE4302

[SS][BP][DI]

INC BYTE

PTR [BP+DI+02]

20302

1

100

FE4402

[DS][SI]

INC BYTE

PTR [SI+02]

10022

1

101

FE4502

[DS][DI]

INC BYTE

PTR [DI+02]

10202

1

110

FE4602

[DS][BP]

INC BYTE

PTR [BP+02]

10102

1

110

FF4602

[DS][BP]

INC WORD PTR [BP+02]

10102

2

111

FE4702

[DS][BX]

INC BYTE

10012

1

04.09.2024

PTR [BX+02]

Тема 6.Классификация

архитектур

28

29.

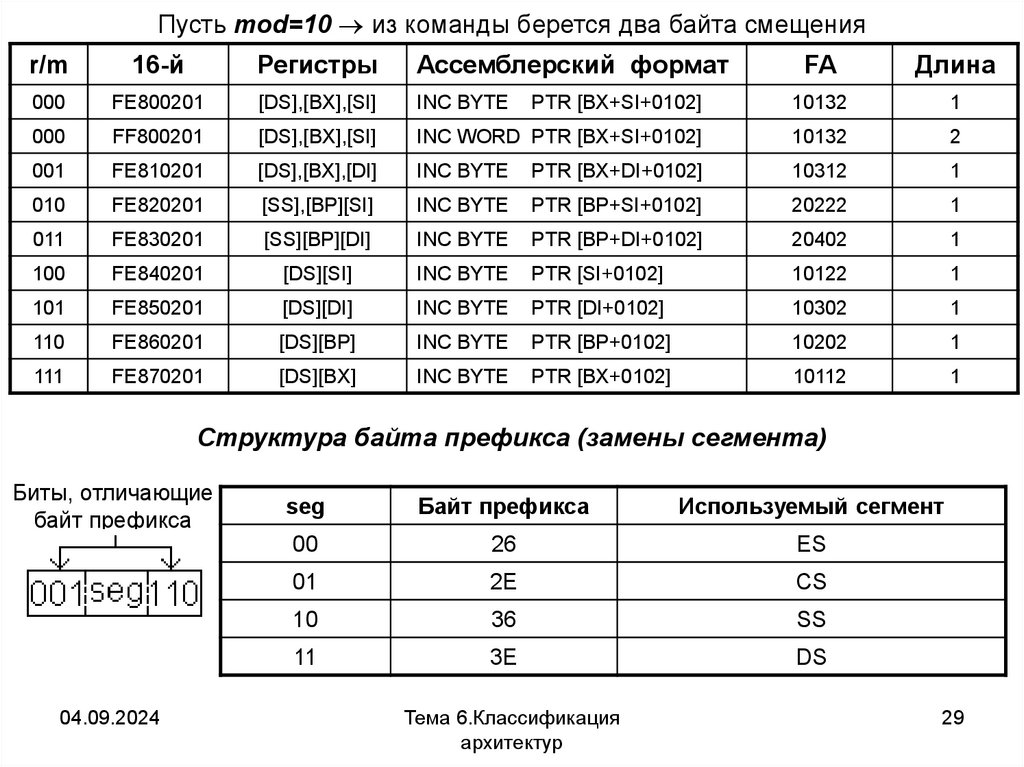

Пусть mod=10 из команды берется два байта смещенияr/m

16-й

Регистры

Ассемблерский формат

FA

Длина

000

FE800201

[DS],[BX],[SI]

INC BYTE

PTR [BX+SI+0102]

10132

1

000

FF800201

[DS],[BX],[SI]

INC WORD PTR [BX+SI+0102]

10132

2

001

FE810201

[DS],[BX],[DI]

INC BYTE

PTR [BX+DI+0102]

10312

1

010

FE820201

[SS],[BP][SI]

INC BYTE

PTR [BP+SI+0102]

20222

1

011

FE830201

[SS][BP][DI]

INC BYTE

PTR [BP+DI+0102]

20402

1

100

FE840201

[DS][SI]

INC BYTE

PTR [SI+0102]

10122

1

101

FE850201

[DS][DI]

INC BYTE

PTR [DI+0102]

10302

1

110

FE860201

[DS][BP]

INC BYTE

PTR [BP+0102]

10202

1

111

FE870201

[DS][BX]

INC BYTE

PTR [BX+0102]

10112

1

Структура байта префикса (замены сегмента)

Биты, отличающие

байт префикса

04.09.2024

seg

Байт префикса

Используемый сегмент

00

26

ES

01

2E

CS

10

36

SS

11

3E

DS

Тема 6.Классификация

архитектур

29

30.

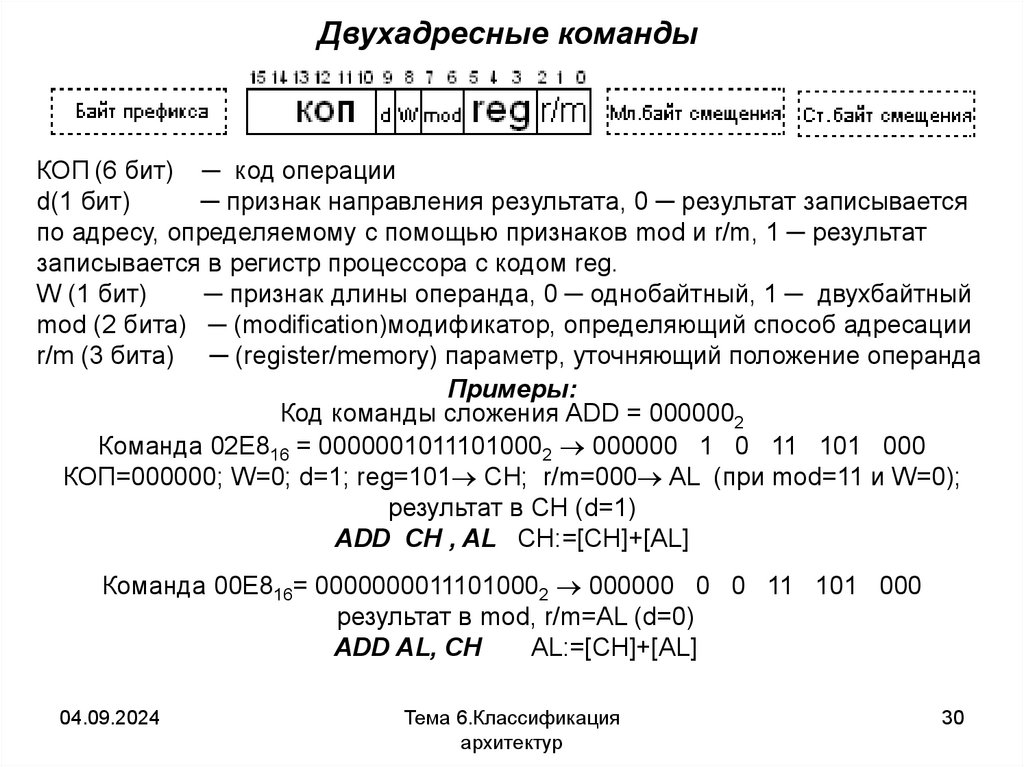

Двухадресные командыКОП (6 бит) ─ код операции

d(1 бит)

─ признак направления результата, 0 ─ результат записывается

по адресу, определяемому с помощью признаков mod и r/m, 1 ─ результат

записывается в регистр процессора с кодом reg.

W (1 бит)

─ признак длины операнда, 0 ─ однобайтный, 1 ─ двухбайтный

mod (2 бита) ─ (modification)модификатор, определяющий способ адресации

r/m (3 бита) ─ (register/memory) параметр, уточняющий положение операнда

Примеры:

Код команды сложения ADD = 0000002

Команда 02E816 = 00000010111010002 000000 1 0 11 101 000

КОП=000000; W=0; d=1; reg=101 CH; r/m=000 AL (при mod=11 и W=0);

результат в CH (d=1)

ADD CH , AL СH:=[CH]+[AL]

Команда 00E816= 00000000111010002 000000 0 0 11 101 000

результат в mod, r/m=AL (d=0)

ADD AL, CH

AL:=[CH]+[AL]

04.09.2024

Тема 6.Классификация

архитектур

30

31.

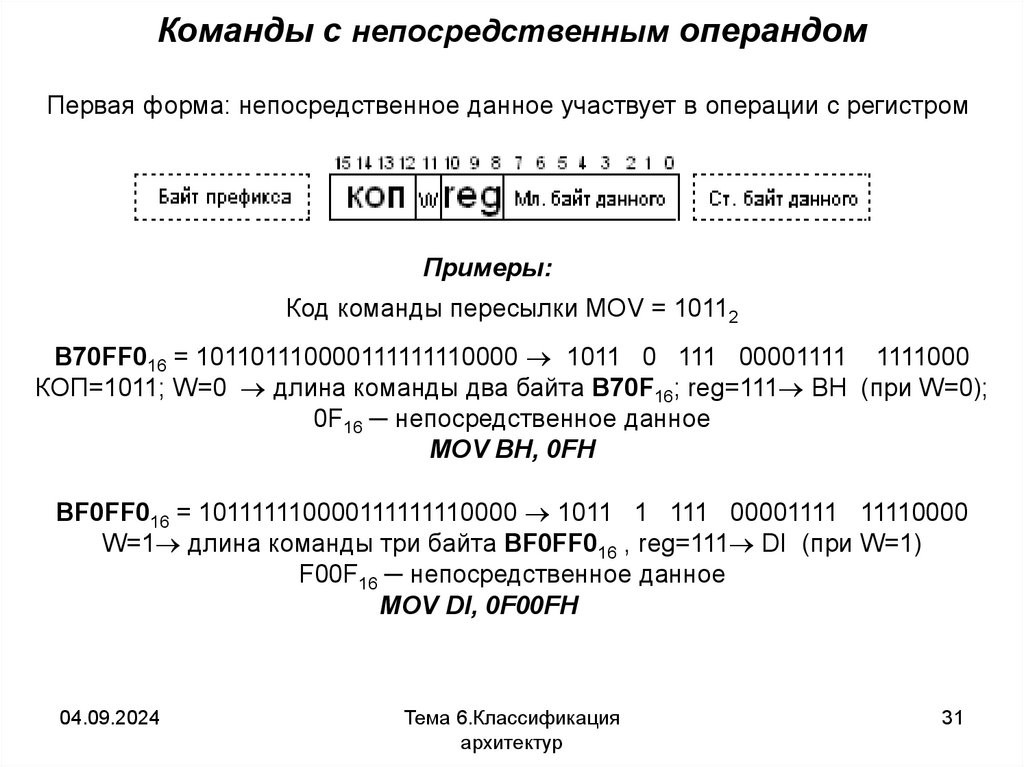

Команды с непосредственным операндомПервая форма: непосредственное данное участвует в операции с регистром

Примеры:

Код команды пересылки MOV = 10112

B70FF016 = 101101110000111111110000 1011 0 111 00001111 1111000

КОП=1011; W=0 длина команды два байта B70F16; reg=111 BH (при W=0);

0F16 ─ непосредственное данное

MOV BH, 0FH

BF0FF016 = 101111110000111111110000 1011 1 111 00001111 11110000

W=1 длина команды три байта BF0FF016 , reg=111 DI (при W=1)

F00F16 ─ непосредственное данное

MOV DI, 0F00FH

04.09.2024

Тема 6.Классификация

архитектур

31

32.

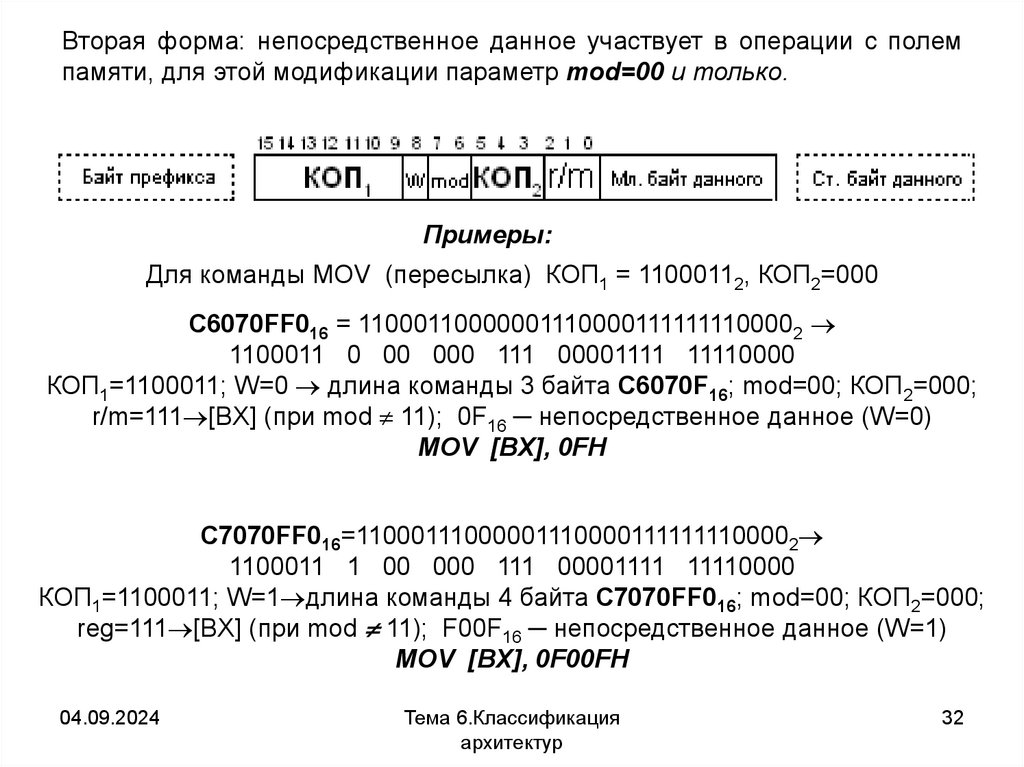

Вторая форма: непосредственное данное участвует в операции с полемпамяти, для этой модификации параметр mod=00 и только.

Примеры:

Для команды MOV (пересылка) КОП1 = 11000112, КОП2=000

С6070FF016 = 110001100000011100001111111100002

1100011 0 00 000 111 00001111 11110000

КОП1=1100011; W=0 длина команды 3 байта С6070F16; mod=00; КОП2=000;

r/m=111 [BX] (при mod 11); 0F16 ─ непосредственное данное (W=0)

MOV [BX], 0FH

С7070FF016=110001110000011100001111111100002

1100011 1 00 000 111 00001111 11110000

КОП1=1100011; W=1 длина команды 4 байта C7070FF016; mod=00; КОП2=000;

reg=111 [BX] (при mod 11); F00F16 ─ непосредственное данное (W=1)

MOV [BX], 0F00FH

04.09.2024

Тема 6.Классификация

архитектур

32

33.

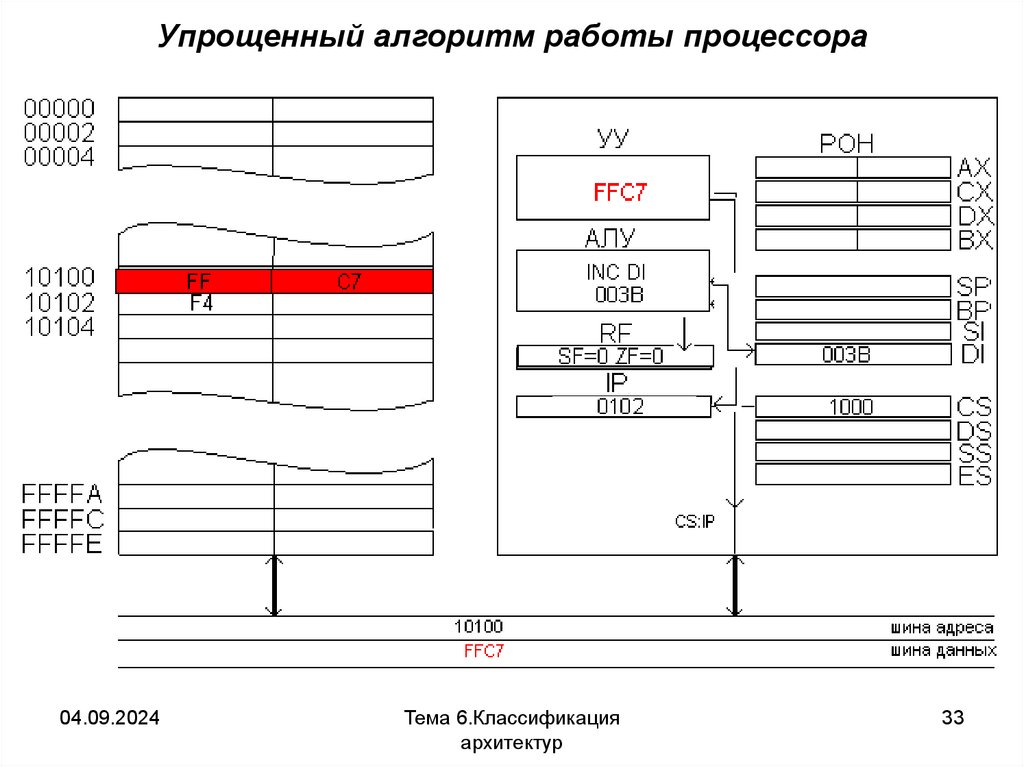

Упрощенный алгоритм работы процессора04.09.2024

Тема 6.Классификация

архитектур

33

34.

Первый этап. По содержимому регистров CS:IP определяется физическийадрес поля памяти, который содержит очередную команду программы. Этот

адрес выставляется на адресную шину и передается в оперативную память.

Второй этап. Выбирается содержимое определенного таким образом поля

памяти. Это содержимое по шине данных передается в устройство

управления процессора.

Третий этап. Устройство управления дешифрует команду и определяет ее

длину, затем увеличивает содержимое регистра IP на длину команды.

Четвертый этап. Устройство управления обеспечивает выполнение

команды, передавая необходимую управляющую информацию АЛУ, а также

пересылая в АЛУ обрабатываемые данные.

Пятый этап. АЛУ выполняет запрошенное в команде действие. Устройство

управления выполняет заданную командой пересылку результата и

формирует соответствующее результату содержимое регистра флагов.

04.09.2024

Тема 6.Классификация

архитектур

34

35.

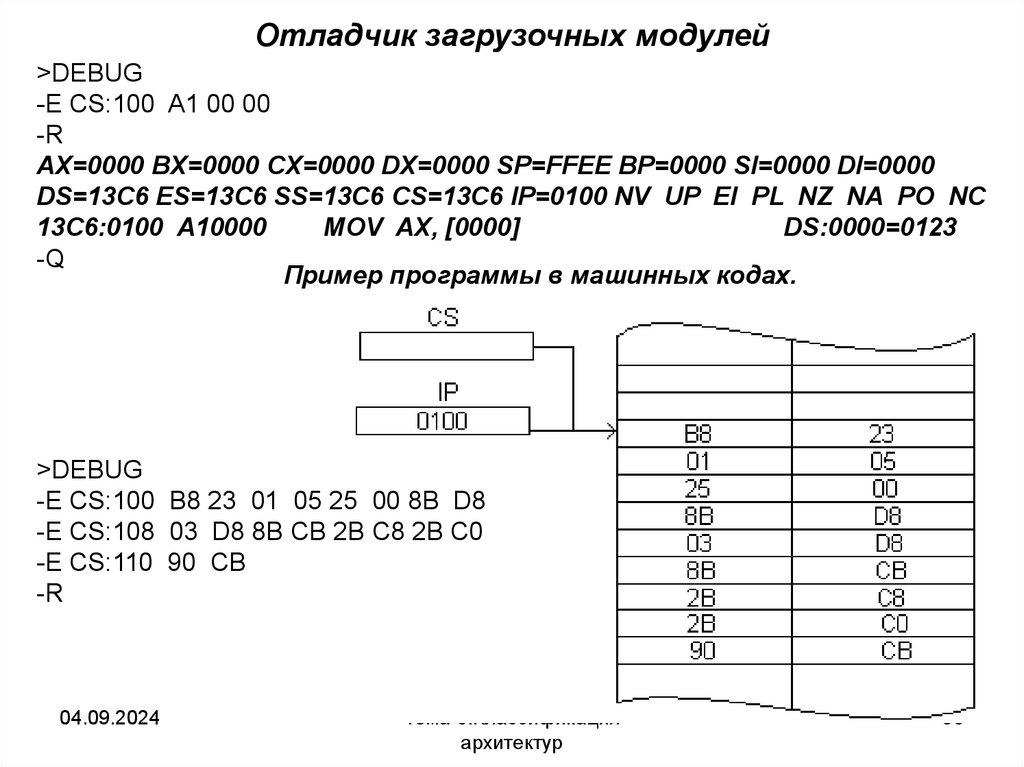

Отладчик загрузочных модулей>DEBUG

-E CS:100 A1 00 00

-R

AX=0000 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=13C6 ES=13C6 SS=13C6 CS=13C6 IP=0100 NV UP EI PL NZ NA PO NC

13C6:0100 A10000

MOV AX, [0000]

DS:0000=0123

-Q

Пример программы в машинных кодах.

>DEBUG

-E CS:100 B8 23 01 05 25 00 8B D8

-E CS:108 03 D8 8B CB 2B C8 2B C0

-E CS:110 90 CB

-R

04.09.2024

Тема 6.Классификация

архитектур

35

36.

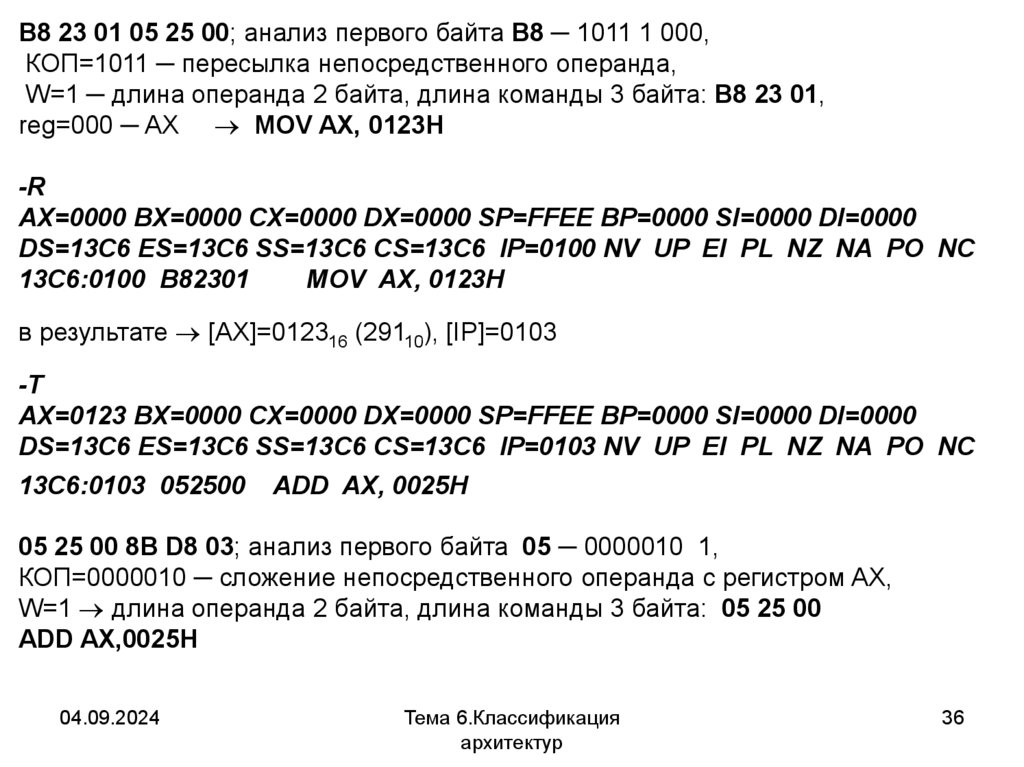

B8 23 01 05 25 00; анализ первого байта B8 ─ 1011 1 000,КОП=1011 ─ пересылка непосредственного операнда,

W=1 ─ длина операнда 2 байта, длина команды 3 байта: B8 23 01,

reg=000 ─ AX MOV AX, 0123H

-R

AX=0000 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=13C6 ES=13C6 SS=13C6 CS=13C6 IP=0100 NV UP EI PL NZ NA PO NC

13C6:0100 B82301

MOV AX, 0123H

в результате [AX]=012316 (29110), [IP]=0103

-T

AX=0123 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=13C6 ES=13C6 SS=13C6 CS=13C6 IP=0103 NV UP EI PL NZ NA PO NC

13C6:0103 052500

ADD AX, 0025H

05 25 00 8B D8 03; анализ первого байта 05 ─ 0000010 1,

КОП=0000010 ─ сложение непосредственного операнда с регистром AX,

W=1 длина операнда 2 байта, длина команды 3 байта: 05 25 00

ADD AX,0025H

04.09.2024

Тема 6.Классификация

архитектур

36

37.

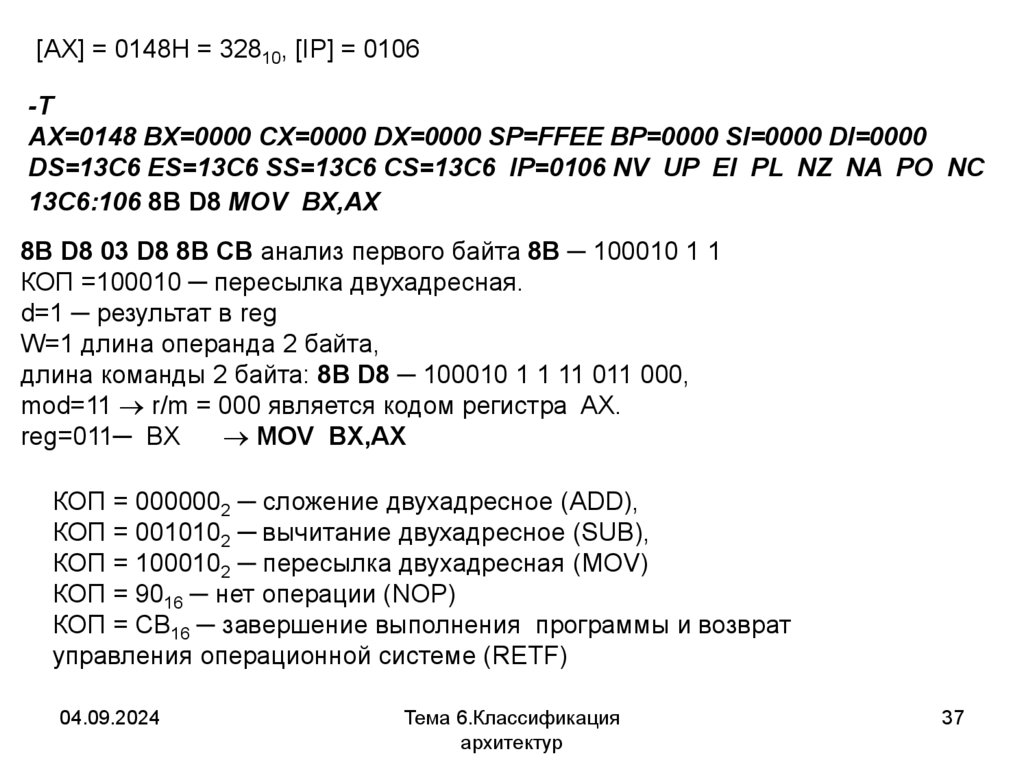

[AX] = 0148H = 32810, [IP] = 0106-T

AX=0148 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=13C6 ES=13C6 SS=13C6 CS=13C6 IP=0106 NV UP EI PL NZ NA PO NC

13C6:106 8B D8 MOV BX,AX

8B D8 03 D8 8B CB анализ первого байта 8B ─ 100010 1 1

КОП =100010 ─ пересылка двухадресная.

d=1 ─ результат в reg

W=1 длина операнда 2 байта,

длина команды 2 байта: 8B D8 ─ 100010 1 1 11 011 000,

mod=11 r/m = 000 является кодом регистра AX.

reg=011─ BX

MOV BX,AX

КОП = 0000002 ─ сложение двухадресное (ADD),

КОП = 0010102 ─ вычитание двухадресное (SUB),

КОП = 1000102 ─ пересылка двухадресная (MOV)

КОП = 9016 ─ нет операции (NOP)

КОП = CB16 ─ завершение выполнения программы и возврат

управления операционной системе (RETF)

04.09.2024

Тема 6.Классификация

архитектур

37

38.

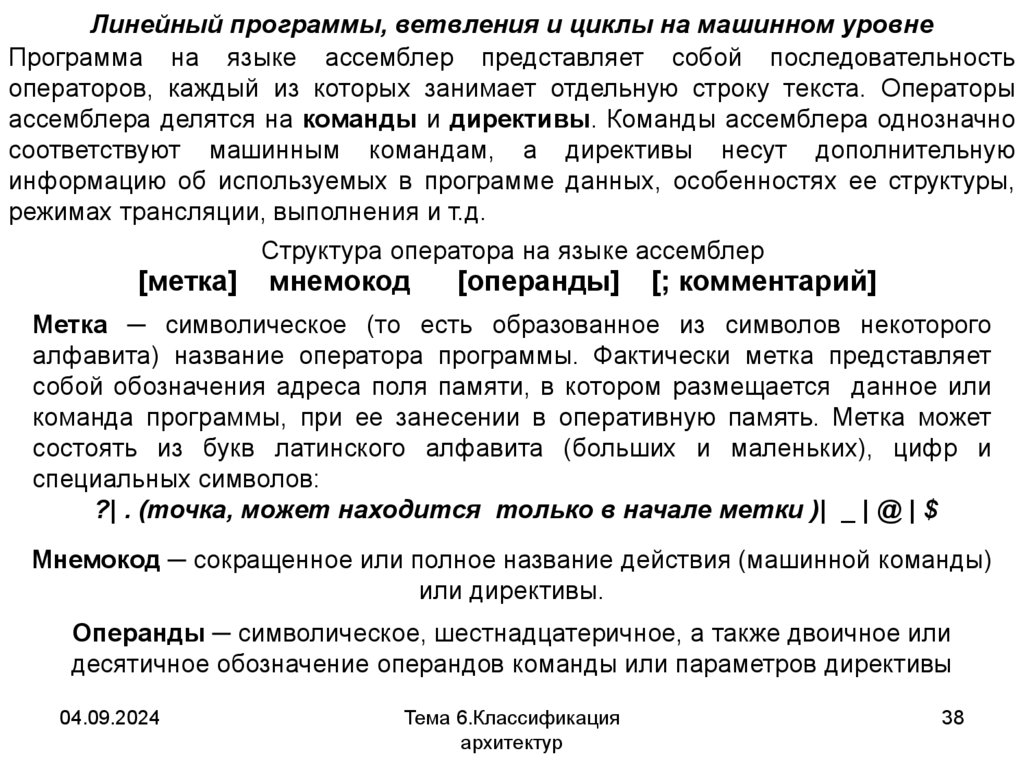

Линейный программы, ветвления и циклы на машинном уровнеПрограмма на языке ассемблер представляет собой последовательность

операторов, каждый из которых занимает отдельную строку текста. Операторы

ассемблера делятся на команды и директивы. Команды ассемблера однозначно

соответствуют машинным командам, а директивы несут дополнительную

информацию об используемых в программе данных, особенностях ее структуры,

режимах трансляции, выполнения и т.д.

Структура оператора на языке ассемблер

[метка]

мнемокод

[операнды]

[; комментарий]

Метка ─ символическое (то есть образованное из символов некоторого

алфавита) название оператора программы. Фактически метка представляет

собой обозначения адреса поля памяти, в котором размещается данное или

команда программы, при ее занесении в оперативную память. Метка может

состоять из букв латинского алфавита (больших и маленьких), цифр и

специальных символов:

?| . (точка, может находится только в начале метки )| _ | @ | $

Мнемокод ─ сокращенное или полное название действия (машинной команды)

или директивы.

Операнды ─ символическое, шестнадцатеричное, а также двоичное или

десятичное обозначение операндов команды или параметров директивы

04.09.2024

Тема 6.Классификация

архитектур

38

39.

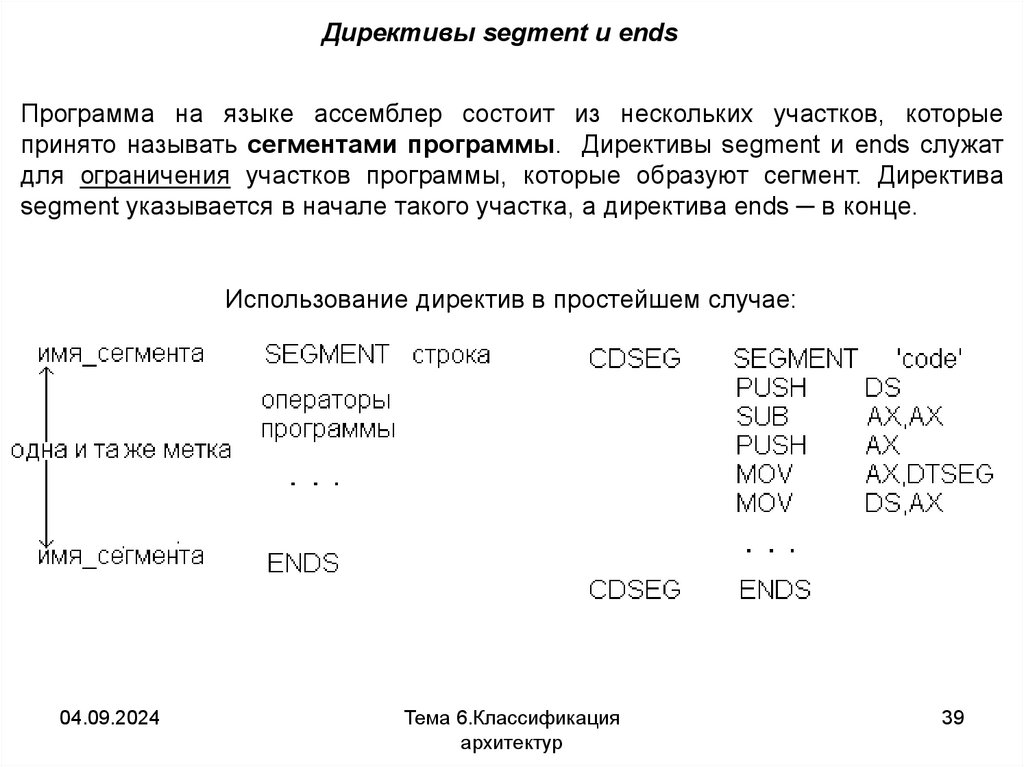

Директивы segment и endsПрограмма на языке ассемблер состоит из нескольких участков, которые

принято называть сегментами программы. Директивы segment и ends служат

для ограничения участков программы, которые образуют сегмент. Директива

segment указывается в начале такого участка, а директива ends ─ в конце.

Использование директив в простейшем случае:

04.09.2024

Тема 6.Классификация

архитектур

39

40.

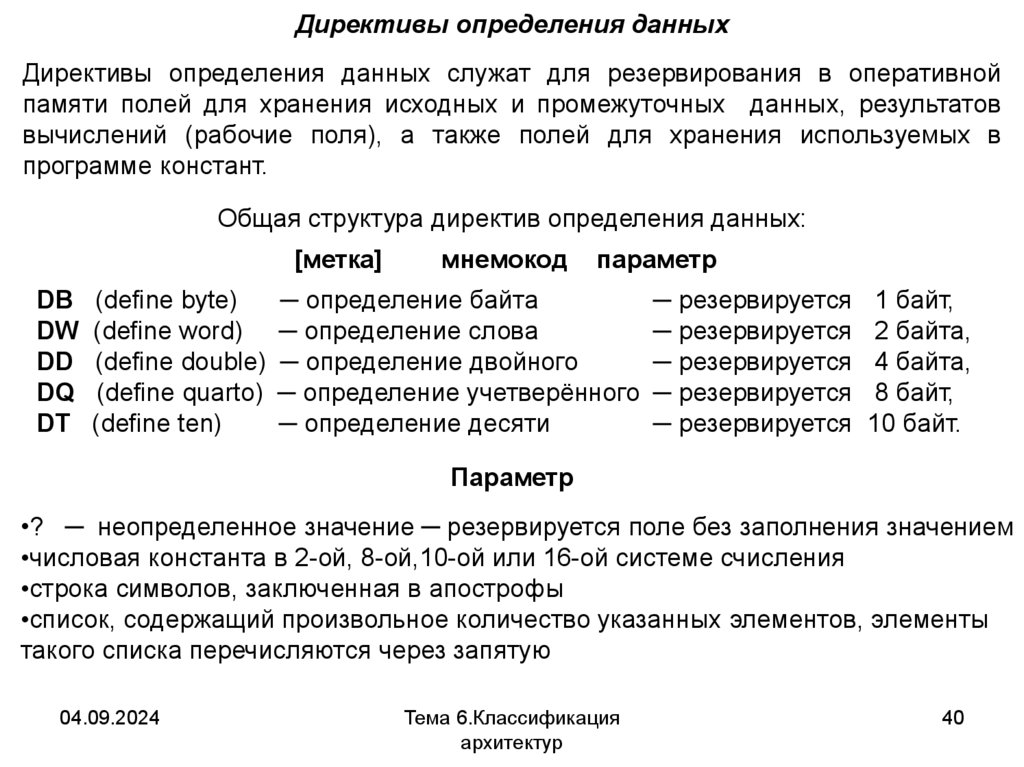

Директивы определения данныхДирективы определения данных служат для резервирования в оперативной

памяти полей для хранения исходных и промежуточных данных, результатов

вычислений (рабочие поля), а также полей для хранения используемых в

программе констант.

Общая структура директив определения данных:

[метка]

мнемокод

параметр

DB (define byte)

─ определение байта

─ резервируется 1 байт,

DW (define word) ─ определение слова

─ резервируется 2 байта,

DD (define double) ─ определение двойного

─ резервируется 4 байта,

DQ (define quarto) ─ определение учетверённого ─ резервируется 8 байт,

DT (define ten)

─ определение десяти

─ резервируется 10 байт.

Параметр

•? ─ неопределенное значение ─ резервируется поле без заполнения значением

•числовая константа в 2-ой, 8-ой,10-ой или 16-ой системе счисления

•строка символов, заключенная в апострофы

•список, содержащий произвольное количество указанных элементов, элементы

такого списка перечисляются через запятую

04.09.2024

Тема 6.Классификация

архитектур

40

41.

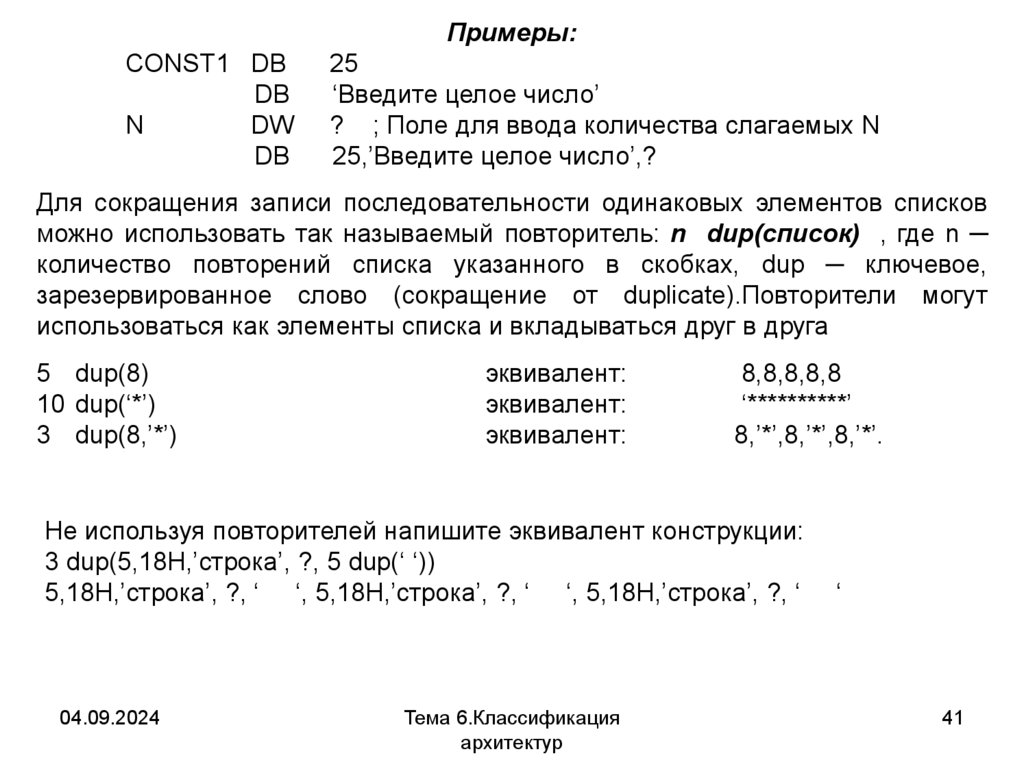

Примеры:CONST1 DB

DB

N

DW

DB

25

‘Введите целое число’

? ; Поле для ввода количества слагаемых N

25,’Введите целое число’,?

Для сокращения записи последовательности одинаковых элементов списков

можно использовать так называемый повторитель: n dup(список) , где n ─

количество повторений списка указанного в скобках, dup ─ ключевое,

зарезервированное слово (сокращение от duplicate).Повторители могут

использоваться как элементы списка и вкладываться друг в друга

5 dup(8)

10 dup(‘*’)

3 dup(8,’*’)

эквивалент:

эквивалент:

эквивалент:

8,8,8,8,8

‘**********’

8,’*’,8,’*’,8,’*’.

Не используя повторителей напишите эквивалент конструкции:

3 dup(5,18H,’строка’, ?, 5 dup(‘ ‘))

5,18H,’строка’, ?, ‘ ‘, 5,18H,’строка’, ?, ‘ ‘, 5,18H,’строка’, ?, ‘

04.09.2024

Тема 6.Классификация

архитектур

‘

41

42.

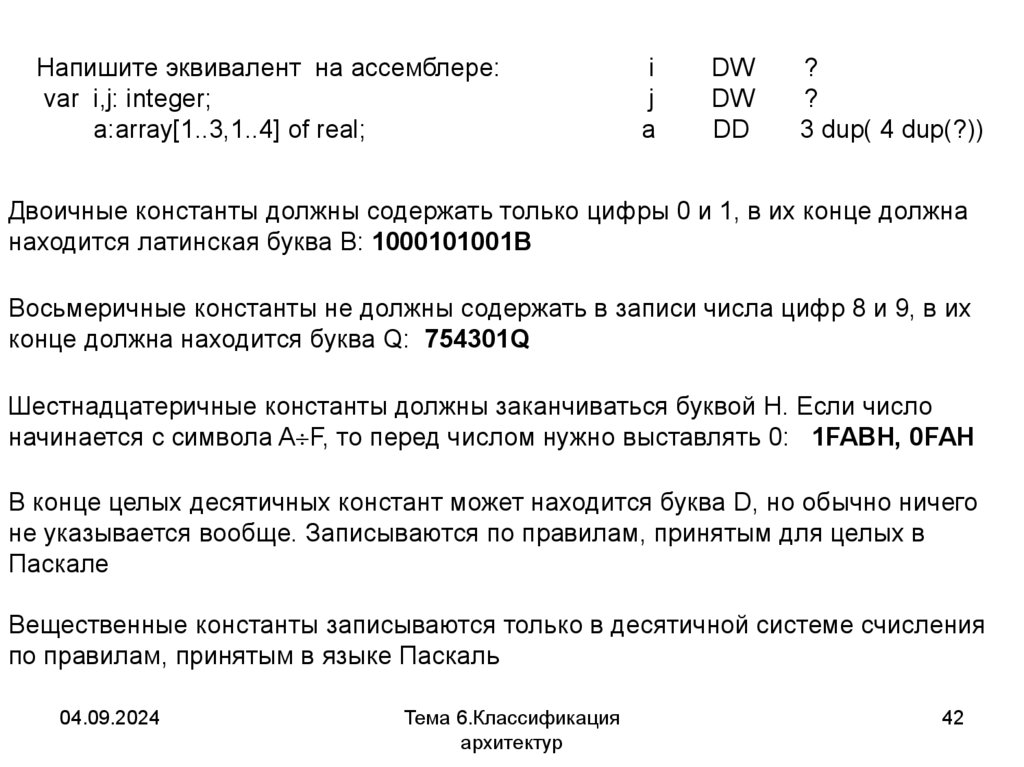

Напишите эквивалент на ассемблере:var i,j: integer;

a:array[1..3,1..4] of real;

i

j

a

DW

DW

DD

?

?

3 dup( 4 dup(?))

Двоичные константы должны содержать только цифры 0 и 1, в их конце должна

находится латинская буква B: 1000101001B

Восьмеричные константы не должны содержать в записи числа цифр 8 и 9, в их

конце должна находится буква Q: 754301Q

Шестнадцатеричные константы должны заканчиваться буквой Н. Если число

начинается с символа A F, то перед числом нужно выставлять 0: 1FABH, 0FAH

В конце целых десятичных констант может находится буква D, но обычно ничего

не указывается вообще. Записываются по правилам, принятым для целых в

Паскале

Вещественные константы записываются только в десятичной системе счисления

по правилам, принятым в языке Паскаль

04.09.2024

Тема 6.Классификация

архитектур

42

43.

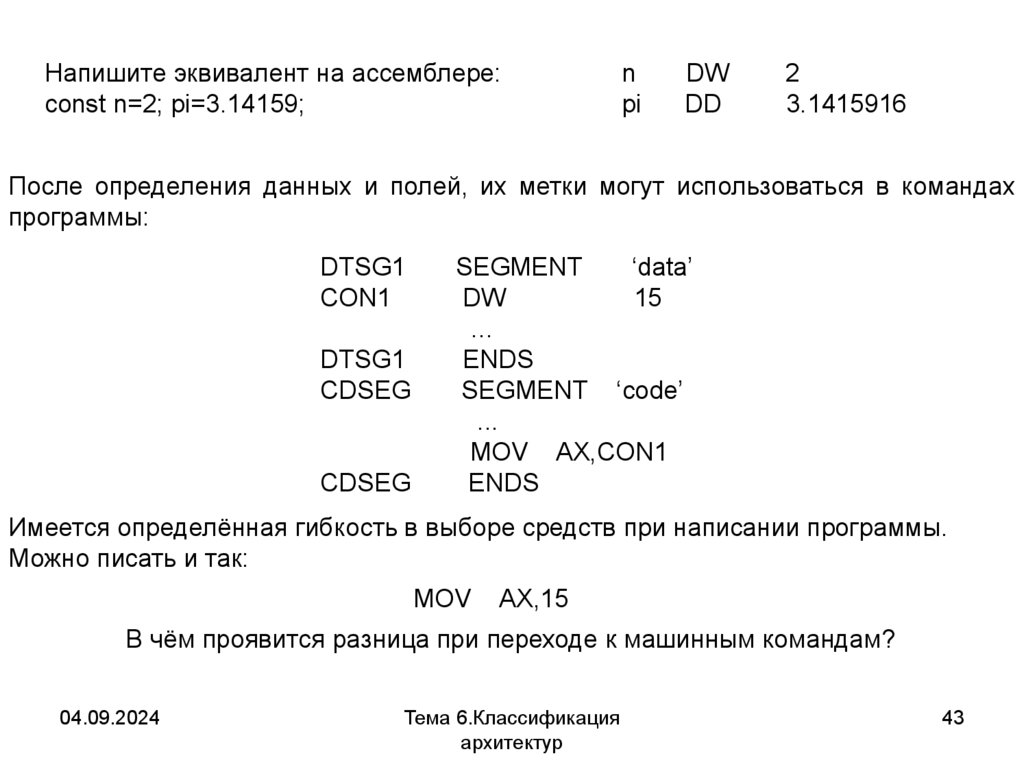

Напишите эквивалент на ассемблере:const n=2; pi=3.14159;

n

pi

DW

DD

2

3.1415916

После определения данных и полей, их метки могут использоваться в командах

программы:

DTSG1

CON1

DTSG1

CDSEG

CDSEG

SEGMENT

‘data’

DW

15

…

ENDS

SEGMENT ‘code’

...

MOV AX,CON1

ENDS

Имеется определённая гибкость в выборе средств при написании программы.

Можно писать и так:

MOV

AX,15

В чём проявится разница при переходе к машинным командам?

04.09.2024

Тема 6.Классификация

архитектур

43

44.

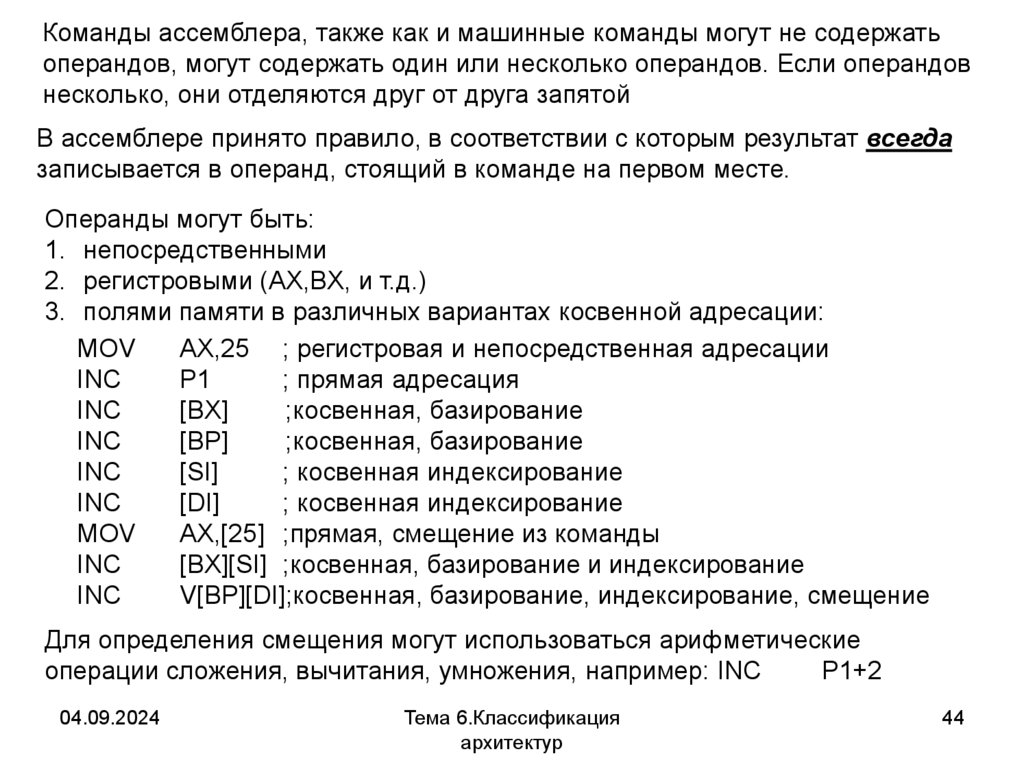

Команды ассемблера, также как и машинные команды могут не содержатьоперандов, могут содержать один или несколько операндов. Если операндов

несколько, они отделяются друг от друга запятой

В ассемблере принято правило, в соответствии с которым результат всегда

записывается в операнд, стоящий в команде на первом месте.

Операнды могут быть:

1. непосредственными

2. регистровыми (AX,BX, и т.д.)

3. полями памяти в различных вариантах косвенной адресации:

MOV

AX,25 ; регистровая и непосредственная адресации

INC

P1

; прямая адресация

INC

[BX]

;косвенная, базирование

INC

[BP]

;косвенная, базирование

INC

[SI]

; косвенная индексирование

INC

[DI]

; косвенная индексирование

MOV

AX,[25] ;прямая, смещение из команды

INC

[BX][SI] ;косвенная, базирование и индексирование

INC

V[BP][DI];косвенная, базирование, индексирование, смещение

Для определения смещения могут использоваться арифметические

операции сложения, вычитания, умножения, например: INC

P1+2

04.09.2024

Тема 6.Классификация

архитектур

44

45.

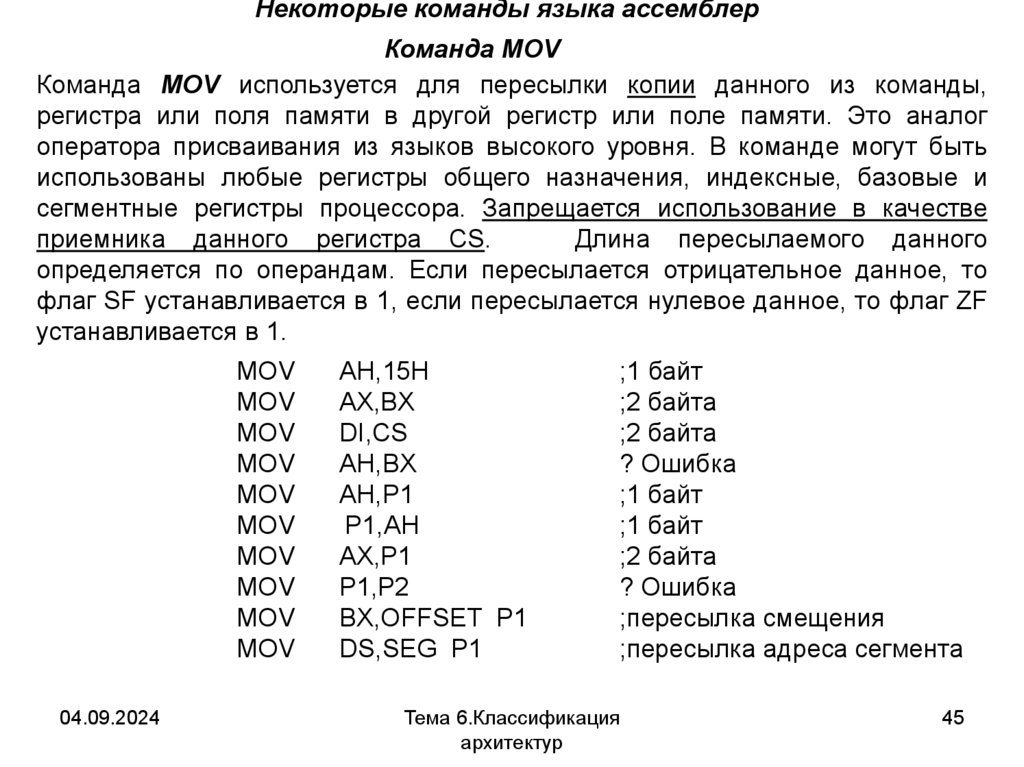

Некоторые команды языка ассемблерКоманда MOV

Команда MOV используется для пересылки копии данного из команды,

регистра или поля памяти в другой регистр или поле памяти. Это аналог

оператора присваивания из языков высокого уровня. В команде могут быть

использованы любые регистры общего назначения, индексные, базовые и

сегментные регистры процессора. Запрещается использование в качестве

приемника данного регистра CS.

Длина пересылаемого данного

определяется по операндам. Если пересылается отрицательное данное, то

флаг SF устанавливается в 1, если пересылается нулевое данное, то флаг ZF

устанавливается в 1.

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

MOV

04.09.2024

AH,15H

AX,BX

DI,CS

AH,BX

AH,P1

P1,AH

AX,P1

P1,P2

BX,OFFSET P1

DS,SEG P1

;1 байт

;2 байта

;2 байта

? Ошибка

;1 байт

;1 байт

;2 байта

? Ошибка

;пересылка смещения

;пересылка адреса сегмента

Тема 6.Классификация

архитектур

45

46.

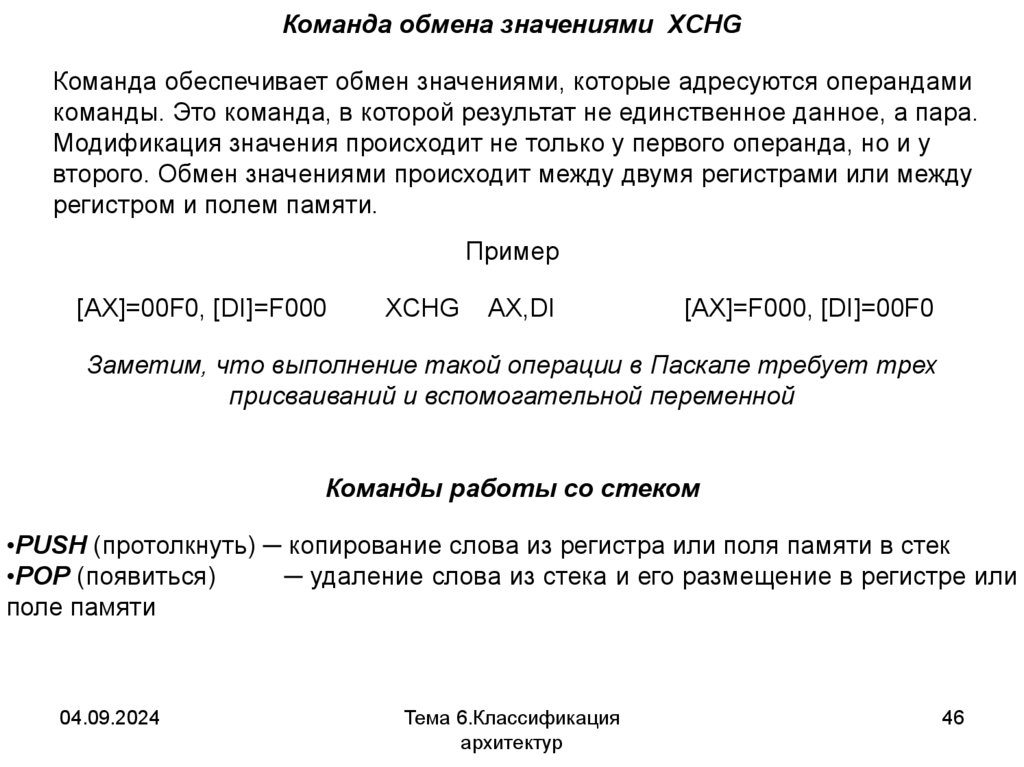

Команда обмена значениями XCHGКоманда обеспечивает обмен значениями, которые адресуются операндами

команды. Это команда, в которой результат не единственное данное, а пара.

Модификация значения происходит не только у первого операнда, но и у

второго. Обмен значениями происходит между двумя регистрами или между

регистром и полем памяти.

Пример

[AX]=00F0, [DI]=F000

XCHG

AX,DI

[AX]=F000, [DI]=00F0

Заметим, что выполнение такой операции в Паскале требует трех

присваиваний и вспомогательной переменной

Команды работы со стеком

•PUSH (протолкнуть) ─ копирование слова из регистра или поля памяти в стек

•POP (появиться)

─ удаление слова из стека и его размещение в регистре или

поле памяти

04.09.2024

Тема 6.Классификация

архитектур

46

47.

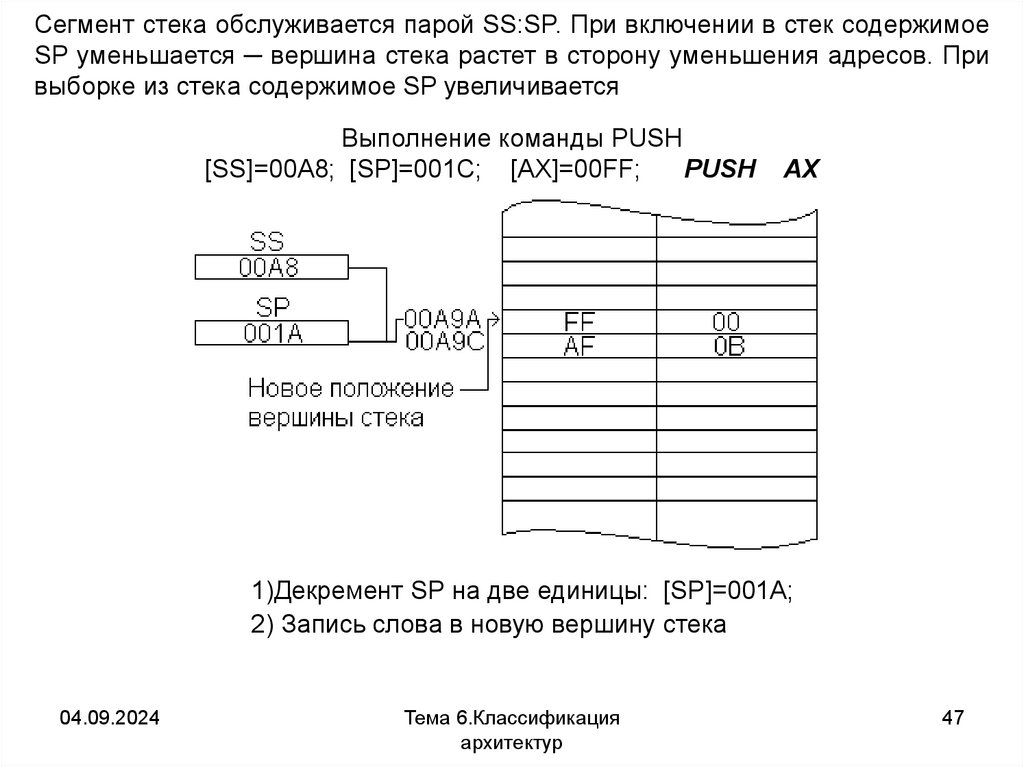

Сегмент стека обслуживается парой SS:SP. При включении в стек содержимоеSP уменьшается ─ вершина стека растет в сторону уменьшения адресов. При

выборке из стека содержимое SP увеличивается

Выполнение команды PUSH

[SS]=00A8; [SP]=001C; [AX]=00FF;

PUSH

AX

1)Декремент SP на две единицы: [SP]=001A;

2) Запись слова в новую вершину стека

04.09.2024

Тема 6.Классификация

архитектур

47

48.

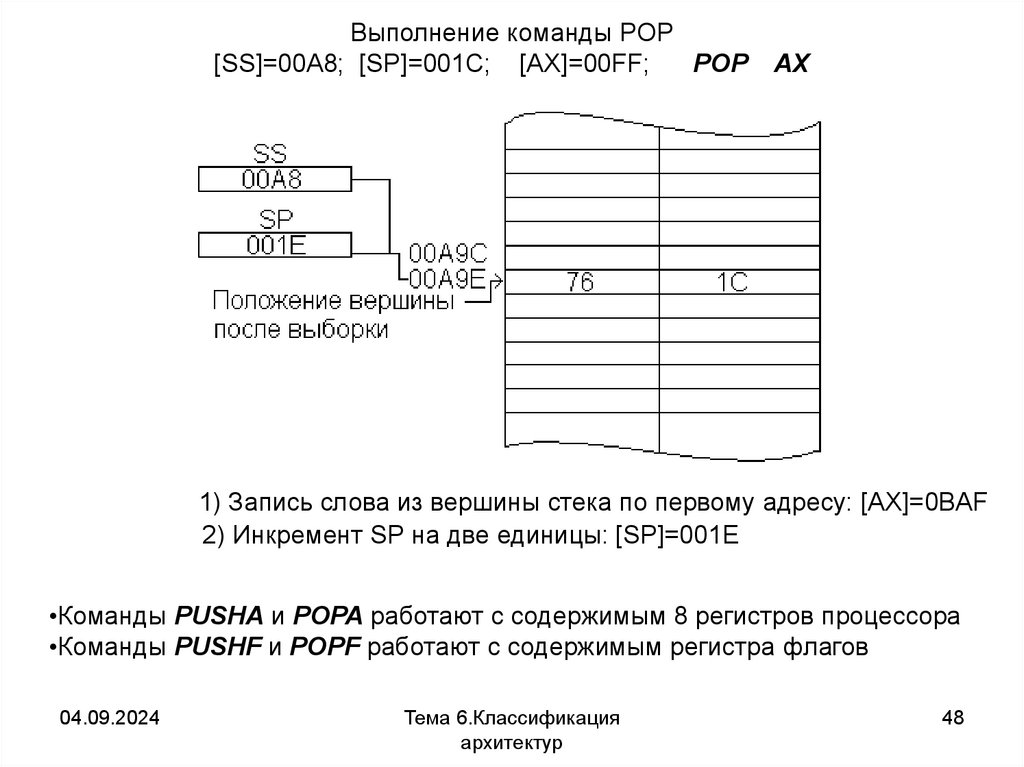

Выполнение команды POP[SS]=00A8; [SP]=001C; [AX]=00FF;

POP

AX

1) Запись слова из вершины стека по первому адресу: [AX]=0BAF

2) Инкремент SP на две единицы: [SP]=001E

•Команды PUSHA и POPA работают с содержимым 8 регистров процессора

•Команды PUSHF и POPF работают с содержимым регистра флагов

04.09.2024

Тема 6.Классификация

архитектур

48

49.

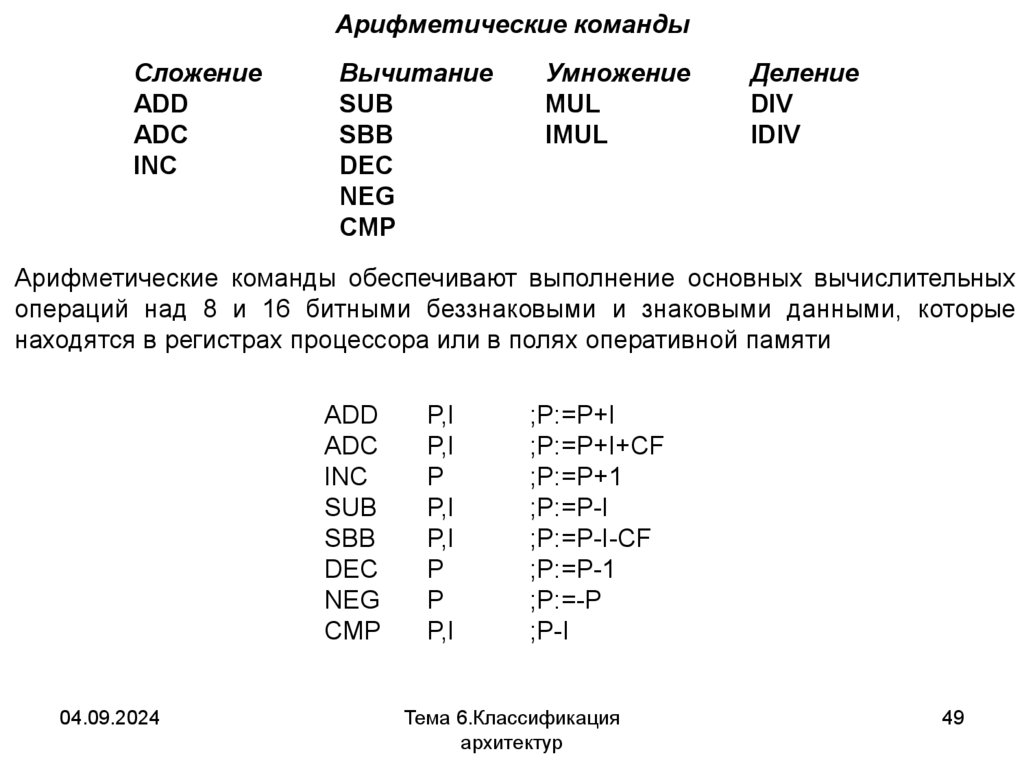

Арифметические командыСложение

ADD

ADC

INC

Вычитание

SUB

SBB

DEC

NEG

CMP

Умножение

MUL

IMUL

Деление

DIV

IDIV

Арифметические команды обеспечивают выполнение основных вычислительных

операций над 8 и 16 битными беззнаковыми и знаковыми данными, которые

находятся в регистрах процессора или в полях оперативной памяти

ADD

ADC

INC

SUB

SBB

DEC

NEG

CMP

04.09.2024

P,I

P,I

P

P,I

P,I

P

P

P,I

;P:=P+I

;P:=P+I+CF

;P:=P+1

;P:=P-I

;P:=P-I-CF

;P:=P-1

;P:=-P

;P-I

Тема 6.Классификация

архитектур

49

50.

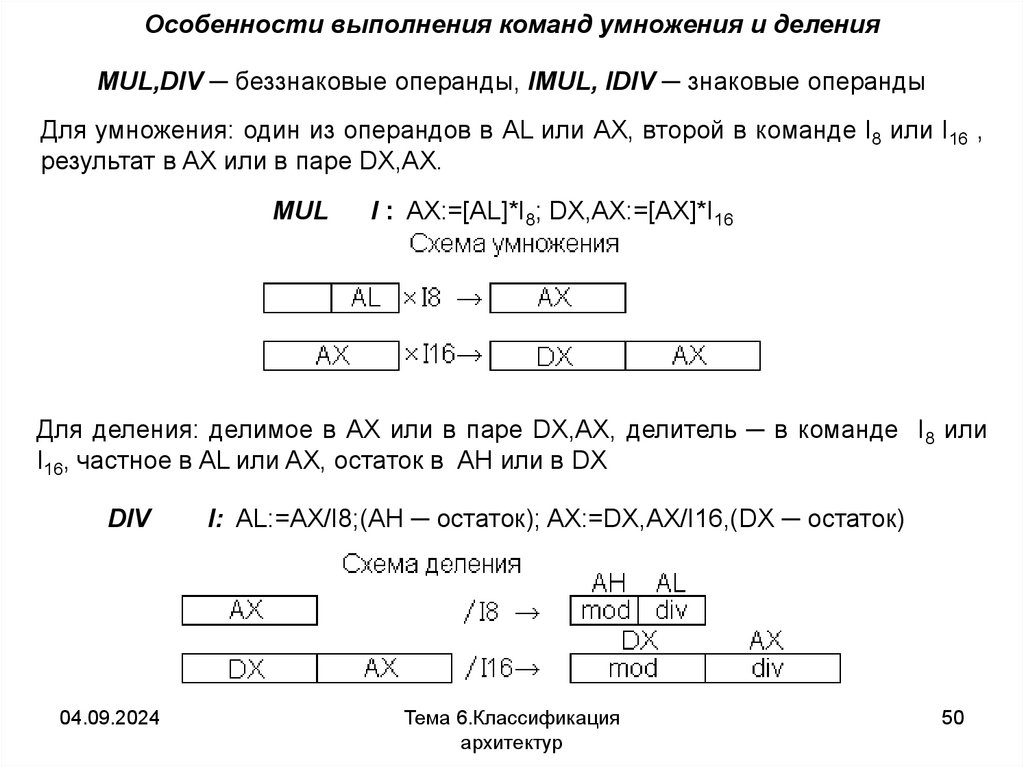

Особенности выполнения команд умножения и деленияMUL,DIV ─ беззнаковые операнды, IMUL, IDIV ─ знаковые операнды

Для умножения: один из операндов в AL или AX, второй в команде I8 или I16 ,

результат в AX или в паре DX,AX.

MUL

I : AX:=[AL]*I8; DX,AX:=[AX]*I16

Для деления: делимое в AX или в паре DX,AX, делитель ─ в команде I8 или

I16, частное в AL или AX, остаток в AH или в DX

DIV

04.09.2024

I: AL:=AX/I8;(AH ─ остаток); AX:=DX,AX/I16,(DX ─ остаток)

Тема 6.Классификация

архитектур

50

51.

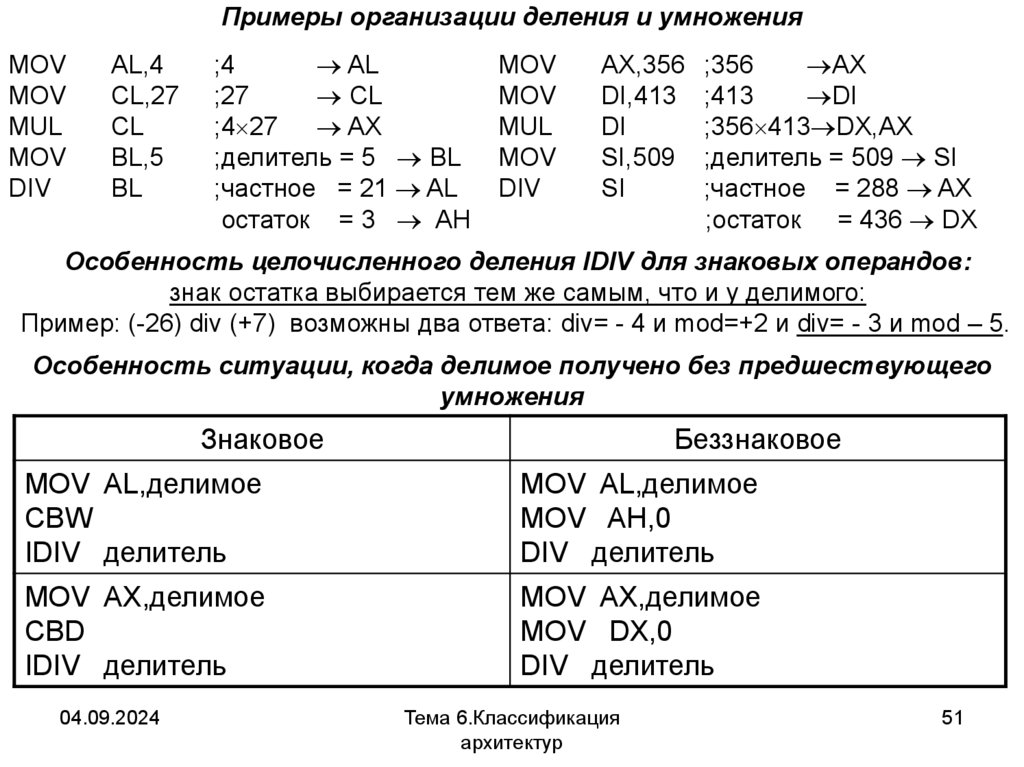

Примеры организации деления и умноженияMOV

MOV

MUL

MOV

DIV

AL,4

CL,27

CL

BL,5

BL

;4

AL

;27

CL

;4 27

AX

;делитель = 5 BL

;частное = 21 AL

остаток = 3 AH

MOV

MOV

MUL

MOV

DIV

AX,356

DI,413

DI

SI,509

SI

;356

AX

;413

DI

;356 413 DX,AX

;делитель = 509 SI

;частное = 288 AX

;остаток = 436 DX

Особенность целочисленного деления IDIV для знаковых операндов:

знак остатка выбирается тем же самым, что и у делимого:

Пример: (-26) div (+7) возможны два ответа: div= - 4 и mod=+2 и div= - 3 и mod – 5.

Особенность ситуации, когда делимое получено без предшествующего

умножения

Знаковое

Беззнаковое

MOV AL,делимое

CBW

IDIV делитель

MOV AL,делимое

MOV AH,0

DIV делитель

MOV AX,делимое

CBD

IDIV делитель

MOV AX,делимое

MOV DX,0

DIV делитель

04.09.2024

Тема 6.Классификация

архитектур

51

52.

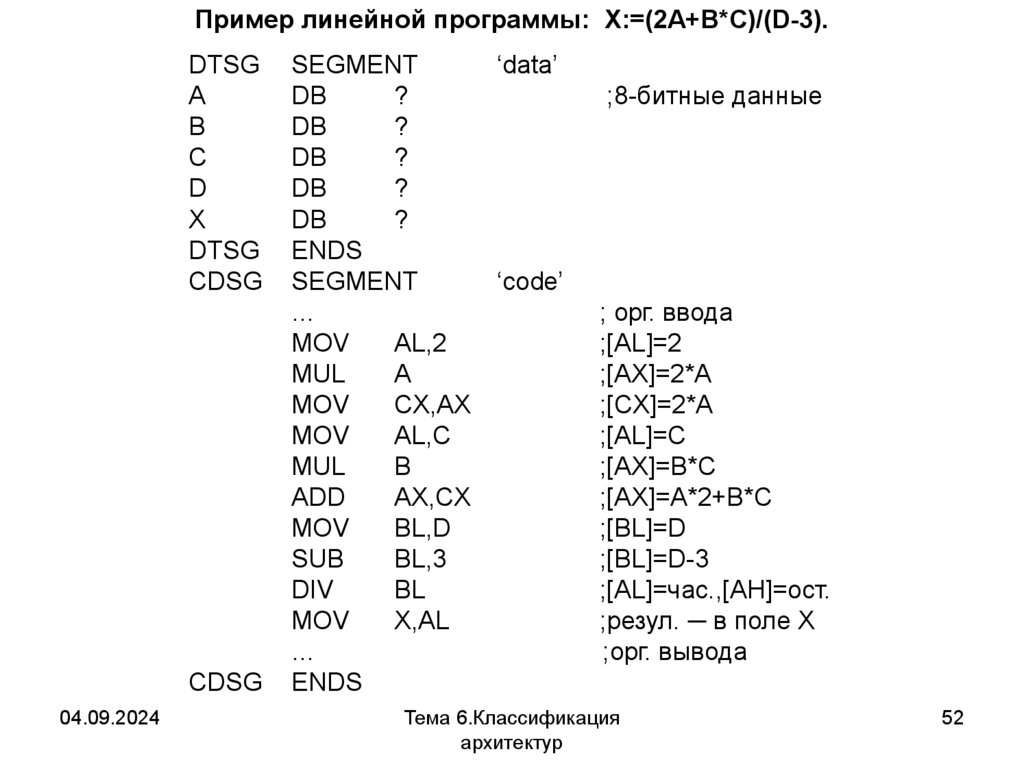

Пример линейной программы: X:=(2A+B*C)/(D-3).DTSG

A

B

C

D

X

DTSG

CDSG

CDSG

04.09.2024

SEGMENT

DB

?

DB

?

DB

?

DB

?

DB

?

ENDS

SEGMENT

…

MOV

AL,2

MUL

A

MOV

CX,AX

MOV

AL,C

MUL

B

ADD

AX,CX

MOV

BL,D

SUB

BL,3

DIV

BL

MOV

X,AL

…

ENDS

‘data’

;8-битные данные

‘code’

; орг. ввода

;[AL]=2

;[AX]=2*A

;[CX]=2*A

;[AL]=C

;[AX]=B*C

;[AX]=A*2+B*C

;[BL]=D

;[BL]=D-3

;[AL]=час.,[AH]=ост.

;резул. ─ в поле X

;орг. вывода

Тема 6.Классификация

архитектур

52

53.

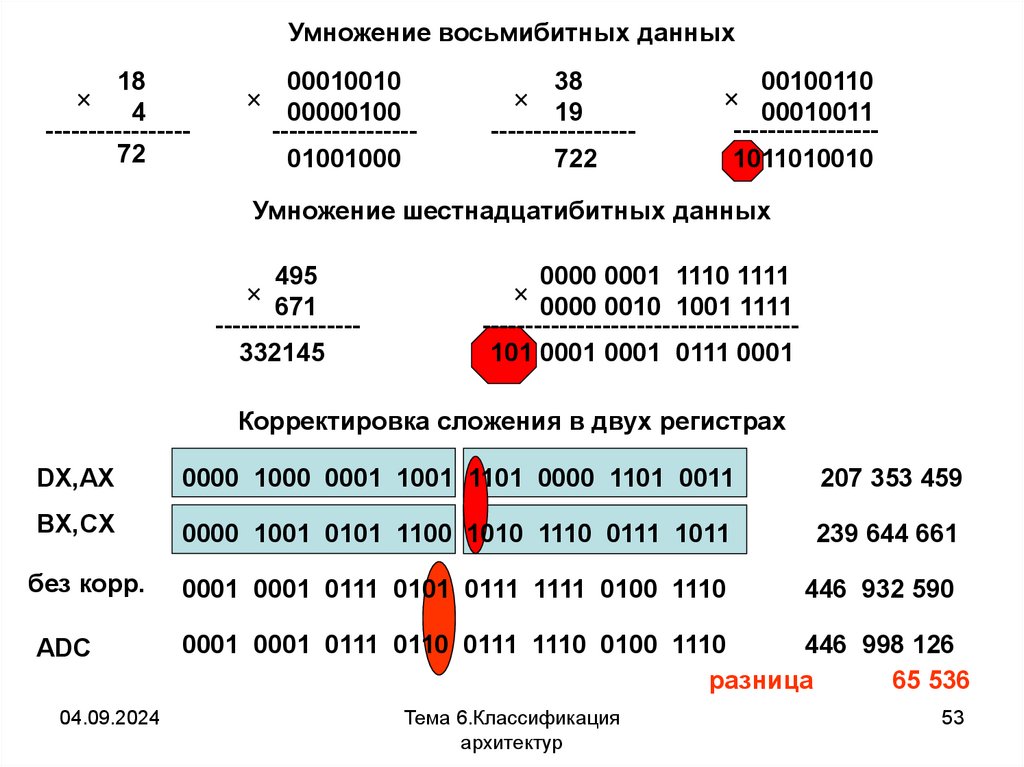

Умножение восьмибитных данных18

4

----------------72

00010010

00000100

----------------01001000

38

19

----------------722

00100110

00010011

----------------1011010010

Умножение шестнадцатибитных данных

495

671

----------------332145

0000 0001 1110 1111

0000 0010 1001 1111

------------------------------------101 0001 0001 0111 0001

Корректировка сложения в двух регистрах

DX,AX

0000 1000 0001 1001 1101 0000 1101 0011

207 353 459

BX,CX

0000 1001 0101 1100 1010 1110 0111 1011

239 644 661

без корр.

0001 0001 0111 0101 0111 1111 0100 1110

446 932 590

ADC

0001 0001 0111 0110 0111 1110 0100 1110

446 998 126

разница

65 536

04.09.2024

Тема 6.Классификация

архитектур

53

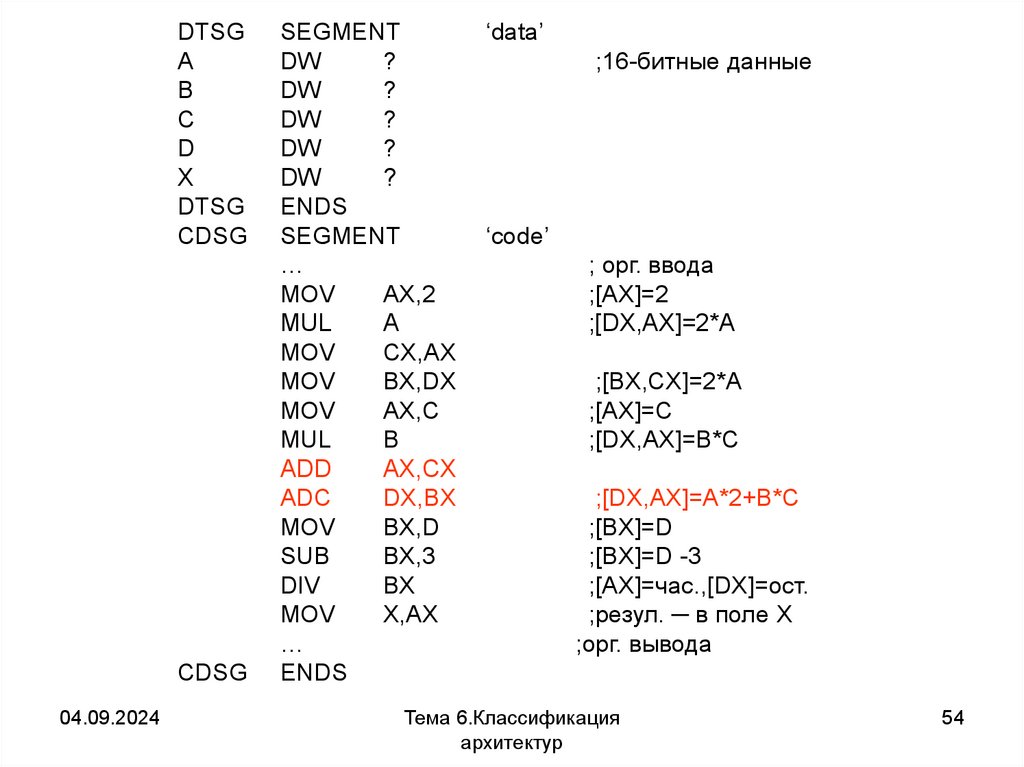

54.

DTSGA

B

C

D

X

DTSG

CDSG

CDSG

04.09.2024

SEGMENT

DW

?

DW

?

DW

?

DW

?

DW

?

ENDS

SEGMENT

…

MOV

AX,2

MUL

A

MOV

CX,AX

MOV

BX,DX

MOV

AX,C

MUL

B

ADD

AX,CX

ADC

DX,BX

MOV

BX,D

SUB

BX,3

DIV

BX

MOV

X,AX

…

ENDS

‘data’

;16-битные данные

‘code’

; орг. ввода

;[AX]=2

;[DX,AX]=2*A

;[BX,CX]=2*A

;[AX]=C

;[DX,AX]=B*C

;[DX,AX]=A*2+B*C

;[BX]=D

;[BX]=D -3

;[AX]=час.,[DX]=ост.

;резул. ─ в поле X

;орг. вывода

Тема 6.Классификация

архитектур

54

55.

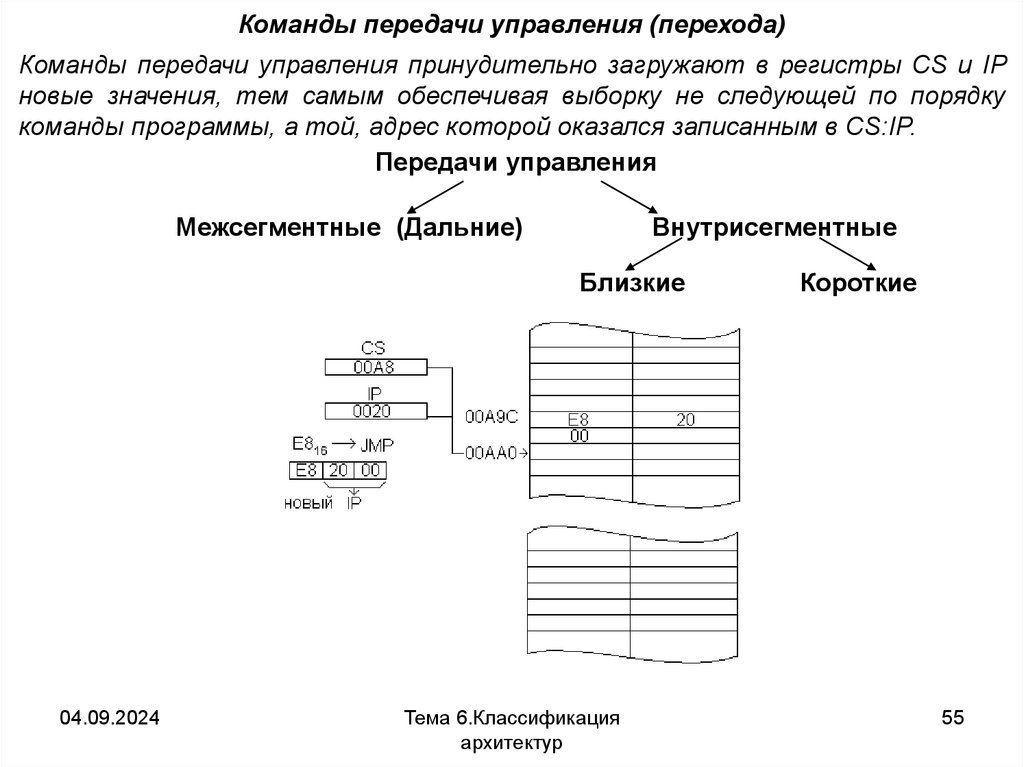

Команды передачи управления (перехода)Команды передачи управления принудительно загружают в регистры CS и IP

новые значения, тем самым обеспечивая выборку не следующей по порядку

команды программы, а той, адрес которой оказался записанным в CS:IP.

Передачи управления

Межсегментные (Дальние)

Внутрисегментные

Близкие

04.09.2024

Тема 6.Классификация

архитектур

Короткие

55

56.

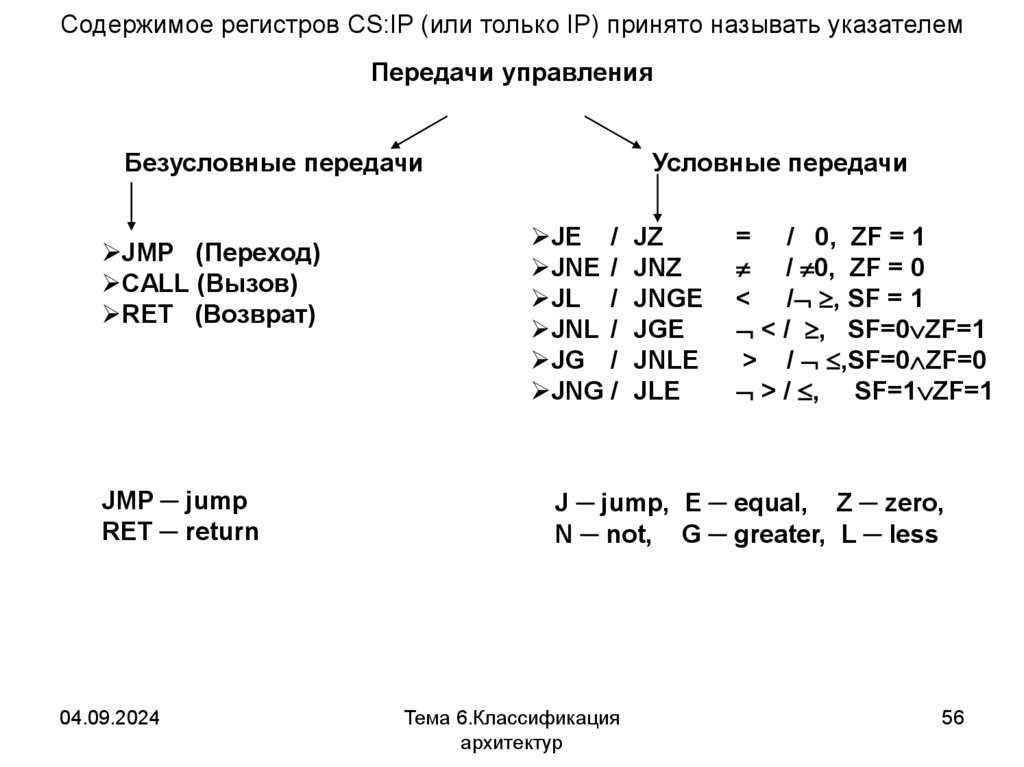

Содержимое регистров CS:IP (или только IP) принято называть указателемПередачи управления

Безусловные передачи

JMP (Переход)

CALL (Вызов)

RET (Возврат)

JMP ─ jump

RET ─ return

04.09.2024

Условные передачи

JE / JZ

JNE / JNZ

JL / JNGE

JNL / JGE

JG / JNLE

JNG / JLE

= / 0, ZF = 1

/ 0, ZF = 0

< / , SF = 1

< / , SF=0 ZF=1

> / ,SF=0 ZF=0

> / , SF=1 ZF=1

J ─ jump, E ─ equal, Z ─ zero,

N ─ not, G ─ greater, L ─ less

Тема 6.Классификация

архитектур

56

57.

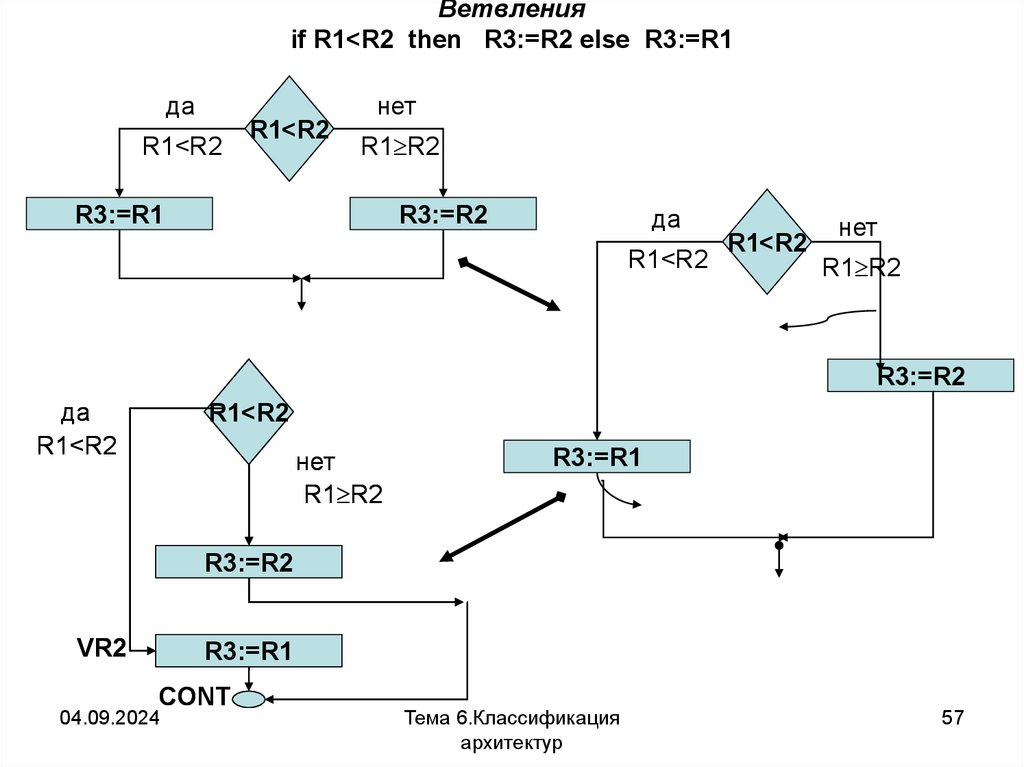

Ветвленияif R1<R2 then R3:=R2 else R3:=R1

да

нет

R1<R2

R1<R2

R1 R2

R3:=R1

да

R3:=R2

R1<R2

R1<R2

нет

R1 R2

R3:=R2

да

R1<R2

R1<R2

нет

R1 R2

R3:=R1

R3:=R2

VR2

R3:=R1

CONT

04.09.2024

Тема 6.Классификация

архитектур

57

58.

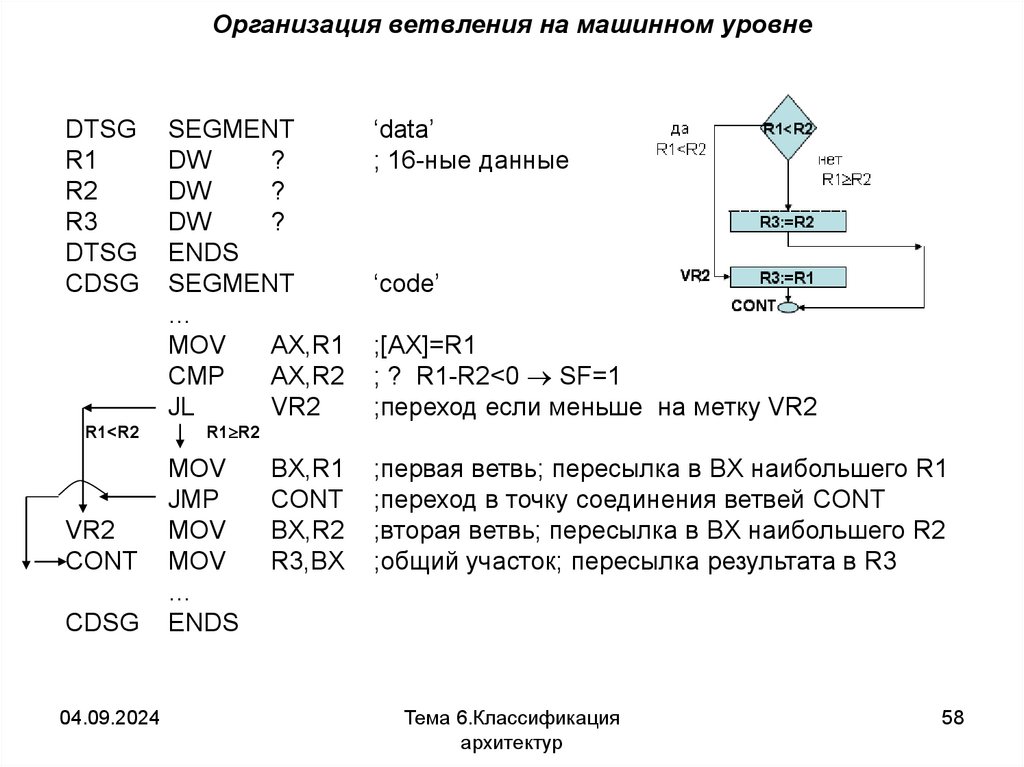

Организация ветвления на машинном уровнеDTSG

R1

R2

R3

DTSG

CDSG

R1<R2

VR2

CONT

CDSG

04.09.2024

SEGMENT

DW

?

DW

?

DW

?

ENDS

SEGMENT

…

MOV

AX,R1

CMP

AX,R2

JL

VR2

‘data’

; 16-ные данные

‘code’

;[AX]=R1

; ? R1-R2<0 SF=1

;переход если меньше на метку VR2

R1 R2

MOV

JMP

MOV

MOV

…

ENDS

BX,R1

CONT

BX,R2

R3,BX

;первая ветвь; пересылка в BX наибольшего R1

;переход в точку соединения ветвей CONT

;вторая ветвь; пересылка в BX наибольшего R2

;общий участок; пересылка результата в R3

Тема 6.Классификация

архитектур

58

59.

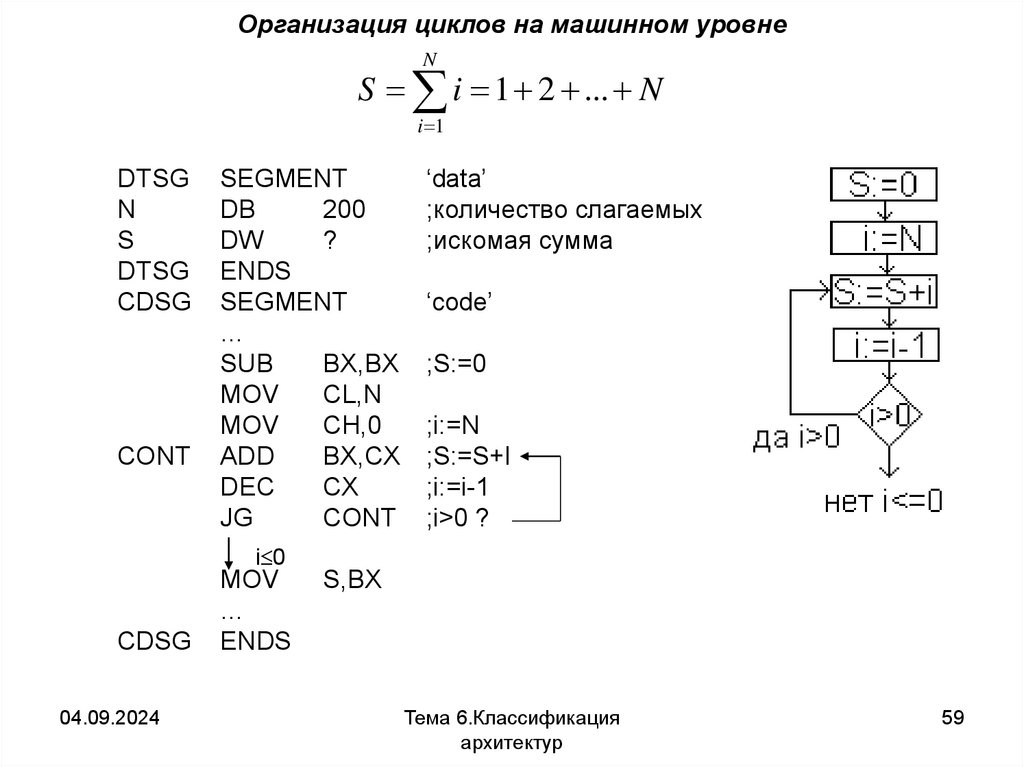

Организация циклов на машинном уровнеN

S i 1 2 ... N

i 1

DTSG

N

S

DTSG

CDSG

CONT

SEGMENT

DB

200

DW

?

ENDS

SEGMENT

…

SUB

BX,BX

MOV

CL,N

MOV

CH,0

ADD

BX,CX

DEC

CX

JG

CONT

‘data’

;количество слагаемых

;искомая сумма

‘code’

;S:=0

;i:=N

;S:=S+I

;i:=i-1

;i>0 ?

i 0

CDSG

04.09.2024

MOV

…

ENDS

S,BX

Тема 6.Классификация

архитектур

59

60.

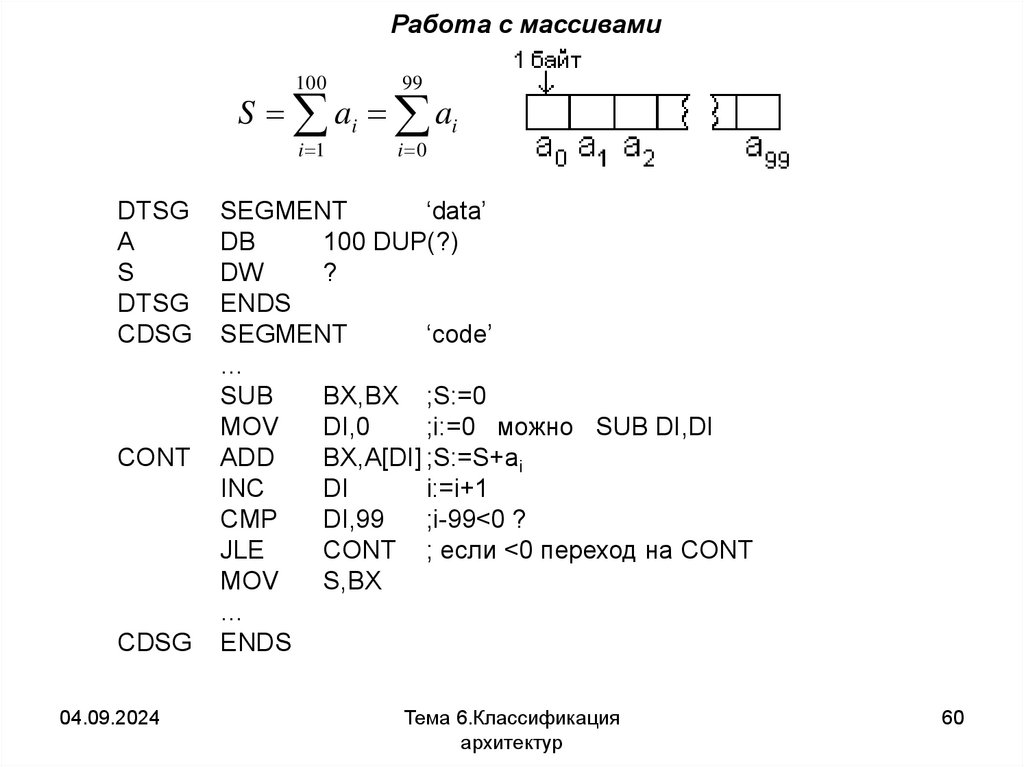

Работа с массивами100

99

i 1

i 0

S ai ai

DTSG

A

S

DTSG

CDSG

CONT

CDSG

04.09.2024

SEGMENT

‘data’

DB

100 DUP(?)

DW

?

ENDS

SEGMENT

‘code’

…

SUB

BX,BX ;S:=0

MOV

DI,0

;i:=0 можно SUB DI,DI

ADD

BX,A[DI] ;S:=S+ai

INC

DI

i:=i+1

CMP

DI,99

;i-99<0 ?

JLE

CONT ; если <0 переход на CONT

MOV

S,BX

…

ENDS

Тема 6.Классификация

архитектур

60

61.

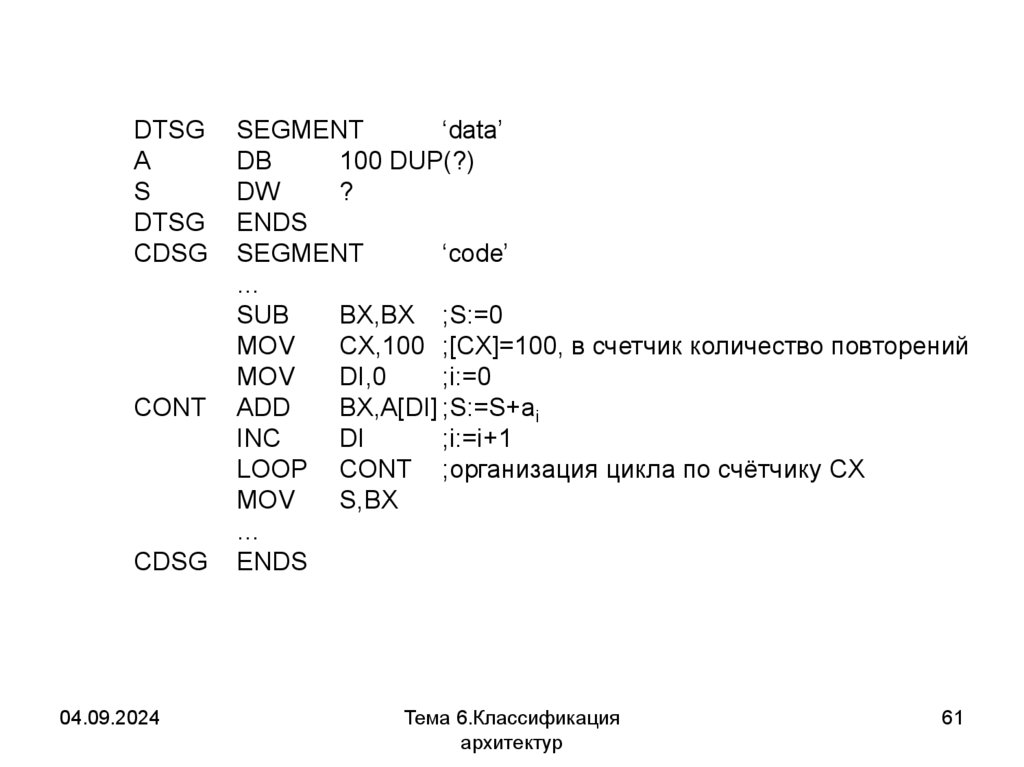

DTSGA

S

DTSG

CDSG

CONT

CDSG

04.09.2024

SEGMENT

‘data’

DB

100 DUP(?)

DW

?

ENDS

SEGMENT

‘code’

…

SUB

BX,BX ;S:=0

MOV

CX,100 ;[CX]=100, в счетчик количество повторений

MOV

DI,0

;i:=0

ADD

BX,A[DI] ;S:=S+ai

INC

DI

;i:=i+1

LOOP CONT ;организация цикла по счётчику CX

MOV

S,BX

…

ENDS

Тема 6.Классификация

архитектур

61

62.

Понятие прерыванияСпособы взаимодействия между процессором и внешними устройствами

во время обмена данными: опрос (полинг) и прерывания.

Опрос представляет собой периодическое прекращение текущей работы

процессора и посылка запросов со стороны процессора каждому из внешних

устройств на возможность или необходимость выполнения операций по обмену.

Запрос на выполнение операций по обмену, посылаемый процессору со стороны

внешних устройств или выполняющейся программы, называется прерыванием.

Для обработки поступившего сигнала прерывания процессор прекращает

выполнение текущей программы и переходит к выполнению другой,

специализированной программы, которая и обеспечивает выполнение

запрошенных в прерывании действий. После обработки прерывания, то есть

после правильного или не правильного, полного или не полного выполнения,

или же после установления факта невозможности

выполнения действий

запроса, процессор может вернуться к выполнению прерванной программы.

04.09.2024

Тема 6.Классификация

архитектур

62

63.

Прерывания бывают маскируемые и немаскируемые. Обработка маскируемыхпрерываний может быть отложена или вообще запрещена. Обработку

немаскируемых прерываний отложить или же запретить невозможно.

Для приема сигналов прерываний от внешних устройств процессора 8086

имеется два входа: вход INTR (INTeRrupt) и вход NMI (Not Masked Interrupt).

При поступлении сигнала прерывания на вход NMI процессор завершает

выполнение текущей команды программы, фиксирует свое текущее состояние и

после этого начинает обработку поступившего запроса.

При поступлении запроса на вход INTR реакция процессора зависит от

состояния флажка IF регистра флагов. Если IF=0, то прерывание не разрешено,

замаскировано и процессор никак не реагирует на появление запроса на

прерывание. Если IF=1, то прерывание разрешено, не замаскировано и

процессор обрабатывает запрос на такое прерывание точно также, как и

проступившее по входу NMI.

Дополнительная информация о прерывании поступает в процессор в виде

целочисленного кода n, 0 n 255, который называется типом (номером)

прерывания. Все прерывания, поступающие на вход NMI, имеют код (относятся

к типу) 2. Прерывания с кодом n 2 поступают на вход INTR, и, следовательно,

они могут быть замаскированы.

04.09.2024

Тема 6.Классификация

архитектур

63

64.

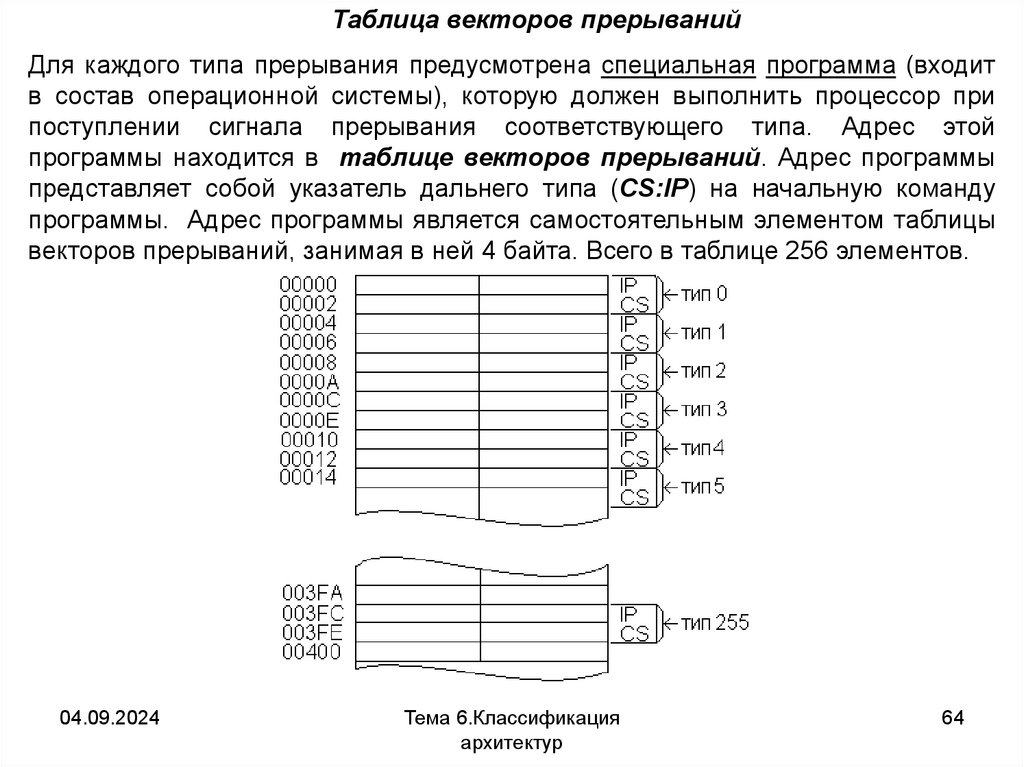

Таблица векторов прерыванийДля каждого типа прерывания предусмотрена специальная программа (входит

в состав операционной системы), которую должен выполнить процессор при

поступлении сигнала прерывания соответствующего типа. Адрес этой

программы находится в таблице векторов прерываний. Адрес программы

представляет собой указатель дальнего типа (CS:IP) на начальную команду

программы. Адрес программы является самостоятельным элементом таблицы

векторов прерываний, занимая в ней 4 байта. Всего в таблице 256 элементов.

04.09.2024

Тема 6.Классификация

архитектур

64

65.

Действия процессора при поступлении незамаскированного прерывания:1. завершает выполнение текущей команды выполняемой программы;

2. cбрасывает флаг IF в состояние 0;

3. запоминает в стеке содержимое всех регистров (РОН, индексных, базовых);

4. запоминает в стеке содержимое регистра флагов;

5. запоминает в стеке адрес следующей команды выполняемой программы;

6. запрашивает у внешнего источника тип прерывания n;

7. выбирает из таблицы векторов прерываний адрес программы обработки

прерывания, соответствующий полученному типу прерывания, и загружает

его в регистры CS:IP.

Классы прерываний: внешние (аппаратные, прерывания ввода\вывода),

внутренние ( программные, исключительные ситуации).

Некоторые типы прерываний:

Тип 0 ─ деление на нуль;

Тип 1 ─ пошаговая работа (трассировка);

Тип 2 ─ немаскируемое прерывание;

Тип 3 ─ прерывание из программы с помощью однобайтной команды INT;

Тип 4 ─ переполнение порядка при работе со знаковым операндом;

Тип 5 ─ выход индекса за границу;

Тип 6 ─ недействительный код операции и т.д.

04.09.2024

Тема 6.Классификация

архитектур

65

66.

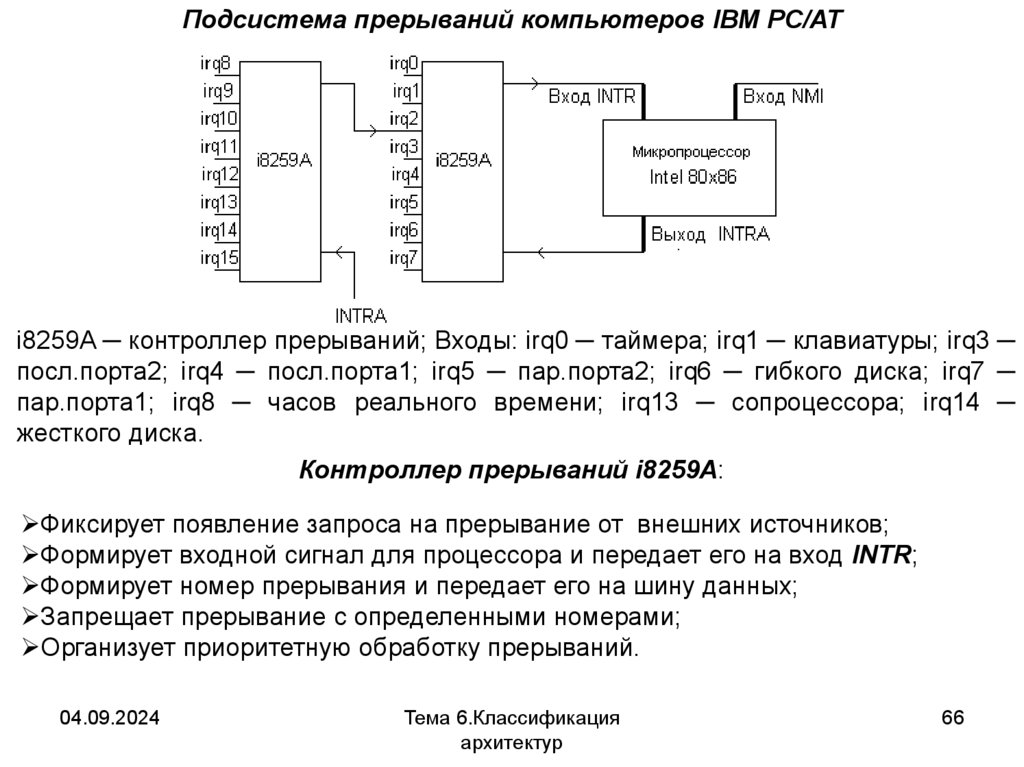

Подсистема прерываний компьютеров IBM PC/ATi8259A ─ контроллер прерываний; Входы: irq0 ─ таймера; irq1 ─ клавиатуры; irq3 ─

посл.порта2; irq4 ─ посл.порта1; irq5 ─ пар.порта2; irq6 ─ гибкого диска; irq7 ─

пар.порта1; irq8 ─ часов реального времени; irq13 ─ сопроцессора; irq14 ─

жесткого диска.

Контроллер прерываний i8259A:

Фиксирует появление запроса на прерывание от внешних источников;

Формирует входной сигнал для процессора и передает его на вход INTR;

Формирует номер прерывания и передает его на шину данных;

Запрещает прерывание с определенными номерами;

Организует приоритетную обработку прерываний.

04.09.2024

Тема 6.Классификация

архитектур

66

67.

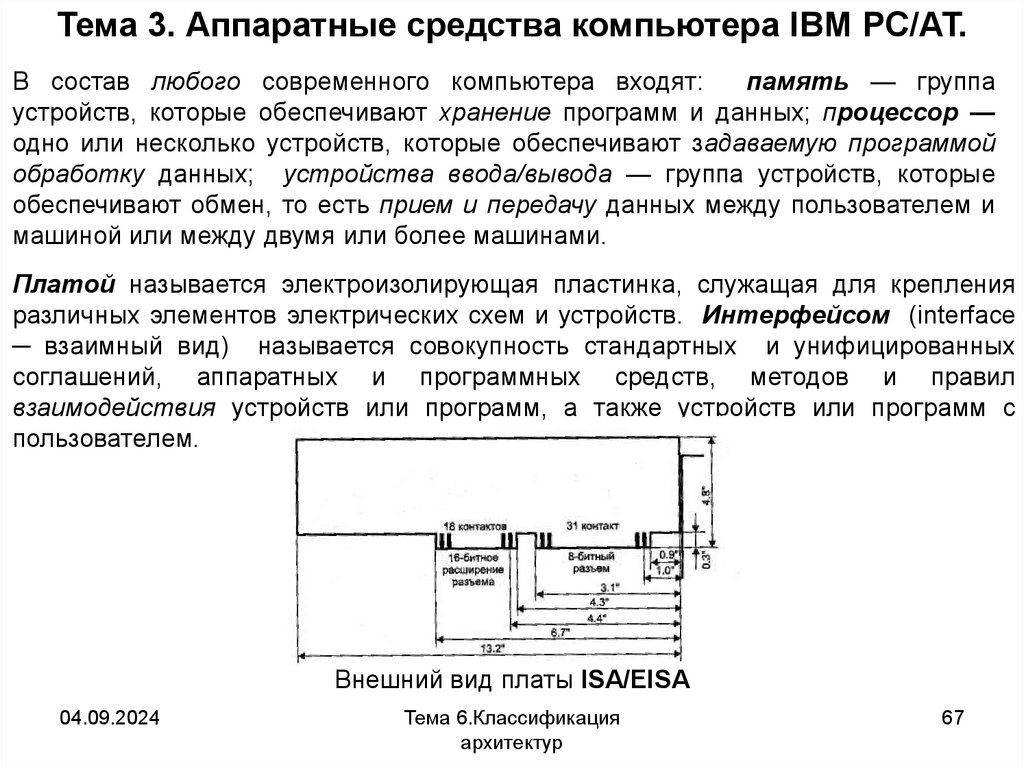

Тема 3. Аппаратные средства компьютера IBM PC/AT.В состав любого современного компьютера входят:

память — группа

устройств, которые обеспечивают хранение программ и данных; процессор —

одно или несколько устройств, которые обеспечивают задаваемую программой

обработку данных; устройства ввода/вывода — группа устройств, которые

обеспечивают обмен, то есть прием и передачу данных между пользователем и

машиной или между двумя или более машинами.

Платой называется электроизолирующая пластинка, служащая для крепления

различных элементов электрических схем и устройств. Интерфейсом (interface

─ взаимный вид) называется совокупность стандартных и унифицированных

соглашений, аппаратных и программных средств, методов и правил

взаимодействия устройств или программ, а также устройств или программ с

пользователем.

Внешний вид платы ISA/EISA

04.09.2024

Тема 6.Классификация

архитектур

67

68.

Память компьютераПамять предназначена для хранения программ

используется во всех подсистемах компьютера.

и

данных.

Память

Технические характеристики памяти

объём;

тип микросхем;

быстродействие;

скорость обмена (или производительность);

удельная стоимость;

достоверность хранения данных.

04.09.2024

Тема 6.Классификация

архитектур

68

69.

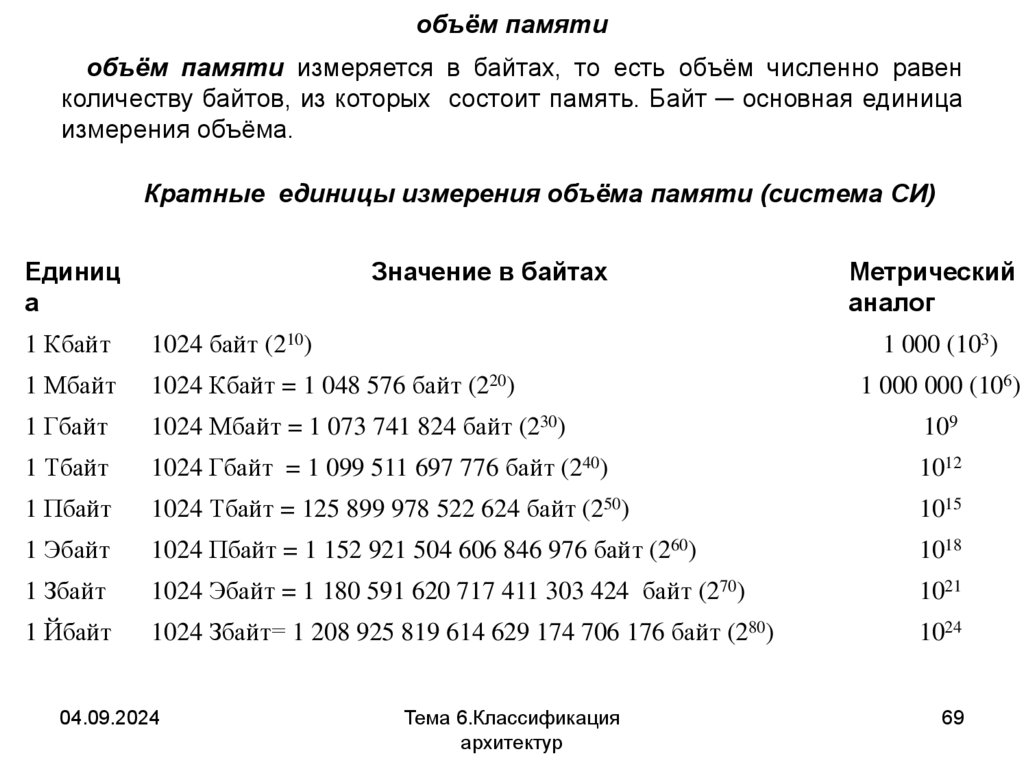

объём памятиобъём памяти измеряется в байтах, то есть объём численно равен

количеству байтов, из которых состоит память. Байт ─ основная единица

измерения объёма.

Кратные единицы измерения объёма памяти (система СИ)

Единиц

а

Значение в байтах

Метрический

аналог

1 Кбайт

1024 байт (210)

1 Мбайт

1024 Кбайт = 1 048 576 байт (220)

1 Гбайт

1024 Мбайт = 1 073 741 824 байт (230)

109

1 Тбайт

1024 Гбайт = 1 099 511 697 776 байт (240)

1012

1 Пбайт

1024 Тбайт = 125 899 978 522 624 байт (250)

1015

1 Эбайт

1024 Пбайт = 1 152 921 504 606 846 976 байт (260)

1018

1 Збайт

1024 Эбайт = 1 180 591 620 717 411 303 424 байт (270)

1021

1 Йбайт

1024 Збайт= 1 208 925 819 614 629 174 706 176 байт (280)

1024

04.09.2024

1 000 (103)

Тема 6.Классификация

архитектур

1 000 000 (106)

69

70.

Тип микросхем памяти определяется физическим внутренним устройствоммикросхемы. От типа микросхемы, в основном, зависят быстродействие и

скорость обмена памяти, которые в свою очередь оказывают существенное

влияние на общее быстродействие компьютера.

Быстродействие памяти определяется временем, затрачиваемым на

выполнение операций записи и считывания данных в память. Чем меньше это

время, тем быстрее память. Быстродействие зависит от времени доступа и

длительности цикла памяти.

Время доступа памяти представляет собой задержку начала получения

данных из памяти относительно появления запроса на них и измеряется в

секундах, точнее в долях секунды — наносекундах (милли=10-3 ─ тысячная

доля, микро=10-6 ─ миллионная доля, нано=10-9 ─ миллиардная доля

секунды). Типичное время доступа 5–10 нс.

Длительность цикла памяти определяется как минимальный период

следующих друг за другом обращений к памяти для выполнения чтения или

записи. В цикл памяти кроме выполнения чтения или записи входит фаза

восстановления, то есть возврата памяти к исходному состоянию. Циклы

чтения и циклы записи могут быть различными по длительности. Циклы

памяти также измеряются в наносекундах.

04.09.2024

Тема 6.Классификация

архитектур

70

71.

Скорость обмена равна объёму передаваемых памятью данных вединицу времени, измеряется в Мбайт/с. Чем меньше время доступа и

больше скорость обмена у данного типа оперативной памяти, тем выше

общее быстродействие компьютера и тем лучше рассматриваемый тип

памяти.

Разрядность шины памяти (системной шины) — количество байт или

бит, с которыми операция чтения или записи может быть выполнена

одновременно.

Тактовая частота шины памяти, системной шины — количество тактов

работы шины в единицу времени.

Удельная стоимость определяется как стоимость хранения одного байта

(килобайта, мегабайта). Обычно измеряется в рублях (евро, долларах) на 1

Мбайт.

Достоверность данных определяется вероятностью появления ошибки

во время обмена или хранения данных в памяти.

04.09.2024

Тема 6.Классификация

архитектур

71

72.

Обнаружение и исправление ошибок.Во время хранения и передачи информации большую практическую важность

имеет задача защиты информации от искажения, которая решается с

помощью специальных методов кодирования информации. Существуют

способы кодирования, позволяющие установить факт появления ошибки ─

обнаружение ошибки, и способы, обеспечивающие и обнаружение и

исправление ошибок.

Общим методом обеспечения надежности хранения и передачи информации

в компьютере и по линиям связи является включение в код дополнительных

контрольных разрядов (битов).

Общепринятый способ, обеспечивающий обнаружение одиночной ошибки. В

каждый байт включается один контрольный разряд, с помощью которого

проводится проверка на нечетность по правилу: количество единиц в байте

(включая контрольный разряд) должно быть нечетным.

04.09.2024

Тема 6.Классификация

архитектур

72

73.

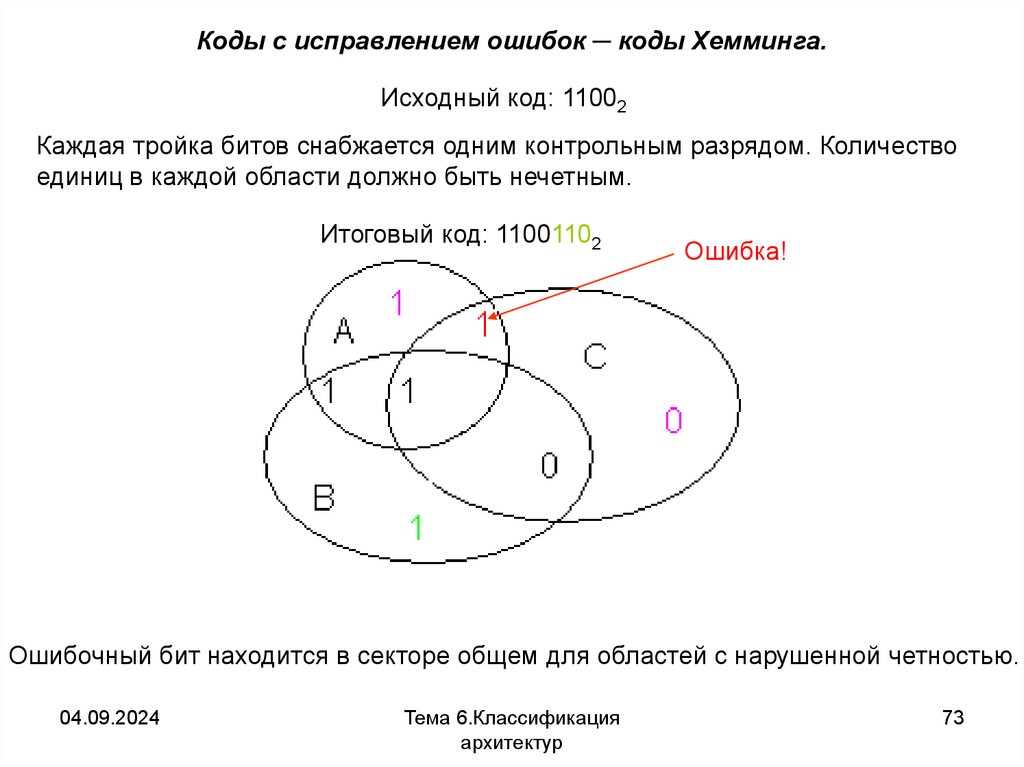

Коды с исправлением ошибок ─ коды Хемминга.Исходный код: 11002

Каждая тройка битов снабжается одним контрольным разрядом. Количество

единиц в каждой области должно быть нечетным.

Итоговый код: 11001102

Ошибка!

Ошибочный бит находится в секторе общем для областей с нарушенной четностью.

04.09.2024

Тема 6.Классификация

архитектур

73

74.

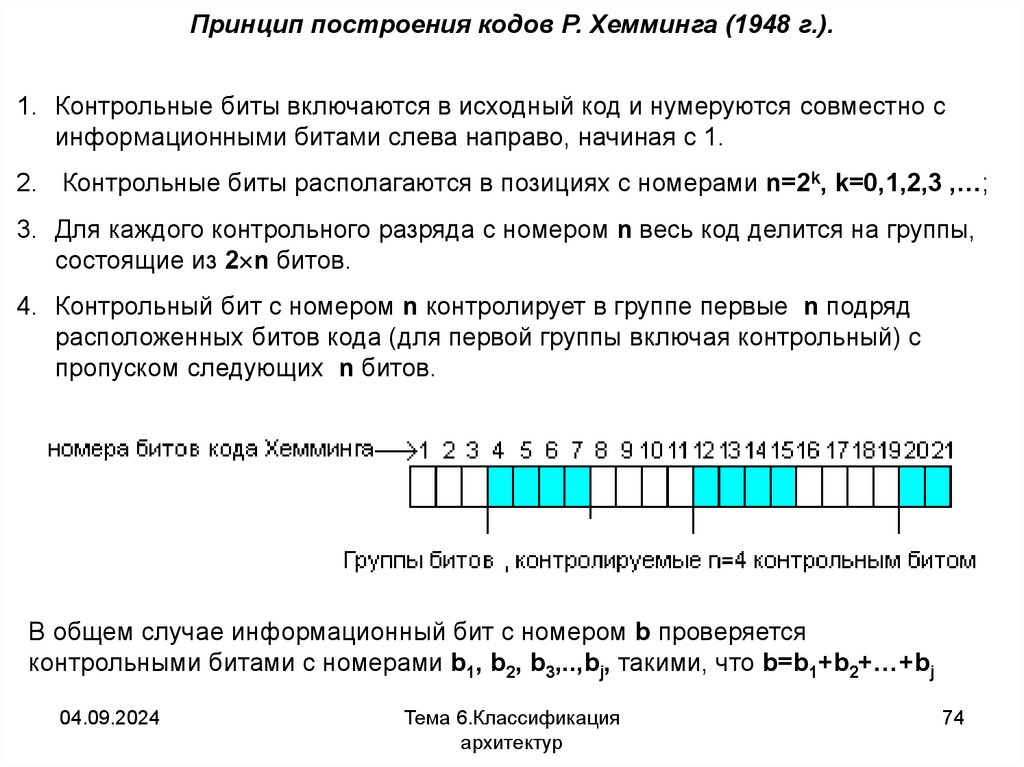

Принцип построения кодов Р. Хемминга (1948 г.).1. Контрольные биты включаются в исходный код и нумеруются совместно с

информационными битами слева направо, начиная с 1.

2. Контрольные биты располагаются в позициях с номерами n=2k, k=0,1,2,3 ,…;

3. Для каждого контрольного разряда с номером n весь код делится на группы,

состоящие из 2 n битов.

4. Контрольный бит с номером n контролирует в группе первые n подряд

расположенных битов кода (для первой группы включая контрольный) с

пропуском следующих n битов.

В общем случае информационный бит с номером b проверяется

контрольными битами с номерами b1, b2, b3,..,bj, такими, что b=b1+b2+…+bj

04.09.2024

Тема 6.Классификация

архитектур

74

75.

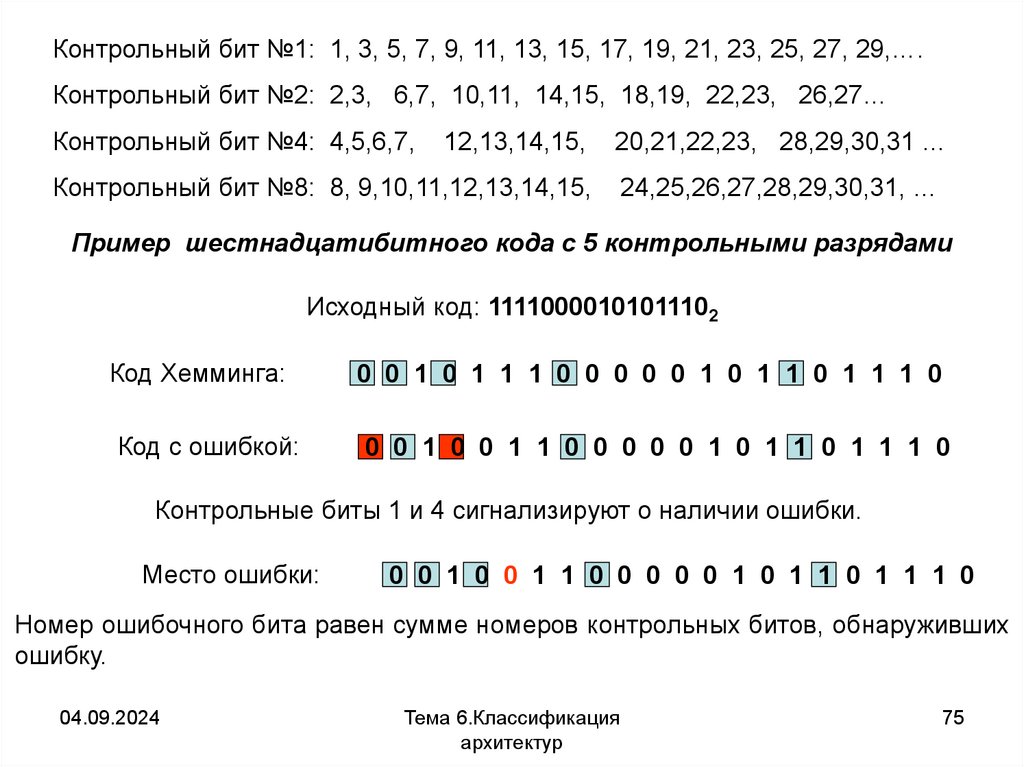

Контрольный бит №1: 1, 3, 5, 7, 9, 11, 13, 15, 17, 19, 21, 23, 25, 27, 29,….Контрольный бит №2: 2,3, 6,7, 10,11, 14,15, 18,19, 22,23, 26,27…

Контрольный бит №4: 4,5,6,7,

12,13,14,15,

20,21,22,23, 28,29,30,31 …

Контрольный бит №8: 8, 9,10,11,12,13,14,15,

24,25,26,27,28,29,30,31, …

Пример шестнадцатибитного кода с 5 контрольными разрядами

Исходный код: 11110000101011102

Код Хемминга:

0 0 1 0 1 1 1 0 0 0 0 0 1 0 1 1 0 1 1 1 0

Код с ошибкой:

0 0 1 0 0 1 1 0 0 0 0 0 1 0 1 1 0 1 1 1 0

Контрольные биты 1 и 4 сигнализируют о наличии ошибки.

Место ошибки:

0 0 1 0 0 1 1 0 0 0 0 0 1 0 1 1 0 1 1 1 0

Номер ошибочного бита равен сумме номеров контрольных битов, обнаруживших

ошибку.

04.09.2024

Тема 6.Классификация

архитектур

75

76.

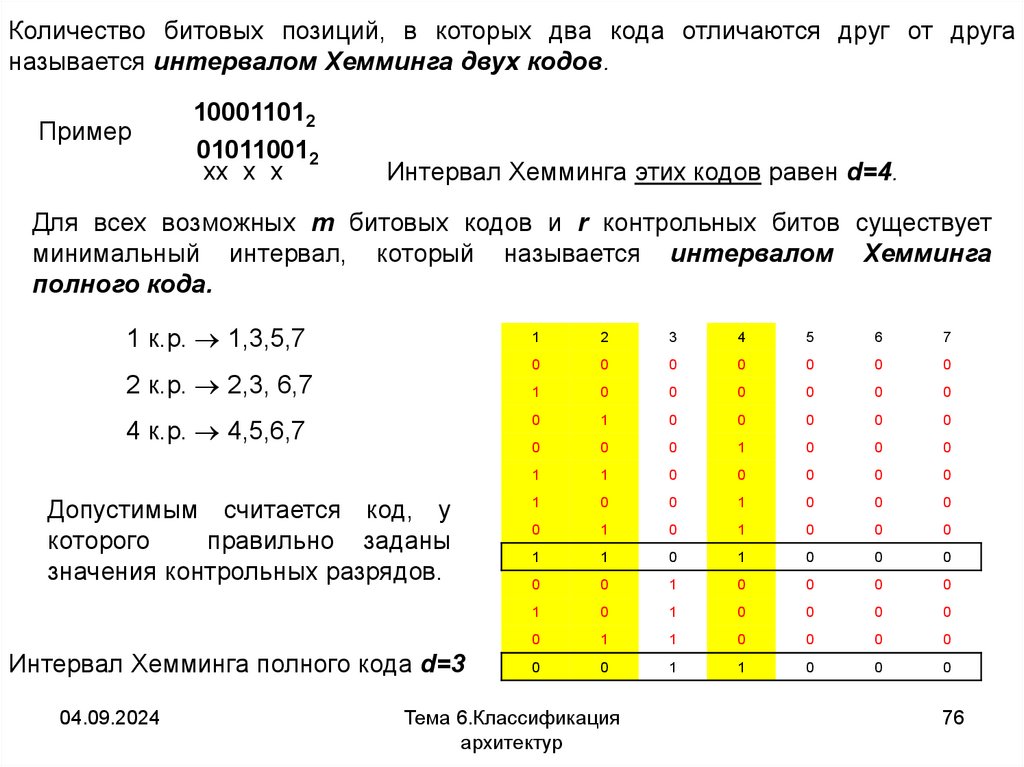

Количество битовых позиций, в которых два кода отличаются друг от друганазывается интервалом Хемминга двух кодов.

Пример

100011012

010110012

xx х х

Интервал Хемминга этих кодов равен d=4.

Для всех возможных m битовых кодов и r контрольных битов существует

минимальный интервал, который называется интервалом Хемминга

полного кода.

1 к.р. 1,3,5,7

2 к.р. 2,3, 6,7

4 к.р. 4,5,6,7

Допустимым считается код, у

которого

правильно заданы

значения контрольных разрядов.

Интервал Хемминга полного кода d=3

04.09.2024

1

2

3

4

5

6

7

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

0

1

0

0

1

0

0

0

0

1

0

1

0

0

0

1

1

0

1

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

1

0

0

0

0

0

0

1

1

0

0

0

Тема 6.Классификация

архитектур

76

77.

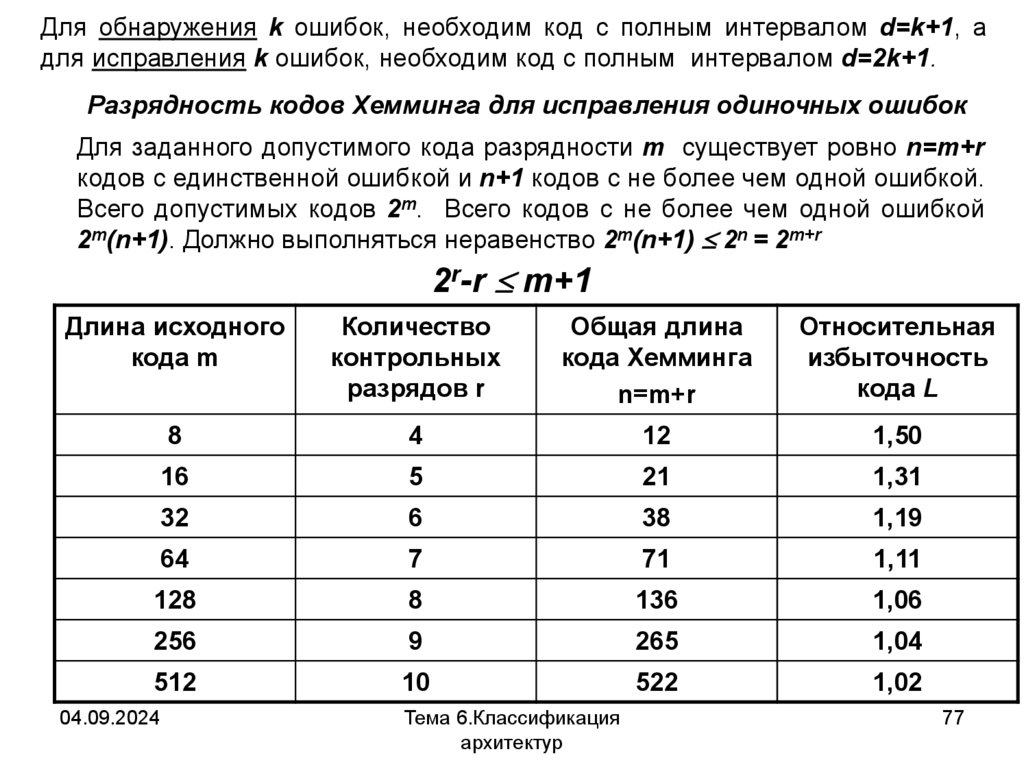

Для обнаружения k ошибок, необходим код с полным интервалом d=k+1, адля исправления k ошибок, необходим код с полным интервалом d=2k+1.

Разрядность кодов Хемминга для исправления одиночных ошибок

Для заданного допустимого кода разрядности m существует ровно n=m+r

кодов с единственной ошибкой и n+1 кодов с не более чем одной ошибкой.

Всего допустимых кодов 2m. Всего кодов с не более чем одной ошибкой

2m(n+1). Должно выполняться неравенство 2m(n+1) 2n = 2m+r

2r-r m+1

Длина исходного

кода m

Количество

контрольных

разрядов r

Общая длина

кода Хемминга

n=m+r

Относительная

избыточность

кода L

8

4

12

1,50

16

5

21

1,31

32

6

38

1,19

64

7

71

1,11

128

8

136

1,06

256

9

265

1,04

512

10

522

1,02

04.09.2024

Тема 6.Классификация

архитектур

77

78.

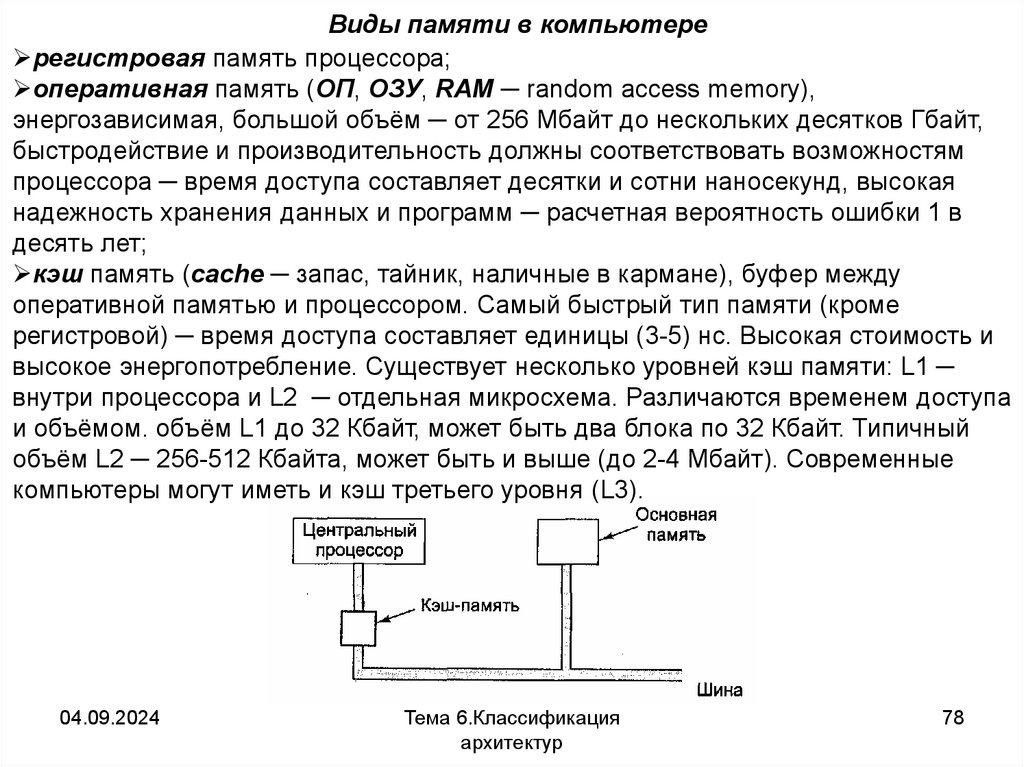

Виды памяти в компьютеререгистровая память процессора;

оперативная память (ОП, ОЗУ, RAM ─ random access memory),

энергозависимая, большой объём ─ от 256 Мбайт до нескольких десятков Гбайт,

быстродействие и производительность должны соответствовать возможностям

процессора ─ время доступа составляет десятки и сотни наносекунд, высокая

надежность хранения данных и программ ─ расчетная вероятность ошибки 1 в

десять лет;

кэш память (cache ─ запас, тайник, наличные в кармане), буфер между

оперативной памятью и процессором. Самый быстрый тип памяти (кроме

регистровой) ─ время доступа составляет единицы (3-5) нс. Высокая стоимость и

высокое энергопотребление. Существует несколько уровней кэш памяти: L1 ─

внутри процессора и L2 ─ отдельная микросхема. Различаются временем доступа

и объёмом. объём L1 до 32 Кбайт, может быть два блока по 32 Кбайт. Типичный

объём L2 ─ 256-512 Кбайта, может быть и выше (до 2-4 Мбайт). Современные

компьютеры могут иметь и кэш третьего уровня (L3).

04.09.2024

Тема 6.Классификация

архитектур

78

79.

буферная память адаптеров, контроллеров, портов (от десятков байт дляпортов до десятков мегабайт — видеопамять, память видеоадаптера).

Адаптером называется устройство, обеспечивающее соединение,

сопряжение устройств с различной формой представления данных. Обычно

через адаптер внешнее устройство подключается к шине ПК. Адаптер

представляет собой пассивное устройство

Контроллером называется управляющее устройство, обеспечивающее

сопряжение устройств с различной формой представления информации.

Контролер отличается от адаптера тем, что он выполняет некоторые

управляющие функции, то есть контроллер это активное устройство. В

состав контроллера может входить независимый специализированный

процессор, который выполняет свои функции по специальной программе.

Такие контроллеры называются программируемыми Например, для обмена

данными между жесткими дисками и оперативной памятью используются

контроллеры DMA (Direct Memory Access), которые фактически являются

сопроцессорами ввода/вывода, разгружающими центральный процессор от

очень длительных операций по обмену данными.

Порт представляет собой разъем на корпусе, обеспечивающий физическое

подсоединение внешнего устройства, а также логический канал связи

центральных устройств компьютера с периферийными.

04.09.2024

Тема 6.Классификация

архитектур

79

80.

постоянная память (ROM ─ Read Only Memory) , используется дляэнергонезависимого хранения системной информации (часть операционной

системы BIOS, базовые операции обмена), только считывание, типовое

значение объёма 128–256К, невысокая скорость обмена. Для повышения

производительности содержимое ROM копируется в ОЗУ и в работе

используется только копия (теневая память — Shadow ROM). В последние

годы вытесняется другими видами энергонезависимой памяти (flash память).

полупостоянная память используется для хранения информации о

конфигурации компьютера (характеристика системного диска и т.д.).

CMOS Memory ─ Complimentary Metal Oxide Semiconductor ─

комплиментарный метал-оксид-полупроводник (КМОП) память, или

CMOS RTC ─ CMOS Real Time Clock используется для хранения данных

о конфигурации компьютера, в том числе составной частью этой

микросхемы являются часы-календарь;

ESCD (Extended Static Configuration Data) память для хранения

параметров конфигурирования устройств Plug and Play. объём

составляет несколько сотен байт. При отключенном электропитании для

поддержания внутреннего состояния используется батарейка или

аккумулятор. Самая экономичная память. Время доступа более 100 нс.

внешняя память (ВЗУ) ─ дисковая, ленточная, флэш-память и т.д., самая

медленная ─ время доступа порядка 30 000 000 нс, самая дешевая, самая

емкая (единицы терабайт)

04.09.2024

Тема 6.Классификация

архитектур

80

81.

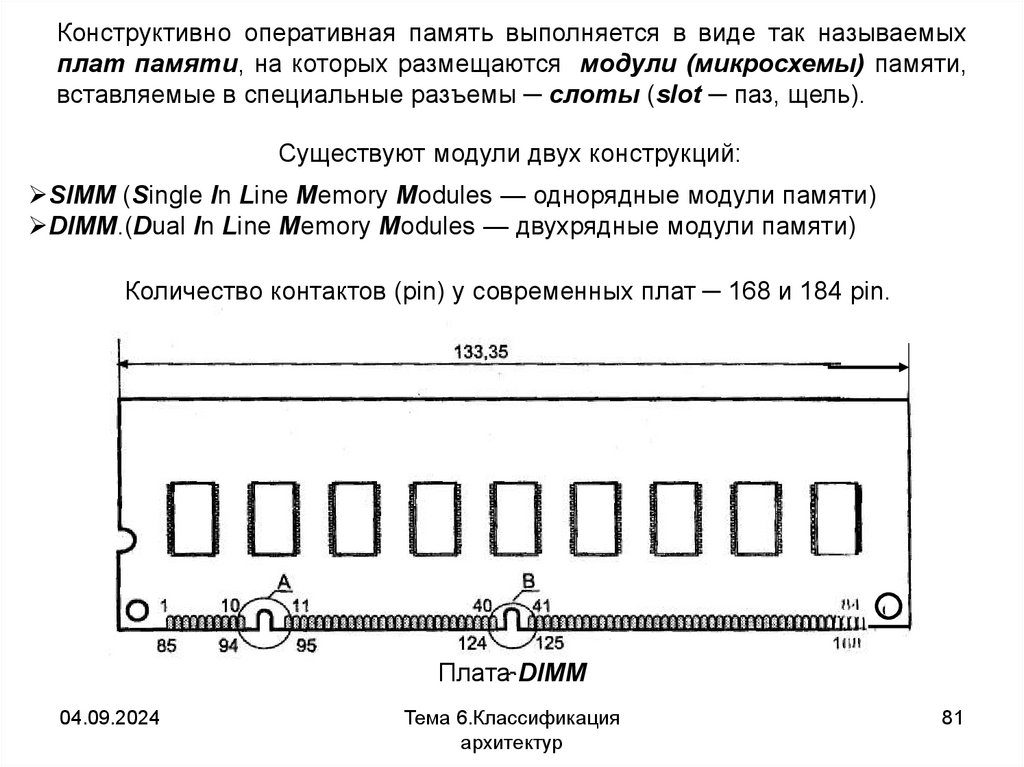

Конструктивно оперативная память выполняется в виде так называемыхплат памяти, на которых размещаются модули (микросхемы) памяти,

вставляемые в специальные разъемы ─ слоты (slot ─ паз, щель).

Существуют модули двух конструкций:

SIMM (Single In Line Memory Modules — однорядные модули памяти)

DIMM.(Dual In Line Memory Modules — двухрядные модули памяти)

Количество контактов (pin) у современных плат ─ 168 и 184 pin.

Плата DIMM

04.09.2024

Тема 6.Классификация

архитектур

81

82.

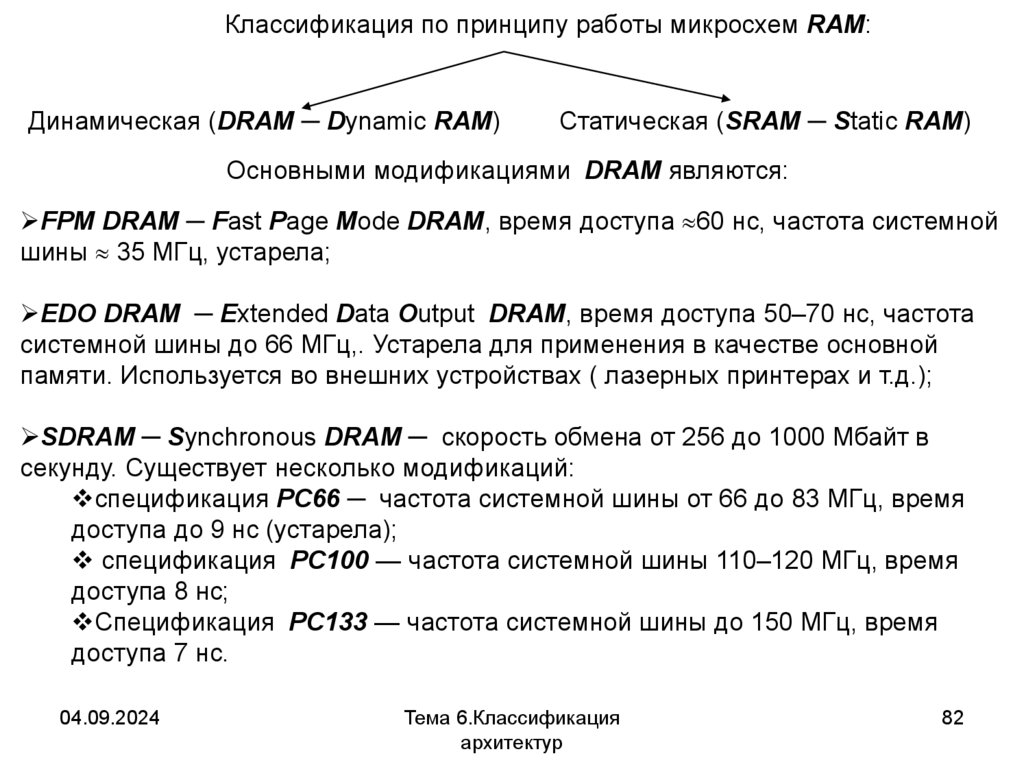

Классификация по принципу работы микросхем RAM:Динамическая (DRAM ─ Dynamic RAM)

Статическая (SRAM ─ Static RAM)

Основными модификациями DRAM являются:

FPM DRAM ─ Fast Page Mode DRAM, время доступа 60 нс, частота системной

шины 35 МГц, устарела;

EDO DRAM ─ Extended Data Output DRAM, время доступа 50–70 нс, частота

системной шины до 66 МГц,. Устарела для применения в качестве основной

памяти. Используется во внешних устройствах ( лазерных принтерах и т.д.);

SDRAM ─ Synchronous DRAM ─ скорость обмена от 256 до 1000 Мбайт в

секунду. Существует несколько модификаций:

спецификация PC66 ─ частота системной шины от 66 до 83 МГц, время

доступа до 9 нс (устарела);

спецификация PC100 — частота системной шины 110–120 МГц, время

доступа 8 нс;

Спецификация PC133 — частота системной шины до 150 МГц, время

доступа 7 нс.

04.09.2024

Тема 6.Классификация

архитектур

82

83.

DDR SDRAM ─ Double Data Rate SDRAM — синхронизированная динамическаяпамять с удвоением данных, производство компании Samsung, время доступа 5–

6 нс, частота шины памяти 600-700 МГц, за один такт передается двойной объём

данных. В настоящее время распространены следующие модификации:

Спецификация PC2100 ─ скорость обмена 2100 Мбайт/сек;

Спецификация PC2700 ─ скорость обмена 2700 Мбайт/сек;

Спецификация PC3200 ─ скорость обмена 3200 Мбайт/сек;

RDRAM (Rambus DRAM — от названия фирмы производителя Rambus Inc.),

время доступа 4 нс, частота шины памяти до 800 МГц; скорость обмена до 6000

Мбайт в секунду, очень дорогая разновидность памяти.

В качество дополнительного параметра микросхем оперативной памяти

рассматривается наличие ECC ─ Error Checking and Correcting ─ подсистемы

контроля и коррекции ошибок.

04.09.2024

Тема 6.Классификация

архитектур

83

84.

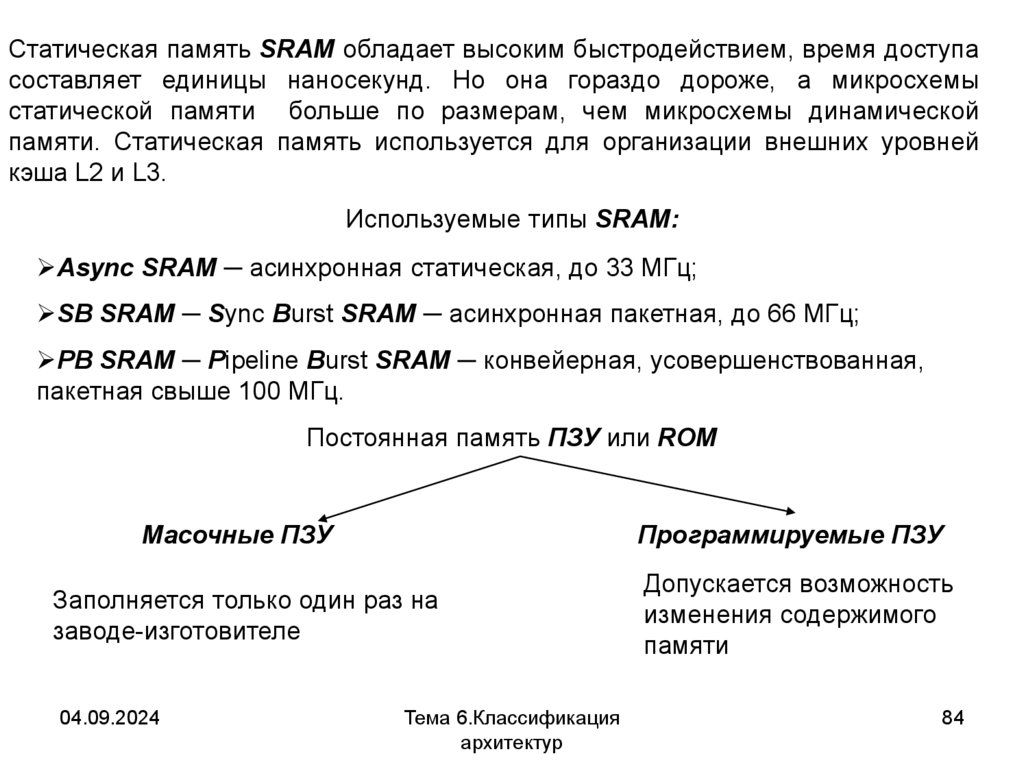

Статическая память SRAM обладает высоким быстродействием, время доступасоставляет единицы наносекунд. Но она гораздо дороже, а микросхемы

статической памяти больше по размерам, чем микросхемы динамической

памяти. Статическая память используется для организации внешних уровней

кэша L2 и L3.

Используемые типы SRAM:

Async SRAM ─ асинхронная статическая, до 33 МГц;

SB SRAM ─ Sync Burst SRAM ─ асинхронная пакетная, до 66 МГц;

PB SRAM ─ Pipeline Burst SRAM ─ конвейерная, усовершенствованная,

пакетная свыше 100 МГц.

Постоянная память ПЗУ или ROM

Масочные ПЗУ

Программируемые ПЗУ

Заполняется только один раз на

заводе-изготовителе

Допускается возможность

изменения содержимого

памяти

04.09.2024

Тема 6.Классификация

архитектур

84

85.

PROM ─ Programmable ROM ─ однократно программируемые ПЗУ. Дляпрограммирования используются специальные устройства. Модули памяти

вынимаются из корпуса компьютера и вставляются в это устройство. В нем в

модули заносится новое содержимое, а затем они вставляются назад в

компьютер.

EPROM ─ Erasable Programmable ROM ─ перепрограммируемые ПЗУ. Можно

неоднократно стирать содержание и заносить новое. Стирание осуществляется

с помощью ультрафиолетового облучения в течении нескольких минут (до 5 мин)

через специальные окошки, которые после облучения вновь заклеиваются. Это

можно делать прямо на компьютере с помощью специально подключаемого

устройства.

EEPROM ─ Electrically Erasable Programmable ROM ─ электрически стираемые,

перепрограммируемые ПЗУ. Стирание осуществляется прямо в компьютере с

помощью высокого (порядка 30 вольт) напряжения.

FEPROM ─ Flash EPROM или Flash память ─ флэш-память ─ электрически

стираемая перепрограммируемая ПЗУ. Объединяет достоинства ROM и RAM.

То есть, с одно стороны, допускает как чтение, так и запись, но при выключении

электропитания содержимое памяти не уничтожается. В отличие от DRAM

энергия потребляется не все время работы, а только в периоды чтения/записи.

04.09.2024

Тема 6.Классификация

архитектур

85

86.

ПроцессорПроцессором (process — обрабатывать), центральным процессором (ЦП)

или CPU (Central Processing Unit — центральный обрабатывающий блок,

устройство), а в персональных компьютерах еще и микропроцессором

называется устройство, обеспечивающее процесс выполнения компьютером

действий по обработке данных, задаваемый выполняемой программой

Технические характеристики процессоров

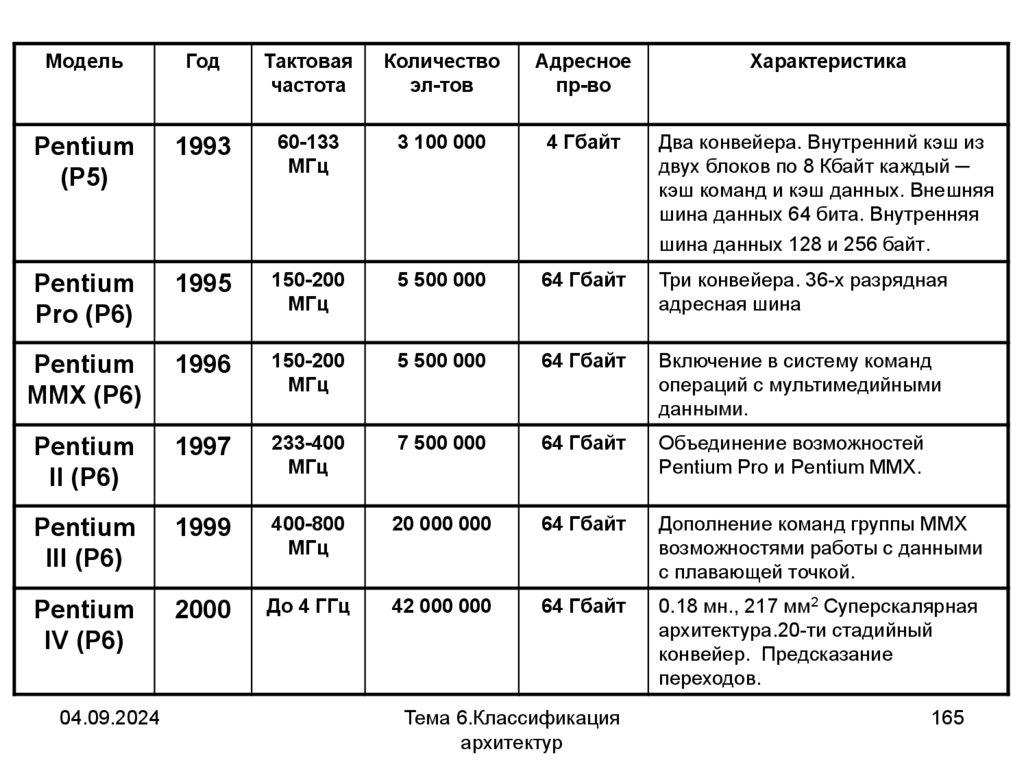

Архитектура процессора (CISC, RISC, VLIW и т.д.)

Модель процессора, однозначно связанная с его системой команд (Intel ─

Xeon, Pentium, Celeron, Merced; AMD ─ Athlon, Duron);

Внутренняя тактовая частота (3-4 ГГц);

Разрядность или длина машинного слова (16, 32, 64, 128 битов);

объём внутреннего кэша L1 (от 128 Кбайт до 2-4 Мбайт);

Производительность. Измеряется в количестве операций с плавающей

точкой в секунду ─ мегафлопах, гигафлопах, терафлопах (до 73 терафлопов);

Плотность логических элементов (Pentium ─ 42 миллиона элементов) ;

Линейный размер логических элементов (0,13; 0,9 микрон);

Форм-фактор ─ геометрические размеры, количество контактов, способ

подключения к материнской плате (Socket7, Slot A, Socket A, Socket 478 и т.д.).

04.09.2024

Тема 6.Классификация

архитектур

86

87.

Вспомогательные процессоры ─ сопроцессоры, чипы, чипсетыДля выполнения операций по управлению отдельными устройствами

компьютера используются функционально похожие на процессор

специализированные

микросхемы,

которые

принято

называть

сопроцессорами и чипами ( chip ─ тонкий кусочек).

Чипсет (chip set ─ набор чипов) ─ базовый набор специализированных

микросхем, при подключении которых друг к другу формируется

функциональный блок компьютера. Например, чипсет материнской

платы, чипсет графического контроллера и т.д.

Чипсет материнской платы является связующим звеном между всеми ее

компонентами. Он фактически определяет возможности по модернизации

компьютера.

Чипсет материнской платы определяет:

Типы и частоты поддерживаемых процессоров.

Скоростные характеристики вторичного кэша, его возможный размер.

Типы, объёмы и максимальное количество модулей памяти.

Поддерживаемые частоты шин, возможное количество контроллеров и т.д.

Функционально современные чипсеты делятся на северный мост,

отвечающий за соединение между собой процессора, оперативной памяти и

графической подсистемы, и южный мост, который отвечает за работу со

всеми периферийными устройствами (дисками, клавиатурой и т.д.)

04.09.2024

Тема 6.Классификация

архитектур

87

88.

ШиныШиной или магистралью называется группа проводов, по каждому из которых

передается один бит данных, один бит адреса или управляющий сигнал, а также

совокупность электронных схем, обеспечивающих правильную передачу

информации внутри компьютера. Участок шины, по которому передаются данные,

называется шиной данных. Участок шины, по которому передаются адреса,

называется адресной шиной. И, наконец, участок шины, по которому передаются

управляющие сигналы называется шиной управления.

Шины имеют разъемы ─ сокеты (socket ─ углубление, гнездо) и слоты,

предназначенные для крепления микросхем (чипов) и дополнительных плат (плат

расширений), а также разъемы ─ порты для подсоединения внешних устройств.

Основные характеристики шин

Назначение ─ тип устройств, подсоединяемых к шине.

Разрядность.

Тактовая частота.

Скорость обмена или пропускная способность.

Разрядность адресной шины определяет адресное

пространство оперативной памяти

04.09.2024

Тема 6.Классификация

архитектур

88

89.

В современных компьютерах используется несколько специализированныхшин, обеспечивающих передачу информации и управляющих сигналов между

устройствам компьютера с различными скоростными характеристиками.

Основные типы шин

Локальная, системная шина (Host bus) служит для соединения процессора с

чипсетом северного моста; шина памяти служит для соединения оперативной

памяти с чипсетом северного моста; шина вторичного кэша служит для

соединения процессора с вторичным кэшем. Тактовые частот до 800 МГц,

разрядность до 256 бит.

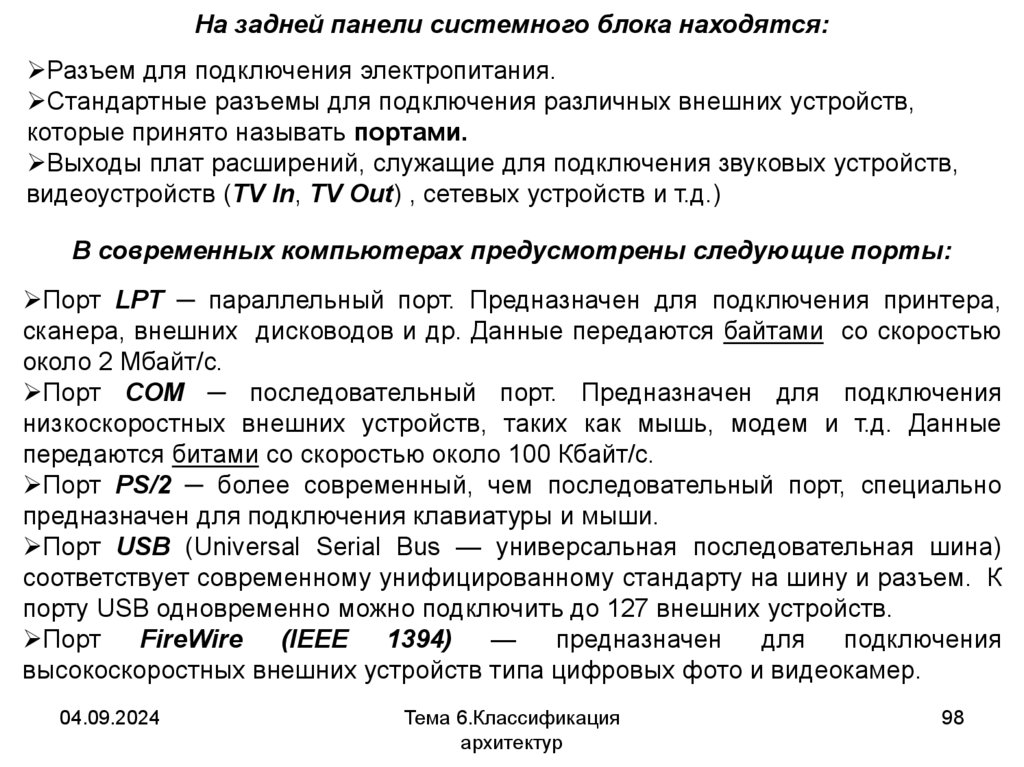

ISA (Industry Standard Architecture — стандартная промышленная архитектура)

и EISA (Extended ISA — расширенный ISA) — традиционные, универсальные

шины для подключения внешних устройств с малой скоростью обмена от 8 до 33

Мбайт/с (мышь, клавиатура), тактовая частота до 8 МГц. Разновидности шин:

ISA8 ─ разрядность 8 бит; ISA16 ─ разрядность 16 бит; EISA – разрядность 32

бита.

PCI (Peripheral Component Interconnect — соединитель периферийных

компонент) — высокоскоростная шина для подсоединения периферийных

устройств со скоростью обмена до 500 Мбайт/с и тактовой частотой 66 МГц;

модификация PCI-X имеет скорость до 1 Гбайт/с. Разрядность 64 и 128 бит.

Подключаются диски, графические компоненты.

04.09.2024

Тема 6.Классификация

архитектур

89

90.

IDE (Integrated Drive Electronics — интегрированное электронное устройство) иEIDE (Extended IDE — расширенный IDE) — шина и стандарт для подключения

жестких, оптических дисков и мобильных дисководов. Скорость обмена до 20

Мбайт/с.

SCSI (Small Computer System Interface — интерфейс малых вычислительных

систем) — шина и стандарт, которые предназначены для подключения

высокопроизводительных дисковых устройств. Скорость обмена до 80 Мбайт/с.

AGP (Advanced Graphic Port — улучшенный графический порт) — шина для

подключения видеоплат со скоростью обмена от 256 Мбайт/с до 1,06 Гбайт/с.

Скорость обмена 256 Мбайт/с считает условной единицей измерения для

видеокарт типа AGP. Скорость 528 Мбайт/с принято обозначать AGP2x, а 1,06

Гбайт/с — AGP4x.

USB (Universal Serial Bus — универсальная последовательная шина) ─

одновременно можно подключить до 127 внешних устройств (принтер, сканер и

т.д.). Скорость обмена данными до 12 Мбайт/с, а у модификации шины USB 2.0

— до 60 Мбайт/с.

FireWire (fire wire ─ огненный провод) или IEEE 1394 — шина и стандарт,

предназначенные для подключения высокоскоростных внешних устройств типа

цифровых фото и видеокамер. Обеспечивает скорость обмена до 50 Мбайт/с.

Arapahoe — перспективная шина третьего поколения, которая должна

обеспечить скорость обмена до 6 Гбайт/с.

04.09.2024

Тема 6.Классификация

архитектур

90

91.

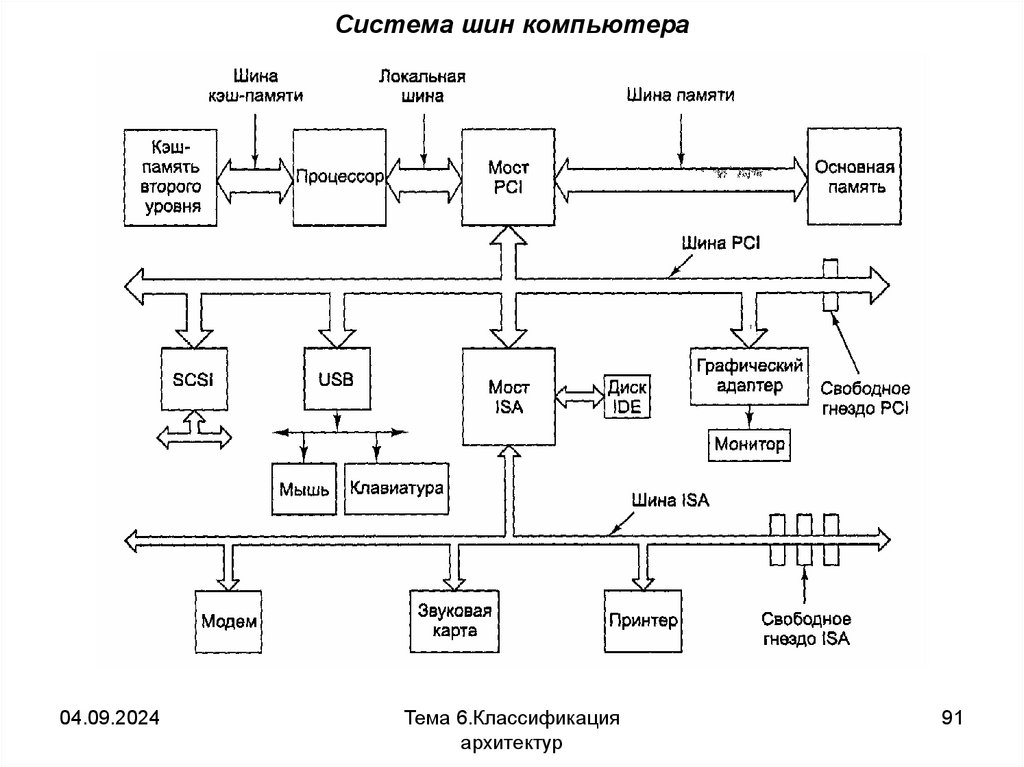

Система шин компьютера04.09.2024

Тема 6.Классификация

архитектур

91

92.

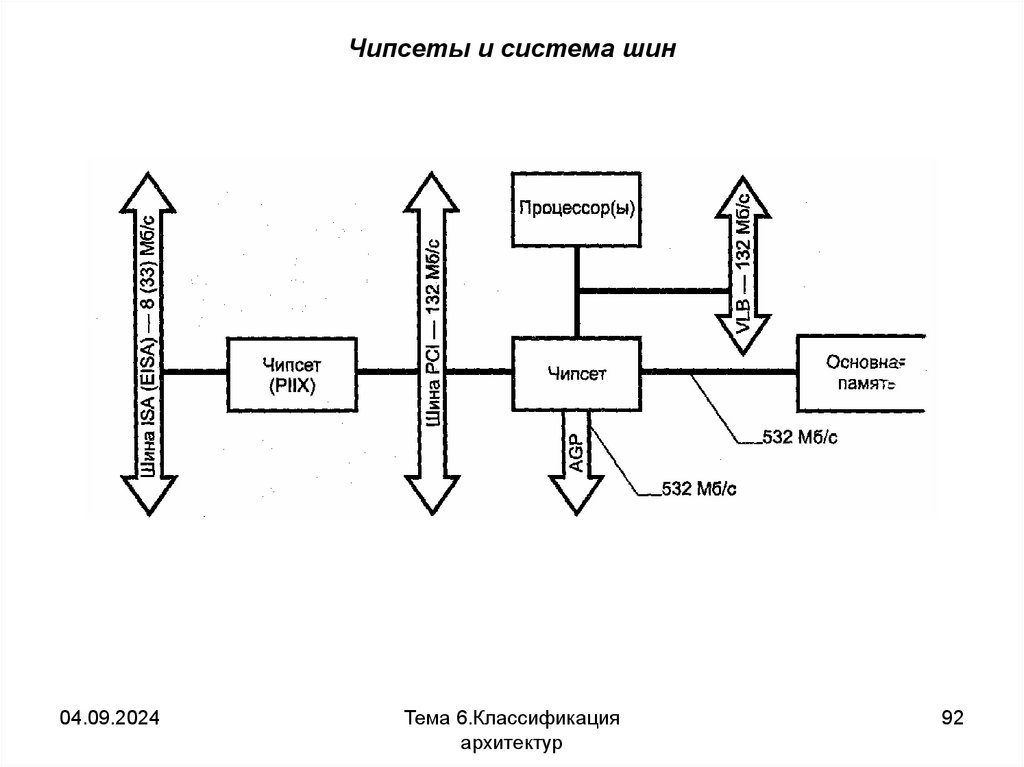

Чипсеты и система шин04.09.2024

Тема 6.Классификация

архитектур

92

93.

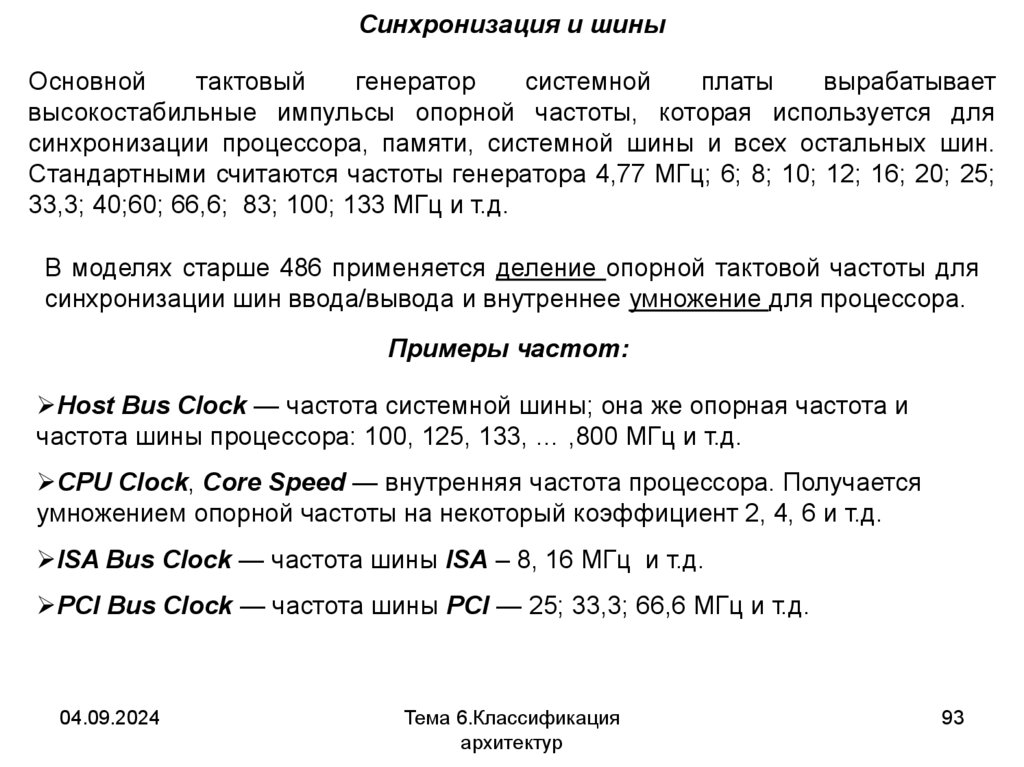

Синхронизация и шиныОсновной

тактовый

генератор

системной

платы

вырабатывает

высокостабильные импульсы опорной частоты, которая используется для

синхронизации процессора, памяти, системной шины и всех остальных шин.

Стандартными считаются частоты генератора 4,77 МГц; 6; 8; 10; 12; 16; 20; 25;

33,3; 40;60; 66,6; 83; 100; 133 МГц и т.д.

В моделях старше 486 применяется деление опорной тактовой частоты для

синхронизации шин ввода/вывода и внутреннее умножение для процессора.

Примеры частот:

Host Bus Clock — частота системной шины; она же опорная частота и

частота шины процессора: 100, 125, 133, … ,800 MГц и т.д.

CPU Clock, Core Speed — внутренняя частота процессора. Получается

умножением опорной частоты на некоторый коэффициент 2, 4, 6 и т.д.

ISA Bus Clock — частота шины ISA – 8, 16 МГц и т.д.

PCI Bus Clock — частота шины PCI — 25; 33,3; 66,6 МГц и т.д.

04.09.2024

Тема 6.Классификация

архитектур

93

94.

Материнская платаМатеринской или системной платой (mother board, system board, system

card) называется основная плата, по которой проходят основные шины

компьютера, и на которой размещены разъемы (слоты, сокеты) для крепления

основных внутренних устройств компьютера (процессора, чипсета, оперативной

памяти, плат расширений).

На материнской плате находятся:

Сокет или слот для крепления процессора или платы, содержащей

микросхемы процессора и внешнего кэша. Например, ZIF Socket (Zero

Insertion Force socket ─ сокет с нулевым усилием вставки).

Слот для крепления плат оперативной памяти.

Система шин.

Чипсет.

Слоты расширений (expansion slot) для крепления дополнительных плат

(expansion card) ─ звуковой платы, видеоплаты, сетевой платы и т.д.

04.09.2024

Тема 6.Классификация

архитектур

94

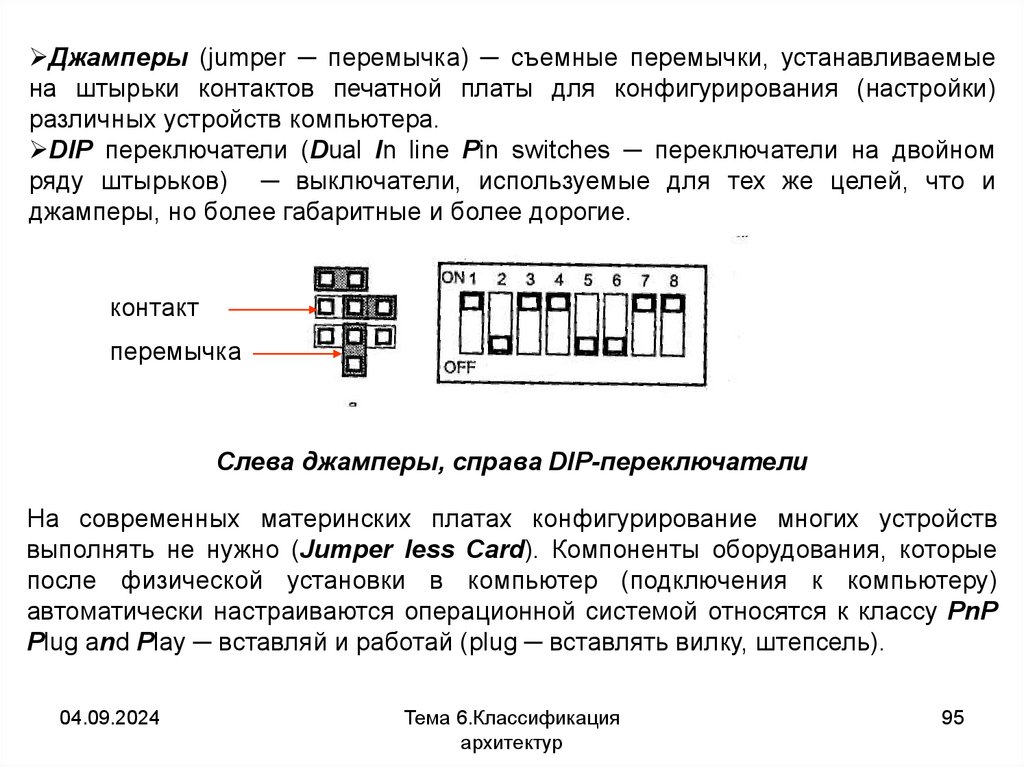

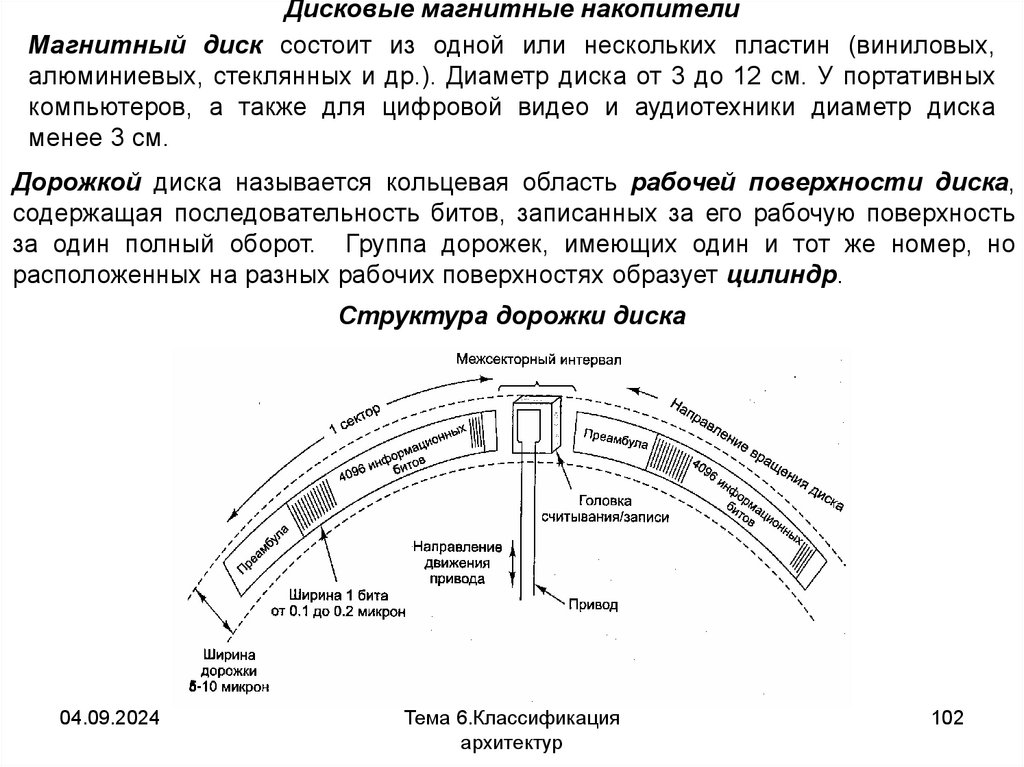

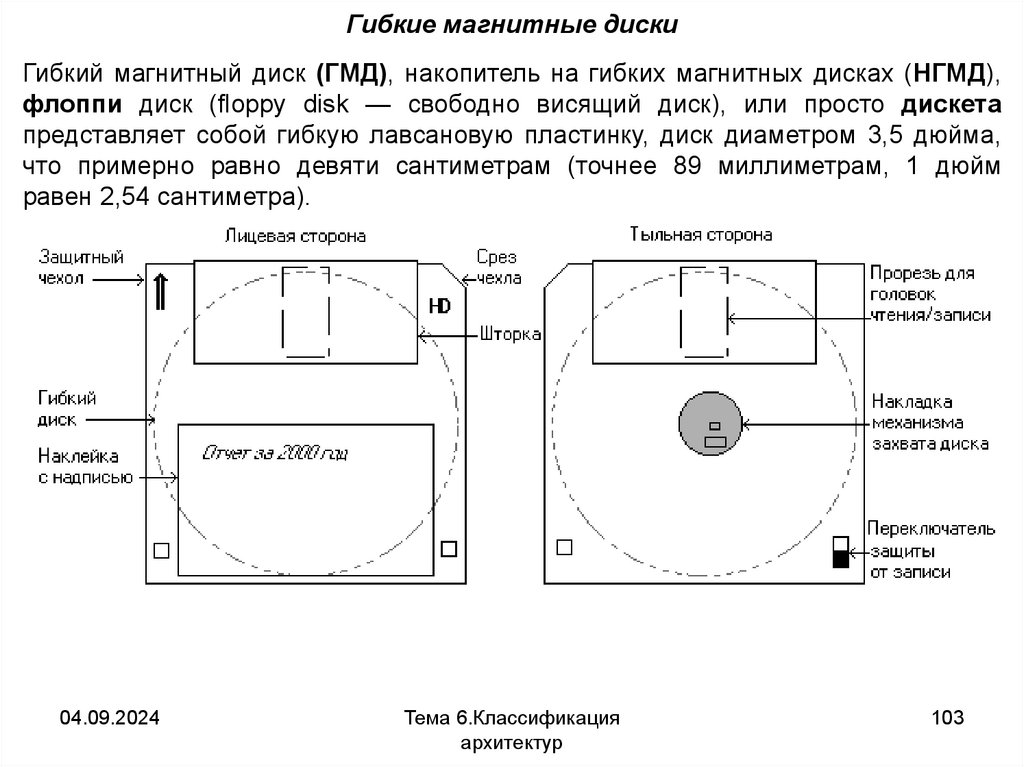

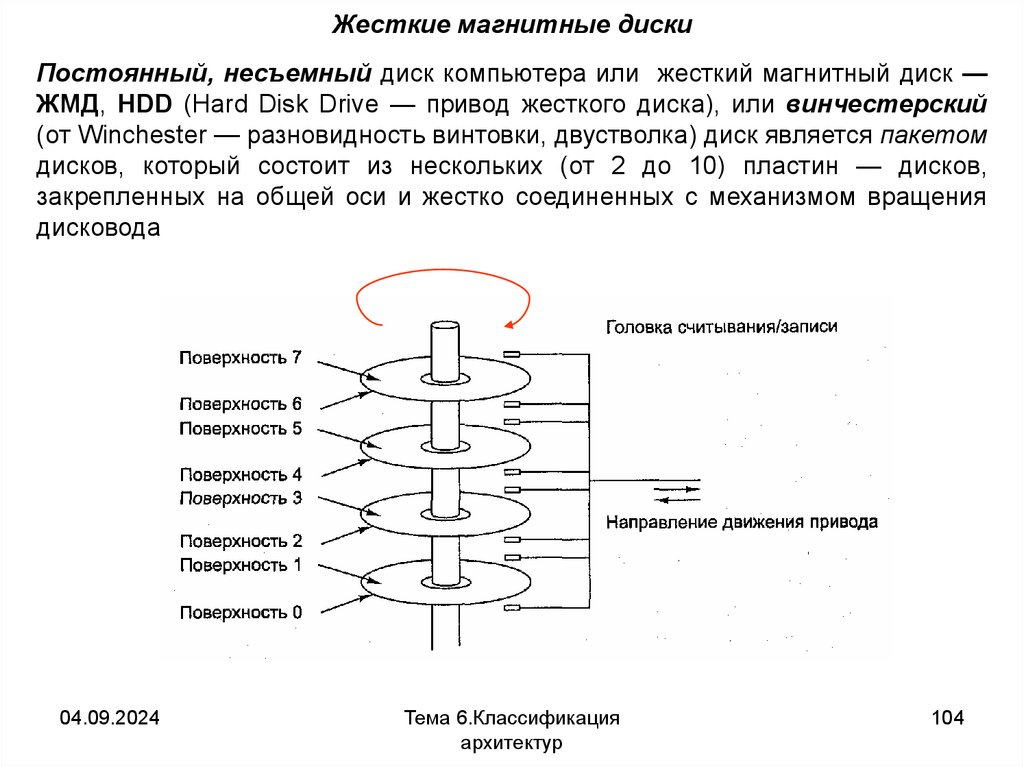

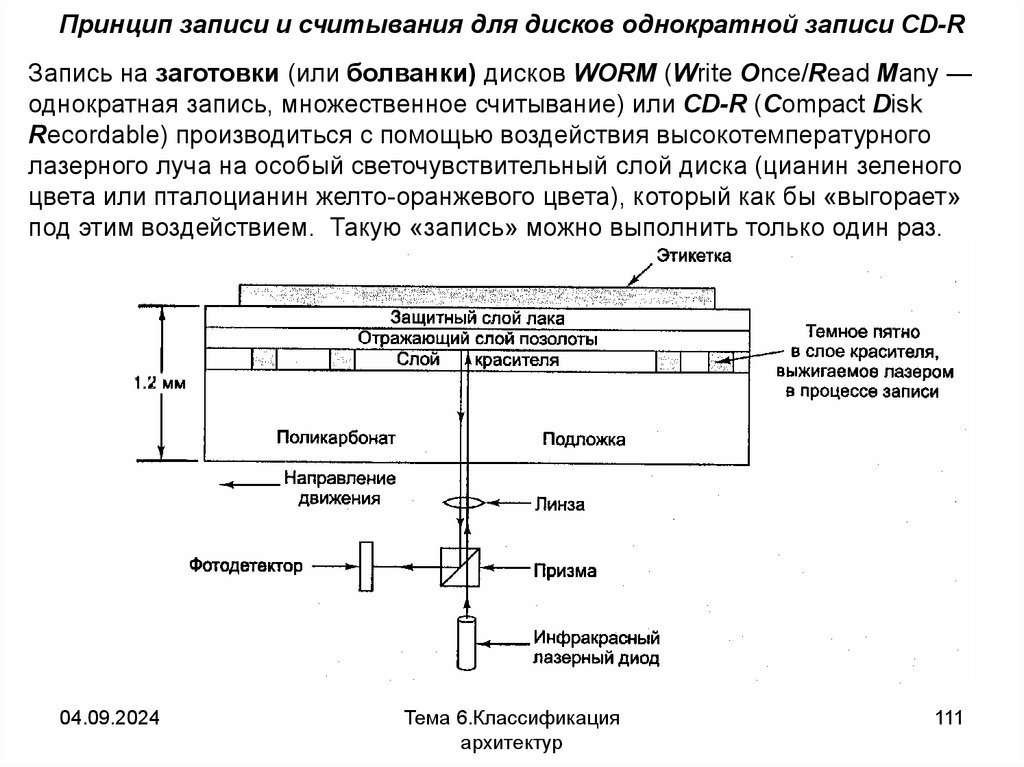

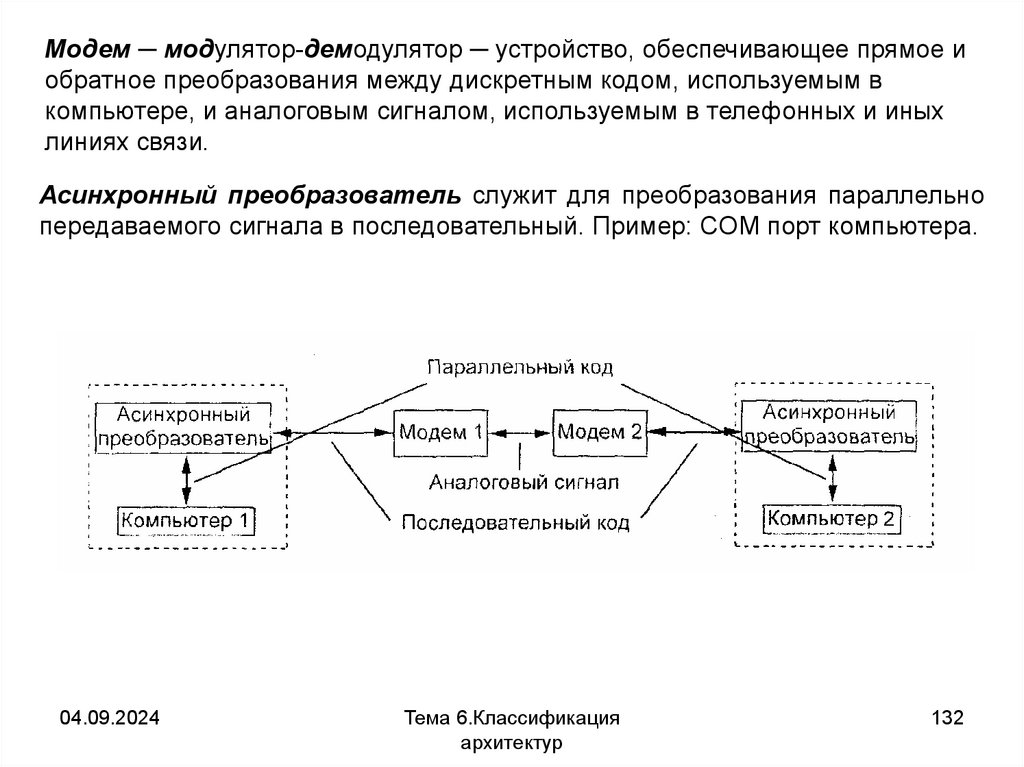

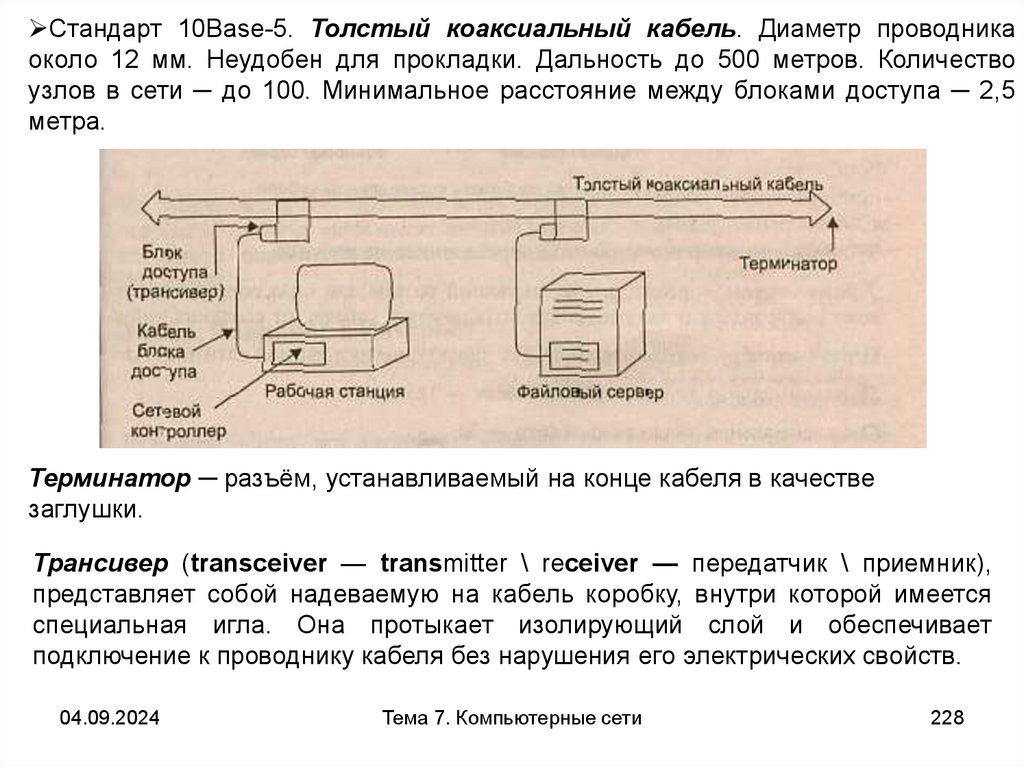

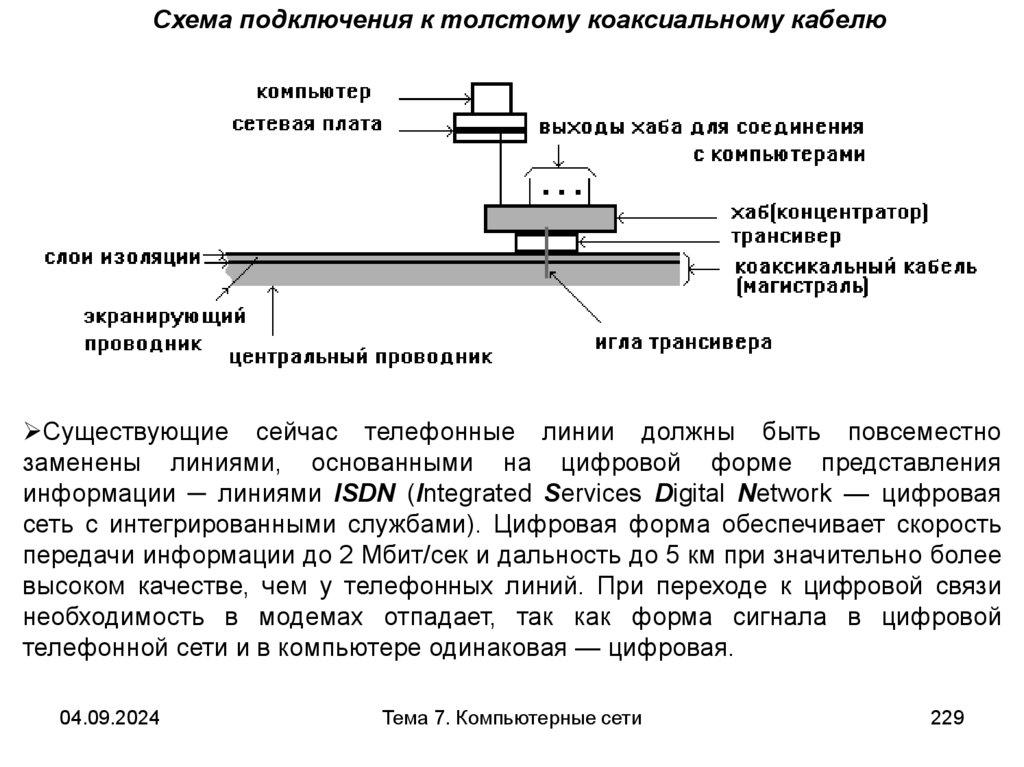

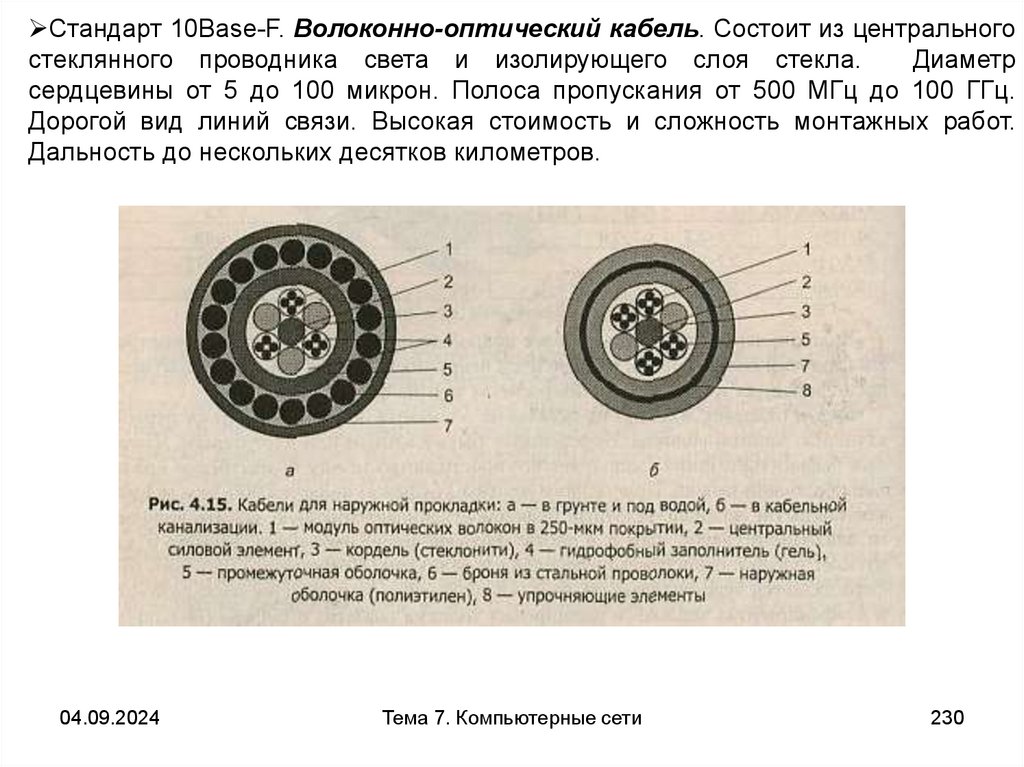

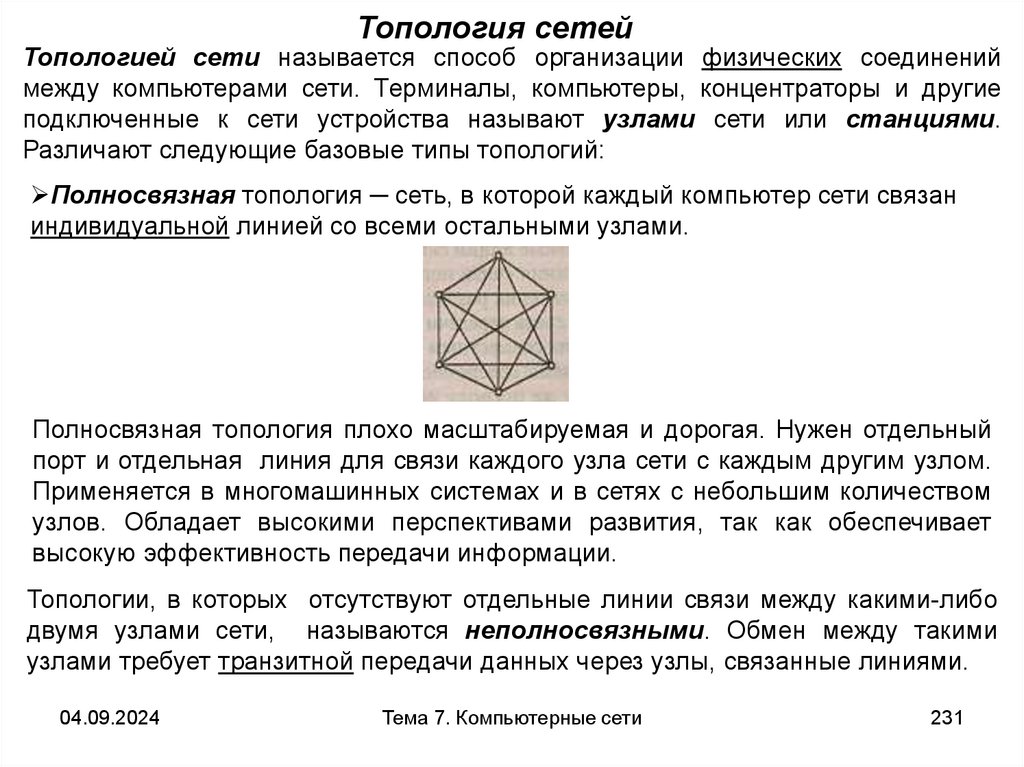

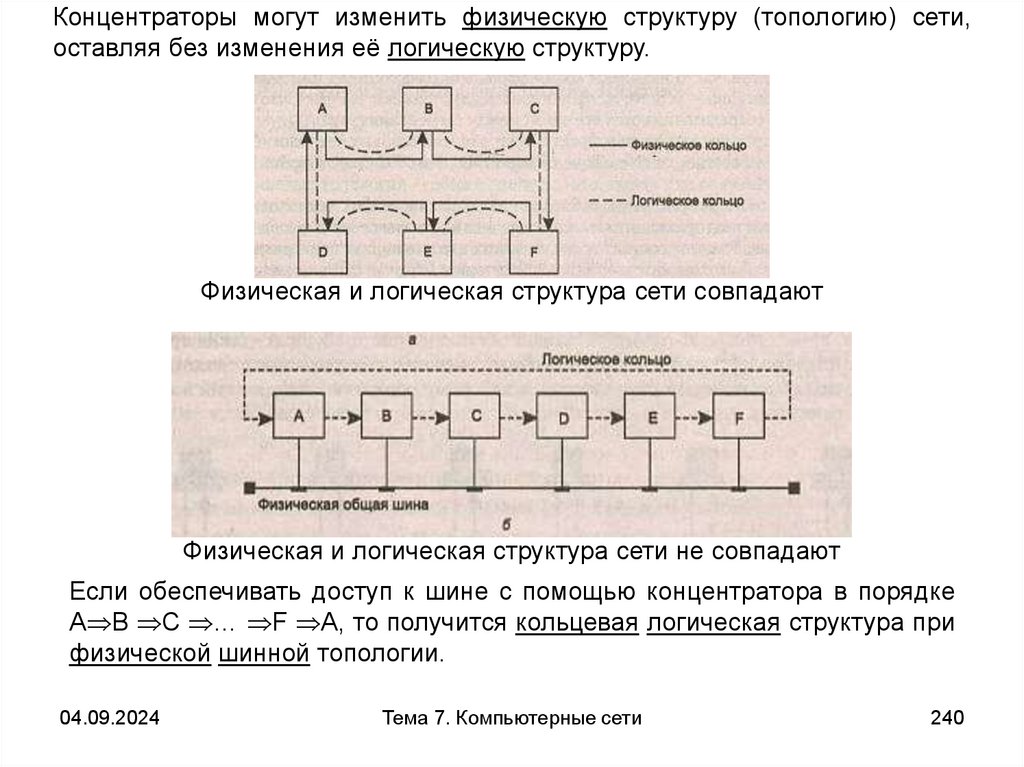

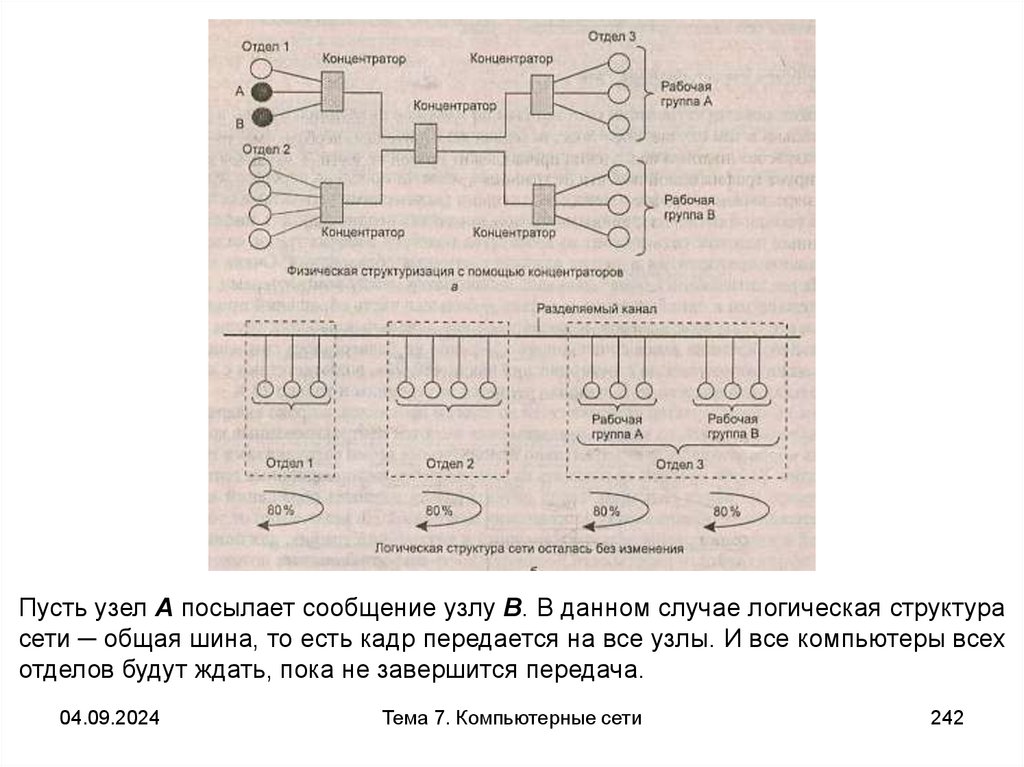

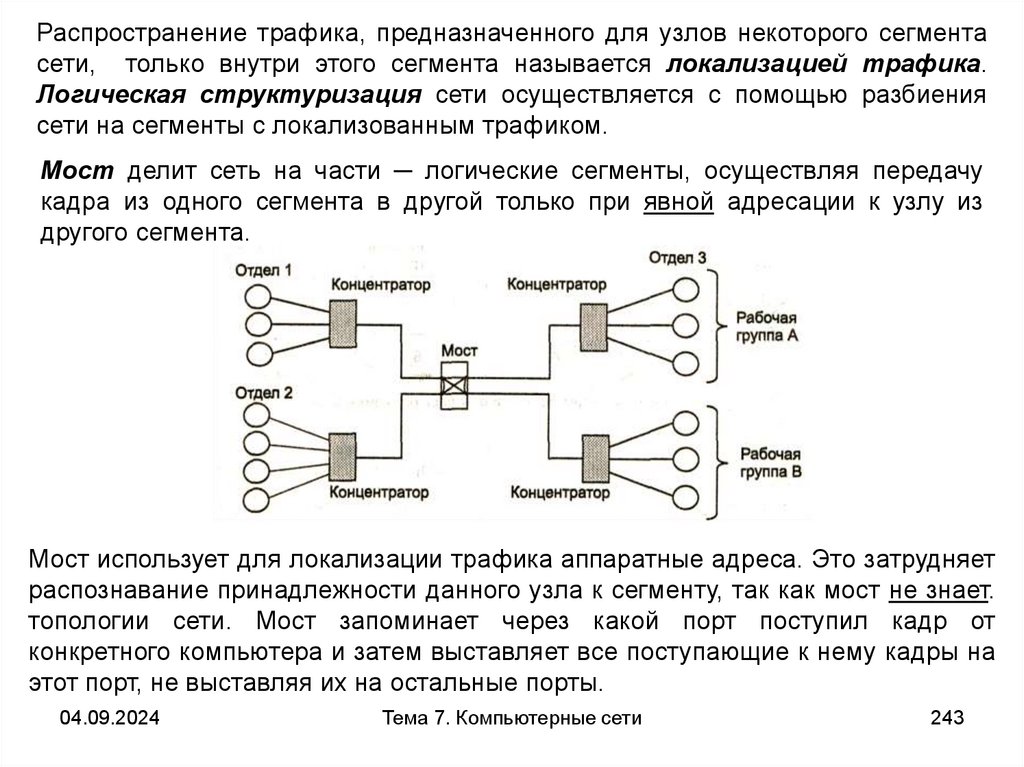

95.