Похожие презентации:

Простір введення\виведення AVR-МК. Джерела перезавантаження AVR-МК. Тема 4

1.

Національний аерокосмічний університет ім. М.Є. ЖуковськогоЦифрові пристрої

Digital devices

&

Microprocessors

Мікропроцесори

Тема 4:

Простір введення\виведення AVR-МК.

Джерела перезавантаження AVR-МК

к.т.н., доцент каф.501

Мазуренко О.В.

2.

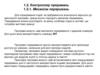

Розподіл адресного простору ОЗП AVR-МК (ATmega16)1

ОЗП (RAM) - 1К х 8

Фізична адресація (Адреса КП ОЗП)

Внутрішня адресація:

Комірка ОЗП

біти:

$045E

RAMEND = $045F

© Мазуренко О.В., 2018

R1

R2

R3

R30

R31

$0000

$0001

$0002

$0003

Простір

введення\виведення

(I\O Space)

ОЗП користувача

$001E

$001F

$0020

$0021

$0023

$0024

$005E

$005F

$0060

$0061

$0063

$0064

R0

НОЗП

Регістровий файл

(Register File)

Адреса: b7 b6 b5 b4 b3 b2 b1 b0

$0000

$0001

$0002

$0003

$003E

$003F

Внутрішні

адреси

простору

введення\

виведення

(I\O Adress)

XH

XL

R27

R26

YH

YL

Y =YH:YL

R29

R28

ZH

ZL

Z =ZH:ZL

R31

R30

X =XH:XL

Мікропроцесори і їх програмування

3.

Простір введення/виведення (I/O Space) МК ATmega16Адреса I/O

(адреса RAM)

$3F ($5F)

$3E ($5E)

$3D ($5D)

$3C ($5C)

$3B $5B)

$3A ($5A)

$39 ($59)

$38 ($58)

$36 ($56)

$35 ($55)

$34 ($54)

$33 ($53)

$32 ($52)

$31 ($51)

$30 ($50)

$2F ($4F)

$2E ($4E)

$2D ($4D)

$2C ($4C)

SREG

SPH

SPL

OCR0

GICR

GIFR

TIMSK

TIFR

TWCR

MCUCR

MCUСSR

TCCR0

TCNT0

OSCCAL

SFIOR

TCCR1A

TCCR1B

TCNT1H

TCNT1L

$2B ($4B)

OCR1AH

$2A ($4A)

OCR1AL

$29 ($49)

OCR1BH

Позначення

© Мазуренко О.В., 2018

2

Функція

Регістр статусу (Status Register)

Старший байт вказівника стека (Stack Pointer High)

Молодший байт вказівника стека (Stack Pointer Low)

Регістр збігу таймера/лічильника 0 (Timer/Counter0 Output Compare Register)

Регістр керування зовнішніми перериваннями

Регістр прапорців зовнішніх переривань

Регістр масок переривань таймерів/лічильників (Timer/Interrupt Mask register)

Регістр прапорців переривань таймерів/лічильників (Timer/Interrupt Flag Register)

Регістр керування двошинним інтерфейсом

Загальний регістр керування МК (MCU General Control Register)

Регістр керування й статусу МК (MCU Control and Status Register)

Регістр керування таймером/лічильником 0 (Timer/Counter0 Control Register)

Таймер/лічильник 0 (Timer/Counter0 (8-bit))

Регістр налаштування частоти тактового генератора (Oscillator Calibration Register)

Регістр керування спеціальними функціями введення\виведення

Керуючий регістр A таймера/лічильника 1 (Timer/Counter1 Control Register A)

Керуючий регістр B таймера/лічильника 1 (Timer/Counter1 Control Register A)

Старший байт таймера/лічильника 1 (Timer/Counter1 High Byte)

Молодший байт таймера/лічильника 1 (Timer/Counter1 Low Byte)

Старший байт регістру збігу A таймера/лічильника 1 (Timer/Counter1 Output

Compare Register A High Byte)

Молодший байт регістру збігу A таймера/ лічильника 1 (Timer/Counter1 Output

Compare Register A Low Byte)

Старший байт регістру збігу B таймера/лічильника 1 (Timer/Counter1 Output

Compare Register B High Byte)

Мікропроцесори і їх програмування

4.

Простір введення/виведення МК ATmega16 (продовження)Адреса I/O

(адреса RAM)

Позначення

$28 ($48)

OCR1BL

$27 ($47)

ICR1H

$26 ($46)

ICR1L

$25 ($45)

$24 ($44)

$23 ($43)

$22 ($42)

$21 ($41)

$20 ($40)

$1F ($3F)

$1E ($3E)

$1D ($3D)

$1C ($3C)

$1B ($3B)

$1A ($3A)

$19 ($39)

$18 ($38)

$17 ($37)

$16 ($36)

$15 ($35)

$14 ($34)

$13 ($33)

$12 ($32)

$11 ($31)

$10 ($30)

TCCR2

TCNT2

OCR2

ASSR

WDTCR

UBRRH

EEARH

EEARL

EEDR

EECR

PORTA

DDRA

PINA

PORTB

DDRB

PINB

PORTC

DDRC

PINC

PORTD

DDRD

PIND

© Мазуренко О.В., 2018

3

Функція

Молодший байт регістру збігу B таймера/лічильника 1 (Timer/Counter1 Output

Compare Register B Low Byte)

Старший байт регістру захоплення таймера/лічильника 1 (Timer/Counter1 Input

Capture Register High Byte)

Молодший байт регістру захоплення таймера/лічильника 1 (Timer/Counter1

Input Capture Register Low Byte)

Регістр керування таймером/лічильником 2 (Timer/Counter2 Control Register)

Таймер/лічильник 2 (Timer/Counter2 (8-bit))

Регістр збігу таймера/лічильника 2 (Timer/Counter2 Output Compare Register)

Регістр статусу асинхронного режиму (Asynchronous Mode Status Register)

Регістр керування вартовим таймером (Watchdog Timer Control Register)

Регістр керування швидкістю УАПП (UART Baud Rate Register) старший байт

Старший байт регістру адреси ППЗПЕС (EEPROM Address Register High)

Молодший байт регістру адреси ППЗПЕС (EERPOM Address Register Low)

Регістр даних ППЗПЕС (EEPROM Data Register)

Регістр керування ППЗПЕС (EEPROM Control Register)

Регістр даних порта A (Data Register, Port A)

Регістр напрямку даних порта A (Data Direction Register, Port A)

Регістр входів порта A (Input Pins, Port A)

Регістр даних порта B (Data Register, Port B)

Регістр напрямку даних порта B (Data Direction Register, Port B)

Регістр входів порта B (Input Pins, Port B)

Регістр даних порта C (Data Register, Port C)

Регістр напрямку даних порта C (Data Direction Register, Port C)

Регістр входів порта C (Input Pins, Port C)

Регістр даних порта D (Data Register, Port D)

Регістр напрямку даних порта D (Data Direction Register, Port D)

Регістр входів порта D (Input Pins, Port D)

Мікропроцесори і їх програмування

5.

Простір введення/виведення МК ATmega16 (закінчення)Адреса I/O

(адреса RAM)

$0F ($2F)

$0E ($2E)

$0D ($2D)

$0C ($2C)

$0B ($2B)

$0A ($2A)

$09 ($29)

SPDR

SPSR

SPCR

UDR

UCSRA

UCSRB

UBRRL

$08 ($28)

ACSR

$07 ($27)

$06 ($26)

$05 ($25)

$04 ($24)

ADMUX

ADCSRA

ADCH

ADCL

Позначення

© Мазуренко О.В., 2018

4

Функція

Регістр даних SPI (SPI I/O Data Register)

Регістр статусу SPI (SPI Status Register)

Регістр керування SPI (SPI Control Register)

Регістр даних УАПП (UART I/O Data Register)

Регістр А керування й статусу УАПП (UART Status Register)

Регістр У керування й статусу УАПП (UART Control Register)

Регістр керування швидкістю УАПП (UART Baud Rate Register) молодший байт

Регістр статусу й керування аналогового компаратора (Analog Comparator

Control and Status Register)

Регістр вибору мультиплексора АЦП (ADC Multi plexer Select Register)

Регістр статусу й керування АЦП (ADC Control and Status Register)

Старший байт регістру даних АЦП (ADC Data Register High)

Молодший байт регістру даних АЦП (ADC Data Register Low)

Мікропроцесори і їх програмування

6.

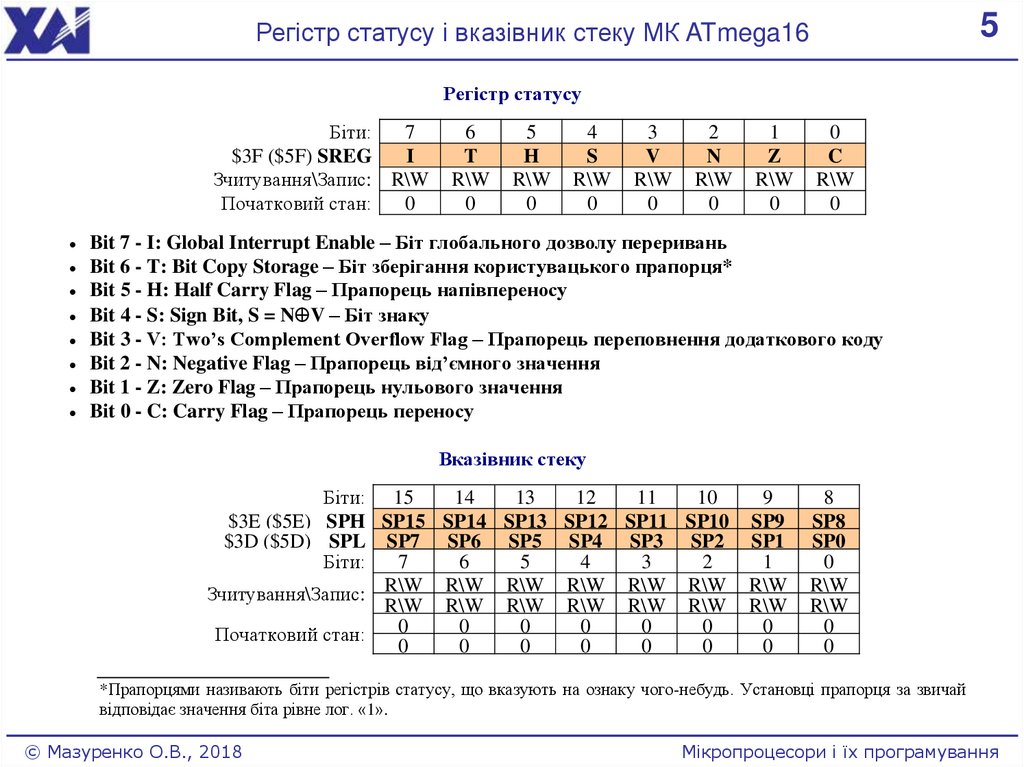

5Регістр статусу і вказівник стеку МК ATmega16

Регістр статусу

Біти:

7

$3F ($5F) SREG

I

Зчитування\Запис: R\W

Початковий стан:

0

6

T

R\W

0

5

H

R\W

0

4

S

R\W

0

3

V

R\W

0

2

N

R\W

0

1

Z

R\W

0

0

C

R\W

0

Bit 7 - I: Global Interrupt Enable – Біт глобального дозволу переривань

Bit 6 - T: Bit Copy Storage – Біт зберігання користувацького прапорця*

Bit 5 - H: Half Carry Flag – Прапорець напівпереносу

Bit 4 - S: Sign Bit, S = N V – Біт знаку

Bit 3 - V: Two’s Complement Overflow Flag – Прапорець переповнення додаткового коду

Bit 2 - N: Negative Flag – Прапорець від’ємного значення

Bit 1 - Z: Zero Flag – Прапорець нульового значення

Bit 0 - C: Carry Flag – Прапорець переносу

Вказівник стеку

Біти: 15

14

13

12

11

10

$3E ($5E) SPH SP15 SP14 SP13 SP12 SP11 SP10

$3D ($5D) SPL SP7 SP6 SP5 SP4 SP3 SP2

Біти:

7

6

5

4

3

2

Зчитування\Запис: R\W R\W R\W R\W R\W R\W

R\W R\W R\W R\W R\W R\W

0

0

0

0

0

0

Початковий стан:

0

0

0

0

0

0

9

SP9

SP1

1

R\W

R\W

0

0

8

SP8

SP0

0

R\W

R\W

0

0

*Прапорцями називають біти регістрів статусу, що вказують на ознаку чого-небудь. Установці прапорця за звичай

відповідає значення біта рівне лог. «1».

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

7.

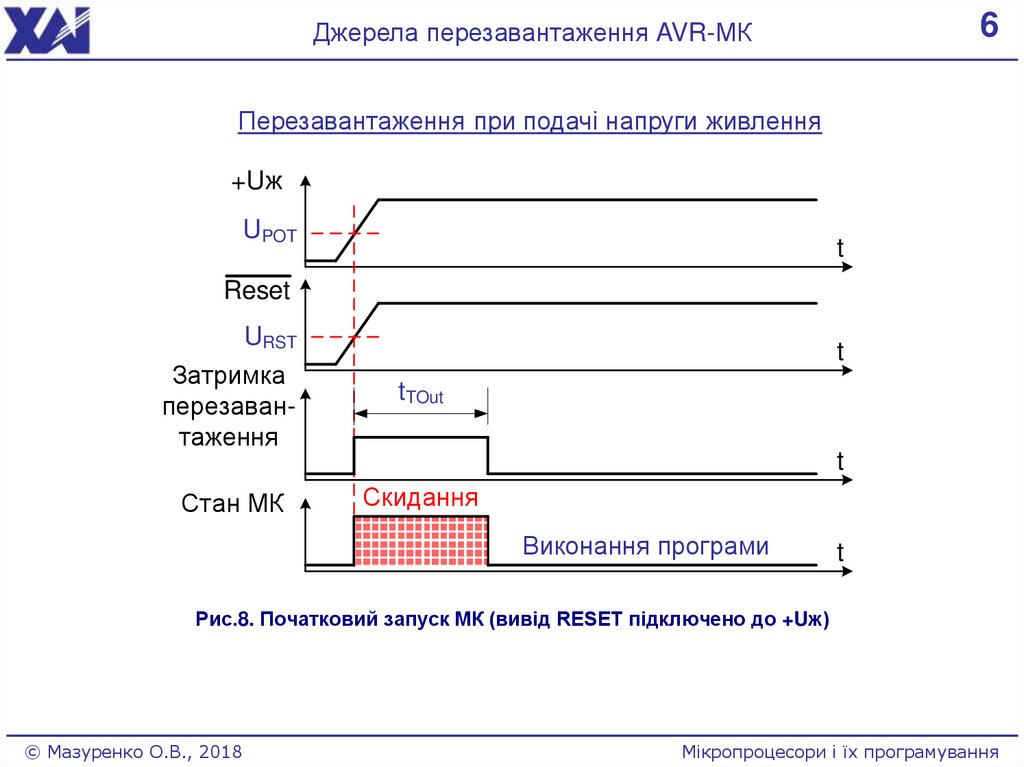

6Джерела перезавантаження AVR-МК

Перезавантаження при подачі напруги живлення

+Uж

UPOT

t

Reset

URST

t

Затримка

перезавантаження

tTOut

Стан МК

Скидання

t

Виконання програми

t

Рис.8. Початковий запуск MК (вивід RESET підключено до +Uж)

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

8.

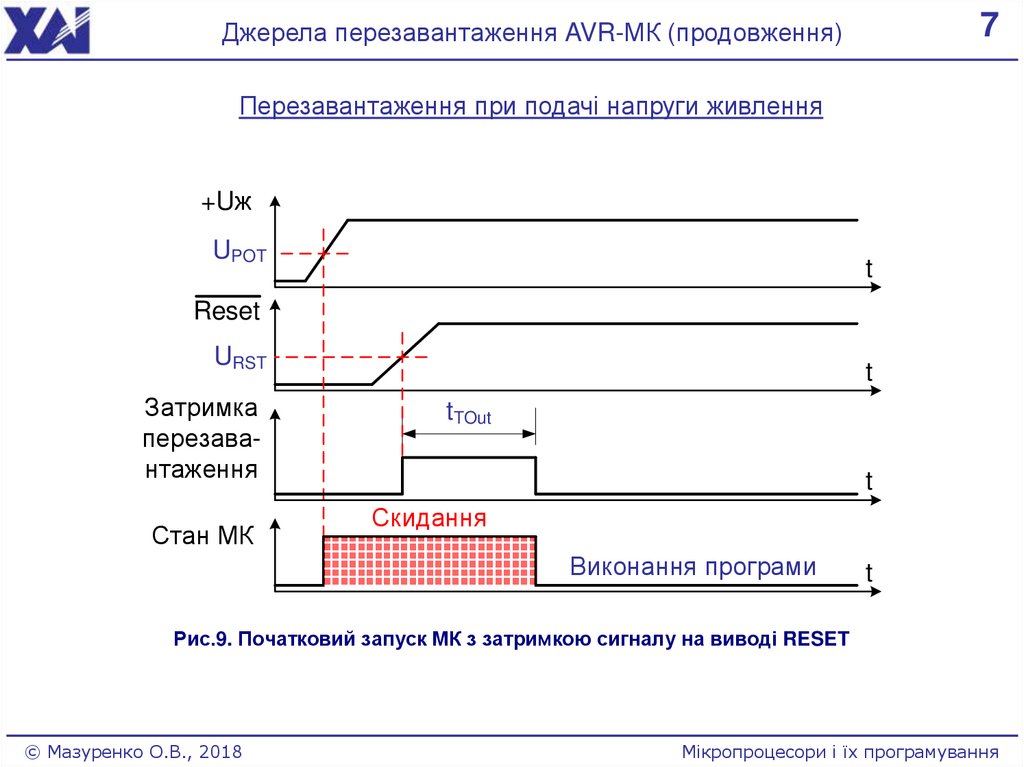

7Джерела перезавантаження AVR-МК (продовження)

Перезавантаження при подачі напруги живлення

+Uж

UPOT

t

Reset

URST

Затримка

перезавантаження

Стан МК

t

tTOut

t

Скидання

Виконання програми

t

Рис.9. Початковий запуск MК з затримкою сигналу на виводі RESET

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

9.

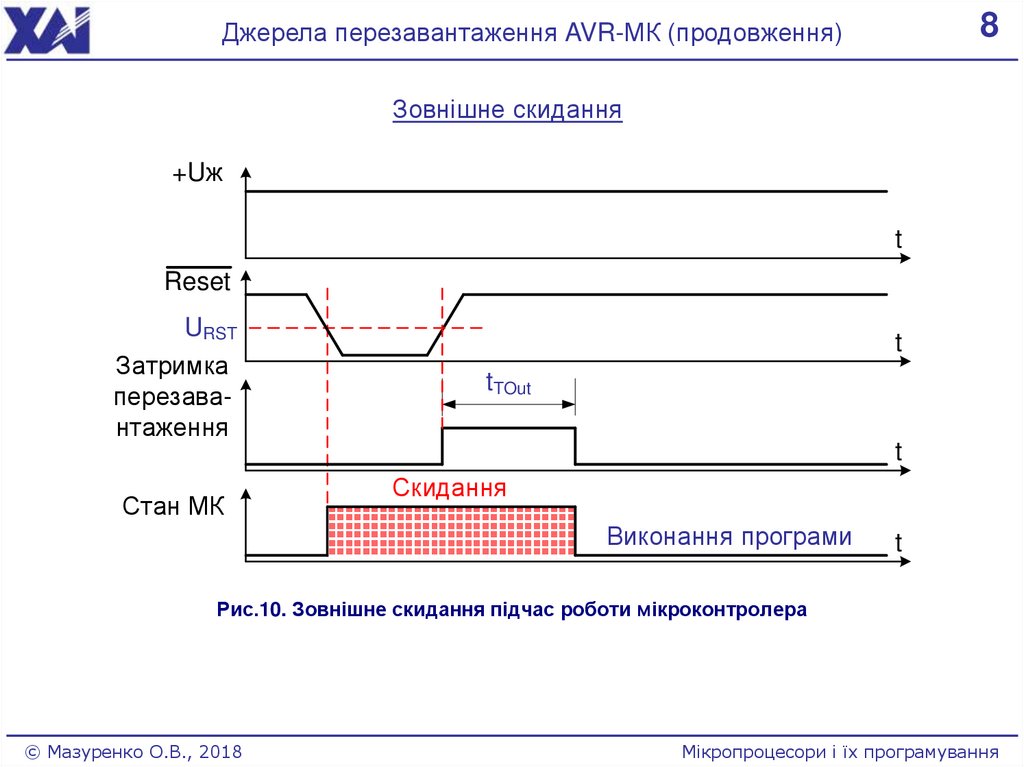

8Джерела перезавантаження AVR-МК (продовження)

Зовнішне скидання

+Uж

t

Reset

URST

Затримка

перезавантаження

Стан МК

t

tTOut

t

Скидання

Виконання програми

t

Рис.10. Зовнішне скидання підчас роботи мікроконтролера

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

10.

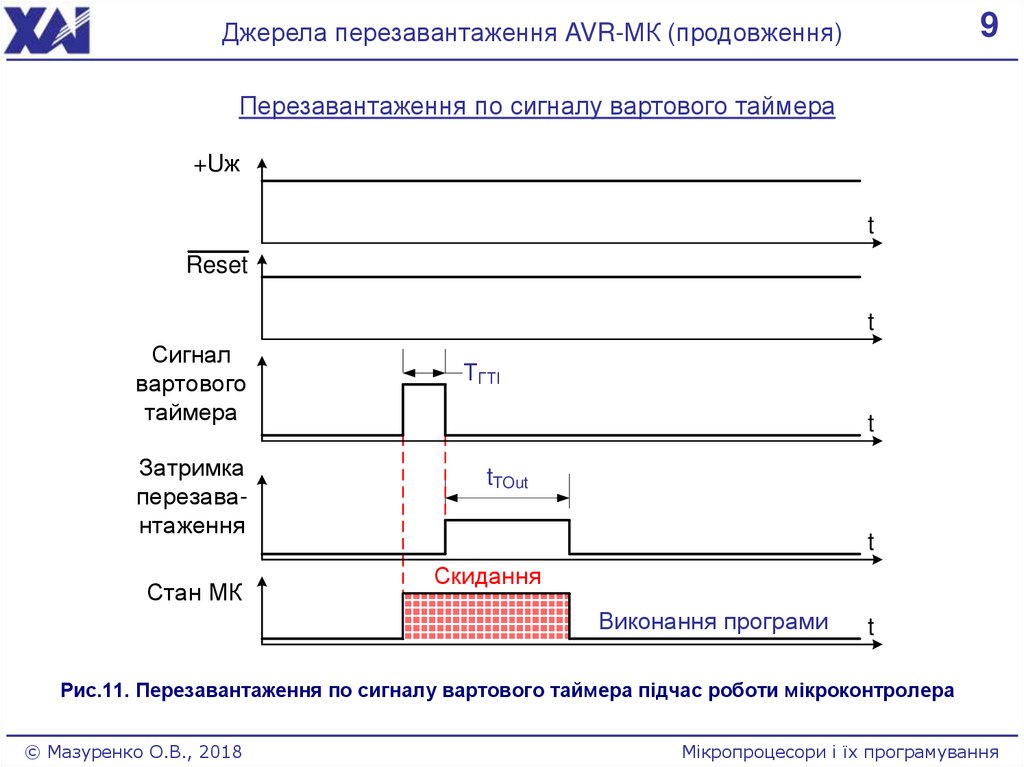

9Джерела перезавантаження AVR-МК (продовження)

Перезавантаження по сигналу вартового таймера

+Uж

t

Reset

t

Сигнал

вартового

таймера

Затримка

перезавантаження

Стан МК

ТГТІ

t

tTOut

t

Скидання

Виконання програми

t

Рис.11. Перезавантаження по сигналу вартового таймера підчас роботи мікроконтролера

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

11.

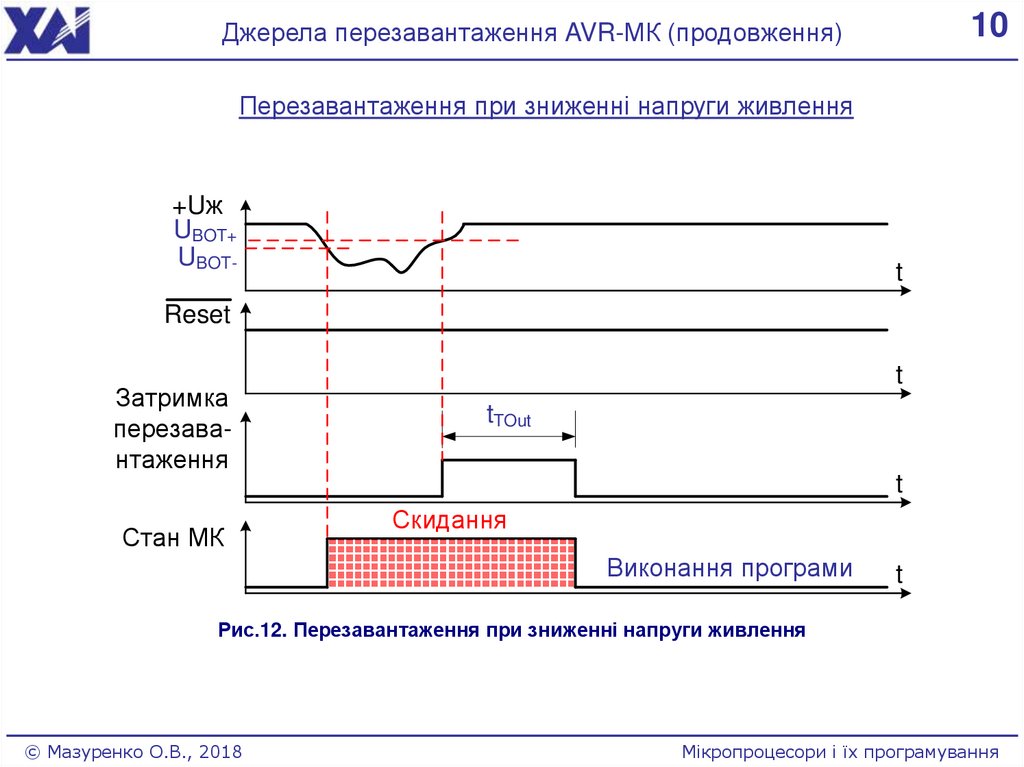

10Джерела перезавантаження AVR-МК (продовження)

Перезавантаження при зниженні напруги живлення

+Uж

UBOT+

UBOT-

t

Reset

Затримка

перезавантаження

Стан МК

t

tTOut

t

Скидання

Виконання програми

t

Рис.12. Перезавантаження при зниженні напруги живлення

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

12.

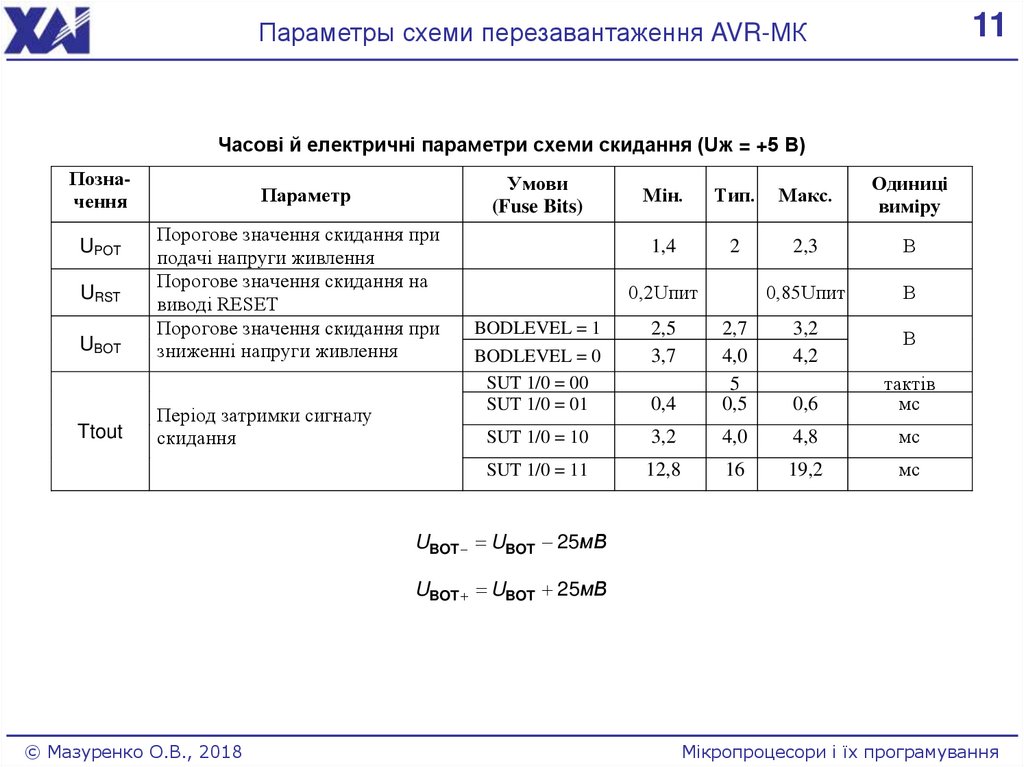

11Параметры схеми перезавантаження AVR-МК

Часові й електричні параметри схеми скидання (Uж = +5 В)

Позначення

UPOT

URST

UBOT

Ttout

Умови

(Fuse Bits)

Параметр

Порогове значення скидання при

подачі напруги живлення

Порогове значення скидання на

виводі RESET

Порогове значення скидання при

зниженні напруги живлення

Період затримки сигналу

скидання

Мін.

Тип.

Макс.

Одиниці

виміру

1,4

2

2,3

В

0,85Uпит

В

3,2

4,2

В

0,4

2,7

4,0

5

0,5

0,6

тактів

мс

SUT 1/0 = 10

3,2

4,0

4,8

мс

SUT 1/0 = 11

12,8

16

19,2

мс

0,2Uпит

BODLEVEL = 1

BODLEVEL = 0

SUT 1/0 = 00

SUT 1/0 = 01

2,5

3,7

UBOT UBOT 25мВ

UBOT UBOT 25мВ

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

13.

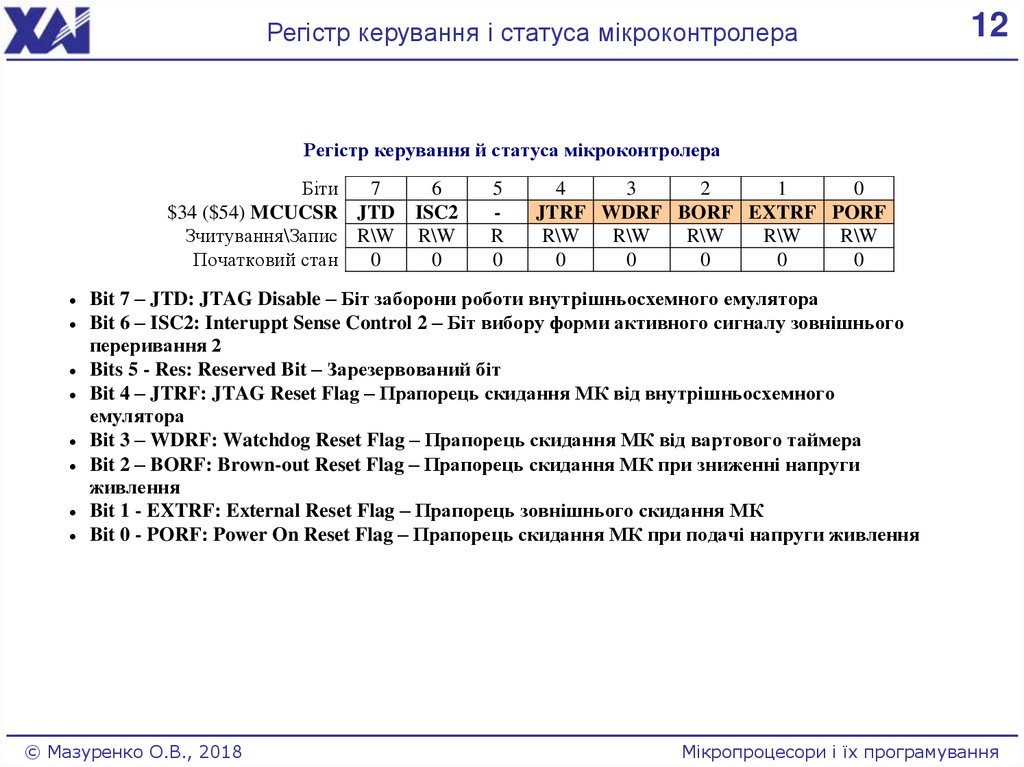

Регістр керування і статуса мікроконтролера12

Регістр керування й статуса мікроконтролера

Біти

7

$34 ($54) MCUCSR JTD

Зчитування\Запис R\W

Початковий стан

0

6

ISC2

R\W

0

5

R

0

4

3

2

1

0

JTRF WDRF BORF EXTRF PORF

R\W

R\W

R\W

R\W

R\W

0

0

0

0

0

Bit 7 – JTD: JTAG Disable – Біт заборони роботи внутрішньосхемного емулятора

Bit 6 – ISC2: Interuppt Sense Control 2 – Біт вибору форми активного сигналу зовнішнього

переривання 2

Bits 5 - Res: Reserved Bit – Зарезервований біт

Bit 4 – JTRF: JTAG Reset Flag – Прапорець скидання МК від внутрішньосхемного

емулятора

Bit 3 – WDRF: Watchdog Reset Flag – Прапорець скидання МК від вартового таймера

Bit 2 – BORF: Brown-out Reset Flag – Прапорець скидання МК при зниженні напруги

живлення

Bit 1 - EXTRF: External Reset Flag – Прапорець зовнішнього скидання МК

Bit 0 - PORF: Power On Reset Flag – Прапорець скидання МК при подачі напруги живлення

© Мазуренко О.В., 2018

Мікропроцесори і їх програмування

Программирование

Программирование