Похожие презентации:

Разработка микропрограммы и принципиальной схемы заданного блока УА

1.

Разработка микропрограммы ипринципиальной схемы

заданного блока УА

2.

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

6.3. Кодирование МО.

6.4. Структура формирователя сигналов

микрооперациий (ФСМО)

6.5. МП функционирования ЦОУ.

6.6. Разработка принципиальной

схемы УУ.

7. Определение временных

характеристик.

3.

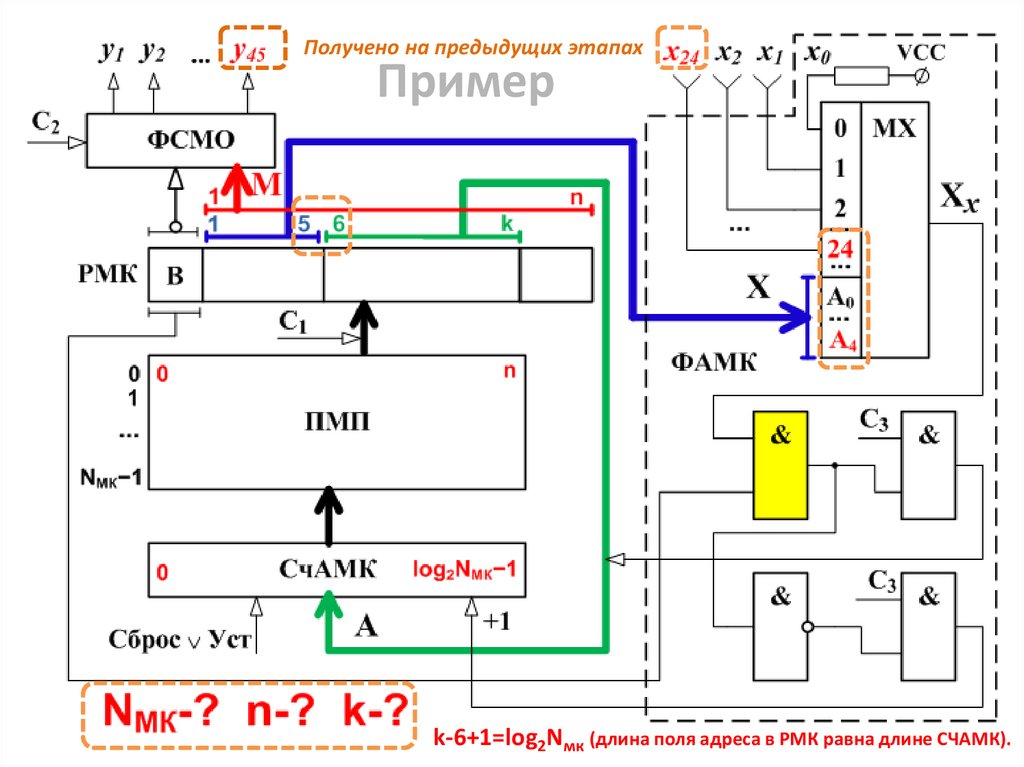

Получено на предыдущих этапахПример

k-6+1=log2Nмк (длина поля адреса в РМК равна длине СЧАМК).

4.

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

1) Расстановка адресов на чертеже «ГСА

функционирования ЦОУ» по правилам заданного

вариантом способа адресации микрокоманд.

2)Форматы команд, используемые для заданного

способа адресации, правила расстановки адресов, процесс

расстановки адресов со ссылками на код чертежа

описываются в разделе 6.2 ПЗ.

3) Выводы по разделу:

Определение NМК− числа микрокоманд в микропрограмме,

длины СчАМК, длины поля адреса в регистре микрокоманд:

РМК (6:k ).

6.3. Кодирование МО.

6.4. МП функционирования ЦОУ.

6.5. Разработка принципиальной схемы узла УУ.

7. Определение временных характеристик.

5.

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

6.3. Кодирование МО.

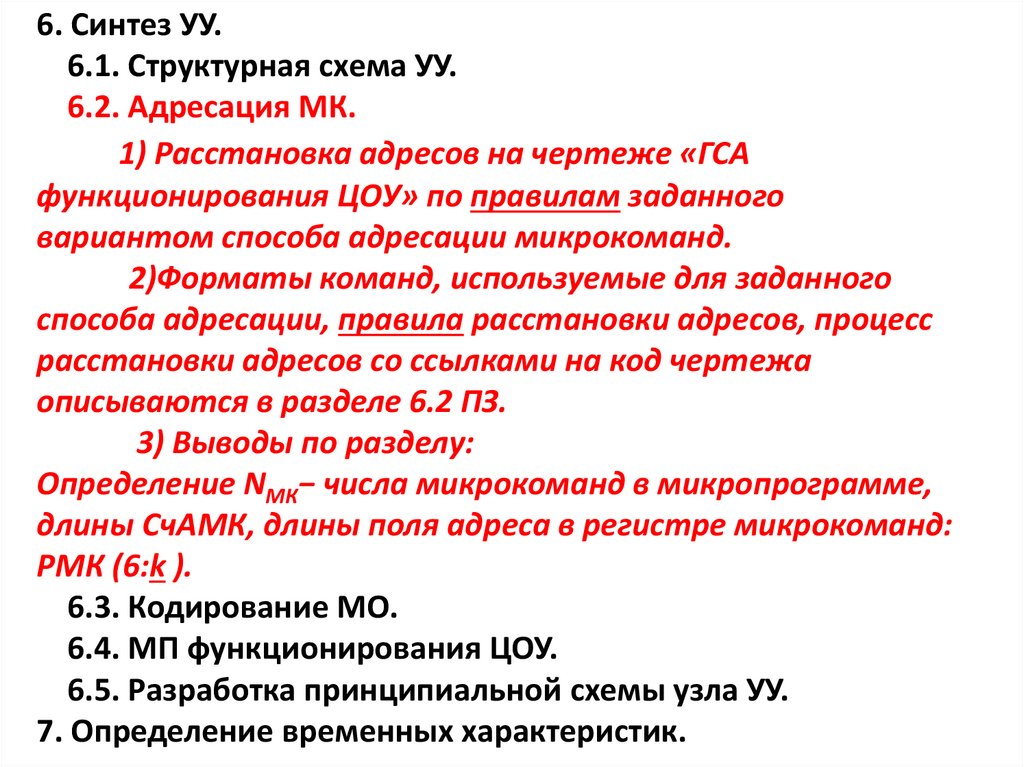

1) В разделе 6.3 ПЗ приводится описание заданного способа

кодирования операционной части микрокоманд, описание процесса

разбиения всего множества микроопераций на подмножества. Для

вертикально-горизонтального кодирования микроопераций на рисунках

(со ссылками на них в тексте!) приводится граф совместимости МО и

граф с выделенными на нем подмножествами МО, получившийся в

результате исключения из графа совместимости универсальной группы

МО. Для горизонтально-вертикального способа кодирования приводится

матрица несовместимости микроопераций (на рисунке , можно в

приложении, если такая большая, что надо согнуть лист).

2) Выводы по разделу: длина (n) и структура операционной части

микрокоманды , описание структурной схемы ФСМО со ссылкой на

соответствующий рисунок в тексте ПЗ. Результат сокращения длины

операционной части по сравнению с горизонтальным кодированием (в

битах) .

6.4. МП функционирования ЦОУ.

6.5. Разработка принципиальной

схемы узла УУ.

7. Определение временных характеристик.

6.

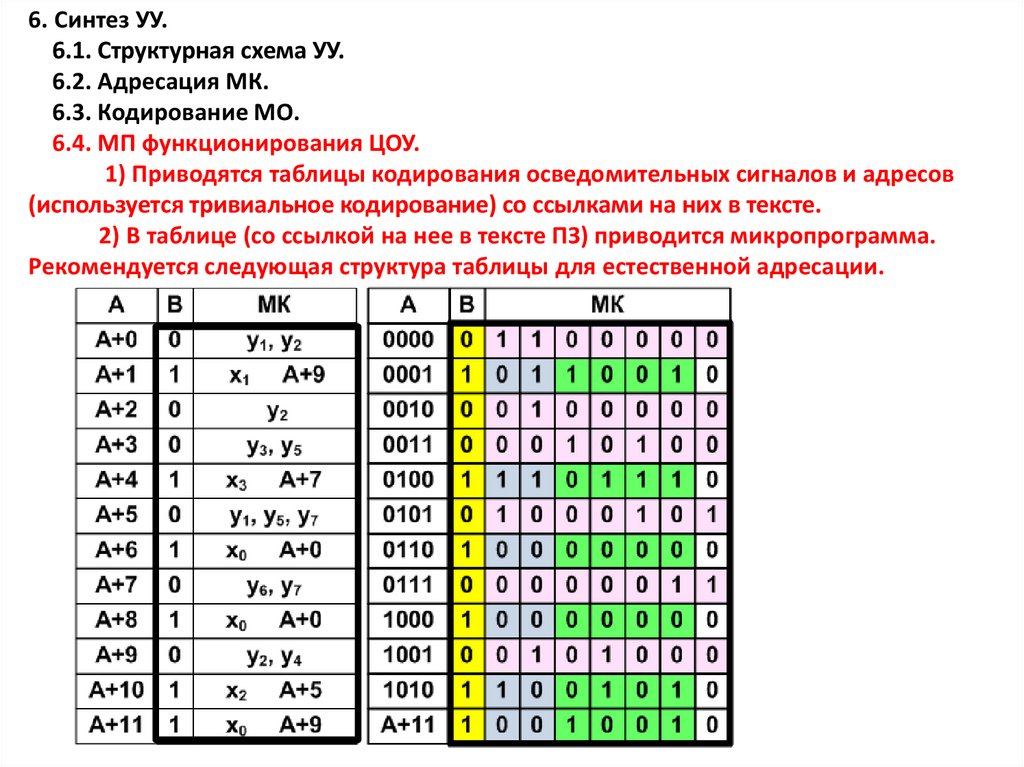

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

6.3. Кодирование МО.

6.4. МП функционирования ЦОУ.

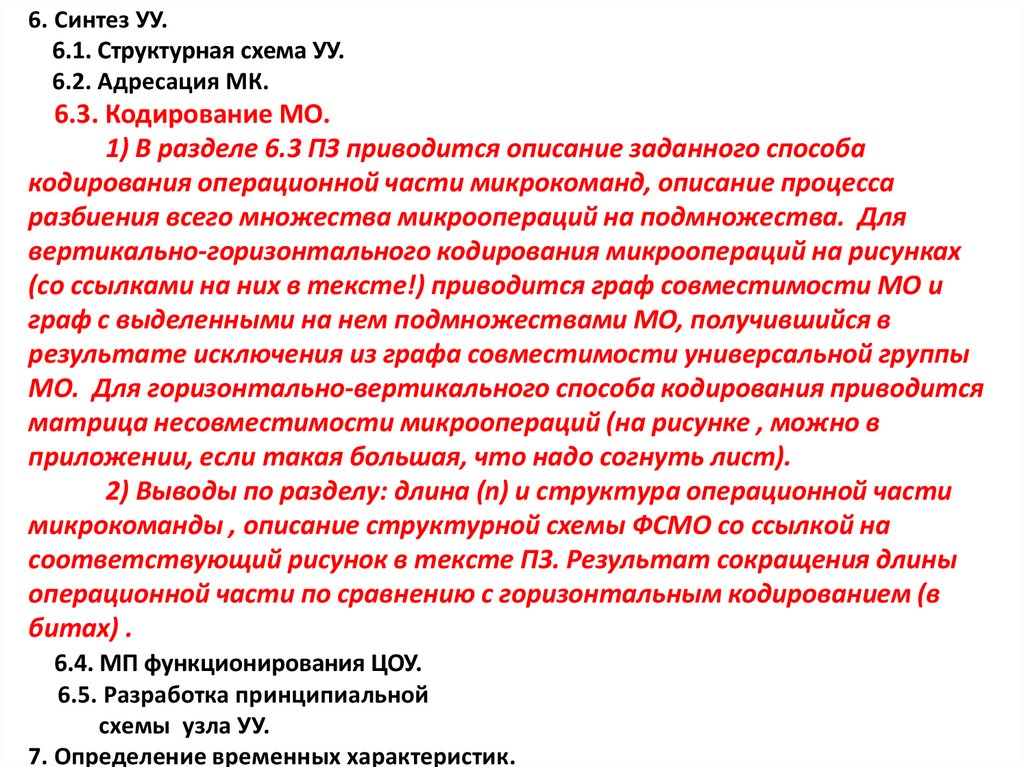

1) Приводятся таблицы кодирования осведомительных сигналов и адресов

(используется тривиальное кодирование) со ссылками на них в тексте.

2) В таблице (со ссылкой на нее в тексте ПЗ) приводится микропрограмма.

Рекомендуется следующая структура таблицы для естественной адресации.

7.

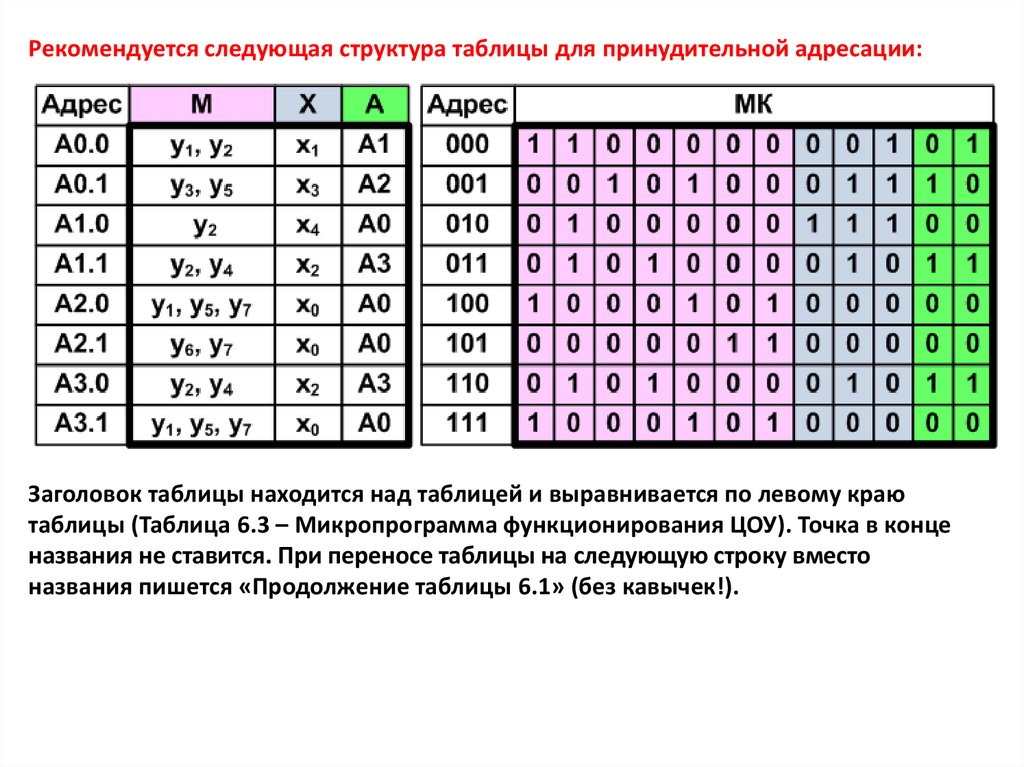

Рекомендуется следующая структура таблицы для принудительной адресации:Заголовок таблицы находится над таблицей и выравнивается по левому краю

таблицы (Таблица 6.3 – Микропрограмма функционирования ЦОУ). Точка в конце

названия не ставится. При переносе таблицы на следующую строку вместо

названия пишется «Продолжение таблицы 6.1» (без кавычек!).

8.

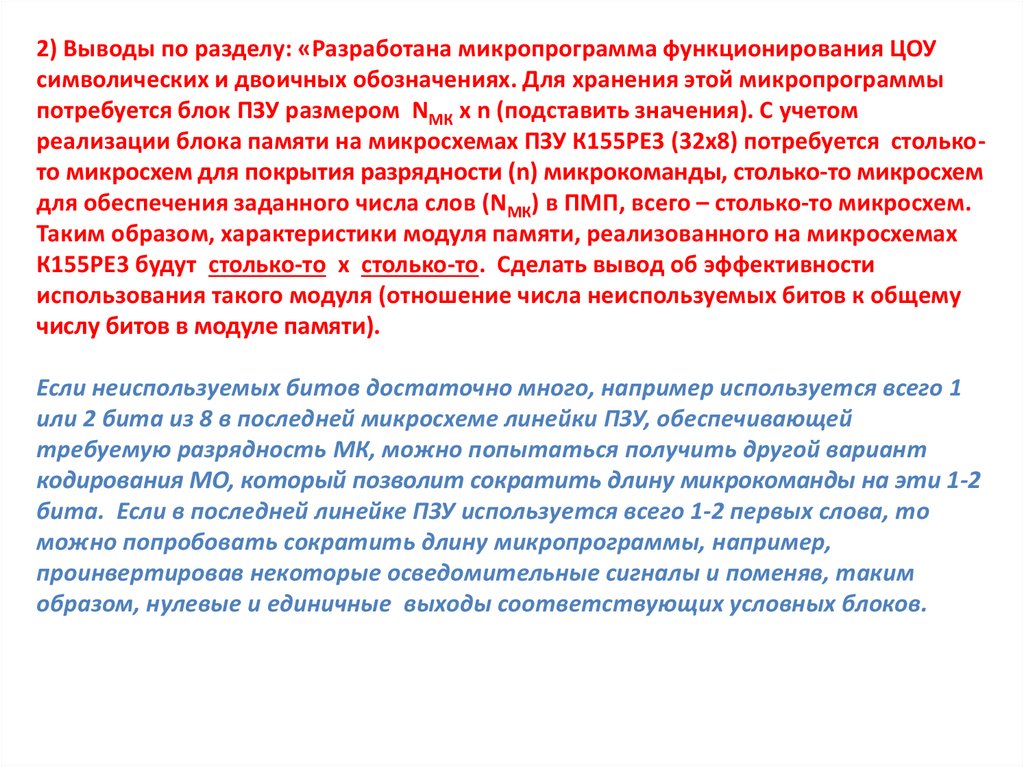

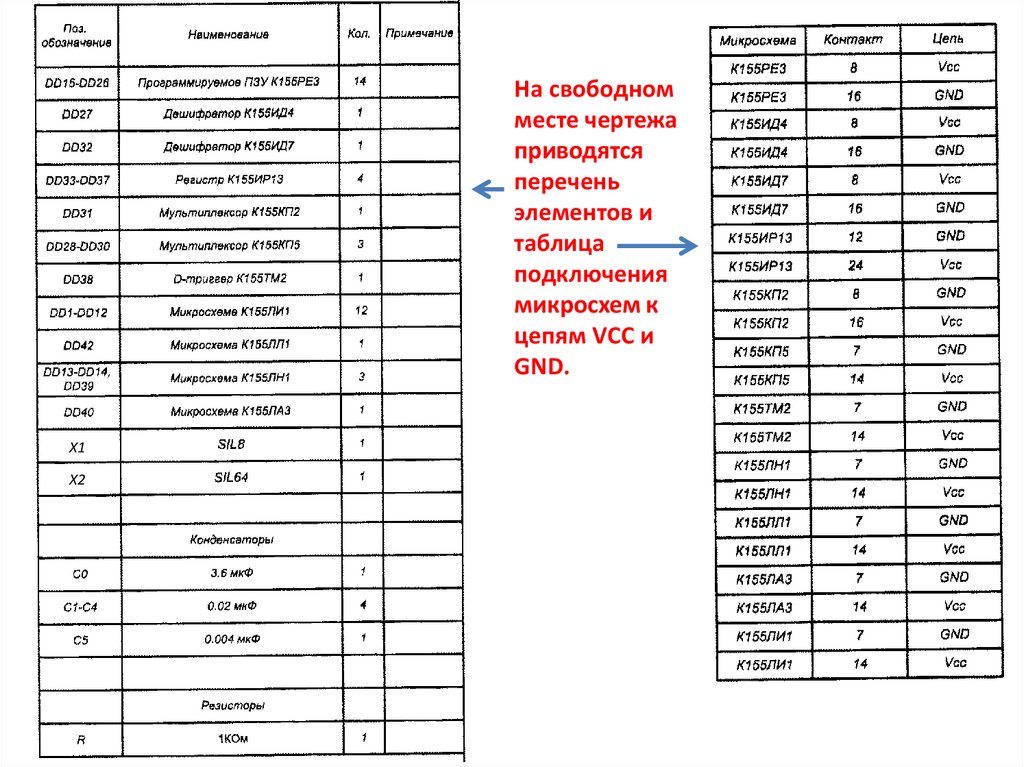

2) Выводы по разделу: «Разработана микропрограмма функционирования ЦОУсимволических и двоичных обозначениях. Для хранения этой микропрограммы

потребуется блок ПЗУ размером NМК х n (подставить значения). С учетом

реализации блока памяти на микросхемах ПЗУ К155РЕ3 (32х8) потребуется столькото микросхем для покрытия разрядности (n) микрокоманды, столько-то микросхем

для обеспечения заданного числа слов (NМК) в ПМП, всего – столько-то микросхем.

Таким образом, характеристики модуля памяти, реализованного на микросхемах

К155РЕ3 будут столько-то х столько-то. Сделать вывод об эффективности

использования такого модуля (отношение числа неиспользуемых битов к общему

числу битов в модуле памяти).

Если неиспользуемых битов достаточно много, например используется всего 1

или 2 бита из 8 в последней микросхеме линейки ПЗУ, обеспечивающей

требуемую разрядность МК, можно попытаться получить другой вариант

кодирования МО, который позволит сократить длину микрокоманды на эти 1-2

бита. Если в последней линейке ПЗУ используется всего 1-2 первых слова, то

можно попробовать сократить длину микропрограммы, например,

проинвертировав некоторые осведомительные сигналы и поменяв, таким

образом, нулевые и единичные выходы соответствующих условных блоков.

9.

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

6.3. Кодирование МО.

6.4. МП функционирования ЦОУ.

6.5. Разработка принципиальной

схемы узла УУ.

7. Определение временных характеристик.

10.

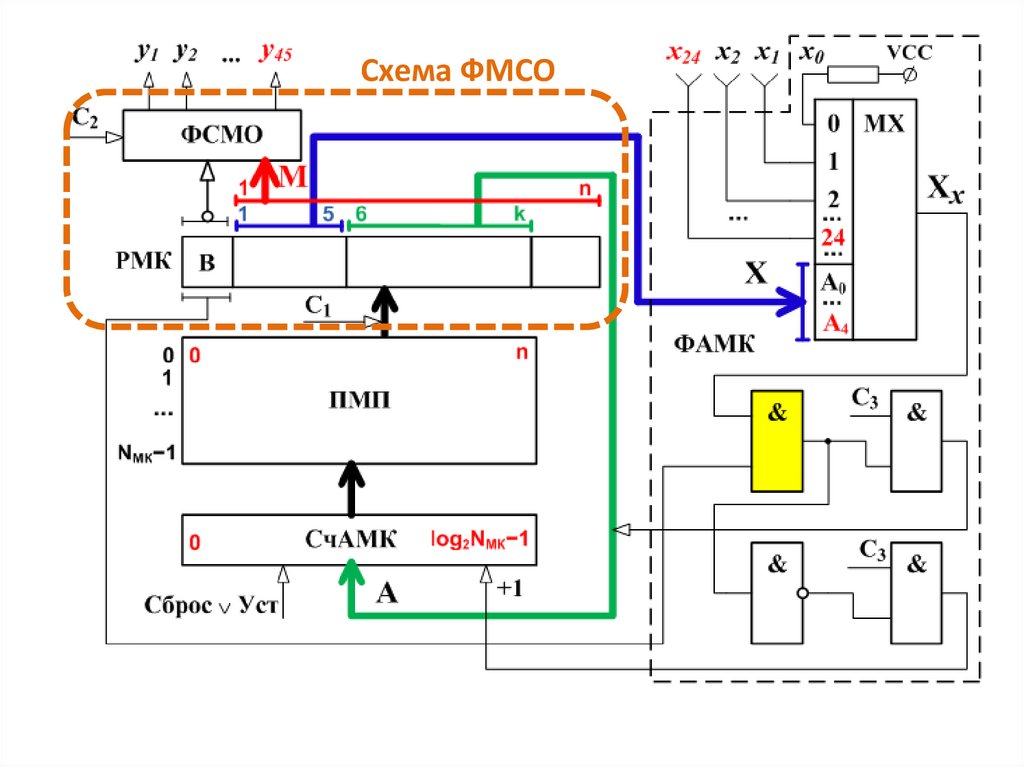

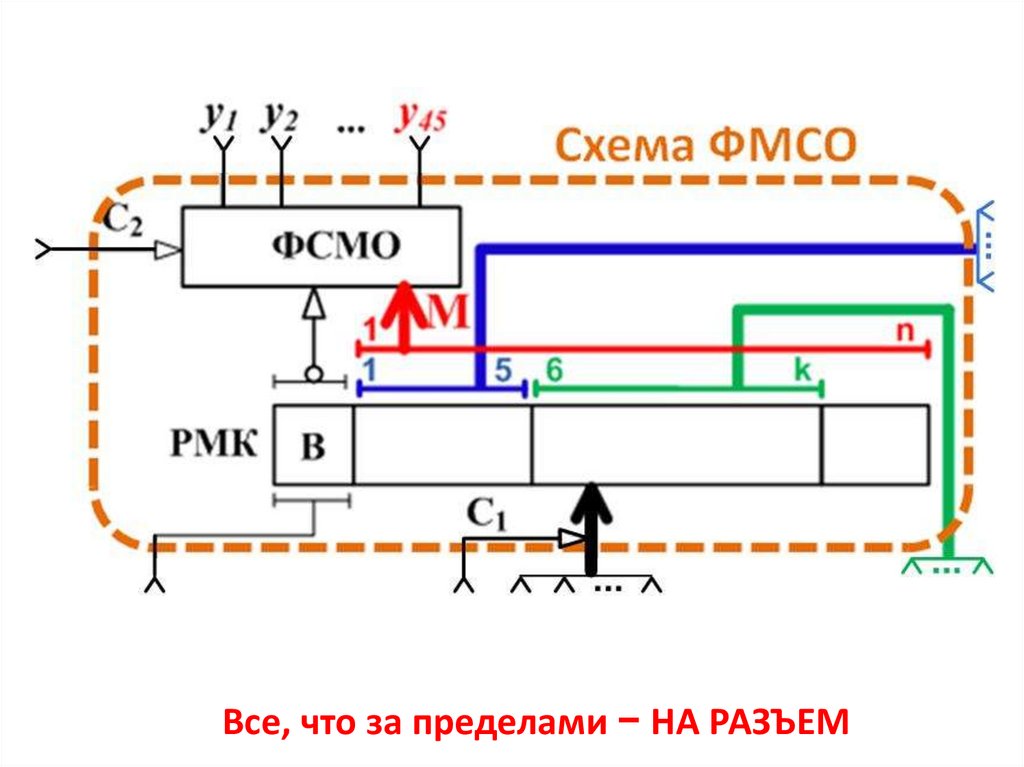

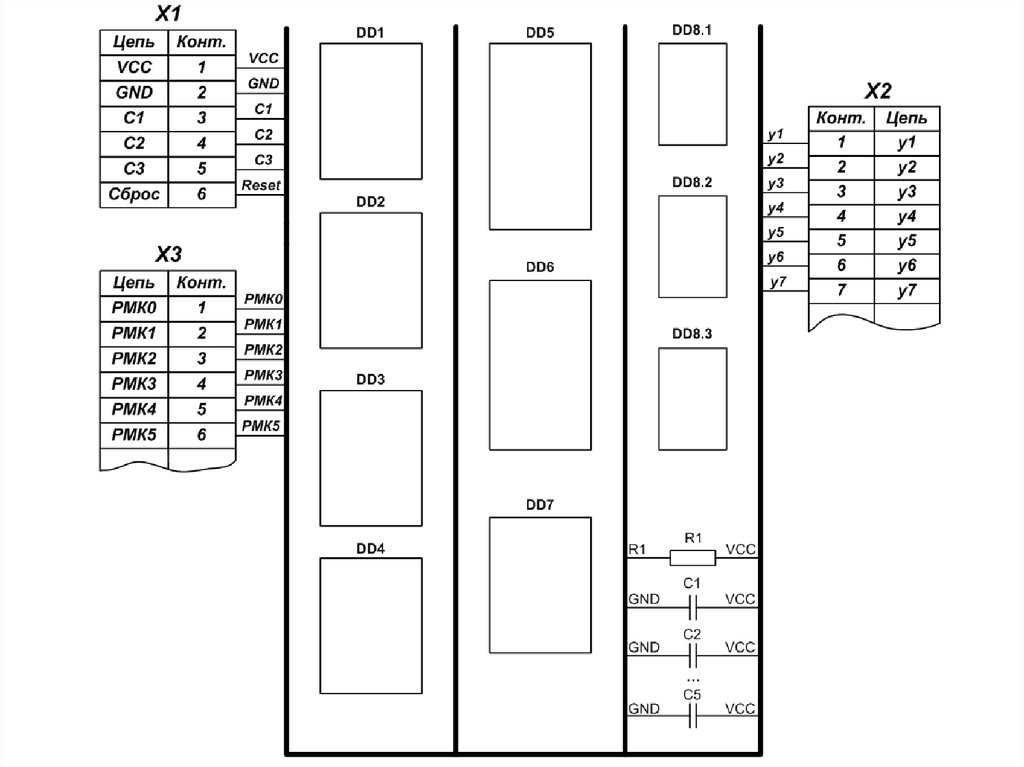

Схема ФМСО11.

Все, что за пределами − НА РАЗЪЕМ12.

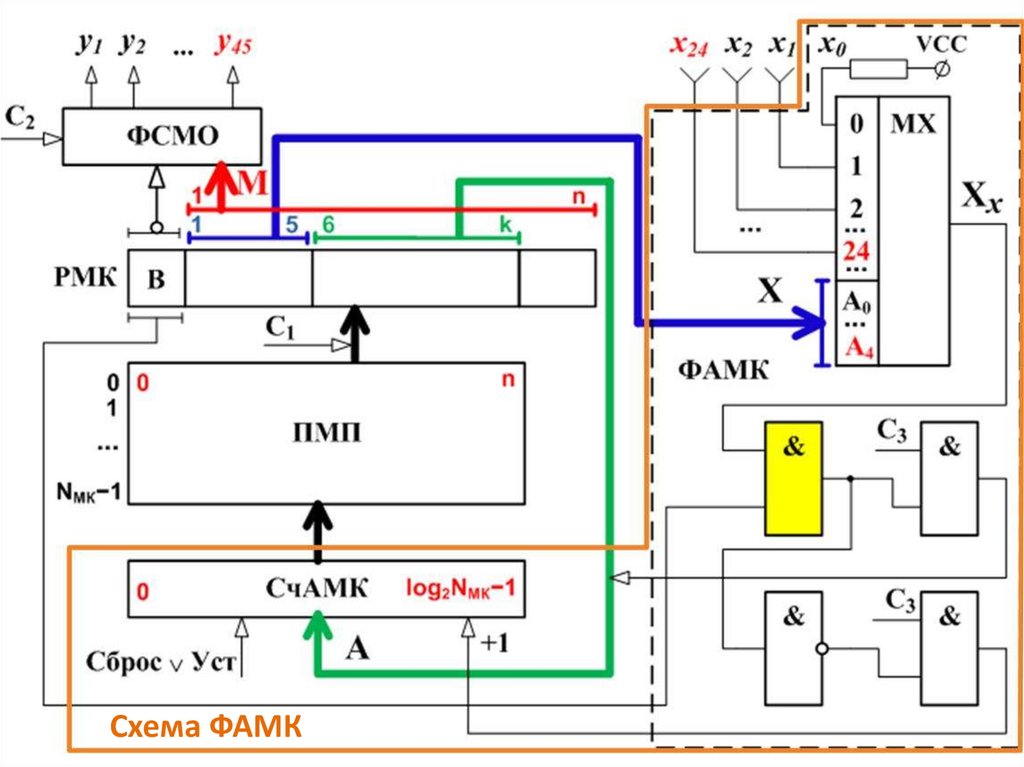

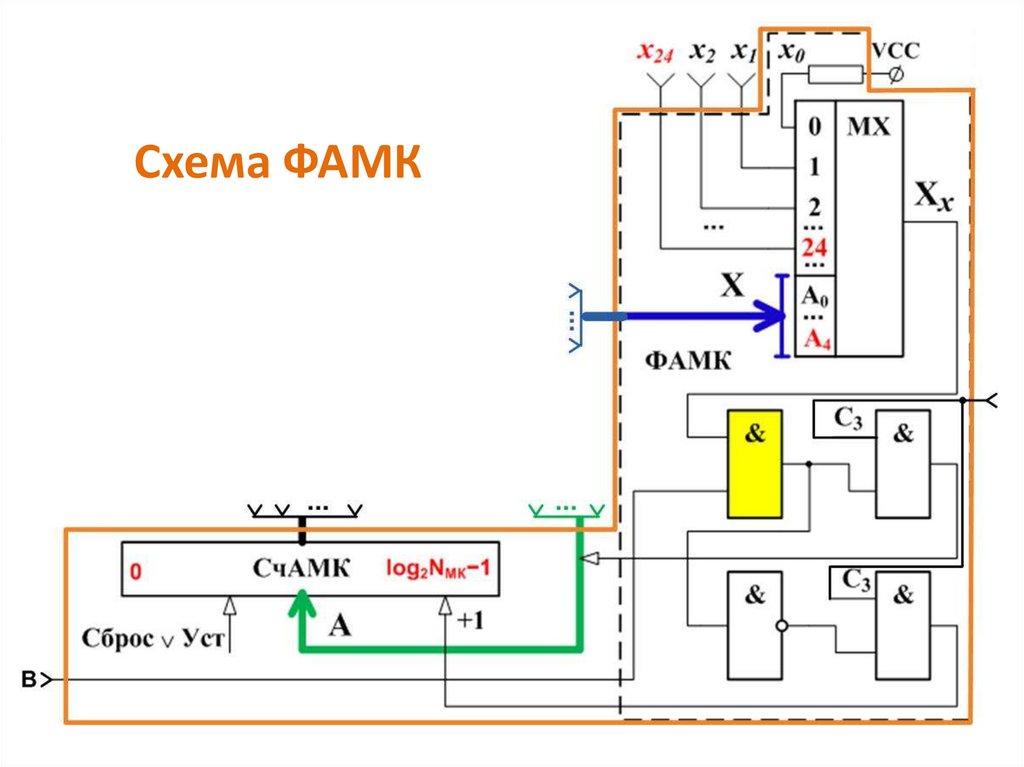

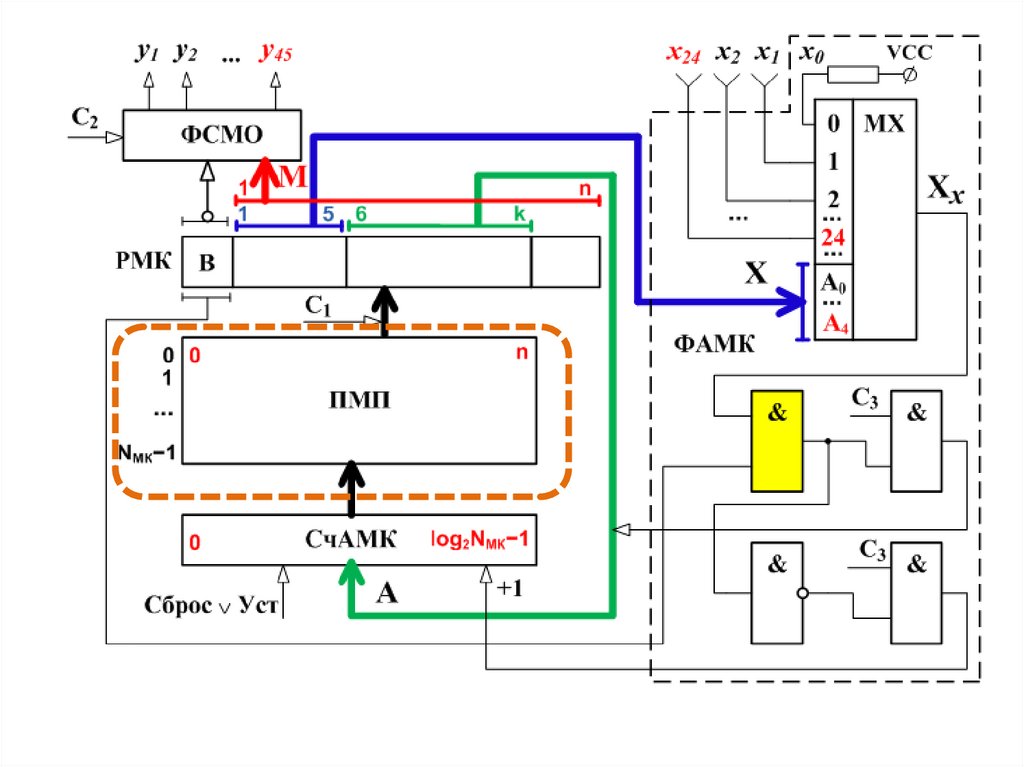

Схема ФАМК13.

Схема ФАМК14.

15.

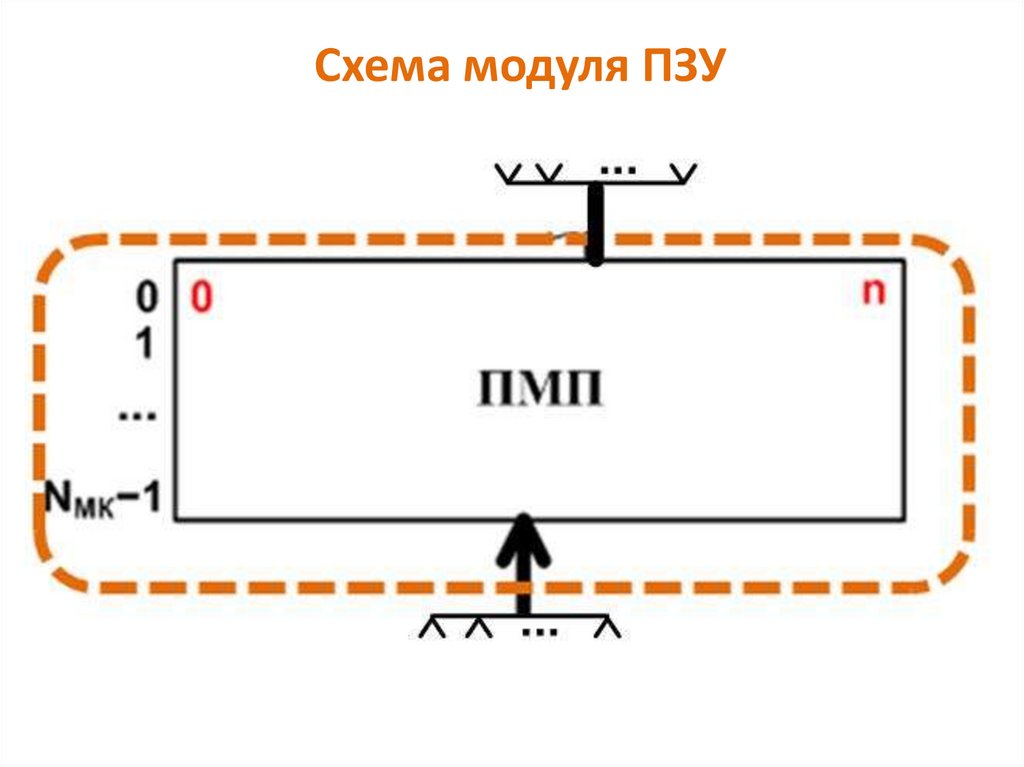

Схема модуля ПЗУ16.

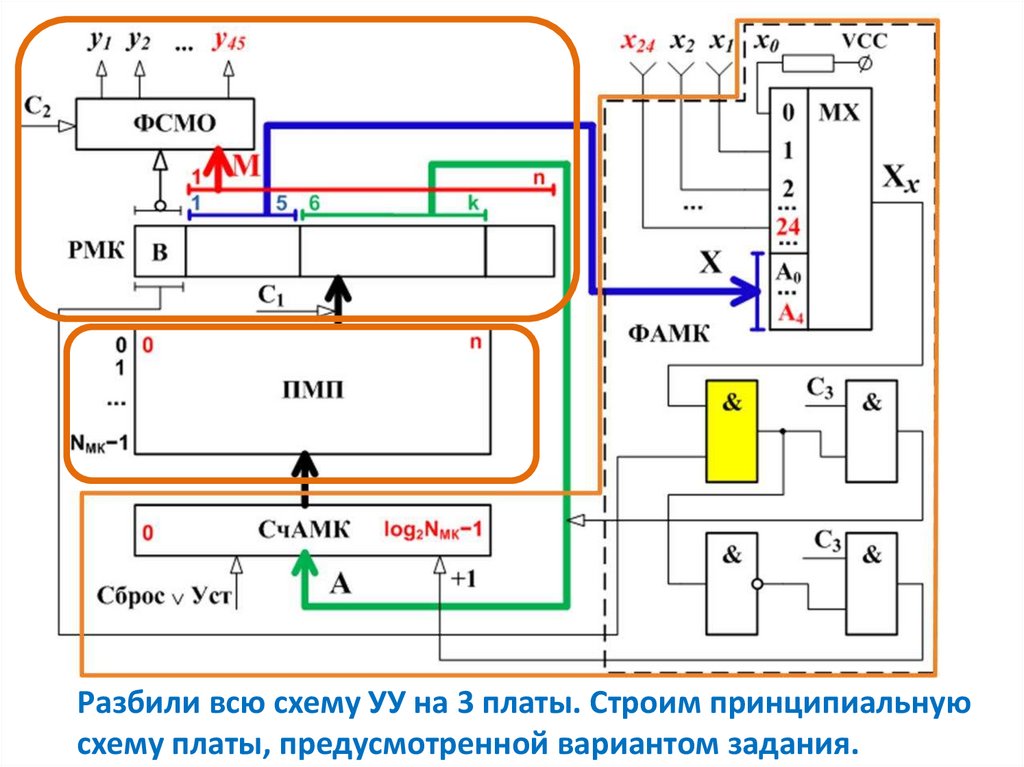

Разбили всю схему УУ на 3 платы. Строим принципиальнуюсхему платы, предусмотренной вариантом задания.

17.

Желающие могутпостроить схему УУ

полностью

18.

Примеры обозначения разъемов на принципиальной схеме19.

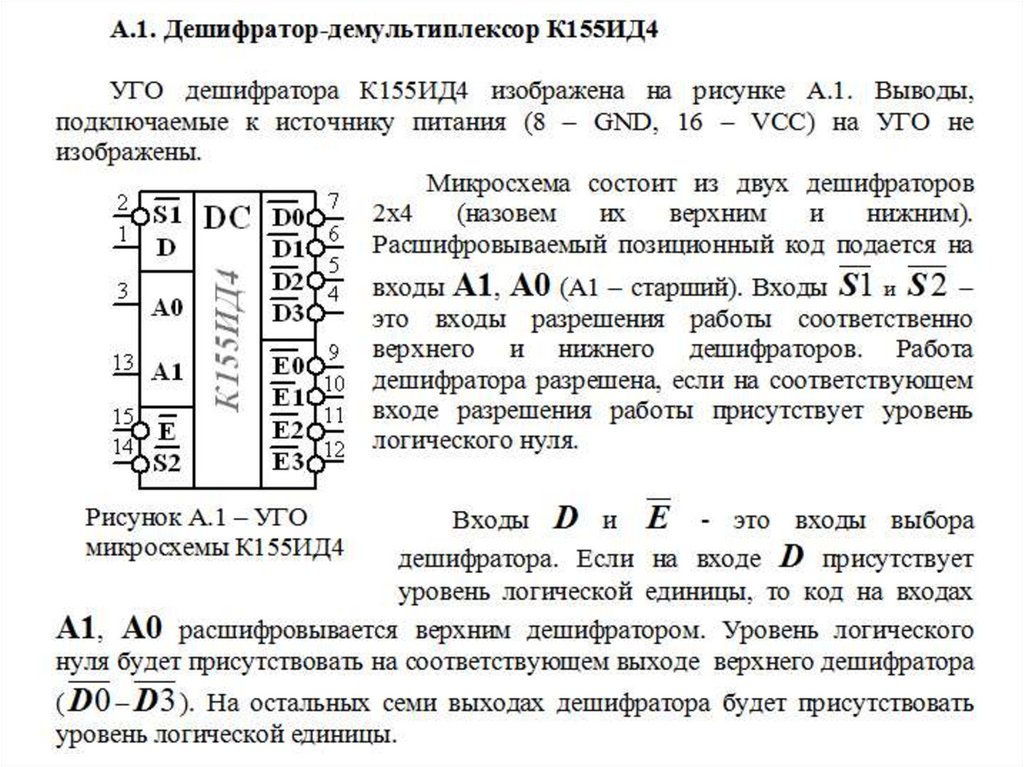

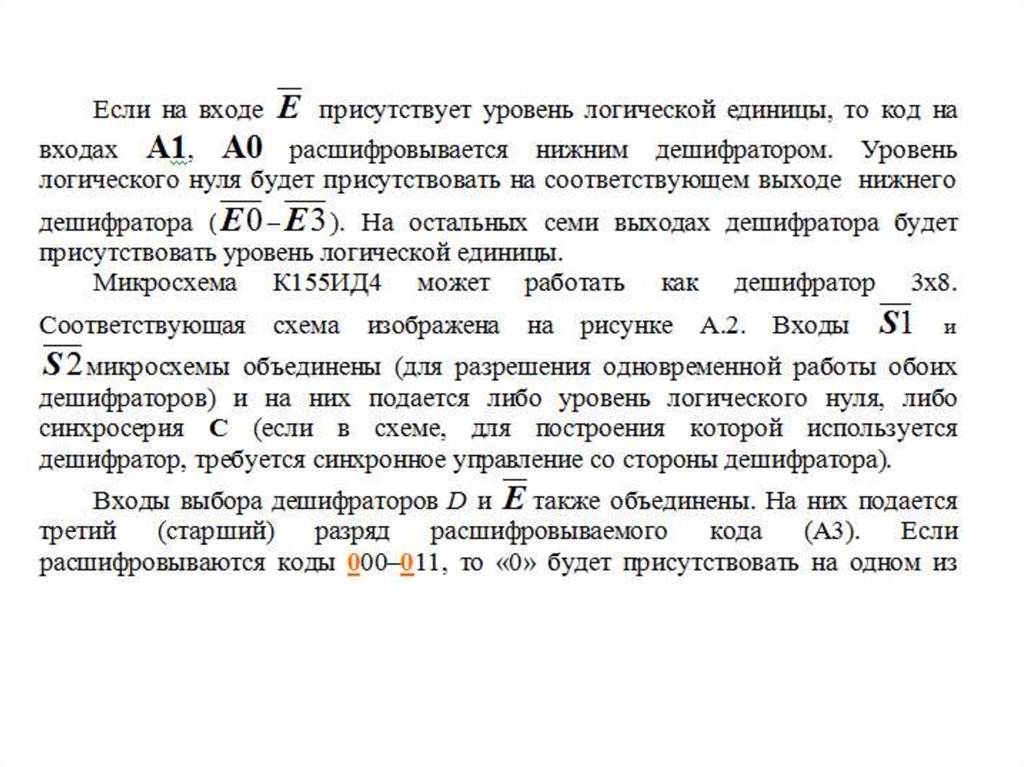

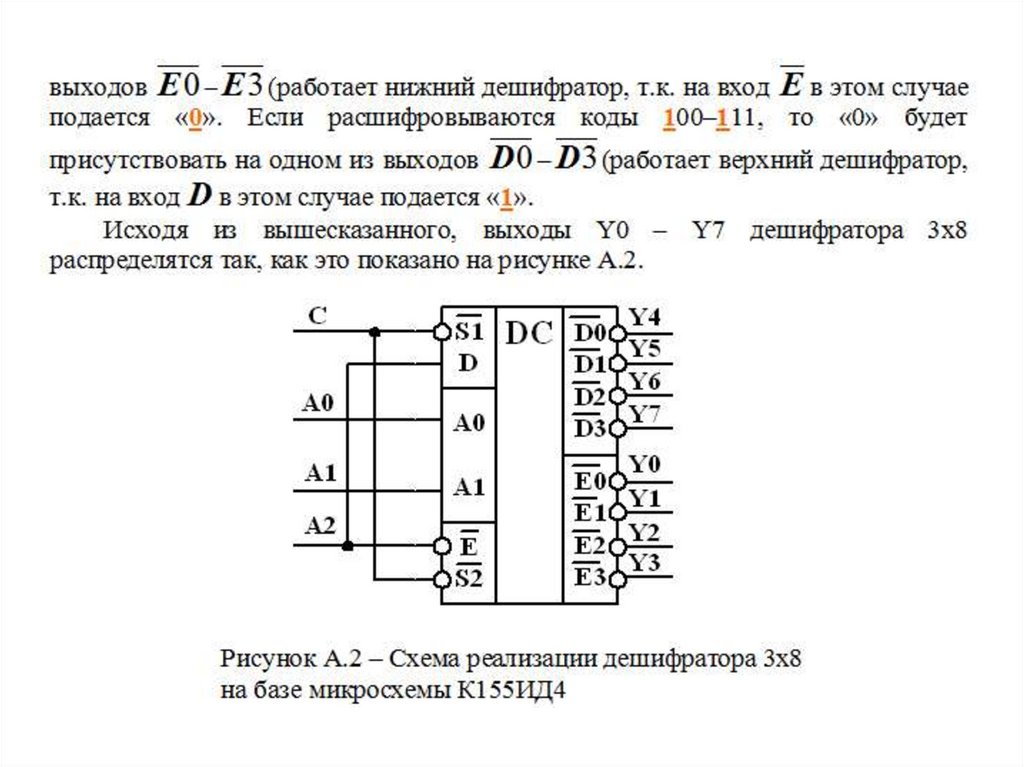

Несколько следующихслайдов демонстрируют

УГО некоторых микросхем,

их описание и полезные

схемы (материал из курса

АКС).

20.

УГО микросхемК155ИР13

21.

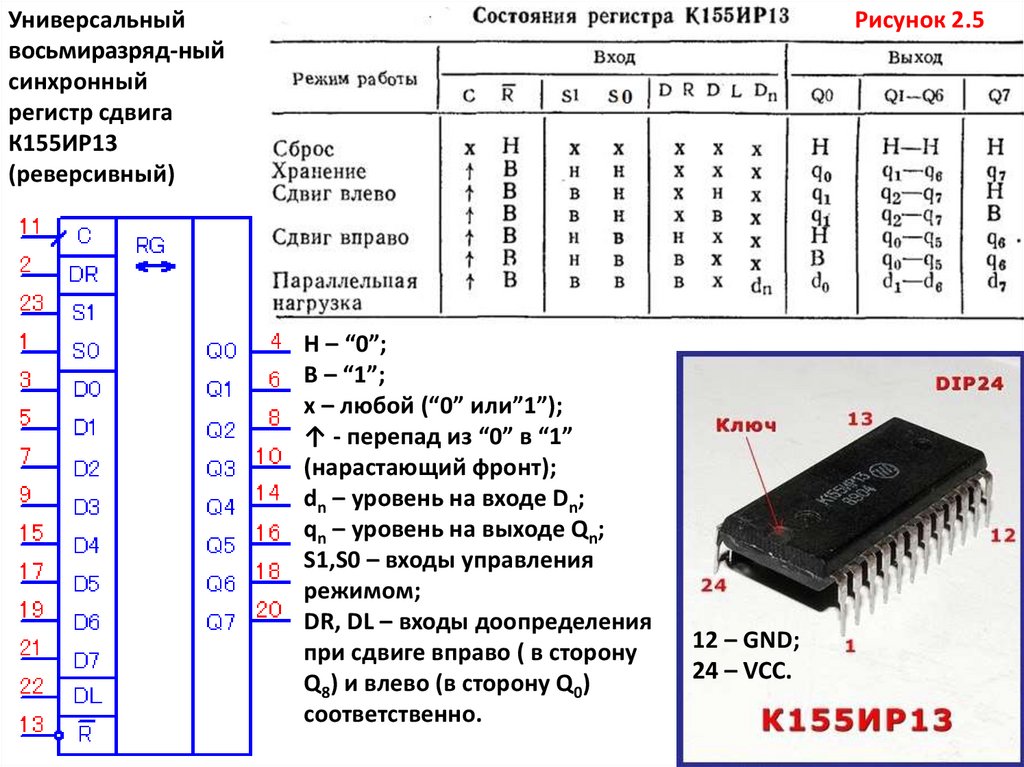

Универсальныйвосьмиразряд-ный

синхронный

регистр сдвига

К155ИР13

(реверсивный)

Рисунок 2.5

H – “0”;

В – “1”;

x – любой (“0” или”1”);

↑ - перепад из “0” в “1”

(нарастающий фронт);

dn – уровень на входе Dn;

qn – уровень на выходе Qn;

S1,S0 – входы управления

режимом;

DR, DL – входы доопределения

при сдвиге вправо ( в сторону

Q8) и влево (в сторону Q0)

соответственно.

12 – GND;

24 – VCC.

22.

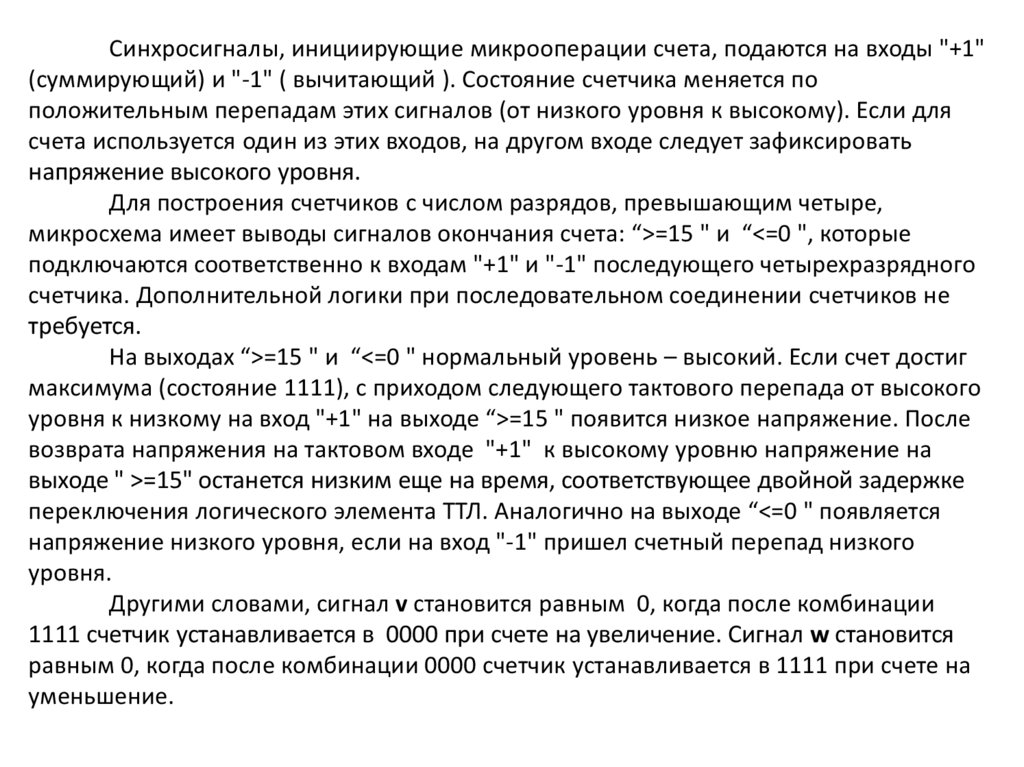

Четырехразрядный реверсивный двоичныйсчетчик в интегральном исполнении К155ИЕ7

Состояния счетчика:

23.

Синхросигналы, инициирующие микрооперации счета, подаются на входы "+1"(суммирующий) и "-1" ( вычитающий ). Состояние счетчика меняется по

положительным перепадам этих сигналов (от низкого уровня к высокому). Если для

счета используется один из этих входов, на другом входе следует зафиксировать

напряжение высокого уровня.

Для построения счетчиков с числом разрядов, превышающим четыре,

микросхема имеет выводы сигналов окончания счета: “>=15 " и “<=0 ", которые

подключаются соответственно к входам "+1" и "-1" последующего четырехразрядного

счетчика. Дополнительной логики при последовательном соединении счетчиков не

требуется.

На выходах “>=15 " и “<=0 " нормальный уровень – высокий. Если счет достиг

максимума (состояние 1111), с приходом следующего тактового перепада от высокого

уровня к низкому на вход "+1" на выходе “>=15 " появится низкое напряжение. После

возврата напряжения на тактовом входе "+1" к высокому уровню напряжение на

выходе " >=15" останется низким еще на время, соответствующее двойной задержке

переключения логического элемента ТТЛ. Аналогично на выходе “<=0 " появляется

напряжение низкого уровня, если на вход "-1" пришел счетный перепад низкого

уровня.

Другими словами, сигнал v становится равным 0, когда после комбинации

1111 счетчик устанавливается в 0000 при счете на увеличение. Сигнал w становится

равным 0, когда после комбинации 0000 счетчик устанавливается в 1111 при счете на

уменьшение.

24.

25.

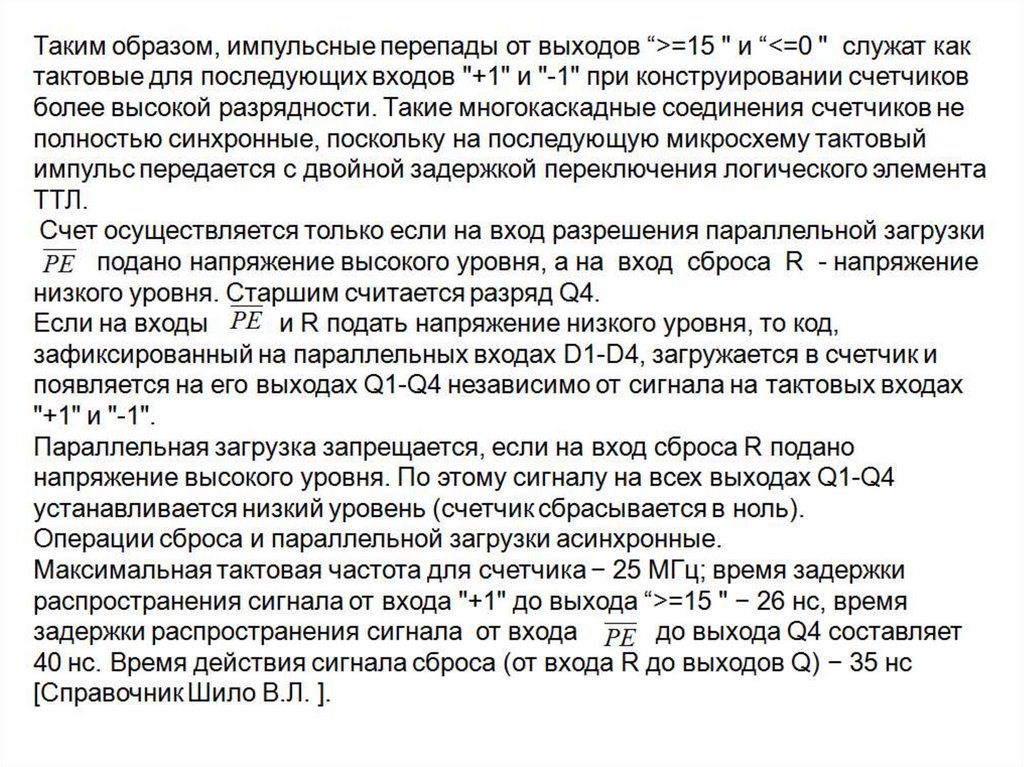

Дешифратор в интегральном исполнении −микросхема К155ИД7 (К555ИД7)

Активный уровень ("0") присутствует на выходе, номер которого

равен значению позиционного кода x2, x1, x0 (x2 – старший разряд),

поданному на входы A2, A1, A0, если для потенциалов на входах

разрешения работы (Enable) выполняется условие: E0 E1 E2 1. На всех

остальных выходах – уровень "1“.

26.

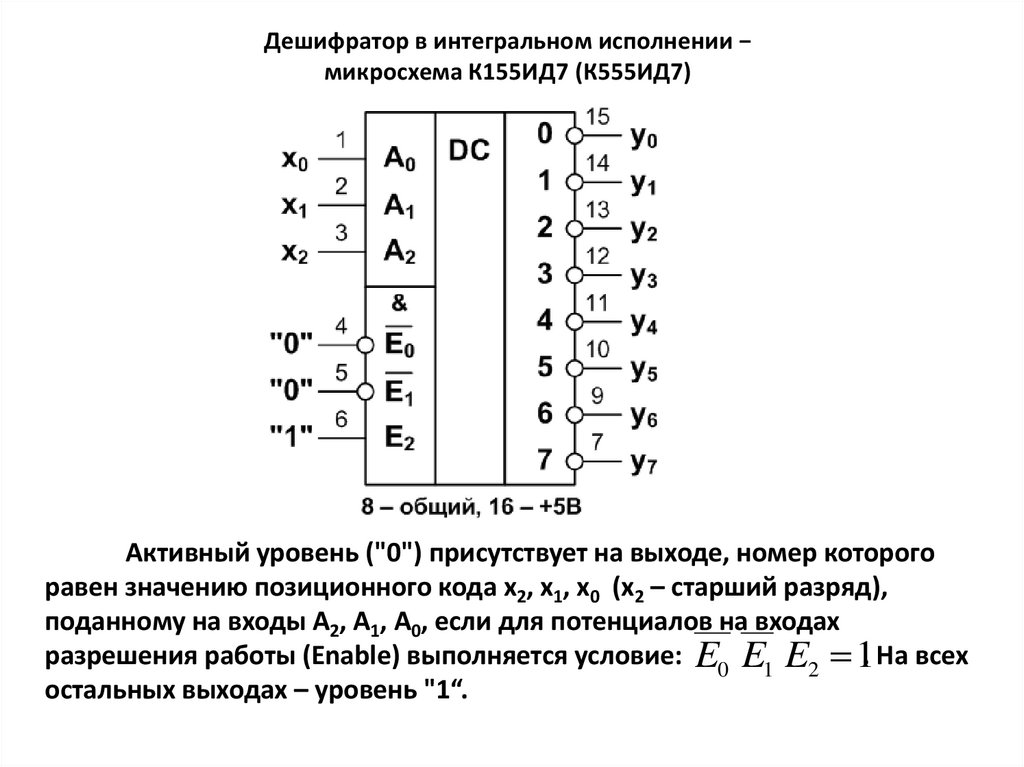

Схема дешифратора 5x3227.

28.

29.

30.

31.

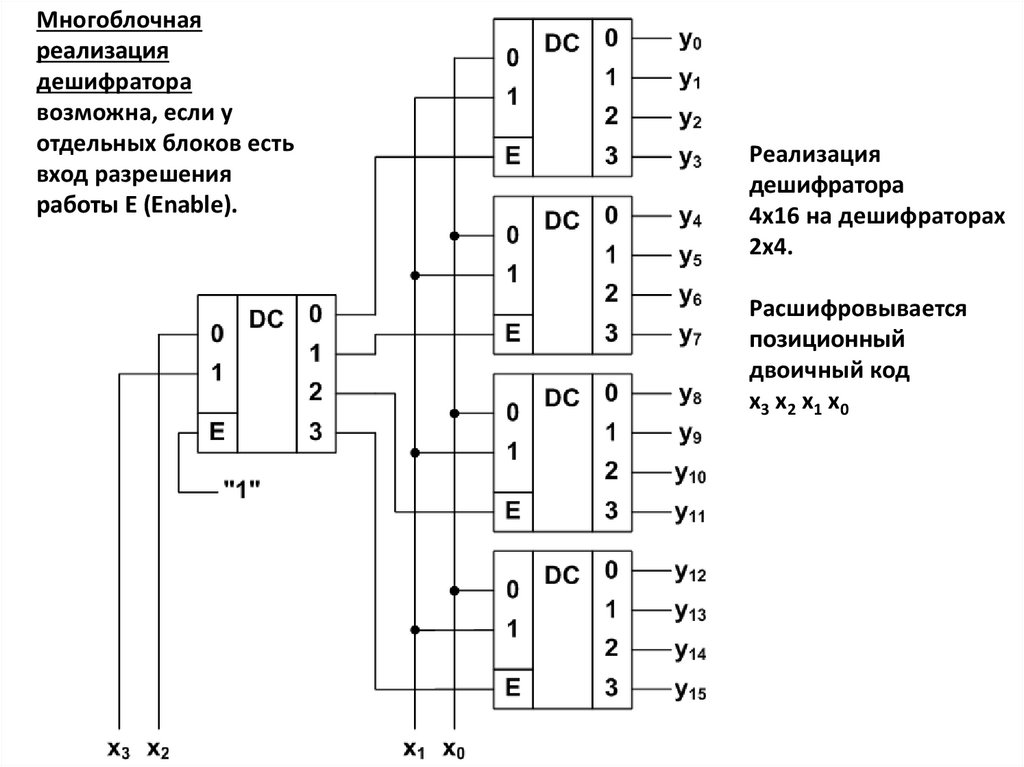

Многоблочнаяреализация

дешифратора

возможна, если у

отдельных блоков есть

вход разрешения

работы E (Enable).

Реализация

дешифратора

4x16 на дешифраторах

2x4.

Расшифровывается

позиционный

двоичный код

х3 х2 х1 х0

32.

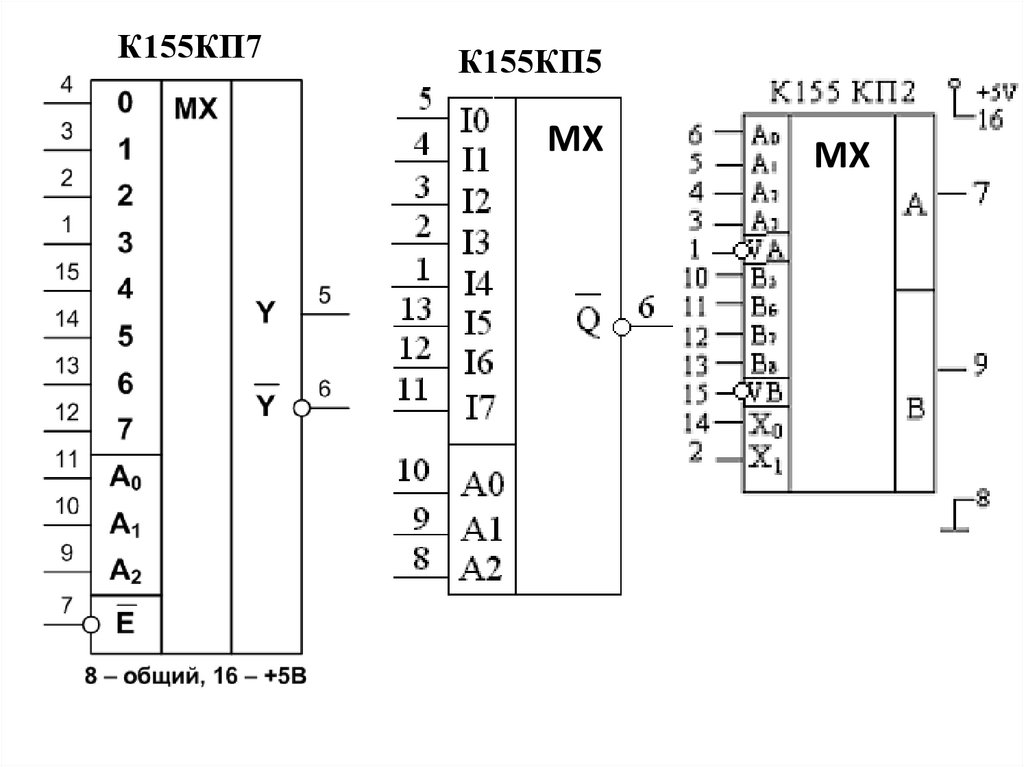

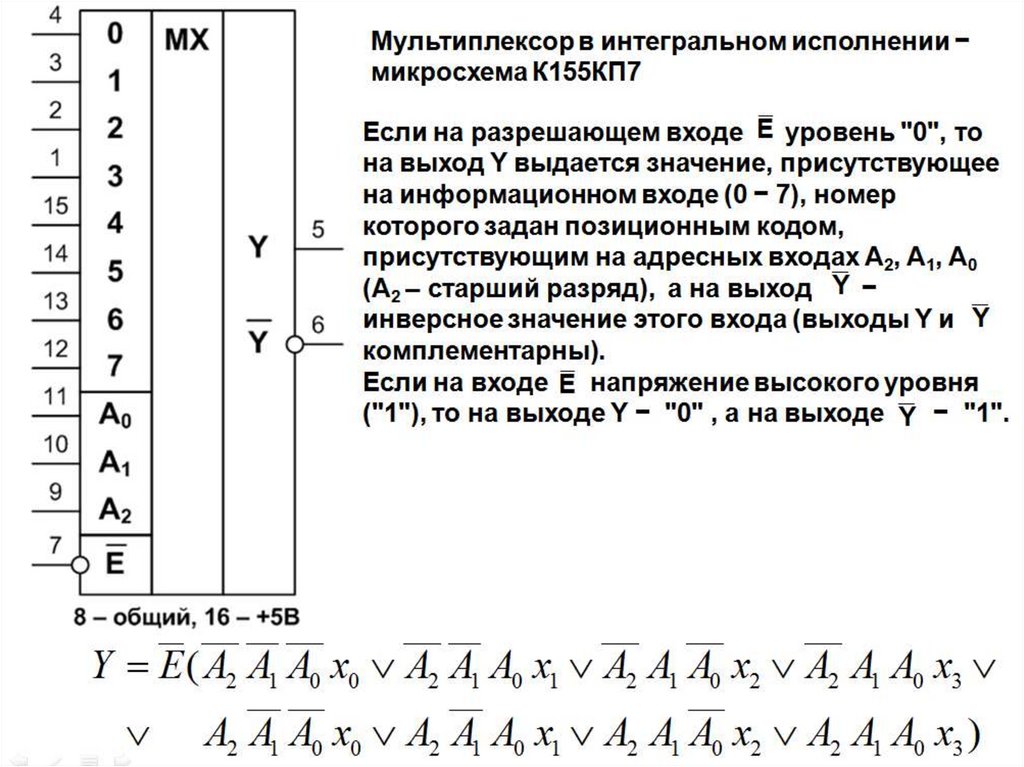

К155КП7К155КП5

MX

MX

33.

34.

Реализация мультиплексора 16x1 на микросхемах К155КП735.

Блочная реализация 16 канальногомультиплексора на четырехканальных

мультиплексорах.

Адресные входы: A3 A2 A1 A0

Число адресных входов

мультиплексора равно log2 от числа

каналов (информационных входов).

36.

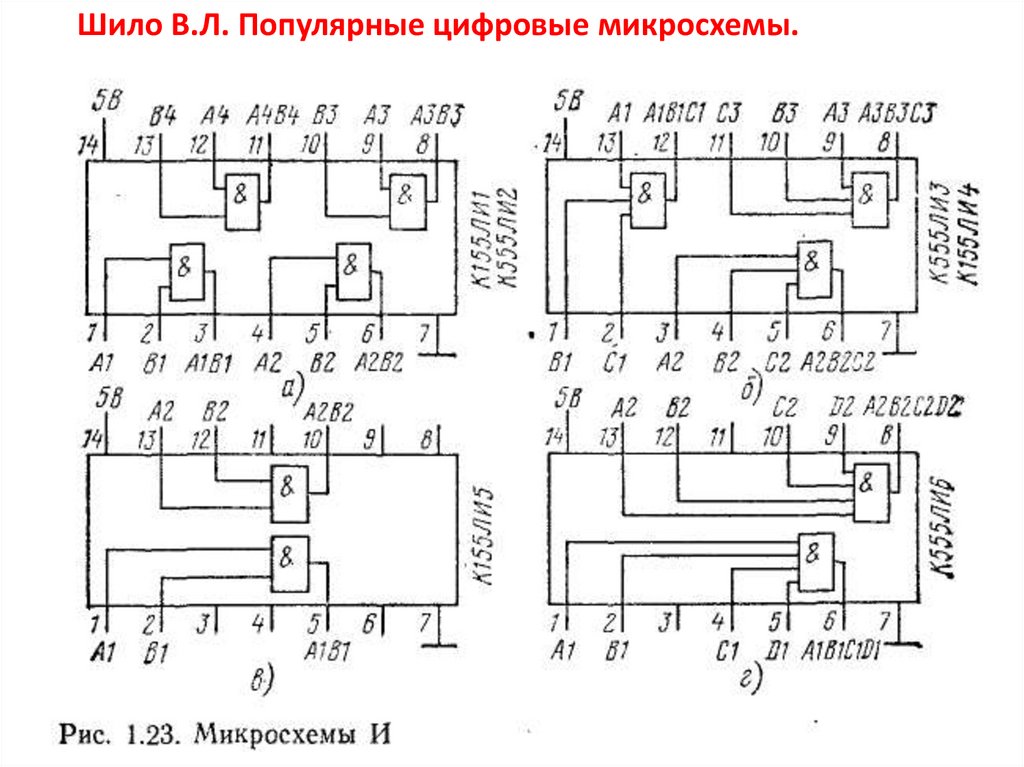

Шило В.Л. Популярные цифровые микросхемы.37.

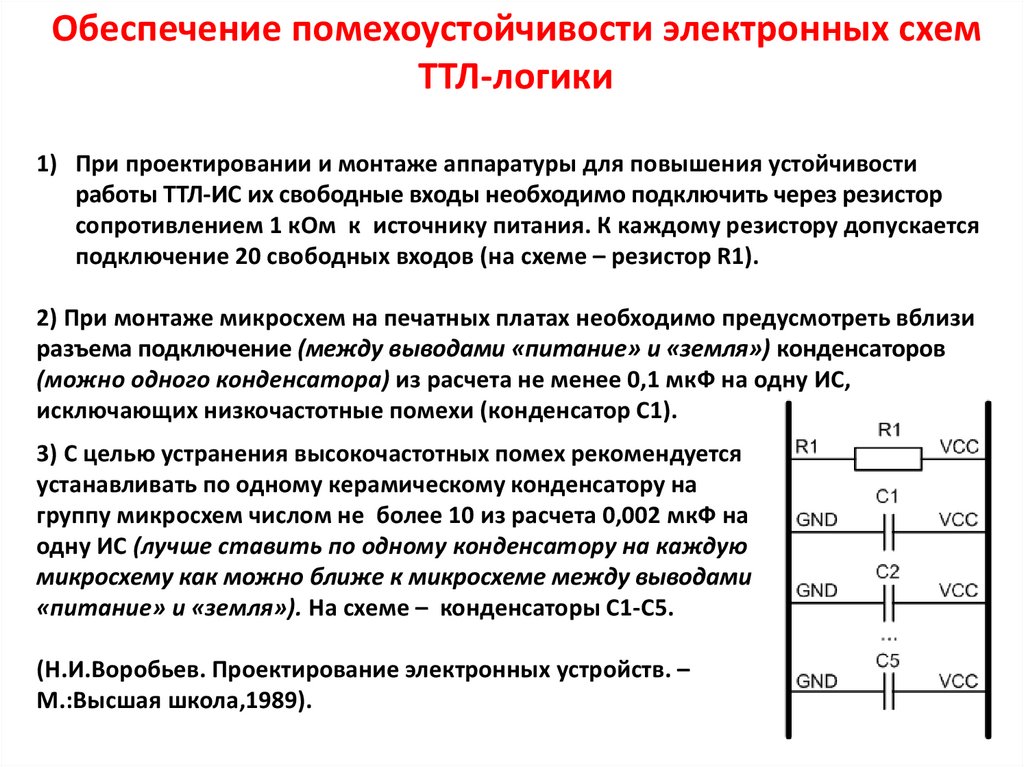

Обеспечение помехоустойчивости электронных схемТТЛ-логики

1) При проектировании и монтаже аппаратуры для повышения устойчивости

работы ТТЛ-ИС их свободные входы необходимо подключить через резистор

сопротивлением 1 кОм к источнику питания. К каждому резистору допускается

подключение 20 свободных входов (на схеме – резистор R1).

2) При монтаже микросхем на печатных платах необходимо предусмотреть вблизи

разъема подключение (между выводами «питание» и «земля») конденсаторов

(можно одного конденсатора) из расчета не менее 0,1 мкФ на одну ИС,

исключающих низкочастотные помехи (конденсатор C1).

3) С целью устранения высокочастотных помех рекомендуется

устанавливать по одному керамическому конденсатору на

группу микросхем числом не более 10 из расчета 0,002 мкФ на

одну ИС (лучше ставить по одному конденсатору на каждую

микросхему как можно ближе к микросхеме между выводами

«питание» и «земля»). На схеме – конденсаторы С1-С5.

(Н.И.Воробьев. Проектирование электронных устройств. –

М.:Высшая школа,1989).

38.

39.

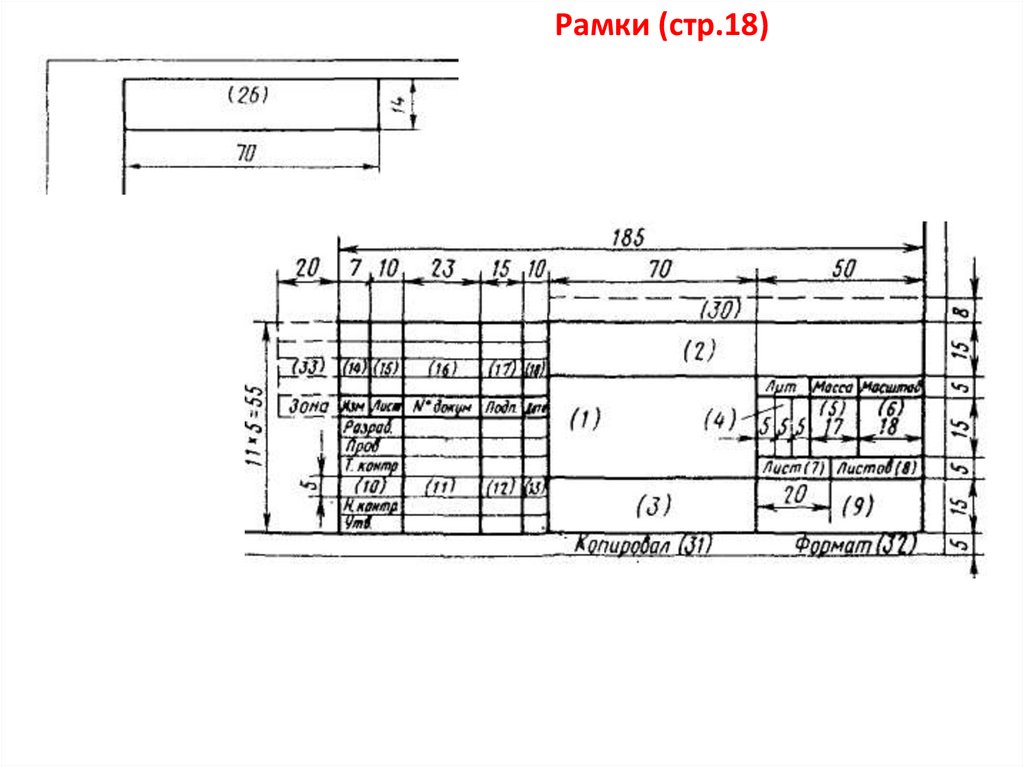

Рамки (стр.18)40.

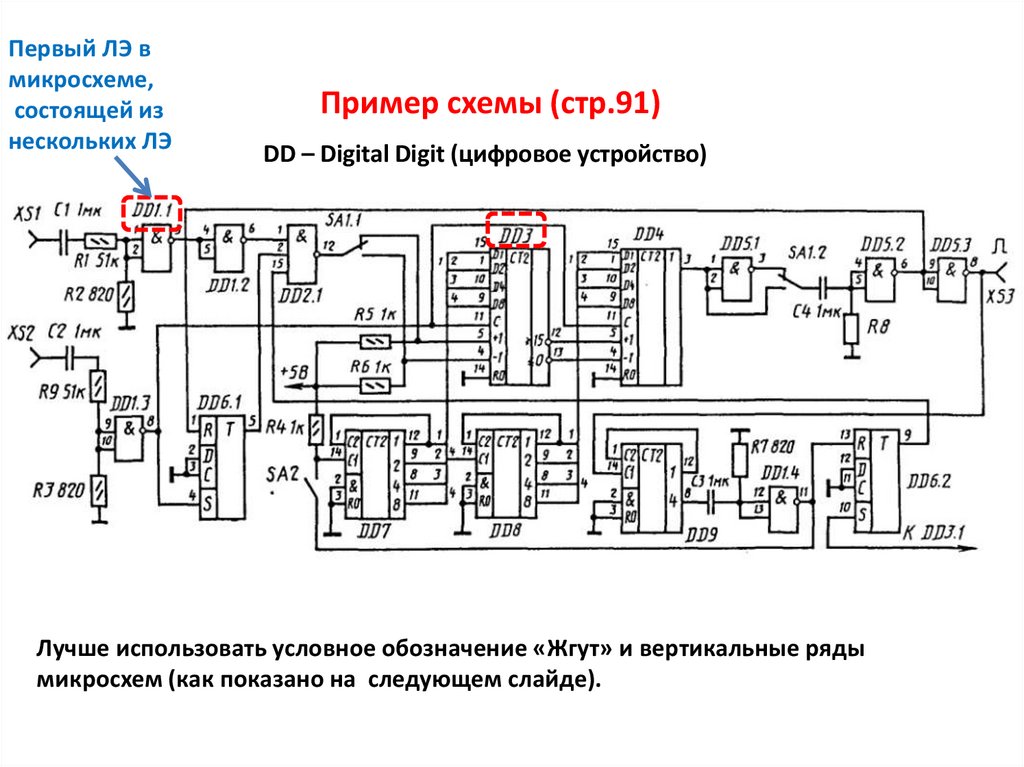

Первый ЛЭ вмикросхеме,

состоящей из

нескольких ЛЭ

Пример схемы (стр.91)

DD – Digital Digit (цифровое устройство)

Лучше использовать условное обозначение «Жгут» и вертикальные ряды

микросхем (как показано на следующем слайде).

41.

42.

На свободномместе чертежа

приводятся

перечень

элементов и

таблица

подключения

микросхем к

цепям VCC и

GND.

Х1

Х2

43.

6. Синтез УУ.6.1. Структурная схема УУ.

6.2. Адресация МК.

6.3. Кодирование МО.

6.4. МП функционирования ЦОУ.

6.5. Разработка принципиальной

схемы узла УУ.

7. Определение временных

характеристик.

МУ к КП – стр. 33-35.

Электроника

Электроника