Похожие презентации:

Синтез цифровых автоматов

1. Синтез цифровых автоматов

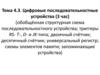

2. Кварцевый резонатор

3. Схема включения

4. На материнской плате

5. План лекции

Обобщенная структура цифровых устройствКлассификация управляющих автоматов

Управляющий автомат Мили.

Управляющий автомат Мура.

Микропрограммный автомат

6. Структура цифрового устройства

DI – входные данныеD0 – выходные данные

Х – сигналы условий (признаков)

Y – управляющие сигналы

C – команды

q - конец операции

Операционный автомат выполняет обработку цифровых данных

под управлением управляющего автомата.

7. Обобщенная микроархитектура процессора

Микроархитектура включает составные части процессора и способы их взаимосвязи8. Уровневая модель компьютера

9. Типы управляющих автоматов

Два типа управляющих автоматов:• Цифровой автомат с жёсткой (фиксированной) логикой

– автоматы Мили и Мура

• Микропрограммный автомат с хранимой в памяти

микропрограммой

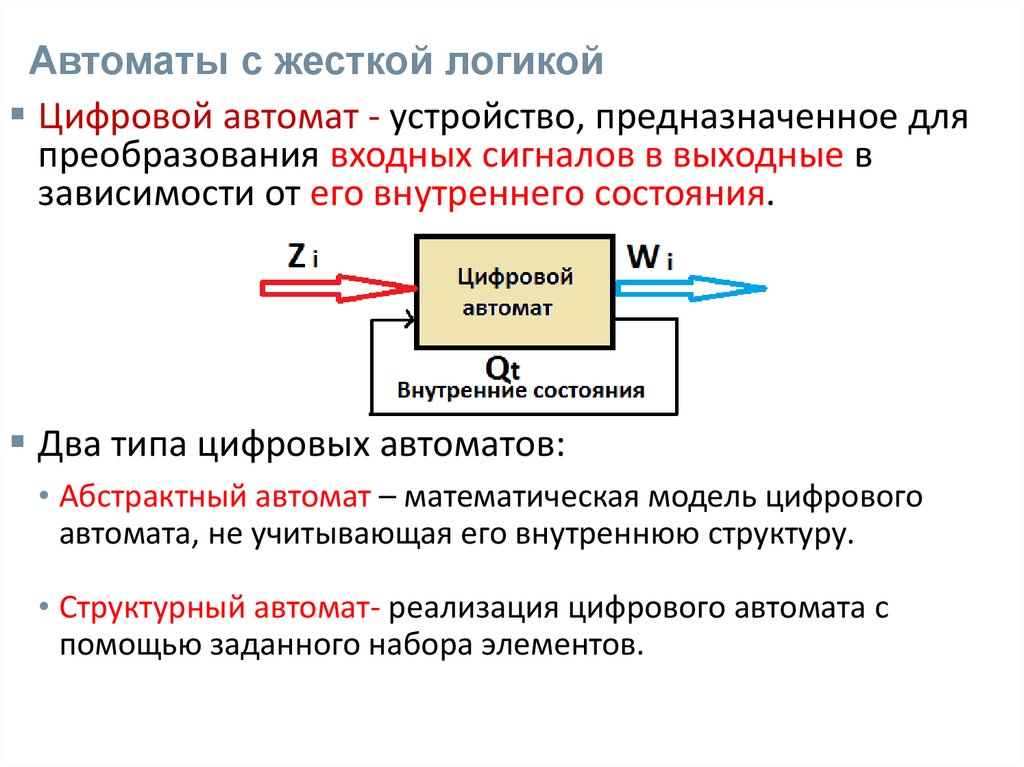

10. Автоматы с жесткой логикой

Цифровой автомат - устройство, предназначенное дляпреобразования входных сигналов в выходные в

зависимости от его внутреннего состояния.

Два типа цифровых автоматов:

• Абстрактный автомат – математическая модель цифрового

автомата, не учитывающая его внутреннюю структуру.

• Структурный автомат- реализация цифрового автомата с

помощью заданного набора элементов.

11. Абстрактный автомат

Абстрактный автомат –задается шестикомпонентнымвектором S=(Q,Z,W, , ,q0), где:

• Q={q1,…,qm} – множество внутренних состояний абстрактного

автомата,

• Z=[z1,…,zk} – множества входных слов

• W={w1,…,wl} – множества выходных слов

• – функция переходов,

• – функция выходов,

• q0 – начальное состояние автомата.

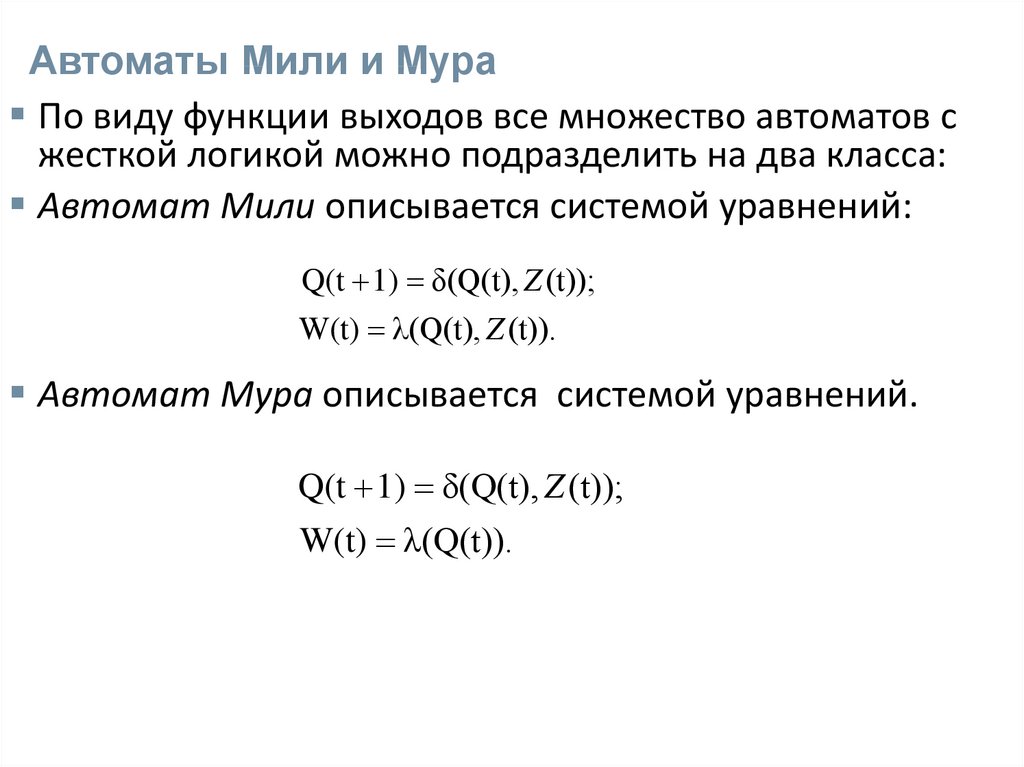

12. Автоматы Мили и Мура

По виду функции выходов все множество автоматов cжесткой логикой можно подразделить на два класса:

Автомат Мили описывается системой уравнений:

Q(t 1) δ(Q(t), Z (t));

W(t) λ(Q(t), Z (t)).

Автомат Мура описывается системой уравнений.

Q(t 1) δ(Q(t), Z (t));

W(t) λ(Q(t)).

13. Способы задания

С помощью таблиц переходов и выходовС помощью графа

Так как следующее состояние получается из текущего, то текущее состояние должно

хранится в памяти состояний.

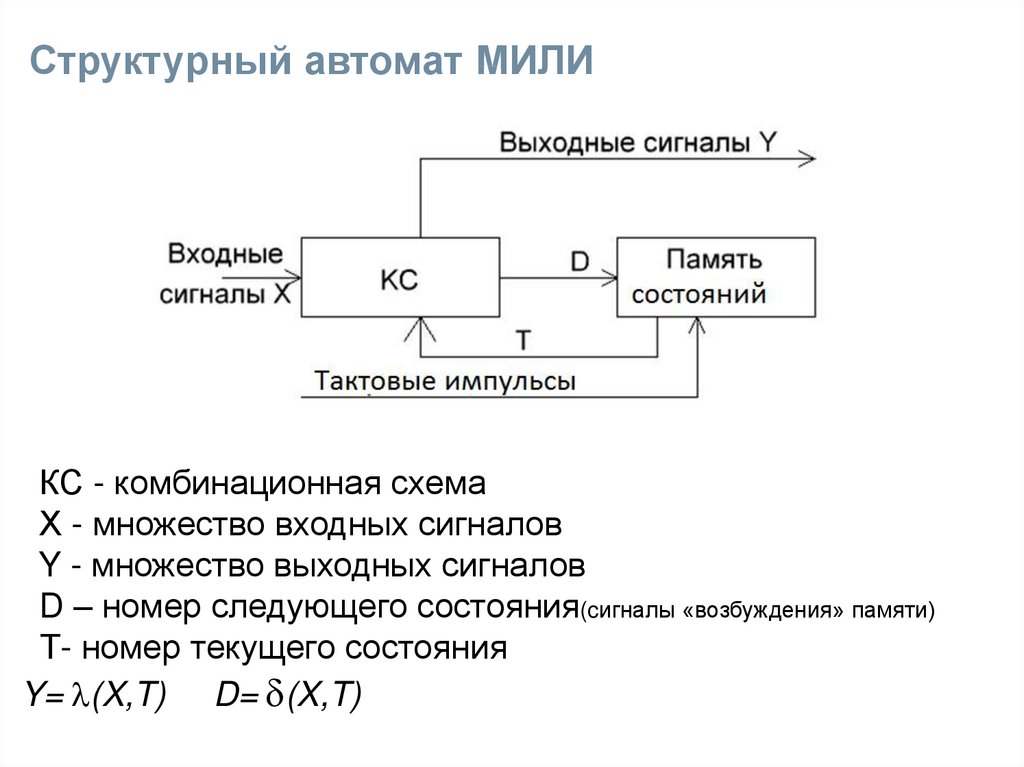

14. Структурный автомат МИЛИ

КС - комбинационная схемаХ - множество входных сигналов

Y - множество выходных сигналов

D – номер следующего состояния(cигналы «возбуждения» памяти)

Т- номер текущего состояния

Y= (X,T) D= (X,T)

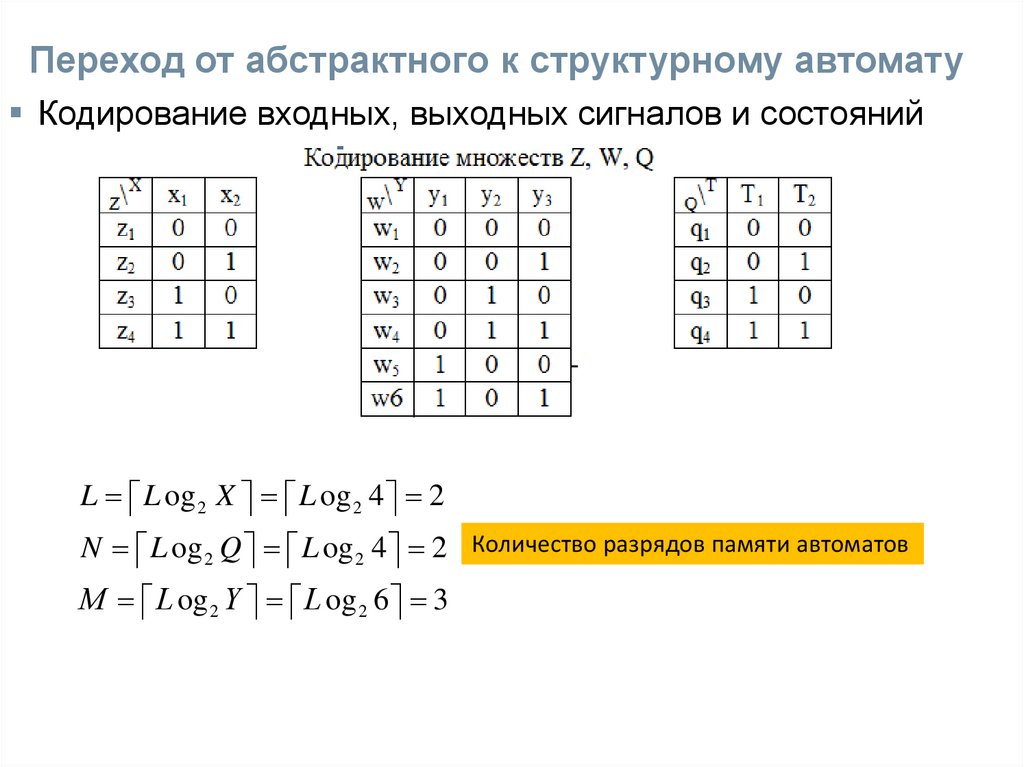

15. Переход от абстрактного к структурному автомату

Кодирование входных, выходных сигналов и состоянийL L og 2 X L og 2 4 2

N L og 2 Q L og 2 4 2 Количество разрядов памяти автоматов

М L og 2 Y L og 2 6 3

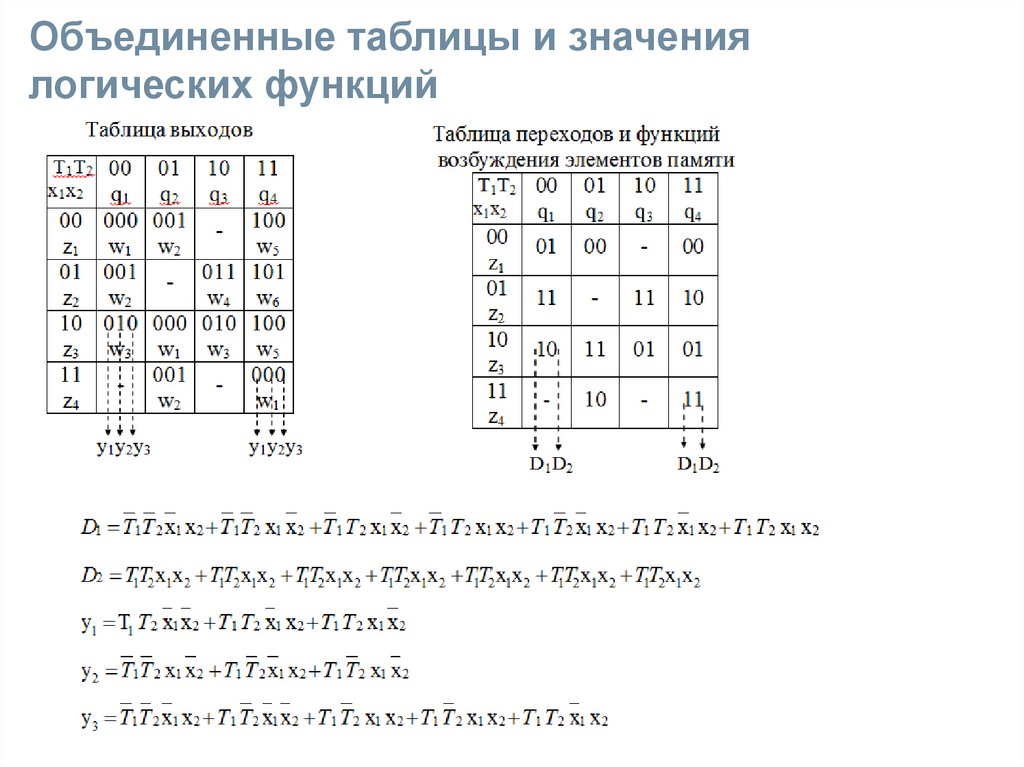

16. Объединенные таблицы и значения логических функций

17. Пример синтеза УА

Разработать устройство суммирования двух чисел .Одно из слагаемых может быть положительным или

отрицательным.

Используем дополнительный код

18. Используемые микросхемы

19. Схема операционной части

RG D1, RG D2 – регистры для хранения чиселX0,X1 – знак

Y0 – Y4 – Управляющие сигналы

20. Операционная часть

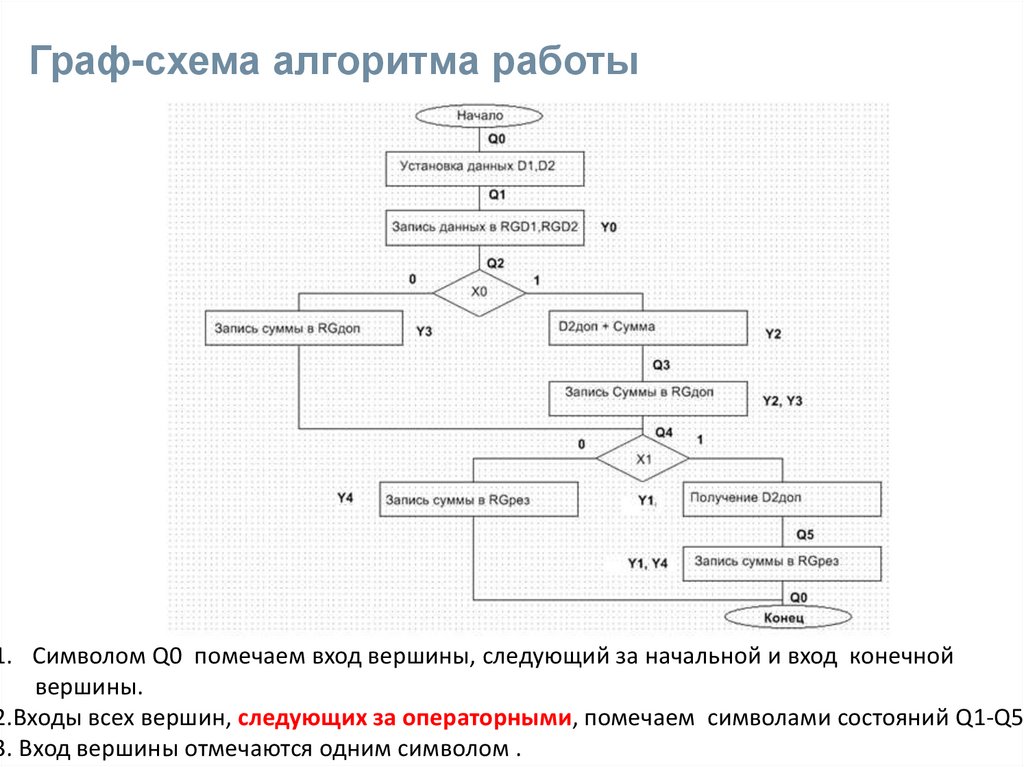

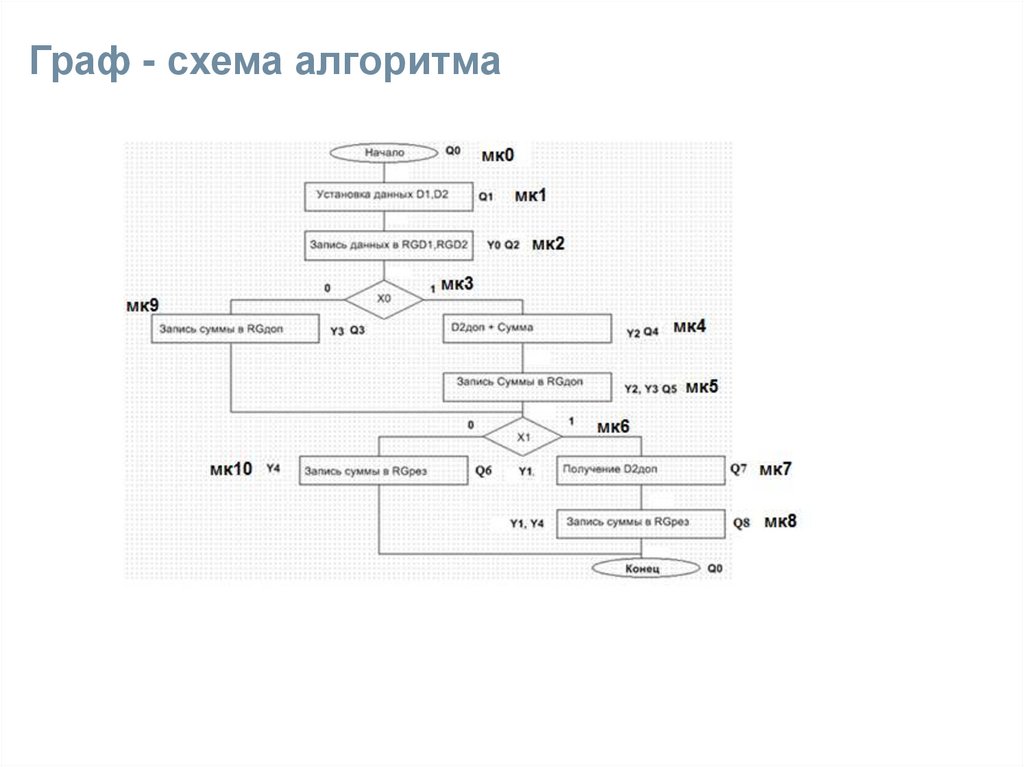

21. Граф-схема алгоритма работы

1. Символом Q0 помечаем вход вершины, следующий за начальной и вход конечнойвершины.

2.Входы всех вершин, следующих за операторными, помечаем символами состояний Q1-Q5.

3. Вход вершины отмечаются одним символом .

22. Кодирование состояний

Всего шесть состояний для их кодирования надо триэлемента памяти (триггера)

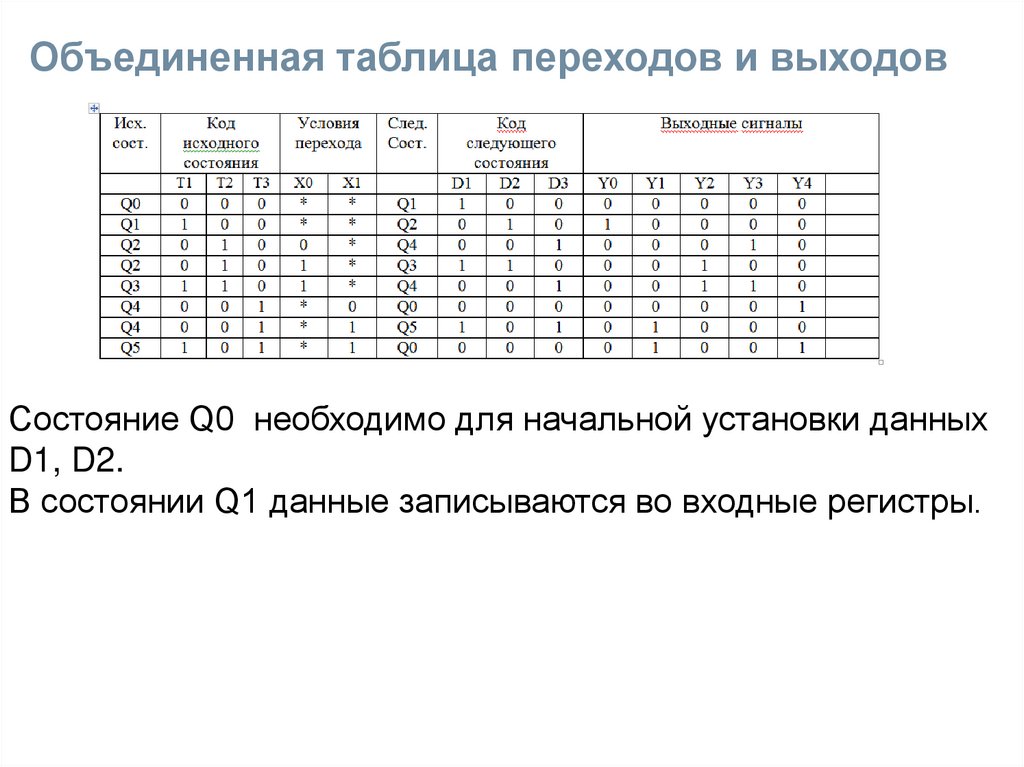

23. Объединенная таблица переходов и выходов

Состояние Q0 необходимо для начальной установки данныхD1, D2.

В состоянии Q1 данные записываются во входные регистры.

24. Логические выражения

25. Минимизация Y и D

26. Управляющая часть

27. Синтез автомата Мура

КС1 реализует функцию D=ƒ2(X,T), а КС2 - Y=ƒ1(T).Для каждой комбинационной схемы строится своя таблица

состояний.

У автомата Мура выход «развязан» от входа

28. Разметка ГСА для автомата Мура

1. Символом Q0 отмечается начальная и конечная вершина .2. Символами Q1-Q5 отмечаются все операторные вершины.

3. Каждая операторная вершина помечается одним символом.

29. Кодирование состояний и таблицы выходов для КС2

Всего 9 состояний – надо 4 триггера30. Кодирование состояний и таблица переходов для КС1

31. Запись СДНФ и минимизация выражений

По таблицам записываем СДНФ – для Y0-Y4 и D1-D4Например:

Минимизируем и разрабатываем схему

32. Недостатки УА на основе жесткой логики

1. При необходимости внесения любых, даженебольших изменений алгоритма работы схему

автомата надо полностью пересинтезировать.

2. При большом числе входных и выходных сигналов

схема автомата сильно разрастается, а синтез сильно

усложняется.

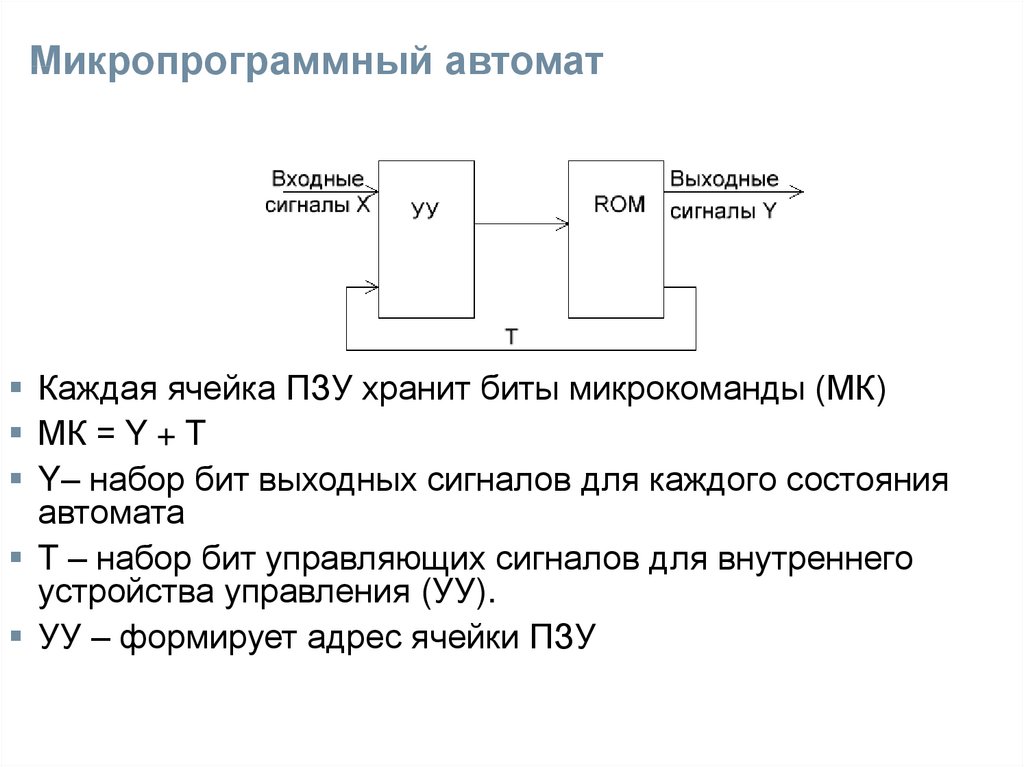

33. Микропрограммный автомат

Каждая ячейка ПЗУ хранит биты микрокоманды (МК)МК = Y + T

Y– набор бит выходных сигналов для каждого состояния

автомата

T – набор бит управляющих сигналов для внутреннего

устройства управления (УУ).

УУ – формирует адрес ячейки ПЗУ

34. Структура микропрограммного автомата

Счётчик-РАМК(регистр адреса микрокоманды) при V=0 выполняет загрузку адресакоманды со входов D, при V=1 выполняется счёт по тактовым импульсам на входе +1.

РМК-регистр микрокоманды, временно хранит микрокоманду

Бит V определяет тип микрокоманды

V=1 – ОМК – операционная микрокоманда, содержащая сигналы Y.

V=0 – УМК – управляющая микрокоманда (команда перехода)

Поле A – адрес перехода, подаётся на входы предзагрузки счётчика и в зависимости от

значения анализируемой переменной Xi на входе V может записывать в счетчик адрес

следующего перехода

Поле Nx – Закодированный номер проверяемой входной переменной. Это значение

подается на адресные входы мультиплексора и разрешает прохождение на его выход

значения соответствующей переменной Xi.

Безусловный переход реализуется путем фиксирования лог. 0 на одном из входов MS.

35. Граф - схема алгоритма

36. Кодировка входных сигналов автомата x0, x1

37. Таблица переходов

Микропрограмма занимает 14 ячеек памяти. Разрядностьвыходных данных ПЗУ определяется:

V+Nx+A+Y=1+2+4+5=12.

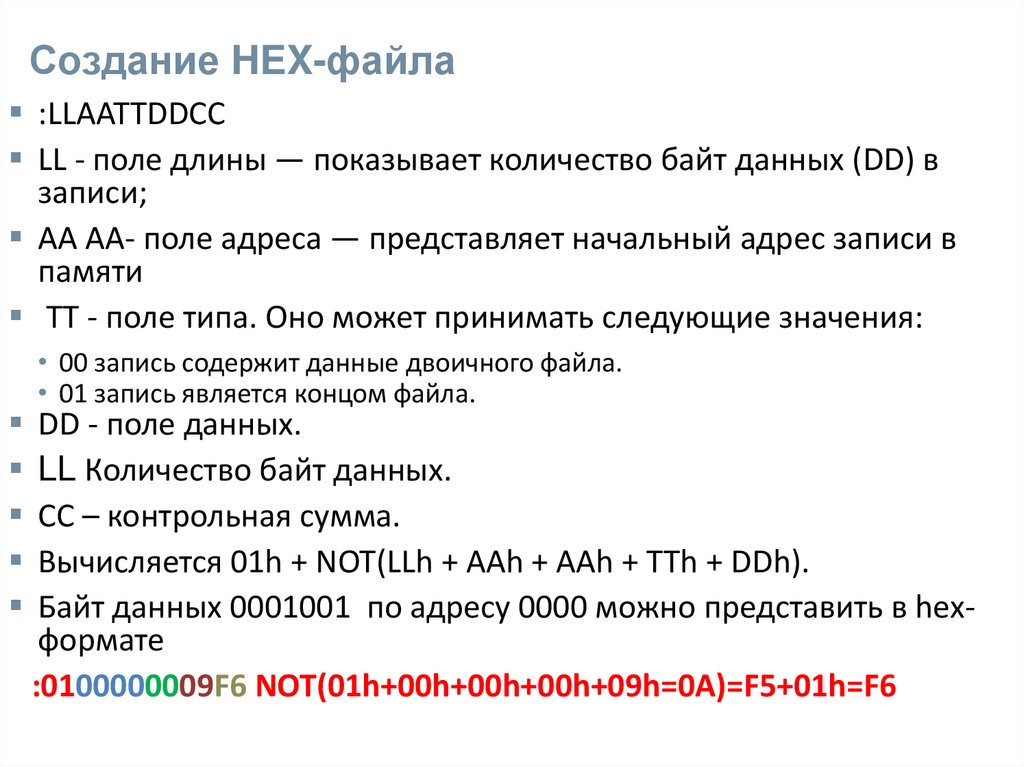

38. Создание HEX-файла

:LLAATTDDCCLL - поле длины — показывает количество байт данных (DD) в

записи;

AA AA- поле адреса — представляет начальный адрес записи в

памяти

TT - поле типа. Оно может принимать следующие значения:

• 00 запись содержит данные двоичного файла.

• 01 запись является концом файла.

DD - поле данных.

LL Количество байт данных.

CC – контрольная сумма.

Вычисляется 01h + NOT(LLh + AAh + AAh + TTh + DDh).

Байт данных 0001001 по адресу 0000 можно представить в hexформате

:0100000009F6 NOT(01h+00h+00h+00h+09h=0A)=F5+01h=F6

Электроника

Электроника