Похожие презентации:

Организация ЭВМ

1. Организация ЭВМ

1. Общая характеристика и классификациявычислительных машин и систем

1

2. Организация ЭВМ

1.1 Аппаратные и программные средствареализации алгоритмов

2

3. Организация ЭВМ

Вычислительная машина (ВМ) - это искусственнаяинженерная система для автоматической обработки

информации по заданному алгоритму.

3

4. Организация ЭВМ

Средства реализации алгоритмоваппаратные (АС)

программные (ПС)

реализуют какие-либо

действия алгоритма

одномоментно, без

возможности

дробления со стороны

программиста

совокупности инструкций

по реализации

вычислительного процесса

с помощью аппаратных

средств в соответствии с

алгоритмом

(сумматоры, умножители,

устройства ЦОС и т.д.)

сводятся к последовательности

машинных команд, выполняемых на АС

ВМ

4

5. Организация ЭВМ

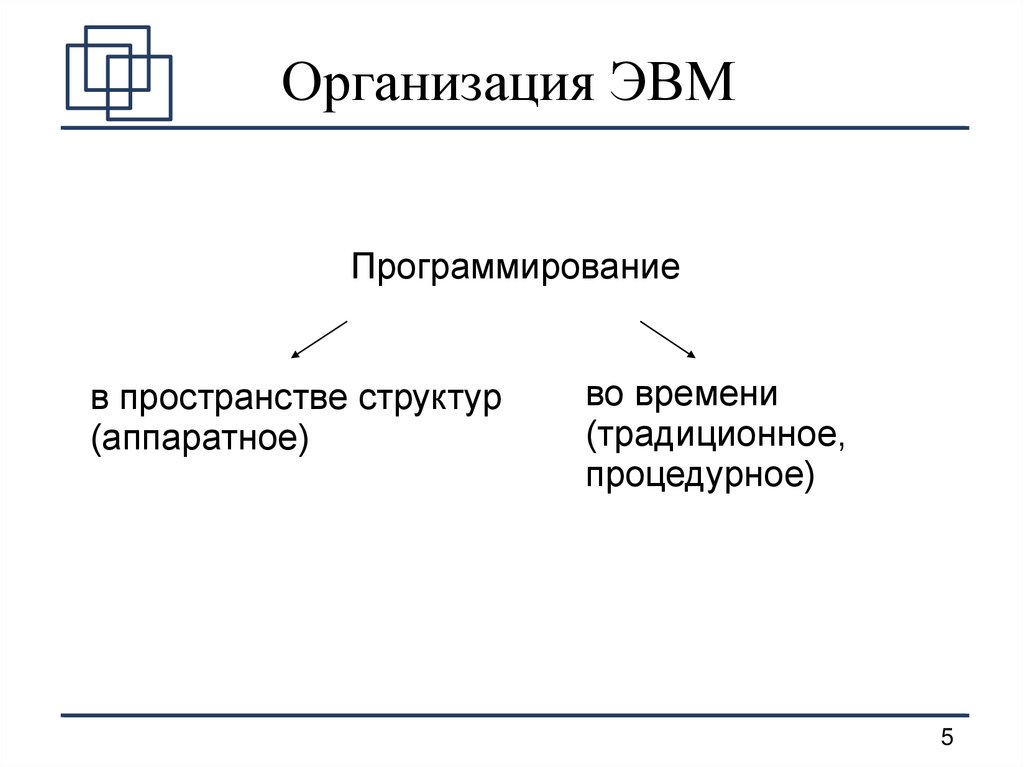

Программированиев пространстве структур

(аппаратное)

во времени

(традиционное,

процедурное)

5

6. Организация ЭВМ

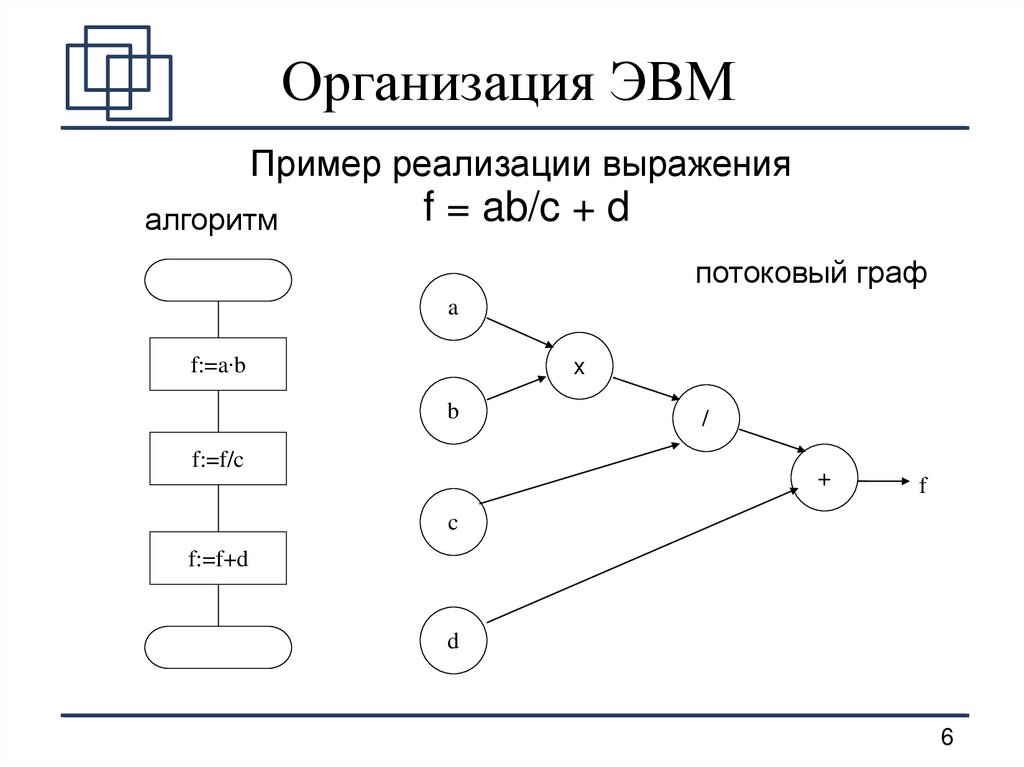

Пример реализации выраженияалгоритм

f = ab/c + d

потоковый граф

a

f:=a∙b

x

b

f:=f/c

/

+

f

c

f:=f+d

d

6

7. Организация ЭВМ

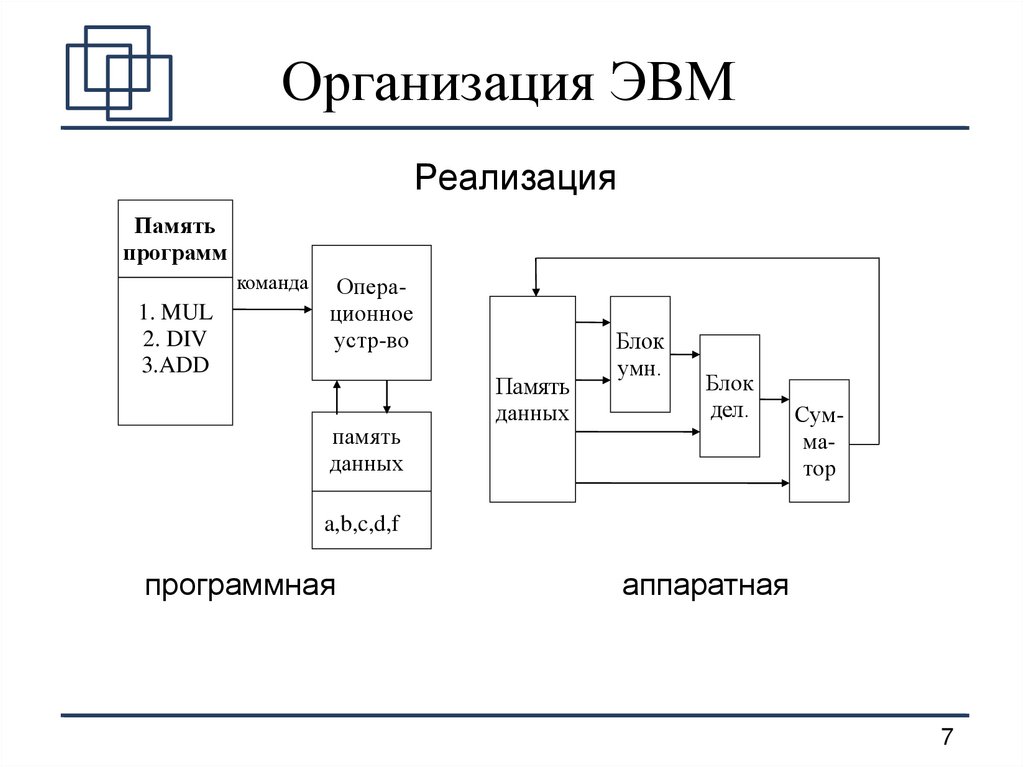

РеализацияПамять

программ

команда

1. MUL

2. DIV

3.ADD

Операционное

устр-во

память

данных

Память

данных

Блок

умн.

Блок

дел.

Сумматор

a,b,c,d,f

программная

аппаратная

7

8. Организация ЭВМ

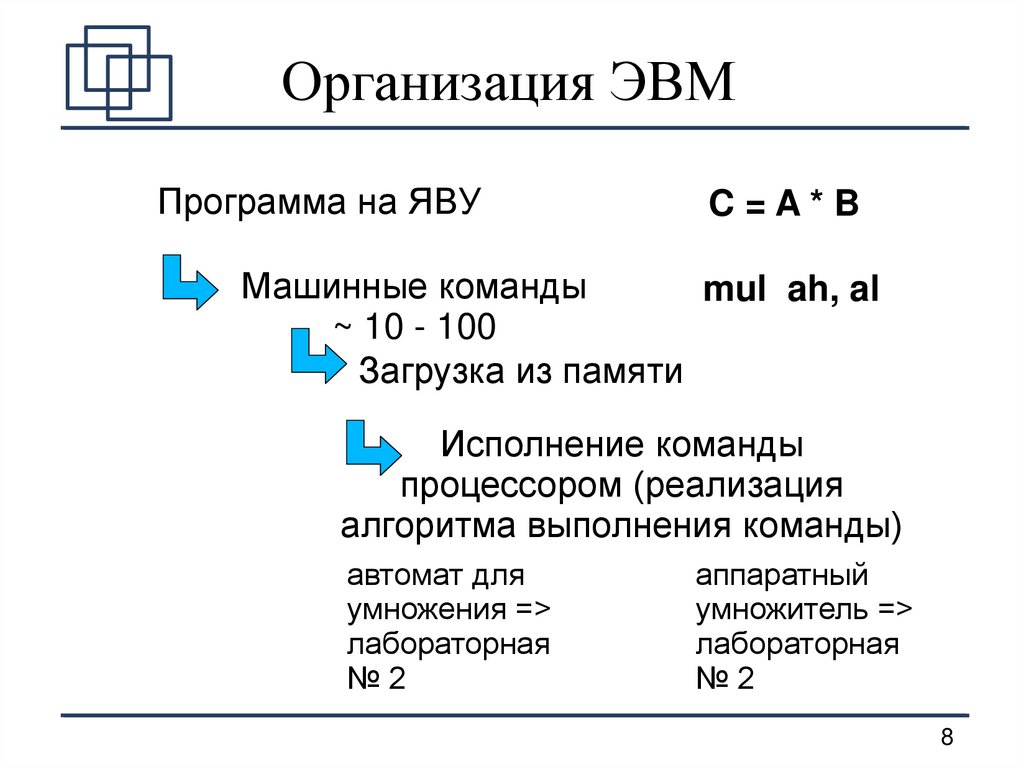

Программа на ЯВУC=A*B

Машинные команды

mul ah, al

~ 10 - 100

Загрузка из памяти

Исполнение команды

процессором (реализация

алгоритма выполнения команды)

автомат для

умножения =>

лабораторная

№2

аппаратный

умножитель =>

лабораторная

№2

8

9. Организация ЭВМ

1.2 Краткие сведения из цифровойсхемотехники

9

10. Организация ЭВМ

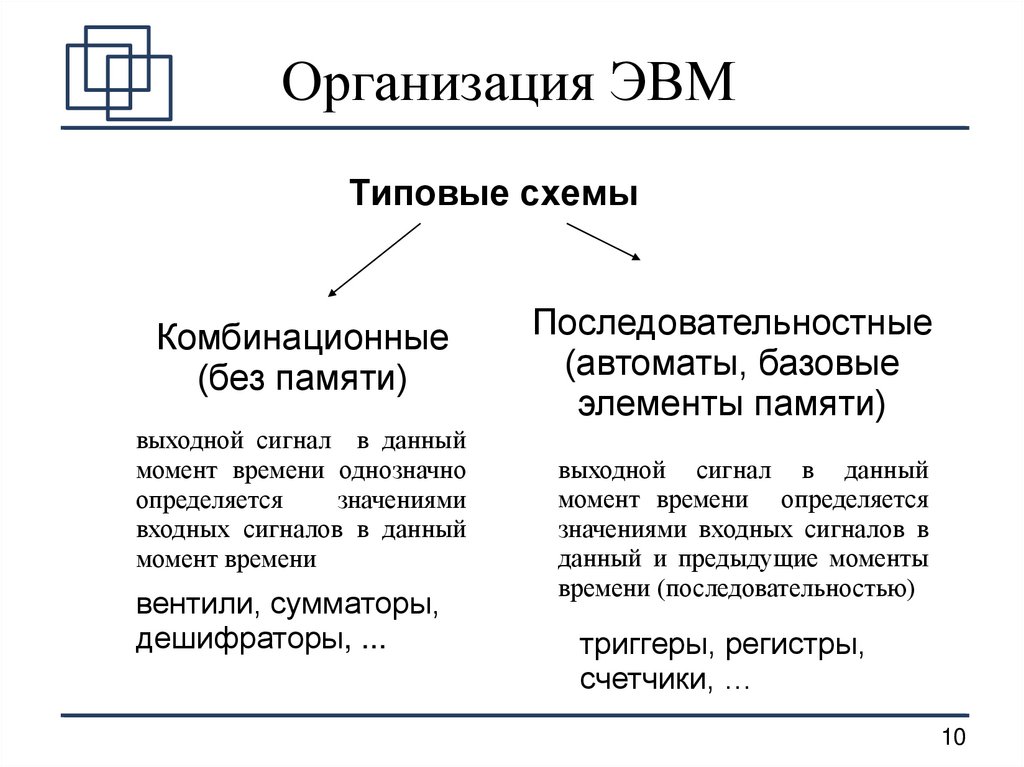

Типовые схемыКомбинационные

(без памяти)

выходной сигнал в данный

момент времени однозначно

определяется

значениями

входных сигналов в данный

момент времени

вентили, сумматоры,

дешифраторы, ...

Последовательностные

(автоматы, базовые

элементы памяти)

выходной сигнал в данный

момент времени определяется

значениями входных сигналов в

данный и предыдущие моменты

времени (последовательностью)

триггеры, регистры,

счетчики, …

10

11. Организация ЭВМ

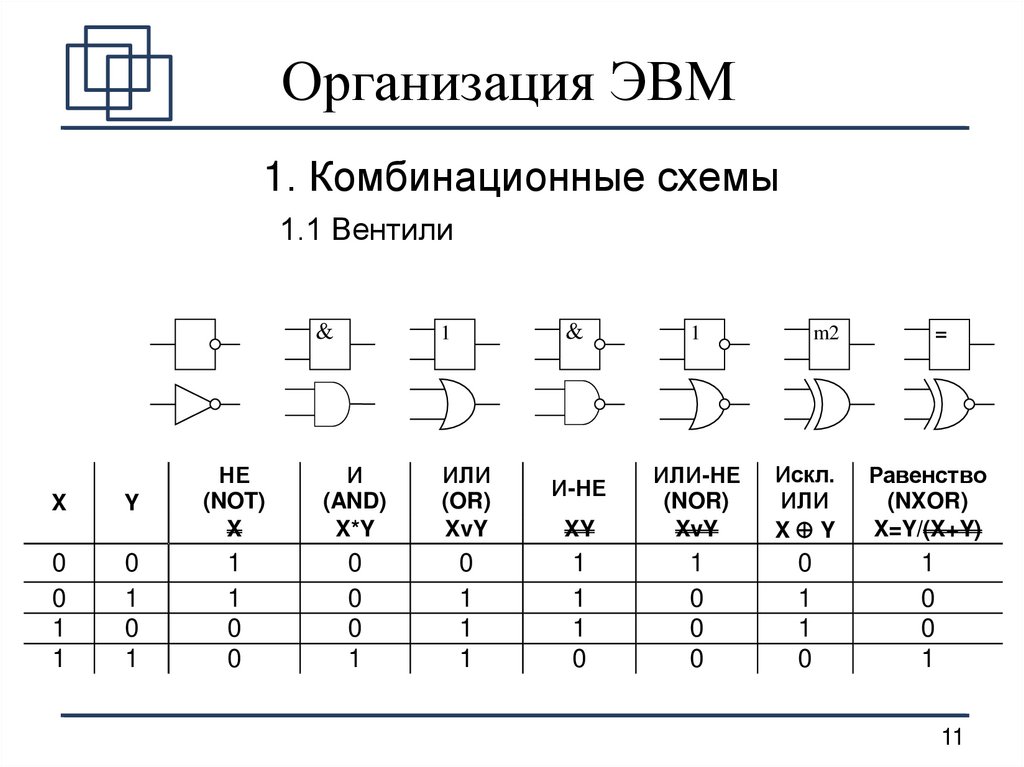

1. Комбинационные схемы1.1 Вентили

X

0

0

1

1

Y

0

1

0

1

&

1

&

НЕ

(NOT)

X

И

(AND)

X*Y

ИЛИ

(OR)

XvY

1

1

0

0

0

0

0

1

0

1

1

1

1

m2

=

XY

ИЛИ-НЕ

(NOR)

XvY

Искл.

ИЛИ

(XOR)

X Y

Равенство

(NXOR)

X=Y/(X+Y)

1

1

1

0

1

0

0

0

0

1

1

0

1

0

0

1

И-НЕ

11

12. Организация ЭВМ

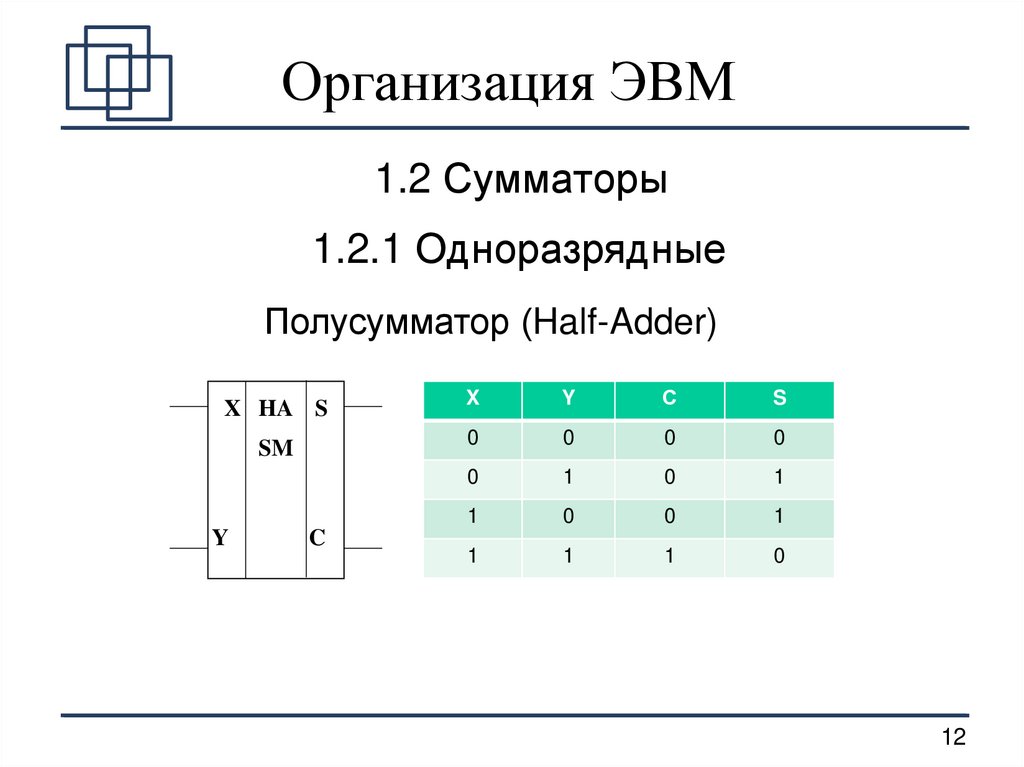

1.2 Сумматоры1.2.1 Одноразрядные

Полусумматор (Half-Adder)

X HA S

SM

Y

C

X

Y

С

S

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

НYM C

12

13. Организация ЭВМ

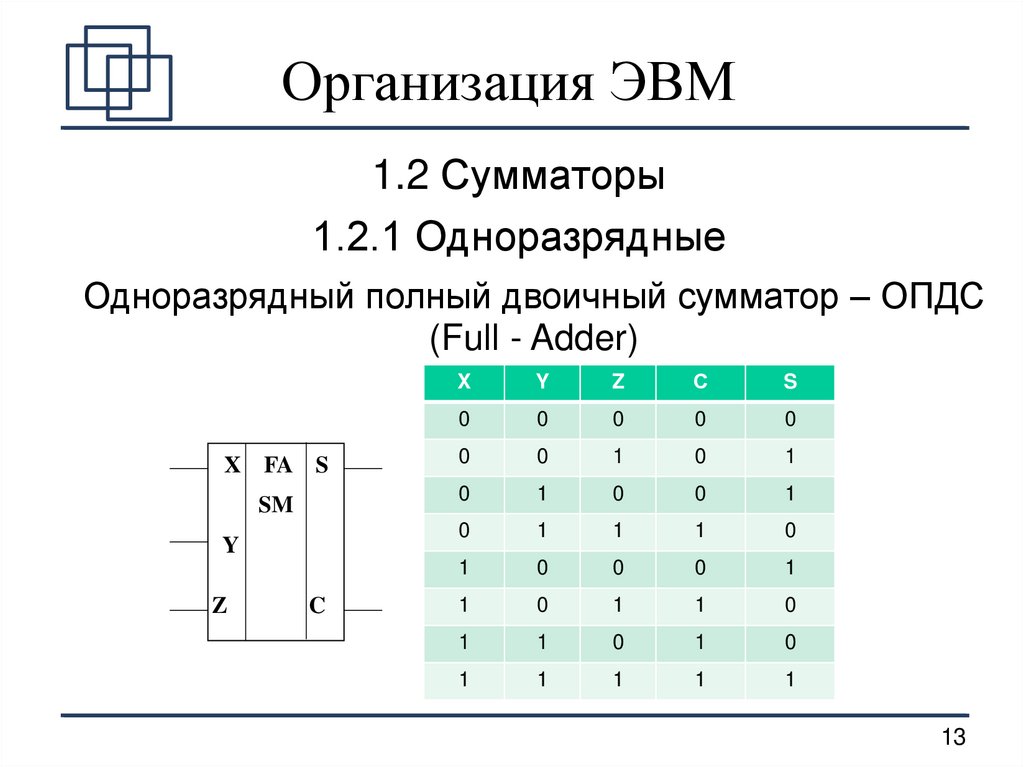

1.2 Сумматоры1.2.1 Одноразрядные

Одноразрядный полный двоичный сумматор – ОПДС

(Full - Adder)

X

FA S

SM

Y

Z

НYM C

C

X

Y

Z

С

S

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

13

14. Организация ЭВМ

1.2 Сумматоры1.2.2 Параллельные

Параллельный сумматор

n

X SM

S

n

Xo

n

Пример : параллельный

сумматор с

последовательным переносом

X

FA S

So

X1

X

FA S

S1

Y

Yo

Ci

НYM C

Co

Ci

Y1

Y

Y

Ci

НYM C

Co

Ci

Co

НYM C

14

15. Организация ЭВМ

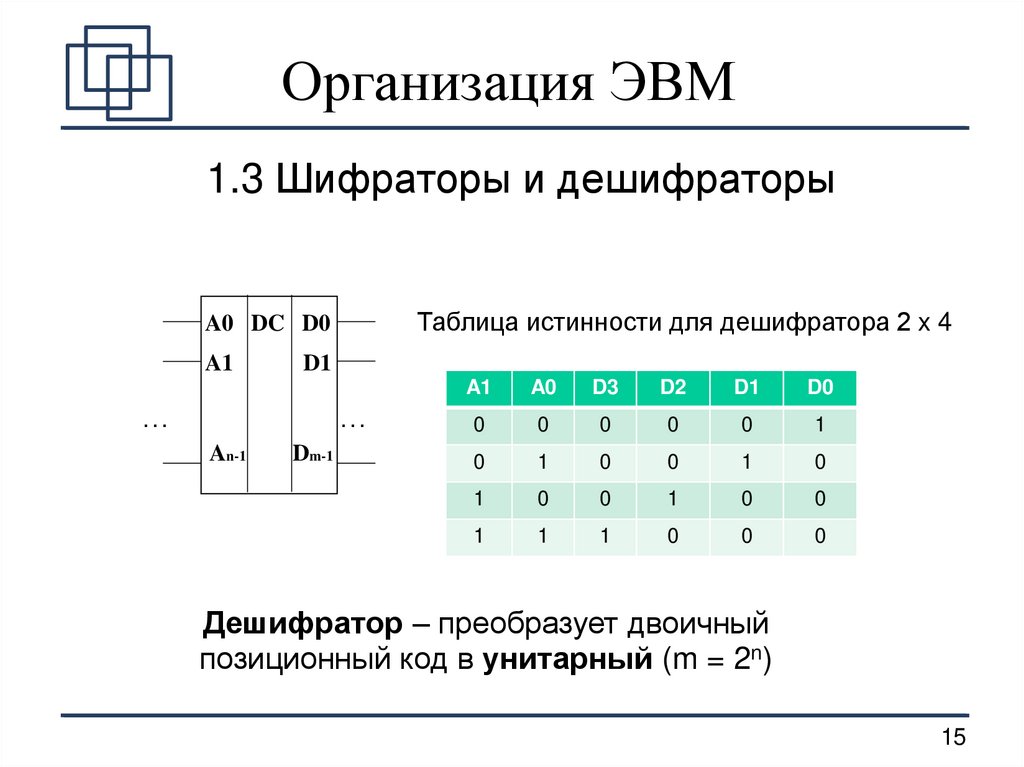

1.3 Шифраторы и дешифраторыТаблица истинности для дешифратора 2 x 4

A0 DC D0

A1

D1

…

…

An-1

НYM C

Dm-1

A1

A0

D3

D2

D1

D0

0

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

0

Дешифратор – преобразует двоичный

позиционный код в унитарный (m = 2n)

15

16. Организация ЭВМ

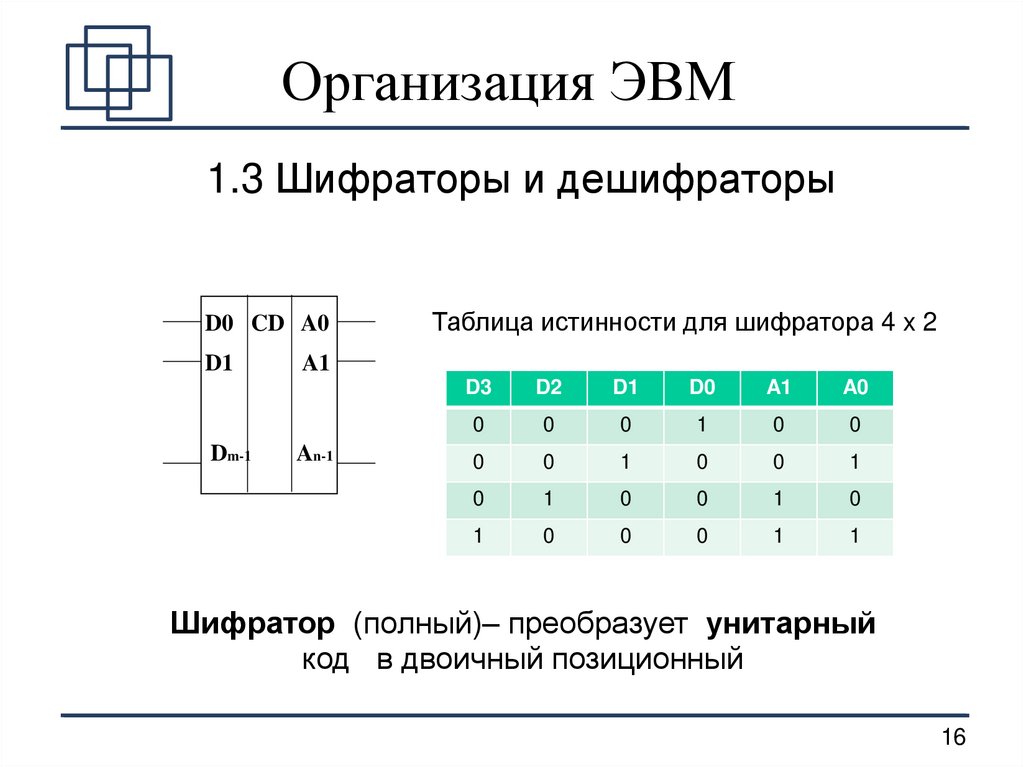

1.3 Шифраторы и дешифраторыD0 CD A0

D1

Dm-1

НYM C

Таблица истинности для шифратора 4 x 2

A1

An-1

D3

D2

D1

D0

A1

A0

0

0

0

1

0

0

0

0

1

0

0

1

0

1

0

0

1

0

1

0

0

0

1

1

Шифратор (полный)– преобразует унитарный

код в двоичный позиционный

16

17. Организация ЭВМ

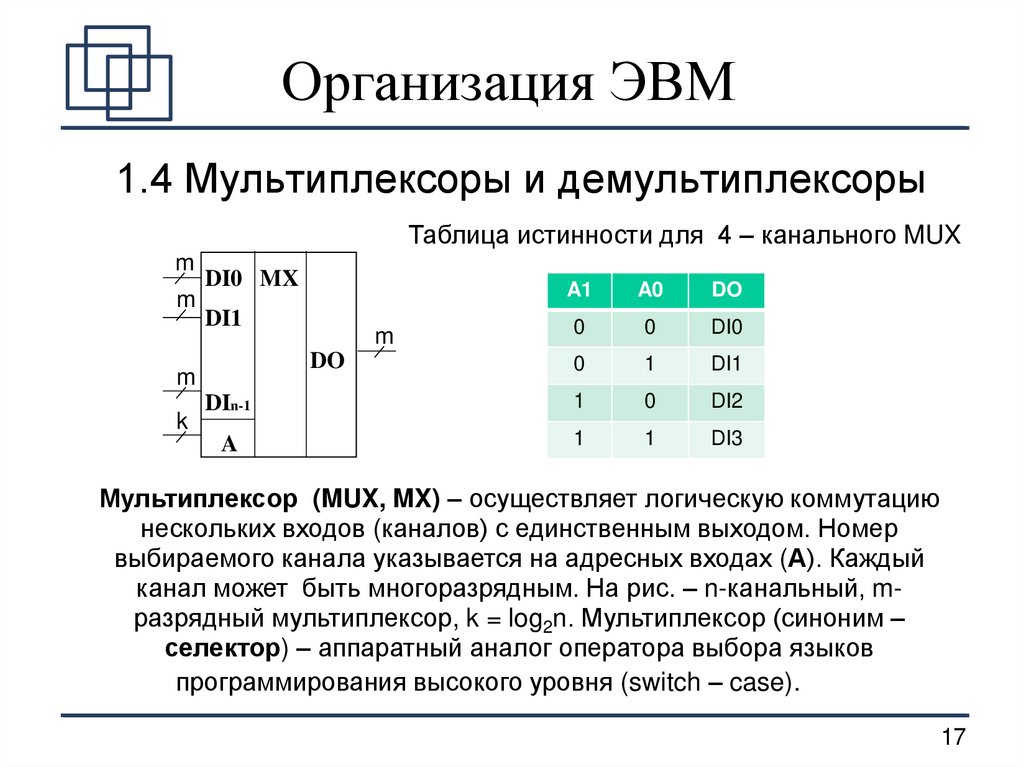

1.4 Мультиплексоры и демультиплексорыТаблица истинности для 4 – канального MUX

m

m

DI0 MX

A1

A0

DO

0

0

DI0

0

1

DI1

DIn-1

1

0

DI2

A

НYM C

1

1

DI3

DI1

DO

m

k

m

Мультиплексор (MUX, MX) – осуществляет логическую коммутацию

нескольких входов (каналов) с единственным выходом. Номер

выбираемого канала указывается на адресных входах (А). Каждый

канал может быть многоразрядным. На рис. – n-канальный, mразрядный мультиплексор, k = log2n. Мультиплексор (синоним –

селектор) – аппаратный аналог оператора выбора языков

программирования высокого уровня (switch – case).

17

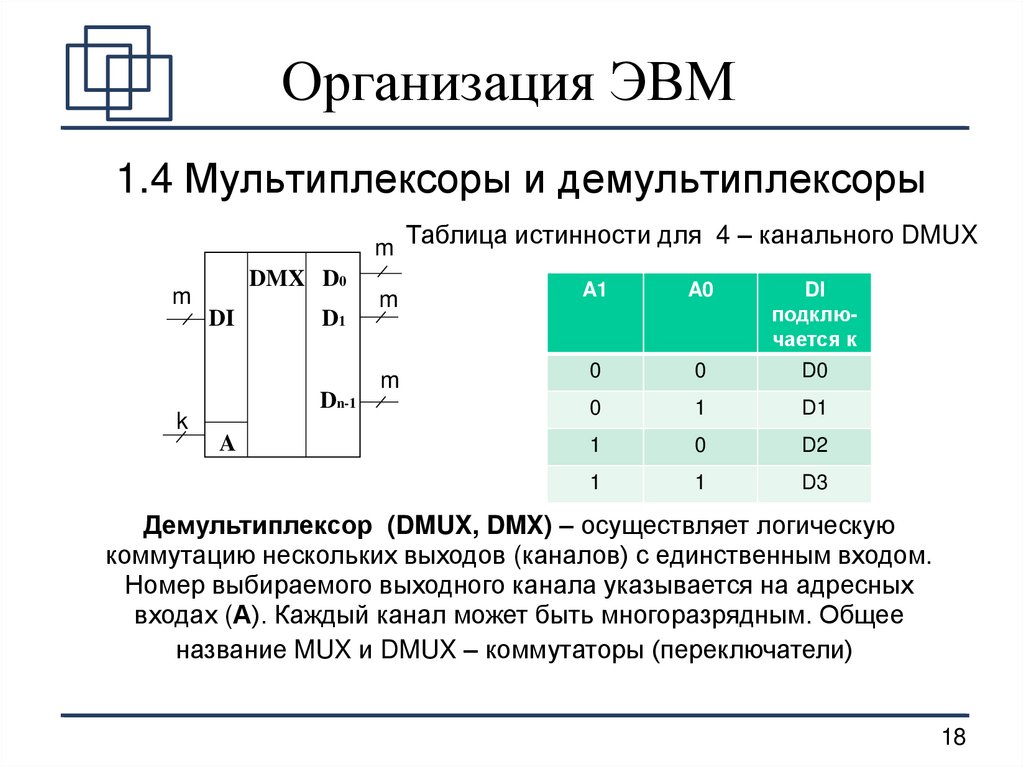

18. Организация ЭВМ

1.4 Мультиплексоры и демультиплексорыm

DMX D0

m

DI

D1

Dn-1

k

A

Таблица истинности для 4 – канального DMUX

m

A1

A0

DI

подключается к

m

0

0

D0

0

1

D1

1

0

D2

1

1

D3

НYM C

Демультиплексор (DMUX, DMX) – осуществляет логическую

коммутацию нескольких выходов (каналов) с единственным входом.

Номер выбираемого выходного канала указывается на адресных

входах (А). Каждый канал может быть многоразрядным. Общее

название MUX и DMUX – коммутаторы (переключатели)

18

19. Организация ЭВМ

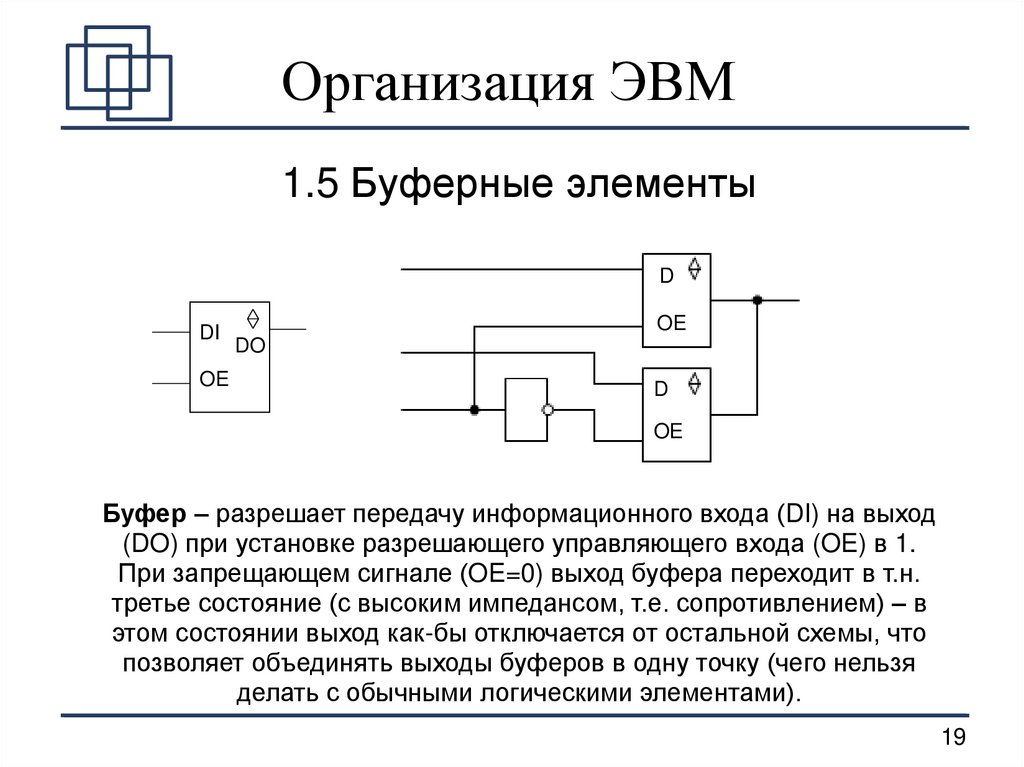

1.5 Буферные элементыD

DI

OE

OE

DO

D

OE

Буфер – разрешает передачу информационного входа (DI) на выход

(DO) при установке разрешающего управляющего входа (OE) в 1.

При запрещающем сигнале (OE=0) выход буфера переходит в т.н.

третье состояние (с высоким импедансом, т.е. сопротивлением) – в

этом состоянии выход как-бы отключается от остальной схемы, что

позволяет объединять выходы буферов в одну точку (чего нельзя

делать с обычными логическими элементами).

19

20. Организация ЭВМ

2 Схемы памяти2.1 Триггеры (flip-flop)

Триггер – полупроводниковая ячейка памяти емкостью в

один бит (имеет два состояния). Строится на базе

нескольких логических элементов (минимум – двух) с

цепями обратной связи.

20

21. Организация ЭВМ

2.1 Триггеры (flip-flop)Классификация триггеров :

1) По управляющим входам (по типу):

RS – триггеры; JK – триггеры;

D – триггеры; T – триггеры и др.

2) По способу управления:

Асинхронные

Синхронные

Со статическим

управлением

С динамическим

управлением

21

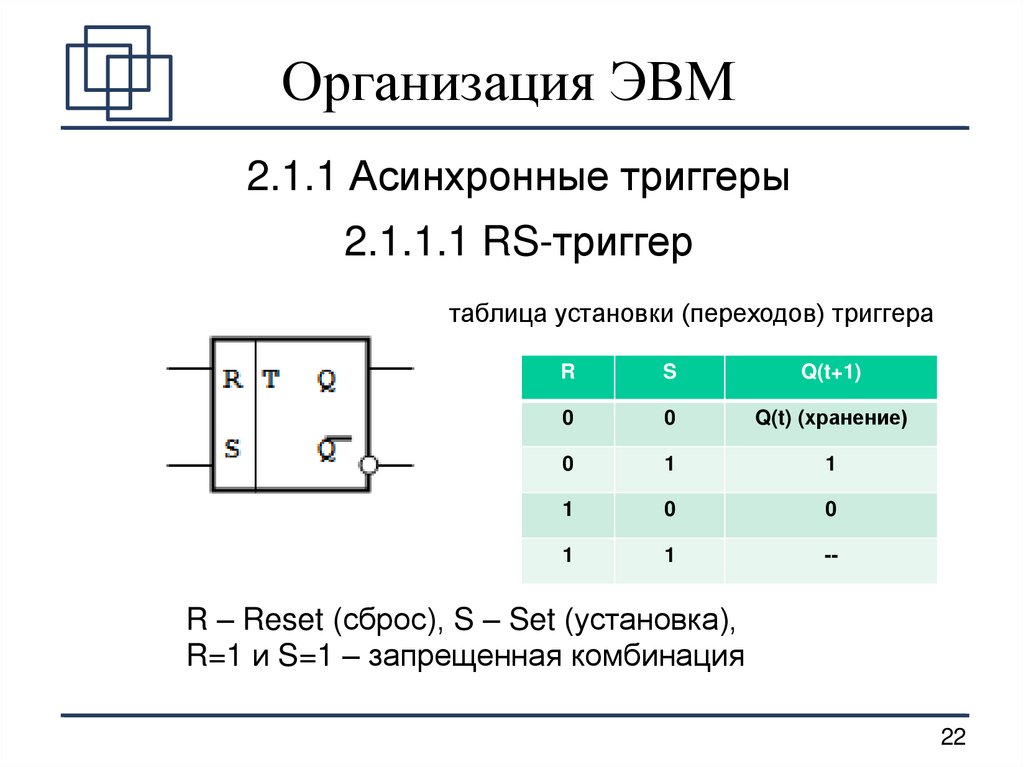

22. Организация ЭВМ

2.1.1 Асинхронные триггеры2.1.1.1 RS-триггер

таблица установки (переходов) триггера

R

S

Q(t+1)

0

0

Q(t) (хранение)

0

1

1

1

0

0

1

1

--

R – Reset (сброс), S – Set (установка),

R=1 и S=1 – запрещенная комбинация

22

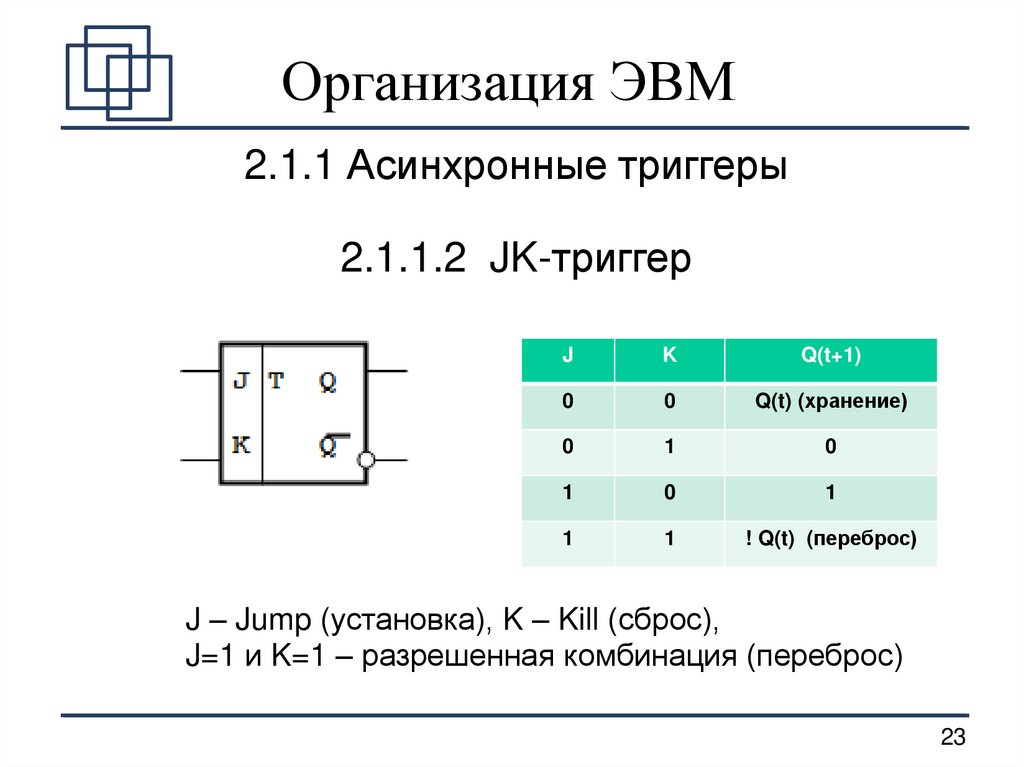

23. Организация ЭВМ

2.1.1 Асинхронные триггеры2.1.1.2 JK-триггер

J

K

Q(t+1)

0

0

Q(t) (хранение)

0

1

0

1

0

1

1

1

! Q(t) (переброс)

J – Jump (установка), K – Kill (сброс),

J=1 и K=1 – разрешенная комбинация (переброс)

23

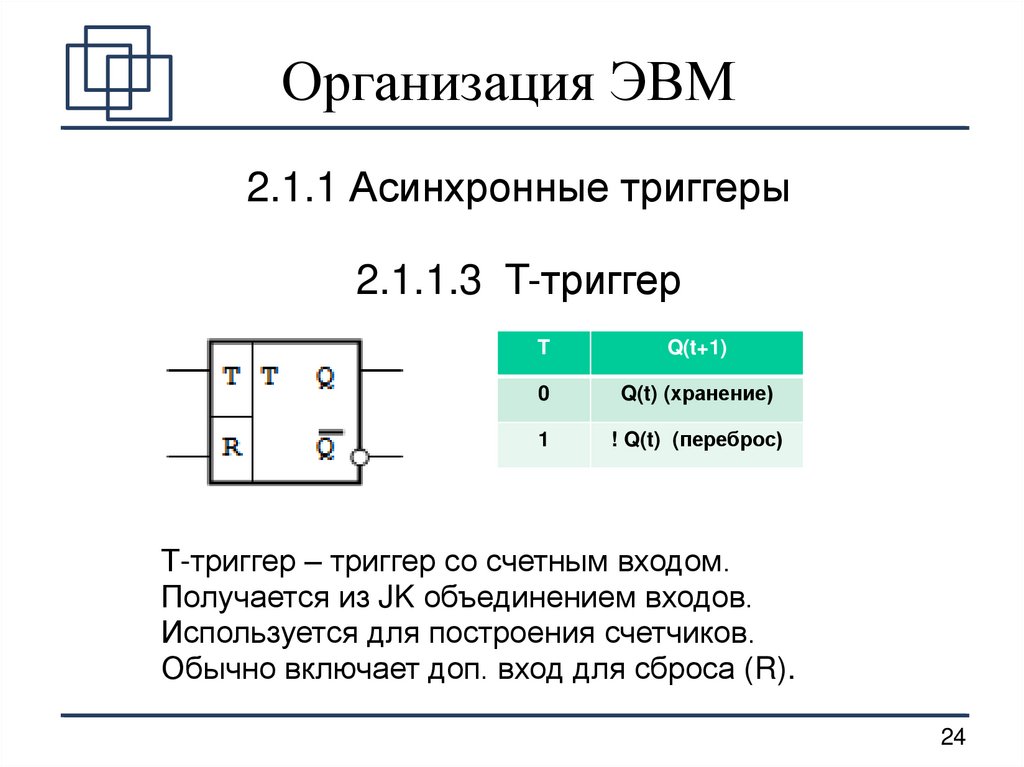

24. Организация ЭВМ

2.1.1 Асинхронные триггеры2.1.1.3 T-триггер

T

Q(t+1)

0

Q(t) (хранение)

1

! Q(t) (переброс)

Т-триггер – триггер со счетным входом.

Получается из JK объединением входов.

Используется для построения счетчиков.

Обычно включает доп. вход для сброса (R).

24

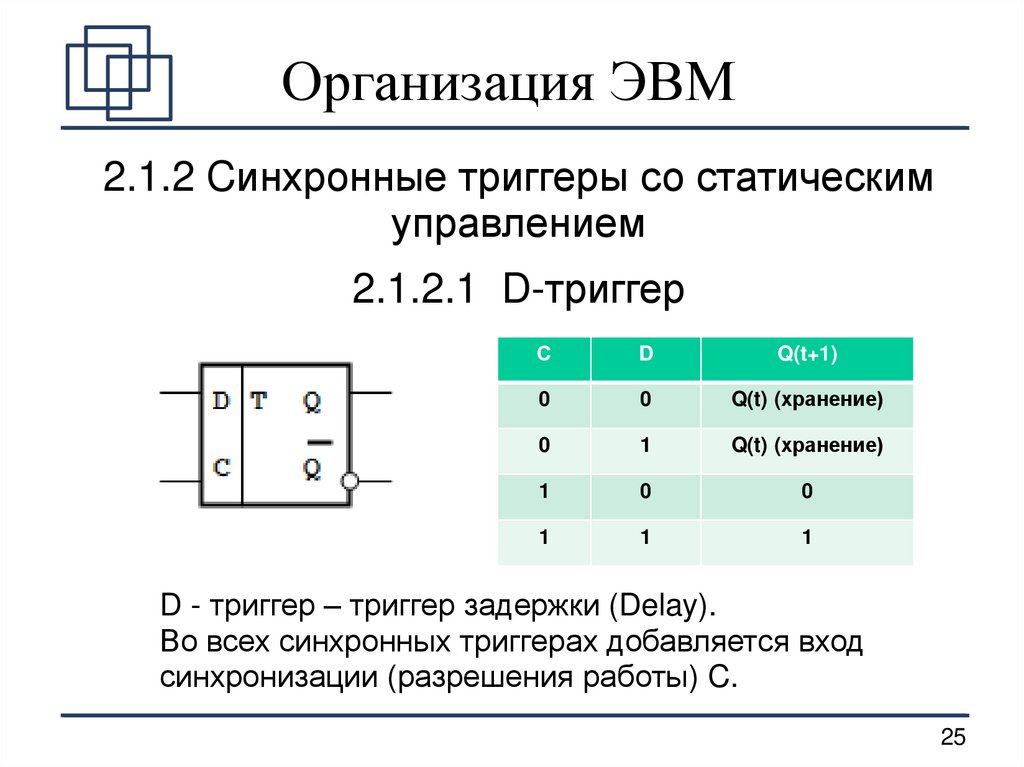

25. Организация ЭВМ

2.1.2 Cинхронные триггеры со статическимуправлением

2.1.2.1 D-триггер

С

D

Q(t+1)

0

0

Q(t) (хранение)

0

1

Q(t) (хранение)

1

0

0

1

1

1

D - триггер – триггер задержки (Delay).

Во всех синхронных триггерах добавляется вход

синхронизации (разрешения работы) C.

25

26. Организация ЭВМ

2.1.2 Cинхронные триггеры со статическимуправлением

2.1.2.2 RS- и другие типы триггеров

Аналогично D – триггер работает по своей таблице

при разрешающем сигнале C (управление уровнем).

26

27. Организация ЭВМ

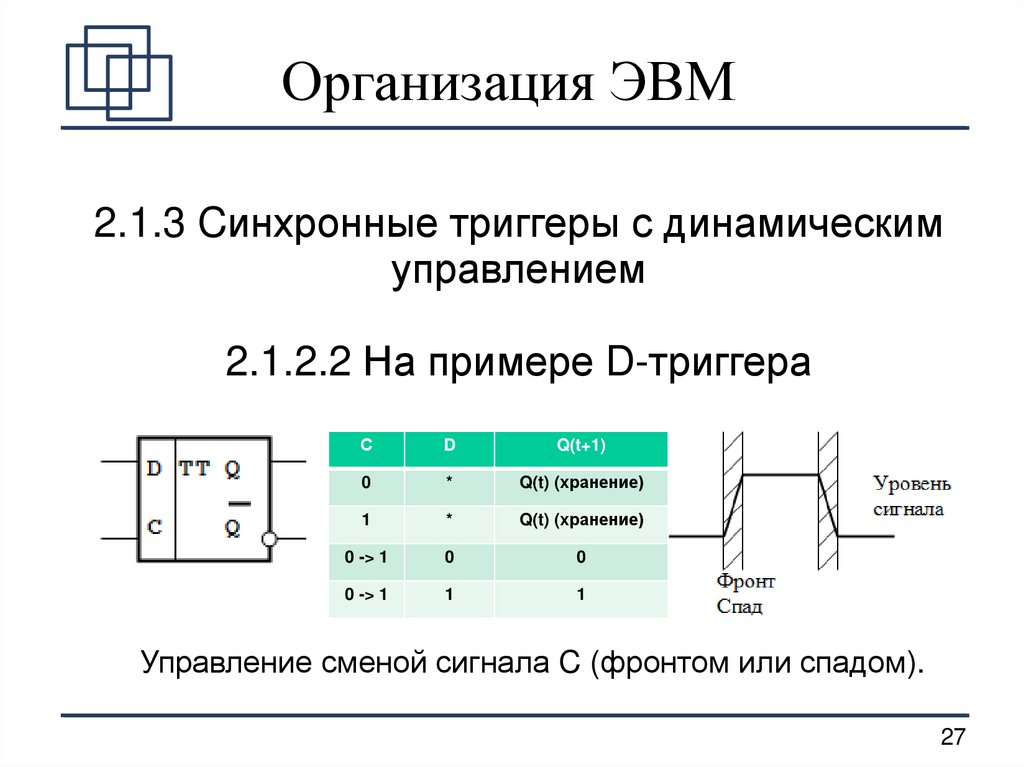

2.1.3 Cинхронные триггеры с динамическимуправлением

2.1.2.2 На примере D-триггера

С

D

Q(t+1)

0

*

Q(t) (хранение)

1

*

Q(t) (хранение)

0 -> 1

0

0

0 -> 1

1

1

Управление сменой сигнала C (фронтом или спадом).

27

28. Организация ЭВМ

2.2 РегистрыРегистр – набор триггеров с дополнительными схемами

управления и передачи сигналов для хранения

многоразрядных двоично-кодированных слов и

выполнения некоторых простых операций

(например, сдвиг) над ними.

Типы регистров :

1)Регистры хранения

2)Регистры сдвига (сдвиговые регистры)

3)Многофункциональные регистры (арифметические и

циклические сдвиги, перекодирование и др.)

28

29. Организация ЭВМ

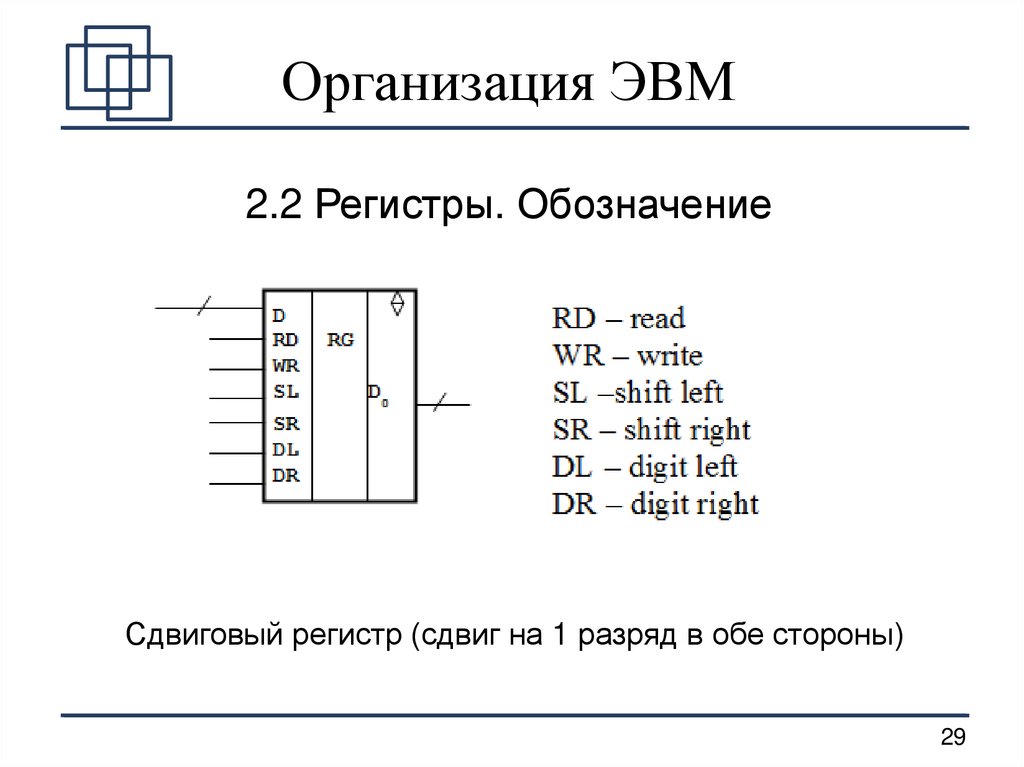

2.2 Регистры. ОбозначениеСдвиговый регистр (сдвиг на 1 разряд в обе стороны)

29

30. Организация ЭВМ

2.3 СчетчикиСчетчик – набор триггеров с дополнительными схемами

управления и передачи сигналов для хранения

многоразрядных двоично-кодированных слов и

выполнения операций счета (инкремент, декремент)

над ними, в том числе – по модулю.

Типы счетчиков :

1)Двоичные (от 0 до 2n – 1)

2)Одно - и двунаправленные

(суммирующие, вычитающие, реверсивные)

3)По указанному модулю K (считают до от 0 до K - 1).

30

31. Организация ЭВМ

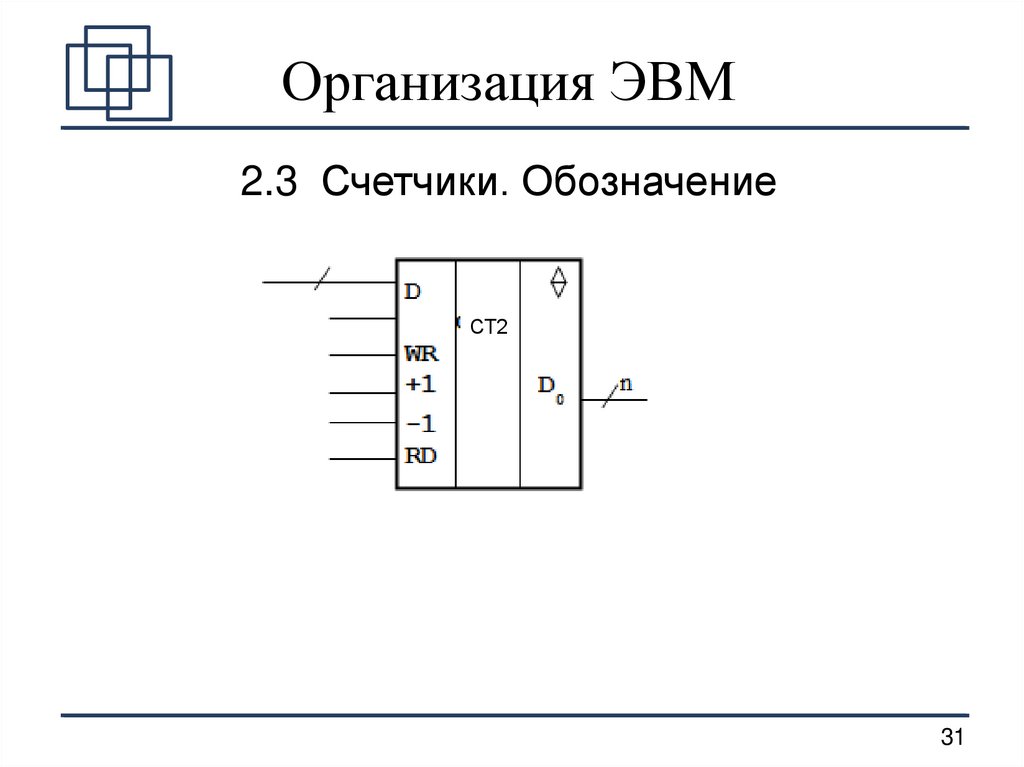

2.3 Счетчики. ОбозначениеСТ2

31

Электроника

Электроника