Похожие презентации:

Коммутационные схемы

1. Коммутационные схемы

Лектор: Завьялов Олег Геннадьевичкандидат физико-математических наук, доцент

2.

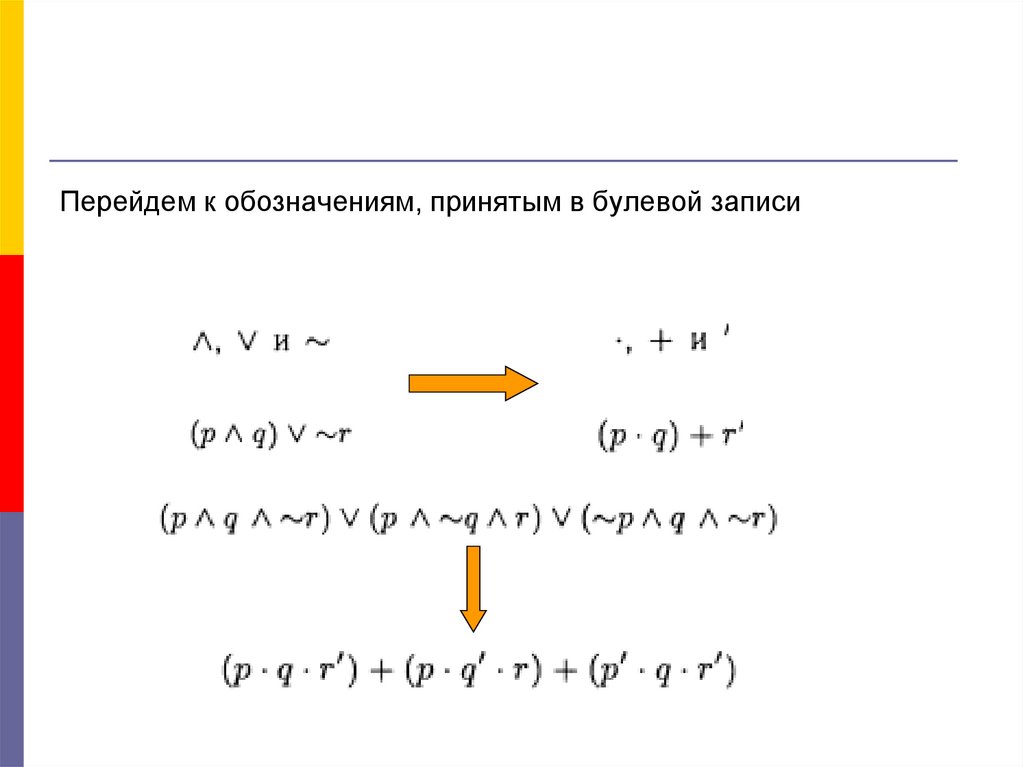

Перейдем к обозначениям, принятым в булевой записи3. Связь между таблицей истинности и электрической цепью (Клод Шеннон, 1838г.)

Схема логического умножения4. Схема логического сложения

5. Логический элемент не Инвертор

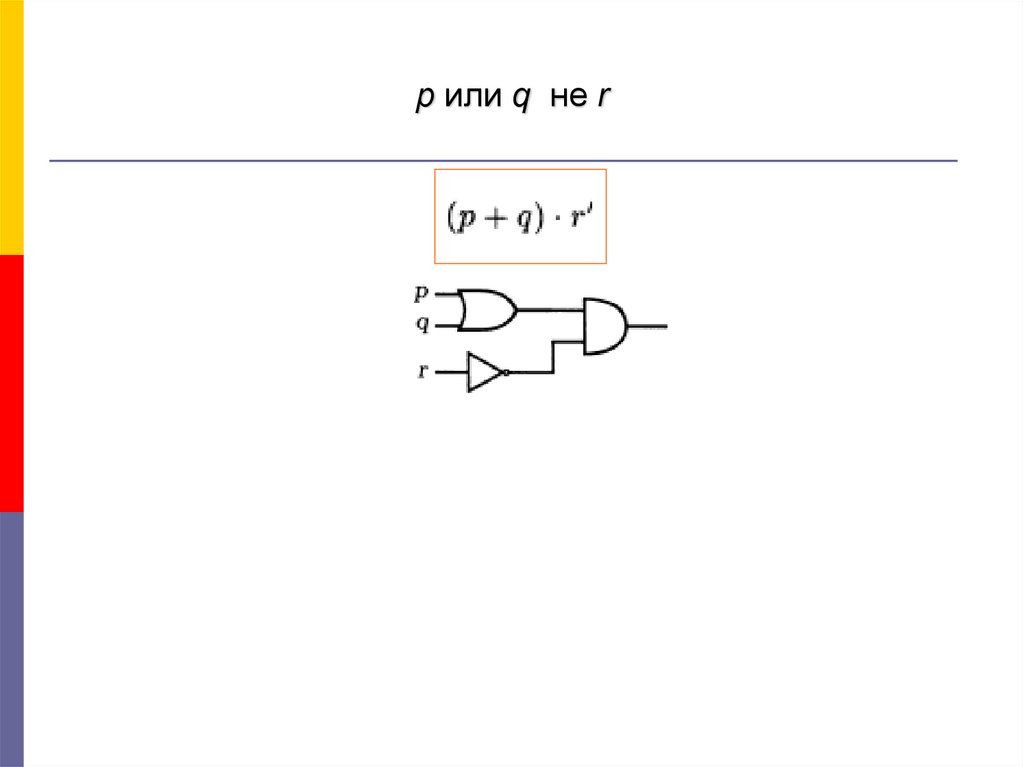

Инвертор отрицает всю предшествующую схему6. p или q не r

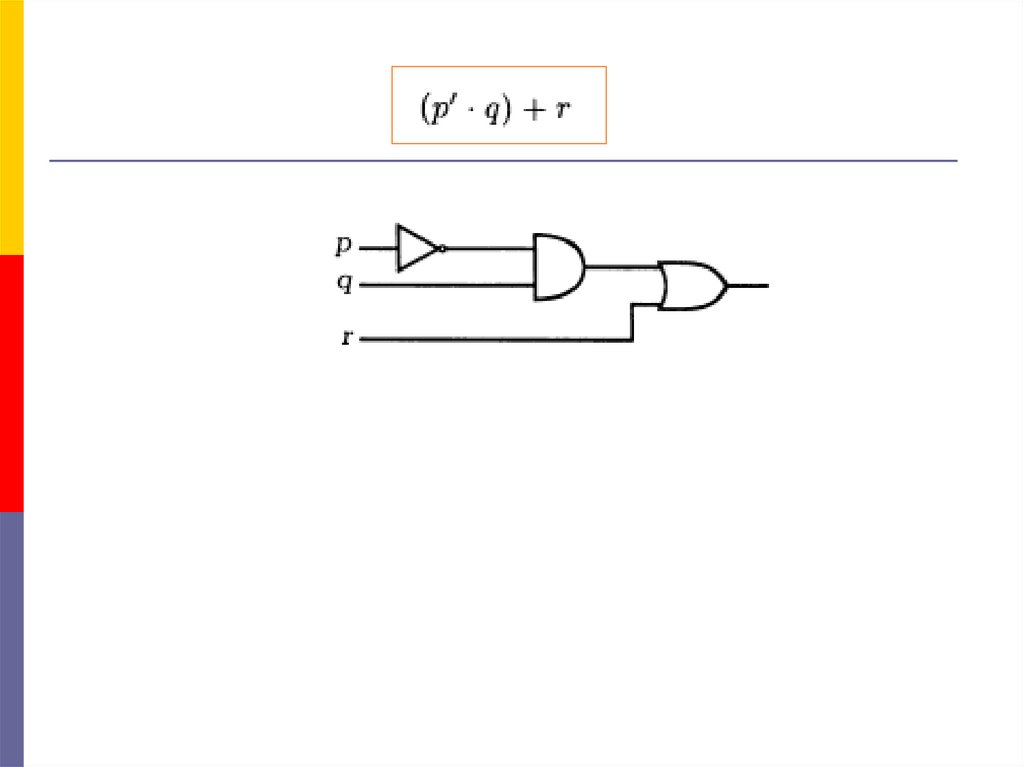

7.

8.

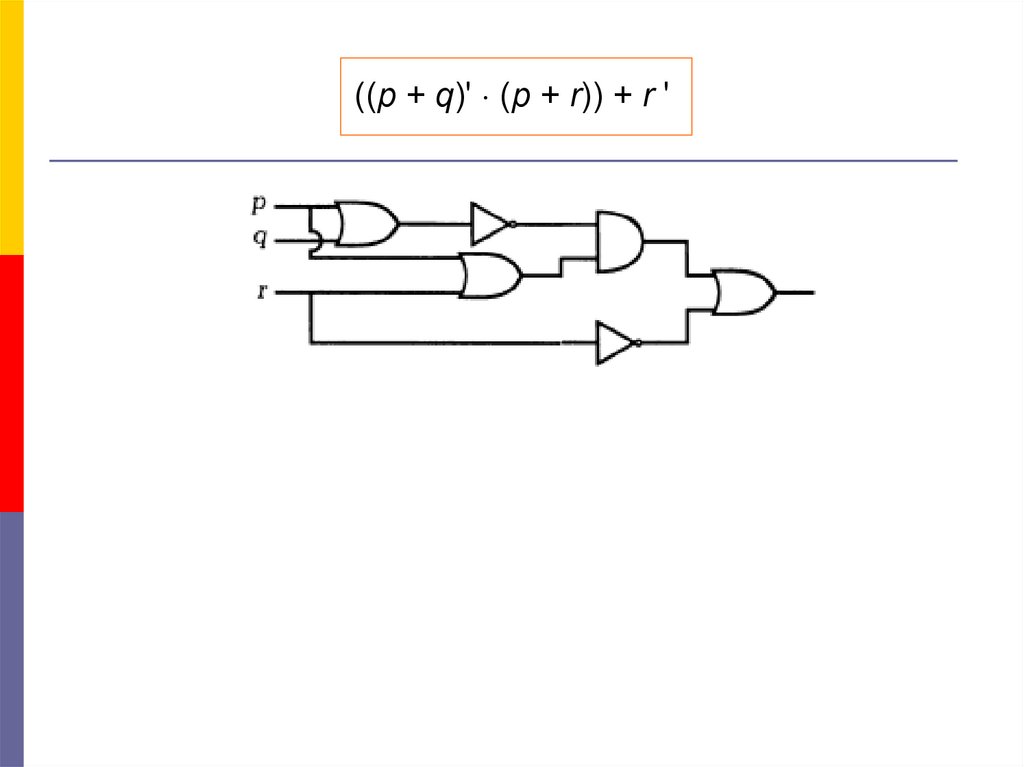

9. ((p + q)' (p + r)) + r '

((p + q)' (p + r)) + r '10. p q r

pqr11.

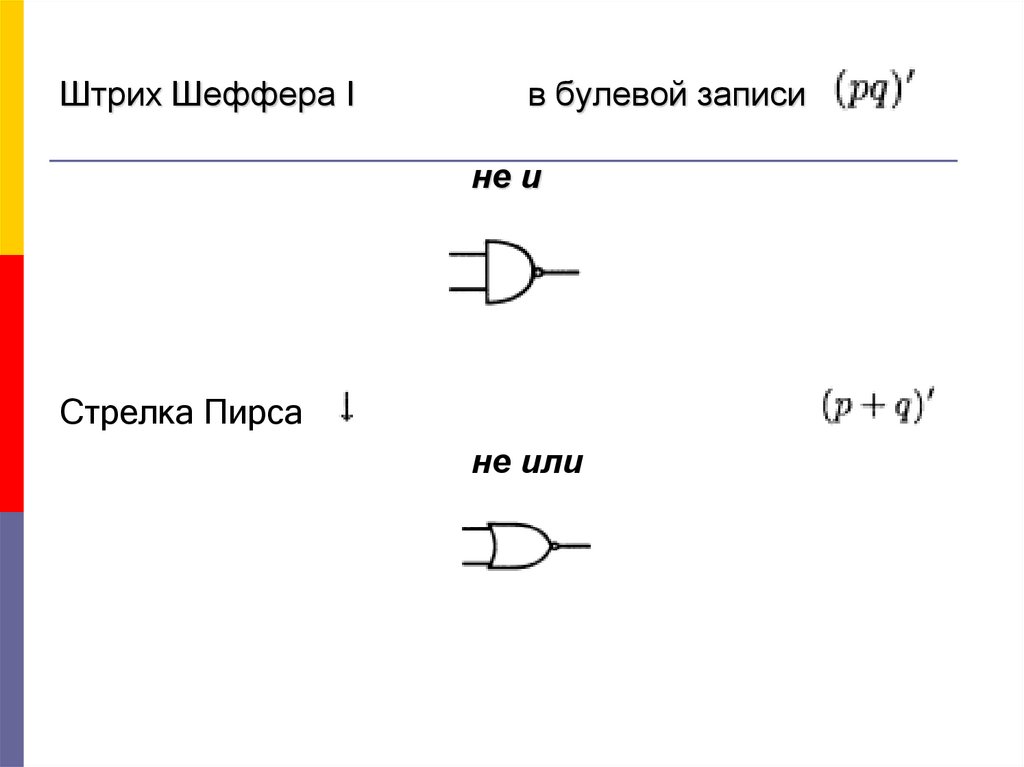

12. Штрих Шеффера I в булевой записи не и

Стрелка Пирсане или

13.

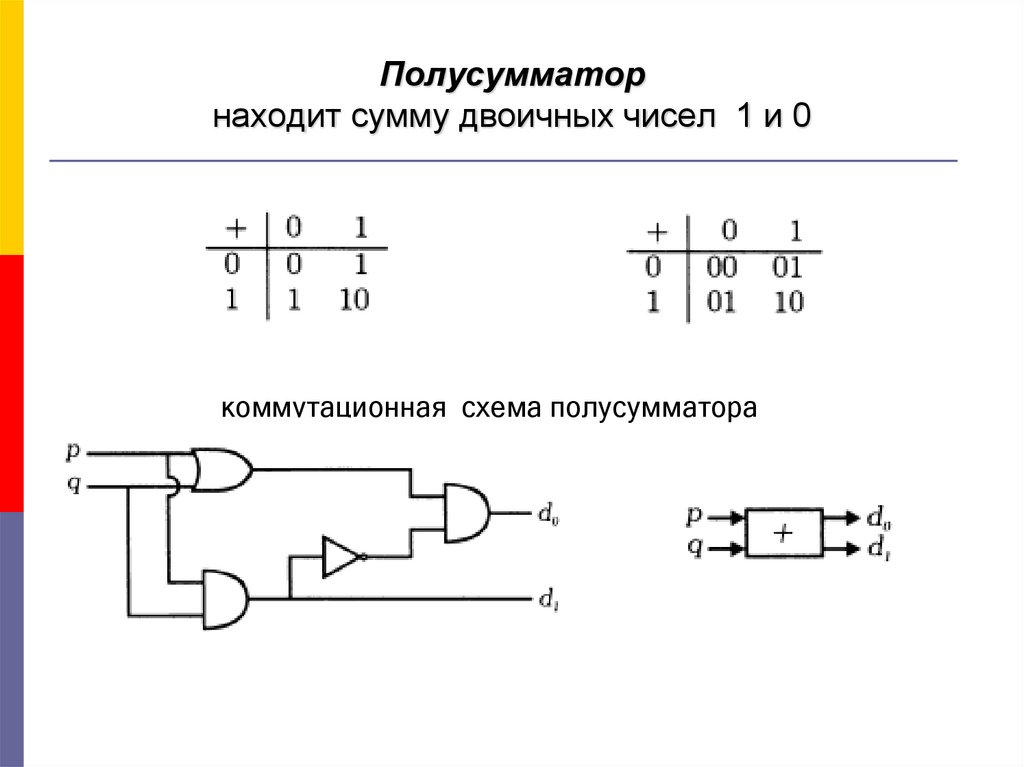

14. Полусумматор находит сумму двоичных чисел 1 и 0

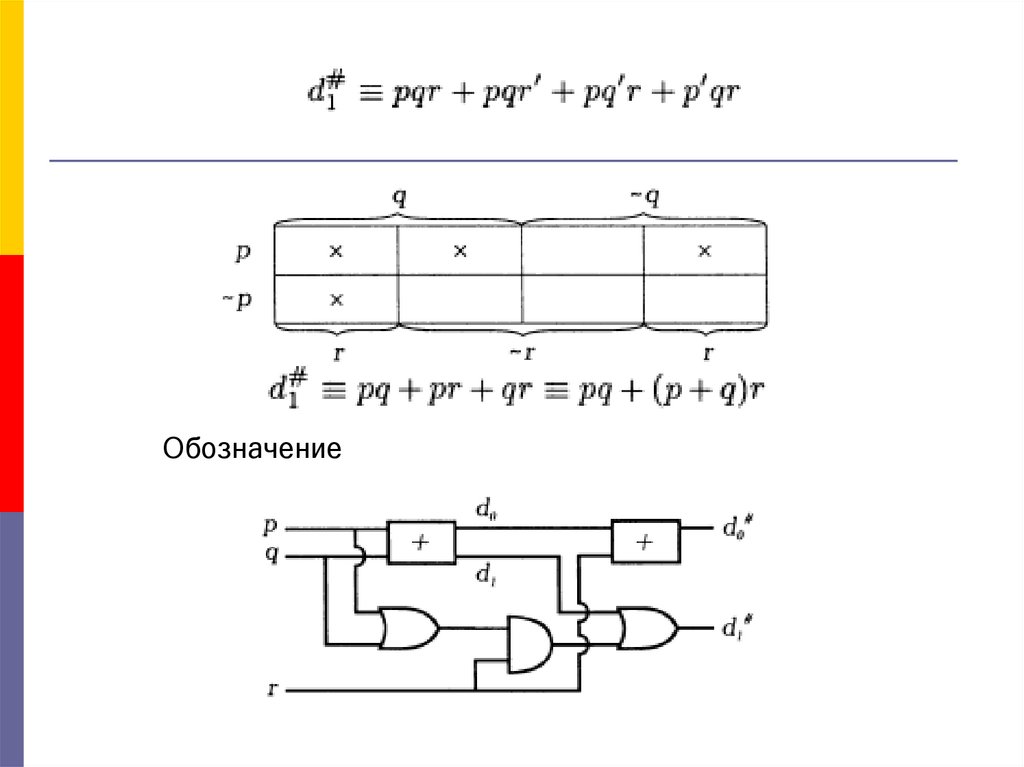

коммутационная схема полусумматора15. Полный сумматор складывает три одноразрядных двоичных числа

16.

Обозначение17. подробнее

18. Обозначение полного сумматора

19. Триггер Триггер на элементах Шеффера

Прямой выход обозначается буквой без инверсии, инверсный– буквой со знаком отрицания.

Вход R называется нулевым, S – единичным.

Триггер устанавливается в нулевое состояние, если принять

R=0, S=1.

На прямом (неинверсном) выходе А=0, а на инверсном

20.

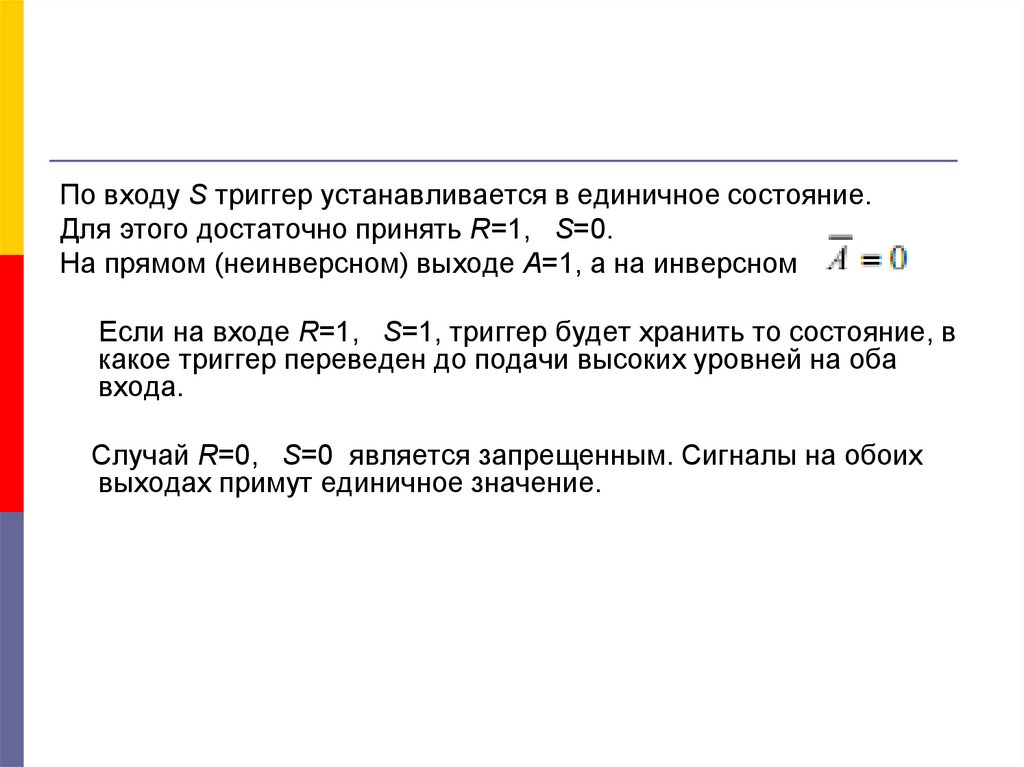

По входу S триггер устанавливается в единичное состояние.Для этого достаточно принять R=1, S=0.

На прямом (неинверсном) выходе А=1, а на инверсном

Если на входе R=1, S=1, триггер будет хранить то состояние, в

какое триггер переведен до подачи высоких уровней на оба

входа.

Случай R=0, S=0 является запрещенным. Сигналы на обоих

выходах примут единичное значение.

21. Триггер на элементах Пирса

Отличается от триггера на элементах Шеффера тем, чтоменяет свои состояния не низких уровней, а высоких.

Запрещенным является состояние R=1, S=1.

Электроника

Электроника