Похожие презентации:

Логические основы устройства компьютера

1. Логические основы устройства компьютера

2. Базовые логические элементы

Базовые логические элементы –реализуют три основные логические операции:

Логический элемент «И» - логическое умножение

Логический элемент «ИЛИ» - логическое сложение

Логический элемент «НЕ» - инверсия

3.

Логические элементы компьютера оперируют ссигналами – электрическими импульсами.

Есть импульс – логический смысл сигнала – 1.

Нет импульса – 0.

На входы логического элемента поступают

сигналы-значения аргументов, на выходе

появляется сигнал-значение функции.

4.

Преобразование сигнала логическимэлементом задается таблицей состояния,

которая фактически

является таблицей истинности.

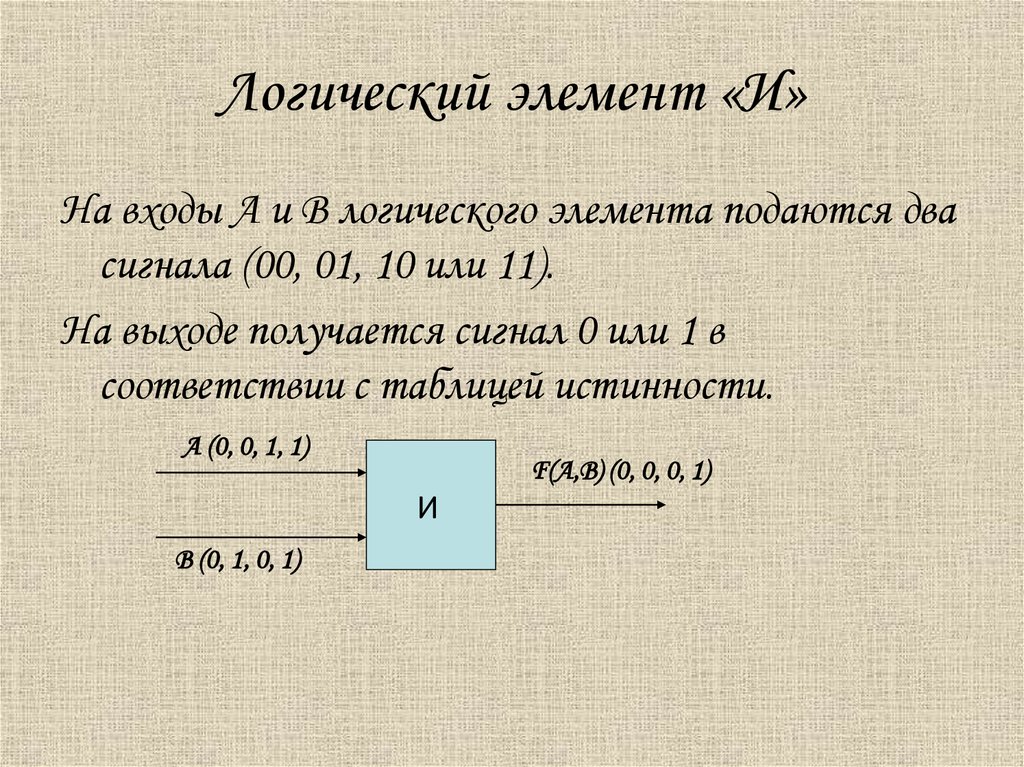

5. Логический элемент «И»

На входы А и В логического элемента подаются двасигнала (00, 01, 10 или 11).

На выходе получается сигнал 0 или 1 в

соответствии с таблицей истинности.

А (0, 0, 1, 1)

F(А,В) (0, 0, 0, 1)

И

В (0, 1, 0, 1)

6.

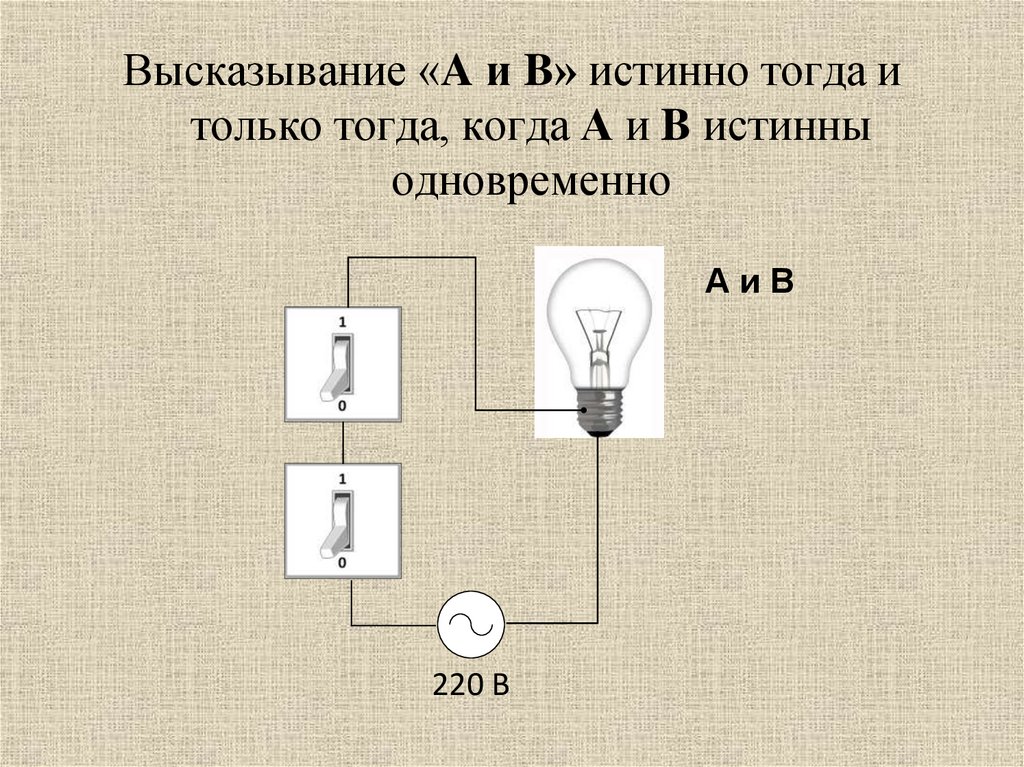

Высказывание «A и B» истинно тогда итолько тогда, когда А и B истинны

одновременно

AиB

220 В

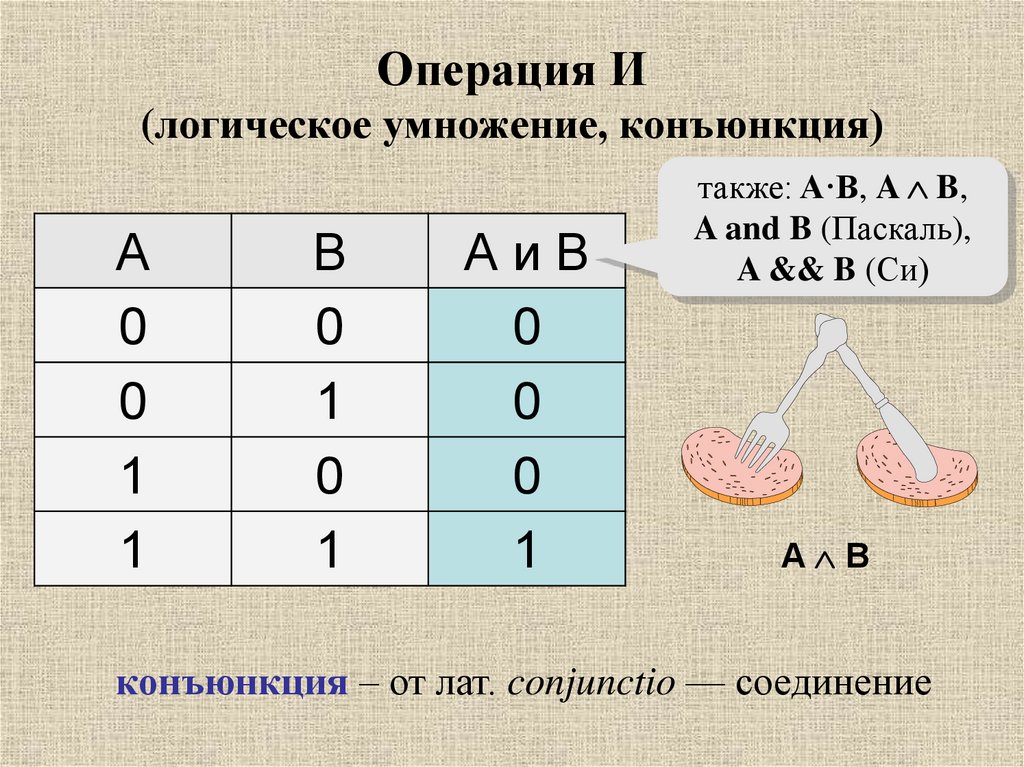

7. Операция И (логическое умножение, конъюнкция)

A0

0

1

1

B

0

1

0

1

АиB

0

0

0

1

также: A·B, A B,

A and B (Паскаль),

A && B (Си)

A B

конъюнкция – от лат. conjunctio — соединение

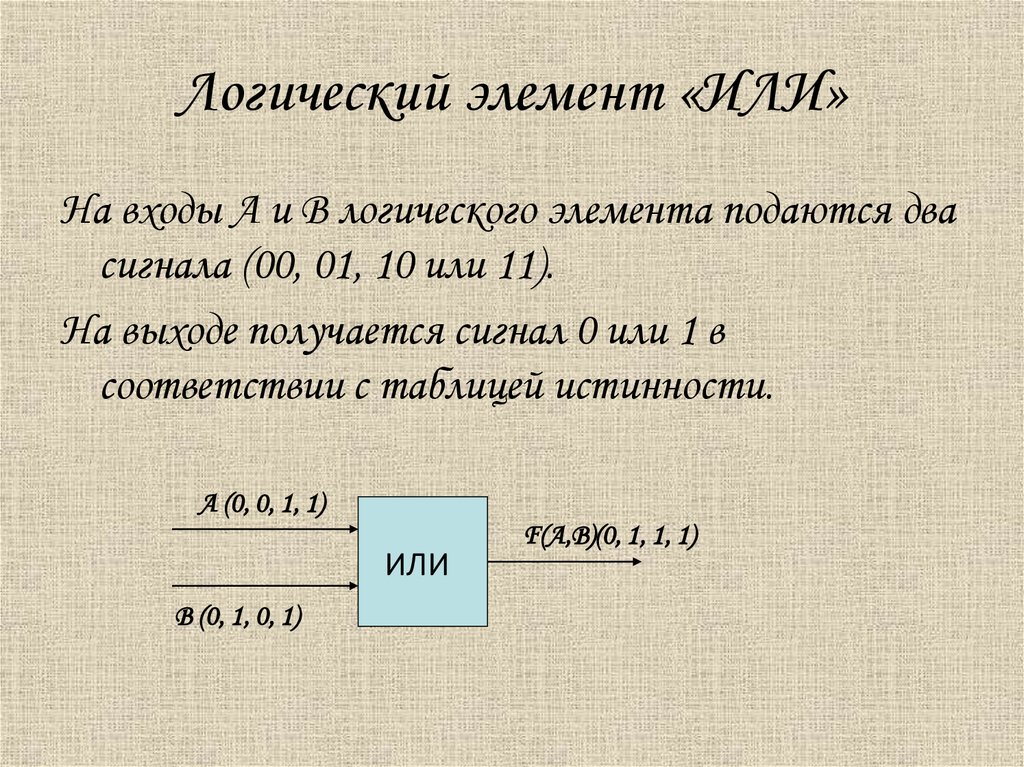

8. Логический элемент «ИЛИ»

На входы А и В логического элемента подаются двасигнала (00, 01, 10 или 11).

На выходе получается сигнал 0 или 1 в

соответствии с таблицей истинности.

А (0, 0, 1, 1)

ИЛИ

В (0, 1, 0, 1)

F(А,В)(0, 1, 1, 1)

9.

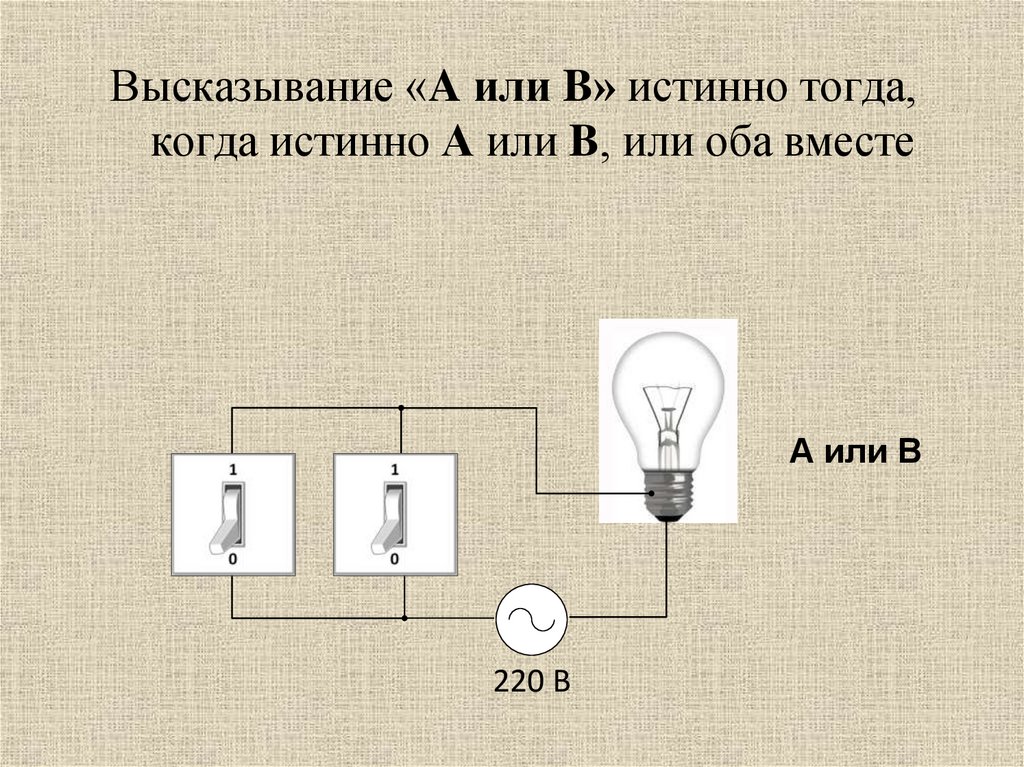

Высказывание «A или B» истинно тогда,когда истинно А или B, или оба вместе

A или B

220 В

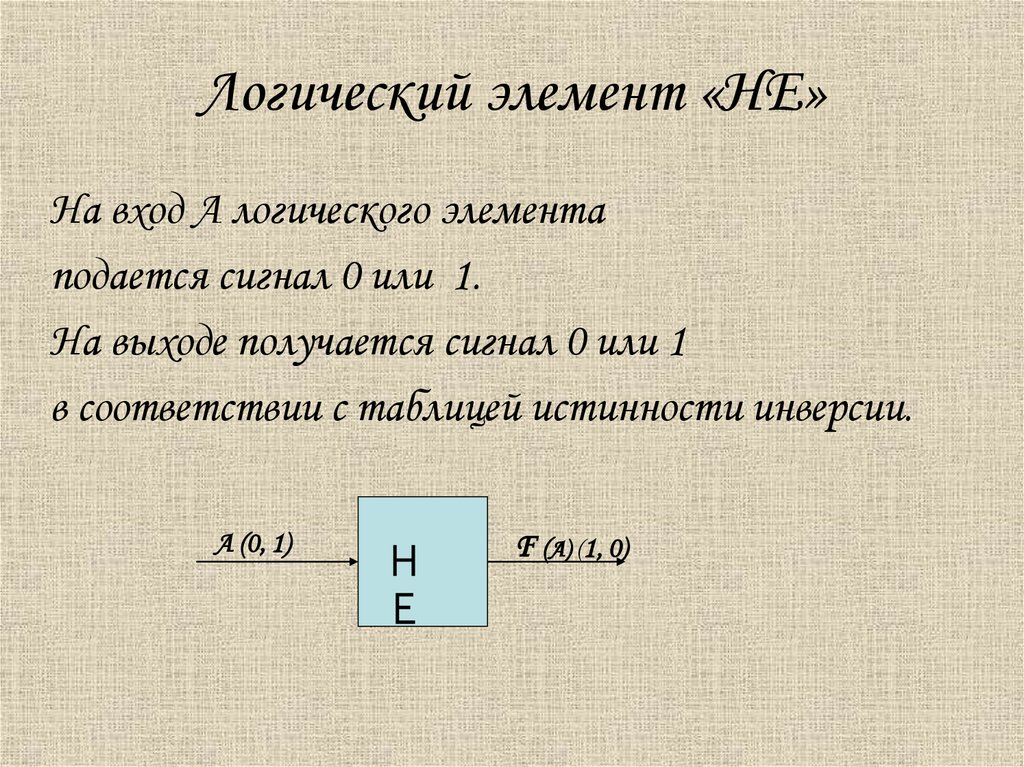

10. Логический элемент «НЕ»

На вход А логического элементаподается сигнал 0 или 1.

На выходе получается сигнал 0 или 1

в соответствии с таблицей истинности инверсии.

А (0, 1)

Н

Е

F (А) (1, 0)

11.

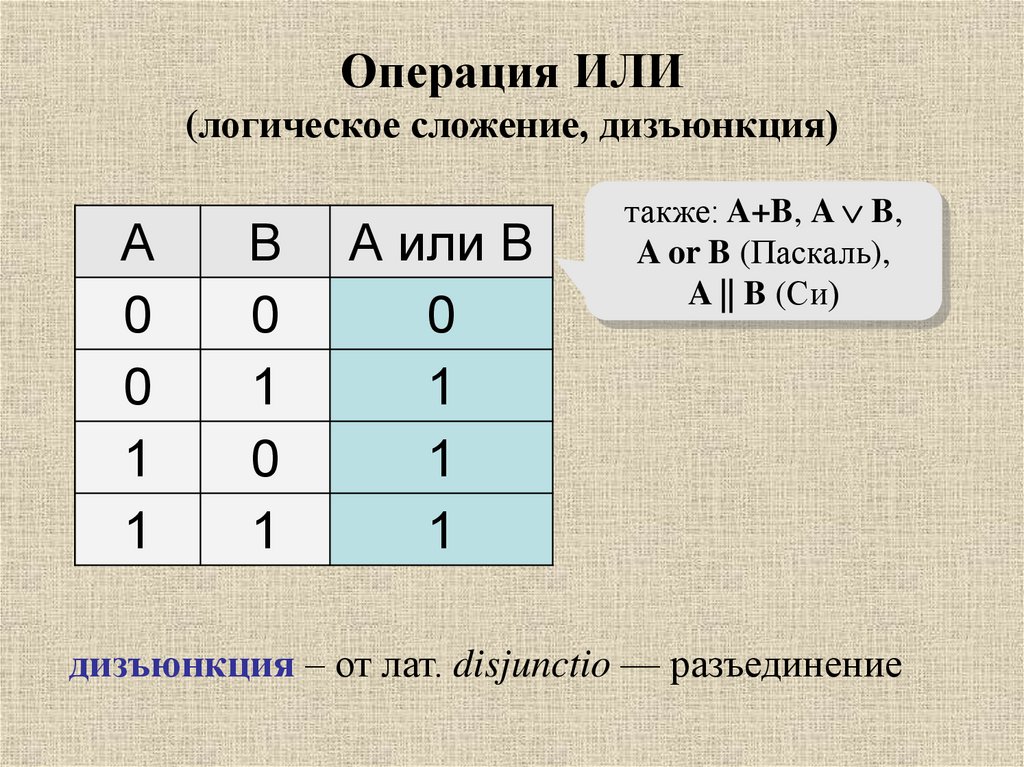

Операция ИЛИ(логическое сложение, дизъюнкция)

A

0

0

1

1

B

0

1

0

1

А или B

0

1

1

1

также: A+B, A B,

A or B (Паскаль),

A || B (Си)

дизъюнкция – от лат. disjunctio — разъединение

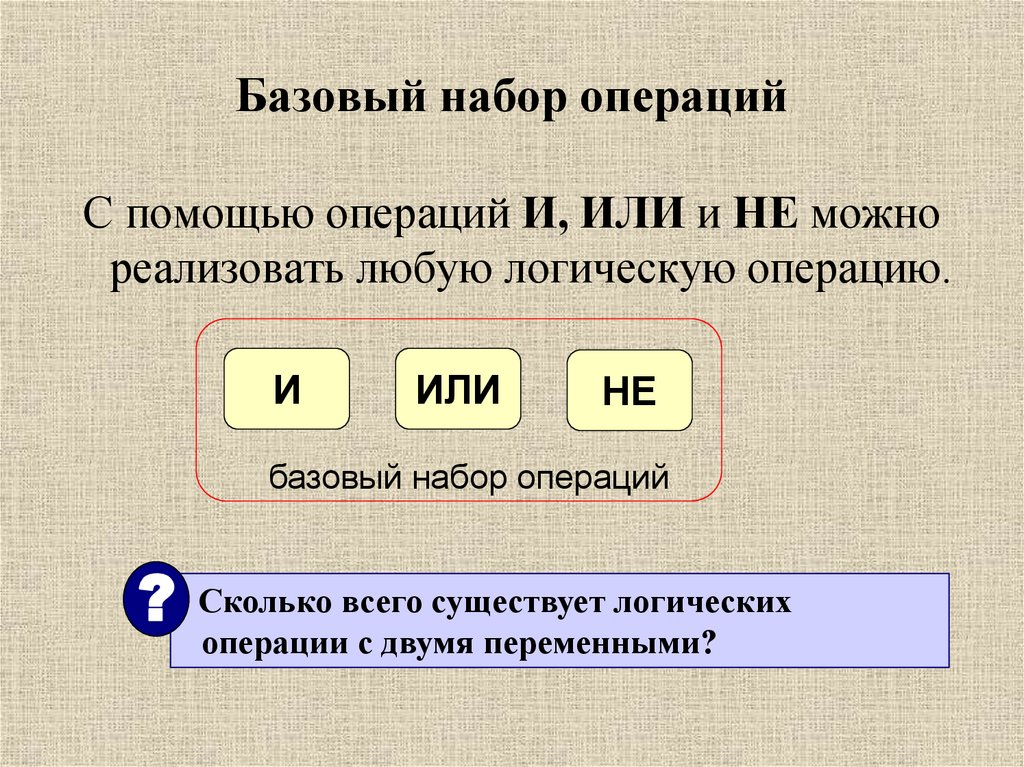

12. Базовый набор операций

С помощью операций И, ИЛИ и НЕ можнореализовать любую логическую операцию.

И

ИЛИ

НЕ

базовый набор операций

? Сколько всего существует логических

операции с двумя переменными?

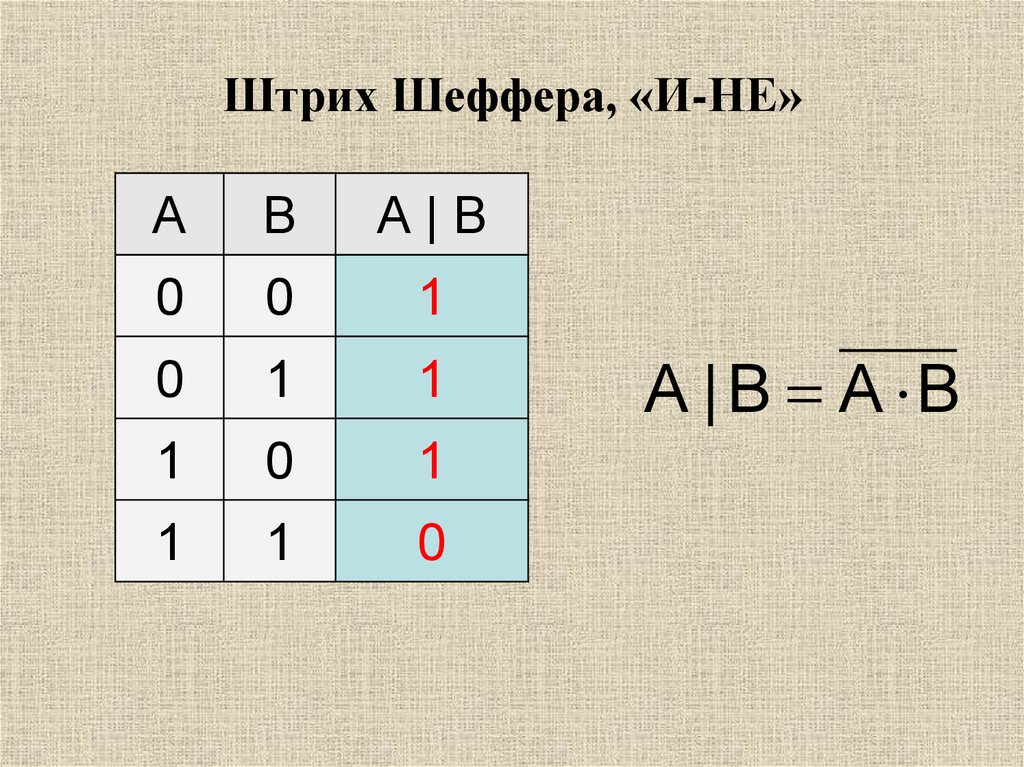

13. Штрих Шеффера, «И-НЕ»

AB

А|B

0

0

1

0

1

1

1

0

1

1

1

0

A | B A B

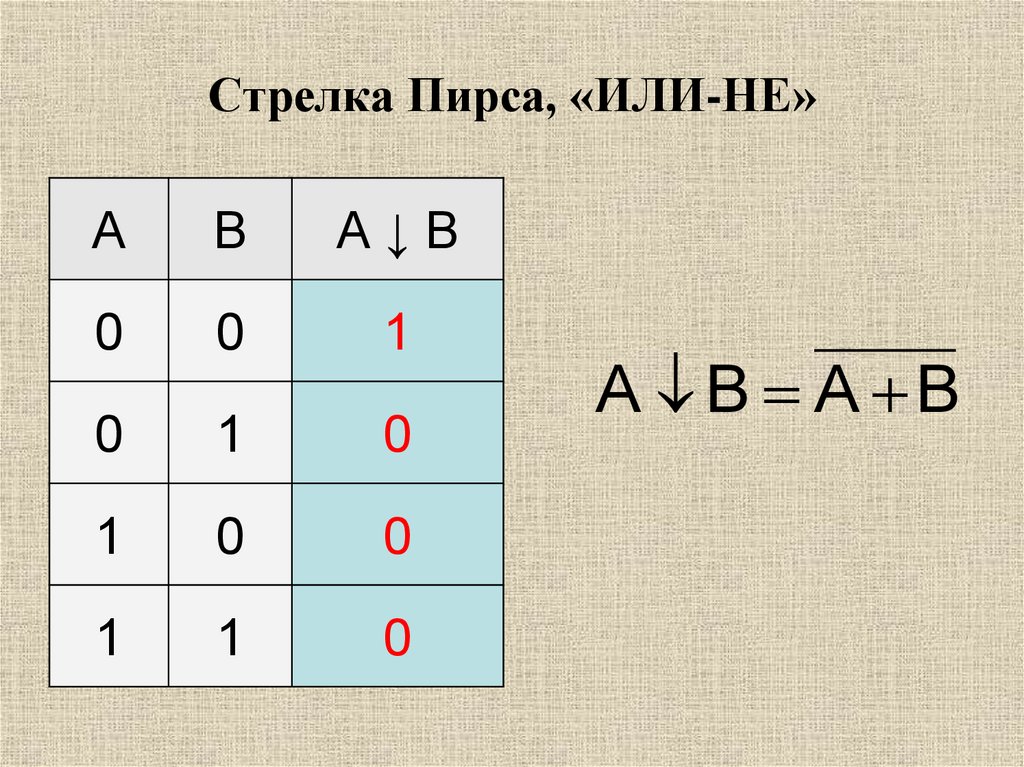

14. Стрелка Пирса, «ИЛИ-НЕ»

AB

А↓B

0

0

1

0

1

0

1

0

0

1

1

0

A B A B

15. Логические элементы компьютера

значокинверсии

A

A

A

&

A B

B

НЕ

A

B

И

A

&

B

A B

ИЛИ

A

1

B

И-НЕ

1

ИЛИ-НЕ

A B

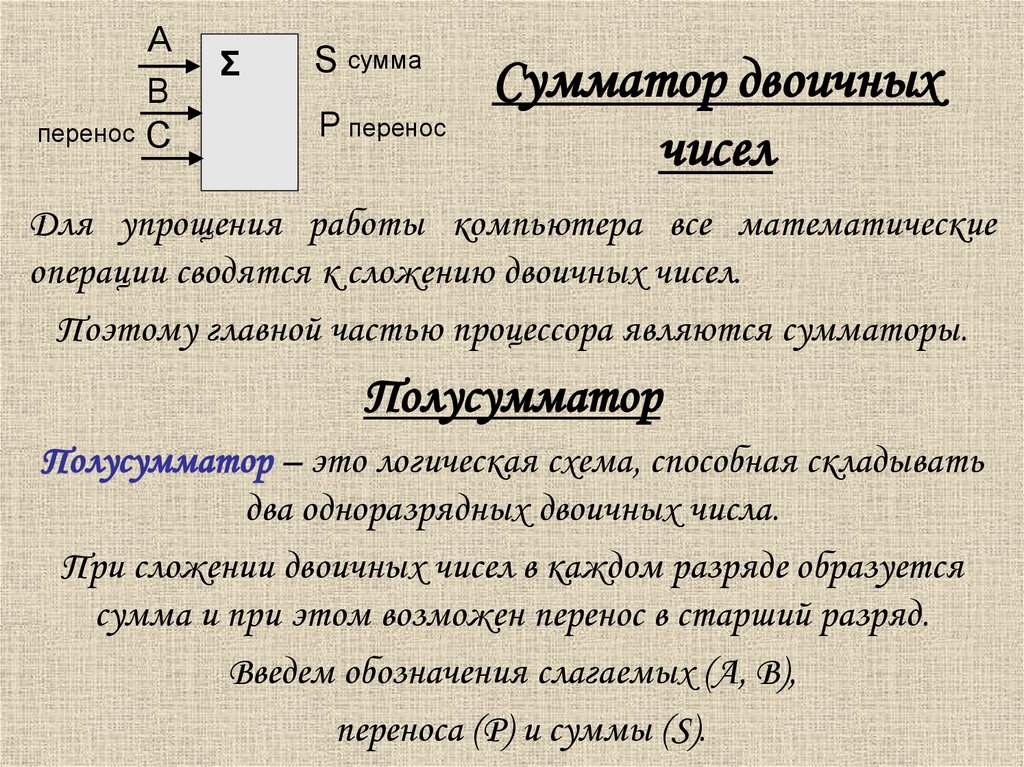

16. Сумматор двоичных чисел

AB

перенос C

Σ

S сумма

P перенос

Сумматор двоичных

чисел

Для упрощения работы компьютера все математические

операции сводятся к сложению двоичных чисел.

Поэтому главной частью процессора являются сумматоры.

Полусумматор

Полусумматор – это логическая схема, способная складывать

два одноразрядных двоичных числа.

При сложении двоичных чисел в каждом разряде образуется

сумма и при этом возможен перенос в старший разряд.

Введем обозначения слагаемых (А, В),

переноса (Р) и cуммы (S).

17.

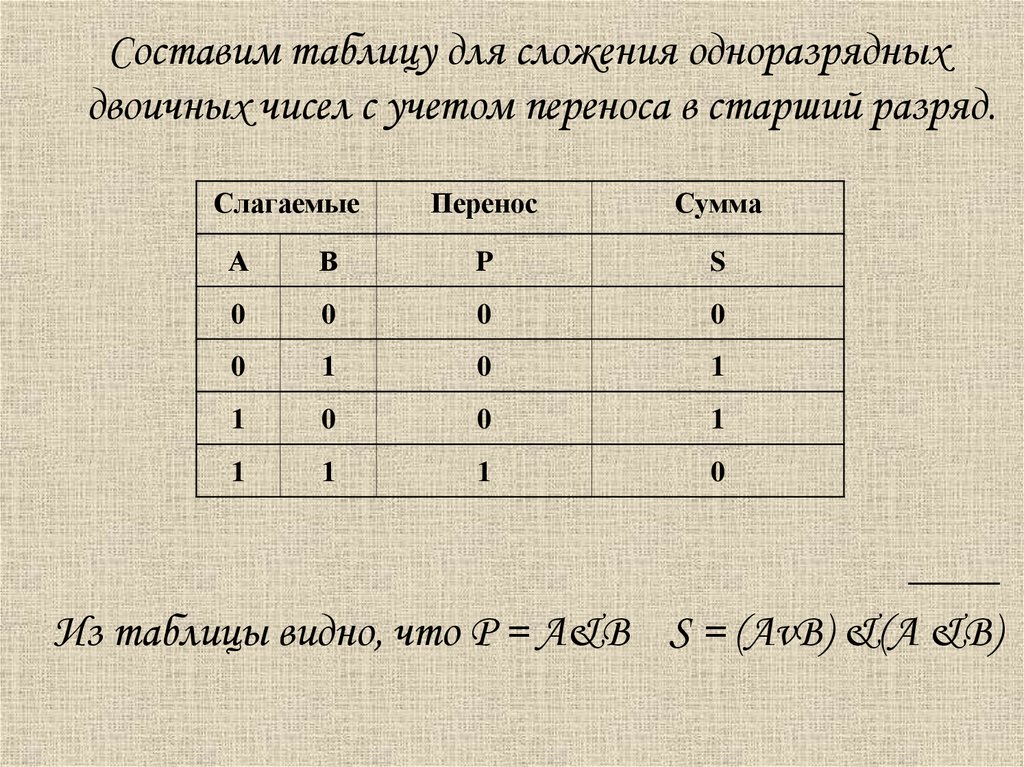

Составим таблицу для сложения одноразрядныхдвоичных чисел с учетом переноса в старший разряд.

Слагаемые

Перенос

Сумма

А

В

P

S

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

____

Из таблицы видно, что Р = А&В S = (AvB) &(A &B)

18.

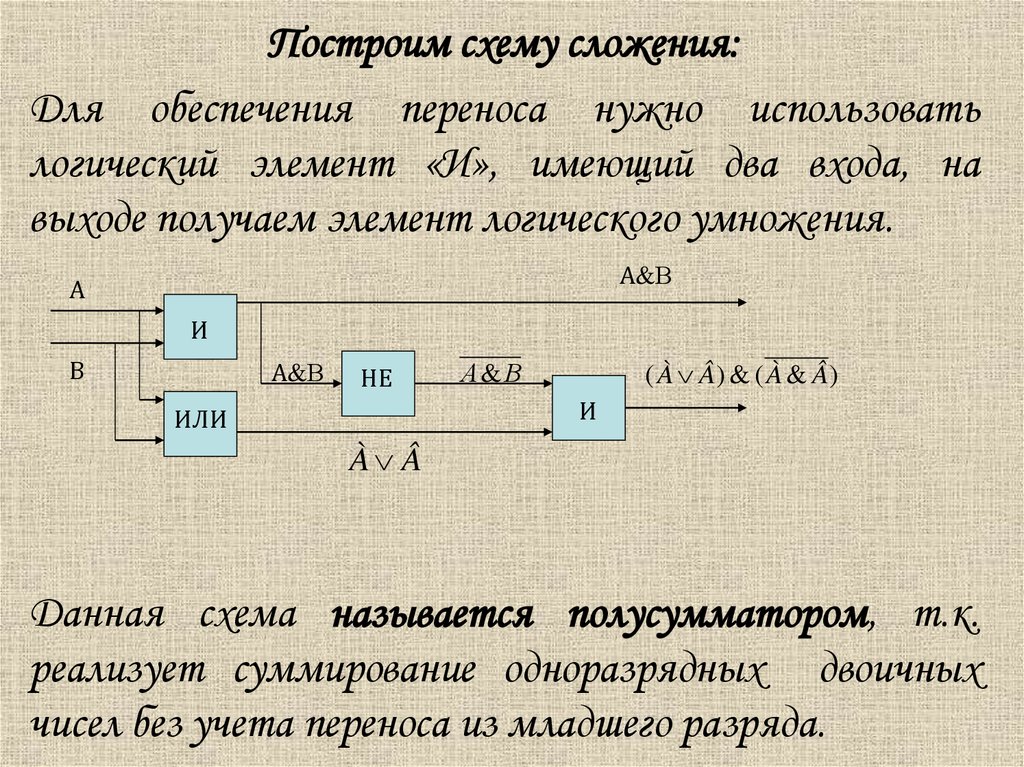

Построим схему сложения:Для обеспечения переноса нужно использовать

логический элемент «И», имеющий два входа, на

выходе получаем элемент логического умножения.

А&В

А

И

В

А&В

НЕ

( À Â) & ( À & Â)

А& В

И

ИЛИ

À Â

Данная схема называется полусумматором, т.к.

реализует суммирование одноразрядных двоичных

чисел без учета переноса из младшего разряда.

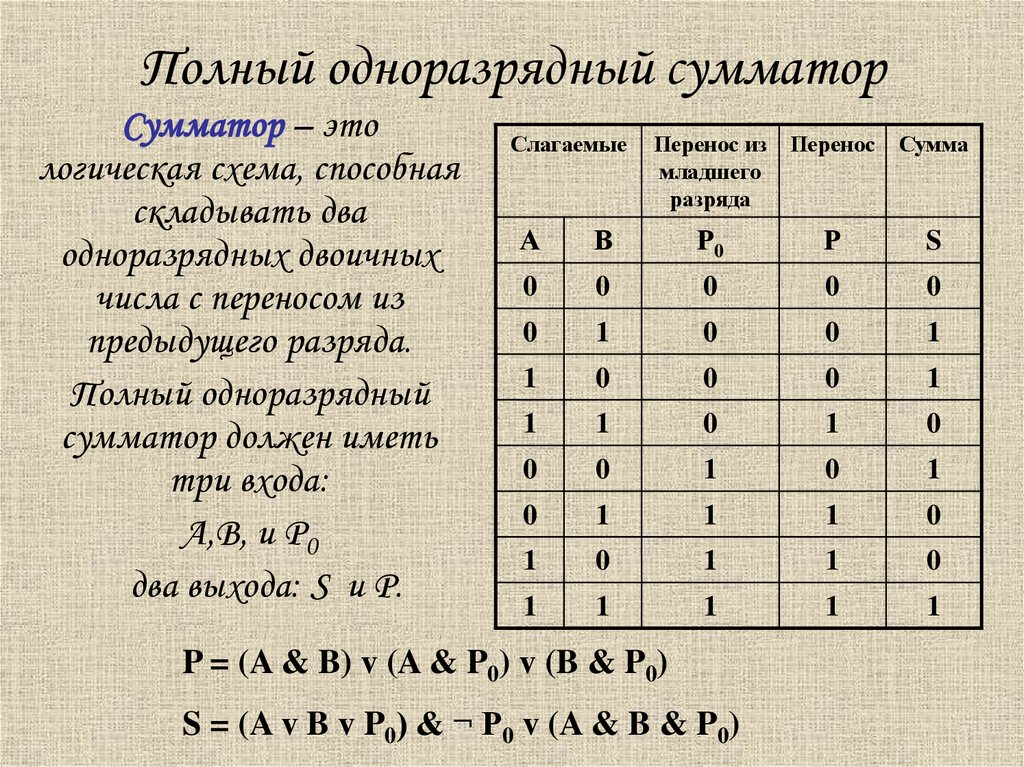

19. Полный одноразрядный сумматор

Сумматор – этологическая схема, способная

складывать два

одноразрядных двоичных

числа с переносом из

предыдущего разряда.

Полный одноразрядный

сумматор должен иметь

три входа:

А,В, и Р0

два выхода: S и Р.

Слагаемые

Перенос из

младшего

разряда

Перенос

Сумма

А

В

Р0

Р

S

0

0

0

0

0

0

1

0

0

1

1

0

0

0

1

1

1

0

1

0

0

0

1

0

1

0

1

1

1

0

1

0

1

1

0

1

1

1

1

1

P = (A & B) v (A & P0) v (B & P0)

S = (A v B v P0) & ¬ P0 v (A & B & P0)

20.

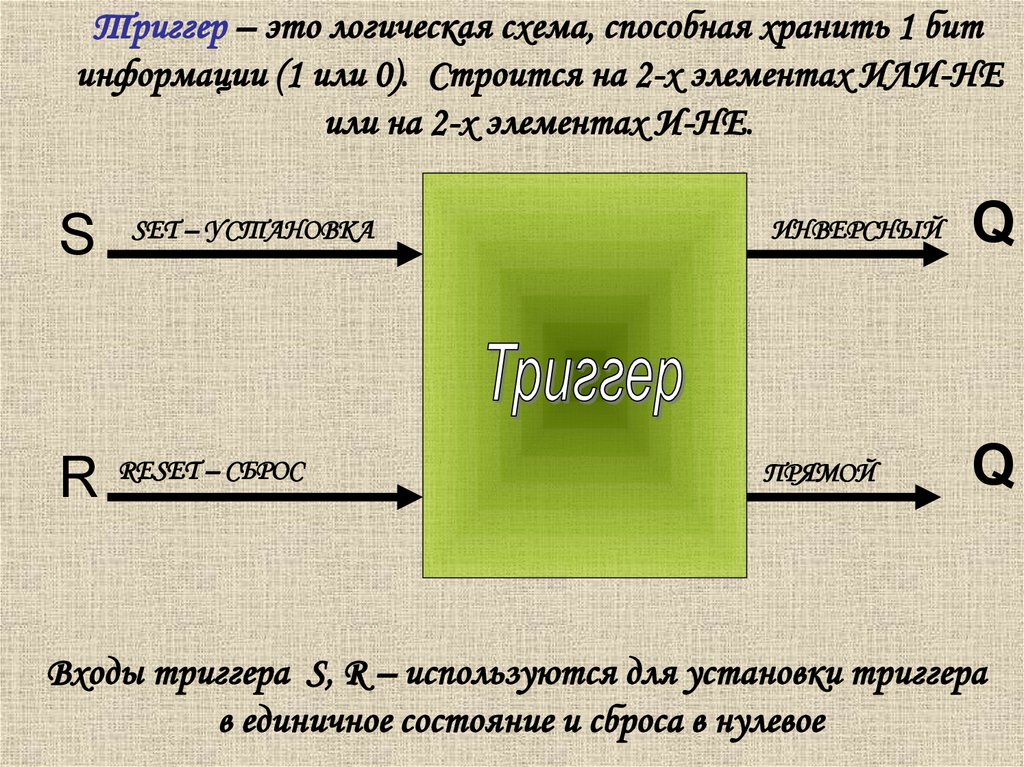

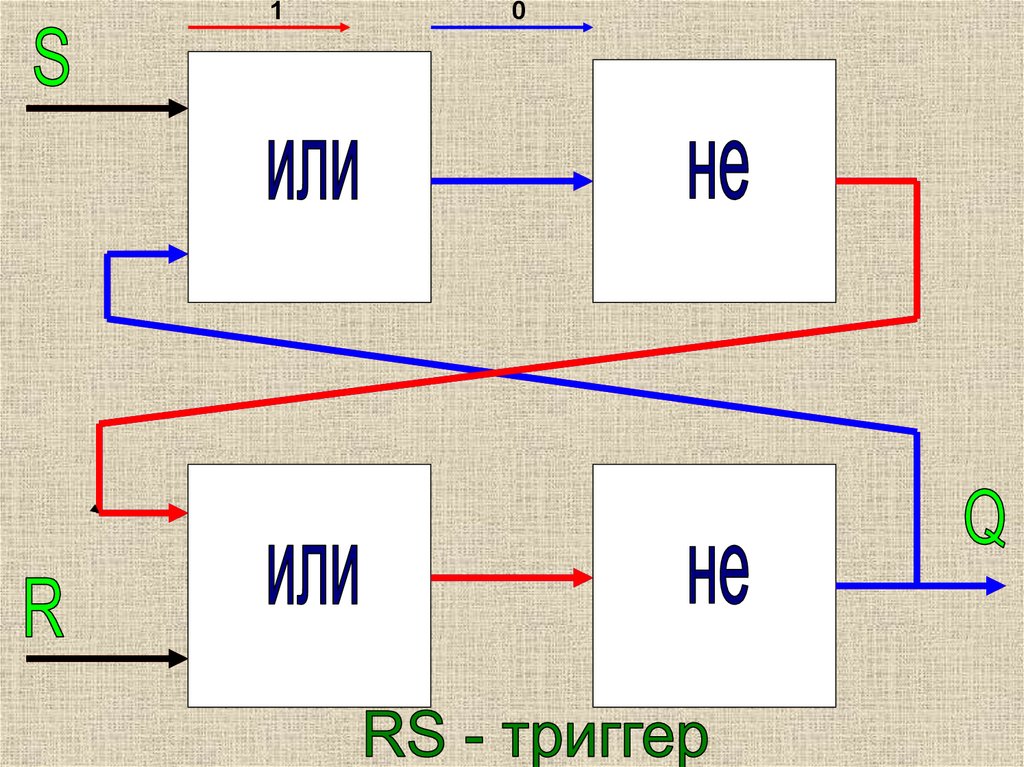

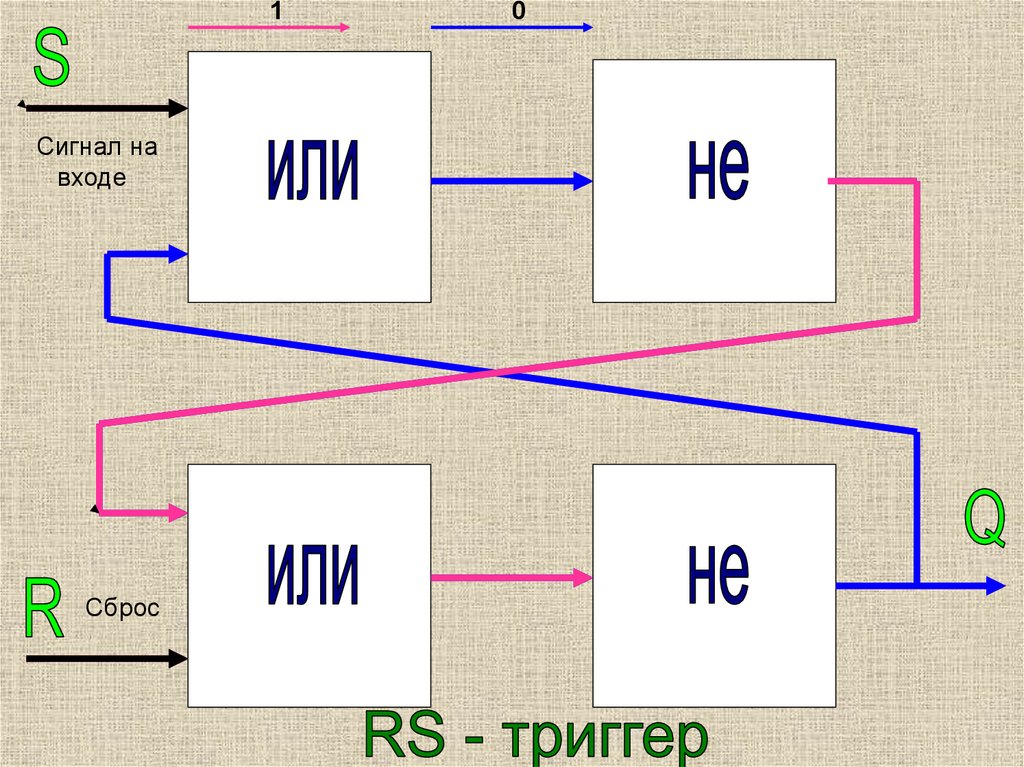

Триггер – это логическая схема, способная хранить 1 битинформации (1 или 0). Строится на 2-х элементах ИЛИ-НЕ

или на 2-х элементах И-НЕ.

S SET – УСТАНОВКА

ИНВЕРСНЫЙ

Q

R RESET – СБРОС

ПРЯМОЙ

Q

Входы триггера S, R – используются для установки триггера

в единичное состояние и сброса в нулевое

21.

10

22.

1Сигнал на

входе

Сброс

0

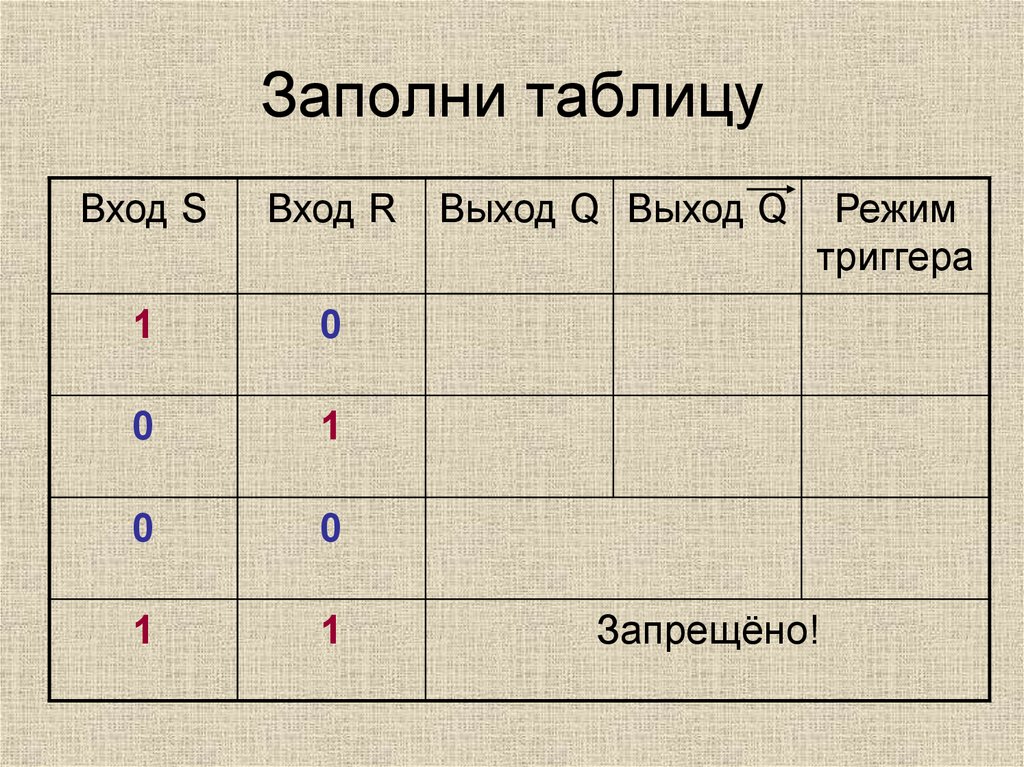

23. Заполни таблицу

Вход SВход R

1

0

0

1

0

0

1

1

Выход Q Выход Q

Режим

триггера

Запрещёно!

24. Мультиплексоры и демультиплексоры

• Мультиплексоры и демультиплексоры – это оптическиеустройства, выполняющие функции объединения и коммутации

нескольких информационных каналов в сетях и волоконнооптических трактах. На входные порты мультиплексора

поступают потоки данных, которые объединяются в общий

трафик и передаются через выходной порт по оптоволоконной

линии связи. На приемной стороне происходит обратный

процесс, позволяющий выделить исходные сигналы и отправить

их по назначению.

• На сегодняшний день используются две категории

мультиплексоров и демультиплексоров:

– активного типа – оборудование потребляет электроэнергию для своего

функционирования. Область применения – цифровые системы PDH и SDH;

– пассивного типа – оборудование не нуждается во внешнем источнике

электропитания. Мультиплексирование/демультиплексирование сигналов

осуществляется при помощи специальных фильтров. Сфера использования

– системы спектрального уплотнения WDM.

25. Шифратор и дешифратор

• Шифратор — это комбинационное устройство, преобразующеедесятичные числа в двоичную систему счисления, причем

каждому входу может быть поставлено в соответствие

десятичное число, а набор выходных логических сигналов

соответствует определенному двоичному коду.

• Дешифратором называется комбинационное устройство,

преобразующее n-разрядный двоичный код в логический

сигнал, появляющийся на том выходе, десятичный номер

которого соответствует двоичному коду.

Электроника

Электроника