Похожие презентации:

Система команд микропроцессора

1.

Система командмикропроцессора

Один из основных принципов построения ЭВМ был сф ормулирован

американским ученым Дж.ф он Нейманом: работой ЭВМ управляет

программа, состоящая из отдельных команд. Программа размещается

вместе с данными в основной памяти ЭВМ. Каждая команда хранится

в отдельной ячейке памяти (или группе смежных ячеек) и имеет свой

адрес. Все команды имеют одинаковую структуру. Они состоят из двух

частей: кода операции и адресной части.

2.

Код операции и адресная часть**_Код операции_** определяет, какую команду нужно выполнить. **_Адресная часть_**

определяет, где хранятся операнды, т.е. обрабатываемые данные, и куда необходимо

поместить результат операции.

1

Одноадресные команды

В одноадресных командах указывается, где находится один из двух обрабатываемых

операндов. Второй операнд должен быть помещен заранее в арифметическое

устройство (для этого в систему команд вводятся специальные команды пересылки

данных между устройствами).

2

Двухадресные команды

В двухадресных командах оба операнда перед выполнением операции находятся в

памяти, поэтому их адреса указываются в команде. После выполнения команды в один

из этих адресов засылается результат, а находившийся там операнд теряется.

3

Трехадресные команды

В трехадресных командах два адреса указывают, где находятся исходные операнды, а

третий — куда необходимо поместить результат.

4

Четырехадресные команды

В четырехадресных командах три адреса используются для указания исходных

3.

Б езадресные командыВ безадресных командах обычно обрабатывается один операнд, который до и после операции

находится в арифметическом устройстве (в память не пересылается). Кроме того,

безадресные команды используются для выполнения служебных операций (очистить экран,

заблокировать клавиатуру, снять блокировку и др.).

Линейные программы

Все команды программы выполняются последовательно, команда за командой, в том

порядке, как они записаны в памяти ЭВМ (естественный порядок следования команд).

Этот порядок характерен для линейных программ, т.е. программ, не содержащих

разветвлений.

Разветвления

Для организации разветвлений, циклического выполнения участков программы, есть

команды, нарушающие естественный порядок. К ним относятся: безусловная передача

управления (или «безусловный переход»), условная передача управления (т.е. переход,

если выполняется заданное условие), обращение к подпрограмме (т.е. «переход с

возвратом»), циклические операции.

Четырехадресные команды

Кроме того, естественный порядок следования команд не соблюдается в машинах,

использующих четырехадресные команды (в этом случае некоторые из команд передачи

управления упраздняются).

4.

Принудительный порядок следованиякоманд

При явном указании адреса следующей команды реализуется «принудительный» порядок следования команд.

Он возможен только в том случае, если программа размещается в доступной процессору части основной памяти.

Поскольку при этом команды (с точки зрения процессора) ничем не отличаются от данных, в процессе

выполнения программы ее команды можно изменять (модифицировать), что повышает гибкость

программирования и универсальность ЭВМ.

1

Команды пересылки данных

команды пересылки данных внутри МП (MOV, PUSH, POP, XCHNG и т.д.); команды ввода-вывода

(IN, OUT);

2

Арифметические команды

основные (сложение, вычитание, умножение, деление); дополнительные (INS, DEC и др.);

3

Логические команды

сдвиг, дизъюнкция, конъюнкция, отрицание равнозначности и др.;

4

Команды обработки строковых данных

пересылка, сравнение, сканирование, слияние/разделение и др.;

5.

Режимы адресации данныхКаждая команда имеет большое число модиф икаций, чаще всего определяемых режимом адресации данных

(операндов). Операнды бывают трех типов: регистровый, непосредственный и «операнд в памяти».

Регистровые операнды

Непосредственные

операнды

«Операнды в памяти»

указываются именами

Непосредственные операнды

указываться с помощью

используемых регистров МП.

бывают всегда числовые.

регистров, символическими

Причем числа могут быть

именами, константами.

представлены в различных

Различные комбинации этих

системах счисления.

элементов в команде

Различаются они по последней

называются способами

букве, сопровождающей число:

адресации.

Регистровые операнды

«Ь» — двоичное, «q» —

восьмеричное, «d» —

десятичное, «h» —

шестнадцатеричное.

«Операнды в памяти» могут

6.

Способы адрес ацииТак, команда MOV (переслать число) может иметь следующие

способы адресации:

mov r,r

mov sr,m

mov r,m

mov sr,r

mov m,r

mov m,sr

mov r,imed

mov r,sr

mov m,imed

где: г — регистр общего назначения микропроцессора; m —

адрес в памяти; imed — число; sr — сегментный регистр.

7.

Ф изический адрес ОППри использовании «операндов в памяти» указание на ф изический адрес ОП может производиться

непосредственно, косвенно и со смещением.

Непосредственн

ая адрес ация

Косвенная

адрес ация

Б азовая

адрес ация

Индексная

адрес ация

При

При косвенной

В IBM PC базовая

Индексная адресация

непосредственной

адресации

адресация

имеет смысл, когда

адресации

исполнительный

реализована с

надо осуществить

исполнительный

адрес ОП хранится в

использованием

перебор элементов

адрес указывается в

одном из 16-битовых

регистров ВХ или ВР.

какого-то набора

виде

регистров МП, а в

данных. Е сли элемент

шестнадцатеричного

команде указывается

данных имеет длину 1

числа, однозначно

имя этого регистра. В

байт, то при переходе

8.

Комбинированные системы адресацииМогут встретиться комбинированные системы адресации, например базовая (или индексная) со смещением,

базово-индексная и т.д. Базово-индексная адресация в команде выглядит в виде такого адреса: \[BP+S I\].

Базовая адресация

Индексная адресация

Появилась впервые, когда стало

Имеет смысл, когда надо

применяться динамическое

осуществить перебор элементов

В команде выглядит в виде такого

размещение программ в ОП, а это

какого-то набора данных.

адреса: \[BP+S I\].

в свою очередь возникло, когда

объем ОП стал настолько

большим, что превысил размеры

выполняемых программ.

Базово-индексная

адресация

9.

Дополнительная информация(Программу можно писать в абсолютных адресах, когда программист сам определяет, в каких ячейках ОП она

должна размещаться для исполнения, и в относительных адресах, когда заранее неизвестно, в какую часть ОП

программа попадет при загрузке. В первом случае программа окончательно готова к использованию, но является

неперемещаемой. Если требуемая область ОП занята хотя бы частично, такую программу выполнить уже нельзя.

Во втором случае программа перед выполнением должна быть «привязана» к своему месту в ОП, поскольку все

программы пишутся так, как будто при загрузке они обязательно попадут в область ОП, начиная с ячейки 0. Перед

загрузкой операционная система ищет свободное место в ОП, в которой можно разместить программу, и адрес

первой ячейки этой свободной области запоминается как общая добавка ко всем адресам, употребляемым в

программе. Этот адрес называется «базовым». Абсолютные адреса определяются по сложению с базовым

адресом. Такая система реализована в мультипрограммных вычислительных машинах с динамическим

распределением ресурсов.)

10.

Циклы работымикропроцессора

Структура

команд

первых

процессоров

была

более

громоздкой. В команде указывались адреса обоих операндов,

адрес, куда записывался результат и адрес следующей

команды.

Для

извлечения

такой команды

несколько раз

обращаться

к памяти,

приходилось

что естественно

приводило к значительному снижению быстродействия.

11.

Упрощение команд1

Программный счетчик

За счет введения программного счетчика избавились от части, в

которой указывался адрес следующей команды.

2

Результат на место операнда

Так как один из операндов, как правило, после выполнения

некоторого действия не нужен, то стали записывать результат на

его место, что позволило исключить еще одно поле.

3

Аккумулятор в АЛУ

С введением аккумулятора в АЛУ приняли, что один из операндов

находится в нем, и отпала необходимость указывать адрес этого

операнда.

12.

Фазы выполнениякоманды

1

Извлечение кода операции

Первая фаза - извлечение кода операции из памяти.

2

Первичная дешифрация

Вторая фаза - первичная дешифрация кода команды для

определения длины ее адресной части и извлечение из

памяти адресной части команды.

3

Вторичная дешифрация

Третья фаза - вторичная дешифрация для определения

операции и выполнение команды.

13.

Командный циклВыполнение каждого из названных циклов требует

нескольких периодов тактового генератора (машинных

тактов). Совокупное время, требуемое для выборки,

декодирования и выполнения команды, образует командный

цикл, или цикл выполнения команды.

Циклы работы микропроцессора

14.

Алгоритм работымикропроцессора

Под алгоритмом понимается конечный набор действий для

выполнения некоторой процедуры, удовлетворяющий трем

основным требованиям: массовости, детерминированности и

результативности.

15.

Фазы работы устройства управления1

Выборки

Устройство управления в процессе функционирования проходит через три фазы: выборка,

декодирование и выполнение. После того как программа и данные поступили в память, адрес

первой выполняемой команды помещается в программный счетчик, и в устройстве управления

устанавливается фаза выборки.

2

Декодирование

Содержимое программного счетчика поступает на адресную шину, и тем самым обеспечивается

возможность выборки соответствующей команды из памяти. Команда, хранящаяся в ячейке с

адресом, заданным на программном счетчике, посылается по шинам данных в регистр команды в

устройстве управления.

3

Выполнение

16.

Пересылка информацииЕсли в команде задан адрес операнда, устройство

управления переходит к пересылке адресуемой информации

между указанной ячейкой и соответствующим блоком

машины, например арифметическим устройством или

устройством вывода. Для осуществления пересылки

адресная часть команды передается на адресную шину,

подготавливая последующее появление адресуемой

информации на шине данных.

17.

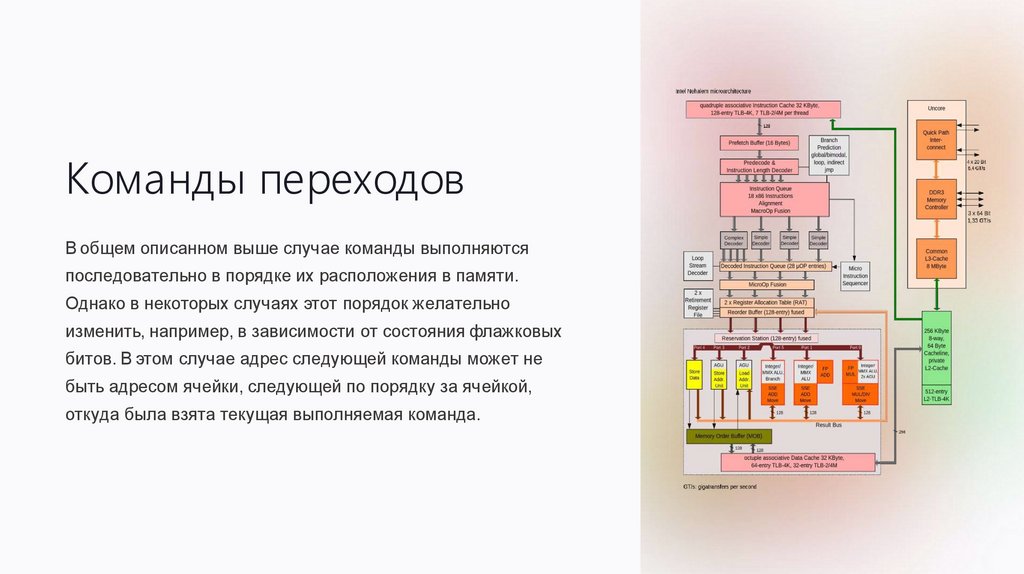

Команды переходовВ общем описанном выше случае команды выполняются

последовательно в порядке их расположения в памяти.

Однако в некоторых случаях этот порядок желательно

изменить, например, в зависимости от состояния флажковых

битов. В этом случае адрес следующей команды может не

быть адресом ячейки, следующей по порядку за ячейкой,

откуда была взята текущая выполняемая команда.

18.

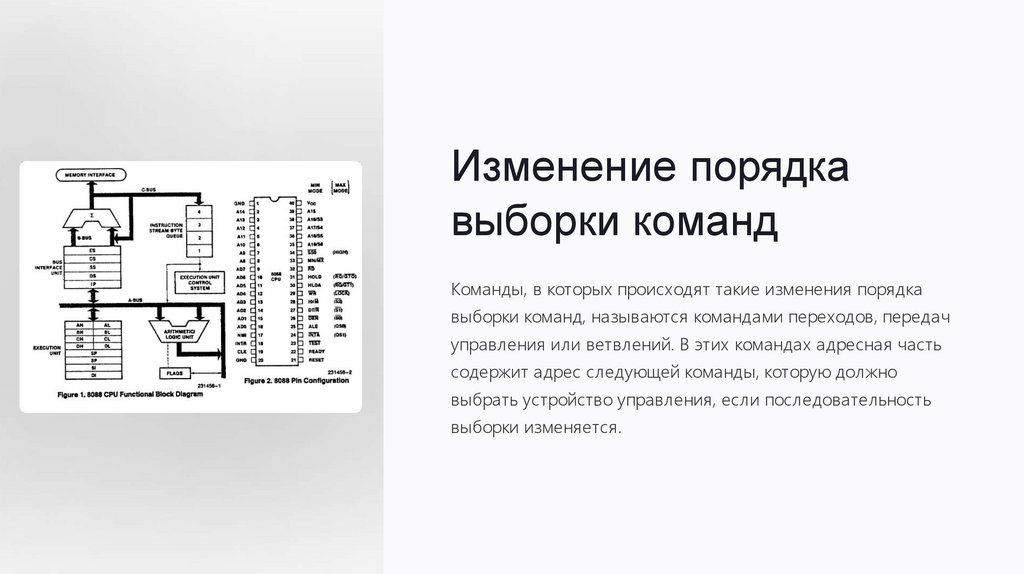

Изменение порядкавыборки команд

Команды, в которых происходят такие изменения порядка

выборки команд, называются командами переходов, передач

управления или ветвлений. В этих командах адресная часть

содержит адрес следующей команды, которую должно

выбрать устройство управления, если последовательность

выборки изменяется.

19.

Взаимодействие элементовпри работе

микропроцессора

Работой микропроцессора управляет программа, записанная в оперативной памяти ЭВМ.

Адрес очередной команды хранится в счетчике команд IP (Instruction Pointer) и в одном из

сегментных регистров (чаще всего в CS). Каждый из них в реальном режиме имеет длину 1 6

бит, тогда как физический адрес ОП должен иметь длину 20 бит. Несогласованность длины

машинного слова (1 6 бит) и длины физического адреса ОП (20 бит) приводит к тому, что в

командах невозможно указать ф изический адрес ОП — его приходится ф ормировать,

собирать из разных регистров МП в процессе работы.

20.

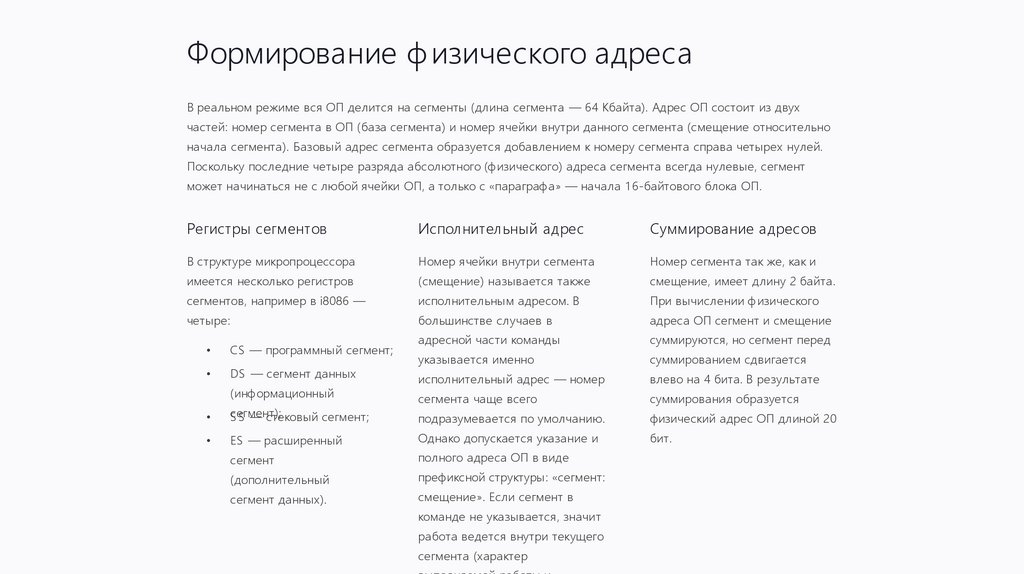

Формирование ф изического адресаВ реальном режиме вся ОП делится на сегменты (длина сегмента — 64 Кбайта). Адрес ОП состоит из двух

частей: номер сегмента в ОП (база сегмента) и номер ячейки внутри данного сегмента (смещение относительно

начала сегмента). Базовый адрес сегмента образуется добавлением к номеру сегмента справа четырех нулей.

Поскольку последние четыре разряда абсолютного (физического) адреса сегмента всегда нулевые, сегмент

может начинаться не с любой ячейки ОП, а только с «параграфа» — начала 1 6-байтового блока ОП.

Регистры сегментов

Исполнительный адрес

Суммирование адресов

В структуре микропроцессора

Номер ячейки внутри сегмента

Номер сегмента так же, как и

имеется несколько регистров

(смещение) называется также

смещение, имеет длину 2 байта.

сегментов, например в i8086 —

исполнительным адресом. В

При вычислении ф изического

четыре:

большинстве случаев в

адреса ОП сегмент и смещение

адресной части команды

суммируются, но сегмент перед

указывается именно

суммированием сдвигается

исполнительный адрес — номер

влево на 4 бита. В результате

сегмента чаще всего

суммирования образуется

подразумевается по умолчанию.

физический адрес ОП длиной 20

бит.

CS — программный сегмент;

DS — сегмент данных

(информационный

сегмент);

S S — стековый сегмент;

ES — расширенный

Однако допускается указание и

сегмент

полного адреса ОП в виде

(дополнительный

префиксной структуры: «сегмент:

сегмент данных).

смещение». Если сегмент в

команде не указывается, значит

работа ведется внутри текущего

сегмента (характер

21.

Формирование ф изического адреса взащищенном режиме

В защищенном режиме базовые адреса сегментов хранятся в дескрипторных таблицах и имеют длину 24 или 32

бита (в зависимости от типа МП). В сегментных же регистрах хранится селектор, содержащий номер

дескрипторной таблицы и дескрипторное смещение, т.е. порядковый номер дескриптора (в котором и хранится

базовый адрес сегмента) в данной дескрипторной таблице.

Селектор

Дескриптор

Физический адрес

Селектор содержит

Дескриптор содержит

Физический адрес

информацию о том, в какой

информацию о сегменте,

формируется путем сложения

дескрипторной таблице

включая его базовый адрес,

базового адреса сегмента,

находится дескриптор

размер и другие атрибуты.

полученного из дескриптора,

сегмента и какой именно

и смещения, указанного в

дескриптор нужно

команде.

использовать.

22.

Формирование физическогоадреса ОП в защищенном

режиме

23.

Передача адреса в памятьФизический адрес очередной команды через внутреннюю магистраль МП и интерфейс памяти

поступает на шину адреса системной магистрали. Одновременно из устройства управления

(УУ) исполнительного блока на шину управления выдается команда (управляющий сигнал) в

ОП, предписывающая выбрать число, находящееся по адресу, указанному в системной

магистрали.

Адрес команды

Физический адрес команды передается на шину адреса.

Управляющий сигнал

Устройство управления выдает команду в ОП, чтобы выбрать число по

указанному адресу.

Чтение данных

Выбранное число, являющееся очередной командой, поступает из ОП через

шину данных системной магистрали, интерфейс памяти, внутреннюю магистраль

МП на регистр команд (INS T).

24.

Обработка командыИз команды в регистре команд выделяется код операции, который поступает в УУ

исполнительного блока для выработки управляющих сигналов, настраивающих

микропроцессор на выполнение требуемой операции.

1

Код операции

Определяет тип операции, которую нужно выполнить (например, сложение,

вычитание, перемещение данных).

2

Управляющие сигналы

Настраивают микропроцессор на выполнение операции, определяемой

кодом операции.

3

Выбор данных

В зависимости от используемого в команде режима адресации

организуется выборка необходимых исходных данных.

25.

Работа микропроцессора привыполнении программного

прерывания

Программы-обработчики прерываний могут находиться в различных частях основной памяти

(место их расположения в разных версиях операционной системы может быть различным).

Для обеспечения совместимости программ под разными версиями операционной системы

обращение к обработчикам прерываний осуществляется по их номерам.

1

Таблица векторов прерываний

Связь между номером прерывания и адресом основной памяти,

соответствующим точке входа в обработчик прерывания, осуществляется

через таблицу векторов прерываний, занимающую 1 Кбайт сегмента 0

основной памяти (при работе в DOS ). При работе в защищенном режиме связь

между номером прерывания и адресом обработчика прерывания

осуществляется через дескрипторную таблицу прерываний (IDT — Interrupt

Descriptor Table), местонахождение которой определяется системным

регистром микропроцессора IDTR.

2

Структура вектора прерываний

Поскольку адрес любого байта основной памяти определяется базовым

адресом сегмента (2 байта) и смещением в сегменте (2 байта), вектор

прерываний разделен на «четверки» байтов, имеющие структуру, показанную

26.

Функции таблицы векторовпрерываний

Таблица векторов прерываний используется не только для хранения адресов обработчиков

прерываний, но и для указания на места хранения в ОП служебной информации. Для этой

цели служат векторы прерываний IDh, lEh, IFh, 41h, 43h, 46h, 4Ah. Так, вектор IDh содержит

адрес таблицы параметров видеосистемы (а не обработчика прерывания); вектор lEh таблицы параметров дискет; вектор IFh- адрес знакогенератора адаптера CGA и т.д.

Прерывание клавиатуры

Обработчик прерывания клавиатуры (INT 09h) обрабатывает нажатия клавиш на клавиатуре.

Прерывание мыши

Обработчик прерывания мыши (INT 03h) обрабатывает движения и клики мыши.

Прерывание жесткого диска

Обработчик прерывания жесткого диска (INT 13h) управляет доступом к жесткому диску.

27.

Команда INTКоманда INT, кроме определения адреса обработчика прерываний, выполняет следующие

действия: сохраняет в стеке часть слова состояния процессора: (SP) <—— (SP) - 2 (вершина

стека) <— (регистр флагов) (SP) <——(SP) - 2 (вершина стека) <-— (CS) (SP) <—(SP) - 2

(вершина стека) <— (IP); сбрасывает флаги разрешения прерывания и трассировки: (IF) < — О

(TF) <— О; заносит адрес точки входа обработчика прерываний в регистры CS и IP: (CS) < —

(номер прерывания \* 4 + 2) (IP) <— (номер прерывания \* 4).

Действие

Описание

Сохранение состояния процессора

Сохраняет в стеке значения регистров

CS, IP и флагов, чтобы вернуться к

прерванной программе.

Сброс флагов

Сбрасывает флаги разрешения

прерывания (IF) и трассировки (TF),

чтобы предотвратить прерывания во

время обработки прерывания.

Загрузка адреса обработчика

Загружает адрес обработчика

прерывания в регистры CS и IP, чтобы

начать выполнение обработчика.

28.

Команда IR E TКоманда INT относится к парным командам - каждый обработчик

прерывания заканчивается командой IRET (возврат из

прерывания). По команде IRET (без параметров) выполняются

следующие действия: (IP) <— (вершина стека) (SP) <— (SP) + 2

(CS) <— (вершина стека) (SP) <— (SP) + 2 (регистр флагов) <—

(вершина стека) (SP) <— (SP) + 2.

1

Восстановление состояния

Восстанавливает значения регистров CS, IP и флагов из

стека, чтобы вернуться к прерванной программе.

2

Продолжение выполнения

Продолжает выполнение прерванной программы с точки

прерывания.

Программирование

Программирование