Похожие презентации:

Разработка программного модуля 2-х канального ввода-вывода по SPI для флеш-памяти

1.

МИНОБРНАУКИ РОССИИФедеральное государственное бюджетное образовательное учреждение

высшего образования

«МИРЭА – Российский технологический университет»

РТУ МИРЭА

Институт кибербезопасности и цифровых технологий

Разработка программных решений и системного программирования

ВКР бакалавра на тему:

«Разработка программного модуля 2-х канального ввода-вывода по

последовательному периферийному интерфейсу для микросхемы флеш памяти»

БСБО-18-21: Колобанов Д.А.

Научный руководитель: к.т.н., доцент кафедры ИКБ Аминев Д.А.

Направление: 09.02.03 «Информационные системы и технологии»

1

2. Актуальность и цель иследования

Актуальность:В условиях постоянного роста требований к скорости и

эффективности передачи данных в современных электронных

системах, двухканальный SPI становится важным

инструментом для разработчиков

Цели работы:

- Изучить основные принципы

работы последовательного

периферийного интерфейса

(SPI) и его архитектуру.

- Разработать схему и

выполнить программную

реализацию управления

двухканальным SPI.

- Провести тестирование

разработанного

двухканального SPIинтерфейса на

работоспособность и

производительность.

Основные задачи:

- Изучить литературные источники

и статьи, описывающие работу

интерфейса SPI и его применения в

современных системах.

- Разработать блок-схемы и

описания основных модулей,

необходимых для реализации

двухканального SPI.

- Написать программное

обеспечение для управления

двумя SPI-каналами, включая

функции и процедуры для обмена

данными.

- Оформить графические

материалы для более наглядного

представления результатов

работы.

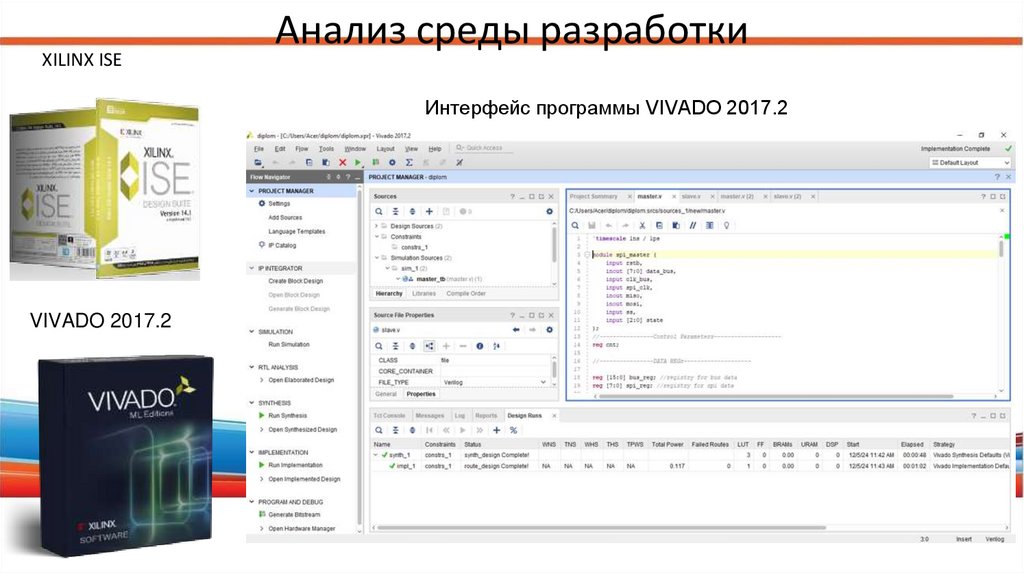

3. Анализ среды разработки

XILINX ISEАнализ среды разработки

Интерфейс программы VIVADO 2017.2

VIVADO 2017.2

4. Исходные временные диаграммы двухканального режима ввода/вывода

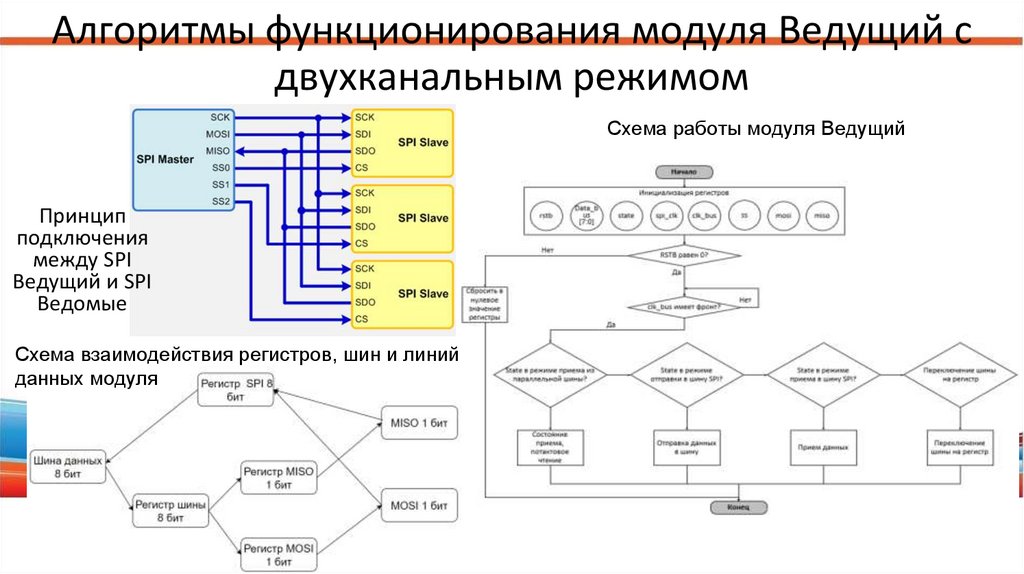

Алгоритмы функционирования модуля Ведущий сдвухканальным режимом

Схема работы модуля Ведущий

Принцип

подключения

между SPI

Ведущий и SPI

Ведомые

Схема взаимодействия регистров, шин и линий

данных модуля

5. Алгоритмы функционирования модуля Ведущий с двухканальным режимом

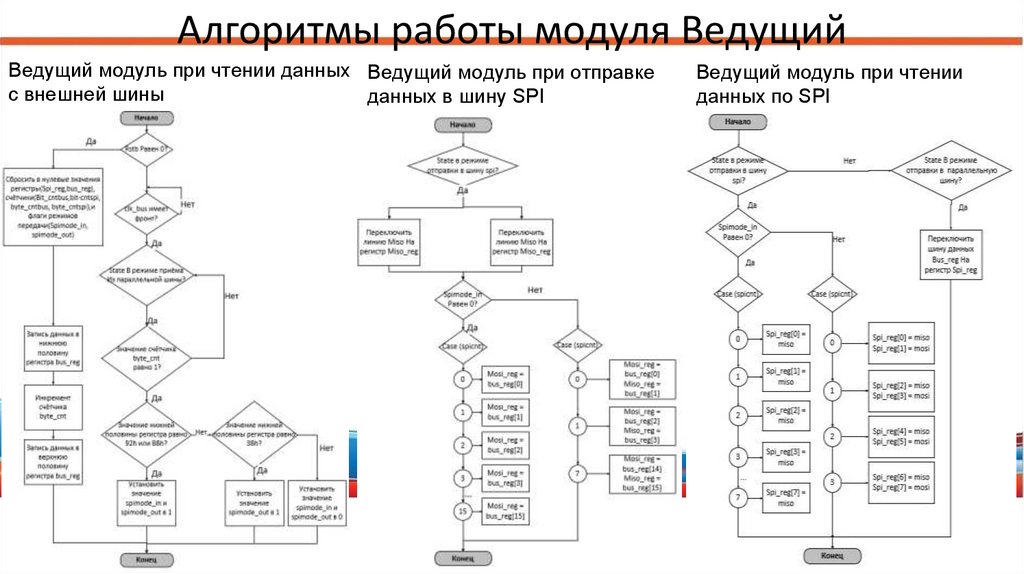

Алгоритмы работы модуля ВедущийВедущий модуль при чтении данных Ведущий модуль при отправке

с внешней шины

данных в шину SPI

Ведущий модуль при чтении

данных по SPI

6. Алгоритмы работы модуля Ведущий

Алгоритмы функционирования модуля Ведомый сдвухканальным режимом

Алгоритм ветки чтения номера команды от Ведущего

Схема работы модуля Ведомый

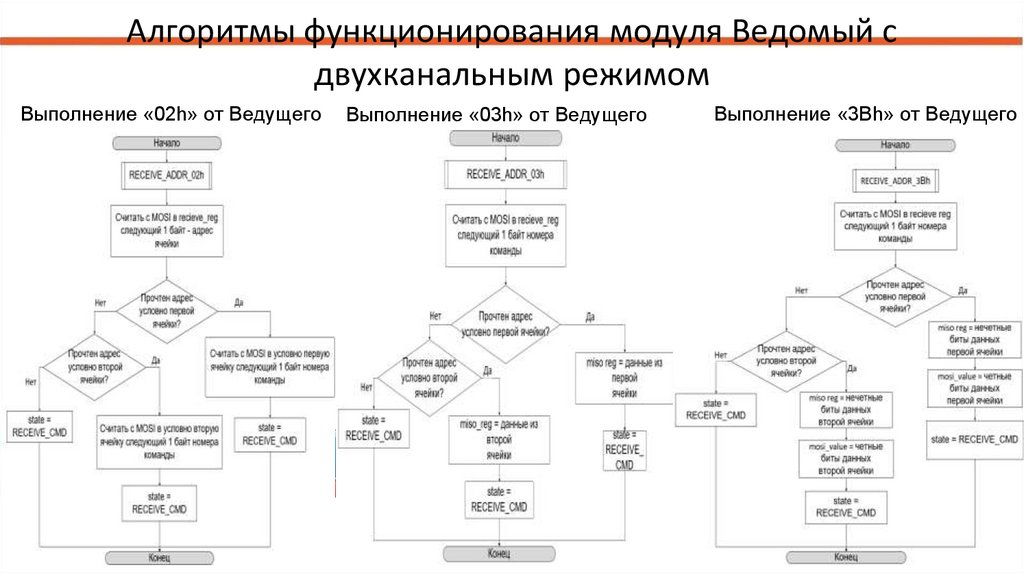

7. Алгоритмы функционирования модуля Ведомый с двухканальным режимом

Выполнение «02h» от ВедущегоВыполнение «03h» от Ведущего

Выполнение «3Bh» от Ведущего

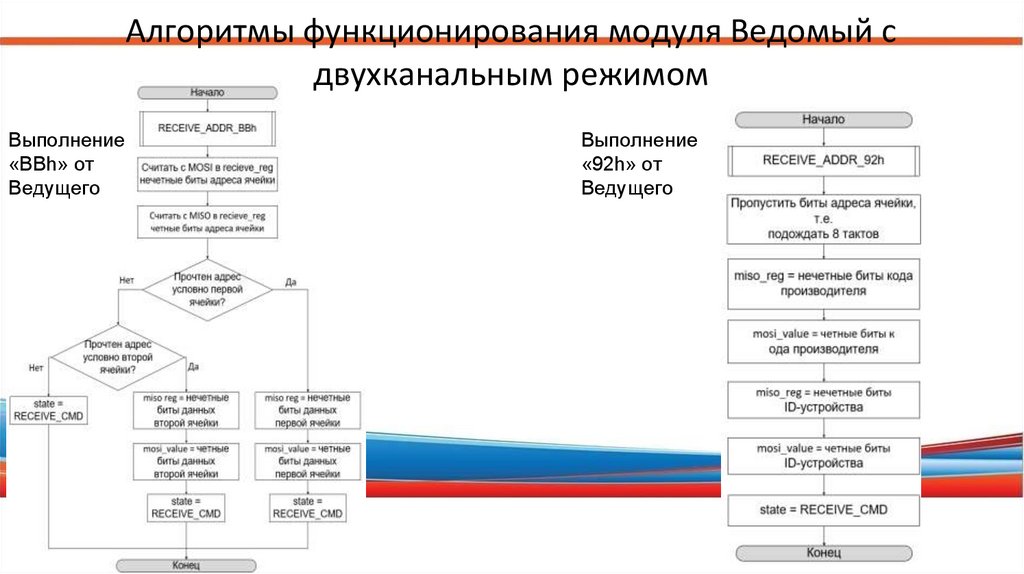

8. Алгоритмы функционирования модуля Ведомый с двухканальным режимом

Выполнение«ВВh» от

Ведущего

Выполнение

«92h» от

Ведущего

9. Алгоритмы функционирования модуля Ведомый с двухканальным режимом

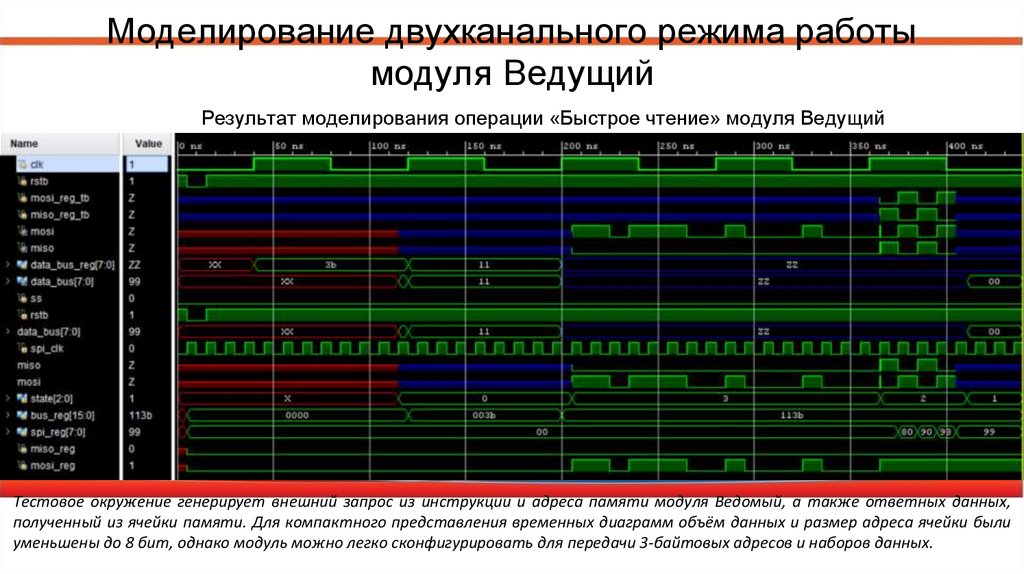

Моделирование двухканального режима работымодуля Ведущий

Результат моделирования операции «Быстрое чтение» модуля Ведущий

Тестовое окружение генерирует внешний запрос из инструкции и адреса памяти модуля Ведомый, а также ответных данных,

полученный из ячейки памяти. Для компактного представления временных диаграмм объём данных и размер адреса ячейки были

уменьшены до 8 бит, однако модуль можно легко сконфигурировать для передачи 3-байтовых адресов и наборов данных.

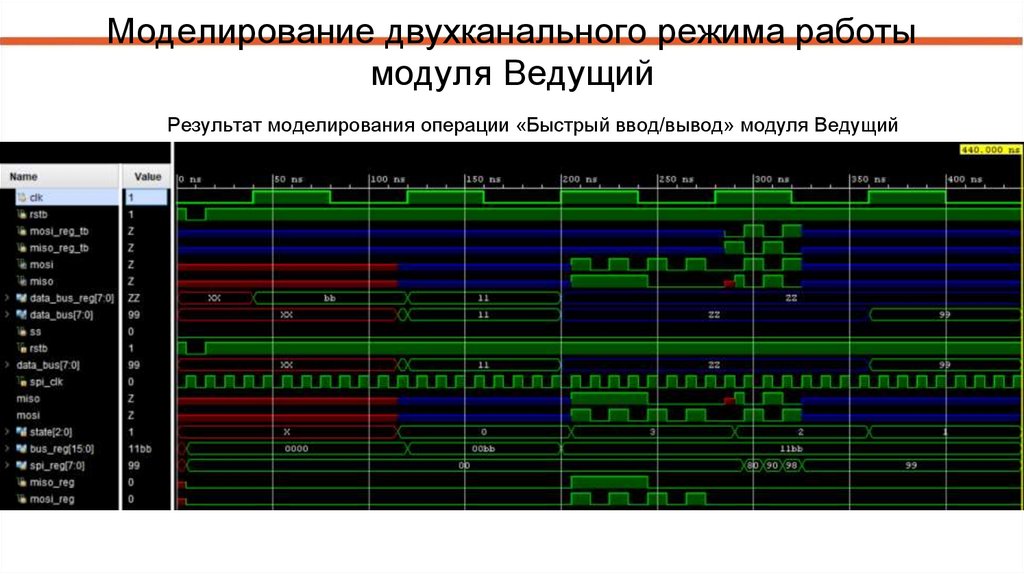

10. Моделирование двухканального режима работы модуля Ведущий

Результат моделирования операции «Быстрый ввод/вывод» модуля Ведущий11. Моделирование двухканального режима работы модуля Ведущий

Результат моделирования операции «Чтение идентификатора производителя» модуля Ведущий12. Моделирование двухканального режима работы модуля Ведущий

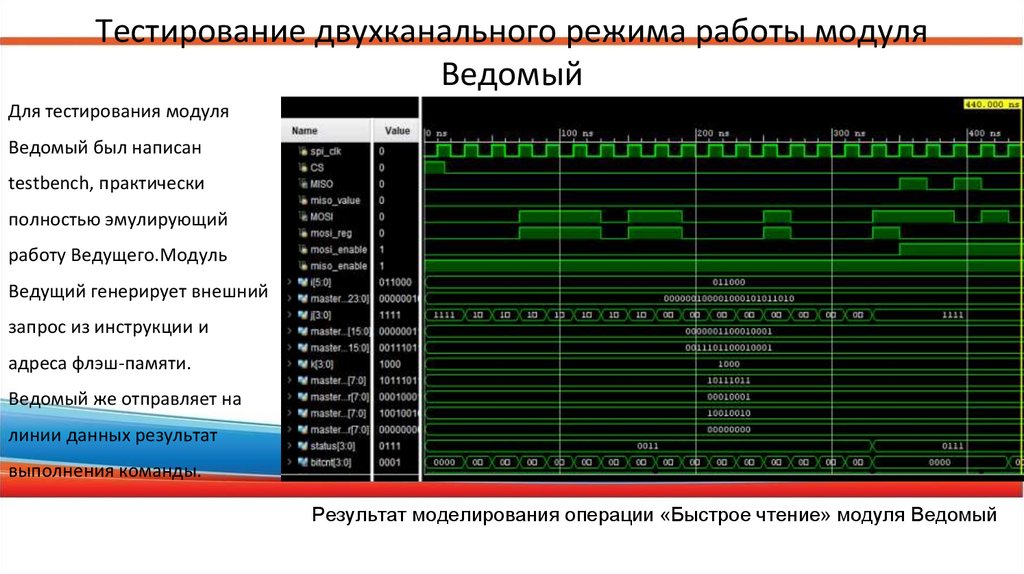

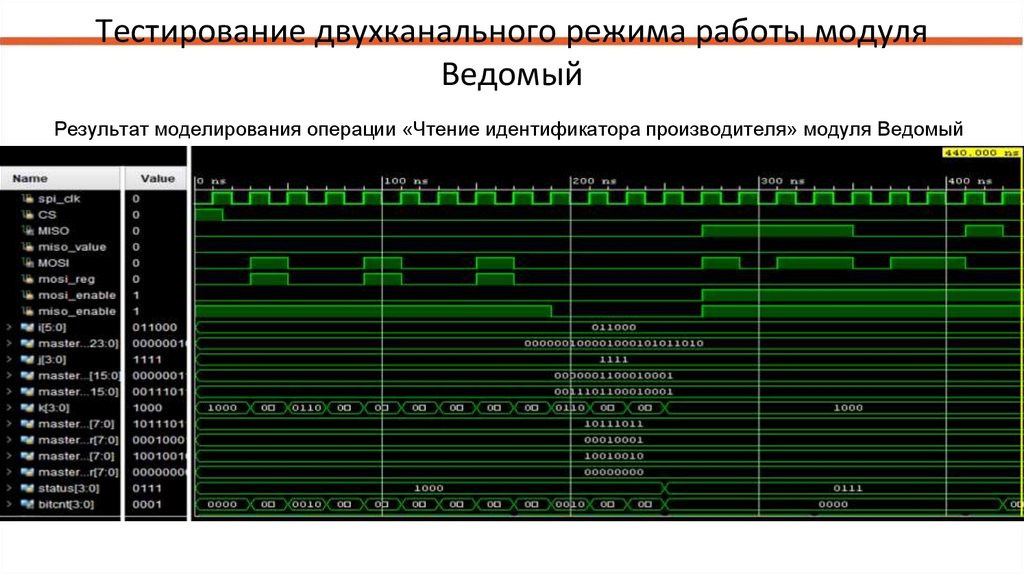

Тестирование двухканального режима работы модуляВедомый

Для тестирования модуля

Ведомый был написан

testbench, практически

полностью эмулирующий

работу Ведущего.Модуль

Ведущий генерирует внешний

запрос из инструкции и

адреса флэш-памяти.

Ведомый же отправляет на

линии данных результат

выполнения команды.

Результат моделирования операции «Быстрое чтение» модуля Ведомый

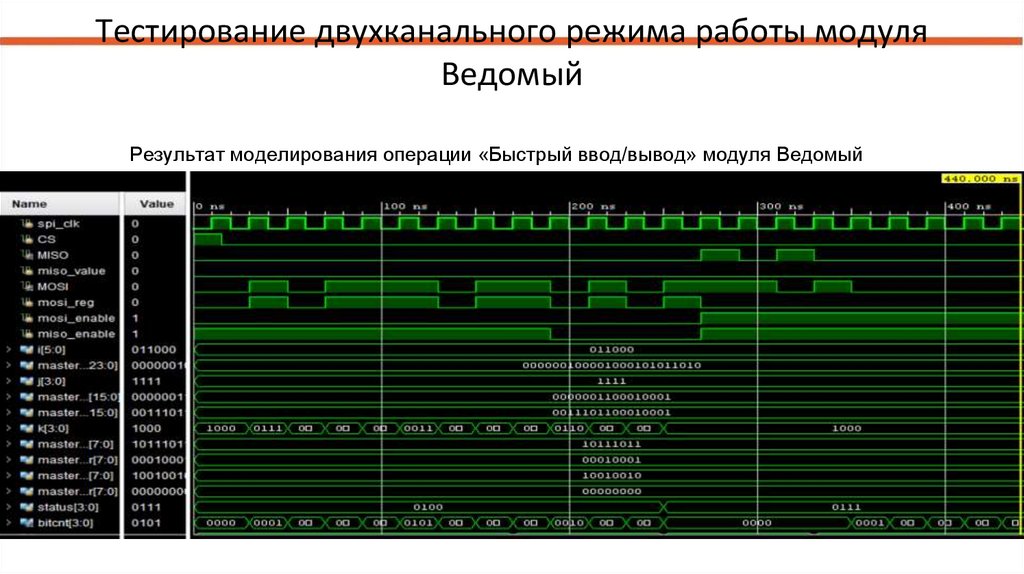

13. Тестирование двухканального режима работы модуля Ведомый

Результат моделирования операции «Быстрый ввод/вывод» модуля Ведомый14. Тестирование двухканального режима работы модуля Ведомый

Результат моделирования операции «Чтение идентификатора производителя» модуля Ведомый15. Тестирование двухканального режима работы модуля Ведомый

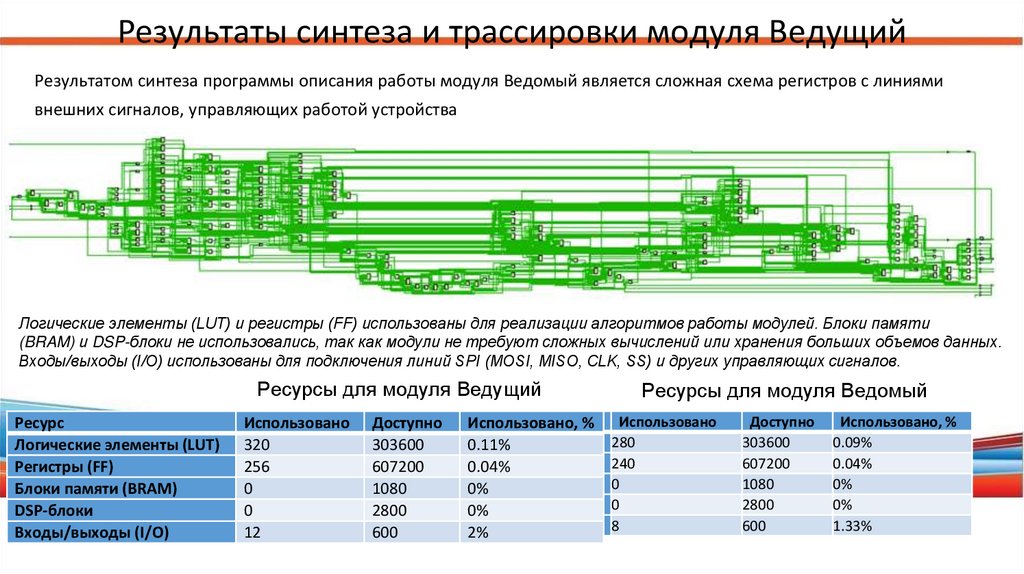

Результаты синтеза и трассировки модуля ВедущийРезультатом синтеза программы описания работы модуля Ведомый является сложная схема регистров с линиями

внешних сигналов, управляющих работой устройства

Логические элементы (LUT) и регистры (FF) использованы для реализации алгоритмов работы модулей. Блоки памяти

(BRAM) и DSP-блоки не использовались, так как модули не требуют сложных вычислений или хранения больших объемов данных.

Входы/выходы (I/O) использованы для подключения линий SPI (MOSI, MISO, CLK, SS) и других управляющих сигналов.

Ресурсы для модуля Ведущий

Ресурс

Логические элементы (LUT)

Регистры (FF)

Блоки памяти (BRAM)

DSP-блоки

Входы/выходы (I/O)

Использовано

320

256

0

0

12

Ресурс Использовано, %

Доступно

Логические

элементы (LUT)

303600

0.11%

Регистры 0.04%

(FF)

607200

Блоки

памяти

1080

0% (BRAM)

2800DSP-блоки0%

600 Входы/выходы

2% (I/O)

Ресурсы для модуля Ведомый

Использовано

280

240

0

0

8

Доступно

303600

607200

1080

2800

600

Использовано, %

0.09%

0.04%

0%

0%

1.33%

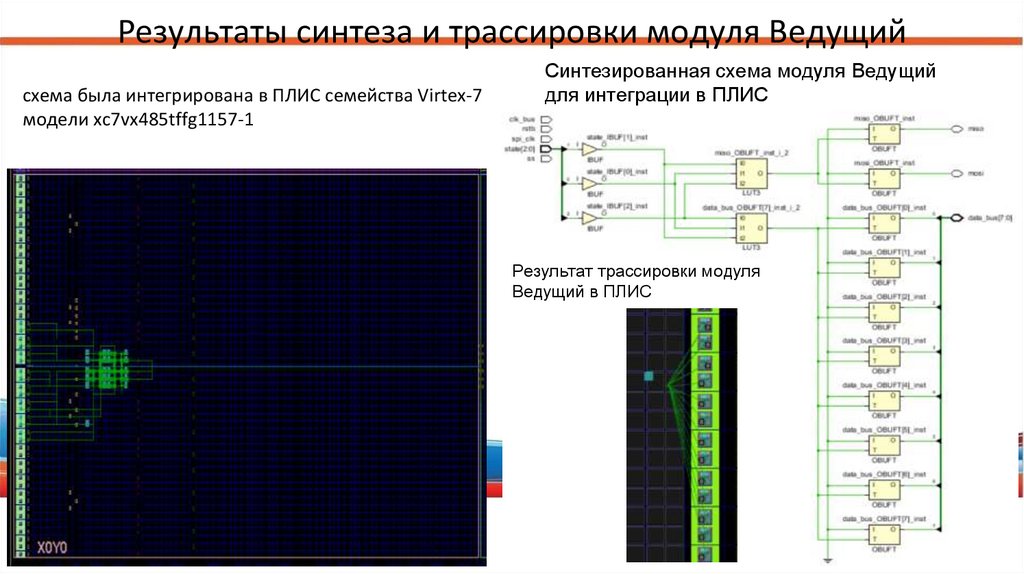

16. Результаты синтеза и трассировки модуля Ведущий

схема была интегрирована в ПЛИС семейства Virtex-7модели xc7vx485tffg1157-1

Синтезированная схема модуля Ведущий

для интеграции в ПЛИС

Результат трассировки модуля

Ведущий в ПЛИС

17. Результаты синтеза и трассировки модуля Ведущий

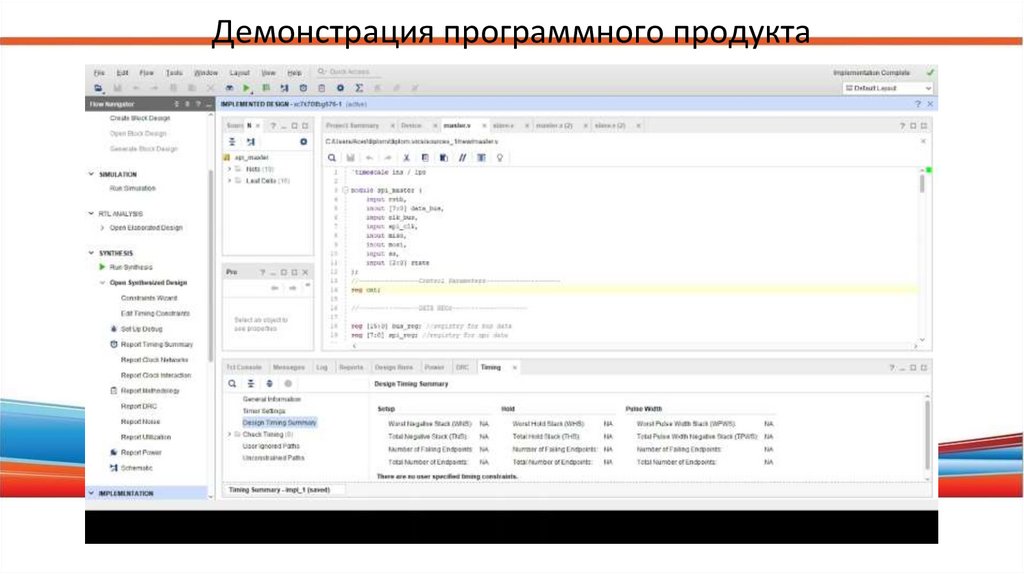

Демонстрация программного продукта18. Демонстрация программного продукта

ЗаключениеПроведен детальный анализ архитектуры микросхемы W25Q64JV и разработаны алгоритмы передачи

данных для интерфейса SPI.

Созданы архитектура и программная реализация модуля передачи данных на языке Verilog, включая

поддержку ключевых функций двухканального SPI.

Моделирование в Xilinx Vivado подтвердило корректность работы модуля.

Проведены синтез и трассировка модуля для ПЛИС, что доказало его готовность к интеграции в

реальные устройства.

Разработанное решение может быть применено в системах с повышенными требованиями к передачи

данных, таких как промышленная автоматизация и для простых потребителей.

Информатика

Информатика