Похожие презентации:

Архитектура процессоров RISC

1. Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение

высшего образования«ПЕРМСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

Кафедра ракетно-космической техники и энергетической системы

Лабораторная работа №2

по дисциплине «Создание презентации согласно

требованиям по оформлению» на тему:

«Архитектура процессоров RISC»

Выполнил: студент гр. ГМЛА-25-1с

К.А. Иванов

Проверил:

Пермь 2025

2. Введение

Цель работы: изучить основные принципы архитектуры RISC.Задачи работы:

изучить теоретические основы архитектуры RISC;

сравнить RISC и CISC.

2/8

3. Теоретические сведения

Сведения:Основные понятия архитектуры RISC: принцип простых и быстрых команд;

Основные компоненты RISC-архитектуры: регистры, ALU, контроллер;

Методика выполнения команд: один такт — одна команда;

Преимущества RISC: высокая скорость выполнения, простота реализации, меньшие

затраты на энергию.

3/8

4. Экспериментальная (практическая) часть

Исследование архитектуры RISC:Простые инструкции фиксированной длины;

Одно тактовое выполнение большинства команд;

Минимальное количество режимов адресации;

Использование большого количества регистров для уменьшения обращения к памяти;

Высокая скорость выполнения и простота реализации.

4/8

5. Экспериментальная (практическая) часть. Продолжение

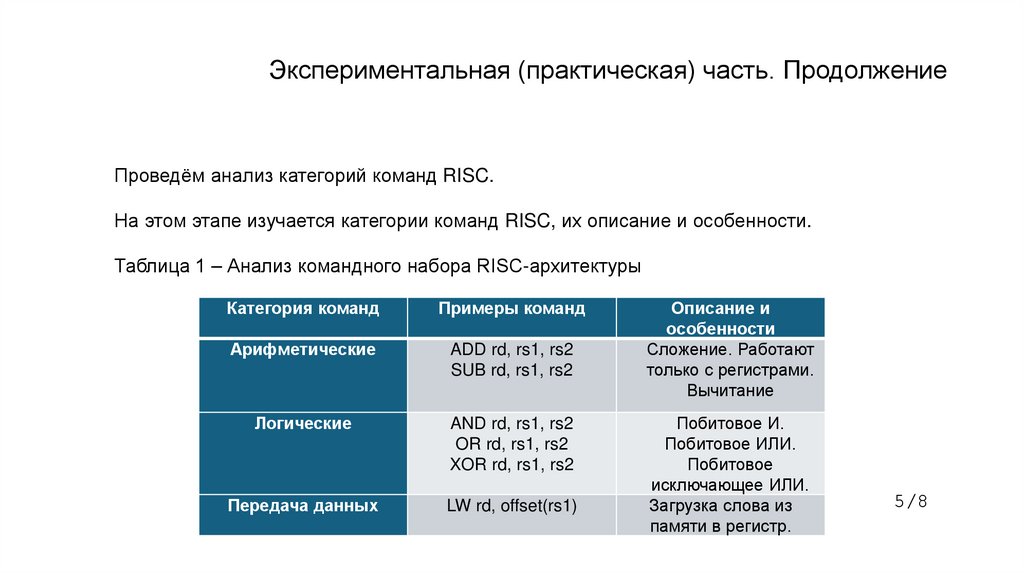

Проведём анализ категорий команд RISC.На этом этапе изучается категории команд RISC, их описание и особенности.

Таблица 1 – Анализ командного набора RISC-архитектуры

Категория команд

Примеры команд

Арифметические

ADD rd, rs1, rs2

SUB rd, rs1, rs2

Логические

AND rd, rs1, rs2

OR rd, rs1, rs2

XOR rd, rs1, rs2

Передача данных

LW rd, offset(rs1)

Описание и

особенности

Сложение. Работают

только с регистрами.

Вычитание

Побитовое И.

Побитовое ИЛИ.

Побитовое

исключающее ИЛИ.

Загрузка слова из

памяти в регистр.

5/8

6. Экспериментальная (практическая) часть. Продолжение

Для выявления преимуществ и недостатков архитектуры RISC, сравним её с антиподом —CISC.

Таблица 1 – Сравнение RISC и CISC

Критерий

Набор инструкций

RISC

Маленький, простой,

фиксированной длины

CISC

Большой, сложный,

переменной длины

Выполнение

инструкций

Регистры

Аппаратное

Часто

через микрокод

Относительно

небольшое

количество

Напрямую через

многие инструкции

Обращение к

памяти

Декодирование

Зависимость от

компилятора

Большое количество

Только через

инструкции LOAD/STOR

E

Простое и быстрое

Очень высокая

Сложное и

медленное

Умеренная

6/8

7. ЗАКЛЮЧЕНИЕ

В ходе лабораторной работы:Изучены теоретические основы архитектуры RISC;

Проведено сравнение RISC и CISC.

7/8

8. Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение

высшего образования«ПЕРМСКИЙ НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

Кафедра ракетно-космической техники и энергетической системы

Спасибо за внимание!

Выполнил: студент гр. ГМЛА-25-1с

Иванов Кирилл Андреевич

e-mail: noobworkerbestdit@gmail.com

Пермь 2025

Программирование

Программирование