Похожие презентации:

Мещанкин_ВК_БСТ2557_Презентация

1. Типы данных в VHDL и SystemVerilog

ТИПЫ ДАННЫХ В VHDL ИSYSTEMVERILOG

Студент Мещанкин Василий Константинович

Группа 2557 Курс 1

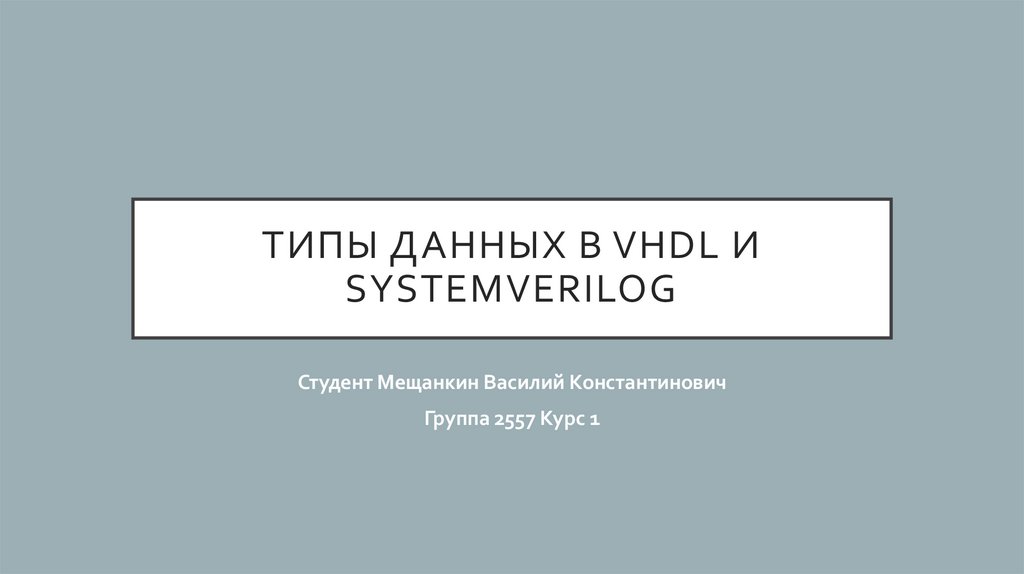

2. История развития HDL

ИСТОРИЯ РАЗВИТИЯ HDLГод

Язык

Инициатор

Стандарт

1987

VHDL

Министерство

обороны США

IEEE 1076

1984/1995

Verilog

Gateway Design

Automation →

Cadence

IEEE 1364

2002–2023

SystemVerilog

Accellera → IEEE

IEEE 1800

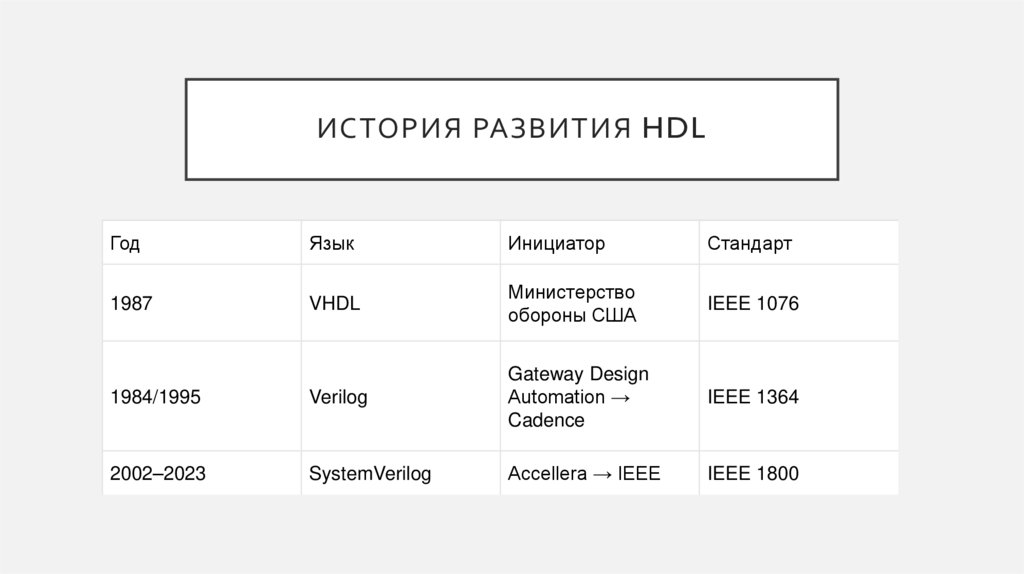

3. Сравнение языков (основные черты)

СРАВНЕНИЕ ЯЗЫКОВ (ОСНОВНЫЕЧЕРТЫ)

Критерий

VHDL

Verilog

SystemVerilog

Типизация

Строгая (требует явного

приведения)

Слабая

Гибкая (logic, typedef)

Синтаксис

Ada-подобный

C-подобный

C++-влияние, ООП

Верификация

Ограниченная

Базовая

Расширенная: assertions,

coverage, классы

Применение

Военные, аэрокосмос,

академия

Промышленность

(1990–2010)

Современные SoC,

UVM

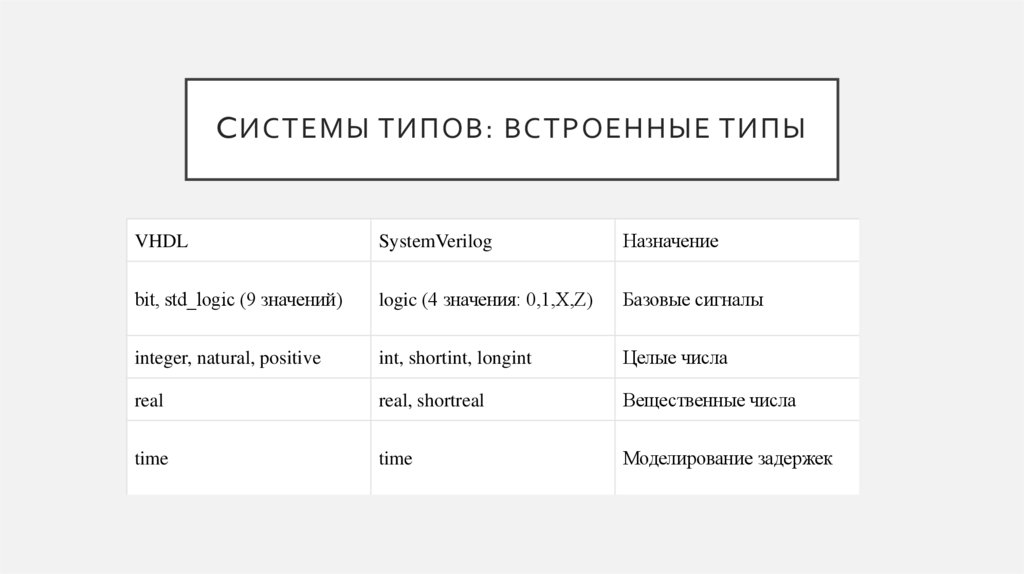

4. cистемы типов: встроенные типы

CИСТЕМЫ ТИПОВ: ВСТРОЕННЫЕ ТИПЫVHDL

SystemVerilog

Назначение

bit, std_logic (9 значений)

logic (4 значения: 0,1,X,Z)

Базовые сигналы

integer, natural, positive

int, shortint, longint

Целые числа

real

real, shortreal

Вещественные числа

time

time

Моделирование задержек

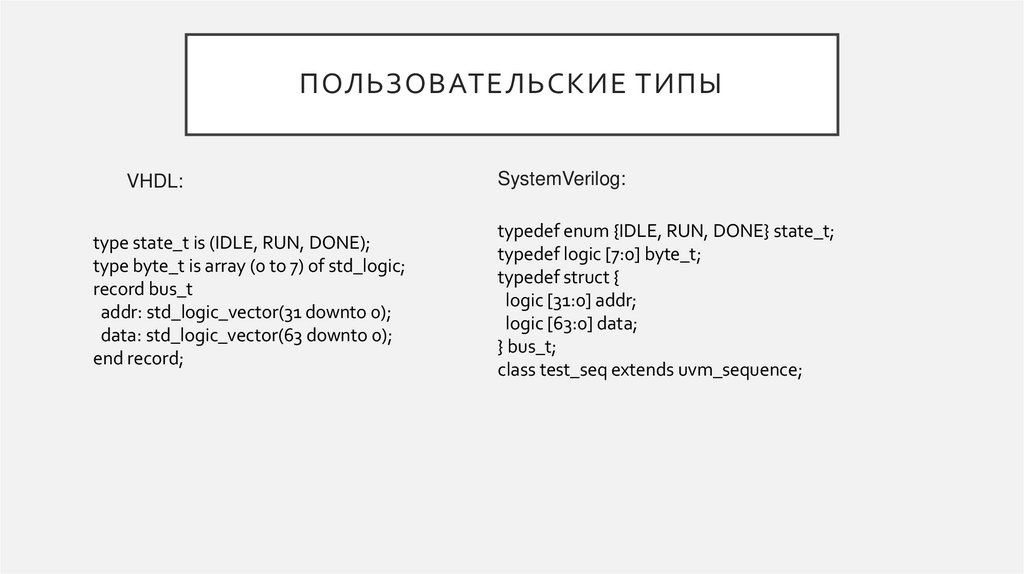

5. Пользовательские типы

ПОЛЬЗОВАТЕЛЬСКИЕ ТИПЫVHDL:

type state_t is (IDLE, RUN, DONE);

type byte_t is array (0 to 7) of std_logic;

record bus_t

addr: std_logic_vector(31 downto 0);

data: std_logic_vector(63 downto 0);

end record;

SystemVerilog:

typedef enum {IDLE, RUN, DONE} state_t;

typedef logic [7:0] byte_t;

typedef struct {

logic [31:0] addr;

logic [63:0] data;

} bus_t;

class test_seq extends uvm_sequence;

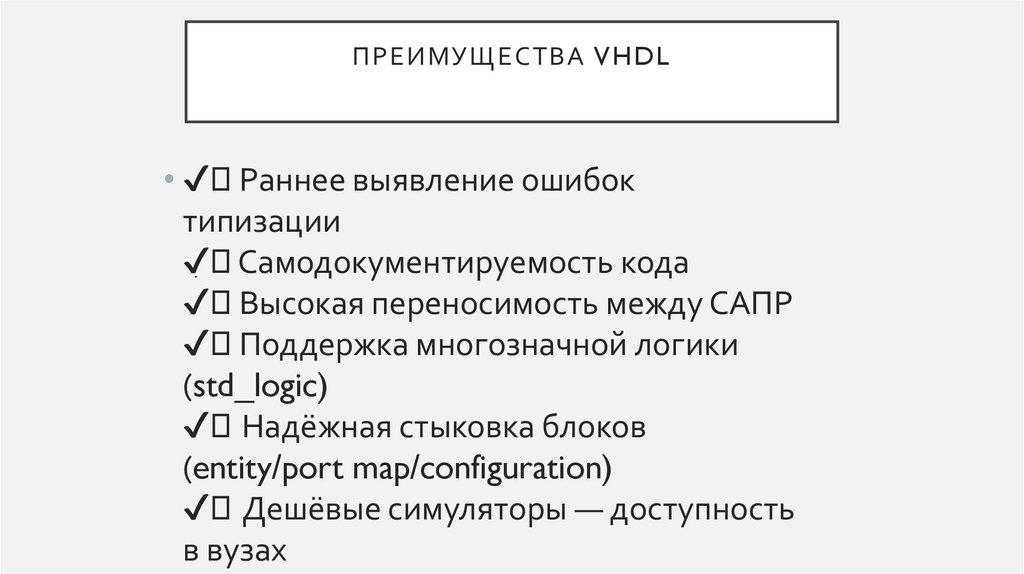

6. Преимущества VHDL

ПРЕИМУЩЕСТВА VHDL• ✔ Раннее выявление ошибок

типизации

✔

Самодокументируемость кода

.

✔ Высокая переносимость между САПР

✔ Поддержка многозначной логики

(std_logic)

✔ Надёжная стыковка блоков

(entity/port map/configuration)

✔ Дешёвые симуляторы — доступность

в вузах

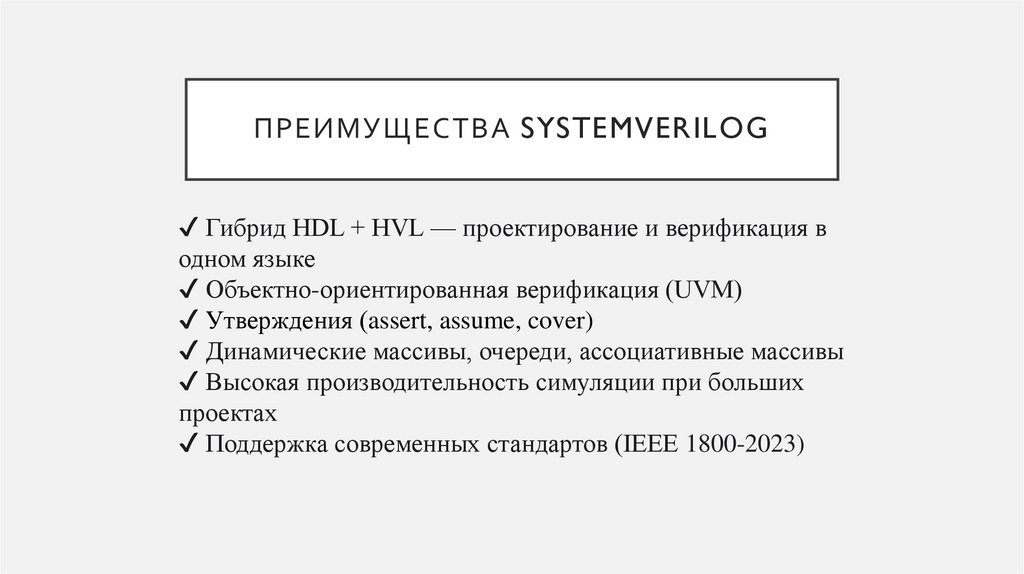

7. Преимущества SystemVerilog

ПРЕИМУЩЕСТВА SYSTEMVERILOG✔ Гибрид HDL + HVL — проектирование и верификация в

одном языке

✔ Объектно-ориентированная верификация (UVM)

✔ Утверждения (assert, assume, cover)

✔ Динамические массивы, очереди, ассоциативные массивы

✔ Высокая производительность симуляции при больших

проектах

✔ Поддержка современных стандартов (IEEE 1800-2023)

Электроника

Электроника