Похожие презентации:

КОУ_ПЗ_1

1.

Практическая работа №1Разработка схемы скремблера

2.

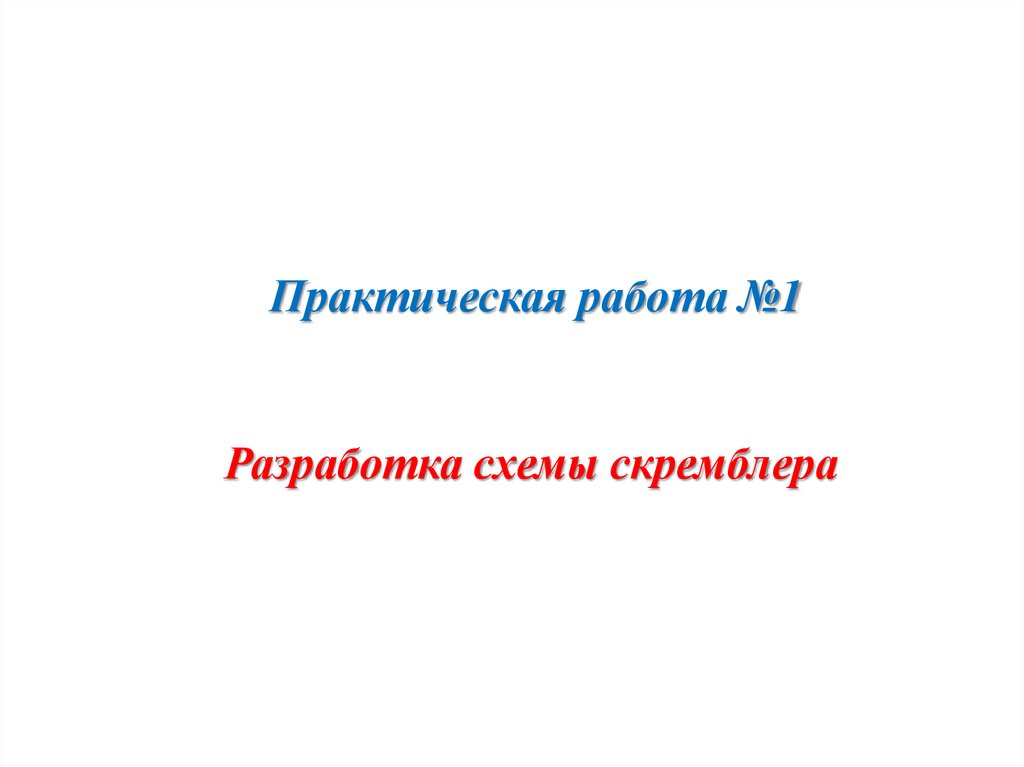

Разработка схемы скремблера и дескремблераПринцип построения скремблирующих и дескремблирующих устройств

Цели скремблирования:

1. Защита передаваемых данных от несанкционированного доступа

2

2. Исключение из потока данных длинных последовательностей 0 и 1 и

периодически повторяющихся групп битов с целью повышения надежности

синхронизации приемника с источником передаваемых по линии данных

Для решения этих задач необходимо преобразовать данные так, чтобы они

выглядели как случайные, то есть лишенные какой-либо видимой

закономерности.

Скремблер

I1

Вход

Сумматор

(mod 2)

Дескремблер

Z1

Линейный

Z2

цифровой сигнал

Y1

Генератор

ПСП

КОУ

Сумматор

(mod 2)

Y2

Синхронизация

Генератор

ПСП

I2

Выход

3.

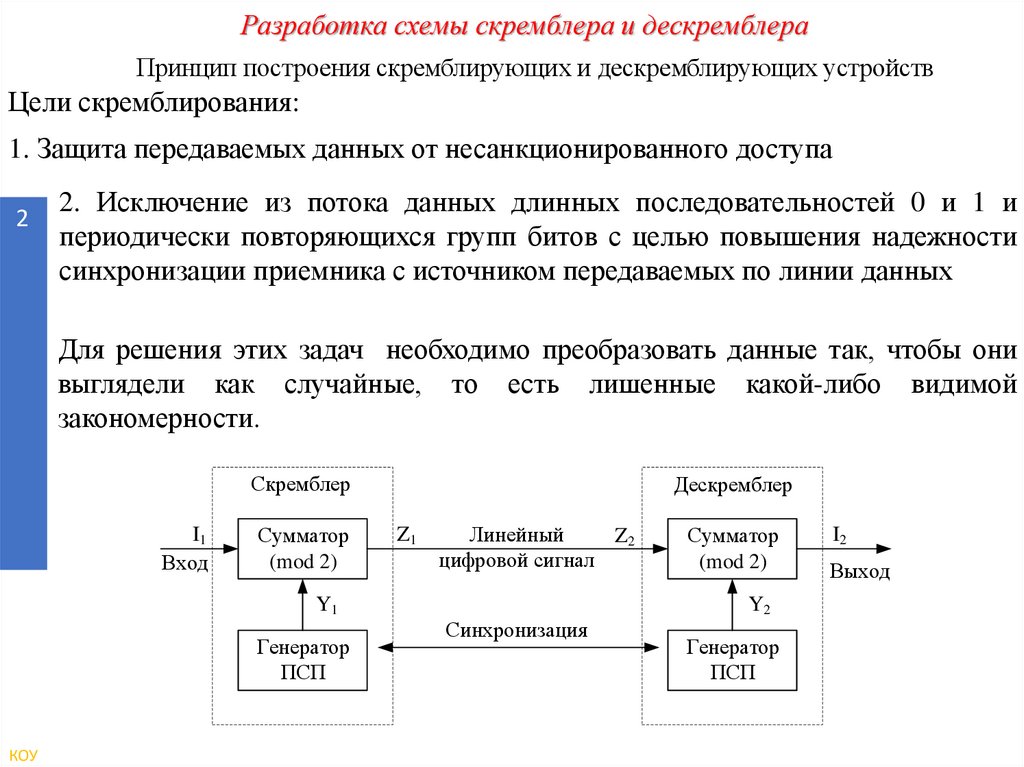

Исходными данными для разработки схемы скремблера является порождающиймногочлен генератора ПСП (псевдослучайной последовательности), например

вида: g(x)=1+x+x9+x10.

Все процессы, протекающие в системе передачи данных, синхронизируются от

тактового генератора (на рисунке не показан).

В каждом такте на вход скремблера подается очередной бит передаваемых

данных, а в сдвиговом регистре накопленный код продвигается на один разряд

вправо.

Регистр сдвига

А

КОУ

Б

В

Сумматор

(mod 2)

Выход

Y

4.

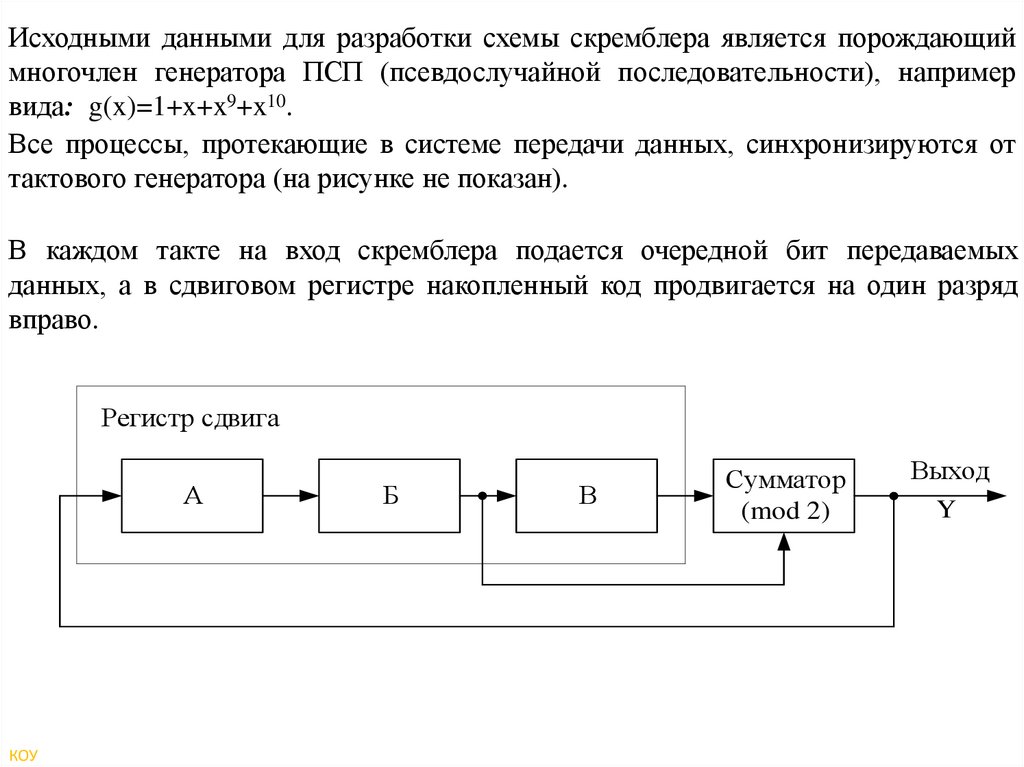

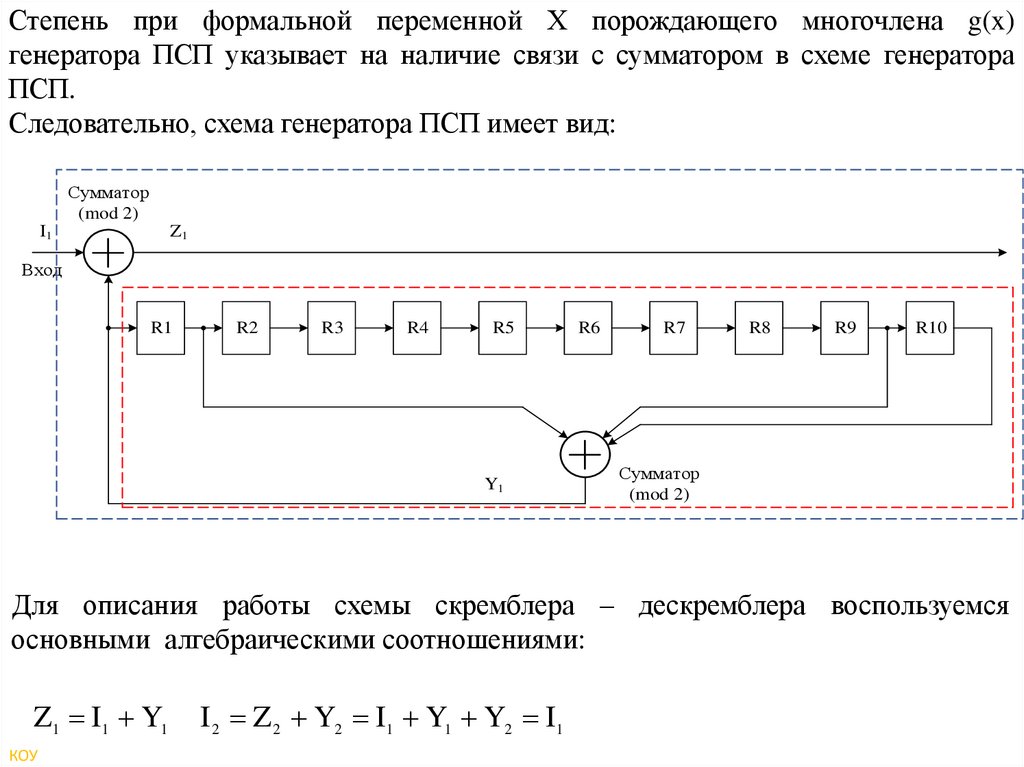

Степень при формальной переменной Х порождающего многочлена g(x)генератора ПСП указывает на наличие связи с сумматором в схеме генератора

ПСП.

Следовательно, схема генератора ПСП имеет вид:

Сумматор

(mod 2)

I1

Z1

Вход

R1

R2

R3

R4

R5

Y1

R6

R7

R8

R9

R10

Сумматор

(mod 2)

Для описания работы схемы скремблера – дескремблера воспользуемся

основными алгебраическими соотношениями:

Z1 I1 Y1

КОУ

I 2 Z 2 Y2 I1 Y1 Y2 I1

5.

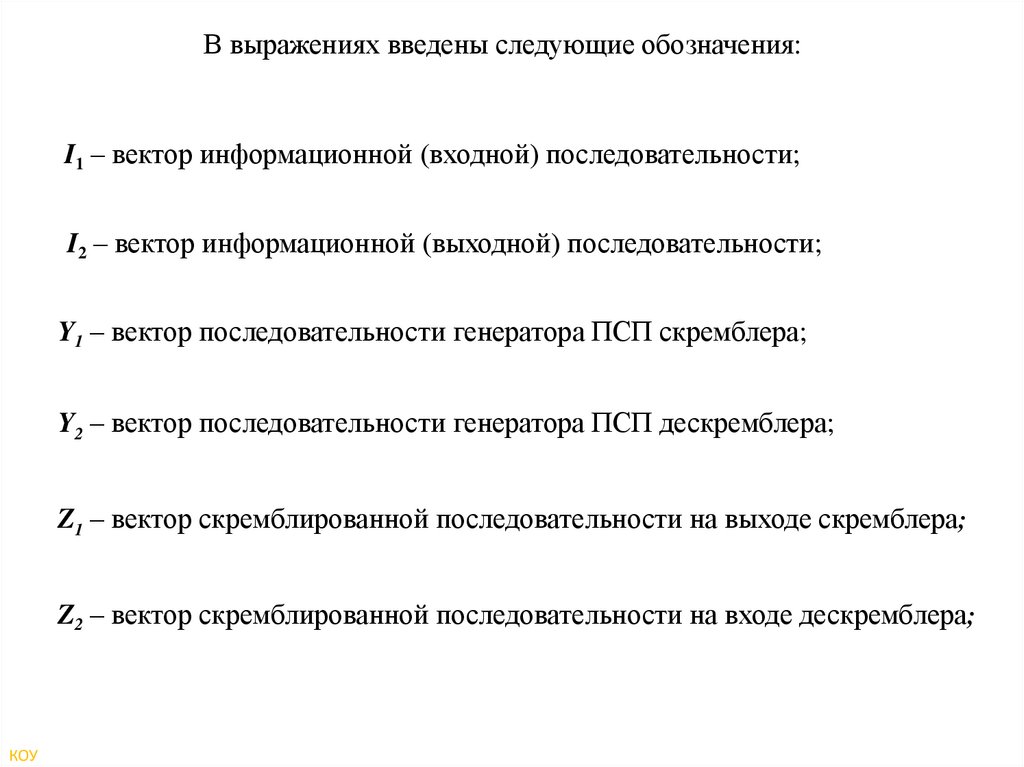

В выражениях введены следующие обозначения:I1 – вектор информационной (входной) последовательности;

I2 – вектор информационной (выходной) последовательности;

Y1 – вектор последовательности генератора ПСП скремблера;

Y2 – вектор последовательности генератора ПСП дескремблера;

Z1 – вектор скремблированной последовательности на выходе скремблера;

Z2 – вектор скремблированной последовательности на входе дескремблера;

КОУ

6.

Работа генератора ПСП представлена в таблице.Исходное состояние (0 такт): R1=. . . =R9 = 0, R10 = 1

Выход сумматора по модулю 2:

1 такт

Сдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1 (строка 1 таблицы)

Выход сумматора по модулю 2:

КОУ

7.

2 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, а «1» из разряда R1 в разряд R2 (строка 2 таблицы)

Выход сумматора по модулю 2:

3 такт

Сдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из R1 в R2, а «1» из R2 в R3 (строка 3 таблицы)

Выход сумматора по модулю 2:

8.

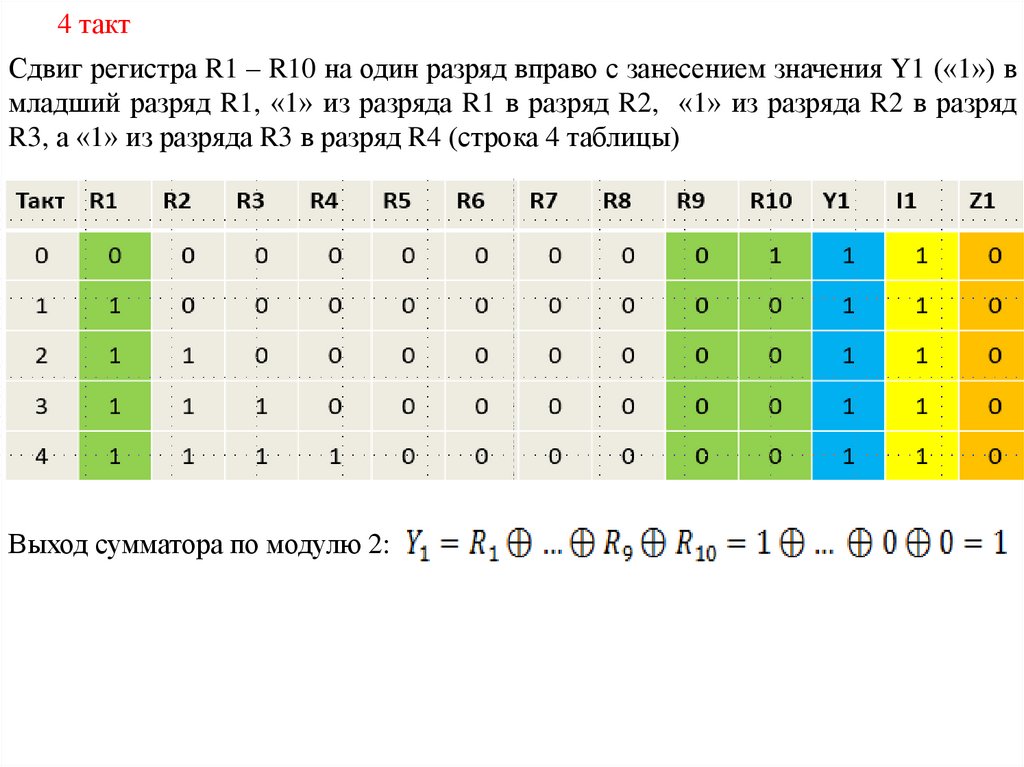

4 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, а «1» из разряда R3 в разряд R4 (строка 4 таблицы)

Выход сумматора по модулю 2:

9.

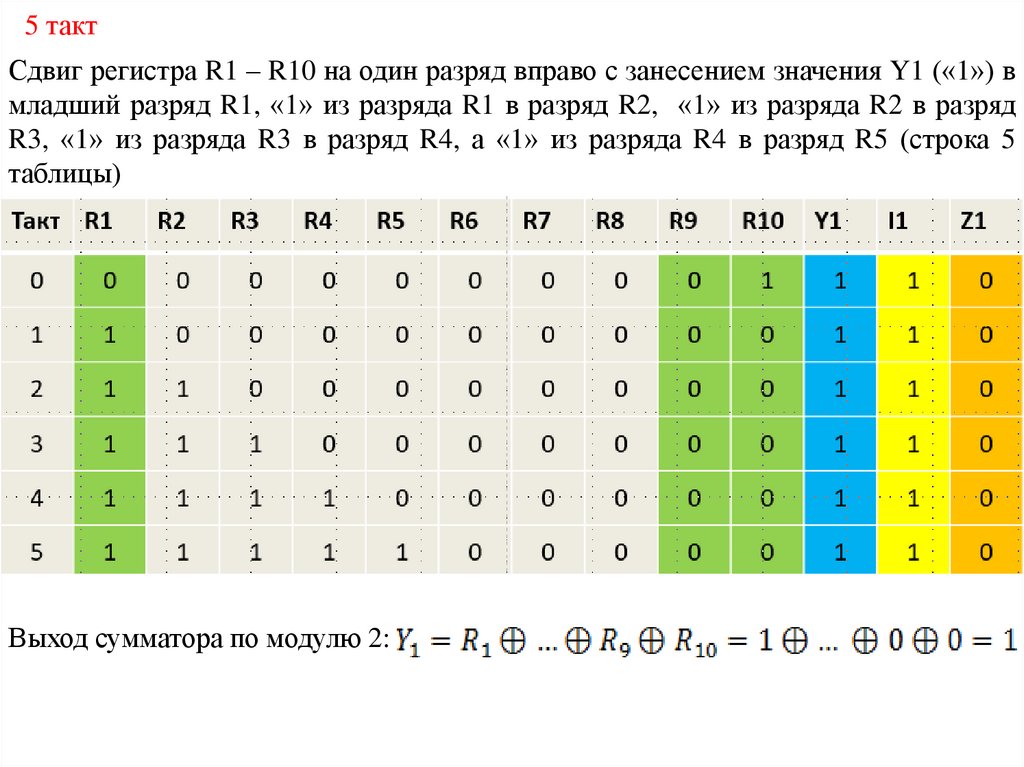

5 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, а «1» из разряда R4 в разряд R5 (строка 5

таблицы)

Выход сумматора по модулю 2:

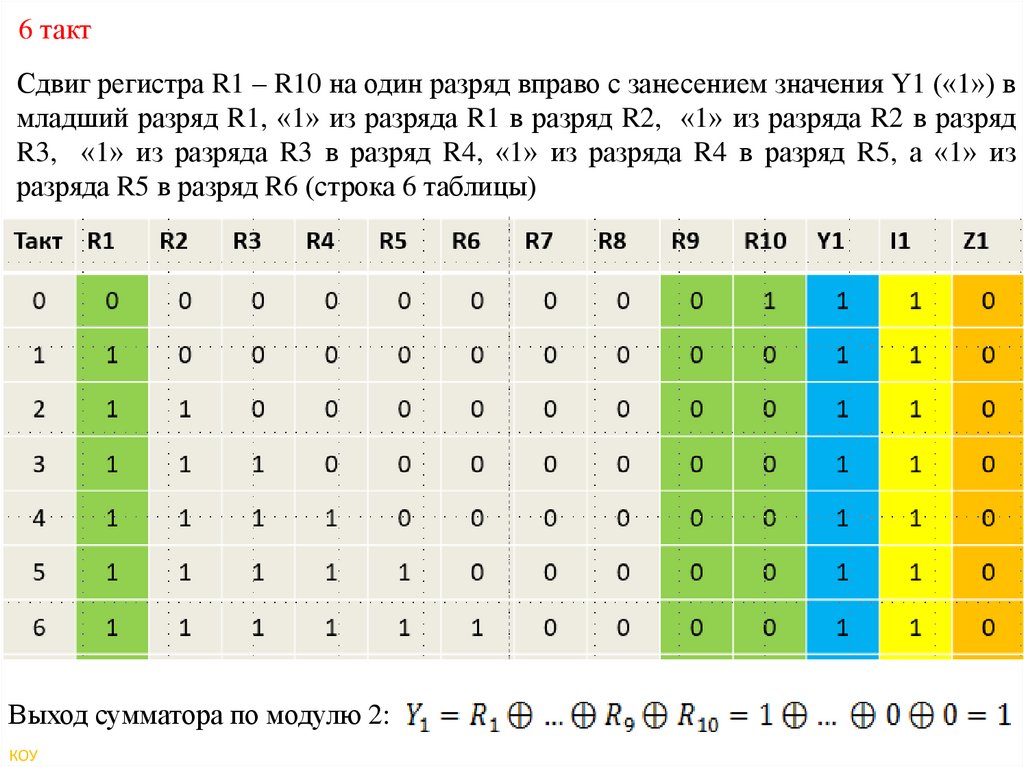

10.

6 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, «1» из разряда R4 в разряд R5, а «1» из

разряда R5 в разряд R6 (строка 6 таблицы)

Выход сумматора по модулю 2:

КОУ

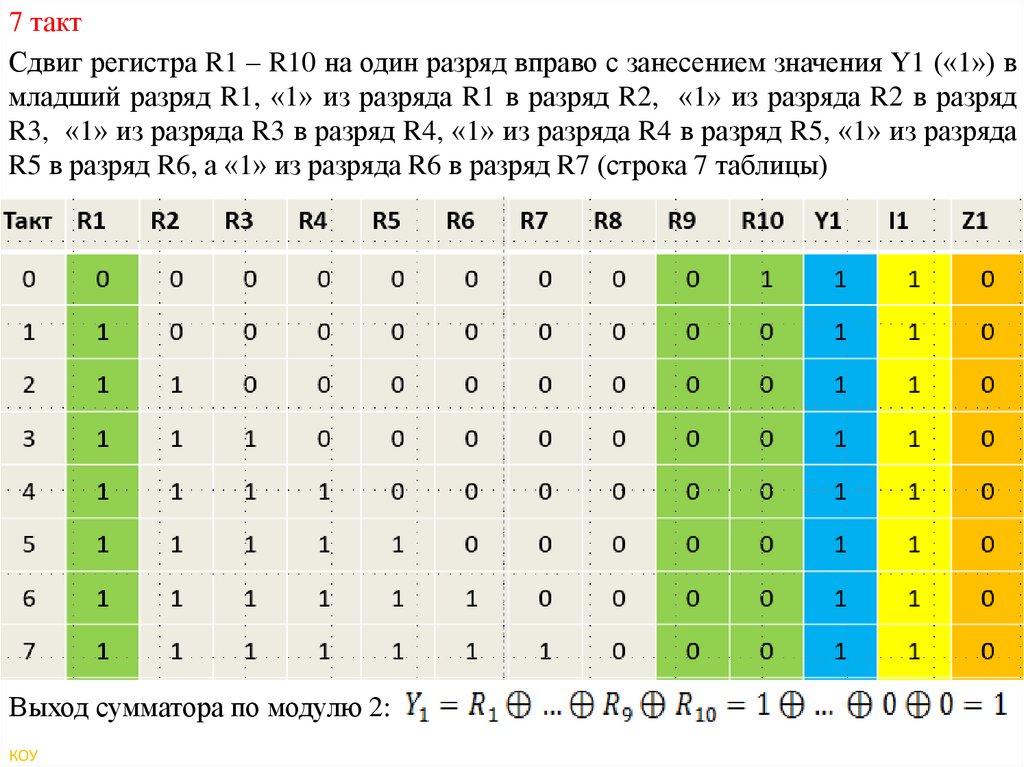

11.

7 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, «1» из разряда R4 в разряд R5, «1» из разряда

R5 в разряд R6, а «1» из разряда R6 в разряд R7 (строка 7 таблицы)

Выход сумматора по модулю 2:

КОУ

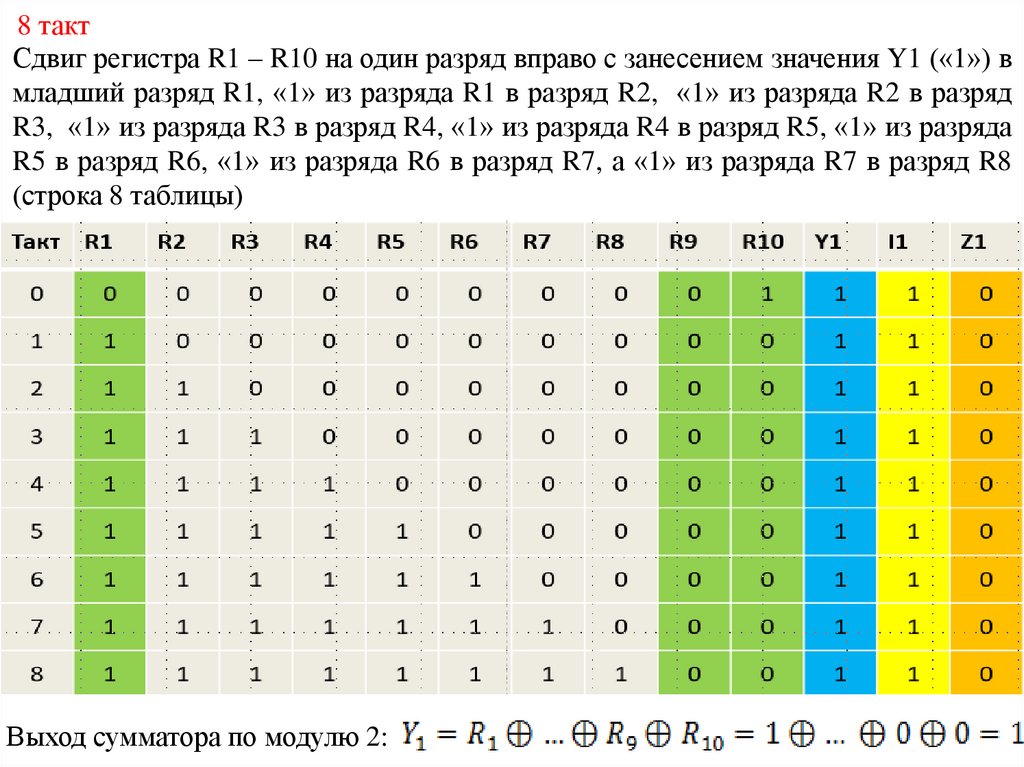

12.

8 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, «1» из разряда R4 в разряд R5, «1» из разряда

R5 в разряд R6, «1» из разряда R6 в разряд R7, а «1» из разряда R7 в разряд R8

(строка 8 таблицы)

Выход сумматора по модулю 2:

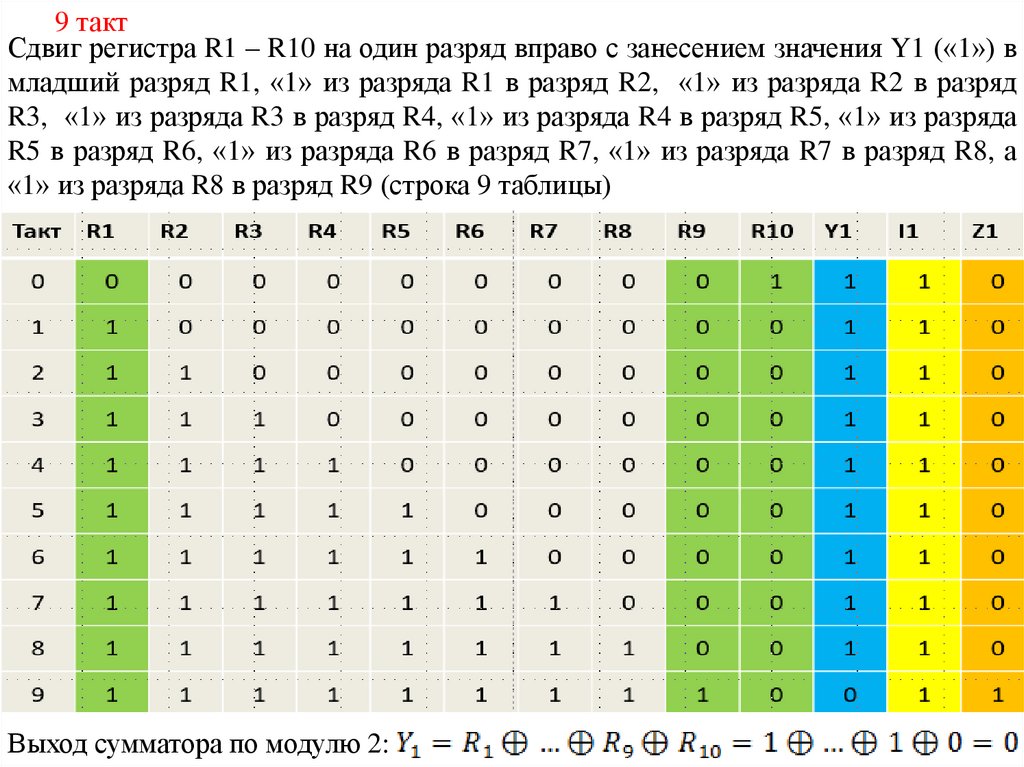

13.

9 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («1») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, «1» из разряда R4 в разряд R5, «1» из разряда

R5 в разряд R6, «1» из разряда R6 в разряд R7, «1» из разряда R7 в разряд R8, а

«1» из разряда R8 в разряд R9 (строка 9 таблицы)

Выход сумматора по модулю 2:

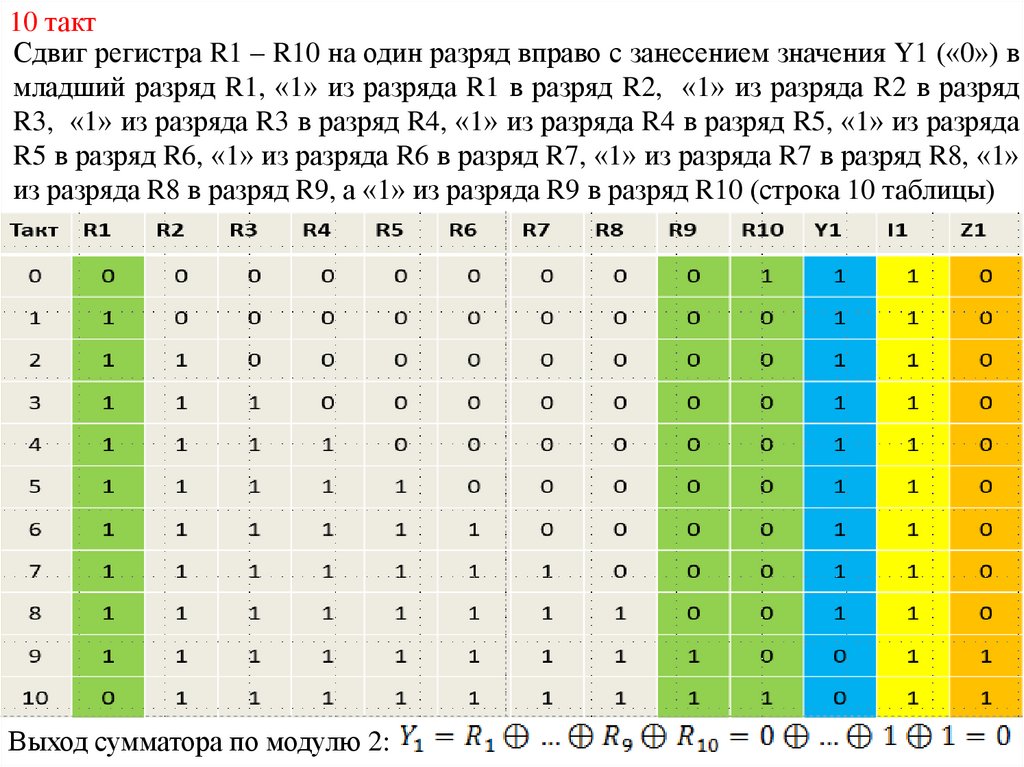

14.

10 тактСдвиг регистра R1 – R10 на один разряд вправо с занесением значения Y1 («0») в

младший разряд R1, «1» из разряда R1 в разряд R2, «1» из разряда R2 в разряд

R3, «1» из разряда R3 в разряд R4, «1» из разряда R4 в разряд R5, «1» из разряда

R5 в разряд R6, «1» из разряда R6 в разряд R7, «1» из разряда R7 в разряд R8, «1»

из разряда R8 в разряд R9, а «1» из разряда R9 в разряд R10 (строка 10 таблицы)

Выход сумматора по модулю 2:

15.

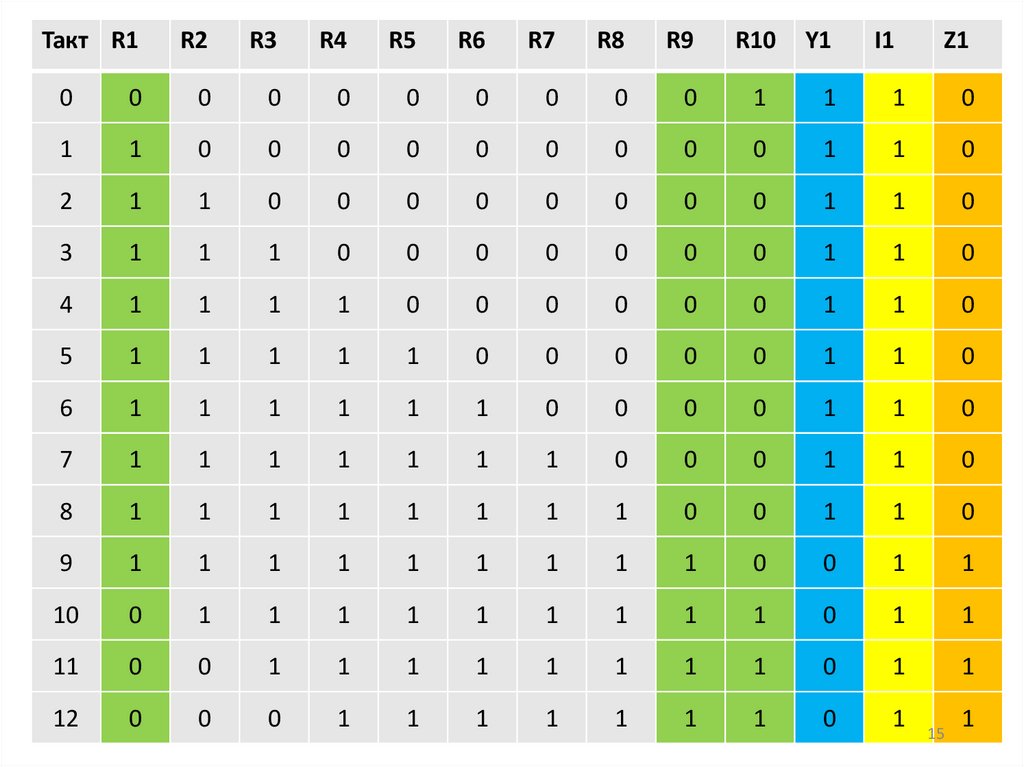

Такт R1R2

R3

R4

R5

R6

R7

R8

R9

R10

Y1

I1

Z1

0

0

0

0

0

0

0

0

0

0

1

1

1

0

1

1

0

0

0

0

0

0

0

0

0

1

1

0

2

1

1

0

0

0

0

0

0

0

0

1

1

0

3

1

1

1

0

0

0

0

0

0

0

1

1

0

4

1

1

1

1

0

0

0

0

0

0

1

1

0

5

1

1

1

1

1

0

0

0

0

0

1

1

0

6

1

1

1

1

1

1

0

0

0

0

1

1

0

7

1

1

1

1

1

1

1

0

0

0

1

1

0

8

1

1

1

1

1

1

1

1

0

0

1

1

0

9

1

1

1

1

1

1

1

1

1

0

0

1

1

10

0

1

1

1

1

1

1

1

1

1

0

1

1

11

0

0

1

1

1

1

1

1

1

1

0

1

1

12

0

0

0

1

1

1

1

1

1

1

0

1

15

1

16.

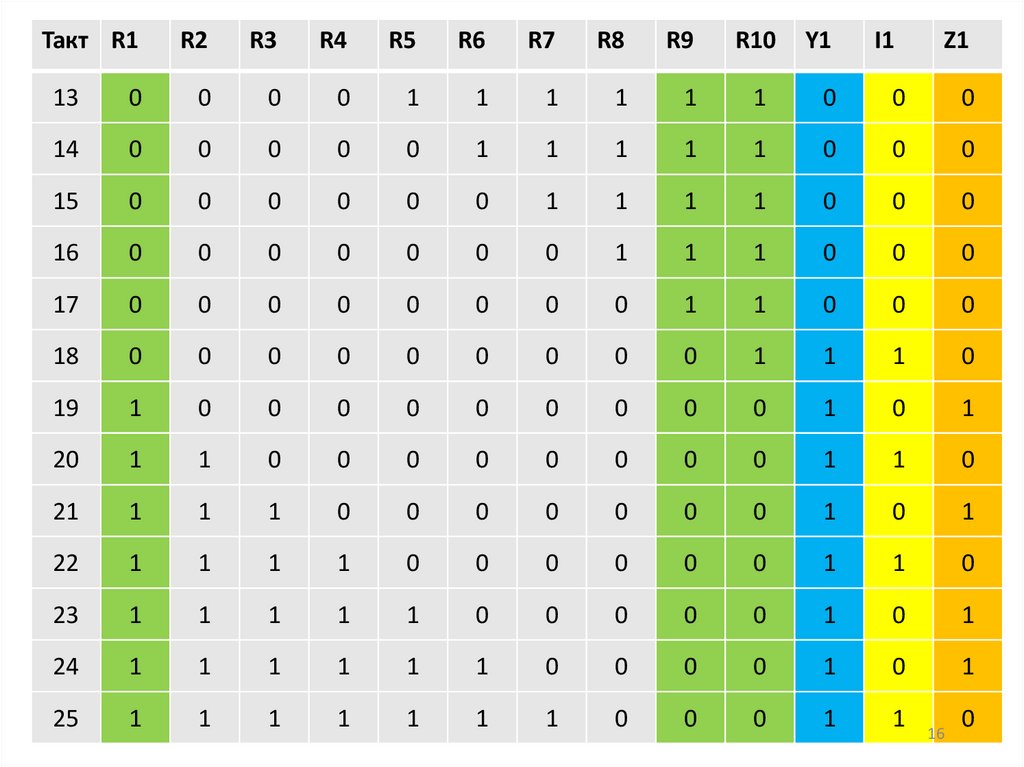

Такт R1R2

R3

R4

R5

R6

R7

R8

R9

R10

Y1

I1

Z1

13

0

0

0

0

1

1

1

1

1

1

0

0

0

14

0

0

0

0

0

1

1

1

1

1

0

0

0

15

0

0

0

0

0

0

1

1

1

1

0

0

0

16

0

0

0

0

0

0

0

1

1

1

0

0

0

17

0

0

0

0

0

0

0

0

1

1

0

0

0

18

0

0

0

0

0

0

0

0

0

1

1

1

0

19

1

0

0

0

0

0

0

0

0

0

1

0

1

20

1

1

0

0

0

0

0

0

0

0

1

1

0

21

1

1

1

0

0

0

0

0

0

0

1

0

1

22

1

1

1

1

0

0

0

0

0

0

1

1

0

23

1

1

1

1

1

0

0

0

0

0

1

0

1

24

1

1

1

1

1

1

0

0

0

0

1

0

1

25

1

1

1

1

1

1

1

0

0

0

1

1

16

0

17.

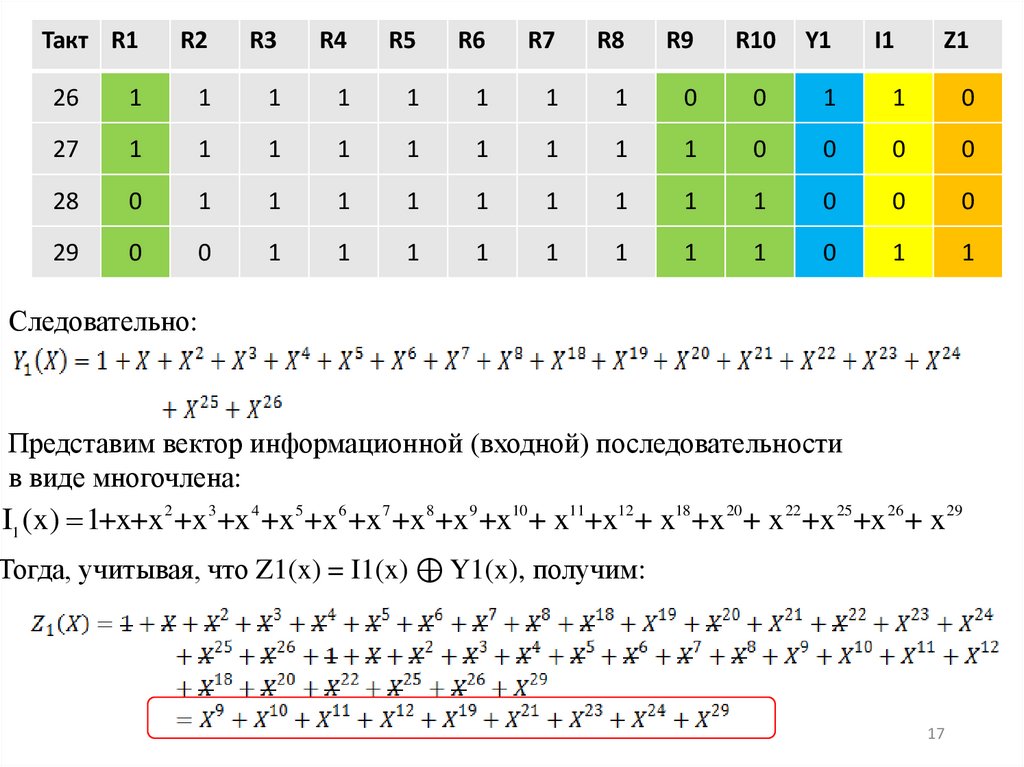

Такт R1R2

R3

R4

R5

R6

R7

R8

R9

R10

Y1

I1

Z1

26

1

1

1

1

1

1

1

1

0

0

1

1

0

27

1

1

1

1

1

1

1

1

1

0

0

0

0

28

0

1

1

1

1

1

1

1

1

1

0

0

0

29

0

0

1

1

1

1

1

1

1

1

0

1

1

Следовательно:

Представим вектор информационной (входной) последовательности

в виде многочлена:

I1 (x) 1+x+x 2 +x3 +x 4 +x5 +x 6 +x 7 +x8 +x9 +x10 + x11+x12 + x18+x 20 + x22 +x 25+x 26 + x29

Тогда, учитывая, что Z1(x) = I1(x) ⊕ Y1(x), получим:

17

Электроника

Электроника