Похожие презентации:

Средства проектирования цифровых устройств с использованием программируемых логических интегральных схем

1.

II.Средства проектированияцифровых устройств с

использованием

программируемых логических

интегральных схем

• Архитектура интегральных схем с

программируемой структурой (ПЛИС).

• Основы языка VHDL и Verilog.

• Процесс проектирования цифровых

устройств с использованием ПЛИС.

1

2. V.I Архитектура интегральных схем с программируемой структурой (ПЛИС)

Список дополнительной литературы:

Грушвицкий Р. И., Мурсаев А. Х., Угрюмов Е. П.

Проектирование систем на микросхемах с программируемой

структурой, БХВ-Петербург, 2006, 708 с.

Сергиенко А. М. VHDL для проектирования вычислительных

устройств – К ЧП «Корнейчук», ООО «ТИД «ДС», 2003 – 208 с.

Зотов В. Ю. Проектирование цифровых устройств на основе

ПЛИС фирмы Xilinx в САПР WebPACK ISE. – М.: Горячая

линия - Телеком, 2003. – 624 с.

IEEE VHDL-93 Standard 2000 Revision

Xilinx ISE Help

Spartan-3 FPGA Family: Complete Data Sheet. Xilinx Inc.

XC9500 CPLD Family: Complete Data Sheet. Xilinx Inc.

2

3. Классификация ИС по способу обеспечения функциональности

Интегральные схемыСтандартные ИС

С фиксированным

функционированием

МИС, СИС, БИС, СБИС

Специализированные ИС

Полузаказные ИС

Заказные ИС

С изменяемым

функционированием

С изменением

программы

МП, МК, SOPC

С изменением

структуры

CPLD,FPGA,

SOPC,...

Полуфабрикаты

МаБИС

3

4. Эволюция ПЛИС

Полузаказныеинтегральные схемы

Программируемые пользователем

интегральные схемы

Базовые матричные

кристаллы (Gate Array,

GA)

Программируемая

матричная логика

(Programmable Array

Logic, PAL)

Программируемые

логические матрицы

(Programmable Logic

Array, PLA)

Базовые матричные

кристаллы на основе

БИС, СБИС

Программируемые

вентильные матрицы

(Field Programmable Gate

Arrays, FPGA)

Сложные

программируемые

логические устройства

(Complex Programmable

Logic Devices, CPLD)

Структурированные

полузаказные СБИС

(Structured Application

Specific Integrated Circuits,

Structured ASIC)

ПЛИС с комбинированной

структурой

Системы на кристалле

(System on Programmable

Chip, SOPC)

4

5.

Преимуществами современных ПЛИСявляются:

•Простота и малое время проектирования.

•Низкая стоимость разработки

•Сокращение используемого пространства печатных плат.

•Более низкая стоимость в с равнении с использованием

отдельных интегральных схем средней степени

интеграции

•Более продолжительное обращение продукта на рынке

за счет возможности перепрограммирования.

•Возможность создание динамически реконфигурируемых

устройств.

К недостаткам можно отнести более низкую скорость работы

ПЛИС в сравнении с ASIC, а также нерентабельность

использования в крупносерийном производстве.

5

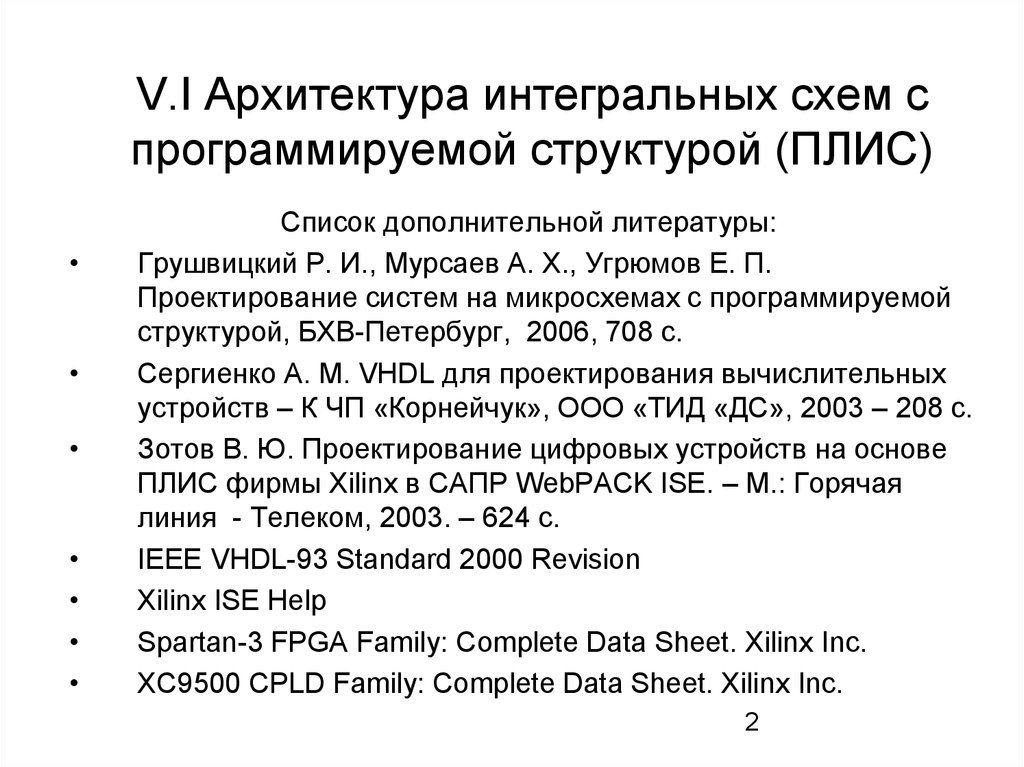

6. Сравнение проектов на ASIC, FPGA,PSoC

ПоказательASIC

FPGA

PSoC

Быстродействие

очень высокое

высокое

высокое

Плотность упаковки элементов

очень высокая

средняя

очень высокая

Стоимость при единичном производстве

очень высокая

средняя

средняя

Стоимость при серийном производстве

низкая

высокая

низкая

Невозвратимые затраты

высокие

нет

нет

Время разработки

большое

малое

малое

Энергопотребление

низкое

высокое

низкое

Сложность разработки

высокая

средняя

средняя

Время отладки

очень большое

малое

малое

Сложность тестирования

высокая

низкая

низкая

Время производства

большое

среднее

среднее

Время выхода на рынок

большое

среднее

среднее

Возможности модернизации

«жесткая» архитектура

в нерабочем режиме

в рабочем режиме

Риск изготовителя

очень высокий

низкий

низкий

Степень автоматизации процесса проектирования

средняя

высокая

высокая

Минимальный объем заказов

высокий

нет

нет

6

7.

Программируемые логические матрицыX1

1

X2

1

Xm

Матрица

И

...

1

&

t1

&

...

tk

F1

1

...

...

Fn

1

Матрица ИЛИ

7

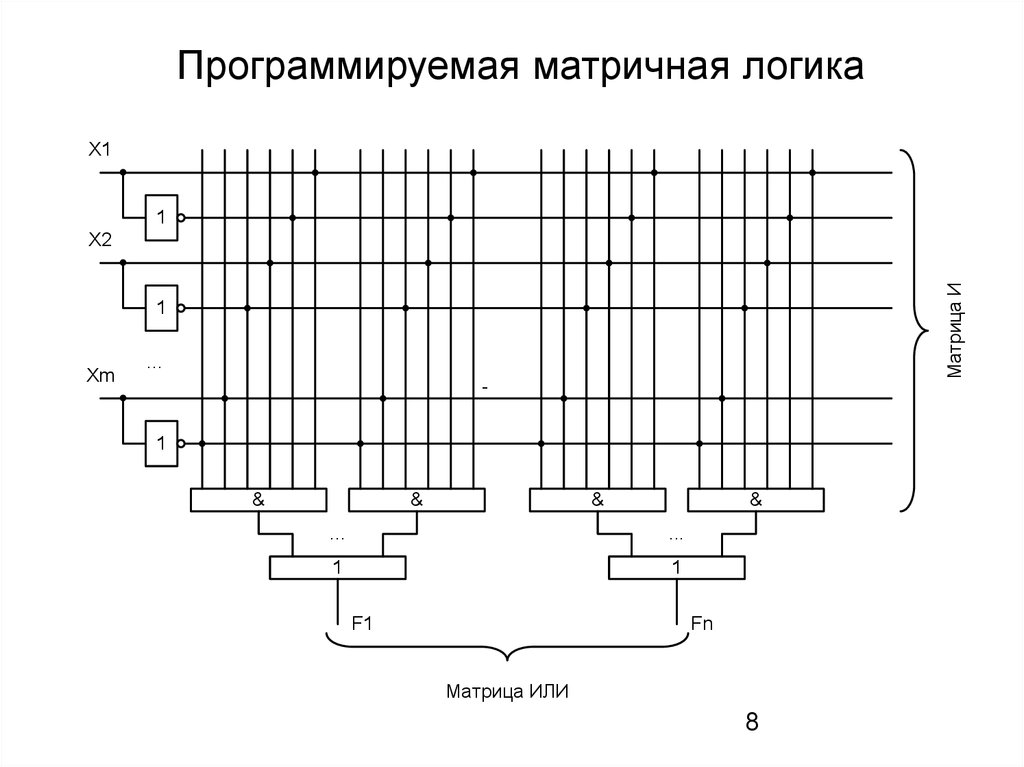

8.

Программируемая матричная логикаX1

1

Матрица И

X2

1

Xm

...

1

&

&

&

&

...

...

1

1

F1

Fn

Матрица ИЛИ

8

9.

Расширение функциональных возможностей ПЛМ иПМЛ возможно с использованием:

•введения обратных и межэлементных связей, что

позволяет наращивать количество термов функций;

•введения элементов памяти, что позволяет проектировать

на ПМЛ и ПЛМ синхронные цифровые автоматы;

•программирования выходных буферов для выдачи

выходных сигналов в прямом или инверсном виде;

•использования мультиплексоров для выбора

альтернативных путей прохождения сигналов;

•репрограммируемых точек связи и памяти конфигурации,

позволяющим перепрограммировать функциональность и

связность частей ПЛМ и ПМЛ.

9

10.

Структура базовых матричных кристалловТиповые структуры

макроячеек

1

1

1234-

4

2

Макроячейки

Буферные ячейки

Внешние контактные площадки

Участки для прокладки трасс соединений

1

3

2

1 - Базовые ячейки (БЯ);

2 - Промежутки между БЯ для

прокладки трасс (транзитные

соединения).

10

11. Классификация ПЛИС по типу программируемых связей

AПЛИС

Однократно

программируемые

Ячейка

памяти

На основе

перемычек

B

На основе

EPROM-OTP

A

Репрограммируемые

На основе

EPROM

E

C

На основе

EEPROM

На основе SRAM

D

11

12. Архитектура сложных программируемых логических устройств (CPLD)

CPLDSPLD

SPLD

GCK, GSR, GTS

GCK, GSR, GTS

МЯ0

МЯ0

МЯ1

I/O

МЯ2

...

МЯ1

ПЛМ или

ПМЛ

Матрица

межсоединений

ПЛМ или

ПМЛ

МЯ2

...

МЯn

МЯn

12

I/O

13.

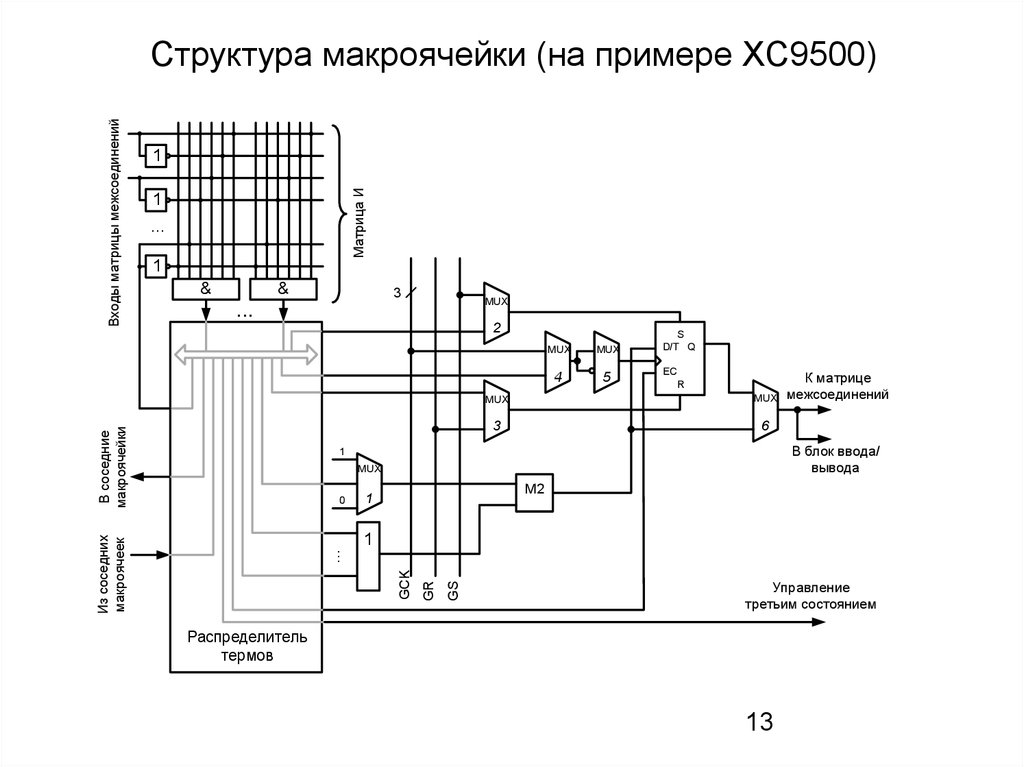

Матрица И1

1

...

1

&

&

3

MUX

...

2

В соседние

макроячейки

MUX

MUX

4

5

S

D/T Q

EC

R

MUX

MUX

3

6

MUX

0

К матрице

межсоединений

В блок ввода/

вывода

1

M2

1

GS

GCK

...

Из соседних

макроячеек

1

GR

Входы матрицы межсоединений

Структура макроячейки (на примере XC9500)

Управление

третьим состоянием

Распределитель

термов

13

14.

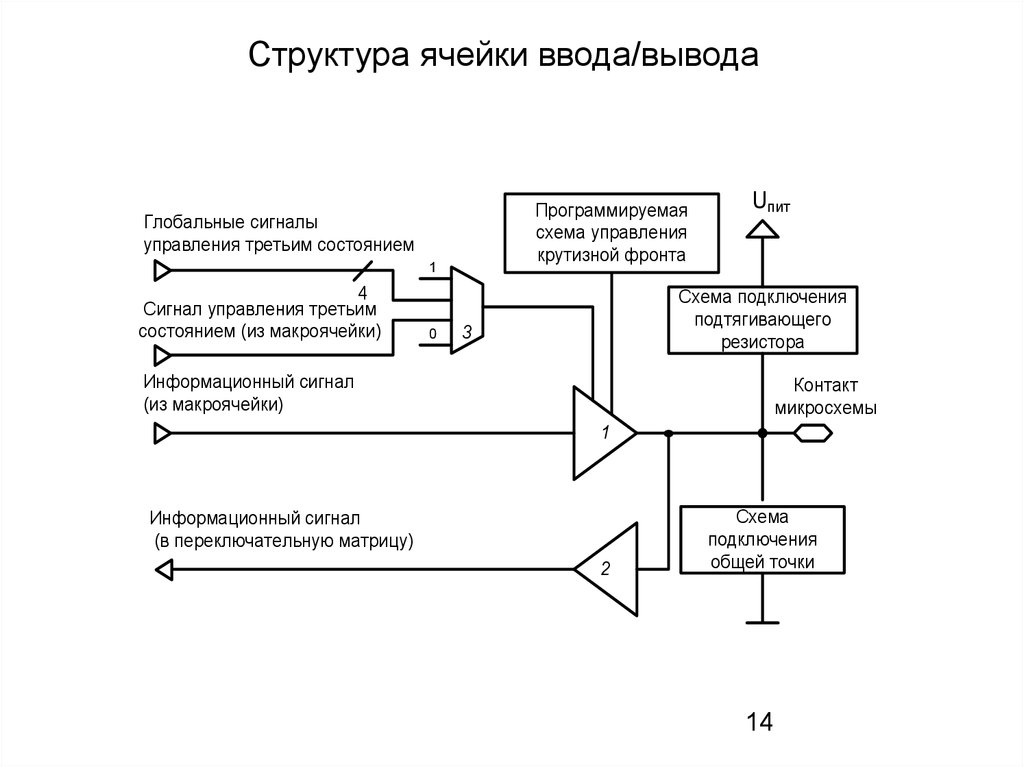

Структура ячейки ввода/выводаПрограммируемая

схема управления

крутизной фронта

Глобальные сигналы

управления третьим состоянием

1

4

Сигнал управления третьим

состоянием (из макроячейки)

0

Uпит

Схема подключения

подтягивающего

резистора

3

Информационный сигнал

(из макроячейки)

Контакт

микросхемы

1

Информационный сигнал

(в переключательную матрицу)

2

Схема

подключения

общей точки

14

15.

ПРИМЕРАрхитектура ПЛИС семейства кристаллов

XC9500

15

16. Функциональный блок CPLD (на примере XC9500)

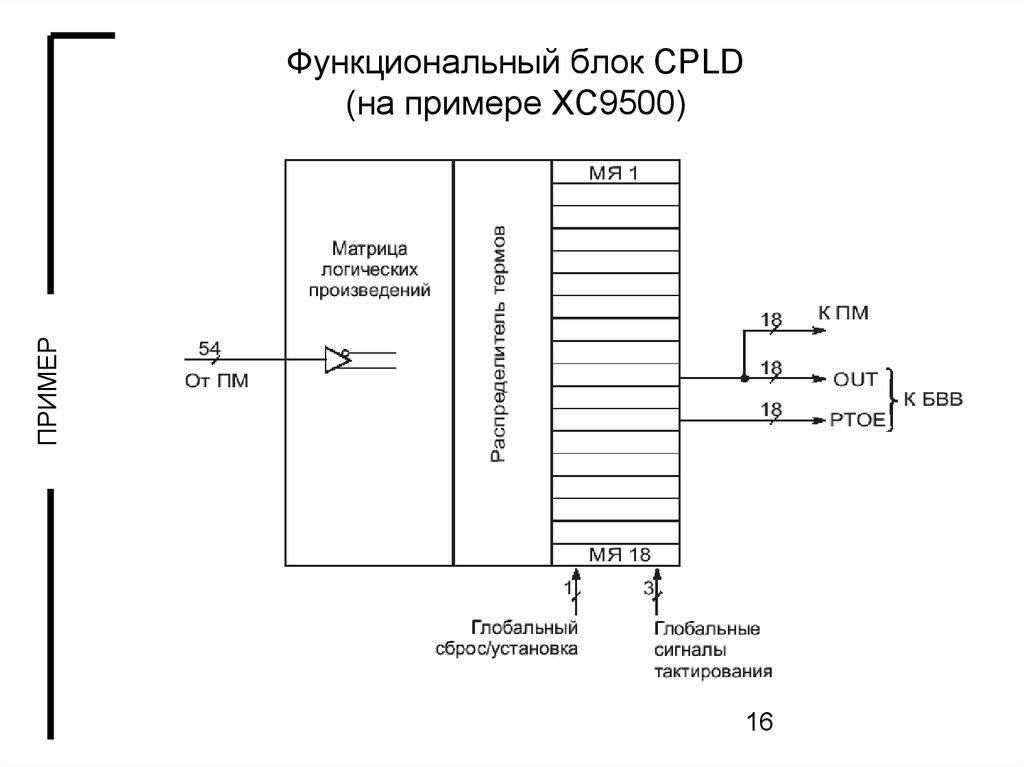

ПРИМЕРФункциональный блок CPLD

(на примере XC9500)

16

17. Макроячейка (на примере XC9500)

ПРИМЕРМакроячейка (на примере XC9500)

17

18.

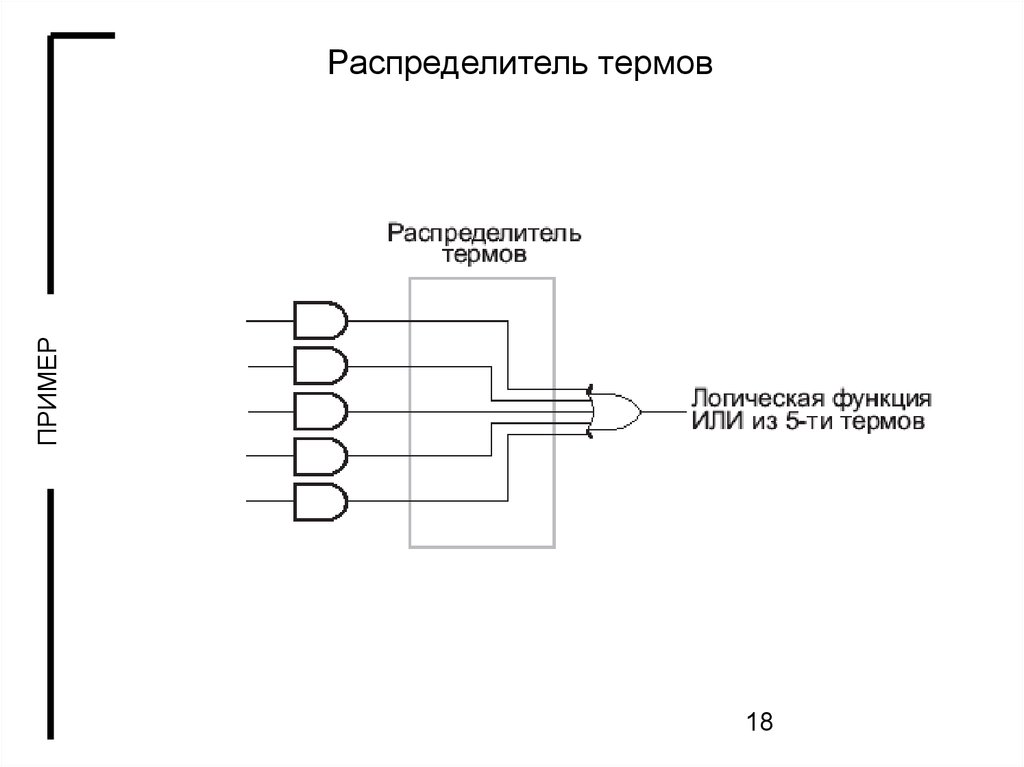

ПРИМЕРРаспределитель термов

18

19. Увеличение функциональности распределитель термов CPLD

ПРИМЕРУвеличение функциональности распределитель

термов CPLD

19

20. Программирование распределителя термов CPLD

ПРИМЕРПрограммирование распределителя термов

CPLD

20

21.

ПРИМЕРСхема распределения тактовых сигналов

(на примере XC9500)

21

22.

Программируемые вентильные матрицы(FPGA)

Конфигурируемый

логический блок

Коммутационный

блок

Менеджер

синхросигналов

C

C

П

П

C

У

У

Умножитель

Блоки ввода/вывода

Блоки ввода/вывода

Блоки ввода/вывода

Сеть распределения

синхросигналов

Цепь

переключательной

матрицы

C

Блоки ввода/вывода

Блок ввода/вывода

пользовательских сигналов

Блок памяти

Блок ввода/вывода

глобальных сигналов

22

23.

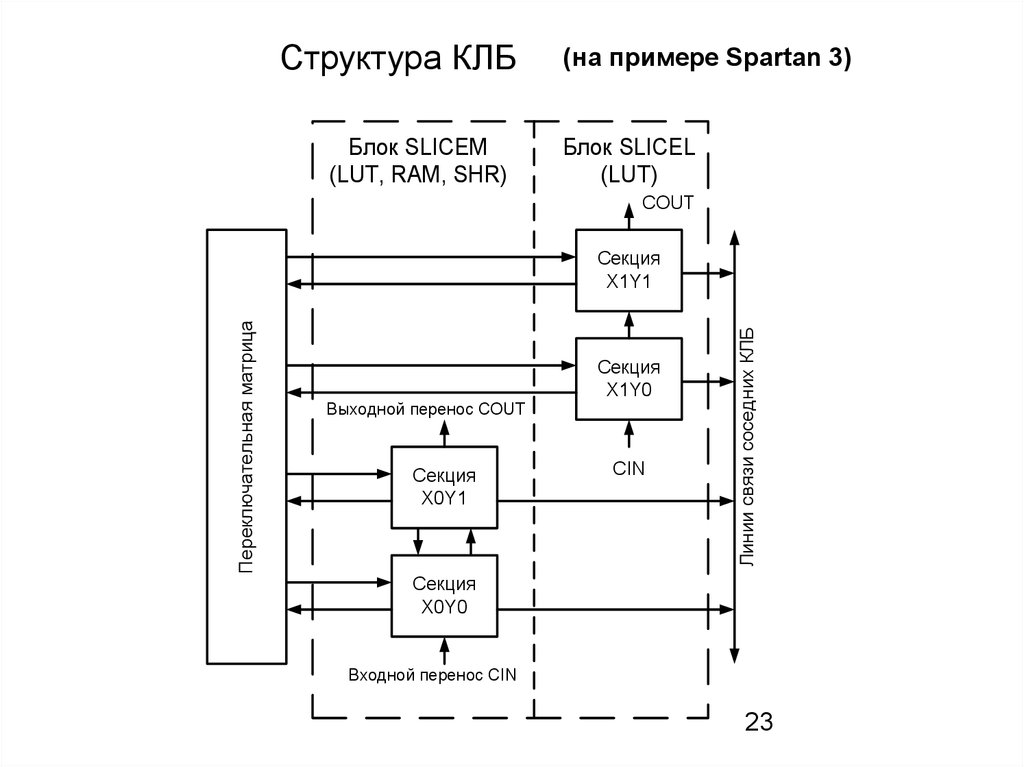

Структура КЛББлок SLICEM

(LUT, RAM, SHR)

(на примере Spartan 3)

Блок SLICEL

(LUT)

COUT

Выходной перенос COUT

Секция

X0Y1

Секция

X1Y0

CIN

Линии связи соседних КЛБ

Переключательная матрица

Секция

X1Y1

Секция

X0Y0

Входной перенос CIN

23

24.

COUTYB

1

0

2

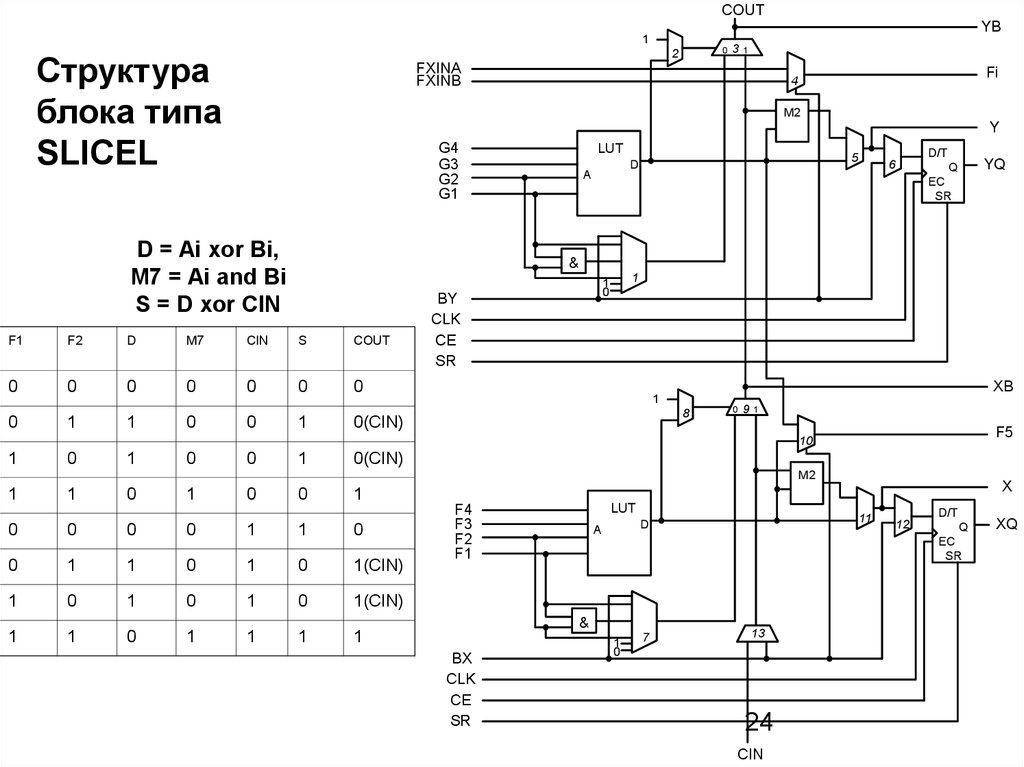

Структура

блока типа

SLICEL

3

1

FXINA

FXINB

Fi

4

M2

Y

G4

G3

G2

G1

D = Ai xor Bi,

M7 = Ai and Bi

S = D xor CIN

LUT

A

D/T

5

D

6

Q

EC

SR

YQ

&

F1

F2

D

M7

CIN

S

COUT

0

0

0

0

0

0

0

0

1

1

0

0

1

0(CIN)

1

1

0

BY

CLK

CE

SR

XB

1

8

0

91

F5

10

1

0

1

0

0

1

0(CIN)

1

1

0

1

0

0

1

M2

0

0

0

0

1

1

0

0

1

1

0

1

0

1(CIN)

1

0

1

0

1

0

1(CIN)

1

1

0

1

1

1

1

LUT

F4

F3

F2

F1

&

BX

CLK

CE

SR

11

D

A

1

0

7

X

13

24

CIN

D/T

12

Q

EC

SR

XQ

25.

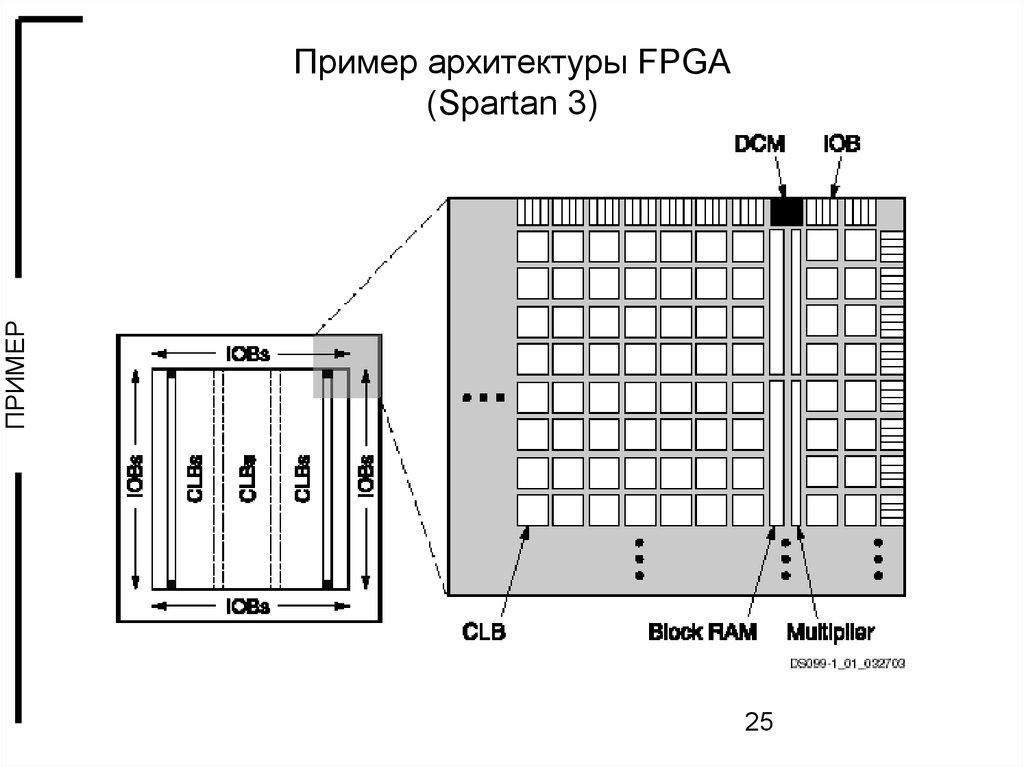

ПРИМЕРПример архитектуры FPGA

(Spartan 3)

25

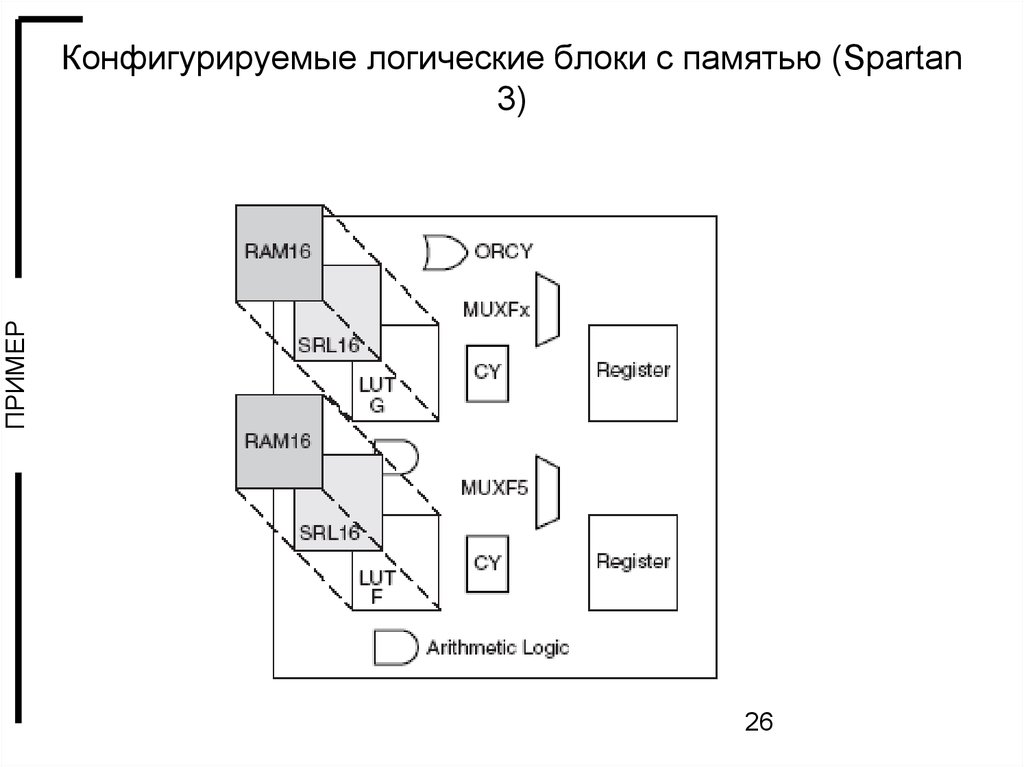

26. Конфигурируемые логические блоки с памятью (Spartan 3)

ПРИМЕРКонфигурируемые логические блоки с памятью (Spartan

3)

26

27.

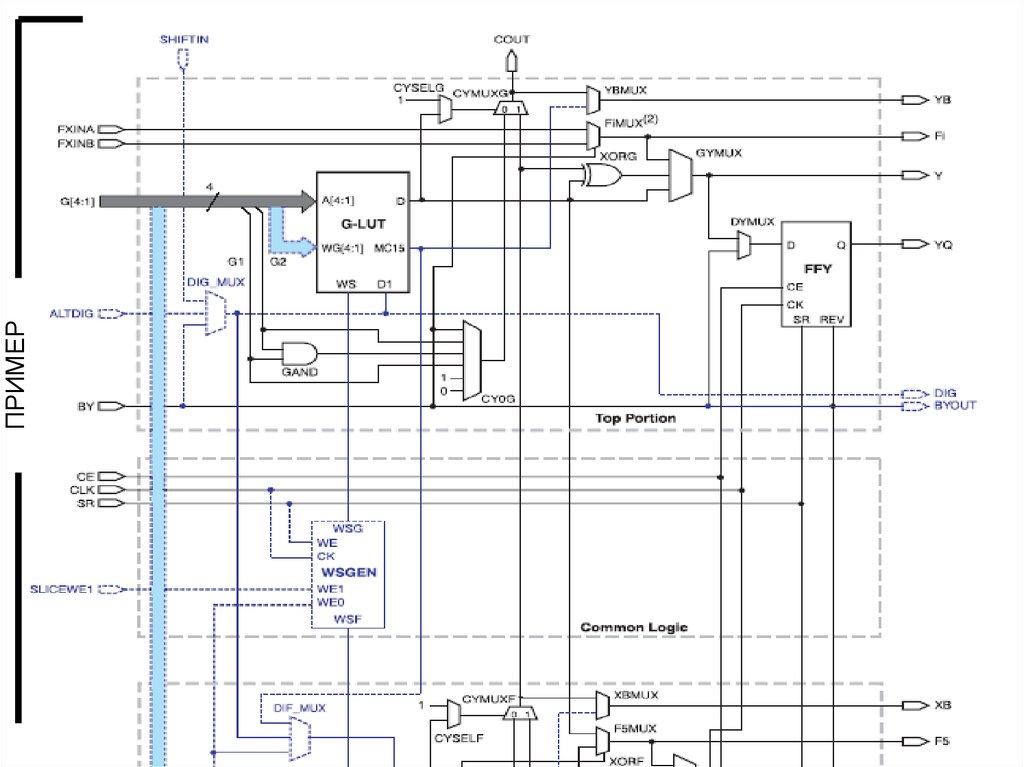

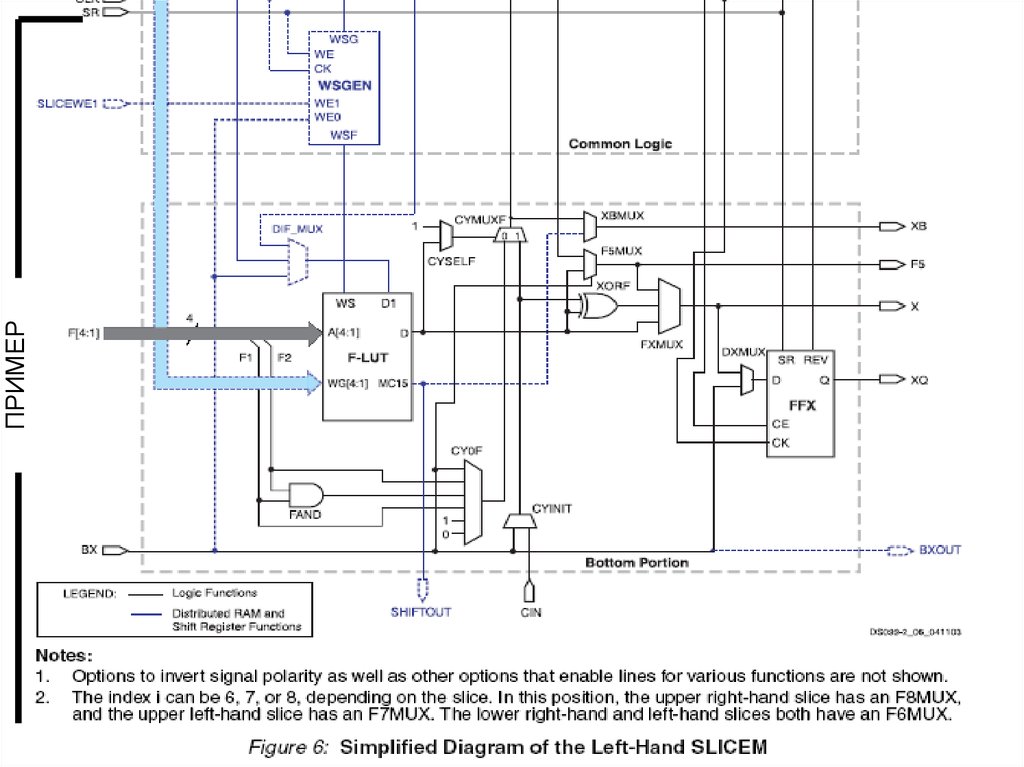

ПРИМЕРОрганизация

логического блока с

памятью в Spartan 3

27

28.

28ПРИМЕР

29.

29ПРИМЕР

30.

ПРИМЕРБлок управления синхронизацией (Spartan 3)

30

31. Устройство коррекции расфазирования синхросигналов (Delay Locked Loops)

ПРИМЕРУстройство коррекции расфазирования синхросигналов

(Delay Locked Loops)

31

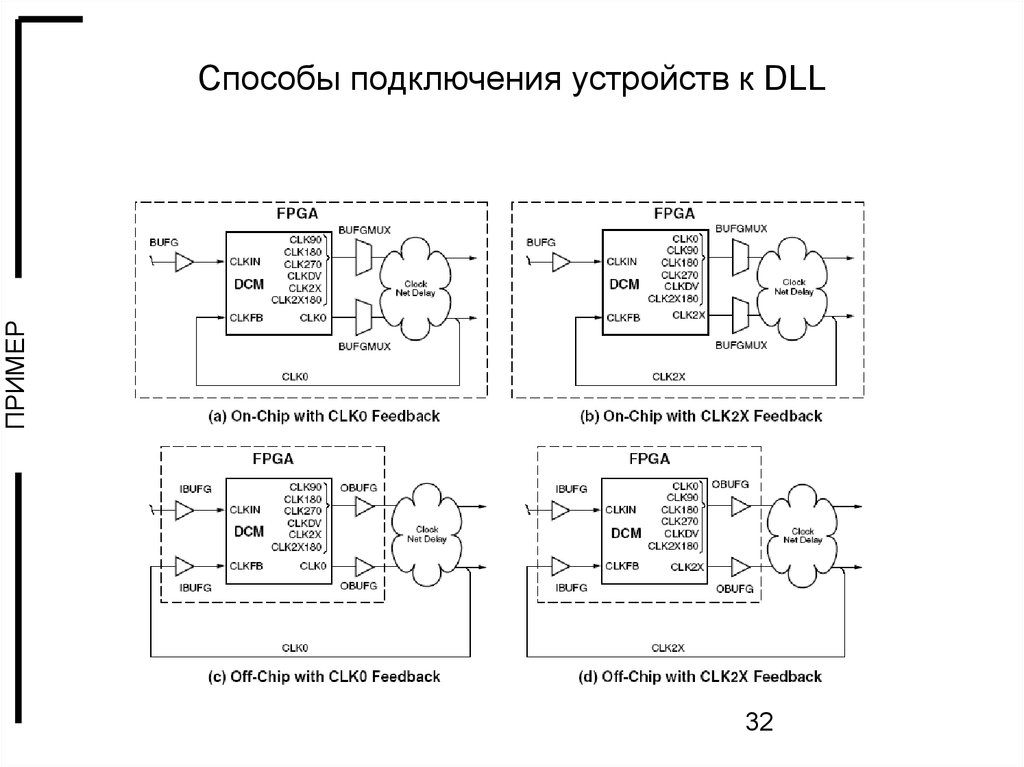

32. Способы подключения устройств к DLL

ПРИМЕРСпособы подключения устройств к DLL

32

33.

ПРИМЕРСеть распределения синхросигналов (Spartan 3)

33

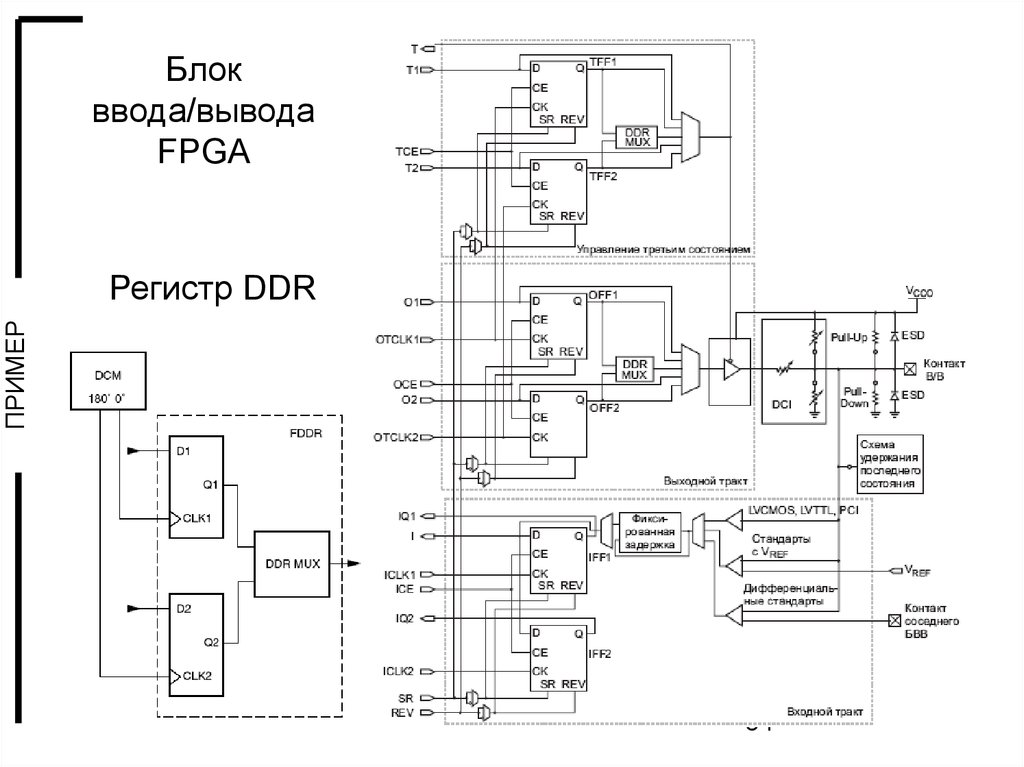

34. Блок ввода/вывода FPGA

ПРИМЕРРегистр DDR

34

35. Схема управления выходом с третьим состоянием

ПРИМЕРСхема управления выходом с третьим состоянием

35

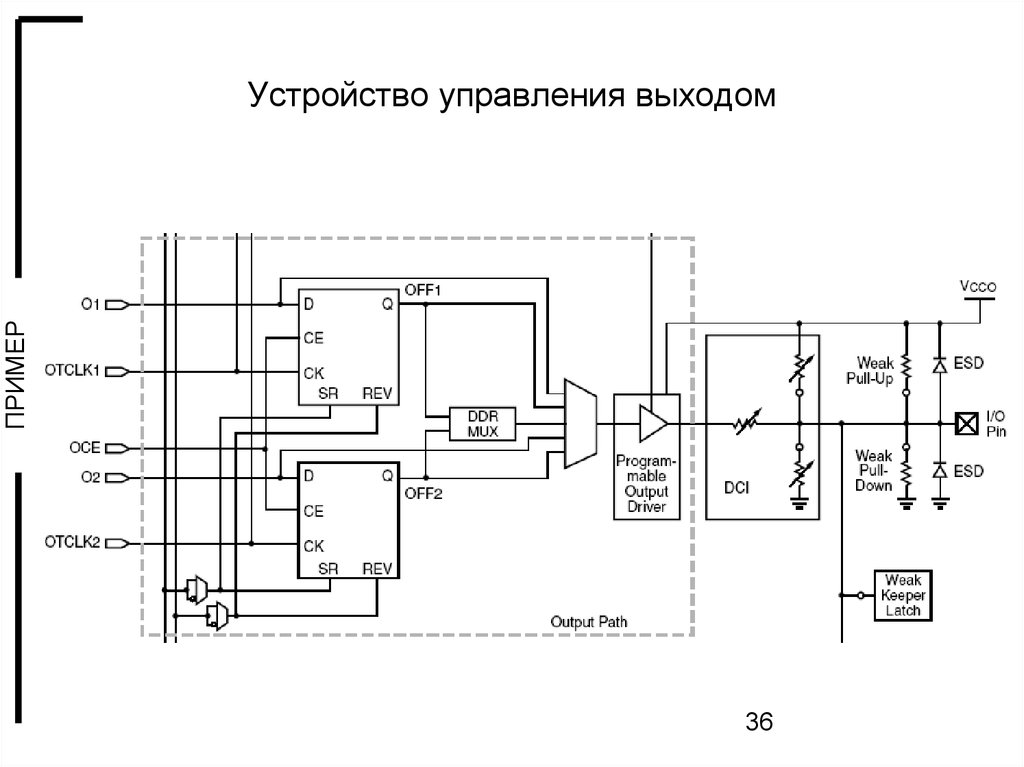

36. Устройство управления выходом

ПРИМЕРУстройство управления выходом

36

37. Устройство управления входом (Spartan 3)

ПРИМЕРУстройство управления входом (Spartan 3)

37

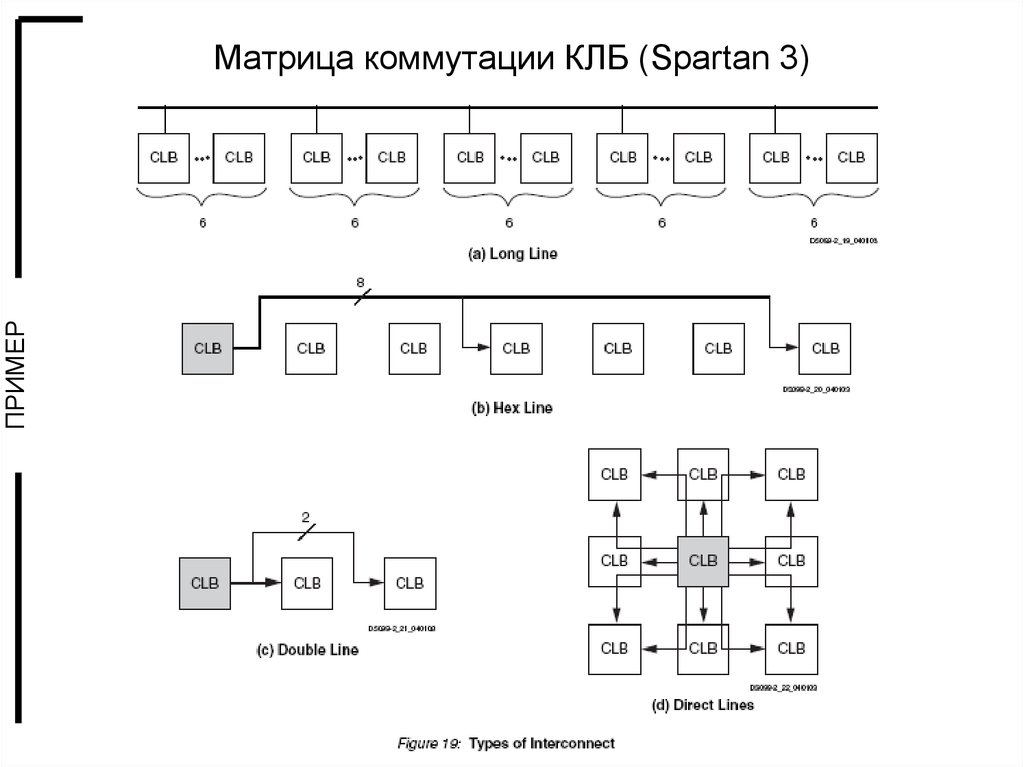

38. Матрица коммутации КЛБ (Spartan 3)

ПРИМЕРМатрица коммутации КЛБ (Spartan 3)

38

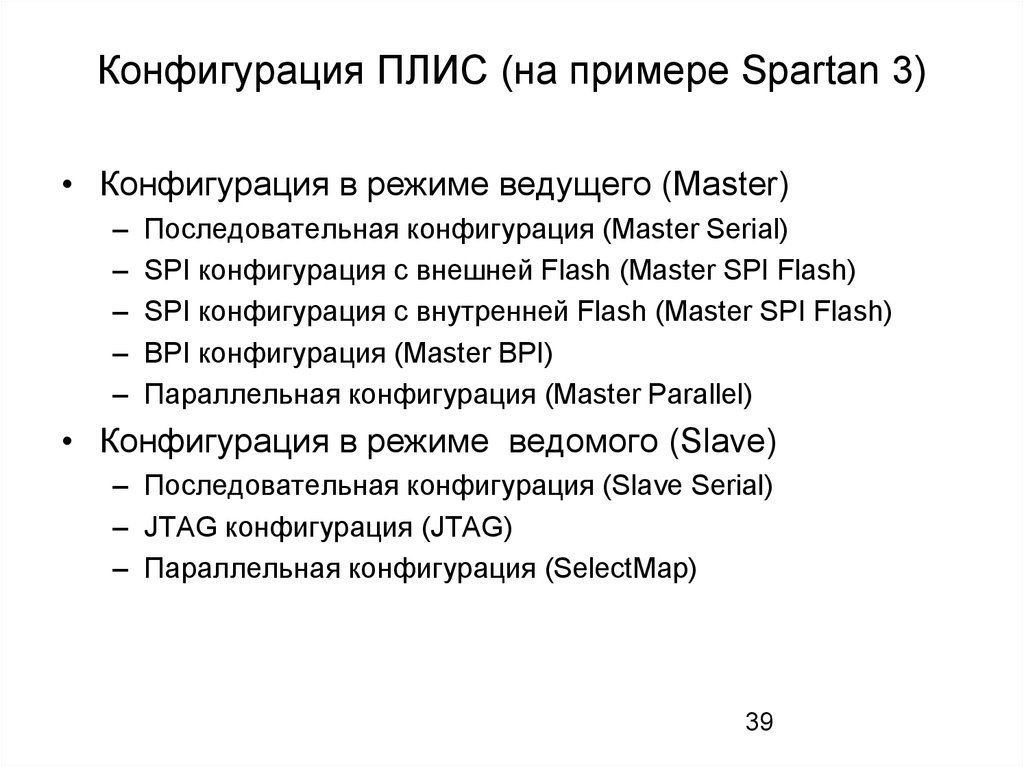

39. Конфигурация ПЛИС (на примере Spartan 3)

• Конфигурация в режиме ведущего (Master)–

–

–

–

–

Последовательная конфигурация (Master Serial)

SPI конфигурация с внешней Flash (Master SPI Flash)

SPI конфигурация с внутренней Flash (Master SPI Flash)

BPI конфигурация (Master BPI)

Параллельная конфигурация (Master Parallel)

• Конфигурация в режиме ведомого (Slave)

– Последовательная конфигурация (Slave Serial)

– JTAG конфигурация (JTAG)

– Параллельная конфигурация (SelectMap)

39

40.

Последовательная конфигурация (Master Serial)ПРИМЕР

Схема конфигурирования по JTAG интерфейсу (3.3 V)

40

41.

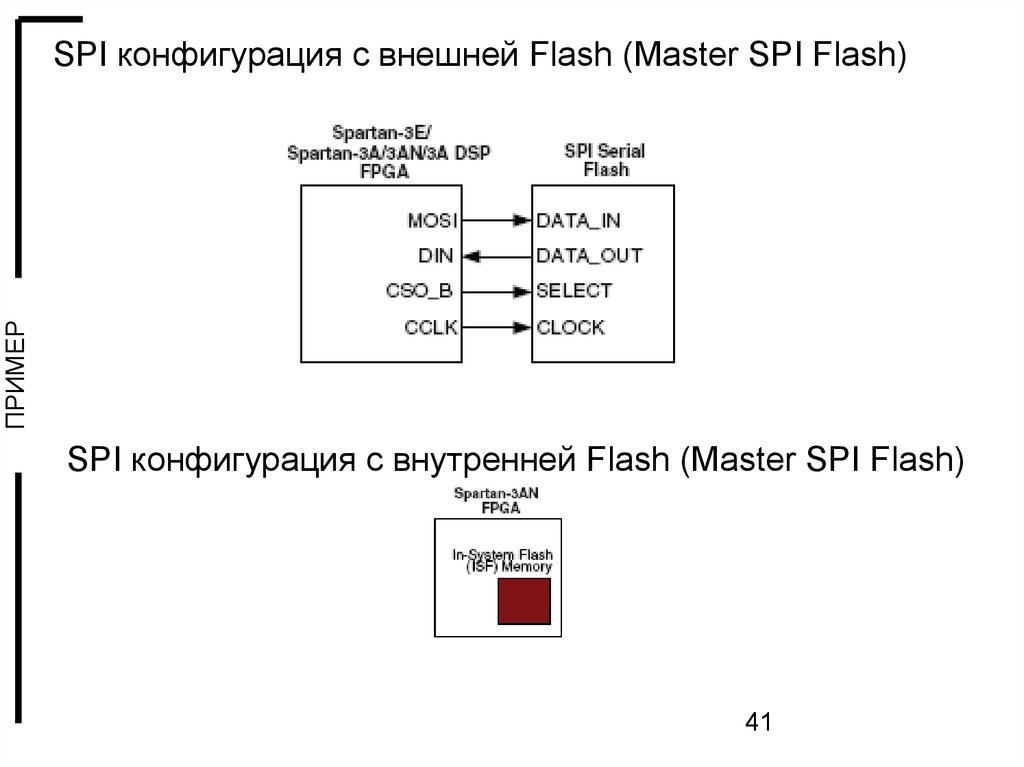

ПРИМЕРSPI конфигурация с внешней Flash (Master SPI Flash)

SPI конфигурация с внутренней Flash (Master SPI Flash)

41

42.

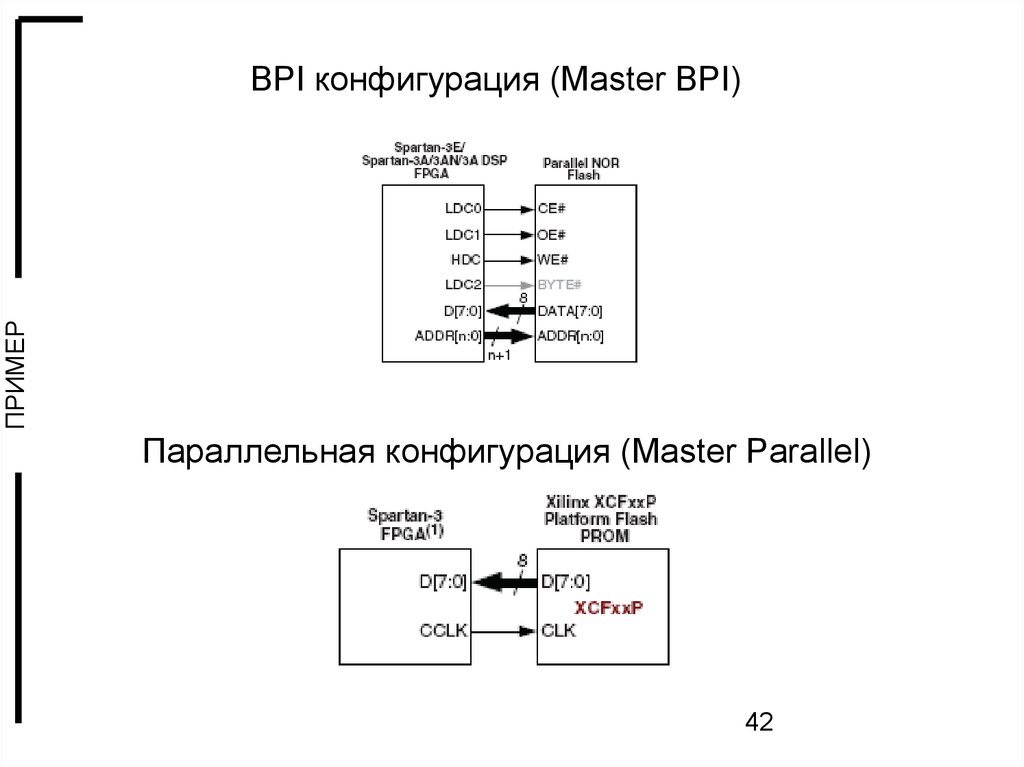

ПРИМЕРBPI конфигурация (Master BPI)

Параллельная конфигурация (Master Parallel)

42

43.

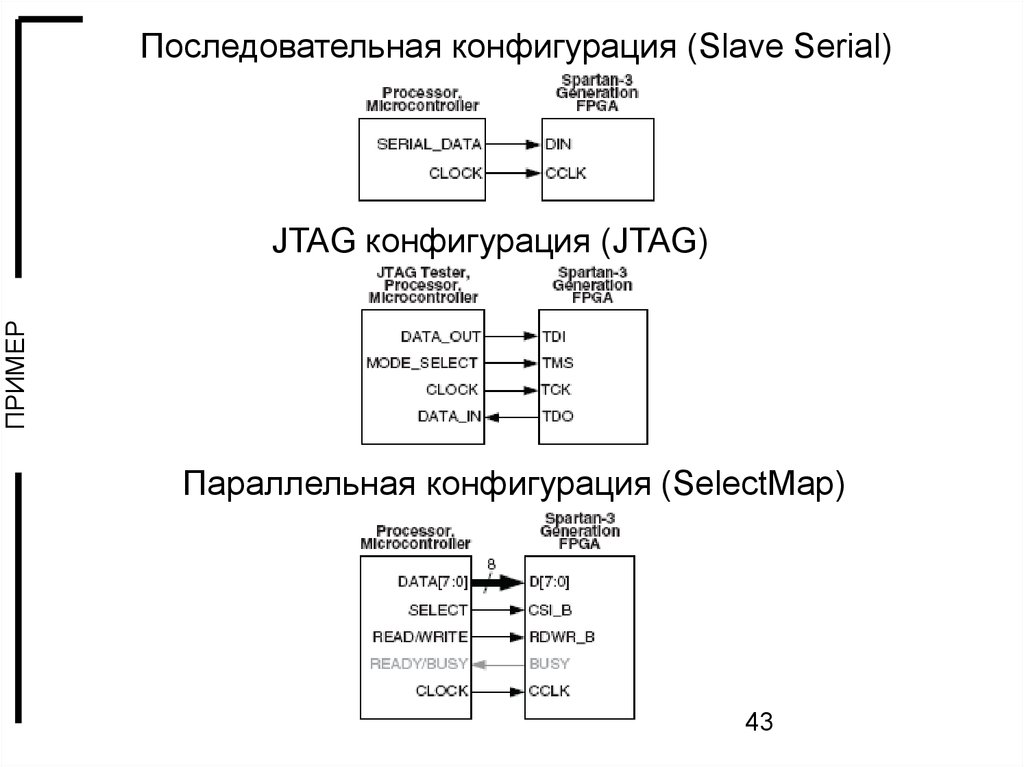

Последовательная конфигурация (Slave Serial)ПРИМЕР

JTAG конфигурация (JTAG)

Параллельная конфигурация (SelectMap)

43

44. Архитектура ПЛИС типа SOPC

Варианты реализации библиотечных блоков:Soft - ядра.

Firm - ядра.

Hard – ядра.

Назначение ядер:

Память (ОЗУ, FIFO, кэш- память, …).

АЛУ (умножители, …).

Интерфейсная логика (JTAG, PCI, SPI, UART, …).

МП и МК.

44

45.

Системы на платеEthernet

MAC

Audio

Codec

Power Supply

CLK

CLK

Interrupt

Controller

GP I/O

Address

Decode

Unit

CPU

UART

(uP / DSP)

CLK

SRAM

Memory

Controller

SRAM

SRAM

SDRAM

Timer

CoProc.

SDRAM

L

C

custom

IF-logic

Display

Controller

Images by H.Walder

Преимущества систем на плате:

– использование хорошо проверенных серийных компонентов;

– более простой процесс тестирования и отладки;

– возможность замены неисправных компонентов;

– низкая стоимость создания опытных образцов и малых

серий.

45

46.

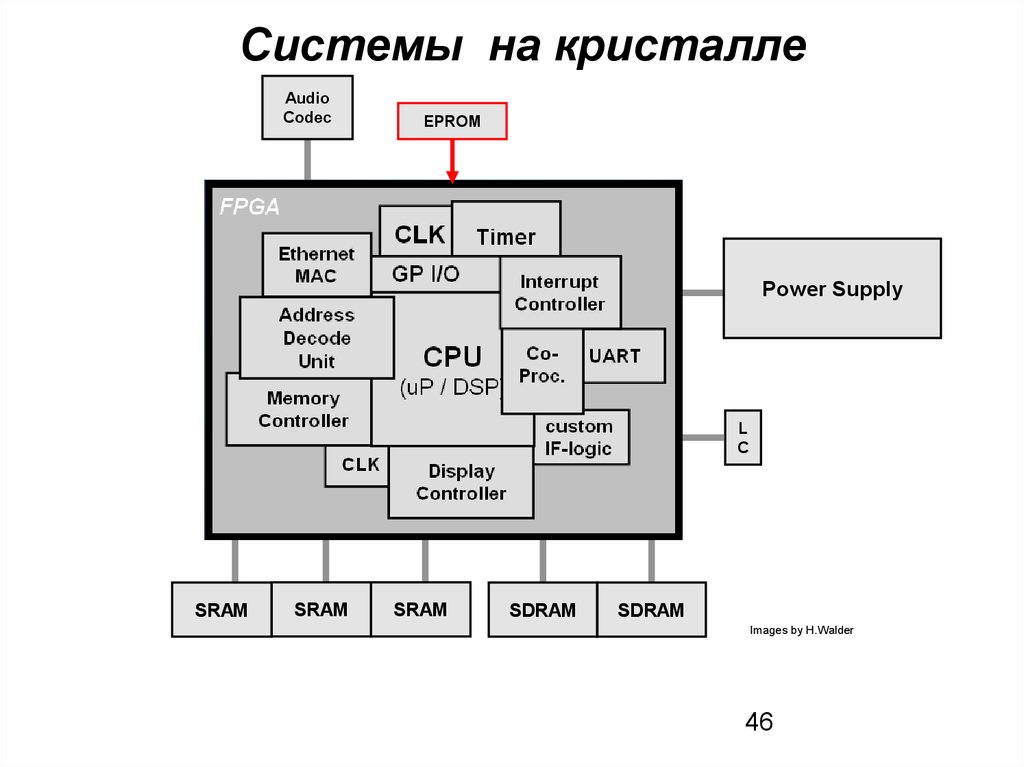

Системы на кристаллеAudio

Codec

EPROM

Power Supply

L

C

SRAM

SRAM

SRAM

SDRAM

SDRAM

Images by H.Walder

46

47.

Преимущества систем на кристалле:–возможность

получения

более

высоких

технических

показателей

(производительность,

энергопотребление,

массогабаритные характеристики);

– более низкая стоимость при крупносерийном выпуске.

– малые затраты на разработку и создание опытных образцов;

– возможность многократной

вероятность переделки платы;

коррекции

проекта,

меньше

– использование хорошо проверенных серийных изделий;

– более простой процесс тестирования и отладки (возможность

реализации и отладки «по частям»).

47

48.

Пример СнК на основе MicroBlazeI-Cache

BRAM

MicroBlaze

32-Bit RISC Core

D-Cache

BRAM

0,1…….32

Custom

Functions

Possible in

Virtex-II Pro

Dedicated Hard IP

PowerPC

405 Core

Data

OPB

PLB

On-Chip Peripheral Bus

Bus

Processor Local Bus

Bridge

Hi-Speed

Peripheral

Custom

Functions

UART

Off-Chip

Memory

Configurable

Sizes

Instruction

Arbiter

LocalLink™

FIFO Channels

Flexible Soft IP

10/100

E-Net

e.g.

Memory

Controller

GB

E-Net

On-Chip

Peripheral

FLASH/SRAM

48

Source: Xilinx

Arbiter

BRAM

Local Memory

Bus

Электроника

Электроника